MITSUBISHI <CONTROL / DRIVER IC>

)

M54977P

Bi-CMOS 12-BIT SERIAL-INPUT LATCHED DRIVER

DESCRIPTION

The M54977P is a semiconductor integrated circuit fabricated

using Bi-CMOS technology. It contains a serial input to

serial/parallel output 12-bit CMOS shift register and CMOS latch as

well as bipolar 12-bit parallel-output driver.

FEATURES

● Serial input to serial/parallel output

● Cascade connections possible through serial output

● Latch circuit included for each stage

● Enable input for output control

● Low supply current .................................. ICC ≥ 10µA at standby

● Serial input/output level is compatible with standard CMOS

● Driver : Withstand voltage ...................................... BVCEO ≥ 30V

Large drive current ................................ (IO(max)=200mA)

● Wide operating temperature range ..................... Ta=-20 – +75°C

APPLICATION

Thermal printer head dot driver, Serial-to parallel conversion,

Relay, solenoid driver

FUNCTION

The M54977P consists of an 12-bit D-type flip-flop, the output of

which is connected to 12 latches.

When data is applied to the serial data input (S-IN) and a clock

pulse is applied to clock input (T), an “L” to “H” change of the clock

will cause the data input signals to enter the internal shift registers

and the data in the shift registers will be shifted in order.

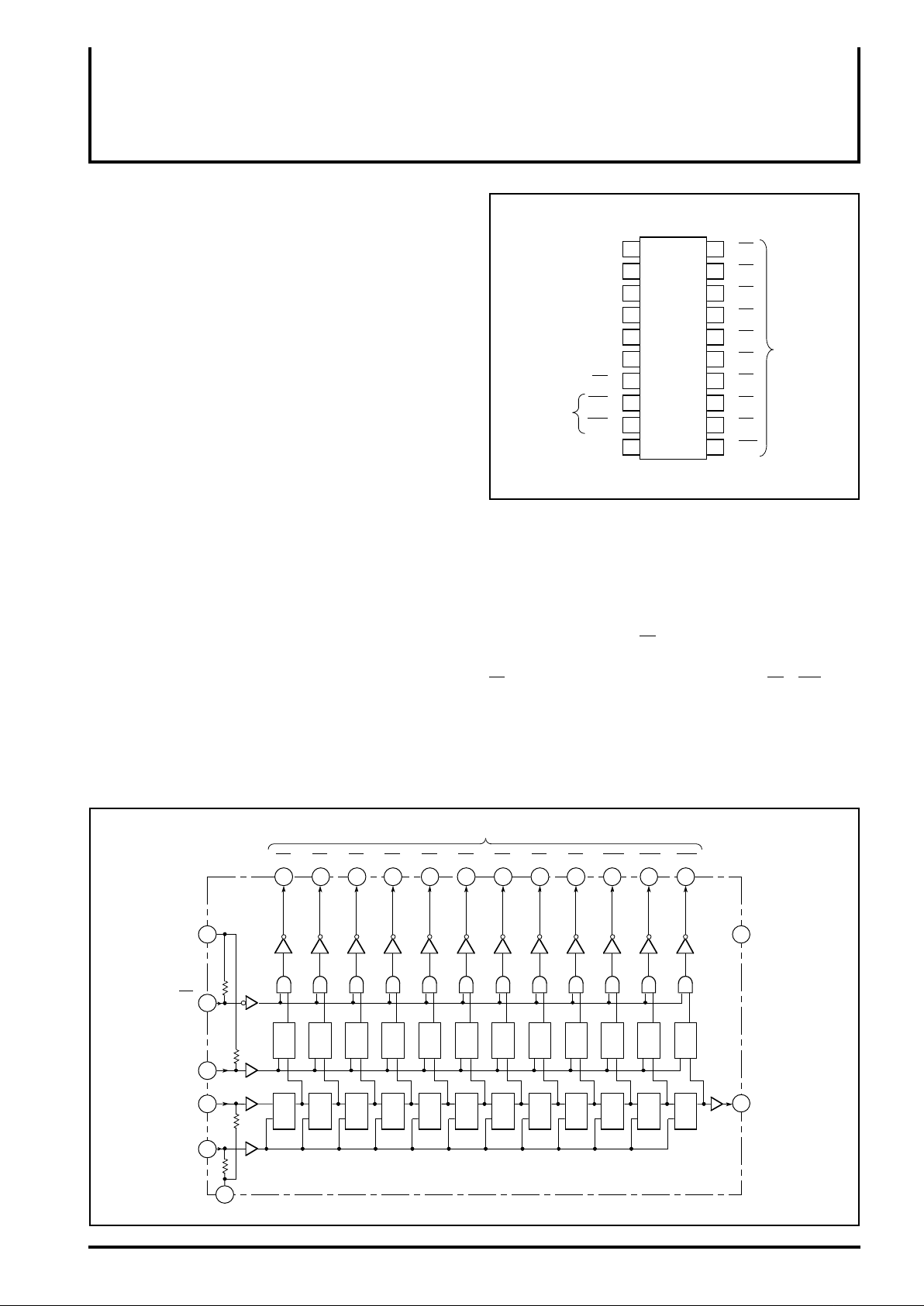

PIN CONFIGURATION(TOP VIEW

S-IN

L-GND

V

S-OUT

LATCH

EN

O12

O11

P-GND

T

→

→

CC

←

→

→

←

←

1

2

3

4

M54977P

7

Outline 20P4

O1

→

20

O2

→

19

O3

→

18

→

O4

17

→

O5

165

→

156

→

14

→

138

→→O9

129

1110

O6

O7

O8

O10

Parallel outputs

Clock

Serial input

Logic GND

Serial output

Latch input

Enable input

Parallel outputs

Driver GND

Using a number of M54977P units for bit expansion in series will

entail connecting serial output (S-OUT) to S-IN of the next-stage

M54977P.

In parallel output, when the latch input is set to “H” and the outputcontrol input (enable input EN) is “L”, a clock pulse changing from

“L” to “H” will cause the serial data input signal to appear at output

O1, and the data will be shifted in order at outputs O2 – O12.

The parallel output will yield a signal that is inverted with respect to

the serial data input.

BLOCK DIAGRAM

Power supply VCC

Enable input

Latch input

Serial input

Clock T

EN

LATCH

S-IN

4

7

6

2

1

L-GND

Parallel outputs

O1

O2

O3

O4

O5

O6

O7

O8

O9

O10

O11

O12

20

Q

L

D

QTD

3

19

L

18

Q

Q

L

D

D

QTD

QTD

16 15 14 13 12 11 9 8

17

Q

Q

Q

Q

Q

Q

L

L

L

L

L

D

D

D

D

QTD

QTD

QTD

QTD

L

D

D

QTD

QTD

L

P-GND

10

Driver GND

Q

Q

Q

L

D

QTD

L

D

D

S-OUT

QTD

QTD

5

Serial output

MITSUBISHI <CONTROL / DRIVER IC>

M54977P

Bi-CMOS 12-BIT SERIAL-INPUT LATCHED DRIVER

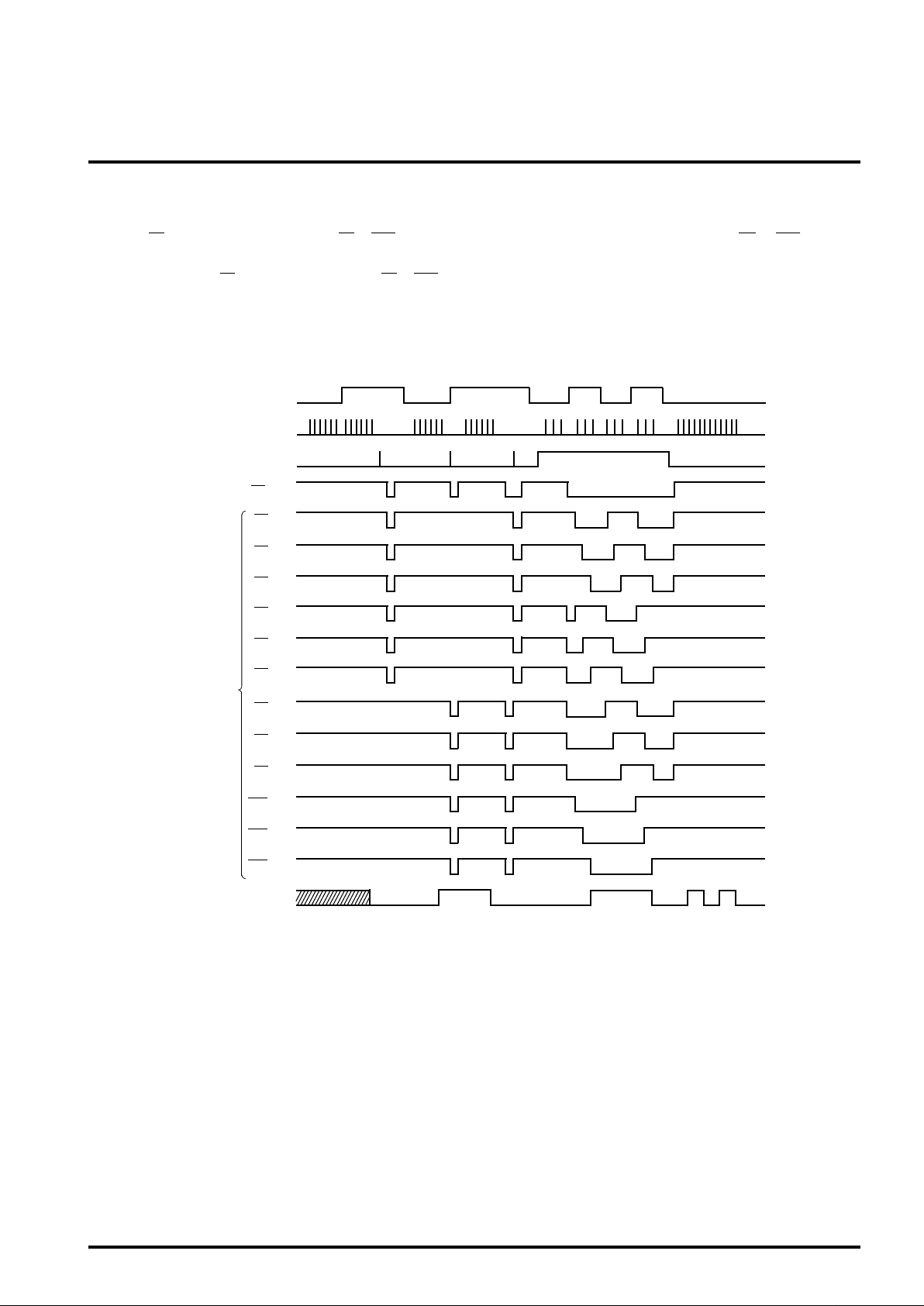

Setting the LATCH input to “L” will prevent data from entering the

latch.

When the EN input is set to “H”, all outputs (O1 – O12) will be set

to OFF. Since the internal logic state of the IC is uncertain at

power-on time, set the EN input to “H” (and outputs O1 – O12 will

set to OFF) until the input data is set and the internal logic state

TIMING CHART

Serial input

S-IN

TClock

LATCHLatch input

ENEnable input

O1

O2

O3

O4

O5

has been determined.

L-GND is the ground of the CMOS logic circuit section and P-GND

is the ground for the output driver section (O1 – O12), which is

made up of bipolar transistors that are capable of driving large

currents.

Parallel outputs

O6

O7

O8

O9

O10

O11

O12

S-OUTSerial output

*The state of the shaded part is unstable.

Loading...

Loading...