Mitsubishi M54972P, M54972FP Datasheet

MITSUBISHI <CONTROL / DRIVER IC>

M54972P/FP

Bi-CMOS 8-BIT SERIAL-INPUT LATCHED DRIVER

DESCRIPTION

The M54972 is a semiconductor integrated circuit consisting of 8

stages of CMOS shift registers and latches with serial inputs and

serial or parallel outputs. It is based on Bi-CMOS process

technology, and has 8 bipolar drivers at the parallel outputs.

FEATURES

●Serial input and serial or parallel output

●Serial output enables cascade connection

●Built-in latch for each stage

●Enable input provides output control

●Low supply current (standby current ICC ≤ 10µA)

●Serial I/O level is compatible with typical CMOS devices

●Driver features: High withstand voltage (BVCEO ≥ 30V)

Capable of large drive currents (IO(max)=300mA)

Low output saturation voltage VOL < 0.6V at lo=300mA

●Wide operating temperature range Ta=-20 – +75°C

APPLICATION

Dot drivers for thermal print heads. Serial/parallel conversion.

Drivers for relays and solenoids.

FUNCTION

The M54972 consists of 8 stages of D-type flip flops connected to

8 latches.

Data is input to serial input S-IN, and clock pulses are input to

clock input T. When the clock changes from low to high, the input

data enters the first shift register and data already in the shift

registers is shifted sequentially.

The serial output S-OUT is used to connect multiple M54972 to

expand the number of parallel outputs. S-OUT is connected to S-IN

of the next stage.

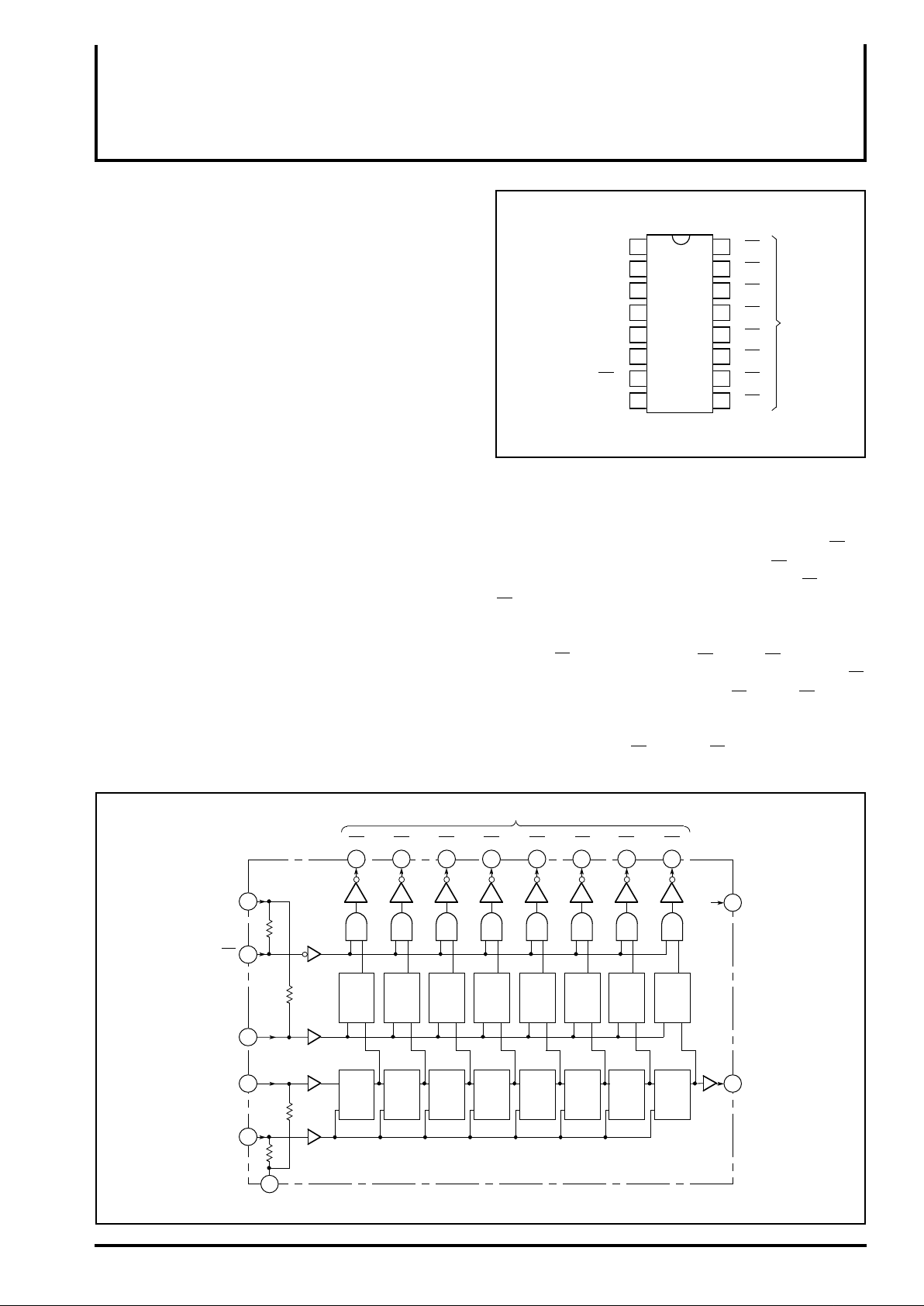

PIN CONFIGURATION (TOP VIEW)

S-IN

L-GND

V

S-OUT

LATCH

EN

P-GND

T

→

1

→

2

M54972P/FP

3

CC

4

←

→

→

Outline

16P4(P)

Clock

Serial input

Logic GND

Power supply

Serial output

Latch input

Enable input

Driver GND

16P2N-A(FP)

For parallel output. When the clock pulse changes from low to

high, latch input (LATCH) is high and output enable input (EN) is

low the serial input data at S-IN appears at output O1 and the other

data already present is shifted sequentially to outputs O2 through

O8.

The parallel outputs are inverted.

When the latch input is held low, the latch retains the stored data.

When the EN input is high, outputs O1 through O8 all turn off. As

the internal logic is unstable when the power is turned on, the EN

input should be kept high (setting outputs O1 through O8 off) until

input data is set and the internal logic is initialized.

L-GND is the GND of CMOS logic circuit and P-GND is the GND of

output driver circuits O1 through O8 which employ bipolar

transistors capable of large drive currents.

O1

→

16

O2

→

15

O3

→

14

→

O4

13

→

125

→

116

→

107

→

98

Parallel outputs

O5

O6

O7

O8

BLOCK DIAGRAM

Power supply

CC

V

ENEnable input

LATCHLatch input

S-INSerial input

Parallel outputs

O1

O2

O3

O4

O5

O6

O7

O8

16 15 14 13 12 11 10 9

4

7

Q

Q

Q

Q

Q

Q

Q

Q

L D

L D

L D

L D

L D

L D

L D

L D

6

2

1

TClock

3

L-GND

Logic GND

QTD

QTD

QTD

QTD

QTD

QTD

QTD

QTD

8

5

Driver GNDP-GND

Serial outputS-OUT

M54972P/FP

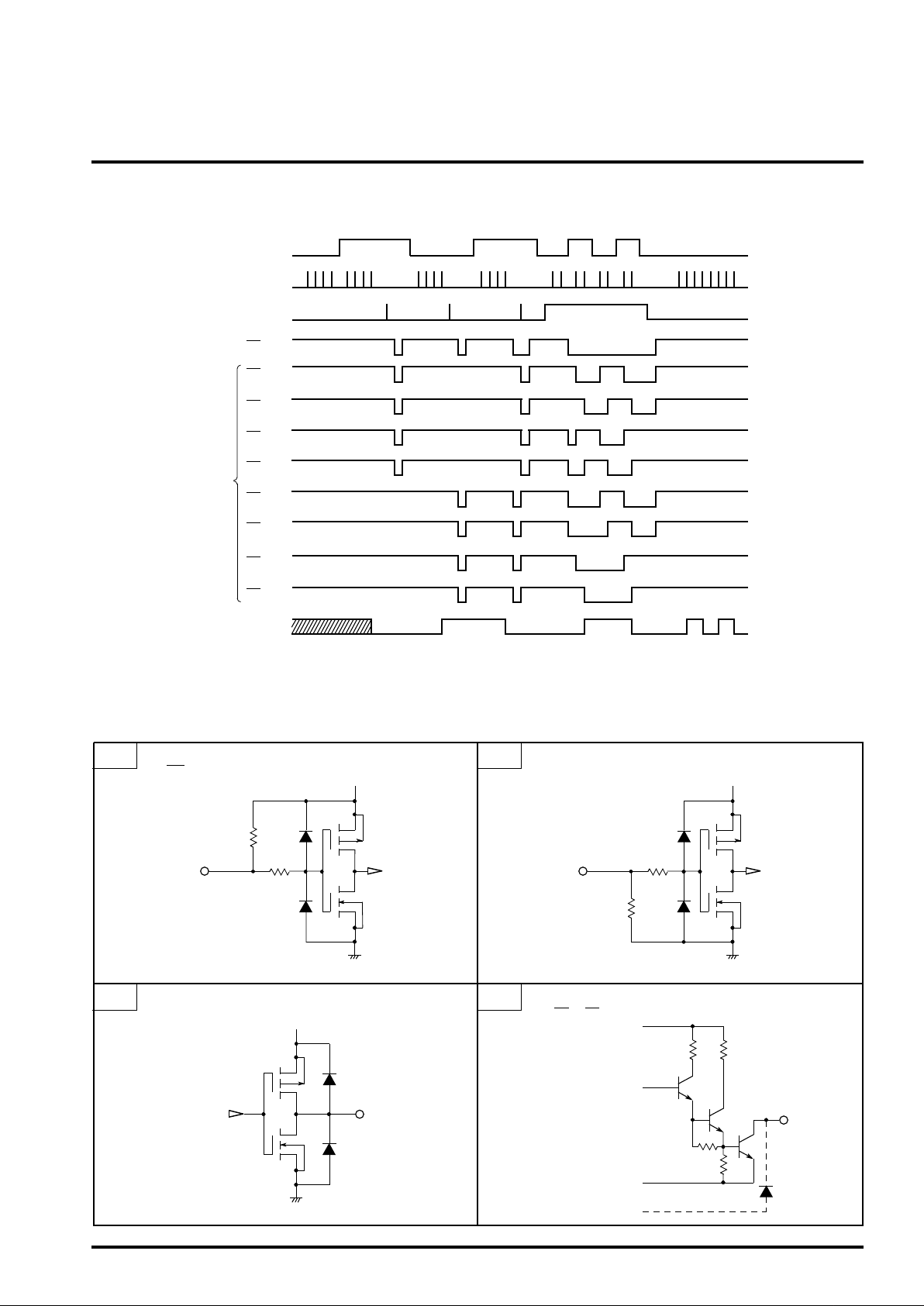

TIMING CHART

MITSUBISHI <CONTROL / DRIVER IC>

Bi-CMOS 8-BIT SERIAL-INPUT LATCHED DRIVER

Serial input

Parallel outputs

LATCHLatch input

S-OUTSerial output

S-IN

TClock

ENEnable input

O1

O2

O3

O4

O5

O6

O7

O8

∗

The shaded area shows the unstable state.

INPUT/OUTPUT CIRCUIT DIAGRAM

1

3

Inputs with pullup resistors

(EN, LATCH)

RIN

Serial output

(S-OUT)

VCC

L-GND

VCC

2

4

Inputs with pulldown resistors

(T, S-IN)

RIN

Parallel outputs

(O1 – O8)

V

CC

VCC

L-GND

L-GND

P-GND

L-GND

Loading...

Loading...