MITSUBISHI <CONTROL / DRIVER IC>

)

M54123L

EARTH LEAKAGE CURRENT DETECTOR

DESCRIPTION

The M54123L is a semiconductor integrated circuit with amplifier

for a high-speed earth leakage circuit breaker.

FEATURES

●Suitable for JIS C 8371

●Good temperature characteristics of input sensitivity current

●High input sensitivity (VT = 6.1mV Typ.)

●Low external component count

●High noise and surge-proof

●Low power dissipation (Pd = 5mW Typ.) and may be used both

as 100V and 200V.

●High mounting density by SIL package with 8 pins

●Wide temperature range (Ta = -20 – +80°C)

APPLICATION

High speed earth leakage circuit breaker

FUNCTION

The M54123L circuit for the amplifying parts of earth leakage

circuit breaker consists of differential amplifier, latch circuit and

voltage regulator. It is connected to the secondary side of the zerocurrent transformer (ZCT) which detects leakage current in the

both input of the differential amplifier. Signals amplified by

differential amplifier are integrated by an external capacitor, and

connects to the input terminal of latch circuit with output suitable for

the characteristics of high-speed earth leakage circuit breaker.

Latch circuit keeps low in the output till the input voltage reaches

the fixed level, and output becomes high when the leakage current

more than fixed flows. It drives a thyristor connected to the output

terminal of latch circuit.

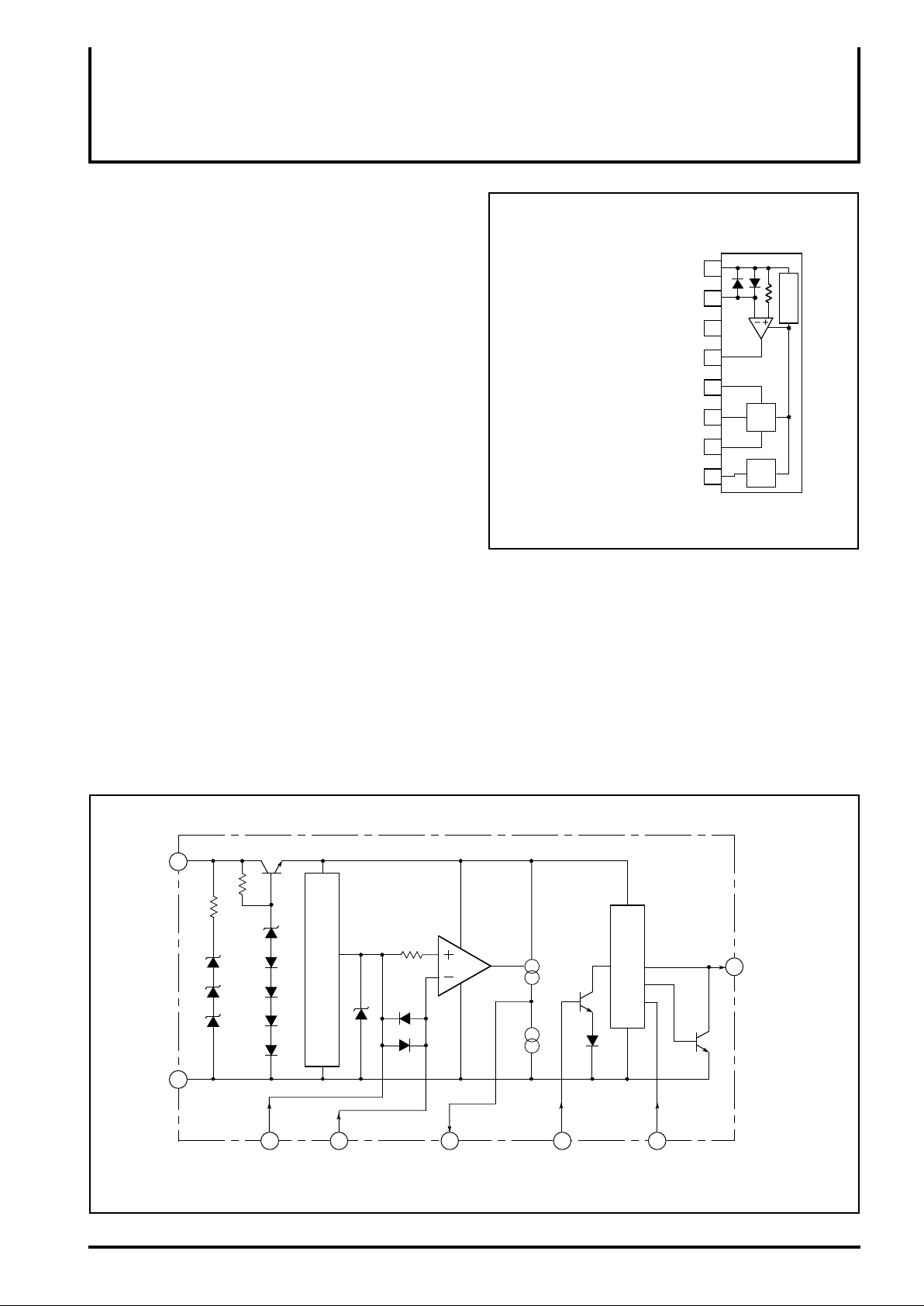

PIN CONFIGURATION(TOP VIEW

Reference voltage

Input

Differential amplifier output

Latch input

Terminal for noise absorption

Output

V

GND

OD

S

NR

OS

VS

→

R

1

2

→

IN

3

AMP

←

4

5

→

C

6

→

←

7

8

Outline 8P5

BIAS

LATCH

REG

BLOCK DIAGRA M

8

VS

3

GND

1

V

R

Reference

voltage

AMP

Reference voltage generator

2

IN

Input

4

O

Differential

amplifier

output

7

OS output

Latch circuit

5

D

SC

Latch

input

6

N

R

Terminal for noise

absorption

MITSUBISHI <CONTROL / DRIVER IC>

)

y

)

)

(°C)

S

EARTH LEAKAGE CURRENT DETECTOR

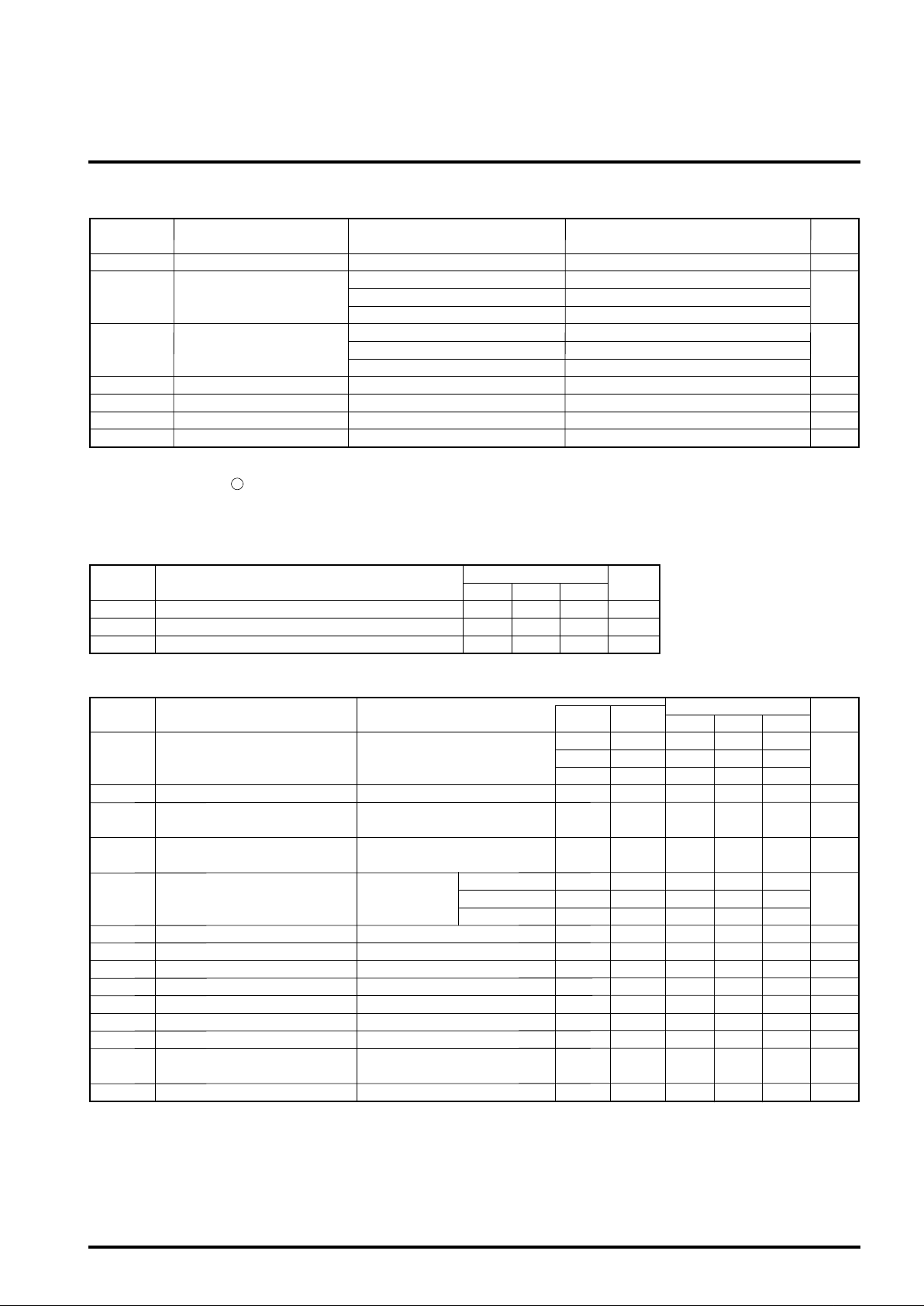

ABSOLUTE MAXIMUM RATINGS(Ta = -20 – 80°C unless otherwise noted

M54123L

Symbol

IS

IVR

IIN

SC

I

Pd

T

opr

Supply current

V

IN terminal current

SC terminal current

Power dissipation

Operating temperature

Tstg Storage temperature

Note 1: Current value between VR and IN, and between IN and VR is less than 1ms in the pulse width, and duty cycle is less than 12%. In applying AC current

continuously, it is 100mArms in the off-state.

Remarks: GND terminal (pin ) of the circuit is a basis of all the voltages except differential input clamp voltage of DC electrical characteristics, and direction of

current is plus (no signal) in flowing into the circuit and is minus (–signal) in flowing out of it. Maximum value and minimum one are shown as absolute

value. Please don’t appl

Parameter Conditions

Between VR-IN (Note 1)

R pin current

Between V

Between IN-V

Between IN-V

Between IN-GND

Between V

3

voltage whose standard is GND terminal in VR and IN pin.

R-GND

R (Note 1)

R (Note 1)

R-IN (Note 1)

Ratings

8

250

30

-250

250

30

-250

5

200

– 80

-20

-55 – 125

Unit

mA

mA

mA

mA

mW

°C

°C

RECOMMENDED OPERATING CONDITIONS(Ta = -20 – 80°C unless otherwise noted

Symbol

S

V

CVS

COS

Parameter

Supply voltage when latch circuit is off-state

External capacitor between VS and GND

External capacitor between OS and GND

Limits

Min. Typ. Max.

12

1

Unit

V

µF

µF

1

ELECTRICAL CHARACTERISTICS(Ta = -20 – 80°C unless otherwise noted

Symbol Test conditions

Parameter

Tempera-

ture

-20

I

S1 Supply current

VS = 12V, VR-VI = 30mV

25

80

T

V

ITD1

ITD2

IO

VSC “ON”

ISC “ON”

IOSL

VIC

VIDC

VSM

IS2

VS “OFF”

TON

∗

Note : Typical values are at Ta = 25°C.

Note 2: When standard value of voltage (60Hz) between V

Note 3: When standard value of voltage V

Note 4: Supply current 2 is necessary to keep high in output O

Note 5: After applying 30mV between V

Note 6: After supply voltage applies 12V and output OS is high-level, it is considered as a good one in the standard value of supply voltage and in the low-level

Note 7: Operating time is a time from applying fixed input till operating latch circuit in 0.047µF between O

Trip voltage

Timed current 1

Timed current 2

Output current

C “ON” voltage (Note 3)

S

S

C input current

Output low-level current

Input clamp voltage

Differential input clamp voltage

Maximum current voltage

Supply current 2 (Note 4)

Latch circuit is off-state supply

voltage (Note 6)

Operating time (Note 7)

R and VI is maximum, and output OS is high-level, it is considered as a good one.

V

is high-level, it is considered as a good one.

of output O

S.

SC “ON” is minimum, and output OS is low-level, or when standard value of voltage VSC “ON” is maximum, and output O

R and VI and shorting between them, it is considered as a good one if standard value of IGT flows out of output OS.

VS = 16V, VR-VI (Note 2)

S = 16V, VR-VI = 30mV,

V

VOD = 1.2V

V

S = 16V, short circuit between

VR and VI, VOD = 0.8V

S1 = 580µA

VSC = 1.4V

VOS = 0.8V

V

S = 16V

V

S = 12V

V

S = 12V, VOSL = 0.2V

V

S = 12V, IIC = 20mA

IDC = 100mA

I

I

SM = 7mA

V

R-VI VOS = 0.6V (Note 5)

I

I

S1 = 530µA

S1 = 480µA

I

VS = 16V, VR-VI = 0.3V

R and VI is minimum, and output OS is low-level, or when standard value of voltage (60Hz) between

S.

-20 – +80

25

25

-20

25

80

25

25

-20 – +80

-20 – +80

-20 – +80

25

-20 – +80

25

25

Test

circuit

1

1

1

2

3

4

5

5

5

6

7

8

9

10

11

12

13

14

D and GND.

Limits

Min. Typ. Max.

∗

580

400

530

480

4

6.1

-12

17

9

-30 µA

37

-200

-100

-75

0.7

1.4

5

200

4.3

0.4

20

6.7

2

28

900

0.5

2

4

Unit

mV

µA

rms

µA

µA

V

µA

µA

V

V

V

µA

V

ms

Loading...

Loading...