MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

DESCRIPTION

The 3851 group is the 8-bit microcomputer based on the 740 family core technology.

The 3851 group is designed for the household products and office

automation equipment and includes serial I/O functions, 8-bit

timer, A-D converter, and I

2

C-bus interface.

FEATURES

●Basic machine-language instructions ...................................... 71

●Minimum instruction execution time .................................. 0.5 µs

(at 8 MHz oscillation frequency)

●Memory size

ROM .............................................................................16 Kbytes

RAM .............................................................................. 512 bytes

●Programmable input/output ports ............................................ 34

●Interrupts ................................................. 16 sources, 16 vectors

●Timers.............................................................................8-bit ✕ 4

●Serial I/O ....................... 8-bit ✕ 1(UART or Clock-synchronized)

●Multi-master I

●P WM ............................................................................... 8-bit ✕ 1

●A-D converter ............................................... 10-bit ✕ 5 channels

●Watchdog timer ............................................................ 16-bit ✕ 1

●Clock generating circuit ..................................... Built-in 2 circuits

(connect to external ceramic resonator or quartz-crystal oscillator)

2

C-bus interface (option) ....................... 1 channel

●Power source voltage

In high-speed mode .................................................. 4.0 to 5.5 V

(at 8 MHz oscillation frequency)

In high-speed mode .................................................. 2.7 to 5.5 V

(at 4 MHz oscillation frequency)

In middle-speed mode............................................... 2.7 to 5.5 V

(at 8 MHz oscillation frequency)

In low-speed mode .................................................... 2.7 to 5.5 V

(at 32 kHz oscillation frequency)

●Power dissipation

In high-speed mode ..........................................................34 mW

(at 8 MHz oscillation frequency, at 5 V power source voltage)

In low-speed mode ............................................................ 60 µW

(at 32 kHz oscillation frequency, at 3 V power source voltage)

●Operating temperature range.................................... –20 to 85°C

APPLICATION

Office automation equipment, FA equipment, Household products,

Consumer electronics, etc.

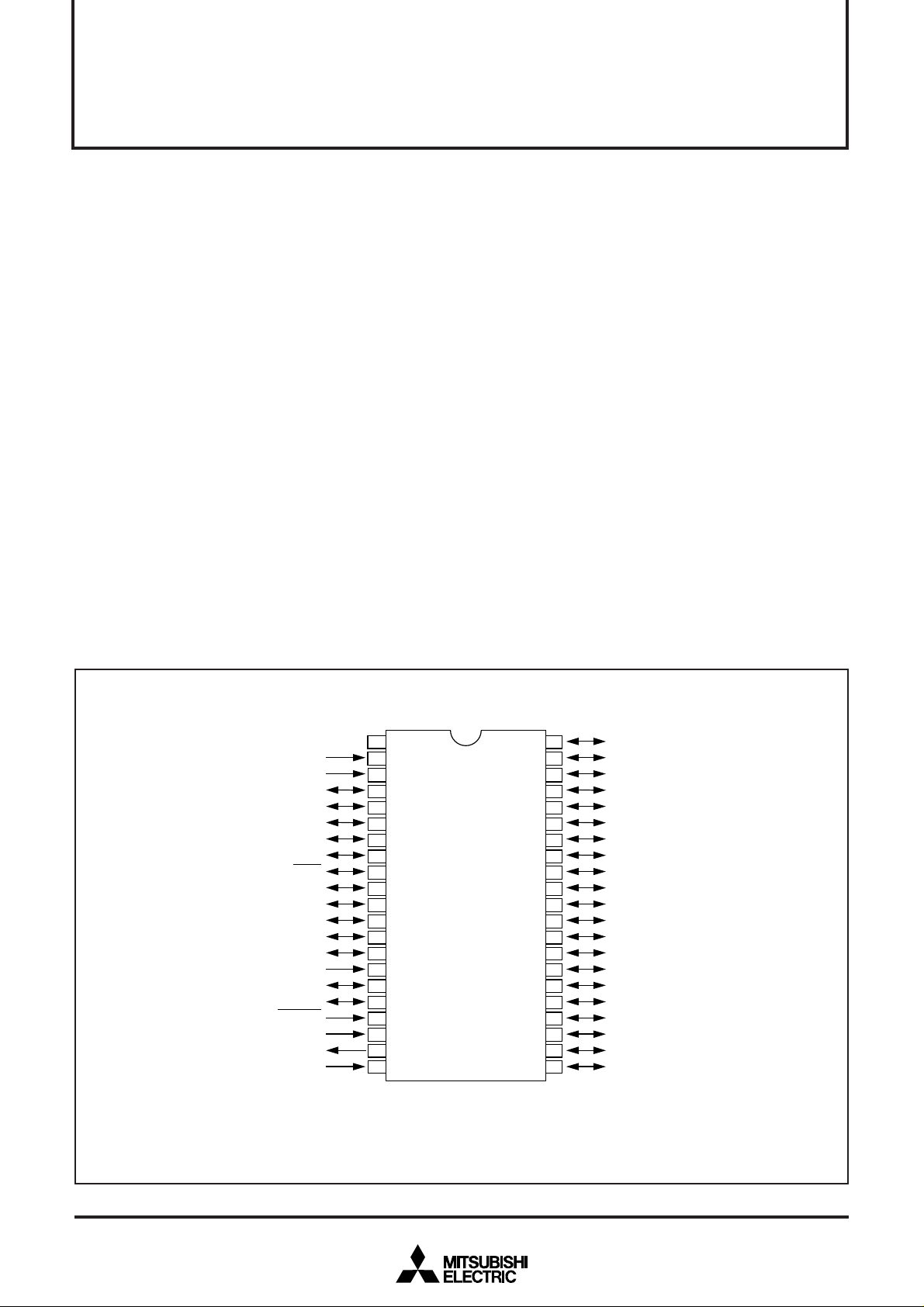

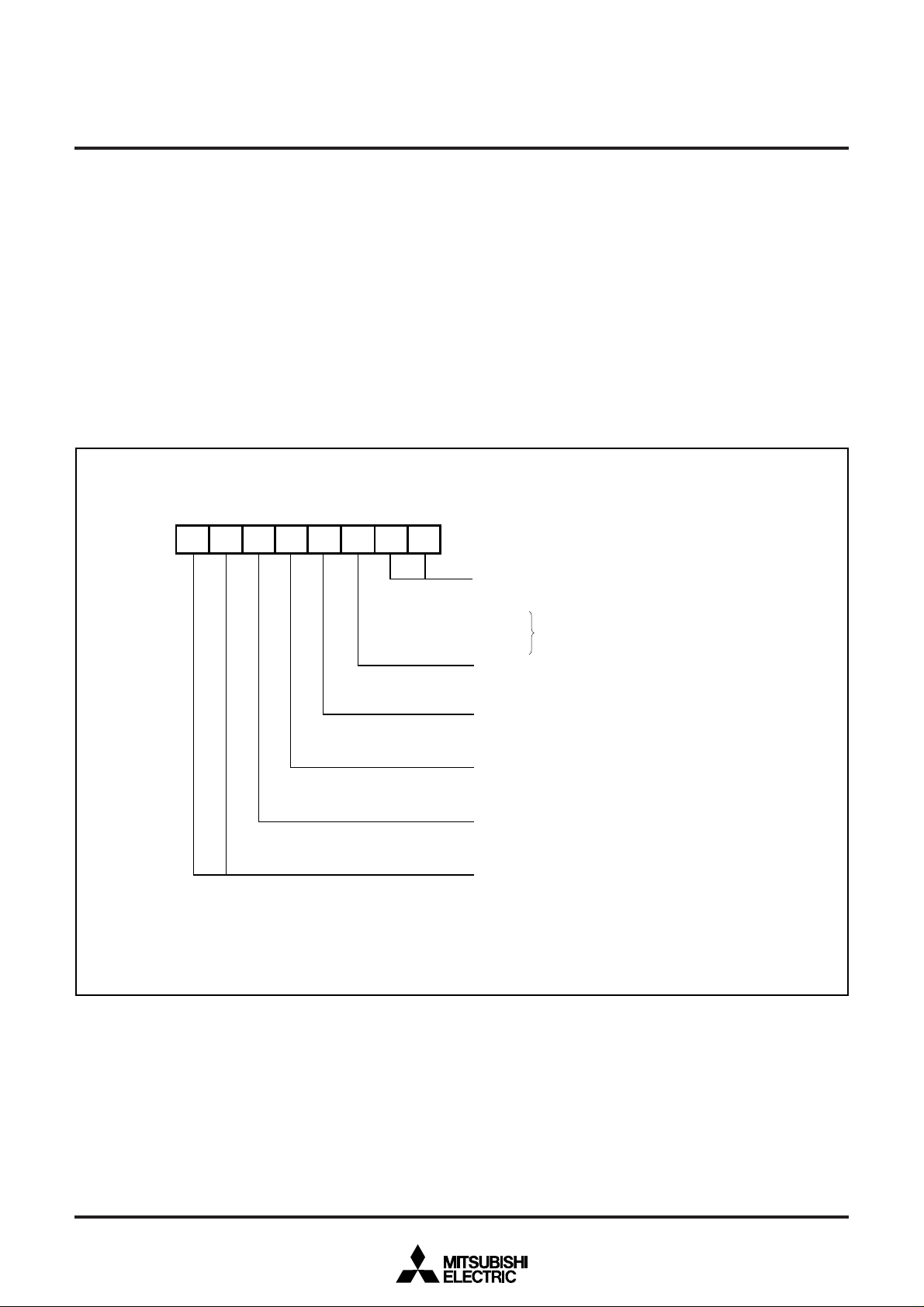

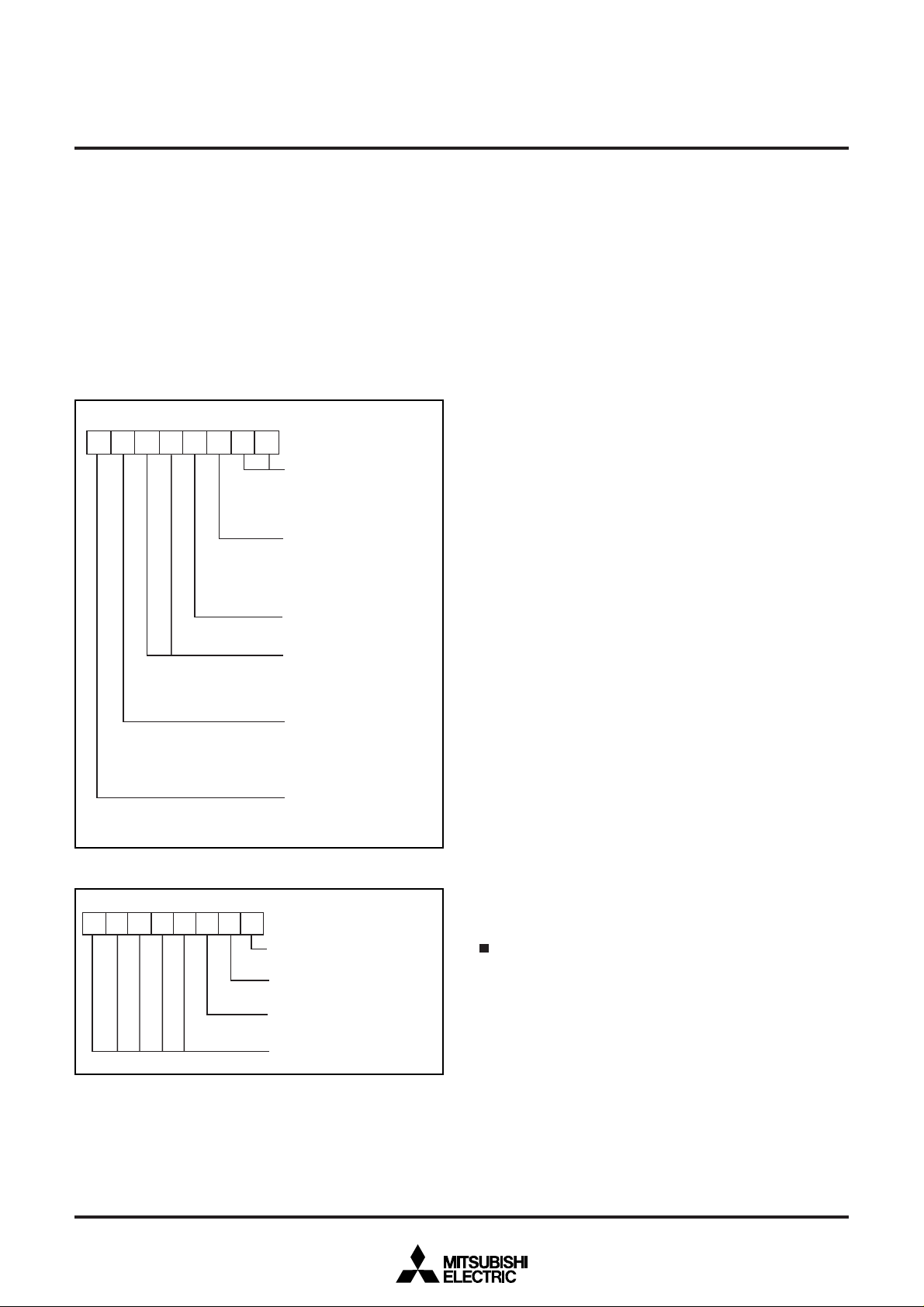

PIN CONFIGURATION (TOP VIEW)

V

CC

V

REF

SS

AV

P44/INT3/PWM

P43/INT

2

P42/INT

1

P41/INT

0

P40/CNTR

P2

7

/CNTR0/S

P26/S

P25/SCL2/TxD

4

/SDA2/RxD

P2

P2

P22/SDA

P20/X

Package type : FP ........................... 42P2R-A (42-pin plastic-molded SSOP)

Package type : SP ........................... 42P4B (42-pin shrink plastic-molded DIP)

3

/SCL

CNV

P21/X

COUT

RESET

X

RDY

CLK

CIN

X

OUT

V

1

1

1

SS

IN

SS

P30/AN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

M38513M4-XXXSP

M38513M4-XXXFP

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

0

P31/AN

1

P32/AN

2

P33/AN

3

P34/AN

4

P0

0

P0

1

P0

2

P0

3

P0

4

P0

5

P0

6

P0

7

P1

0

P1

1

P1

2

P13/(LED0)

P1

4

/(LED1)

5

/(LED2)

P1

P16/(LED3)

7

/(LED4)

P1

Fig. 1 M38513M4-XXXFP/SP pin configuration

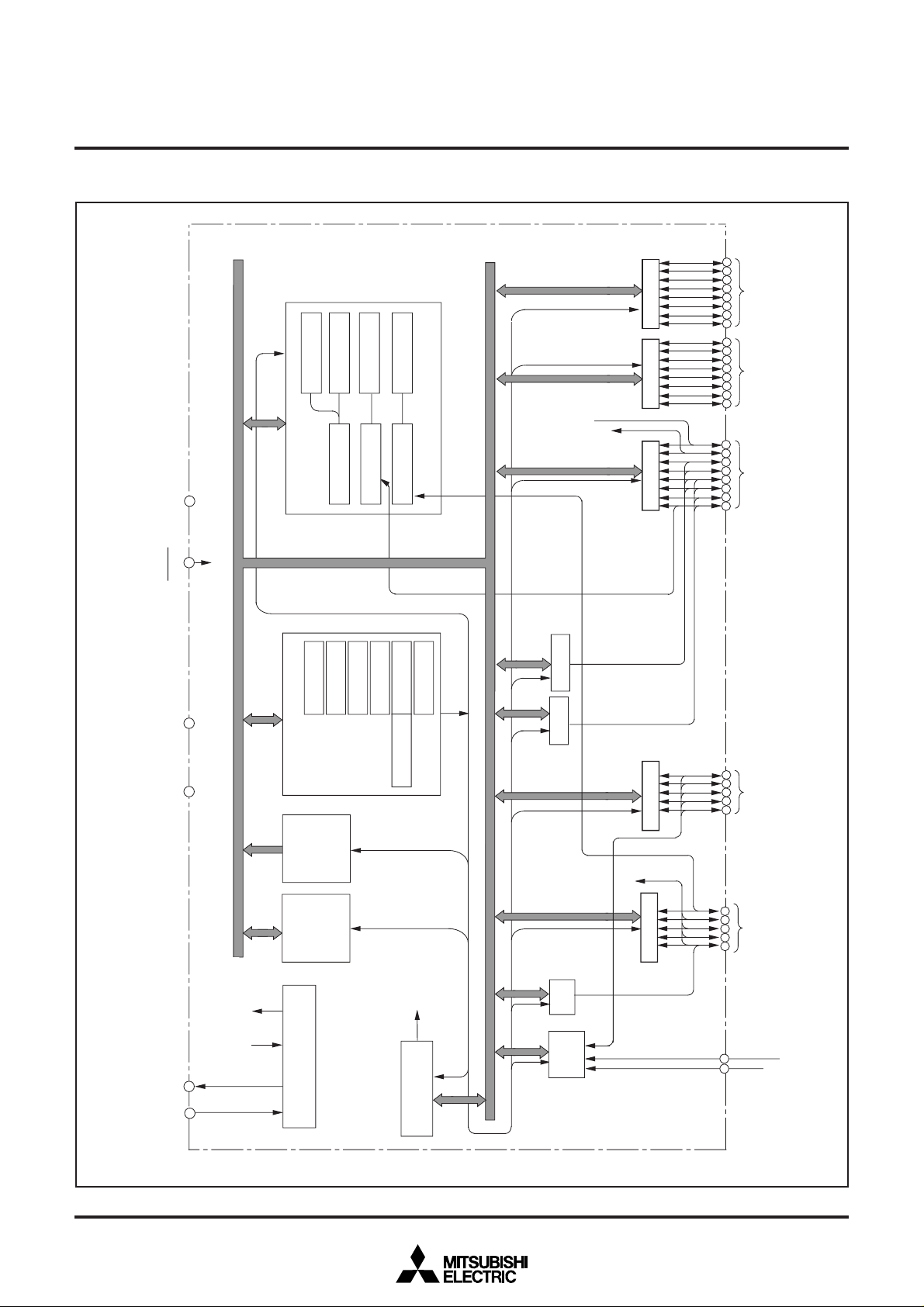

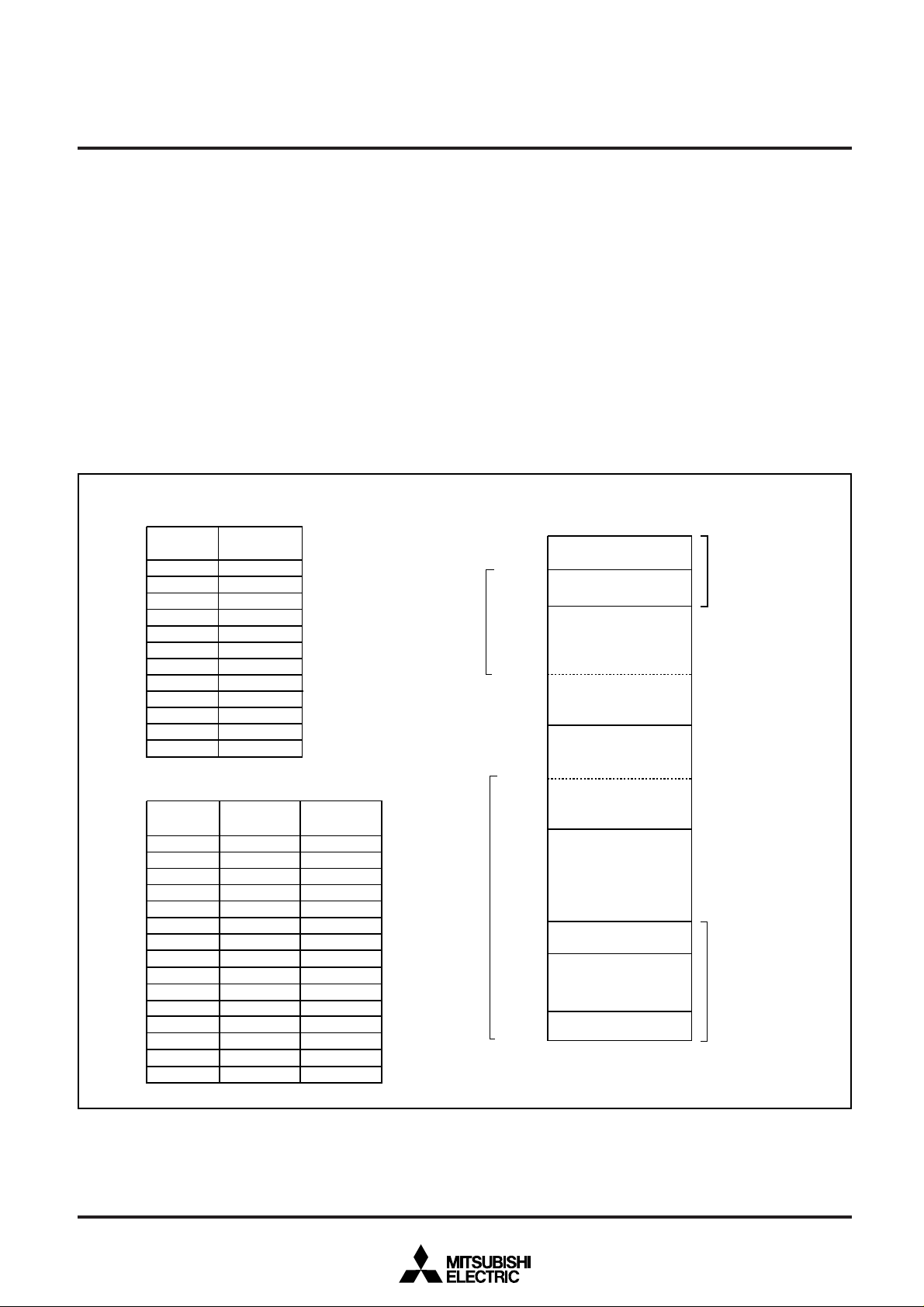

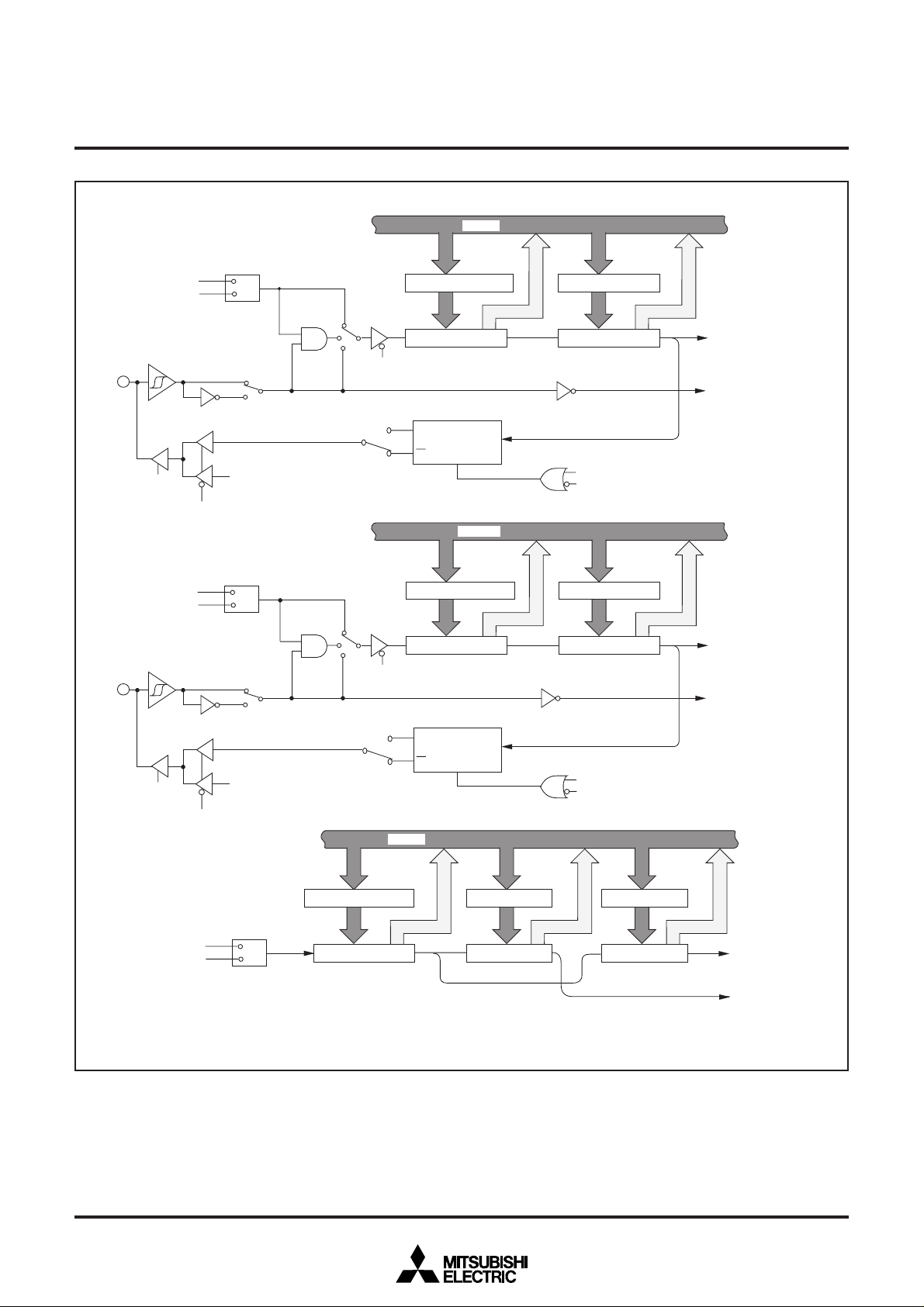

FUNCTIONAL BLOCK

INT

0

–

CNTR

0

CNTR

1

V

REF

AV

SS

R A M

R O M

C P U

A

X

Y

S

PC

H

PC

L

PS

V

SS

21

RESET

18

V

CC

1 15

CNV

SS

23

X

IN

19

20

SI/O(8)

Reset input

Clock generating circuit

Main-clock

input

Main-clock

output

A-D

converter

(10)

Timer Y( 8 )

Timer X( 8 )

Prescaler 12(8)

Prescaler X(8)

Prescaler Y(8)

Timer 1( 8 )

Timer 2( 8 )

Sub-clock

input

X

OUT

X

CIN

X

COUT

Sub-clock

output

Watchdog

timer

Reset

P2(8)

P3(5)

I/O port P2

I/O port P3

P4(5)

I/O port P4

I C

INT

3

4

6

8

5

7

39

4138 40

42

9

11

13

17

10

12

14

16

P1(8)

I/O port P1

22 24 26 2823

25

27 29

P0(8)

I/O port P0

30 31

32 3334 35 36

37

PWM

(8)

2

X

CIN

X

COUT

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

FUNCTIONAL BLOCK DIAGRAM

Fig. 2 Functional block diagram

2

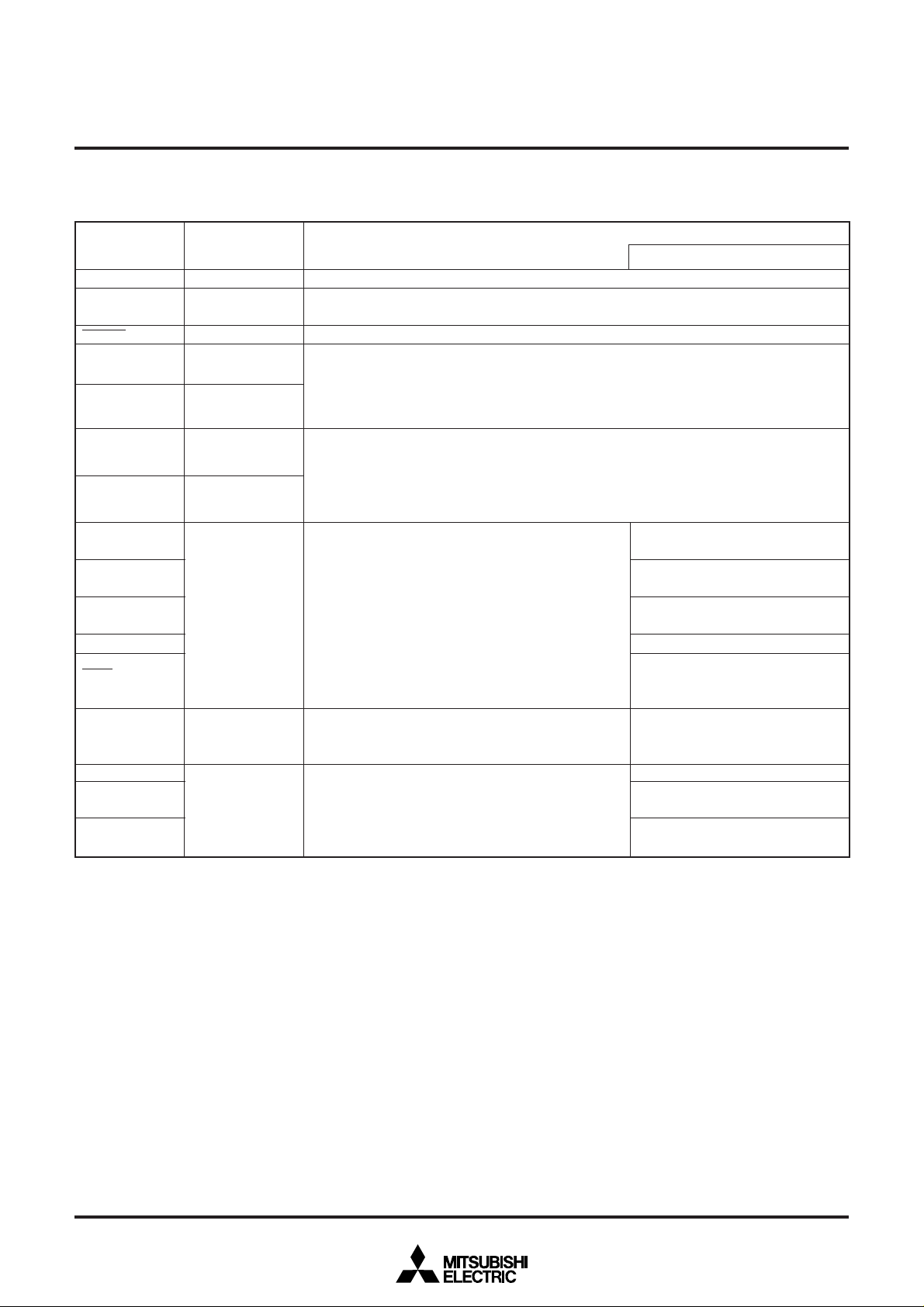

PIN DESCRIPTION

Table 1 Pin description

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

VCC, VSS

RESET

IN

X

XOUT

P00–P07

P10–P17

P20/XCOUT

P21/XCIN

P22/SDA1

P23/SCL1

P24/SDA2/RxD

P25/SCL2/TxD

P26/SCLK

P27/CNTR0/

SRDY

P30/AN0–

P34/AN4

P40/CNTR1

P41/INT0–

P43/INT2

P44/INT3/PWM

NamePin

Power source

SS inputCNVSS

CNV

Reset input

Clock input

Clock output

I/O port P0

I/O port P1

I/O port P2

I/O port P3

I/O port P4

Functions

•Apply voltage of 2.7 V – 5.5 V to Vcc, and 0 V to Vss.

•This pin controls the operation mode of the chip.

•Normally connected to V

•Reset input pin for active “L.”

•Input and output pins for the clock generating circuit.

•Connect a ceramic resonator or quartz-crystal oscillator between the X

the oscillation frequency.

•When an external clock is used, connect the clock source to the XIN pin and leave the XOUT

pin open.

•8-bit CMOS I/O port.

•I/O direction register allows each pin to be individually programmed as either input or output.

•CMOS compatible input level.

•CMOS 3-state output structure.

•P1

3 to P17 (5 bits) are enabled to output large current for LED drive.

•8-bit CMOS I/O port.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•CMOS compatible input level.

•P22 to P25 can be switched between CMOS compatible input level or SMBUS input level in the I2C-BUS

interface function.

•P20, P21, P24 to P27: CMOS3-state output structure.

•P24, P25: N-channel open-drain structure in the I2CBUS interface function.

•P2

2, P23: N-channel open-drain structure.

•8-bit CMOS I/O port with the same function as port P0.

•CMOS compatible input level.

•CMOS 3-state output structure.

•8-bit CMOS I/O port with the same function as port P0.

•CMOS compatible input level.

•CMOS 3-state output structure.

SS.

Function except a port function

IN and XOUT pins to set

• Sub-clock generating circuit I/O

pins (connect a resonator)

• I2C-BUS interface function pins

• I2C-BUS interface function pin/

Serial I/O function pins

• Serial I/O function pin

• Serial I/O function pin/

Timer X function pin

• A-D converter input pin

• Timer Y function pin

• Interrupt input pins

• Interrupt input pin

• PWM output pin

3

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

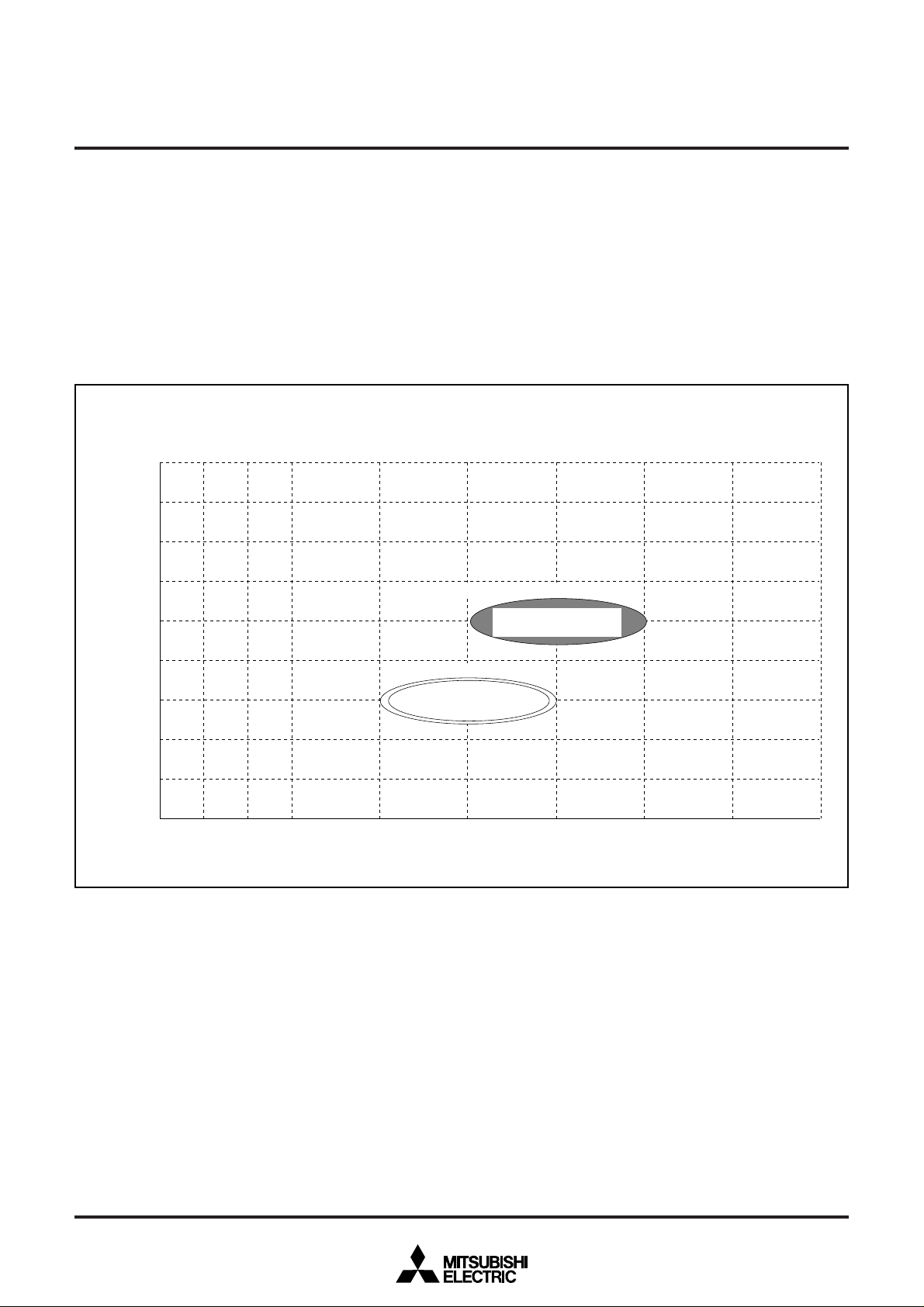

GROUP EXPANSION

Mitsubishi plans to expand the 3851 group as follows:

Memory Type

Support for mask ROM and One Time PROM versions.

Memory Size

ROM/PROM size ............................................................ 16 K bytes

RAM size ......................................................................... 512 bytes

Memory Expansion Plan

ROM size (bytes)

48K

32K

28K

24K

Packages

42P2R-A ............................................ 42-pin plastic molded SSOP

42P4B ......................................... 42-pin shrink plastic-molded DIP

Under development

M38514E6FP/SP

M38514M6-XXXFP/SP

20K

16K

12K

8K

128 192 256

Fig. 3 Memory expansion plan

Mass production

M38513E4FP/SP

M38513M4-XXXFP/SP

384 512 640 768 896 1024

RAM size (bytes)

4

FUNCTIONAL DESCRIPTION CENTRAL PROCESSING UNIT (CPU)

The 3851 group uses the standard 740 Family instruction set. Refer to the table of 740 Family addressing modes and machine

instructions or the 740 Family Software Manual for details on the

instruction set.

Machine-resident 740 Family instructions are as follows:

The FST and SLW instructions cannot be used.

The STP, WIT, MUL, and DIV instructions can be used.

[CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit, etc.

The CPU mode register is allocated at address 003B

16.

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b7

b0

CPU mode register

(

CPUM : address

003B16)

Processor mode bits

b1 b0

0 0 : Single-chip mode

0 1 :

1 0 : Not available

1 1 :

Stack page selection bit

0 : 0 page

1 : 1 page

Not used (return “1” when read)

(Do not write “0” to this bit.)

C

switch bit

Port X

0 : I/O port function (stop oscillating)

CIN–XCOUT

1 : X

Main clock (X

0 : Oscillating

1 : Stopped

Main clock division ratio selection bits

b7 b6

0 0 : φ = f(X

0 1 : φ = f(X

1 0 : φ = f(X

1 1 : Not available

IN–XOUT

oscillating function

) stop bit

IN

)/2 (high-speed mode)

IN

)/8 (middle-speed mode)

CIN

)/2 (low-speed mode)

Fig. 4 Structure of CPU mode register

5

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

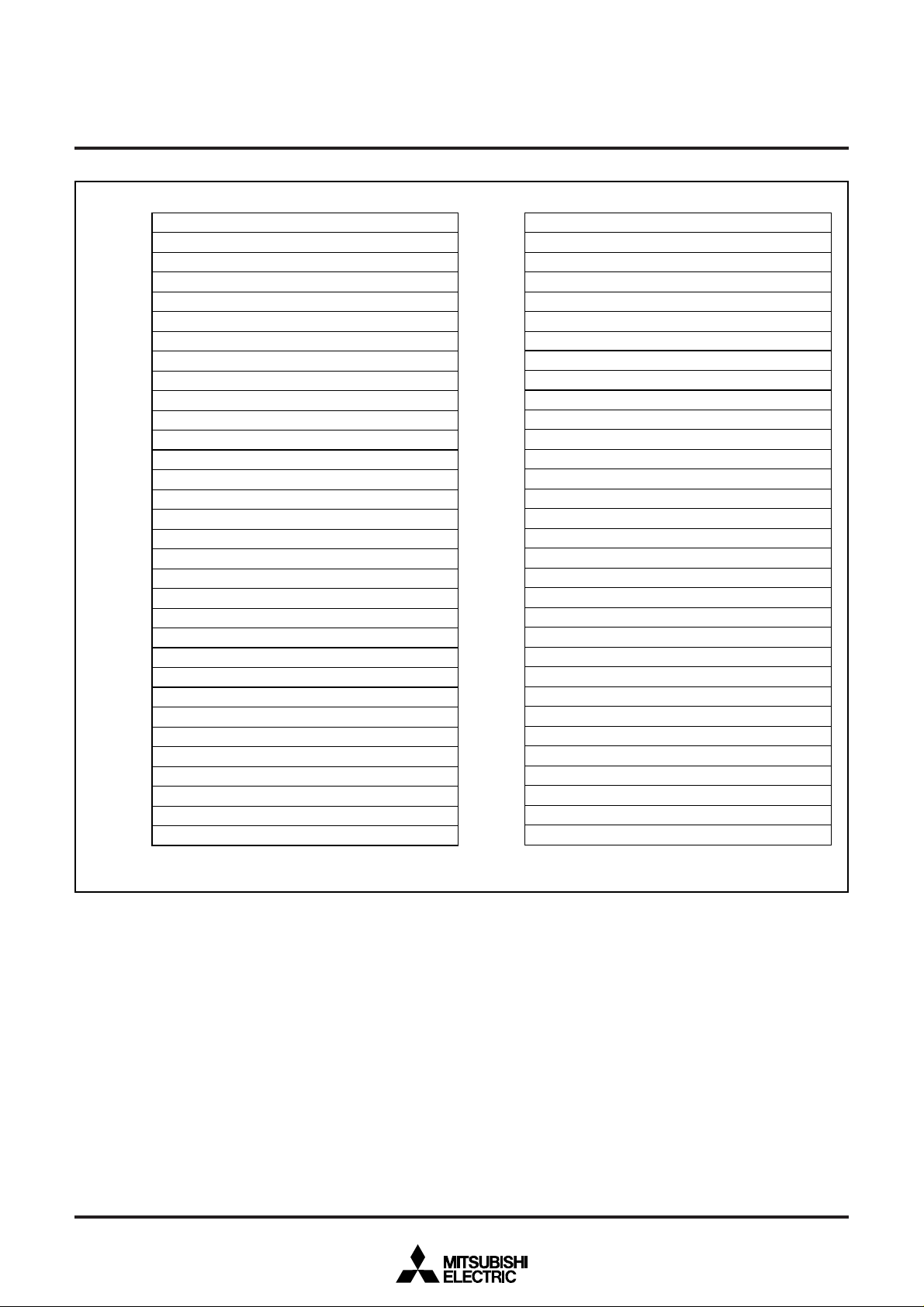

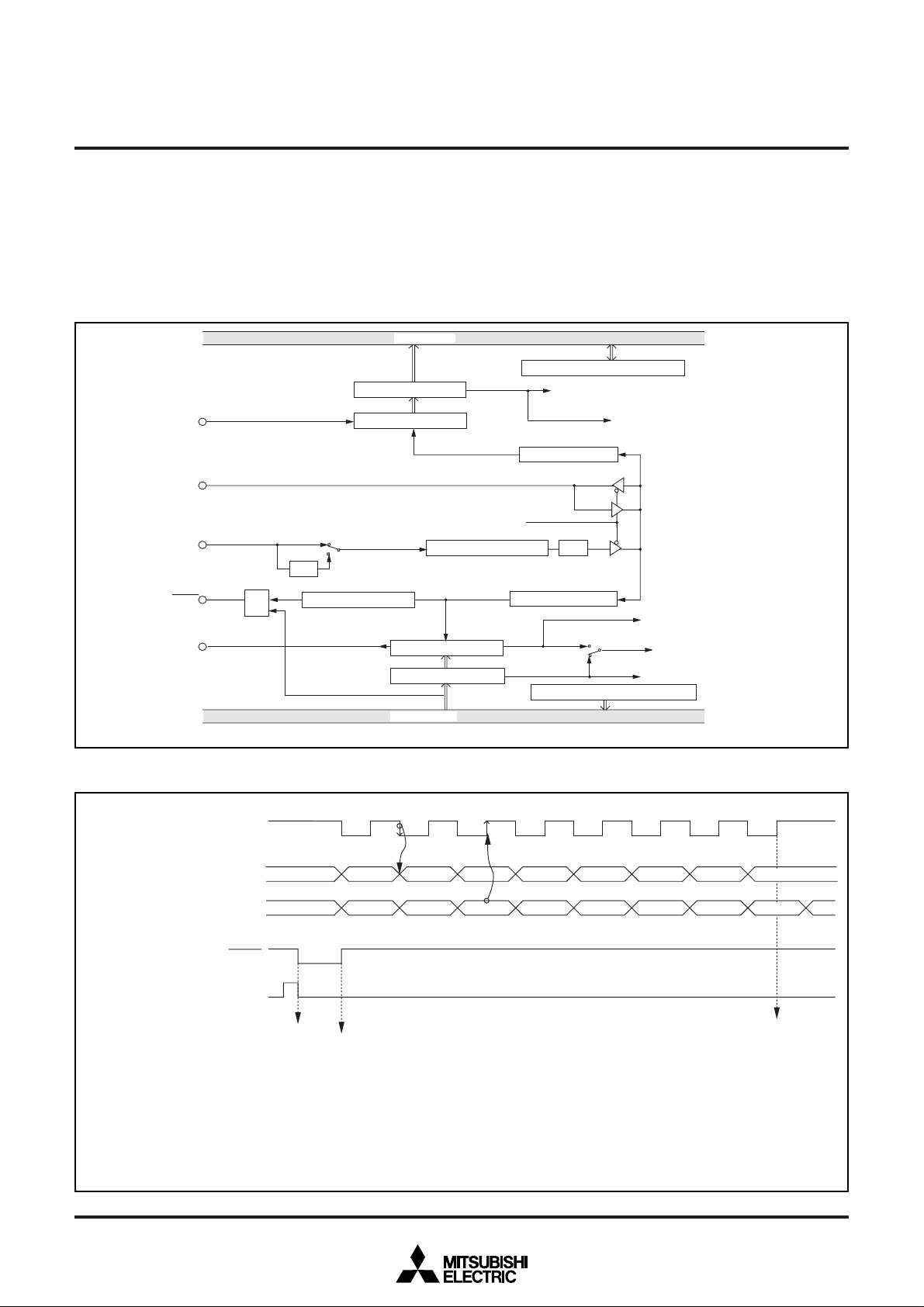

MEMORY

Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

RAM

RAM is used for data storage and for stack area of subroutine

calls and interrupts.

ROM

The first 128 bytes and the last 2 bytes of ROM are reserved for

device testing and the rest is user area for storing programs.

Interrupt Vector Area

The interrupt vector area contains reset and interrupt vectors.

RAM area

RAM size

(bytes)

192

256

384

512

640

768

896

1024

1536

2048

3072

4032

Address

XXXX

00FF

013F

01BF

023F

02BF

033F

03BF

043F

063F

083F

0C3F

0FFF

16

16

16

16

16

16

16

16

16

16

16

16

16

Zero Page

Access to this area with only 2 bytes is possible in the zero page

addressing mode.

Special Page

Access to this area with only 2 bytes is possible in the special

page addressing mode.

0000

RAM

0040

0100

XXXX

0440

16

16

16

16

16

SFR area

Zero page

Reserved area

Not used

ROM area

ROM size

(bytes)

4096

8192

12288

16384

20480

24576

28672

32768

36864

40960

45056

49152

53248

57344

61440

Fig. 5 Memory map diagram

Address

YYYY

F000

E000

D000

C000

B000

A000

9000

8000

7000

6000

5000

4000

3000

2000

1000

YYYY

16

Reserved ROM area

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

Address

ZZZZ

F080

E080

D080

C080

B080

A080

9080

8080

7080

6080

5080

4080

3080

2080

1080

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

ROM

ZZZZ

FF00

FFDC

FFFE

FFFF

16

16

16

16

16

(128 bytes)

Interrupt vector area

Reserved ROM area

Special page

6

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

0000

0001

0002

0003

0004

0005

0006

0007

0008

0009

000A

000B

000C

000D

000E

000F

0010

0011

0012

0013

0014

0015

0016

0017

0018

0019

001A

001B

001C

001D

001E

001F

Port P0 (P0)

16

Port P0 direction register (P0D)

16

Port P1 (P1)

16

Port P1 direction register (P1D)

16

Port P2 (P2)

16

Port P2 direction register (P2D)

16

Port P3 (P3)

16

Port P3 direction register (P3D)

16

Port P4 (P4)

16

Port P4 direction register (P4D)

16

16

16

16

16

16

16

16

16

16

16

16

16

Reserved ✽

16

Reserved ✽

16

Reserved ✽

Transmit/Receive buffer register (TB/RB)

16

Serial I/O status register (SIOSTS)

16

Serial I/O control register (SIOCON)

16

UART control register (UARTCON)

16

Baud rate generator (BRG)

16

PWM control register (PWMCON)

16

PWM prescaler (PREPWM)

16

PWM register (PWM)

16

✽ Reserved : Do not write “1” to this address.

0020

0021

0022

0023

0024

0025

0026

0027

0028

0029

002A

002B

002C

002D

002E

002F

0030

0031

0032

0033

0034

0035

0036

0037

0038

0039

003A

003B

003C

003D

003E

003F

Prescaler 12 (PRE12)

16

Timer 1 (T1)

16

Timer 2 (T2)

16

Timer XY mode register (TM)

16

Prescaler X (PREX)

16

Timer X (TX)

16

Prescaler Y (PREY)

16

Timer Y (TY)

16

Timer count source selection register (TCSS)

16

16

16

2C

16

data shift register (S0)

I

2

16

C address register (S0D)

I

2

16

C status register (S1)

I

2

16

C control register (S1D)

I

2C

16

clock control register (S2)

I

2

16

C start/stop condition control register (S2D)

I

16

16

16

A-D control register (ADCON)

16

A-D conversion low-order register (ADL)

16

A-D conversion high-order register (ADH)

16

16

MISRG

16

Watchdog timer control register (WDTCON)

16

Interrupt edge selection register (INTEDGE)

16

CPU mode register (CPUM)

16

Interrupt request register 1 (IREQ1)

16

Interrupt request register 2 (IREQ2)

16

Interrupt control register 1 (ICON1)

16

Interrupt control register 2 (ICON2)

16

Fig. 6 Memory map of special function register (SFR)

7

I/O PORTS

The I/O ports have direction registers which determine the input/

output direction of each individual pin. Each bit in a direction register corresponds to one pin, and each pin can be set to be input

port or output port.

When “0” is written to the bit corresponding to a pin, that pin becomes an input pin. When “1” is written to that bit, that pin

becomes an output pin.

If data is read from a pin which is set to output, the value of the

port output latch is read, not the value of the pin itself. Pins set to

input are floating. If a pin set to input is written to, only the port

output latch is written to and the pin remains floating.

Table 2 I/O port function

Pin

P00–P07

P10–P17

P20/XCOUT

P21/XCIN

P22/SDA1

P23/SCL1

P24/SDA2/RxD

P25/SCL2/TxD

P26/SCLK

P27/CNTR0/SRDY

P30/AN0—

P34/AN4

P40/CNTR1

P41/INT0—

P43/INT2

P44/INT3/PWM

Name

Port P0

Port P1

Port P2

Port P3

Port P4

Input/Output

Input/output,

individual

bits

I/O Structure Non-Port Function

CMOS compatible

input level

CMOS 3-state output Sub-clock generating

CMOS compatible

input level

CMOS/SMBUS input

level (when selecting

2

I

C-BUS interface

function)

N-channel open-drain

output

CMOS compatible

input level

CMOS/SMBUS input

level (when selecting

I2C-BUS interface

function)

CMOS 3-state output

N-channel open-drain

output (when

selecting I2C-BUS

interface function)

CMOS compatible

input level

CMOS 3-state output

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

circuit

I2C-BUS interface function I/O

2

C-BUS interface func-

I

tion I/O

Serial I/O function I/O

Serial I/O function I/O

Serial I/O function I/O

Timer X function I/O

A-D conversion input

Timer Y function I/O

External interrupt input

External interrupt input

PWM output

3851 Group

Related SFRs

CPU mode register

2

I

C control register

I2C control register

Serial I/O control

register

Serial I/O control

register

Serial I/O control

register

Timer XY mode register

A-D control register

Timer XY mode register

Interrupt edge selection

register

Interrupt edge selection

register

PWM control register

Ref.No.

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(12)

(13)

8

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

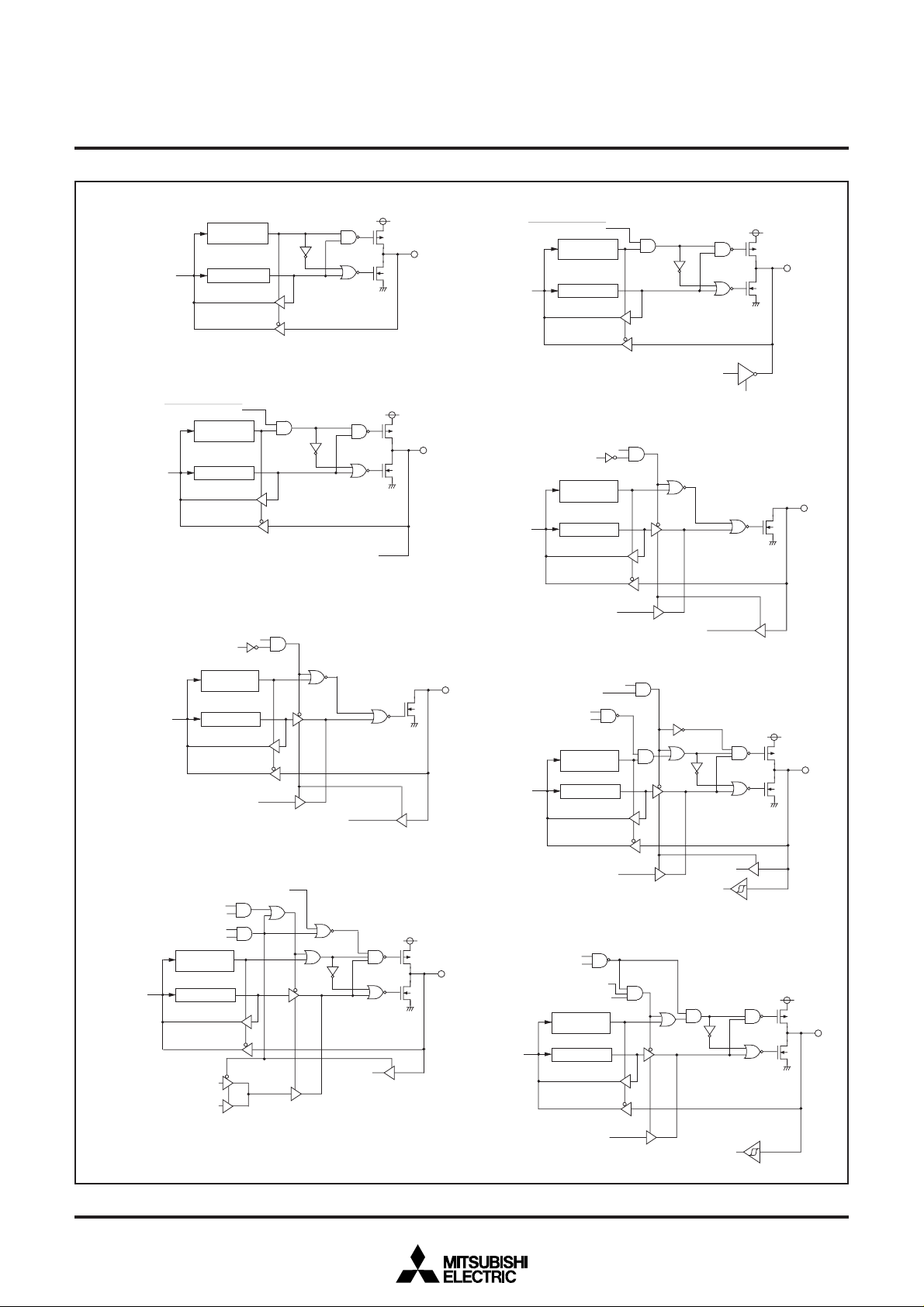

(1) Port P0, P1

Data bus

(3) Port P2

Data bus

(5) Port P2

SDA/SCL pin selection bit

Data bus

1

Port XC switch bit

Direction

register

Port latch

2

I C-BUS interface enable bit

3

Direction

register

Port latch

Direction

register

Port latch

Sub-clock generating circuit input

(2) Port P2

Data bus

(4) Port P2

2

I C-BUS interface enable bit

SDA/SCL pin selection bit

Data bus

(6) Port P2

SDA/SCL pin selection bit

0

Port XC switch bit

Direction

register

Port latch

2

Direction

register

Port latch

SDA output

4

2

I C-BUS interface enable bit

Serial I/O enable bit

Receive enable bit

Port P2

SDA input

1

Port X

Oscillator

C switch bit

SCL output

(7) Port P2

2

I C bus interface enable bit

SDA/SCL pin selection bit

Data bus

5

P-channel output disable bit

Serial I/O enable bit

Transmit enable bit

Direction

register

Port latch

Serial I/O output

SCL output

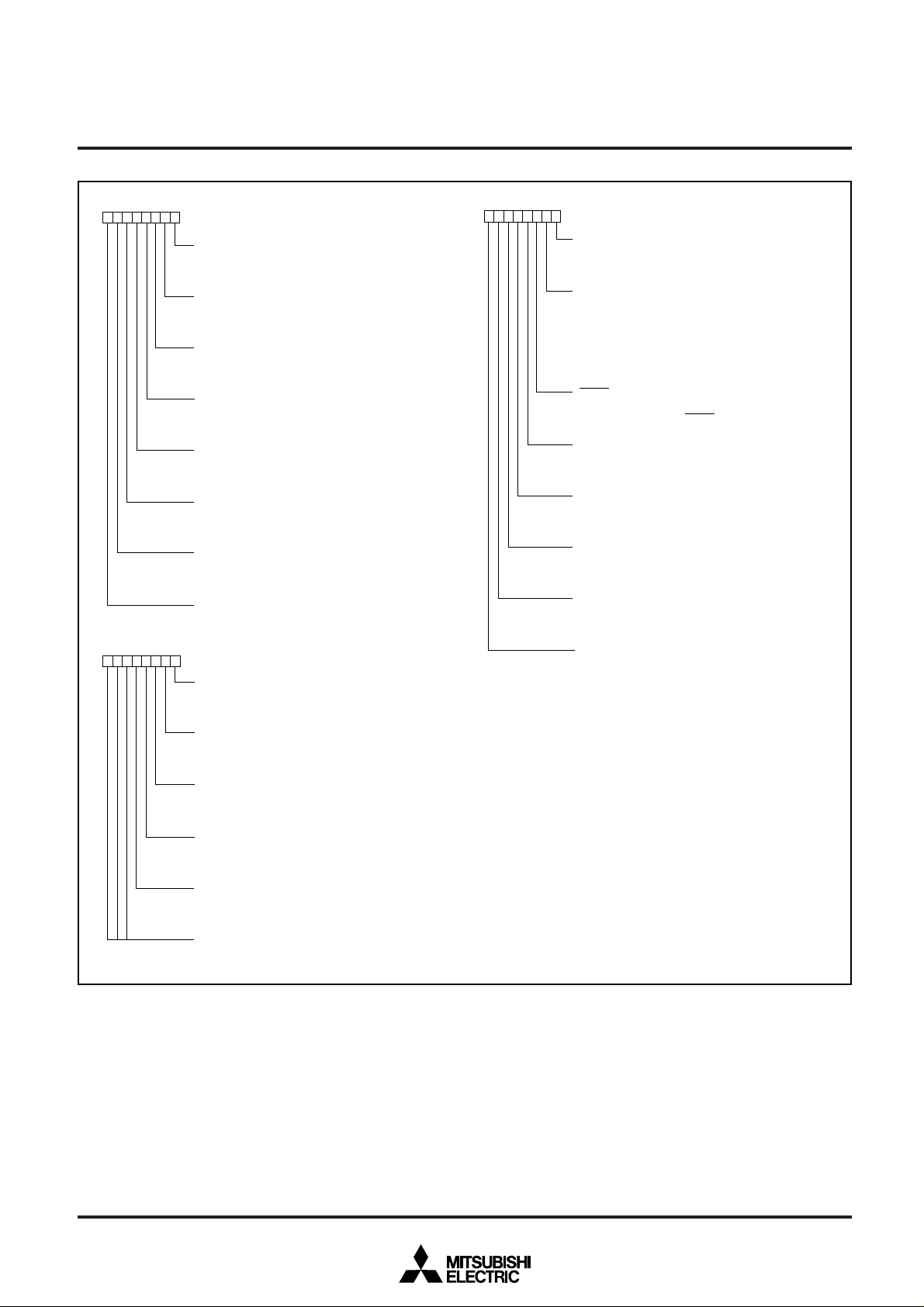

Fig. 7 Port block diagram (1)

SCL input

SCL input

Data bus

SDA output

(8) Port P2

Serial I/O enable bit

Serial I/O clock selection bit

Serial I/O mode selection bit

Data bus

6

Serial I/O enable bit

Direction

register

Port latch

Serial clock output

Direction

register

Port latch

SDA input

Serial I/O input

External clock input

9

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

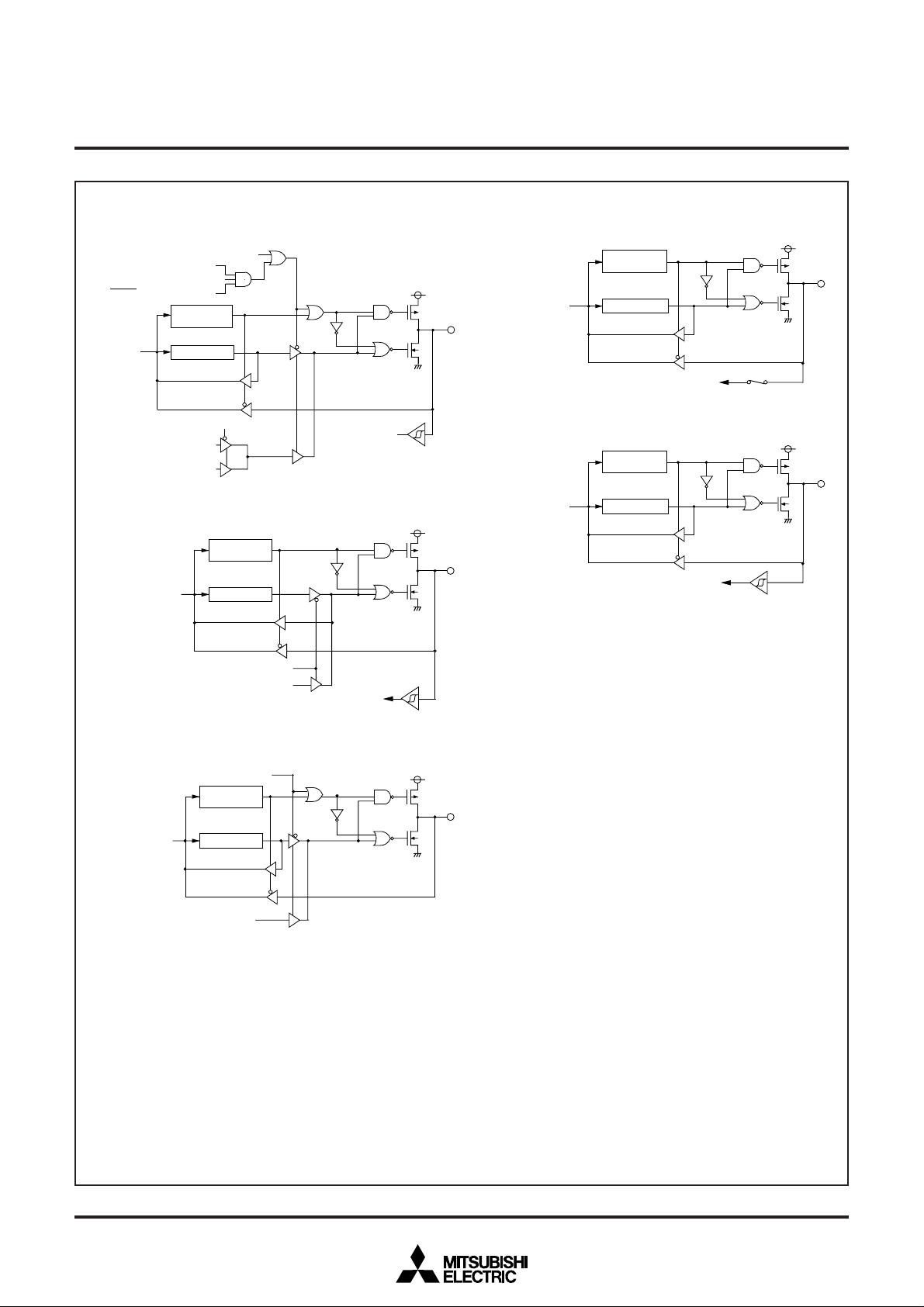

(9) Port P2

Serial I/O mode selection bit

Serial I/O enable bit

S

RDY

output enable bit

Data bus

Serial ready output

(11) Port P4

7

Pulse output mode

Direction

register

Port latch

Pulse output mode

Timer output

0

Data bus Port latch

Direction

register

Pulse output mode

Timer output

CNTR

0

interrupt

CNTR1 interrupt input

input

(10) Port P30–P3

Data bus

(12) Port P41–P4

Data bus

4

Direction

register

Port latch

A-D converter input

3

Direction

register

Port latch

Analog input pin selection bit

Interrupt input

(13) Port P4

Data bus

4

PWM output enable bit

Direction

register

Port latch

PWM output

Fig. 8 Port block diagram (2)

10

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

INTERRUPTS

Interrupts occur by 16 sources among 16 sources: seven external,

eight internal, and one software.

Interrupt Control

Each interrupt is controlled by an interrupt request bit, an interrupt

enable bit, and the interrupt disable flag except for the software interrupt set by the BRK instruction. An interrupt occurs if the

corresponding interrupt request and enable bits are “1” and the interrupt disable flag is “0”.

Interrupt enable bits can be set or cleared by software.

Interrupt request bits can be cleared by software, but cannot be

set by software.

The BRK instruction cannot be disabled with any flag or bit. The I

(interrupt disable) flag disables all interrupts except the BRK instruction interrupt.

When several interrupts occur at the same time, the interrupts are

received according to priority.

Interrupt Operation

By acceptance of an interrupt, the following operations are automatically performed:

1. The contents of the program counter and the processor status

register are automatically pushed onto the stack.

2. The interrupt disable flag is set and the corresponding interrupt

request bit is cleared.

3. The interrupt jump destination address is read from the vector

table into the program counter.

■Notes

When the active edge of an external interrupt (INT0–INT3, SCL/

SDA, CNTR

bit may also be set. Therefore, take the following sequence:

1. Disable the interrupt

2. Change the interrupt edge selection register

(SCL/SDA interrupt pin polarity selection bit for SCL/SDA; the

timer XY mode register for CNTR

3. Clear the interrupt request bit to “0”

4. Accept the interrupt.

0, CNTR1) is set, the corresponding interrupt request

0 and CNTR1)

11

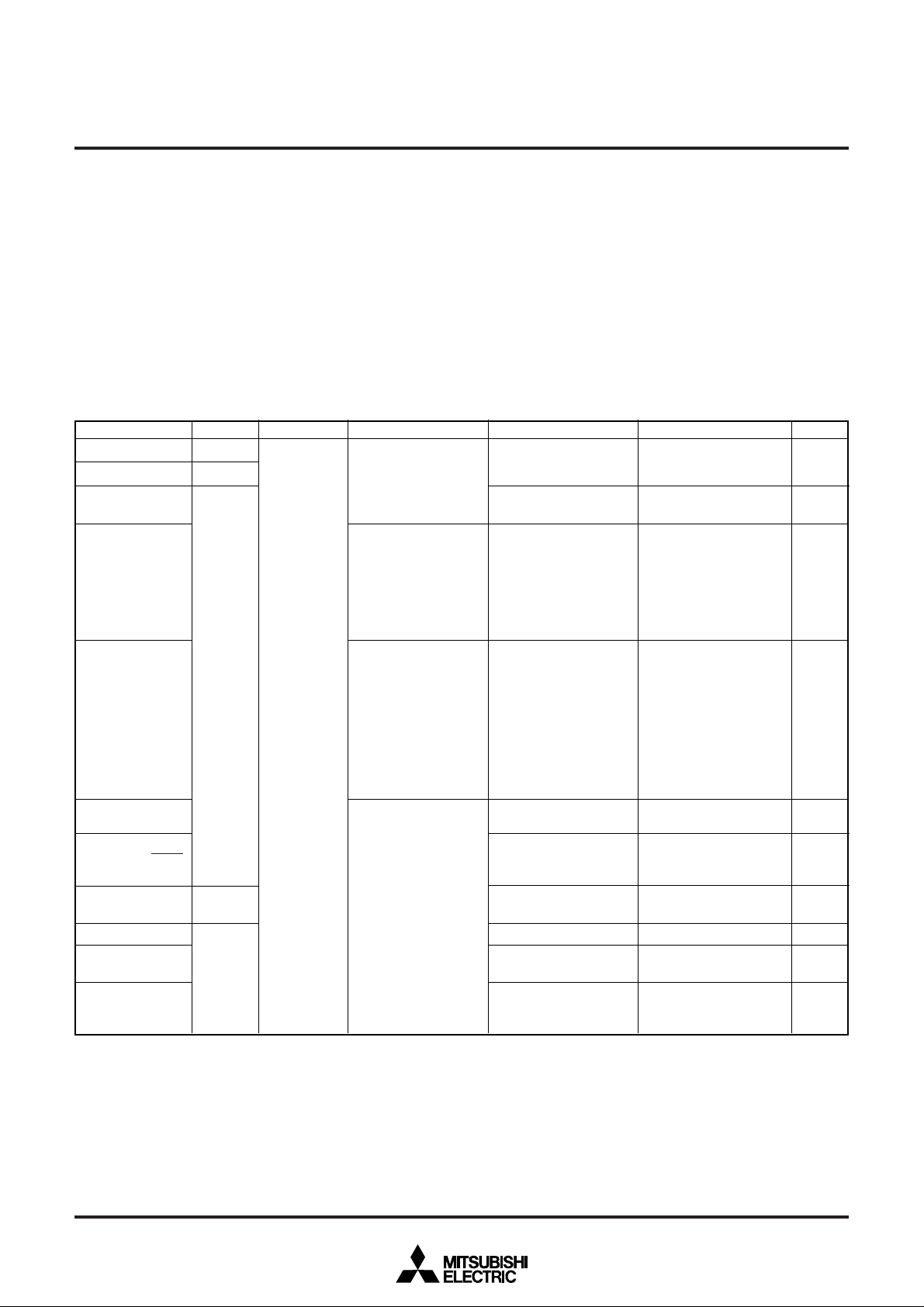

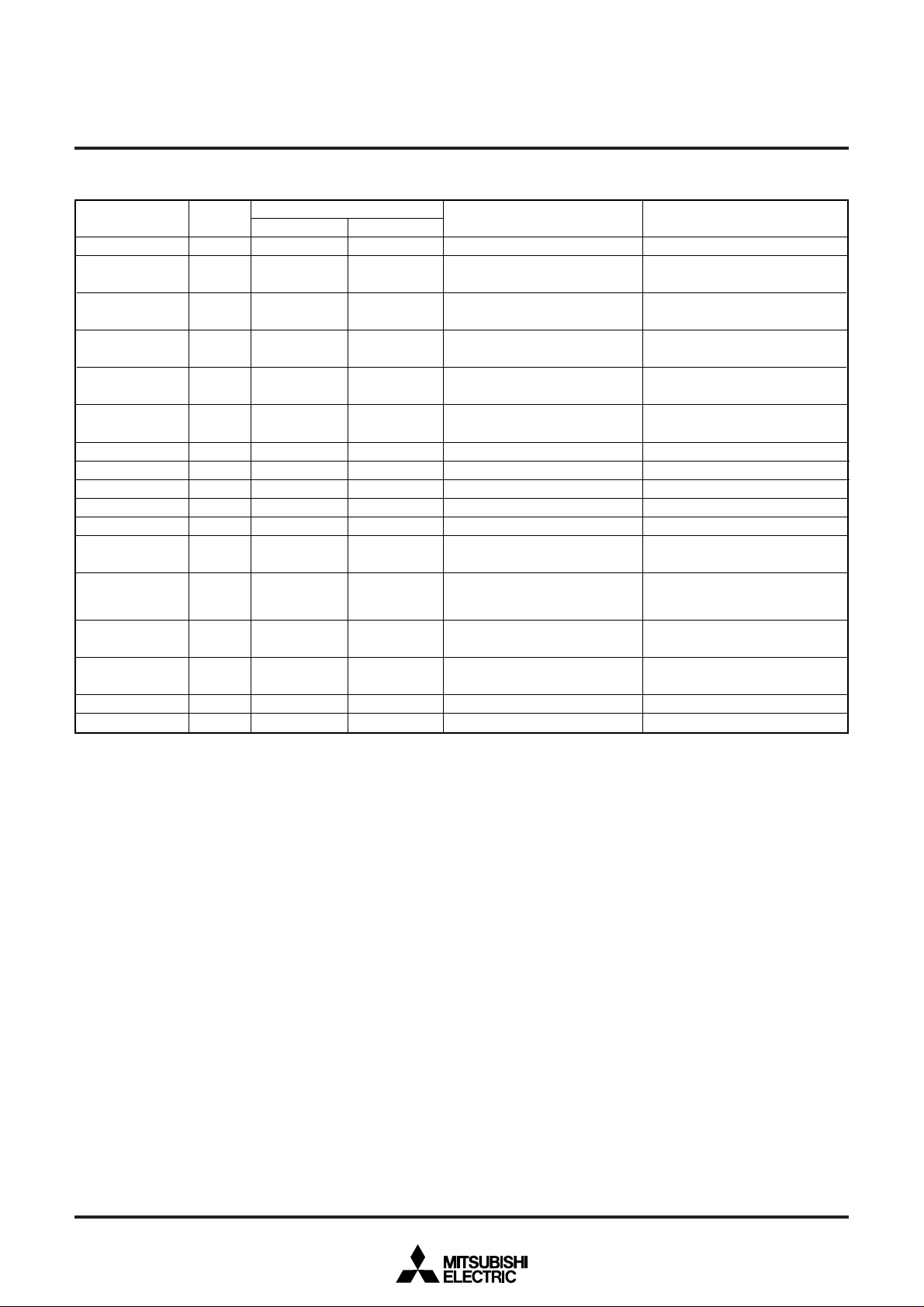

Table 3 Interrupt vector addresses and priority

Interrupt Source

Reset (Note 2)

INT0

SCL, SDA

1

INT

INT2

INT3

I2C

Timer X

Timer Y

Timer 1

Timer 2

Serial I/O

reception

Serial I/O

Transmission

0

CNTR

CNTR1

A-D converter

BRK instruction

Notes 1: Vector addresses contain interrupt jump destination addresses.

2: Reset function in the same way as an interrupt with the highest priority.

Priority

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Vector Addresses (Note 1)

High

FFFD16

FFFB16

FFF916

FFF716

FFF516

FFF316

FFF116

FFEF16

FFED16

FFEB16

FFE916

FFE716

FFE516

FFE316

FFE116

FFDF16

Low

FFFC

FFFA

16

FFF816

FFF616

FFF416

FFF216

FFF016

FFEE16

FFEC16

FFEA16

FFE816

FFE616

FFE416

FFE216

FFE016

FFDE16

16

FFDC16FFDD16

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Interrupt Request

Generating Conditions

At reset

At detection of either rising or

falling edge of INT0 input

At detection of either rising or

falling edge of SCL or SDA input

At detection of either rising or

falling edge of INT

At detection of either rising or

falling edge of INT

At detection of either rising or

falling edge of INT

At completion of data transfer

At timer X underflow

At timer Y underflow

At timer 1 underflow

At timer 2 underflow

At completion of serial I/O data

reception

At completion of serial I/O transfer shift or when transmission

buffer is empty

At detection of either rising or

falling edge of CNTR0 input

At detection of either rising or

falling edge of CNTR1 input

At completion of A-D conversion

At BRK instruction execution

1 input

2 input

3 input

3851 Group

Remarks

Non-maskable

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

STP release timer underflow

Valid when serial I/O is selected

Valid when serial I/O is selected

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

Non-maskable software interrupt

12

Interrupt request bit

Interrupt enable bit

Interrupt disable flag (I)

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 9 Interrupt control

b7 b0

b7 b0

BRK instruction

Interrupt edge selection register

(INTEDGE : address 003A

INT0 active edge selection bit

1

active edge selection bit

INT

2

active edge selection bit

INT

3

active edge selection bit

INT

Not used (returns “0” when read)

Interrupt request register 1

(IREQ1 : address 003C

INT0 interrupt request bit

SCL/SDA interrupt request bit

1

interrupt request bit

INT

2

interrupt request bit

INT

3

interrupt request bit

INT

2

I

C interrupt request bit

Timer X interrupt request bit

Timer Y interrupt request bit

0 : No interrupt request issued

1 : Interrupt request issued

16

)

16

)

Reset

0 : Falling edge active

1 : Rising edge active

b7 b0

Interrupt request

Interrupt request register 2

16

(IREQ2 : address 003D

Timer 1 interrupt request bit

Timer 2 interrupt request bit

Serial I/O reception interrupt request bit

Serial I/O transmit interrupt request bit

0

interrupt request bit

CNTR

1

interrupt request bit

CNTR

AD converter interrupt request bit

Not used (returns “0” when read)

0 : No interrupt request issued

1 : Interrupt request issued

)

b7 b0

Interrupt control register 1

(ICON1 : address 003E

16

)

INT0 interrupt enable bit

SCL/SDA interrupt enable bit

1

interrupt enable bit

INT

2

interrupt enable bit

INT

3

interrupt enable bit

INT

2

I

C interrupt enable bit

Timer X interrupt enable bit

Timer Y interrupt enable bit

0 : Interrupts disabled

1 : Interrupts enabled

Fig. 10 Structure of interrupt-related registers (1)

b7 b0

Interrupt control register 2

16

(ICON2 : address 003F

)

Timer 1 interrupt enable bit

Timer 2 interrupt enable bit

Serial I/O reception interrupt enable bit

Serial I/O transmit interrupt enable bit

0

interrupt enable bit

CNTR

1

interrupt enable bit

CNTR

AD converter interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit)

0 : Interrupts disabled

1 : Interrupts enabled

13

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

TIMERS

The 3851 group has four timers: timer X, timer Y, timer 1, and

timer 2.

The division ratio of each timer or prescaler is given by 1/(n + 1),

where n is the value in the corresponding timer or prescaler latch.

All timers are count down. When the timer reaches “00

derflow occurs at the next count pulse and the corresponding

timer latch is reloaded into the timer and the count is continued.

When a timer underflows, the interrupt request bit corresponding

to that timer is set to “1”.

b7

b0

Timer XY mode register

(TM : address 0023

Timer X operating mode bit

b1b0

0 0: Timer mode

0 1: Pulse output mode

1 0: Event counter mode

1 1: Pulse width measurement mode

CNTR0 active edge selection bit

0: Interrupt at falling edge

Count at rising edge in event

counter mode

1: Interrupt at rising edge

Count at falling edge in event

counter mode

Timer X count stop bit

0: Count start

1: Count stop

Timer Y operating mode bit

b5b4

0 0: Timer mode

0 1: Pulse output mode

1 0: Event counter mode

1 1: Pulse width measurement mode

1 active edge selection bit

CNTR

0: Interrupt at falling edge

Count at rising edge in event

counter mode

1: Interrupt at rising edge

Count at falling edge in event

counter mode

Timer Y count stop bit

0: Count start

1: Count stop

Fig. 11 Structure of timer XY mode register

b7

b0

Timer count source selection register

(TCSS : address 0028

Timer X count source selection bit

IN

)/16 (f(X

IN

)/16 (f(X

IN

)/16 (f(X

CIN

CIN

CIN

CIN

CIN

CIN

)

0 : f(X

1 : f(XIN)/2 (f(X

Timer Y count source selection bit

0 : f(X

1 : f(XIN)/2 (f(X

Timer 12 count source selection bit

0 : f(X

1 : f(X

Not used (returns “0” when read)

16”, an un-

16)

16

)

)/16 at low-speed mode)

)/2 at low-speed mode)

)/16 at low-speed mode)

)/2 at low-speed mode)

)/16 at low-speed mode)

Timer 1 and Timer 2

The count source of prescaler 12 is the oscillation frequency divided by 16. The output of prescaler 12 is counted by timer 1 and

timer 2, and a timer underflow sets the interrupt request bit.

Timer X and Timer Y

Timer X and Timer Y can each select in one of four operating

modes by setting the timer XY mode register.

(1) Timer Mode

The timer counts the count source selected by Timer count source

selection bit.

(2) Pulse Output Mode

The timer counts the count source selected by Timer count source

selection bit. Whenever the contents of the timer reach “00

signal output from the CNTR

CNTR

0 (or CNTR1) active edge selection bit is “0”, output begins

0 (or CNTR1) pin is inverted. If the

16”, the

at “ H”.

If it is “1”, output starts at “L”. When using a timer in this mode, set

the corresponding port P2

7 ( or port P40) direction register to out-

put mode.

(3) Event Counter Mode

Operation in event counter mode is the same as in timer mode, except that the timer counts signals input through the CNTR

CNTR

1 pin.

When the CNTR

rising edge of the CNTR

When the CNTR

falling edge of the CNTR

0 (or CNTR1) active edge selection bit is “0”, the

0 (or CNTR1) pin is counted.

0 (or CNTR1) active edge selection bit is “1”, the

0 (or CNTR1) pin is counted.

0 or

(4) Pulse Width Measurement Mode

If the CNTR0 (or CNTR1) active edge selection bit is “0”, the timer

counts the selected signals by the count source selection bit while

the CNTR

0 (or CNTR1) pin is at “H”. If the CNTR0 (or CNTR1) ac-

tive edge selection bit is “1”, the timer counts it while the CNTR

(or CNTR1) pin is at “L”.

The count can be stopped by setting “1” to the timer X (or timer Y)

count stop bit in any mode. The corresponding interrupt request

bit is set each time a timer overflows.

■Note

When switching the count source by the timer 12, X and Y count

source bit, the value of timer count is altered in unconsiderable

amount owing to generating of a thin pulses in the count input

signals.

Therefore, select the timer count source before set the value to

the prescaler and the timer.

0

Fig. 12 Structure of timer count source selection register

14

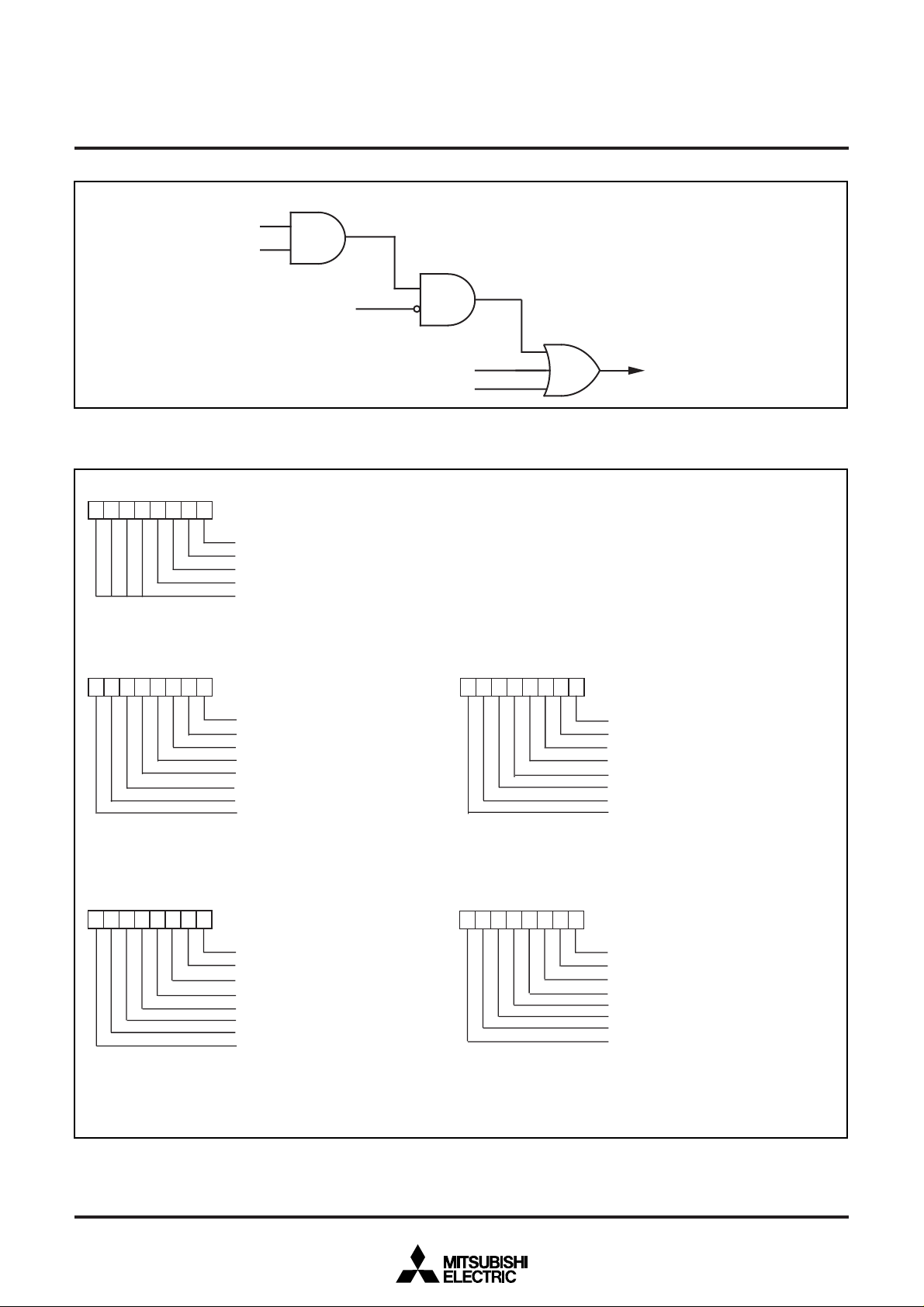

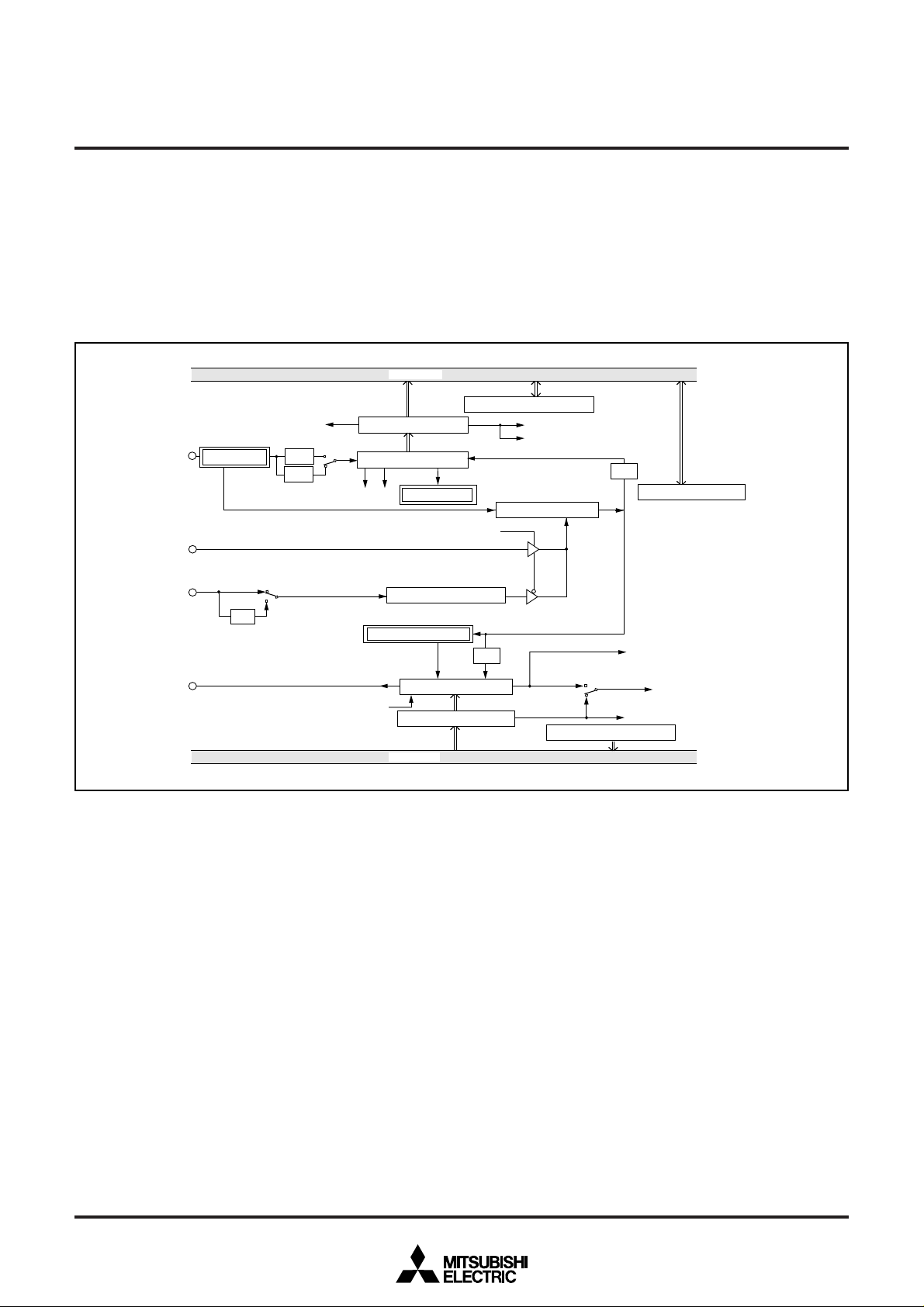

Data bus

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

f(XIN)/16

f(XIN)/2

Timer X count source selection bit

7/CNTR0

P2

7

Port P2

direction register

f(XIN)/16

f(XIN)/2

Timer Y count source selection bit

P40/CNTR1

Port P4

direction register

CNTR

edge selection

“0”

“1”

Port P2

latch

Pulse output mode

CNTR

edge selection

“0”

“1”

Port P4

0

Pulse output mode

latch

0 active

bit

7

1 active

bit

0

Pulse width

measurement

mode

Event

counter

mode

CNTR

edge selection

bit

Pulse width

measurement mode

Event

counter

mode

CNTR1 active

edge selection

bit

Timer mode

Pulse output mode

Timer X count stop bit

0 active

“1”

“0”

Timer mode

Pulse output mode

Timer Y count stop bit

“1”

“0”

Data bus

Prescaler X latch (8)

Prescaler X (8)

Q

Toggle flip-flop

Q

R

Data bus

Prescaler Y latch (8)

Prescaler Y (8)

Q

Toggle flip-flop

Q

R

Timer X latch (8)

Timer X (8)

T

Timer X latch write pulse

Pulse output mode

Timer Y latch (8)

Timer Y (8)

T

Timer Y latch write pulse

Pulse output mode

To timer X interrupt

request bit

To CNTR

0 interrupt

request bit

To timer Y interrupt

request bit

To CNTR

1 interrupt

request bit

Prescaler 12 latch (8)

f(XIN)/16

f(XCIN)

Timer 12 count source selection bit

Prescaler 12 (8)

Fig. 13 Block diagram of timer X, timer Y, timer 1, and timer 2

Timer 1 latch (8)

Timer 1 (8)

Timer 2 latch (8)

Timer 2 (8)

To timer 2 interrupt

request bit

To timer 1 interrupt

request bit

15

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

SERIAL I/O

Serial I/O can be used as either clock synchronous or asynchronous (UART) serial I/O. A dedicated timer is also provided for baud

rate generation.

Data bus

Address 0018

Transmit shift register

Transmit buffer register

Data bus

P24/RXD

P26/SCLK

XIN

P2

7/SRDY

P2

5/TXD

Receive buffer register

Receive shift register

BRG count source selection bit

1/4

F/F

Falling-edge detector

(1) Clock Synchronous Serial I/O Mode

Clock synchronous serial I/O mode can be selected by setting the

serial I/O mode selection bit of the serial I/O control register (bit 6

of address 001A

For clock synchronous serial I/O, the transmitter and the receiver

must use the same clock. If an internal clock is used, transfer is

started by a write signal to the TB/RB.

16

Shift clock

Serial I/O synchronous

clock selection bit

Frequency division ratio 1/(n+1)

Baud rate generator

Address 001C

Shift clock

Address 0018

Clock control circuit

16

Clock control circuit

16

16) to “1”.

Serial I/O control register

Receive buffer full flag (RBF)

Receive interrupt request (RI)

1/4

Transmit interrupt source selection bit

Serial I/O status register

Address 001A16

Transmit shift completion flag (TSC)

Transmit interrupt request (TI)

Transmit buffer empty flag (TBE)

Address 0019

16

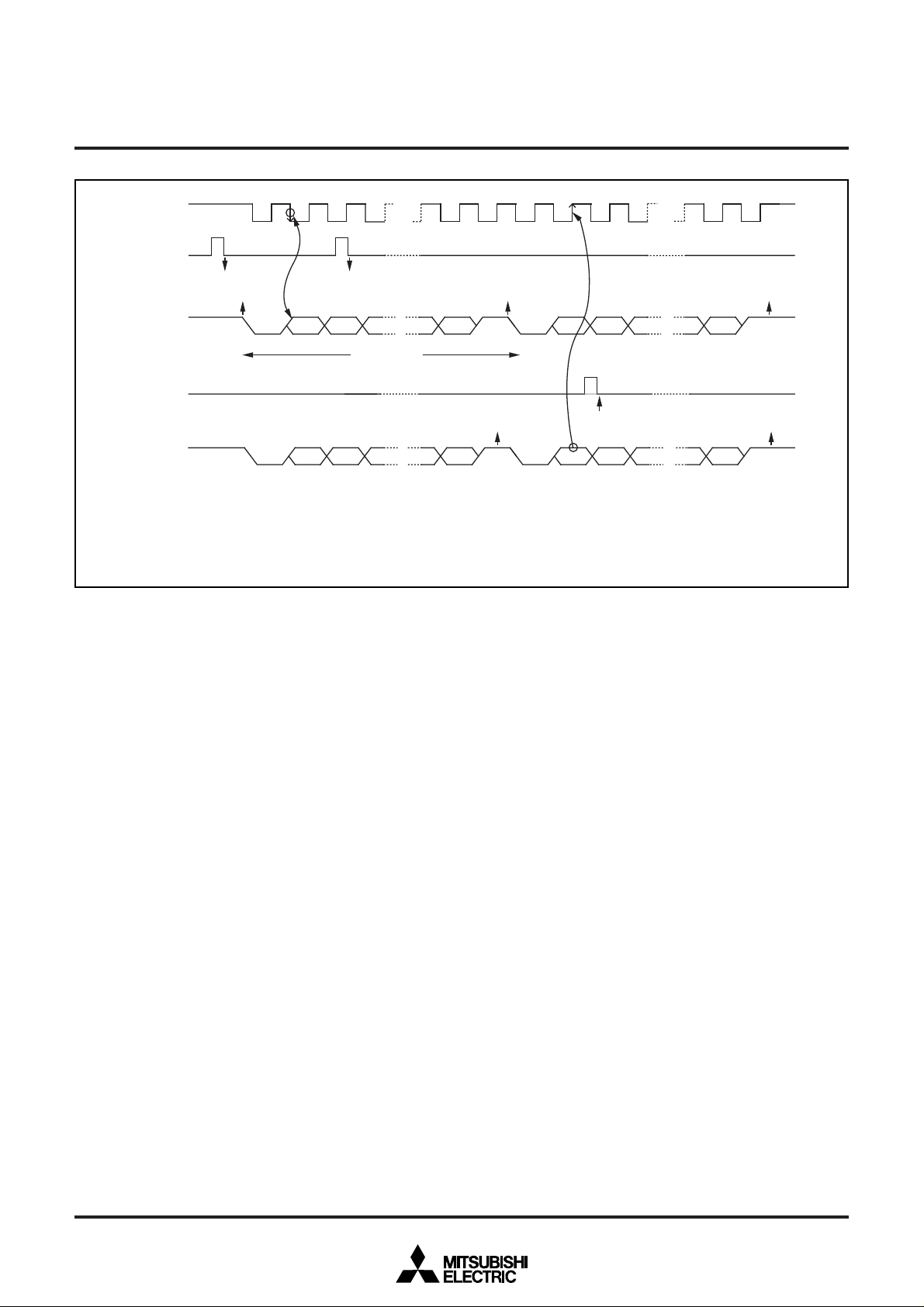

Fig. 14 Block diagram of clock synchronous serial I/O

Transfer shift clock

(1/2 to 1/2048 of the internal

clock, or an external clock)

Serial output TxD

Serial input RxD

Receive enable signal S

RDY

D

0

D

0

Write pulse to receive/transmit

buffer register (address 0018

16

)

TBE = 0

TBE = 1

TSC = 0

1: As the transmit interrupt (TI), either when the transmit buffer has emptied (TBE=1) or after the transmit shift operation has

Notes

ended (TSC=1), by setting the transmit interrupt source selection bit (TIC) of the serial I/O control register.

2: If data is written to the transmit buffer register when TSC=0, the transmit clock is generated continuously and serial data

is output continuously from the TxD pin.

3: The receive interrupt (RI) is set when the receive buffer full flag (RBF) becomes “1” .

Fig. 15 Operation of clock synchronous serial I/O function

D

D

1

D

1

D

2

D

2

D

3

D

3

D

4

D

4

D

5

D

5

D

6

D

6

7

D

7

RBF = 1

TSC = 1

Overrun error (OE)

detection

16

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

(2) Asynchronous Serial I/O (UART) Mode

Clock asynchronous serial I/O mode (UART) can be selected by

clearing the serial I/O mode selection bit (b6) of the serial I/O control register to “0”.

Eight serial data transfer formats can be selected, and the transfer

formats used by a transmitter and receiver must be identical.

The transmit and receive shift registers each have a buffer, but the

Data bus

P2

P2

P2

4/RX

6/SCLK1

X

5/TX

D

ST detector

BRG count source selection bit

IN

D

Character length selection bit

1/4

Character length selection bit

Address 0018

OE

7 bits

8 bits

Serial I/O synchronous clock selection bit

16

Receive buffer register

Receive shift register

PE FE

SP detector

Frequency division ratio 1/(n+1)

Baud rate generator

Address 001C

ST/SP/PA generator

Transmit shift register

Transmit buffer register

Data bus

two buffers have the same address in memory. Since the shift register cannot be written to or read from directly, transmit data is

written to the transmit buffer register, and receive data is read from

the receive buffer register.

The transmit buffer register can also hold the next data to be

transmitted, and the receive buffer register can hold a character

while the next character is being received.

Serial I/O control register

Receive buffer full flag (RBF)

Receive interrupt request (RI)

Clock control circuit

16

1/16

Transmit interrupt source selection bit

Address

0018

Serial I/O status register

16

Address 001A

1/16

16

UART control register

Address 001B

Transmit shift completion flag (TSC)

Transmit interrupt request (TI)

Transmit buffer empty flag (TBE)

Address

0019

16

16

Fig.16 Block diagram of UART serial I/O

17

Transmit or receive clock

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Transmit buffer write

Receive buffer read

signal

TBE=0 TBE=0

TSC=0

TBE=1

Serial output TXD

signal

Serial input R

Notes

X

D

1: Error flag detection occurs at the same time that the RBF flag becomes “1” (at 1st stop bit, during reception).

2: As the transmit interrupt (TI), when either the TBE or TSC flag becomes “1,” can be selected to occur depending on the setting of the transmit

interrupt source selection bit (TIC) of the serial I/O control register.

3: The receive interrupt (RI) is set when the RBF flag becomes “1.”

4: After data is written to the transmit buffer when TSC=1, 0.5 to 1.5 cycles of the data shift cycle is necessary until changing to TSC=0.

ST

0

D

1

1 start bit

7 or 8 data bit

1 or 0 parity bit

1 or 2 stop bit (s)

ST

0

D

1

Fig. 17 Operation of UART serial I/O function

[Transmit Buffer Register/Receive Buffer

Register (TB/RB)] 0018

The transmit buffer register and the receive buffer register are located at the same address. The transmit buffer is write-only and

the receive buffer is read-only . If a character bit length is 7 bits, the

MSB of data stored in the receive buffer is “0”.

16

[Serial I/O Status Register (SIOSTS)] 001916

The read-only serial I/O status register consists of seven flags

(bits 0 to 6) which indicate the operating status of the serial I/O

function and various errors.

Three of the flags (bits 4 to 6) are valid only in UART mode.

The receive buffer full flag (bit 1) is cleared to “0” when the receive

buffer register is read.

If there is an error, it is detected at the same time that data is

transferred from the receive shift register to the receive buffer register, and the receive buffer full flag is set. A write to the serial I/O

status register clears all the error flags OE, PE, FE, and SE (bit 3

to bit 6, respectively). Writing “0” to the serial I/O enable bit SIOE

(bit 7 of the serial I/O control register) also clears all the status

flags, including the error flags.

Bits 0 to 6 of the serial I/O status register are initialized to “0” at reset, but if the transmit enable bit (bit 4) of the serial I/O control

register has been set to “1”, the transmit shift completion flag (bit

2) and the transmit buffer empty flag (bit 0) become “1”.

TBE=1

STD

SP

RBF=1

STD

SP D

D

0

D

1

Generated at 2nd bit in 2-stop-bit mode

RBF=0

0

D

1

TSC=1

SP

RBF=1

SP

Serial I/O Control Register (SIOCON)] 001A16

The serial I/O control register consists of eight control bits for the

serial I/O function.

[UART Control Register (UARTCON)] 001B16

The UART control register consists of four control bits (bits 0 to 3)

which are valid when asynchronous serial I/O is selected and set

the data format of an data transfer and one bit (bit 4) which is always valid and sets the output structure of the P2

5/TXD pin.

[Baud Rate Generator (BRG)] 001C16

The baud rate generator determines the baud rate for serial transfer.

The baud rate generator divides the frequency of the count source

by 1/(n + 1), where n is the value written to the baud rate generator.

■Note

When using the serial I/O, clear the I2C-BUS interface enable bit

to “0” or the S

CL/SDA interrupt pin selection bit to “0”.

18

MITSUBISHI MICROCOMPUTERS

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b7

b0

Serial I/O status register

(SIOSTS : address 001916)

b7

Transmit buffer empty flag (TBE)

0: Buffer full

1: Buffer empty

Receive buffer full flag (RBF)

0: Buffer empty

1: Buffer full

Transmit shift completion flag (TSC)

0: Transmit shift in progress

1: Transmit shift completed

Overrun error flag (OE)

0: No error

1: Overrun error

Parity error flag (PE)

0: No error

1: Parity error

Framing error flag (FE)

0: No error

1: Framing error

Summing error flag (SE)

0: (OE) U (PE) U (FE)=0

1: (OE) U (PE) U (FE)=1

Not used (returns “1” when read)

b0

Serial I/O control register

(SIOCON : address 001A

16

)

BRG count source selection bit (CSS)

0: f(X

IN

)

1: f(X

IN

)/4

Serial I/O synchronous clock selection bit (SCS)

0: BRG output divided by 4 when clock synchronous

serial I/O is selected, BRG output divided by 16

when UART is selected.

1: External clock input when clock synchronous serial

I/O is selected, external clock input divided by 16

when UART is selected.

S

RDY

output enable bit (SRDY)

0: P2

7

pin operates as ordinary I/O pin

1: P2

7

pin operates as S

RDY

output pin

Transmit interrupt source selection bit (TIC)

0: Interrupt when transmit buffer has emptied

1: Interrupt when transmit shift operation is completed

Transmit enable bit (TE)

0: Transmit disabled

1: Transmit enabled

Receive enable bit (RE)

0: Receive disabled

1: Receive enabled

Serial I/O mode selection bit (SIOM)

0: Clock asynchronous (UART) serial I/O

1: Clock synchronous serial I/O

b7

b0

UART control register

(UARTCON : address 001B

Character length selection bit (CHAS)

0: 8 bits

1: 7 bits

Serial I/O enable bit (SIOE)

16

)

0: Serial I/O disabled

(pins P2

4

to P27 operate as ordinary I/O pins)

1: Serial I/O enabled

(pins P2

4

to P27 operate as serial I/O pins)

Parity enable bit (PARE)

0: Parity checking disabled

1: Parity checking enabled

Parity selection bit (PARS)

0: Even parity

1: Odd parity

Stop bit length selection bit (STPS)

0: 1 stop bit

1: 2 stop bits

P2

5/TX

D P-channel output disable bit (POFF)

0: CMOS output (in output mode)

1: N-channel open drain output (in output mode)

Not used (return “1” when read)

Fig. 18 Structure of serial I/O control registers

19

Loading...

Loading...