Mitsubishi M38279EF-XXXFP, M38277M8MXXXHP, M38277M8MXXXGP, M38277M8MXXXFP, M38279EFHP Datasheet

...

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

DESCRIPTION

The 3827 group is the 8-bit microcomputer based on the 740 family core technology.

The 3827 group has the LCD drive control circuit, the A-D/D-A

converter, the UART, and the PWM as additional functions.

The various microcomputers in the 3827 group include variations

of internal memory size and packaging. For details, refer to the

section on part numbering.

For details on availability of microcomputers in the 3827 group, refer to the section on group expansion.

FEATURES

●Basic machine-language instructions ...................................... 71

●The minimum instruction execution time ........................... 0.5 µs

(at 8MHz oscillation frequency)

●Memory size

ROM ................................................................. 4 K to 60 K bytes

RAM.................................................................192 to 2048 bytes

●Programmable input/output ports ............................................ 55

●Output port ................................................................................. 8

●Input port .................................................................................... 1

●Interrupts ................................................. 17 sources, 16 vectors

(includes key input interrupt)

●Timers ...........................................................8-bit ✕ 3, 16-bit ✕ 2

●Ser ial I/O1 ....................8-bit ✕ 1 (UART or Clock-synchronized)

●Serial I/O2 ...................................8-bit ✕ 1 (Clock-synchronized)

●PWM output .................................................................... 8-bit ✕ 1

●A-D con verter ............................................... 10-bit ✕ 8 channels

●D-A con verter ................................................. 8-bit ✕ 2 channels

●LCD drive control circuit

Bias...................................................................................1/2, 1/3

Duty ........................................................................... 1/2, 1/3, 1/4

Common output.......................................................................... 4

Segment output ........................................................................ 40

●2 Clock generating circuits

(connect to external ceramic resonator or quartz-crystal oscillator)

●Watchdog timer ............................................................ 14-bit ✕ 1

●Power source voltage ................................................ 2.2 to 5.5 V

●Power dissipation

In high-speed mode ..........................................................40 mW

(at 8 MHz oscillation frequency, at 5 V power source voltage)

In low-speed mode............................................................ 60 µW

(at 32 kHz oscillation frequency, at 3 V power source voltage)

●Operating temperature range................................... – 20 to 85°C

APPLICATIONS

Camera, wireless phone, etc.

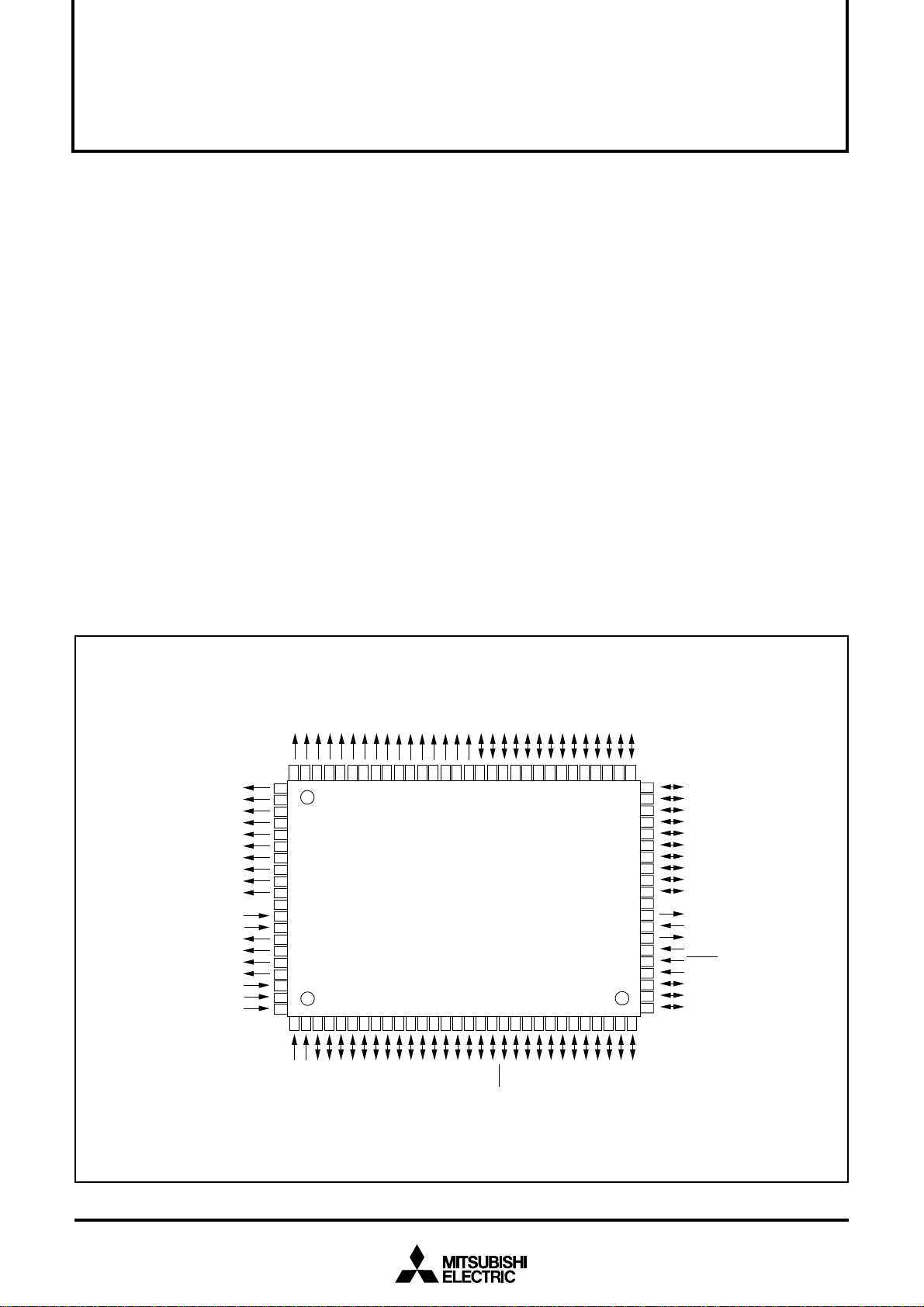

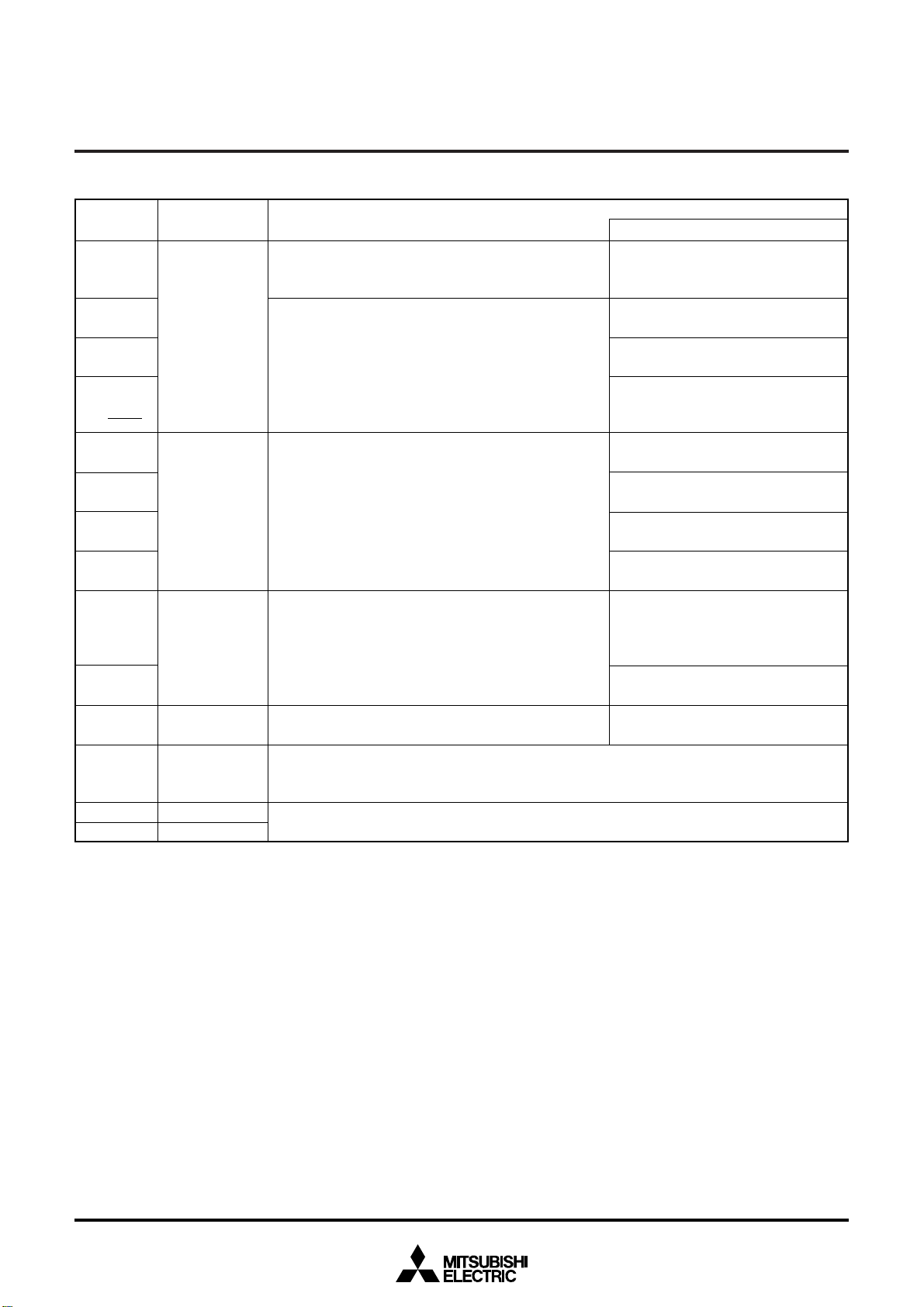

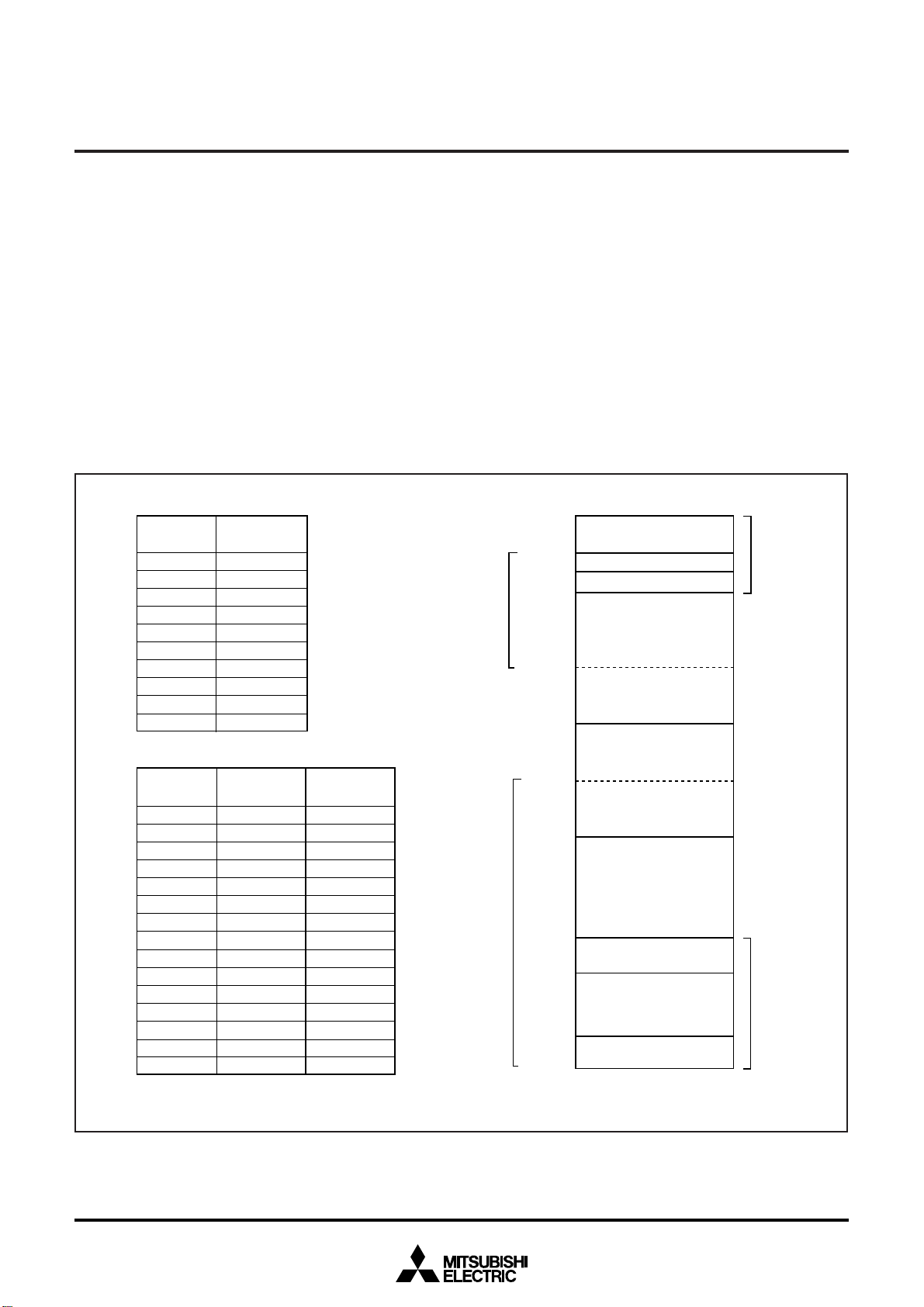

PIN CONFIGURATION (TOP VIEW)

SEG11

SEG14

SEG12

SEG10

SEG13

80

77

79

76

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

VCC

VREF

AVSS

COM3

COM2

COM1

COM0

VL3

VL2

C2

78

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

00

1

2

4

5

3

1

C1

VL1

P65/AN5

P66/AN6

P67/AN7

P34/SEG22

P32/SEG20

P30/SEG18

SEG16

SEG17

SEG15

73

75

72

74

P35/SEG23

P33/SEG21

P31/SEG19

70

71

P36/SEG24

68

67

69

66

P03/SEG29

P01/SEG27

P37/SEG25

P02/SEG28

P00/SEG26

63

65

62

64

61

M38277M8MXXXFP

9

8

6

7

P64/AN4

P61/SOUT2/AN1

P62/SCLK21/AN2

P63/SCLK22/AN3

14

12

11

10

P57/DA2

P60/SIN2/AN0

15

13

P56/DA1

P53/RTP1

P54/CNTR0

P55/CNTR1

20

17

19

16

18

P52/RTP0

P46/SCLK1

P47/SRDY1

P50/PWM0

P51/PWM1

P07/SEG33

P05/SEG31

P06/SEG32

P04/SEG30

58

60

57

59

22

21

23

24

4/RXD

3/φ/TOUT

P45/TXD

P4

P42/INT2

P4

P14/SEG38

P12/SEG36

P10/SEG34

56

25

P41/INT1

P11/SEG35

55

26

P40/ADT

P15/SEG39

P13/SEG37

51

53

52

54

50

P16

49

P17

48

P20

47

P21

46

P22

P23

45

P24

44

P25

43

P26

42

P27

41

VSS

40

XOUT

39

XIN

38

XCOUT

37

XCIN

36

35

RESET

34

P70/INT0

33

P71

P72

32

P73

31

29

30

28

27

7

P76

P7

P74

P75

Package type : 100P6S-A (100-pin plastic-molded QFP)

Fig. 1 M38277M8MXXXFP pin configuration

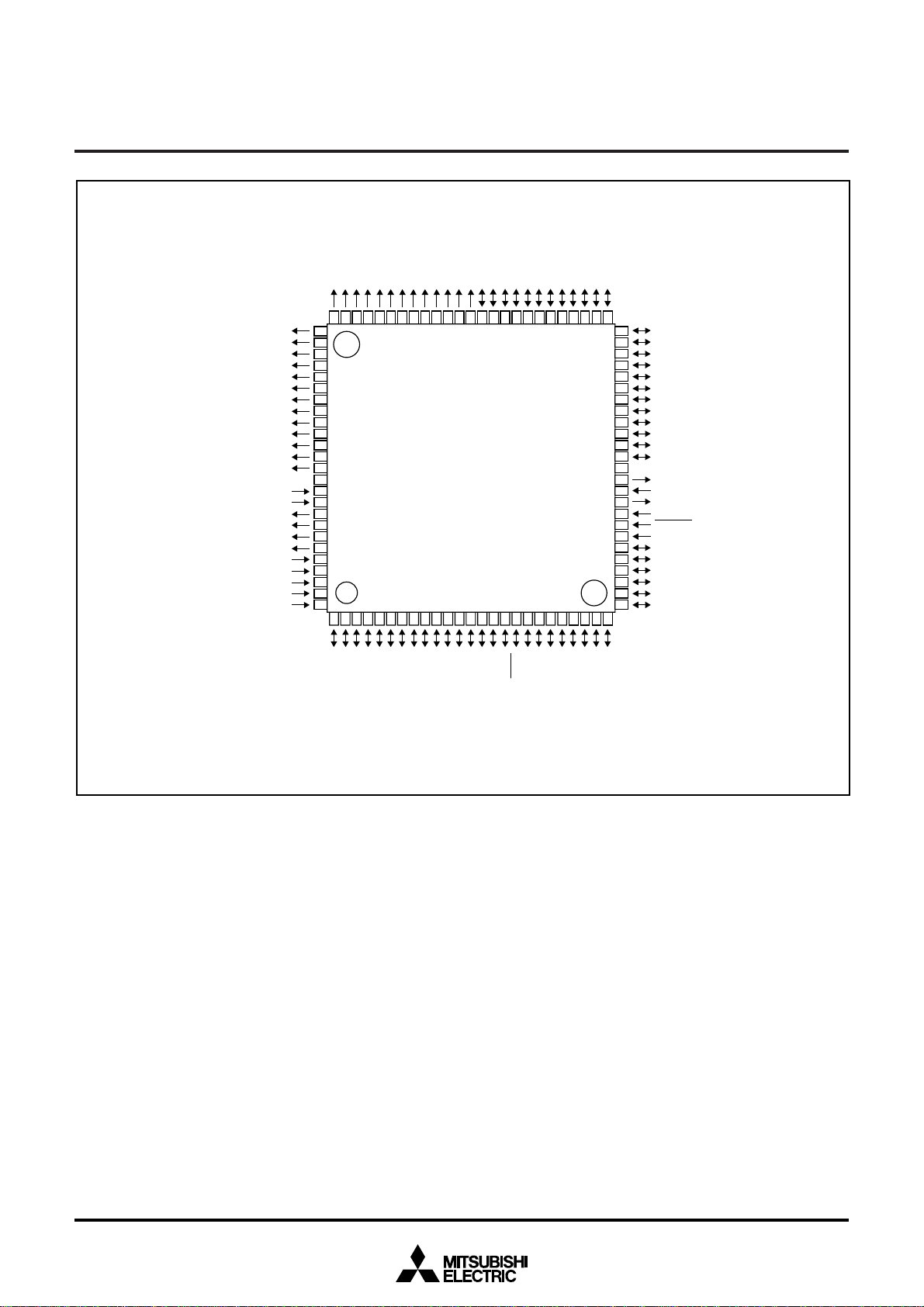

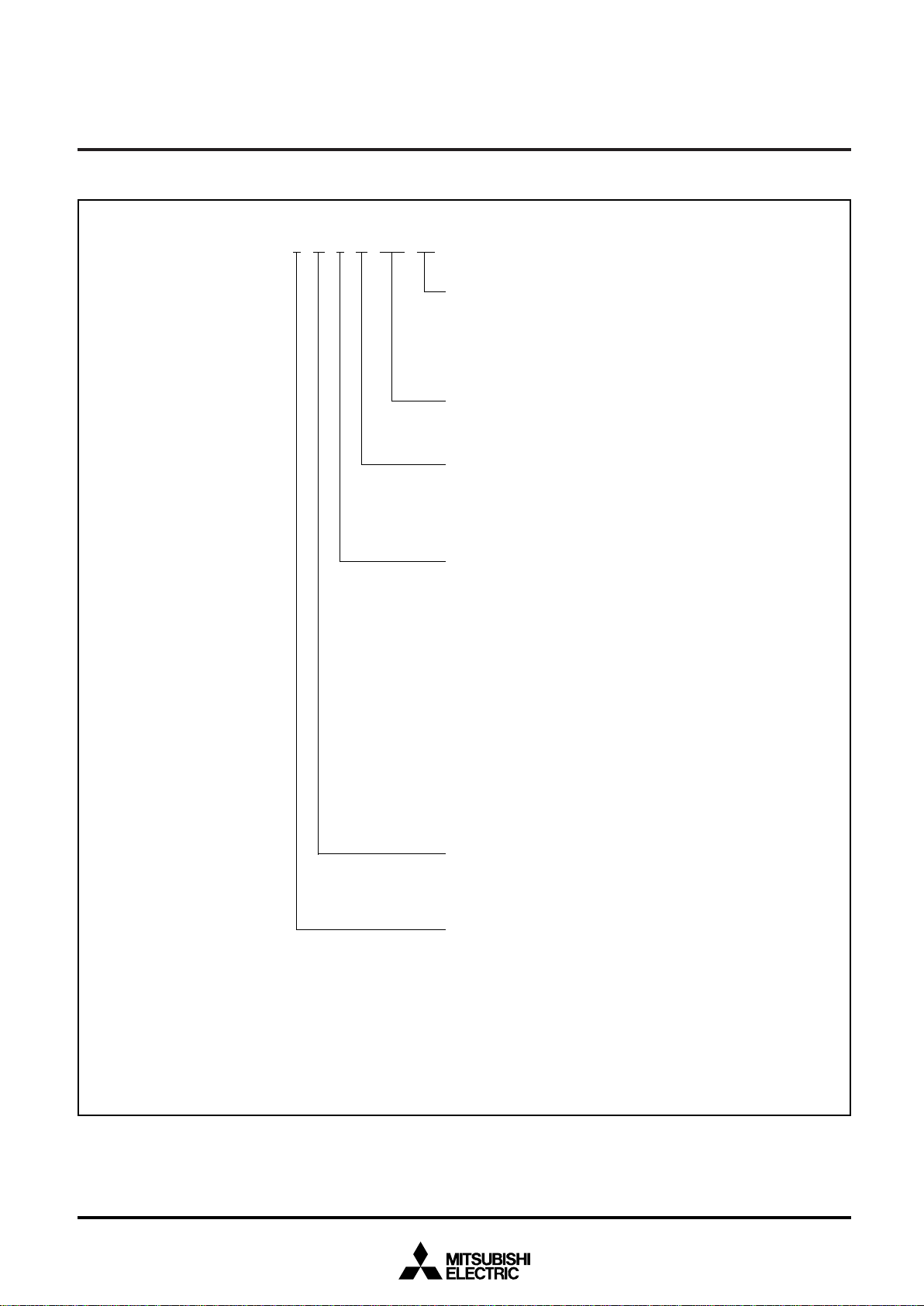

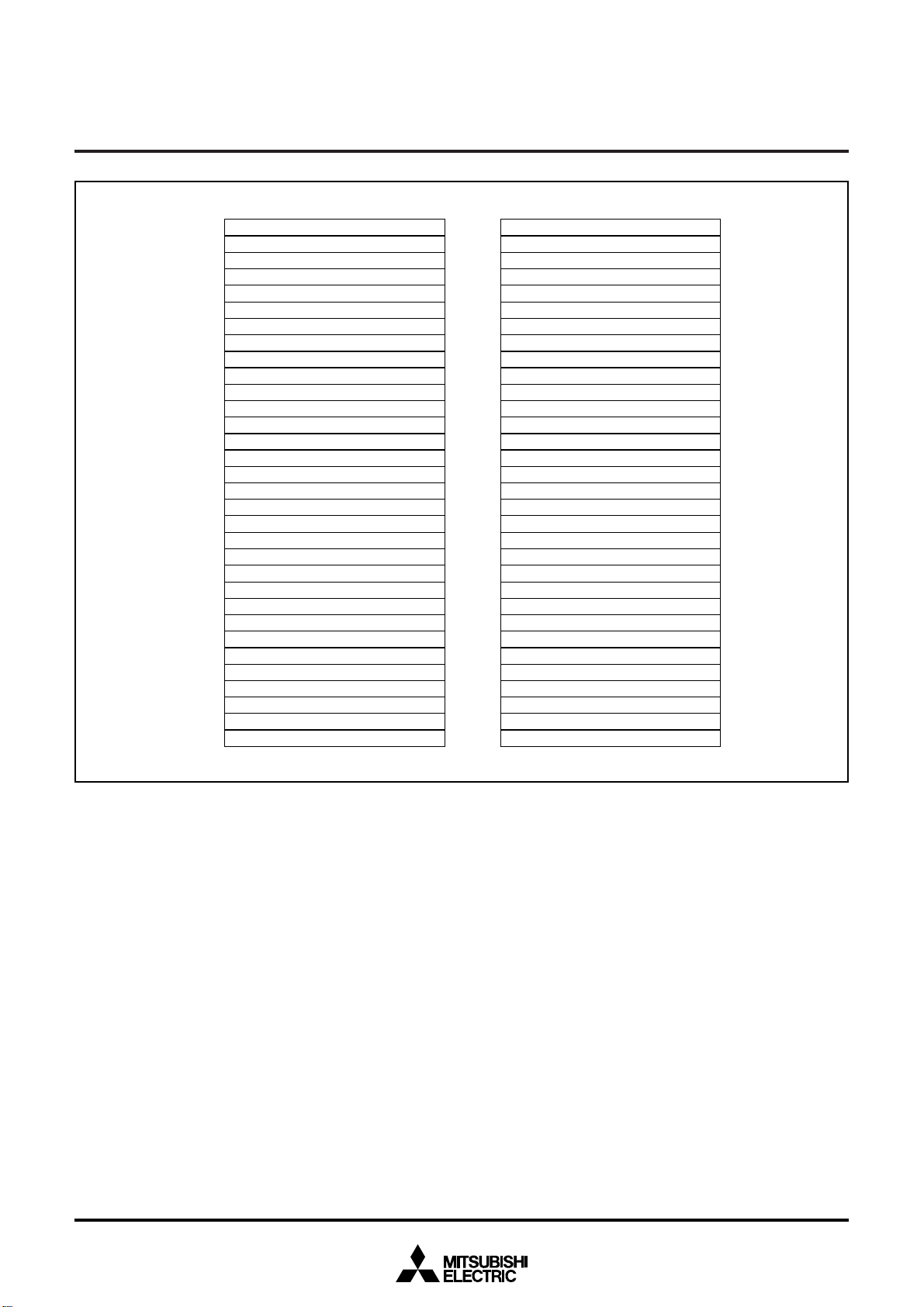

PIN CONFIGURATION (TOP VIEW)

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

VCC

VREF

AVSS

COM3

COM2

COM1

COM0

VL3

VL2

VL1

SEG13

SEG14

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

C2

99

C1

100 26

3

2

1

P66/AN6

P67/AN7

P31/SEG19

SEG15

71

72

P33/SEG21

P30/SEG18

SEG17

70

67

68

69

66

M38277M8MXXXGP

M38277M8MXXXHP

6

9

5

8

4

7

10

P64/AN4

P65/AN5

P63/SCLK22/AN3

P57/DA2

P60/SIN2/AN0

P61/SOUT2/AN1

P62/SCLK21/AN2

P32/SEG20

SEG16

P00/SEG26

P02/SEG28

P37/SEG25

P34/SEG22

P36/SEG24

P35/SEG23

64

65

63

13

12

11

P56/DA1

P53/RTP1

P54/CNTR0

P55/CNTR1

P04/SEG30

P01/SEG27

P03/SEG29

61

58

62

59

60

17

16

18

15

14

P52/RTP0

P46/SCLK1

P47/SRDY1

P51/PWM1

P50/PWM0

P05/SEG31

57

19

XD

T

P45/

P12/SEG36

P07/SEG33

P11/SEG35

P06/SEG32

56

21

20

P44/RXD

55

3/φ/TOUT

P4

P13/SEG37

P10/SEG34

52

53

54

51

50

P14/SEG38

49

P15/SEG39

48

P16

47

P17

46

P20

45

P21

44

P22

43

P23

42

P24

41

P25

40

P26

39

P27

38

VSS

37

XOUT

36

XIN

35

COUT

X

34

XCIN

33

RESET

32

P70/INT0

31

P71

30

P72

29

P73

28

P74

27

P75

24

23

22

1/INT1

P40/ADT

P4

P42/INT2

P76

25

7

P7

Package type : GP........ 100P6Q-A (100-pin plastic-molded LQFP)

Package type : HP........ 100PFB-A (100-pin plastic-molded TQFP)

Fig. 2 M38277M8MXXXGP/M38277M8MXXXHP pin configuration

2

Key input/key-on wake-up interrupt

INT1,INT2

CNTR0,CNTR

1

DA

1

DA

2

T

OUT

INT

0

ADT

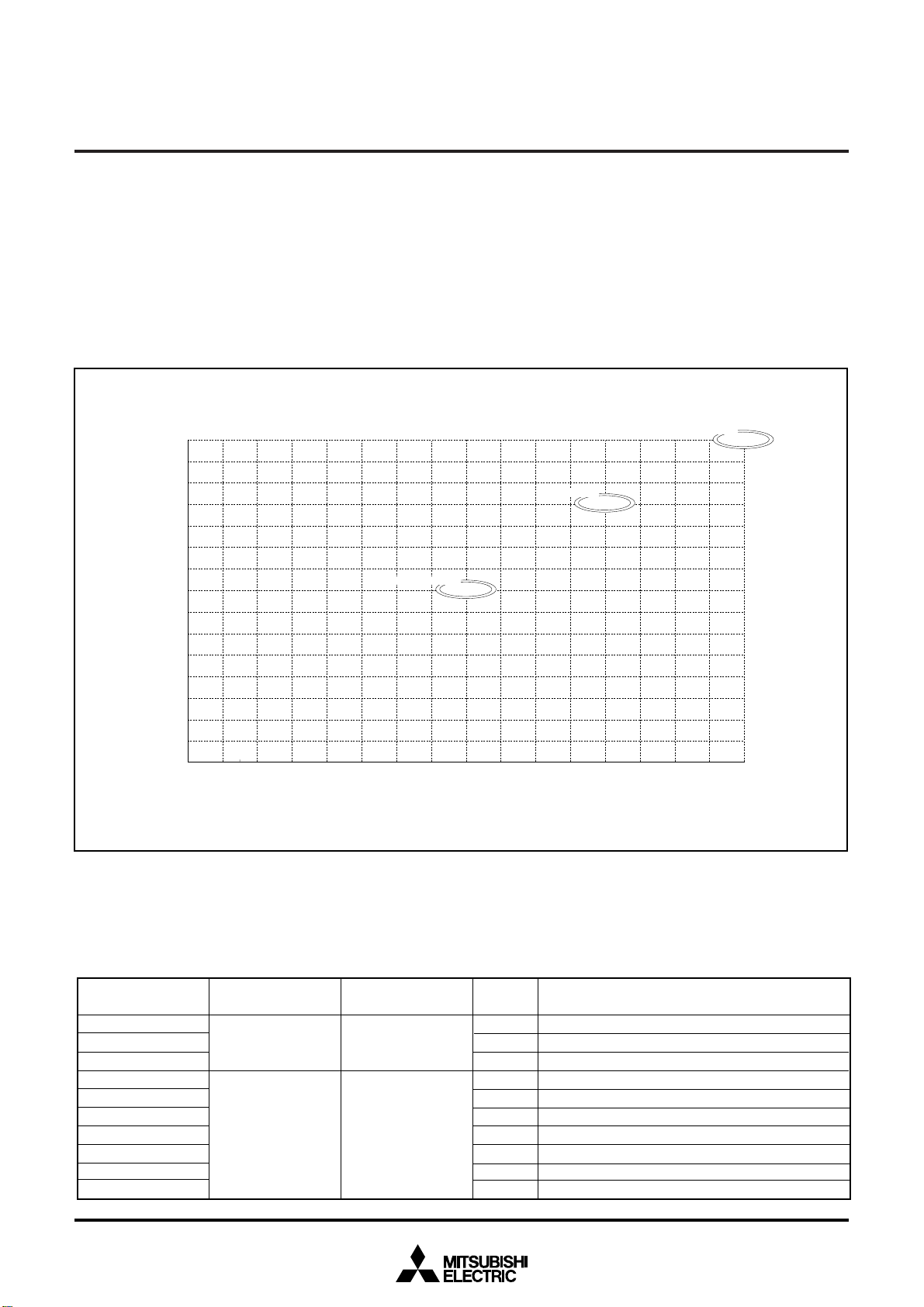

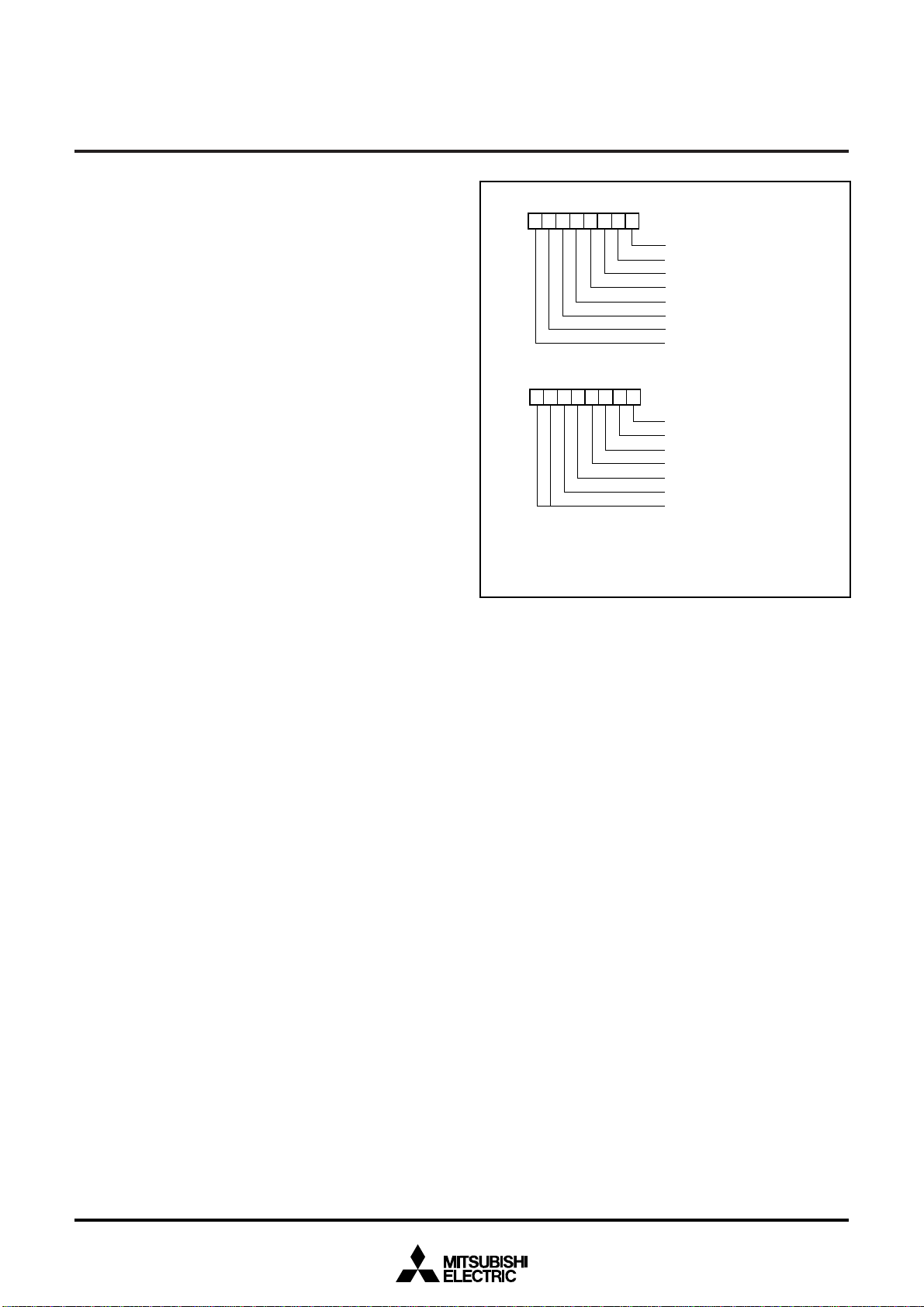

Data bus

C P U

A

X

Y

S

PC

H

PCL

PS

RESET

V

CC

VSS

Reset input ( 5 V ) ( 0 V )

R O M

R A M

LCD display

RAM

(20 bytes)

I/O port P5

P4(8)

I/O port P4

I/O port P2

P2(8)

I/O port P0

P0(8)

I/O port P1

P1(8)

P6(8)

I/O port P7

P7(8)

Output port P3

P3(8)

I/O port P6

P5(8)

Sub-clock input

Sub-clock output

XCIN XCOUT

Clock generating circuit

X

IN OUT

X

Main clock input

Main clock output

COUT

X

X

CIN

Sub-clock output

Sub-clock input

SI/O1 (8)

VREF

AVSS

A-D converter

(10)

Timer X(16)

Timer Y(16)

Timer 1(8) Timer 2(8)

Timer 3(8)

LCD drive

control circuit

VL1C1C2

VL2

VL3

COM0

COM1

COM2

COM3

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

φ

X

CIN

COUT

X

SI/O2(8)

Watchdog timer

Reset

PWM(8)

φ

Real time port function

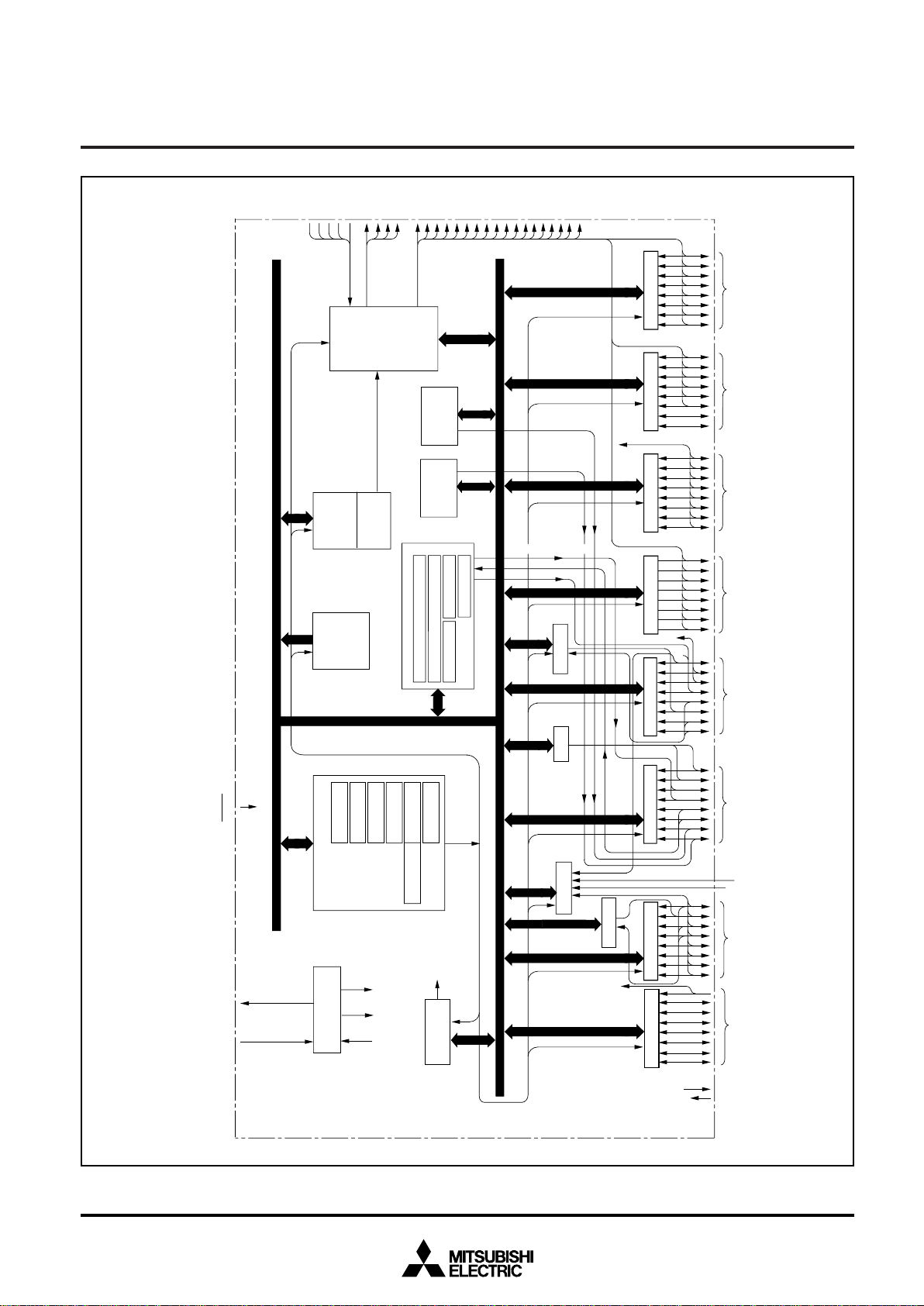

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

D-A2 D-A1

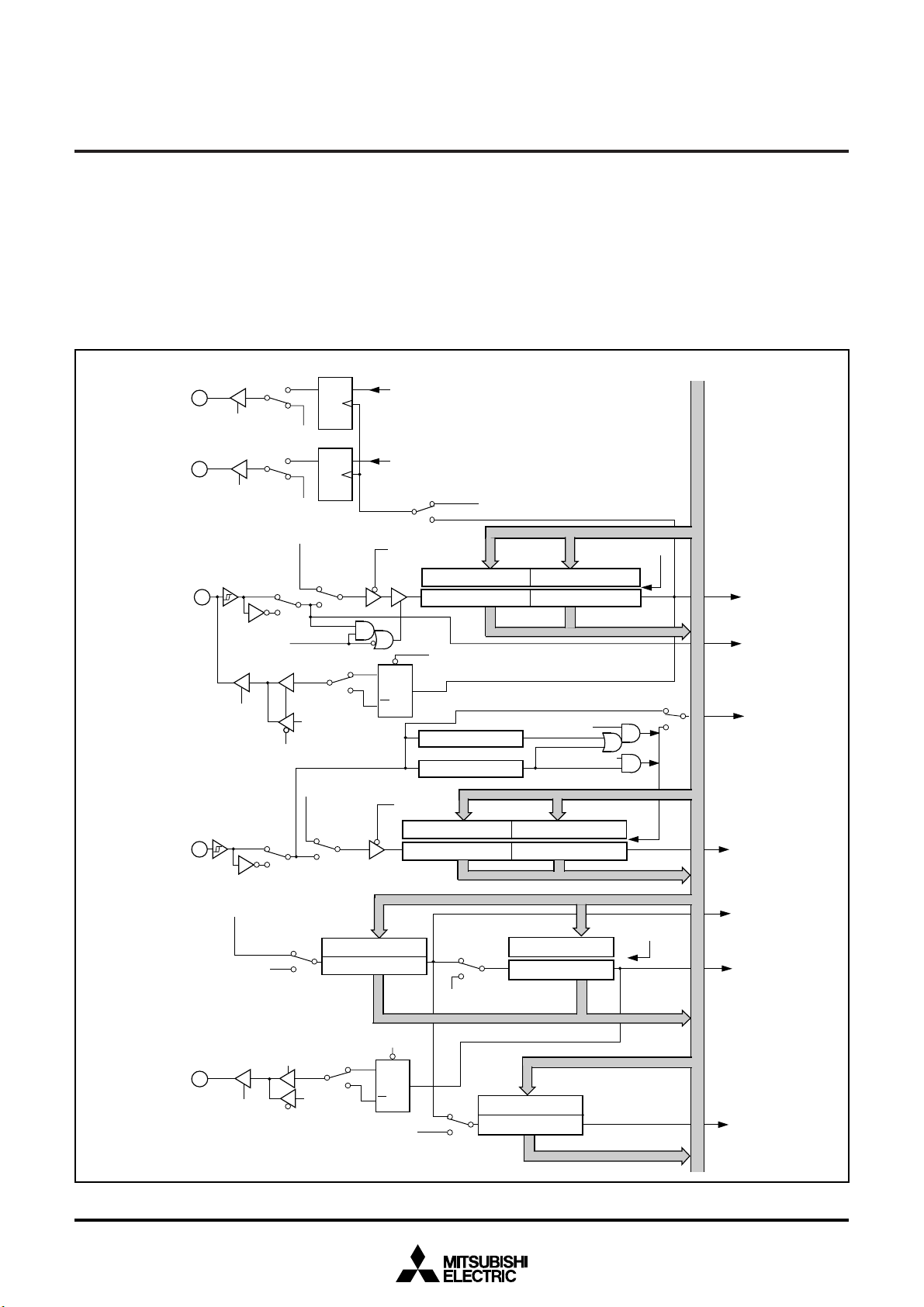

FUNCTIONAL BLOCK DIAGRAM

Fig. 3 Functional block diagram

3

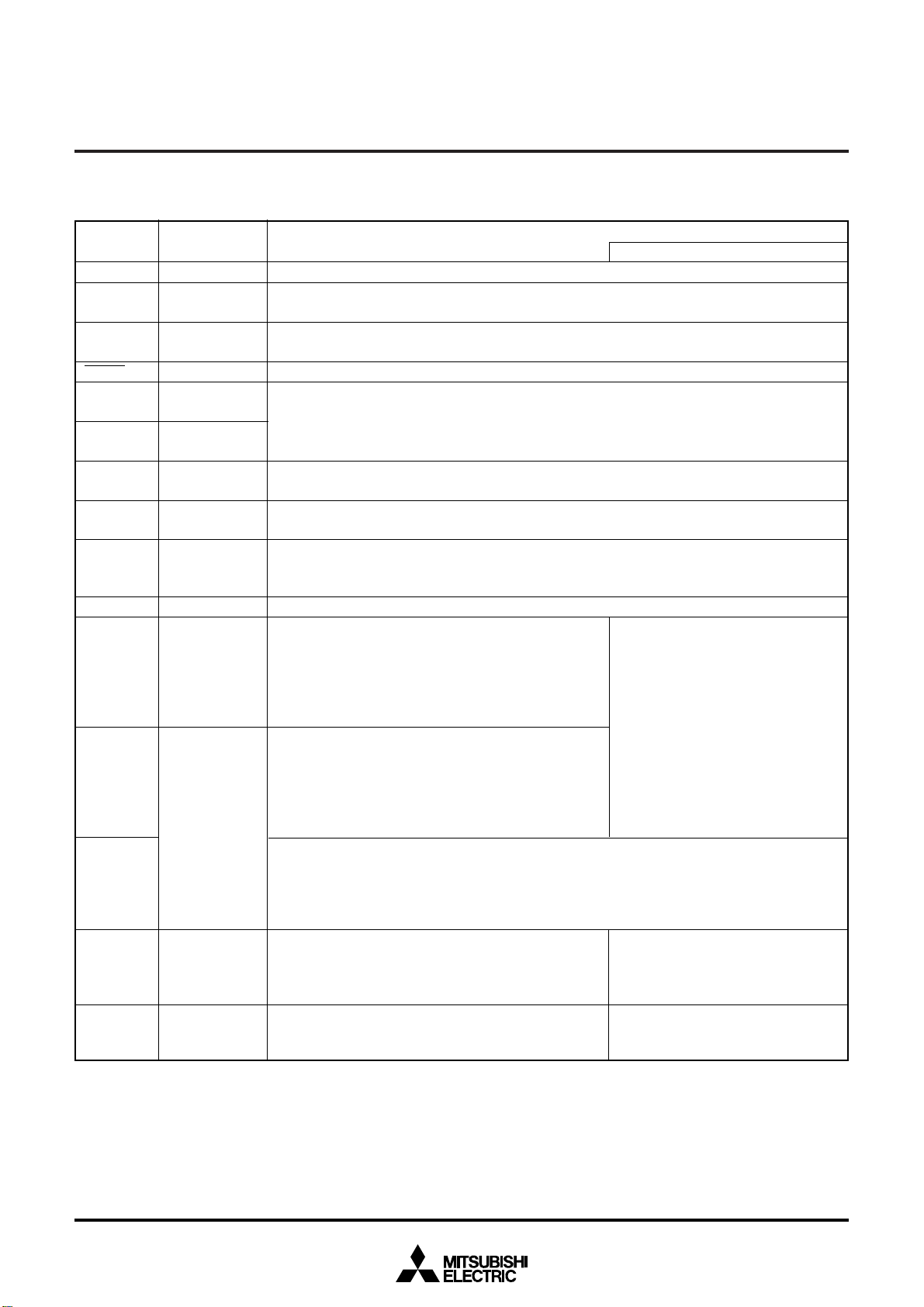

PIN DESCRIPTION

Table 1 Pin description (1)

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

V

CC, VSS

V

REF

AVSS

RESET

X

IN

XOUT

VL1–VL3

C1, C2

COM0–COM

SEG0–SEG

P00/SEG26–

P07/SEG33

P10/SEG34–

P15/SEG39

P16, P17

P20 – P27

P30/SEG18 –

P37/SEG

25

FunctionPin Name

Power source •Apply voltage of 2.2 V to 5.5 V to VCC, and 0 V to VSS.

Analog refer-

•Reference voltage input pin for A-D converter and D-A converter.

ence voltage

Analog power

source

Reset input

Clock input

•GND input pin for A-D converter and D-A converter.

•Connect to V

SS.

•Reset input pin for active “L”.

•Input and output pins for the main clock generating circuit.

•Connect a ceramic resonator or a quar tz-crystal oscillator between the X

Clock output

LCD power

source

Charge-pump

the oscillation frequency.

•If an external clock is used, connect the clock source to the XIN pin and leave the XOUT pin open.

•Input 0 ≤ V

L1 ≤ VL2 ≤ VL3 ≤ VCC voltage.

•Input 0 – VL3 voltage to LCD.

•External capacitor pins for a voltage multiplier (3 times) of LCD contorl.

capacitor pin

Common output

3

17

Segment output

I/O port P0

•LCD common output pins.

2 and COM3 are not used at 1/2 duty ratio.

•COM

•COM

3 is not used at 1/3 duty ratio.

•LCD segment output pins.

•8-bit output port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•Pull-up control is enabled.

•I/O direction register allows each port to be individually

programmed as either input or output.

I/O port P1

•6-bit output port with same function as por t P0.

•CMOS compatible input level.

•CMOS 3-state output structure.

•Pull-up control is enabled.

•I/O direction register allows each 6-bit pin to be programmed as either input or output.

•2-bit I/O port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•I/O direction register allows each pin to be individually programmed as either input or output.

•Pull-up control is enabled.

I/O port P2

•8-bit I/O port with same function as port P0.

•CMOS compatible input level.

•CMOS 3-state output structure.

•Pull-up control is enabled.

Output port P3

•8-bit output por t with same function as port P0.

•CMOS 3-state output structure.

•Port output control is enabled.

Function except a port function

IN and XOUT pins to set

•LCD segment output pins

•Key input (key-on wake-up) interrupt

input pins

•LCD segment output pins

4

Table 2 Pin description (2)

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

P40/ADT

P41/INT1,

P42/INT2

P43/φ/TOUT

P44/RXD,

P45/TXD,

P46/SCLK1,

P47/SRDY1

P50/PWM0,

P51/PWM1

P52/RTP0,

P53/RTP1

P54/CNTR0,

P55/CNTR1

P56/DA1,

P57/DA2

P60/AN0/S

IN2,

P61/AN1/S

OUT2,

P62/AN2/S

CLK21,

P63/AN3/S

CLK22

P64/AN4–

P67/AN7

P70/INT0

P71–P77

XCOUT

XCIN

Name

I/O port P4

I/O port P5

I/O port P6

Input port P7

I/O port P7

Sub-clock output

Sub-clock input

FunctionPin

•1-bit I/O port with same function as P16 and P17.

•CMOS compatible input level.

•CMOS 3-state output structure.

•7-bit I/O port with same function as P16 and P17.

•CMOS compatible input level.

•CMOS 3-state output structure.

•Pull-up control is enabled.

•8-bit I/O port with same function as P1

6 and P17.

•CMOS compatible input level.

•CMOS 3-state output structure.

•Pull-up control is enabled.

•8-bit I/O port with same function as P1

6 and P17.

•CMOS compatible input level.

•CMOS 3-state output structure.

•Pull-up control is enabled.

•1-bit I/O port.

•CMOS compatible input level.

•7-bit I/O port with same function as P1

6 and P17.

•CMOS compatible input level.

•N-channel open-drain output structure.

•Sub-clock generating circuit I/O pins.

(Connect a resonator. External clock cannot be used.)

Function except a port function

•A-D trigger input pin

•Interrupt input pin

•Interrupt input pins

•φ clock output pin

•Timer 2 output pin

•Serial I/O1 I/O pins

•PWM function pins

•Real time port function pins

•Timer X, Y function pins

•D-A conversion output pins

•A-D conversion input pins

•Serial I/O2 I/O pins

•A-D conversion input pins

•Interrupt input pin

5

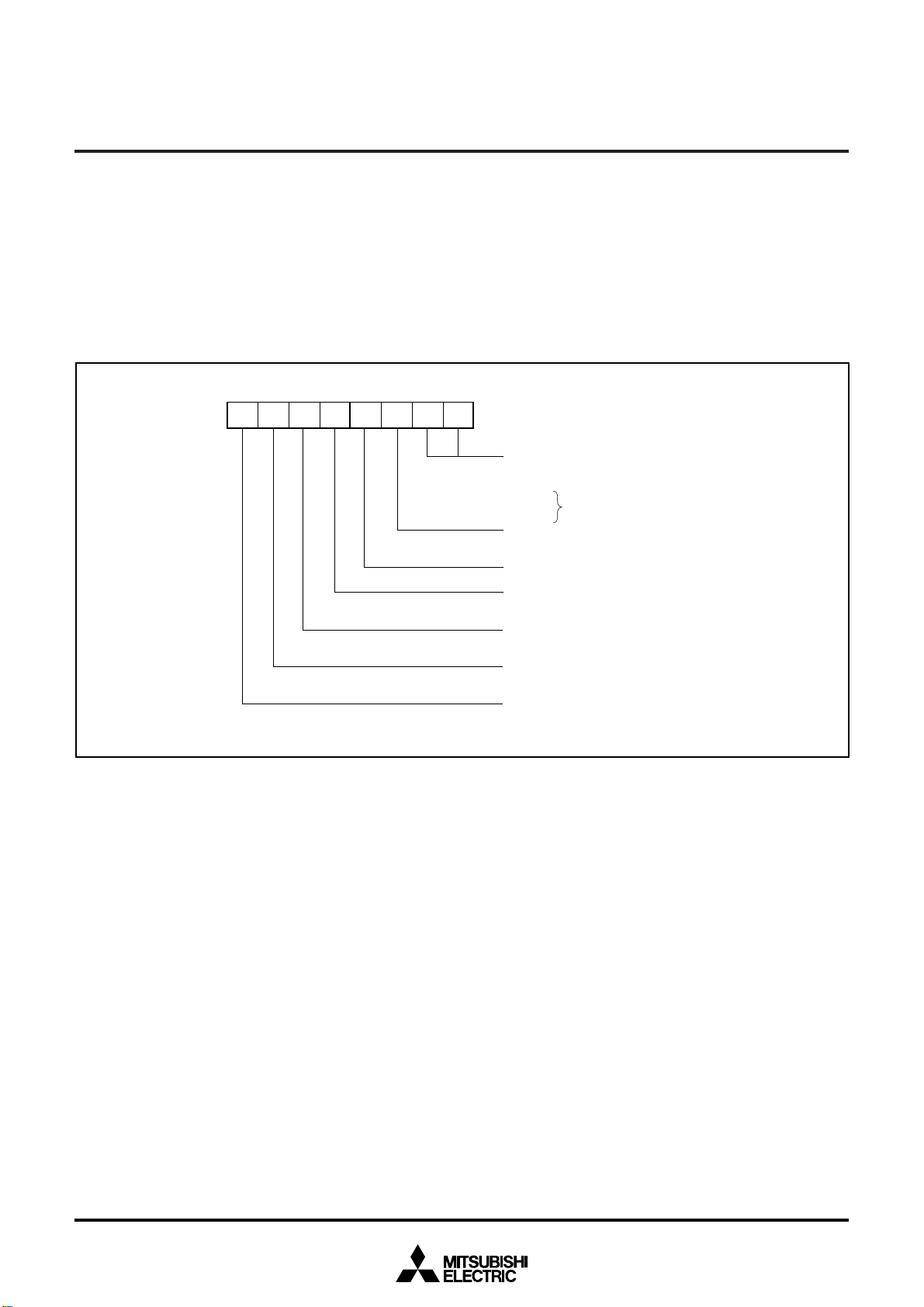

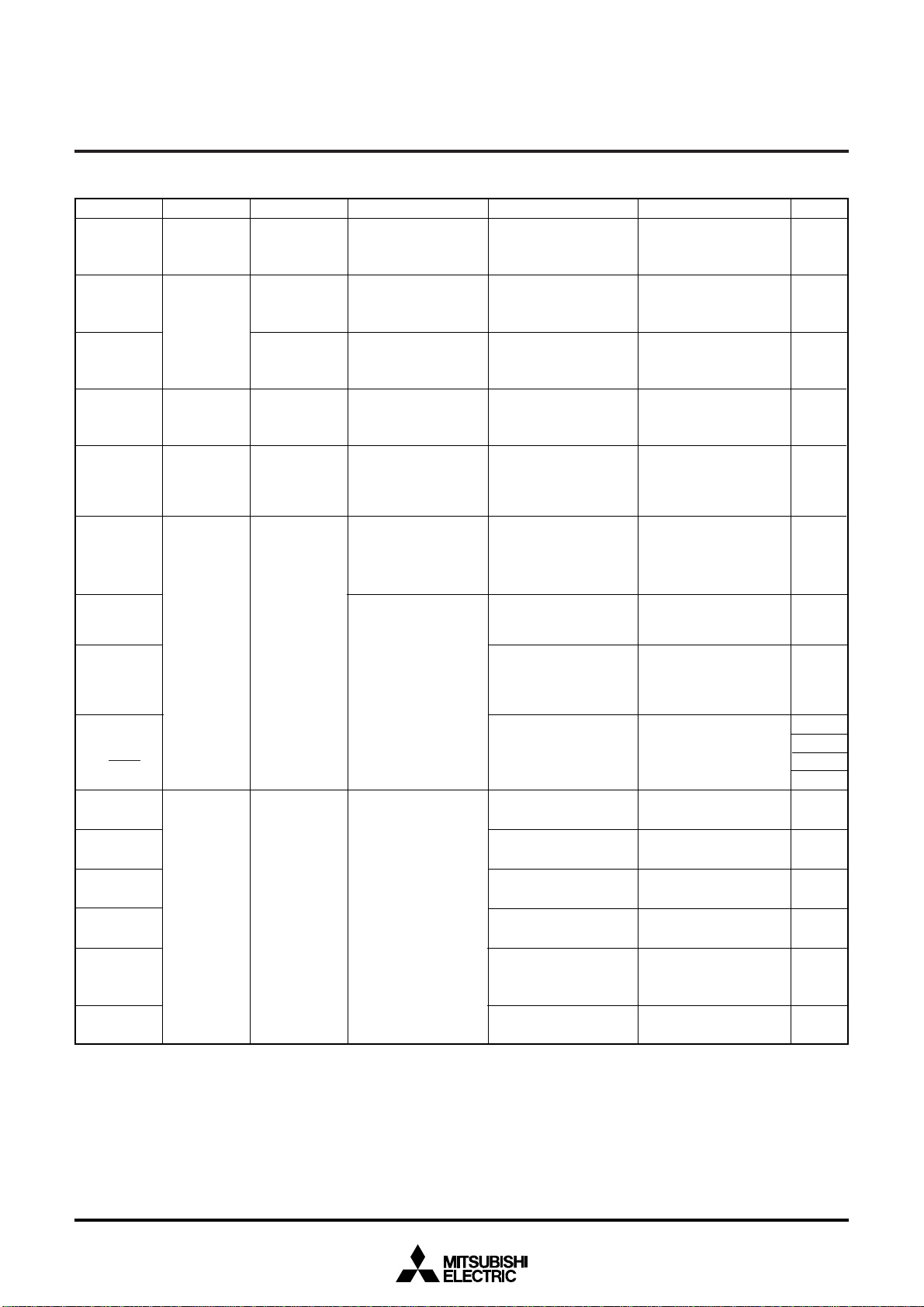

PART NUMBERING

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Product

M3827 7 M 8 M XXX HP

Package type

: 100P6S-A package

FP

: 100PFB-A package

HP

: 100P6Q-A package

GP

: 100D0 package

FS

ROM number

Omitted in some types.

Normally, using hyphen

When electrical characteristic, or division of quality

identification code using alphanumeric character.

– : Standard

M : Low power source version

ROM/PROM size

: 4096 bytes

1

2

: 8192 bytes

3

: 12288 bytes

: 16384 bytes

4

5

: 20480 bytes

6

: 24576 bytes

: 28672 bytes

7

8

: 32768 bytes

9

: 36864 bytes

: 40960 bytes

A

B

: 45056 bytes

C

: 49152 bytes

: 53248 bytes

D

E

: 57344 bytes

F

: 61440 bytes

The first 128 bytes and the last 2 bytes of ROM

are reserved areas ; they cannot be used.

Fig. 4 Part numbering

6

Memory type

: Mask ROM version

M

: EPROM or One Time PROM version

E

RAM size

0

: 192 bytes

1

: 256 bytes

2

: 384 bytes

3

: 512 bytes

4

: 640 bytes

5

: 768 bytes

6

: 896 bytes

7

: 1024 bytes

8

: 1536 bytes

9

: 2048 bytes

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

GROUP EXPANSION

Mitsubishi plans to expand the 3827 group as follows:

Memory Type

Support for Mask ROM, One Time PROM, and EPROM versions

Memory Size

ROM/PROM size ................................................. 4 K to 60 K bytes

RAM size ............................................................192 to 2048 bytes

Memory Expansion Plan

ROM size (bytes)

60K

56K

52K

48K

44K

40K

36K

32K

28K

24K

20K

16K

12K

8K

4K

Under development

Package

100PFB-A ................................0.4 mm-pitch plastic molded TQFP

100P6Q-A ................................0.5 mm-pitch plastic molded LQFP

100P6S-A ................................0.65 mm-pitch plastic molded QFP

100D0 ..................... Window type ceramic LCC (EPROM version)

M38277M8M

Planning

M38278MCM

Under development

M38279EF

256 384 512 640 768 896

192

Note: Products under development or planning: the development schedule and specifications

may be revised without notice.

Fig. 5 Memory expansion plan

Currently supported products are listed below.

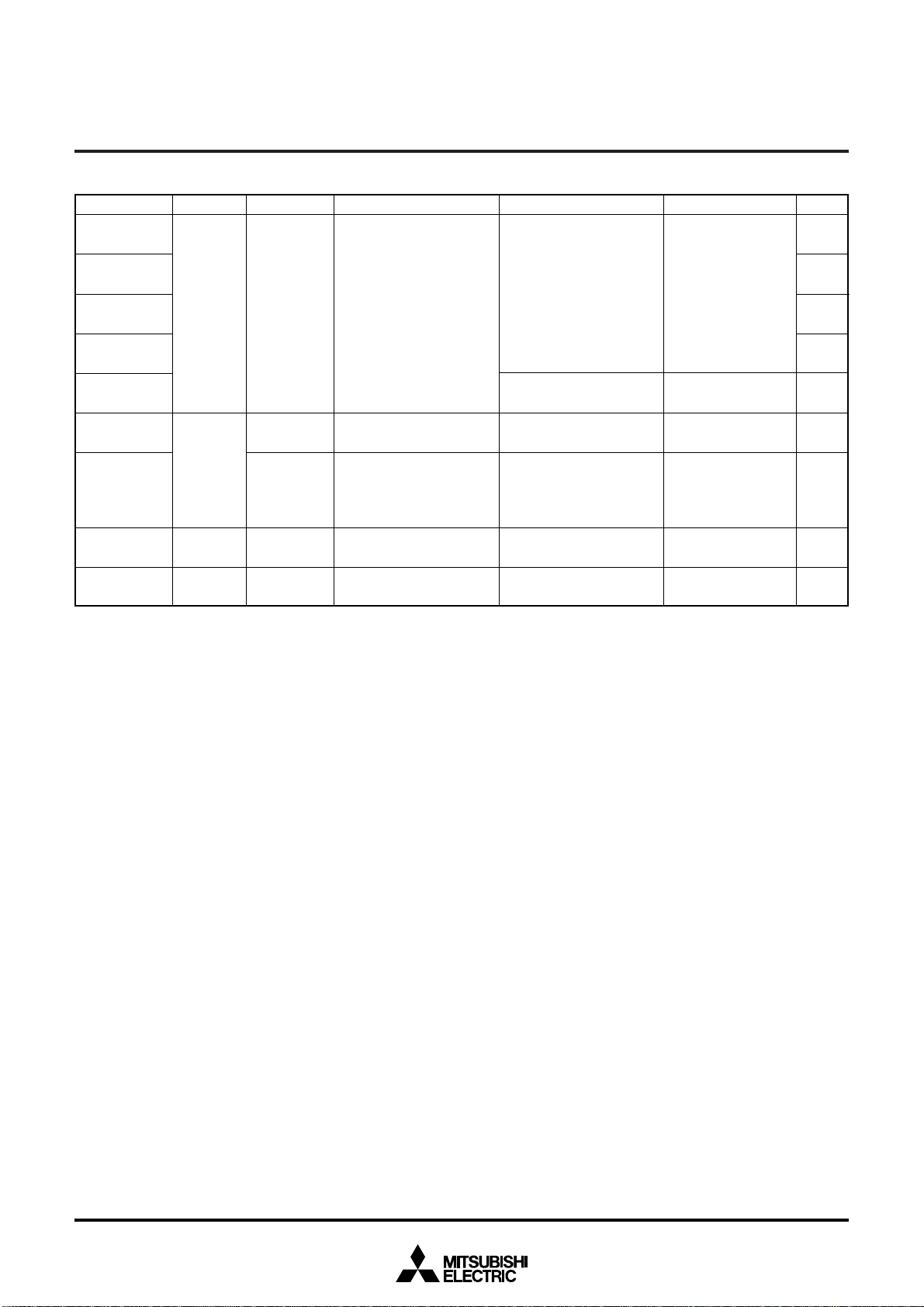

Table 3 List of supported products

Product

(P) ROM size (bytes)

ROM size for User in ( )

M38277M8MXXXFP

M38277M8MXXXHP

M38277M8MXXXGP

32768

(32638)

M38279EF-XXXFP

M38279EFFP

M38279EF-XXXHP

M38279EFHP

M38279EF-XXXGP

61440

(61310)

M38279EFGP

M38279EFFS

RAM size (bytes)

RAM size (bytes)

1024

2048

1024

Package

100P6S-A

100PFB-A

100P6Q-A

100P6S-A

100P6S-A

100PFB-A

100PFB-A

100P6Q-A

100P6Q-A

100D0

1408

1536 1664 1792

Remarks

Mask ROM version

Mask ROM version

Mask ROM version

One Time PROM version

One Time PROM version (blank)

One Time PROM version

One Time PROM version (blank)

One Time PROM version

One Time PROM version (blank)

EPROM version

204819201152 1280

As of May 1998

7

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

FUNCTIONAL DESCRIPTION

Central Processing Unit (CPU)

The 3827 group uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine

instructions or the 740 Family Software Manual for details on the

instruction set.

Machine-resident 740 family instructions are as follows:

The FST and SLW instruction cannot be used.

The STP, WIT, MUL, and DIV instruction can be used.

b7 b0

[CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit and

the internal system clock selection bit.

The CPU mode register is allocated at address 003B

CPU mode register

(CPUM (CM) : address 003B

Processor mode bits

b1 b0

0 0 : Single-chip mode

0 1 :

1 0 :

1 1 :

Stack page selection bit

0 : 0 page

1 : 1 page

Not used (returns “1” when read)

(Do not write “0” to this bit.)

Port X

0 : Stop oscillating

1 : X

Main clock ( X

0 : Oscillating

1 : Stopped

Main clock division ratio selection bit

0 : X

1 : X

Internal system clock selection bit

0 : X

1 : X

Not available

C

switch bit

CIN

, X

COUT

IN-XOUT

IN

/2 (high-speed mode)

IN

/8 (middle-speed mode)

IN-XOUT

selected (middle-/high-speed mode)

CIN-XCOUT

16

)

) stop bit

selected (low-speed mode)

16.

Fig. 6 Structure of CPU mode register

8

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MEMORY

Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

RAM

RAM is used for data storage and for stack area of subroutine

calls and interrupts.

ROM

The first 128 bytes and the last 2 bytes of ROM are reserved for

device testing and the rest is user area for storing programs.

Interrupt V ector Area

The interrupt vector area contains reset and interrupt vectors.

RAM area

RAM size

(bytes)

192

256

384

512

640

768

896

1024

1536

2048

ROM area

ROM size

(bytes)

4096

8192

12288

16384

20480

24576

28672

32768

36864

40960

45056

49152

53248

57344

61440

Address

XXXX

00FF

013F16

01BF16

023F16

02BF16

033F16

03BF16

043F16

063F16

083F16

Address

YYYY

F000

E00016

D00016

C00016

B00016

A00016

900016

800016

700016

600016

500016

400016

300016

200016

100016

16

16

16

16

Address

ZZZZ

F08016

E08016

D08016

C08016

B08016

A08016

908016

808016

708016

608016

508016

408016

308016

208016

108016

16

Zero Page

Access to this area with only 2 bytes is possible in the zero page

addressing mode.

Special Page

Access to this area with only 2 bytes is possible in the special

page addressing mode.

000016

SFR area

Zero page

Special page

RAM

ROM

004016

005416

010016

XXXX16

084016

YYYY16

ZZZZ16

FF0016

FFDC16

FFFE16

FFFF16

LCD display RAM area

Reserved area

Not used

Reserved ROM area

(128 bytes)

Interrupt vector area

Reserved ROM area

Fig. 7 Memory map diagram

9

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Port P0 (P0)

000016

Port P0 direction register (P0D)

000116

Port P1 (P1)

000216

Port P1 output control register (P1D)

000316

Port P2 (P2)

000416

Port P2 direction register (P2D)

000516

Port P3 (P3)

000616

Port P3 output control register (P3C)

000716

Port P4 (P4)

000816

Port P4 direction register (P4D)

000916

Port P5 (P5)

000A16

Port P5 direction register (P5D)

000B16

Port P6 (P6)

000C16

Port P6 direction register (P6D)

000D16

Port P7 (P7)

000E16

Port P7 direction register (P7D)

000F16

001016

001116

001216

001316

001416

Key input control register (KIC)

001516

PULL register A (PULLA)

001616

PULL register B (PULLB)

001716

Transmit/Receive buffer register(TB/RB)

001816

Serial I/O1 status register (SIO1STS)

001916

Serial I/O1 control register (SIO1CON)

001A16

UART control register (UARTCON)

001B16

Baud rate generator (BRG)

001C16

Serial I/O2 control register (SIO2CON)

001D16

Reserved area

001E16

Serial I/O2 register (SIO2)

001F16

0020

16

Timer X (low) (TXL)

Timer X (high) (TXH)

002116

Timer Y (low) (TYL)

002216

Timer Y (high) (TYH)

002316

002416

Timer 1 (T1)

Timer 2 (T2)

002516

Timer 3 (T3)

002616

Timer X mode register (TXM)

002716

Timer Y mode register (TYM)

002816

Timer 123 mode register (T123M)

002916

OUT/φ output control register (CKCON)

T

002A16

PWM control register (PWMCON)

002B16

PWM prescaler (PREPWM)

002C16

PWM register (PWM)

002D16

002E16

002F16

003016

A-D control register (ADCON)

003116

A-D control register (low-order) (ADL)

003216

A-D control register (high-order) (ADH)

003316

D-A1 conversion register (DA1)

003416

D-A2 conversion register (DA2)

003516

D-A control register (DACON)

003616

Watchdog timer control register (WDTCON)

003716

Segment output enable register (SEG)

003816

LCD mode register (LM)

003916

Interrupt edge selection register (INTEDGE)

003A16

CPU mode register (CPUM)

003B16

Interrupt request register 1(IREQ1)

003C16

Interrupt request register 2(IREQ2)

003D16

Interrupt control register 1(ICON1)

003E16

Interrupt control register 2(ICON2)

003F16

Fig. 8 Memory map of special function register (SFR)

10

I/O PORTS

Direction Registers

The I/O ports have direction registers which determine the input/

output direction of each individual pin. (P0

0–P07 and P10–P15 use

bit 0 of port P0, P1 direction registers respectively.)

When “1” is written to that bit, that pin becomes an output pin.

When “0” is written to the bit corresponding to a pin, that pin becomes an input pin.

If data is read from a pin set to output, the value of the port output

latch is read, not the value of the pin itself. Pins set to input are

floating and the value of that pin can be read. If a pin set to input

is written to, only the port output latch is written to and the pin remains floating.

Port P3 Output Control Register

Bit 0 of the port P3 output control register (address 000716) enables control of the output of ports P3

0 to P37.

When the bit is set to “1”, the port output function is valid.

When resetting, bit 0 of the port P3 output control register is set to

“0” (the port output function is invalid.) and ports P3

0 to P37 are

pulled up.

Pull-up Control

By setting the PULL register A (address 001616) or the PULL register B (address 0017

program.

However, the contents of PULL register A and PULL register B do

not affect ports programmed as the output ports.

The PULL register A setting is invalid for pins set to segment output on the segment output enable register.

16), ports P0 to P6 can control pull-up with a

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

b7 b0

b7 b0

Note : The contents of PULL register A and PULL register B

do not affect ports programmed as the output port.

Fig. 9 Structure of PULL register A and PULL register B

PULL register A

(PULLA : address 0016

P00, P01 pull-up

P0

2, P03 pull-up

4–P07 pull-up

P0

P1

0–P13 pull-up

4, P15 pull-up

P1

P1

6, P17 pull-up

0–P23 pull-up

P2

P2

4–P27 pull-up

PULL register B

(PULLB : address 0017

P41–P43 pull-up

P4

4–P47 pull-up

0–P53 pull-up

P5

P5

4–P57 pull-up

0–P63 pull-up

P6

P6

4–P67 pull-up

Not used (return “0” when read)

16)

16)

0 : No pull-up

1 : Pull-up

11

Table 4 List of I/O port function (1)

Pin

P00/SEG26–

P07/SEG33

P10/SEG34–

P15/SEG39

P16 , P17

P20–P27

P30/SEG18–

P37/SEG25

P40/ADT

Port P0

Port P1

Port P2

Port P3

Port P4

Input/OutputName

Input/output,

byte unit

Input/output,

6-bit unit

Input/output,

individual bits

Input/output,

individual bits

Output

Input/output,

individual bits

I/O Format

CMOS compatible

input level

CMOS 3-state output

CMOS compatible

input level

CMOS 3-state output

CMOS compatible

input level

CMOS 3-state output

CMOS compatible

input level

CMOS 3-state output

CMOS 3-state output

CMOS compatible

input level

N-channel open-drain

output

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Non-Port Function

LCD segment output

LCD segment output

Key input (key-on

wake-up) interrupt

input

LCD segment output

A-D trigger input

External interrupt input

Related SFRs

PULL register A

Segment output enable

register

PULL register A

Segment output enable

register

PULL register A

PULL register A

Interrupt control register2

Key input control register

PULL register A

Segment output enable

register

P3 output enable register

A-D control register

Interrupt edge selection

register

Diagram No.

(1)

(2)

(1)

(2)

(4)

(4)

(3)

(13)

P4

1/INT1,

P42/INT2

P43/φ/TOUT

P44/RXD,

P45/TXD,

P46/SCLK1,

P47/SRDY1

P50/PWM0,

P51/PWM1

P52/RTP0,

P53/RTP1

P54/CNTR0

P55/CNTR1

P56/DA1

P57/DA2

Port P5

Input/output,

individual bits

CMOS compatible

input level

CMOS 3-state output

CMOS compatible

input level

CMOS 3-state output

External interrupt input

Timer output φ output

Serial I/O1 function I/O

PWM output

Real time port

function output

Timer X function I/O

Timer Y function input

DA1 output

A-D VREF input

DA2 output

PULL register B

Interrupt edge selection

register

PULL register B

Timer 123 mode register

TOUT/φ output control

register

PULL register B

Serial I/O1 control register

Serial I/O1 status register

UART control register

PULL register B

PWM control register

PULL register B

Timer X mode register

PULL register B

Timer X mode register

PULL register B

Timer Y mode register

PULL register B

D-A control register

A-D control register

PULL register B

D-A control register

(4)

(12)

(5)

(6)

(7)

(8)

(10)

(9)

(11)

(14)

(15)

(15)

12

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Table 5 List of I/O port function (2)

Pin Name I/O Format Non-Port Function Related SFRS

P60/SIN2/AN0

P61/SOUT2/

AN1

P62/SCLK21/

AN2

P63/SCLK22 /

AN3

P64/AN4–

P67/AN7

P70/INT0

P71–P77

Port P6

Port P7

Input/Output

Input/

output,

individnal

bits

Input

Input/

output,

individnal

bits

CMOS compatible input

level

CMOS 3-state output

CMOS compatible input

level

CMOS compatible input

level

N-channel open-drain

output

A-D conversion input

Serial I/O2 function I/O

A-D conversion input

External interrupt input

A-D control register

Serial I/O2 control

register

A-D control register

Interrupt edge

selection register

3827 Group

Diagram No.

(17)

(18)

(19)

(20)

(16)

(23)

(13)

COM0–COM3

SEG0–SEG17

Notes1: How to use double-function ports as function I/O ports, refer to the applicable sections.

2: Make sure that the input level at each pin is either 0 V or V

tential, a current will flow V

Common

Segment

Output

Output

CC to VSS through the input-stage gate.

LCD common output

LCD segment output

CC during execution of the STP instruction. When an input level is at an intermediate po-

LCD mode register

(21)

(22)

13

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

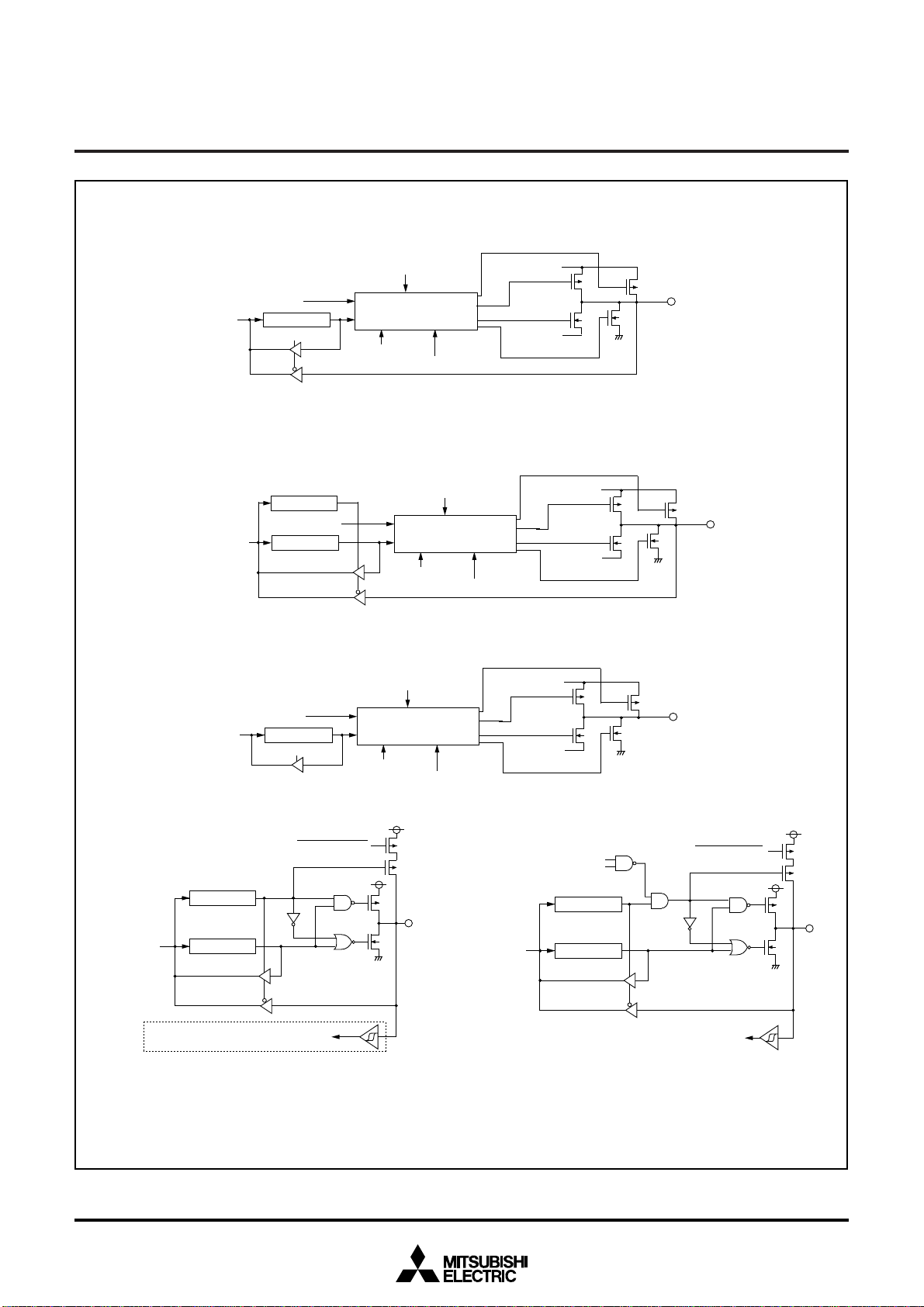

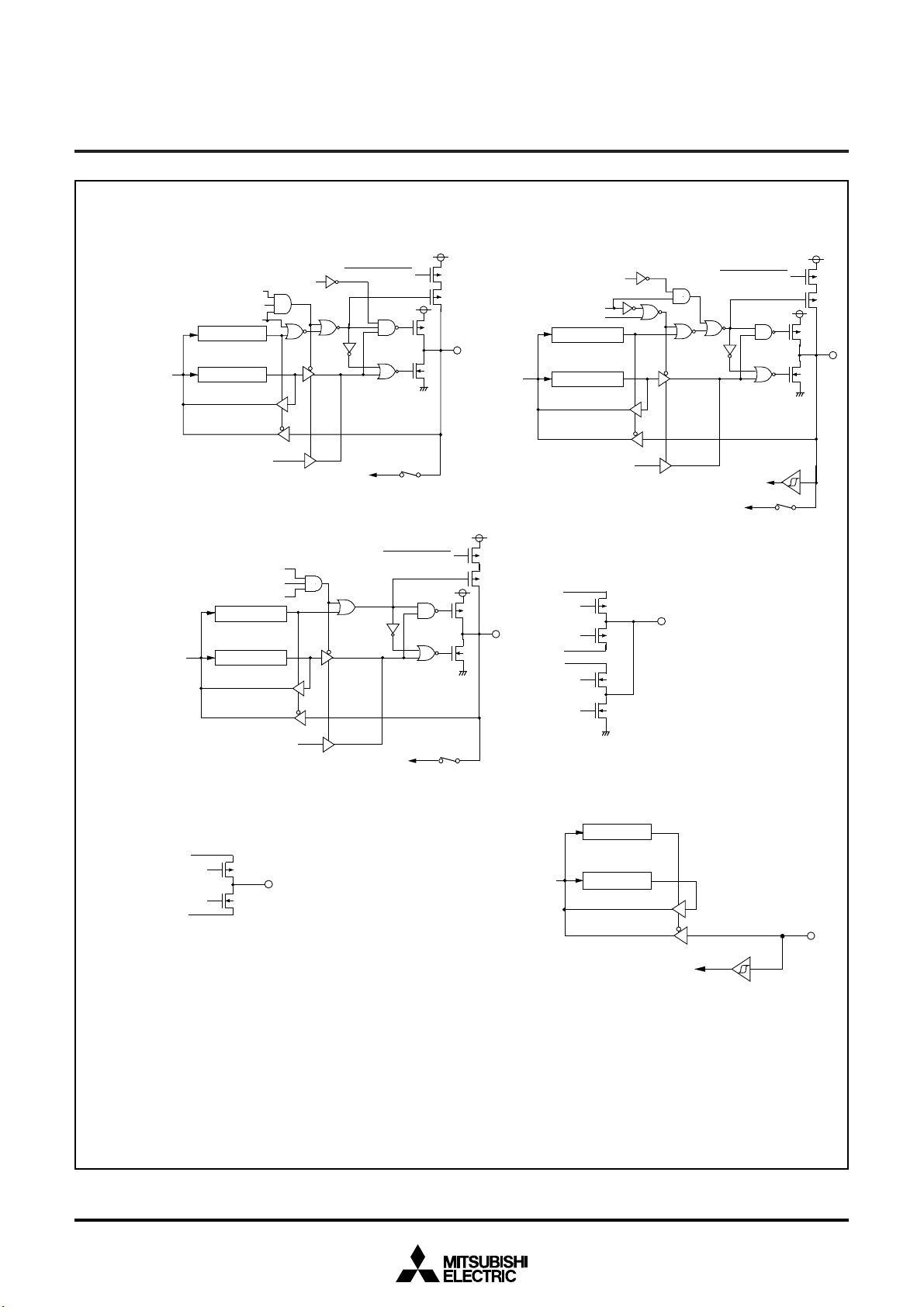

(1) Ports P01–P07, P11–P15

Segment data

Data bus

Port latch

Port direction register

(2) Ports P00, P10

Direction register

Segment data

Data bus

Port latch

(3) Port P3

Segment data

Data bus

Port latch

LCD drive timing

Interface logic level

shift circuit

Port/Segment

Port direction register

LCD drive timing

Port/Segment

LCD drive timing

Interface logic level

shift circuit

Port/Segment

Segment/Port

Segment

Interface logic level

shift circuit

Port direction register

Segment/Port

Segment

Output control

Pull-up

VL2/VL3/VCC

V

L1/VSS

Port

Pull-up

Segment/Port

Segment

Pull-up

VL2/VL3/VCC

V

L1/VSS

Port

VL2/VL3/VCC

L1/VSS

V

Port

(4) Ports P16, P17, P2, P41, P42

Direction register

Data bus

Fig. 10 Port block diagram (1)

14

Port latch

Key input interrupt input

1, INT2 interrupt input

INT

Except P1

Pull-up control

6, P17

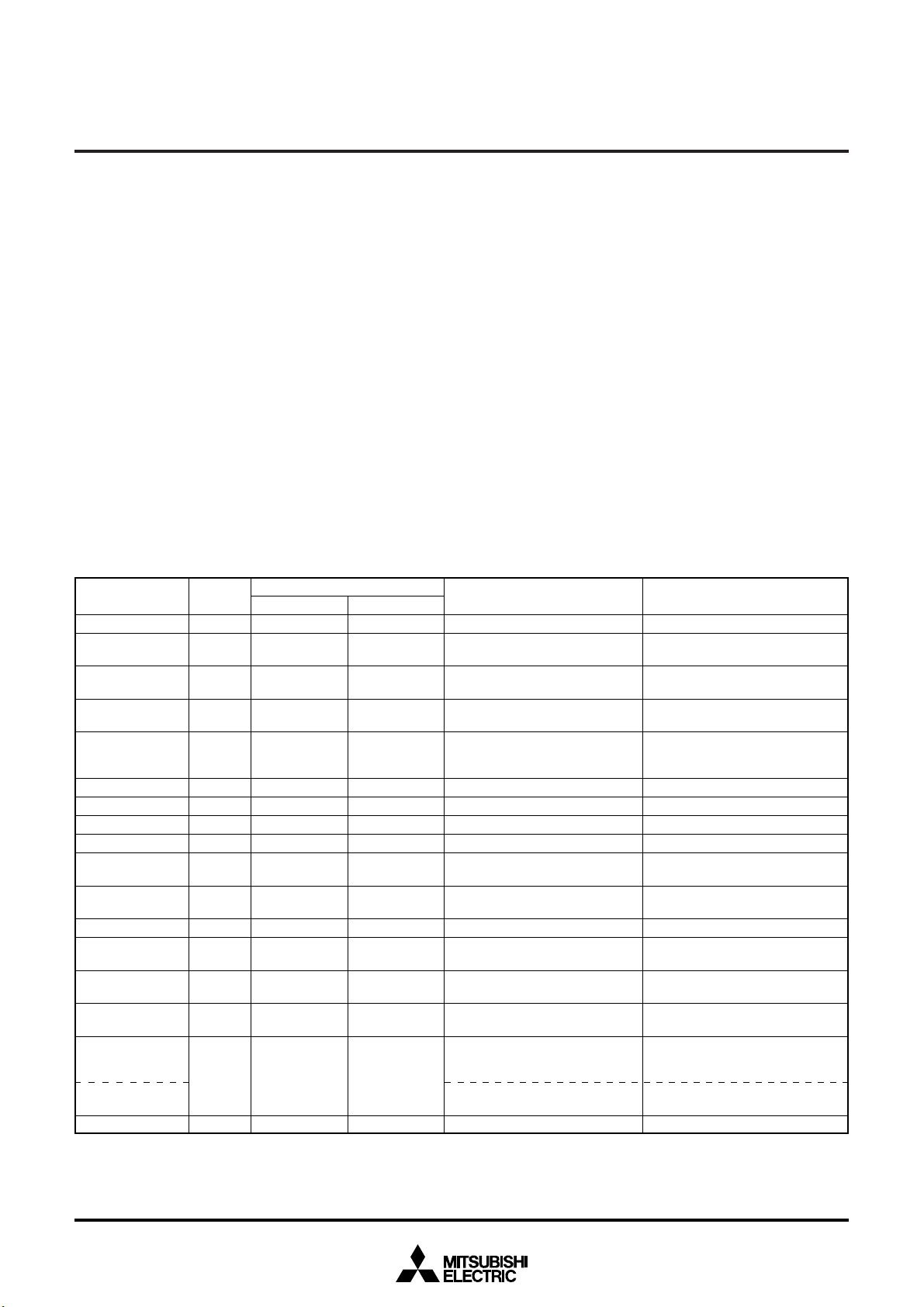

(5) Port P44

Serial I/O1 enable bit

Reception enable bit

Data bus

Pull-up control

Direction register

Port latch

Serial I/O1 input

(6) Port P45 (7) Port P46

Serial I/O1 clock

selection bit

Serial I/O1 enable bit

Serial I/O1 enable bit

P45/TxD P-channel output disable bit

Serial I/O1 enable bit

Transmission enable bit

Direction register

Pull-up control

Serial I/O1 mode selection bit

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Pull-up control

Direction register

Data bus

Port latch

Serial I/O1 output

(8) Port P47

Serial I/O1 mode selection bit

Serial I/O1 enable bit

S

RDY1 output enable bit

Direction register

Data bus Port latch

Serial I/O1 ready output

(10) Ports P50,P51

Direction register

Data bus

Port latch

Pull-up control

Pull-up control

Data bus

Serial I/O1 clock outupt

Port latch

(9) Ports P52, P53

Direction register

Data bus

Real time control bit

Real time port data

(11) Port P54

Data bus

Serial I/O1 clock input

Pull-up control

Port latch

Pull-up control

Direction register

Port latch

PWM function enable bit

PWM output

Fig. 11 Port block diagram (2)

Pulse output mode

Timer output

CNTR0 interrupt input

15

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

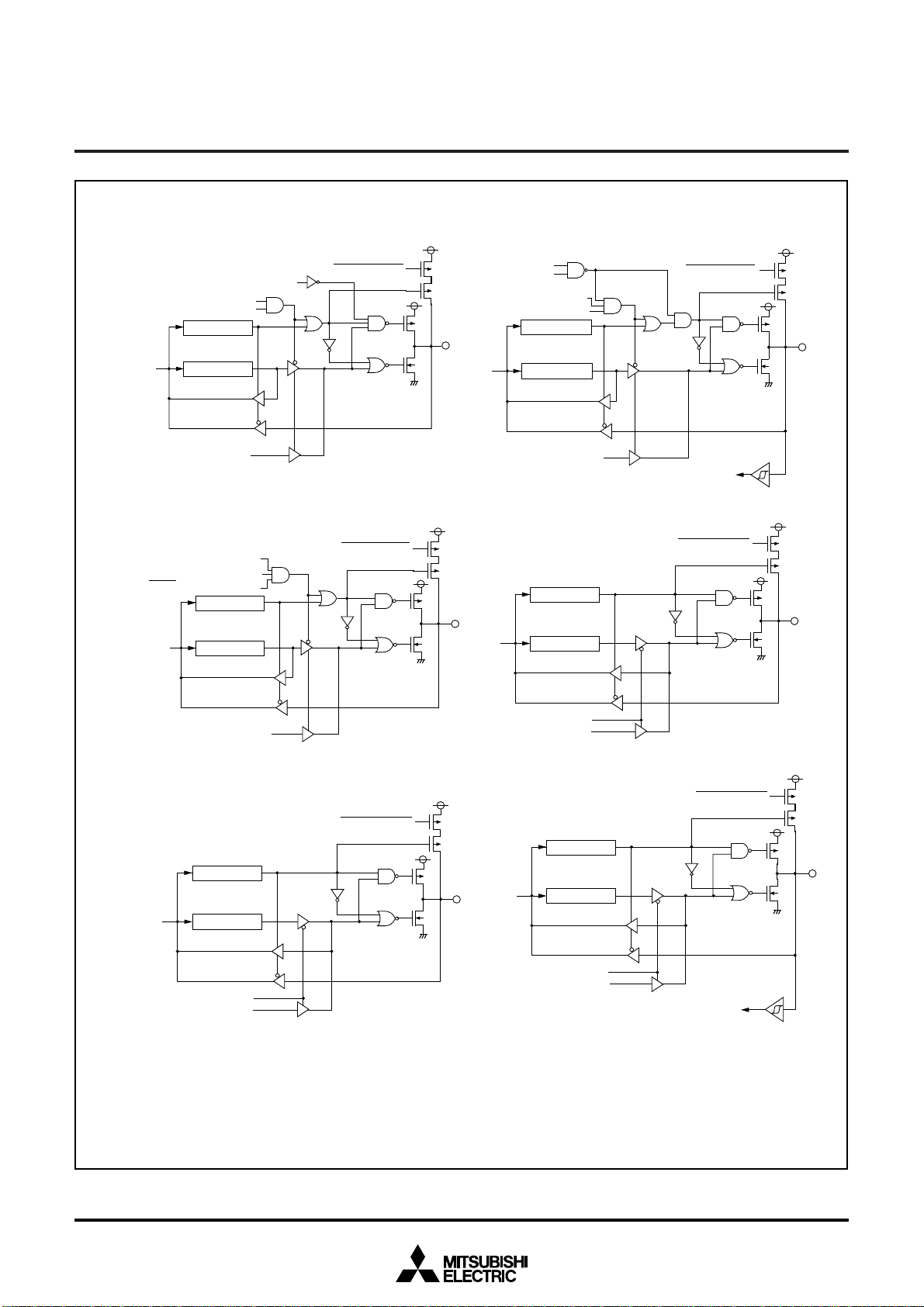

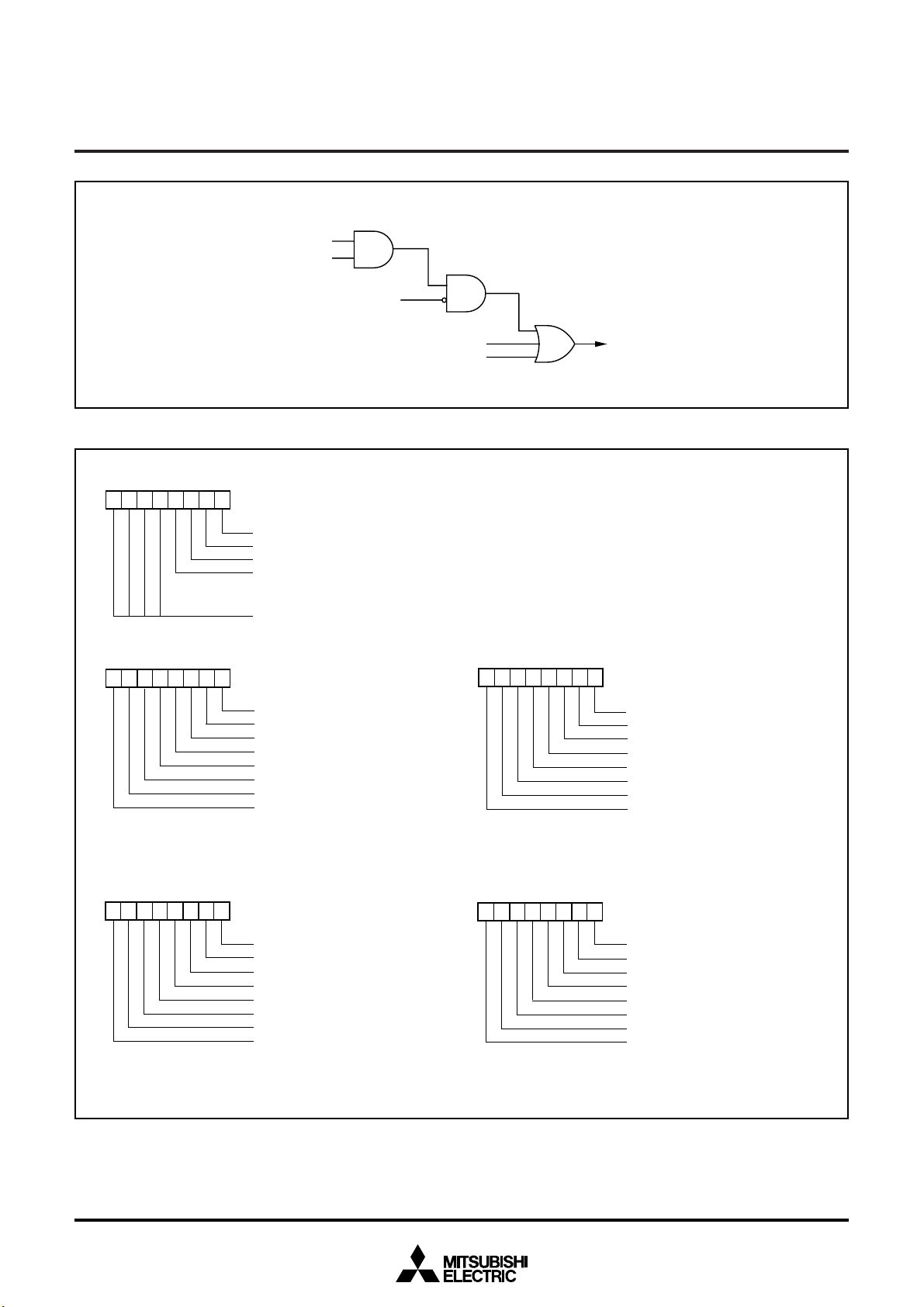

(12) Port P43

TOUT/φ output control

Timer output

TOUT/φ selection bit

(14) Port P55

Data bus

Direction register

Port latchData bus

φ output

Direction register

Port latch

Pull-up control

Pull-up control

(13) Ports P40, P71–P77

Direction register

Data bus

Port latch

Except P71 to P77

(15) Ports P56, P57

Direction register

Data bus

Port latch

A-D trigger input

Pull-up control

CNTR1 interrupt input

(16) Ports P64–P67

Direction register

Data bus Port latch

A-D conversion input

Fig. 12 Port block diagram (3)

Pull-up control

Analog input pin selection bit

Except P5

(17) Port P60

Data bus

D-A conversion output

VREF input switch

7

Direction register

Port latch

A-D conversion input

D-A

1, D-A2 output enable bit

VREF input selection bit

Pull-up control

Serial I/O2 input

Analog input pin selection bit

16

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

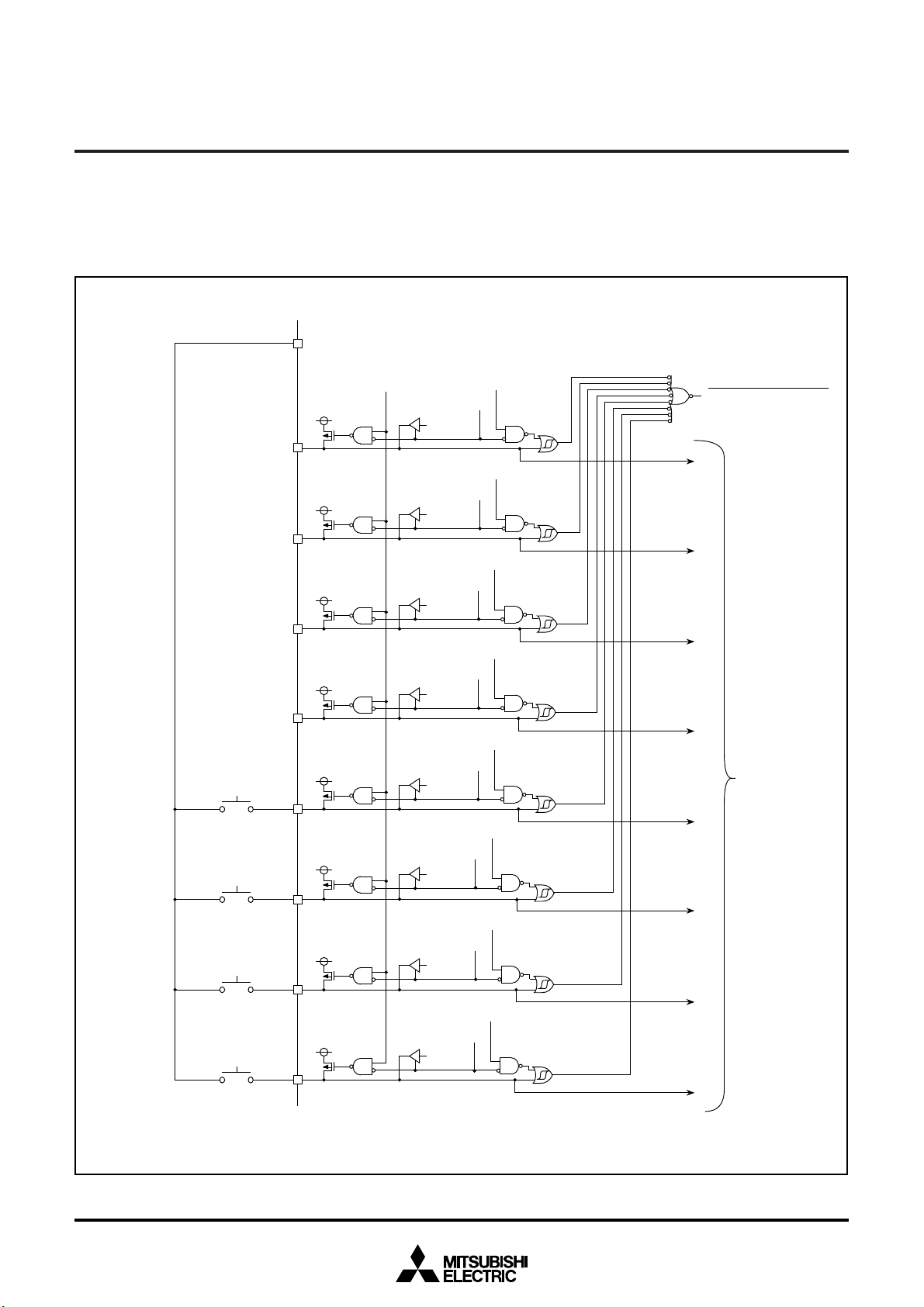

(18) Port P61

P61/SOUT2 P-channel output disable bit

Serial I/O2 transmit completion signal

Synchronous clock selection bit

Serial I/O2 port selection bit

Data bus

Direction register

Port latch

Serial I/O2 output

A-D conversion input

(20) Port P63

Synchronous clock selection bit

Synchronous clock output pin selection bit

Serial I/O2 port selection bit

Direction register

Data bus

Port latch

Pull-up control

Analog input pin selection bit

Pull-up control

(19) Port P62

Synchronous clock selection bit

Serial I/O2 port selection bit

Synchronous clock output pin

Data bus

selection bit

Direction register

Port latch

Serial I/O2 clock output

(21) COM0–COM3

VL3

VL2

VL1

Pull-up control

Serial I/O2 clock input

A-D conversion input

The gate input signal of each

transistor is controlled by the

LCD duty ratio and the bias

value.

Analog input pin selection bit

Serial I/O2 clock output

(22) SEG0–SEG17

VL2/VL3

VL1/VSS

Fig. 13 Port block diagram (4)

A-D conversion input

The voltage applied to the sources of

P-channel and N-channel transistors

is the controlled voltage by the bias

value.

Analog input pin selection bit

(23) Port P70

Data bus

VSS

Direction register

Port latch

INT0 input

17

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

INTERRUPTS

Interrupts occur by seventeen sources: seven external, nine internal, and one software.

Interrupt Control

Each interrupt except the BRK instruction interrupt have both an

interrupt request bit and an interrupt enable bit, and is controlled

by the interrupt disable flag. An interrupt occurs if the corresponding interrupt request and enable bits are “1” and the interrupt

disable flag is “0.” Interrupt enable bits can be set or cleared by

software. Interrupt request bits can be cleared by software, but

cannot be set by software. The BRK instruction interrupt and reset

cannot be disabled with any flag or bit. The I flag disables all interrupts except the BRK instruction interrupt and reset. If several

interrupts requests occurs at the same time the interrupt with highest priority is accepted first.

Table 6 Interrupt vector addresses and priority

Interrupt Source

Reset (Note 2)

INT0

INT1

Serial I/O1

reception

Serial I/O1

transmission

Timer X

Timer Y

Timer 2

Timer 3

CNTR

0

CNTR1

Timer 1

INT2

Serial I/O2

Key input

(Key-on wake-up)

ADT

A-D conversion

BRK instruction

Notes1: Vector addresses contain interrupt jump destination addresses.

2: Reset function in the same way as an interrupt with the highest priority.

Prior ity

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Vector Addresses (Note 1)

LowHigh

FFFD

FFFB16

FFF916

FFF716

FFF516

FFF316

FFF116

FFEF16

FFED16

FFEB16

FFE916

FFE716

FFE516

FFE316

FFE116

FFDF16

FFDD16

16

FFFC16

FFFA16

FFF816

FFF616

FFF416

FFF216

FFF016

FFEE16

FFEC16

FFEA16

FFE816

FFE616

FFE416

FFE216

FFE016

FFDE16

FFDC16

Interrupt Operation

Upon acceptance of an interrupt the following operations are automatically performed:

1. The contents of the program counter and processor status

register are automatically pushed onto the stack.

2. The interrupt disable flag is set and the corresponding

interrupt request bit is cleared.

3. The interrupt jump destination address is read from the vector table into the program counter.

■Notes

When the active edge of an external interrupt (INT0–INT2, CNTR0,

CNTR

1) is set or when switching interrupt sources of ADT/A-D

conversion interrupt, the corresponding interrupt request bit may

also be set. Therefore, take following sequence:

(1) Disable the external interrupt which is selected.

(2) Change the active edge in interrupt edge selection register

(timer XY mode register when using CNTR

(3) Clear the set interrupt request bit to “0.”

(4) Enable the external interrupt which is selected.

Interrupt Request

Generating Conditions

At reset

At detection of either rising or

falling edge of INT

At detection of either rising or

falling edge of INT1 input

At completion of serial I/O1 data

reception

At completion of serial I/O1

transmit shift or when transmission buffer is empty

At timer X underflow

At timer Y underflow

At timer 2 underflow

At timer 3 underflow

At detection of either rising or

falling edge of CNTR0 input

At detection of either rising or

falling edge of CNTR

At timer 1 underflow

At detection of either rising or

falling edge of INT

At completion of serial I/O2 data

transmission or reception

At falling of conjunction of input

level for port P2 (at input mode)

At falling of ADT input

At completion of A-D conversion

At BRK instruction execution

0 input

1 input

2 input

Non-maskable

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

Valid when serial I/O1 is selected

Valid when serial I/O1 is selected

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

Valid when serial I/O2 is selected

External interrupt

(valid when an “L” level is applied)

Valid when ADT interrupt is selected External interrupt

(Valid at falling)

Valid when A-D interrupt is selected

Non-maskable software interrupt

0, CNTR1)

Remarks

18

Interrupt request bit

Interrupt enable bit

Interrupt disable flag (I)

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 14 Interrupt control

b7 b0

b7 b0

Interrupt edge selection register

16

(INTEDGE : address 003A

)

INT0 interrupt edge selection bit

INT

1

interrupt edge selection bit

2

interrupt edge selection bit

INT

INT

3

interrupt edge selection bit

Not used (return “0” when read)

Interrupt request register 1

(IREQ1 : address 003C

16

)

INT0 interrupt request bit

1

interrupt request bit

INT

Serial I/O1 receive interrupt request bit

Serial I/O1 transmit interrupt request bit

Timer X interrupt request bit

Timer Y interrupt request bit

Timer 2 interrupt request bit

Timer 3 interrupt request bit

BRK instruction

Reset

0 : Falling edge active

1 : Rising edge active

b7 b0

0 : No interrupt request issued

1 : Interrupt request issued

Interrupt request

Interrupt request register 2

(IREQ2 : address 003D

16

)

CNTR0 interrupt request bit

CNTR

1

interrupt request bit

Timer 1 interrupt request bit

INT

2

interrupt request bit

Serial I/O2 interrupt request bit

Key input interrupt request bit

ADT/AD conversion interrupt request bit

Not used (returns “0” when read)

b7 b0

Interrupt control register 1

(ICON1 : address 003E

INT0 interrupt enable bit

1

interrupt enable bit

INT

Serial I/O receive interrupt enable bit

Serial I/O transmit interrupt enable bit

Timer X interrupt enable bit

Timer Y interrupt enable bit

Timer 2 interrupt enable bit

Timer 3 interrupt enable bit

Fig. 15 Structure of interrupt-related registers

b7 b0

16

)

Interrupt control register 2

(ICON2 : address 003F

16

)

CNTR0 interrupt enable bit

1

interrupt enable bit

CNTR

Timer 1 interrupt enable bit

INT

2

interrupt enable bit

Serial I/O2 interrupt enable bit

Key input interrupt enable bit

ADT/AD conversion interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit.)

0 : Interrupts disabled

1 : Interrupts enabled

19

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Key Input Interrupt (Key-on wake-up)

A Key-on wake up interrupt request is generated by applying “L”

level to any pin of port P2 that have been set to input mode. In

other words, it is generated when AND of input level goes from “1”

Port PXx

“L” level output

Port P27 output

Port P26 output

Port P25 output

PULLA register

Bit 2 = “1”

✽

✽

✽

Key input control register = “1”

Port P27

direction register = “1”

✽✽

Port P27

latch

Port P26

direction register = “1”

✽✽

Port P26

latch

Port P25

direction register = “1”

✽✽

Port P25

latch

to “0”. An example of using a key input interrupt is shown in Figure

16, where an interrupt request is generated by pressing one of the

keys consisted as an active-low key matrix which inputs to ports

P2

0–P23.

Key input interrupt request

Key input control register = “1”

Key input control register = “1”

Port P24 output

Port P23

input

Port P22

input

Port P21

input

Port P20

input

Key input control register = “1”

Port P24

✽

✽

✽

✽

✽

direction register = “1”

✽✽

Port P24

latch

Port P23

direction register = “0”

Port P22

direction register = “0”

Port P21

direction register = “0”

Port P20

direction register = “0”

Key input control register = “1”

✽✽

Port P23

latch

Key input control register = “1”

✽✽

Port P22

latch

Key input control register = “1”

✽✽

Port P21

latch

Key input control register = “1”

✽✽

Port P20

latch

Port P2 input

reading circuit

Fig. 16 Connection example when using key input interrupt and port P2 block diagram

20

✽ P-channel transistor for pull-up

✽✽ CMOS output buffer

MITSUBISHI MICROCOMPUTERS

3827 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

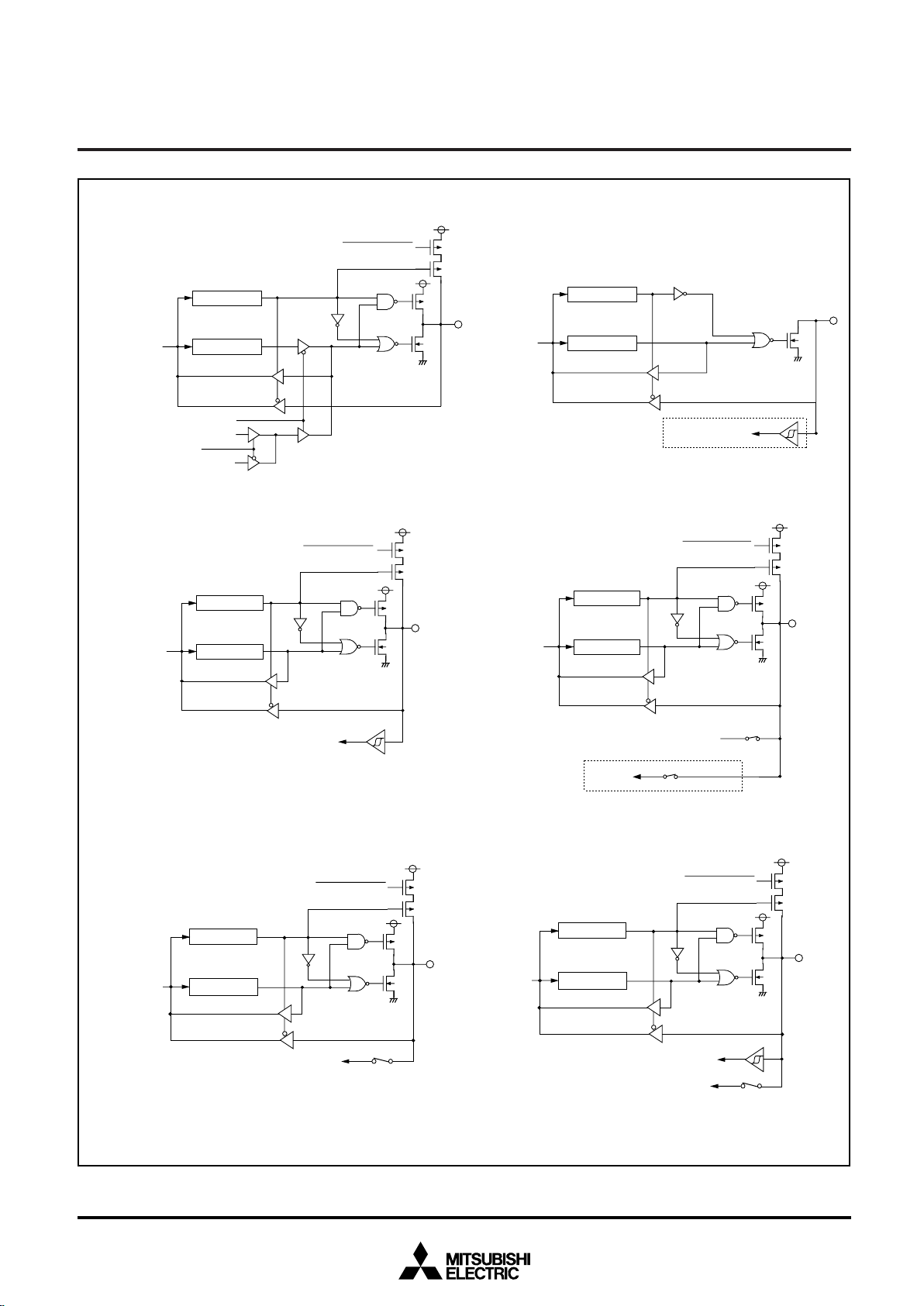

TIMERS

The 3827 group has five timers: timer X, timer Y, timer 1, timer 2,

and timer 3. Timer X and timer Y are 16-bit timers, and timer 1,

timer 2, and timer 3 are 8-bit timers.

All timers are down count timers. When the timer reaches “00

an underflow occurs at the next count pulse and the corresponding timer latch is reloaded into the timer and the count is

continued. When a timer underflows, the interr upt request bit cor-

Real time port

P5

2

P52 direction register

P53

3 direction register

P5

4/CNTR0

P5

P54 direction register

P55/CNTR1

f(XIN)/16

(f(XCIN)/16 in φ = XCIN divided by 2)

P4

3/φ/TOUT

3 direction register

P4

control bit “1”

P5

Real time port

control bit “1”

P5

f(XIN)/16

(f(XIN)/16 in low-speed mode✽)

CNTR

0 active

edge switch bit

“0”

Pulse width

measurement

mode

“1”

CNTR0 active

edge switch bit

Pulse output mode

CNTR1 active

edge switch bit

“0”

“1”

Timer 1 count source

selection bit

XCIN

TOUT output

control bit

f(XIN)/16(f(XCIN)/16 in low-speed mode✽)

Q D

Latch

“0”

2 latch

Q D

“0”

3 latch

Timer X operating mode bits

“00”,“01”,“11”

Latch

Real time port

control bit “0”

“10”

“0”

“1”

4 latch

P5

f(XIN)/16

(f(XCIN)✕16 in φ = XCIN divided by 2)

“00”,“01”,“11”

Timer Y operating

“10”

mode bit

“0”

Timer 1 latch (8)

Timer 1 (8)

“1”

OUT output

T

active edge

switch bit

P4

3 latch

“0”

“1”

T

OUT output

control bit

Q

Q

16”,

2 data for real time port

P5

3 data for real time port

P5

Timer X stop

control bit

Timer X (low) latch (8) Timer X (high) latch (8)

S

Q

T

Q

Rising edge detection

Falling edge detection

Timer Y stop

control bit

Timer Y (low) latch (8) Timer Y (high) latch (8)

Timer Y (low) (8) Timer Y (high) (8)

S

T

Timer 3 count

source selection bit

responding to that timer is set to “1”.

Read and write operation on 16-bit timer must be performed for

both high and low-order bytes. When reading a 16-bit timer, read

the high-order byte first. When writing to a 16-bit timer, write the

low-order byte first. The 16-bit timer cannot perform the correct operation when reading during the write operation, or when writing

during the read operation.

Data bus

Timer X mode register

“1”

Pulse output mode

write signal

Timer X write

control bit

Timer X (low) (8)

Timer X (high) (8)

Timer Y operating mode bit

Pulse width HL continuously measurement mode

Period

measurement mode

Timer 2 count source

selection bit

“0”

Timer 2 latch (8)

Timer 2 (8)

“1”

f(XIN)/16

(f(XCIN)✕16 in φ=XCIN divided by 2)

Timer 3 latch (8)

“0”

Timer 3 (8)

“1”

“00”,“01”,“10”

“11”

Timer 2 write

control bit

Timer Y

interrupt

request

Timer 1

interrupt

request

Timer 2

interrupt

request

Timer 3

interrupt

request

Timer X

interrupt

request

CNTR0

interrupt

request

CNTR1

interrupt

request

Fig. 17 Timer block diagram

21

Loading...

Loading...