Mitsubishi M37736M4LXXXHP Datasheet

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

DESCRIPTION

The M37736M4LXXXHP is a single-chip microcomputer using the

7700 Family core. This single-chip microcomputer has a CPU and a

bus interface unit. The CPU is a 16-bit parallel processor that can be

an 8-bit parallel processor, and the bus interface unit enhances the

memory access efficiency to execute instructions fast. This

microcomputer also includes a 32 kHz oscillation circuit, in addition

to the ROM, RAM, multiple-function timers, serial I/O, A-D converter,

and so on.

Its strong points are the low power dissipation, the low supply voltage,

and the small package.

In the M37736M4LXXXHP, as the multiplex method of the external

bus, either of 2 types can be selected.

FEATURES

●Number of basic instructions .................................................. 103

●Memory size ROM ................................................. 32 Kbytes

RAM ................................................ 2048 bytes

●Instruction execution time

The fastest instruction at 12 MHz frequency ...................... 333 ns

●Single power supply ...................................................... 2.7–5.5 V

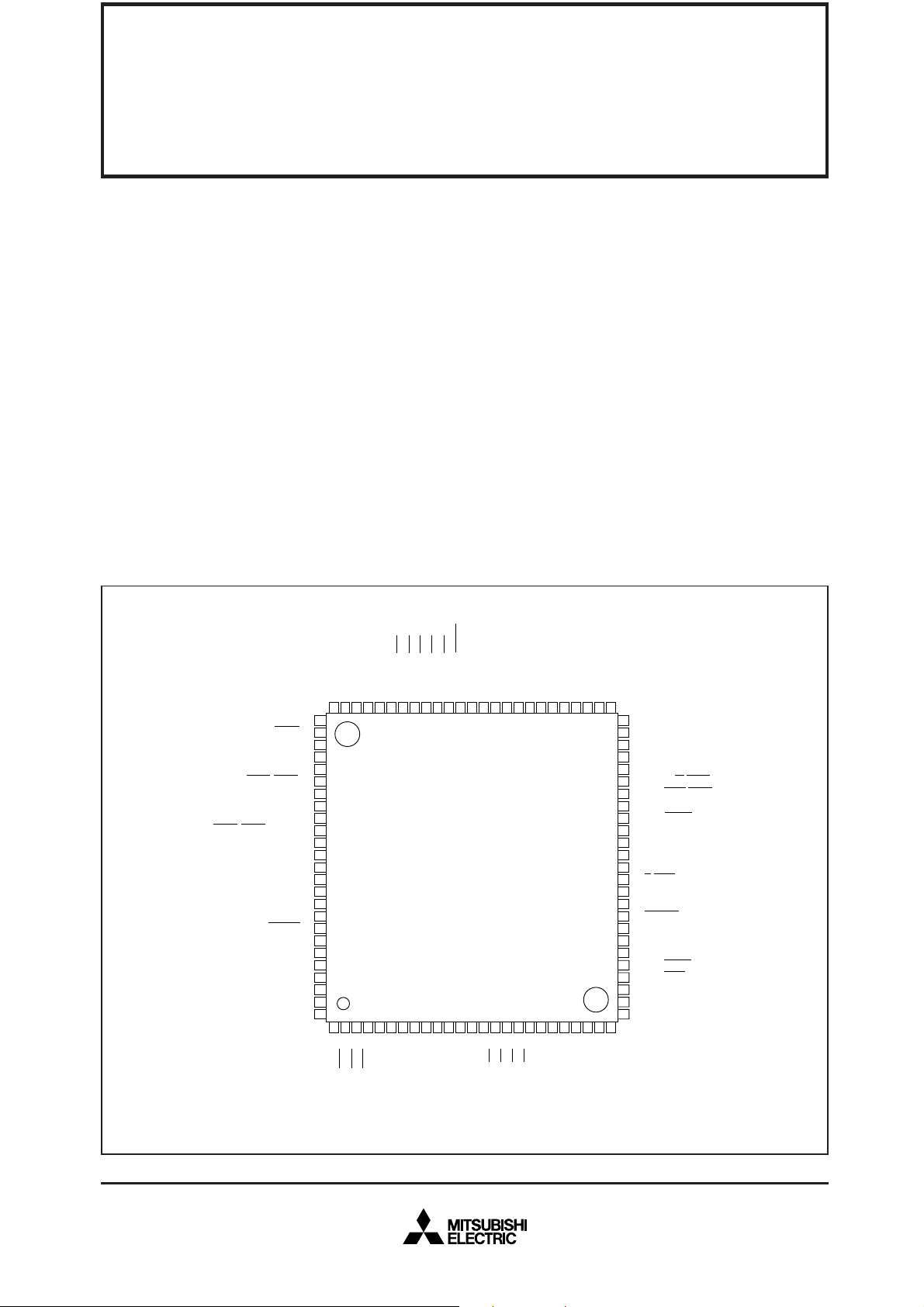

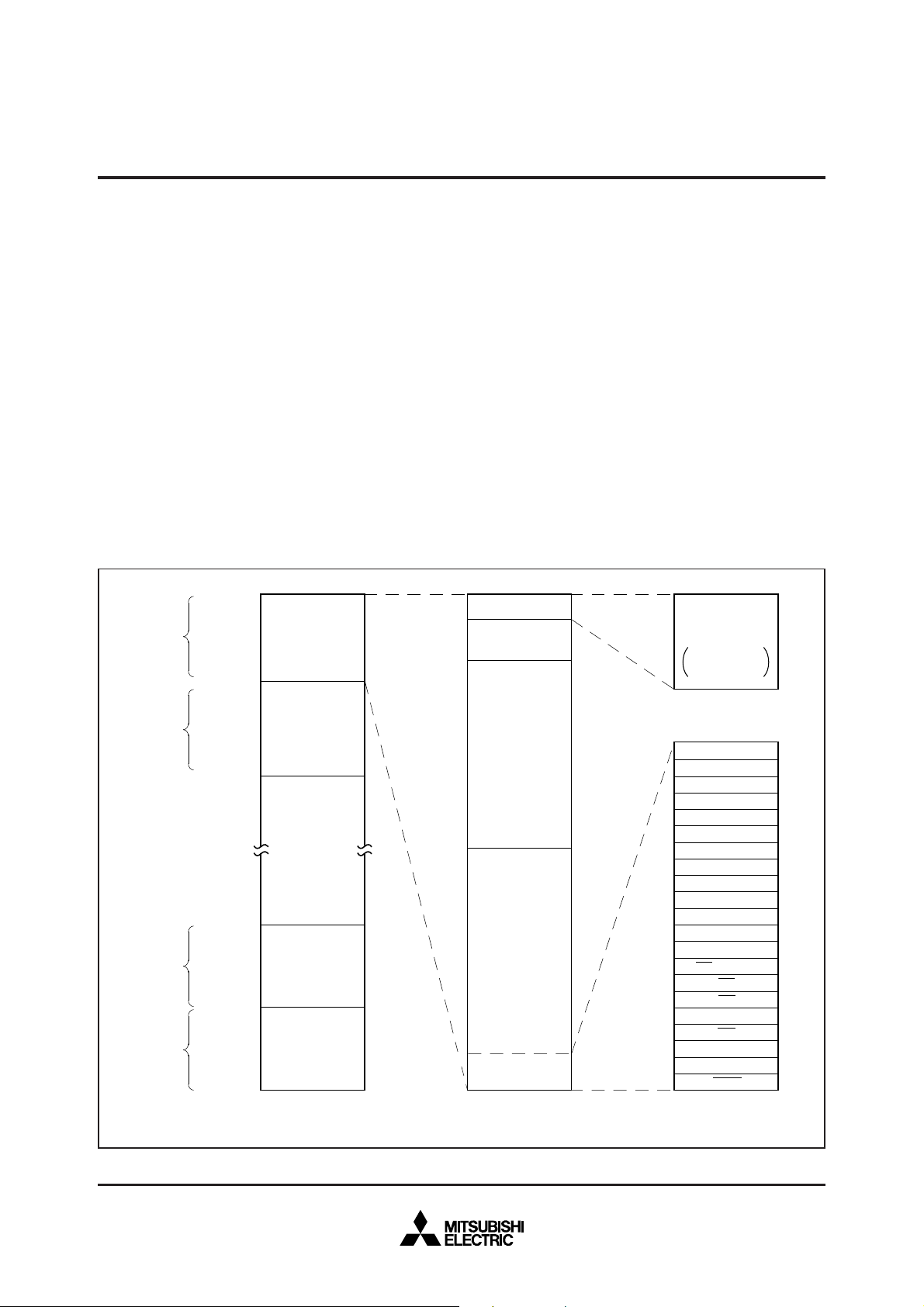

PIN CONFIGURATION (TOP VIEW)

0

1

2

/CS

/CS

/CS

0

1

2

/A

/A

/A

0

1

2

↔ P0

↔ P0

M37736M4LXXXHP

↔

↔

↔

↔

↔

IN

IN

IN

OUT

OUT

/TA4

/TA3

/TA2

1

7

5

/TA4

/TA3

0

6

P5

P5

P6

P6

P5

P91/CLK2 ↔

P9

P8

P8

P8

4

/CTS1/RTS1 ↔

P8

P8

P8

2/RXD0

/CLKS0 ↔

P8

0

P8

/CTS0/RTS0/CLKS1 ↔

AV

P7

7

/AN7/X

P7

6

/AN6/X

P7

5

/AN5/AD

P7

P7

P7

P7

P7

P6

7

/TB2IN/f

P6

6

0

/CTS2 ↔

7/TXD1

6/RXD1

5

/CLK1 ↔

3/TXD0

1

/CLK0 ↔

V

CC

CC

V

REF

SS

AV

V

SS

CIN

COUT

TRG

4

/AN4 ↔

3

/AN3 ↔

2

/AN2 ↔

1

/AN1 ↔

0

/AN0 ↔

SUB

/TB1

2

2

D

D

X

X

/R

/T

2

3

↔ P9

→ P9

→ P94→ P95→ P96→ P97↔ P0

75747372717069686766656463626160595857565554535251

76

77

↔

78

↔

79

80

81

82

↔

83

84

85

86

87

88

→

89

90

91

↔

92

↔

93

↔

94

95

96

97

98

99

↔

100

IN

↔

123456789

↔

↔

↔

↔

2

1

0

IN

/INT

/INT

/INT

4

3

2

/TB0

5

P6

P6

P6

P6

●Low power dissipation (At 3 V supply voltage, 12 MHz frequency)

............................................ 9 mW (Typ.)

●Interrupts ............................................................ 19 types, 7 levels

●Multiple-function 16-bit timer ................................................. 5 + 3

●Serial I/O (UART or clock synchronous) ..................................... 3

●10-bit A-D converter .............................................. 8-channel inputs

●12-bit watchdog timer

●Programmable input/output, output

(ports P0, P1, P2, P3, P4, P5, P6, P7, P8, P9, P10) ............... 84

●Clock generating circuit ........................................ 2 circuits built-in

●Small package ..................... 100-pin plastic molded fine-pitch QFP

(100P6Q-A;0.5 mm lead pitch)

APPLICATION

Control devices for general commercial equipment such as office

automation, office equipment, personal information equipment, and

others.

Control devices for general industrial equipment such as

communication equipment, and others.

0

1

2

/D

/D

3

/CS

3

/A

3

↔ P0

10

↔

OUT

/TA2

4

P5

4

/CS

4

/A

4

↔ P0

11

↔

IN

/TA1

3

P5

8

16

17

/RSMP

/A

/A

/D

5

6

7

8

/A

/A

/A

/A

5

6

7

0

↔ P0

↔ P0

↔ P0

↔ P1

1213141516

↔

↔

↔

↔

3

IN

/KI

OUT

OUT

7

/TA0

1

/TA1

/TA0

P10

2

0

P5

P5

P5

9

/D

9

/A

1

↔ P1

↔

2

/KI

6

P10

10

11

/D

/D

10

11

/A

/A

2

3

↔ P1

↔ P1

171819

↔

↔

1

0

/KI

/KI

5

4

P10

P10

12

13

/D

/D

12

13

/A

/A

4

5

↔ P1

↔ P1

2021222324

↔

↔

3

2

P10

P10

14

/D

14

/A

6

↔ P1

↔

1

P10

15

/D

15

/A

7

↔ P1

↔

0

P10

0

/A

16

/A

0

↔ P2

↔

7

P4

1

/A

17

/A

1

↔ P2

↔

6

P4

/D

2

/A

18

/A

2

↔ P2

25

↔

5

P4

↔ P23/A19/A3/D

50

49

↔ P24/A20/A4/D

↔ P25/A21/A5/D

48

↔ P26/A22/A6/D

47

↔ P27/A23/A7/D

46

45

↔ P30/R/W/WEL

44

↔ P3

1

/BHE/WEH

43

↔ P3

2

/ALE

42

↔ P3

3

/HLDA

41

→ EVL0

40

→ EVL1

39

V

CC

38

V

SS

37

→ E/RDE

36

→ X

OUT

35

← X

IN

34

← RESET

33

← BSEL

32

31

30

29

28

27

26

← CNV

← BYTE

0

↔ P4

1

↔ P4

↔ P4

2/f1

↔ P4

3

↔ P4

4

SS

/HOLD

/RDY

3

4

5

6

7

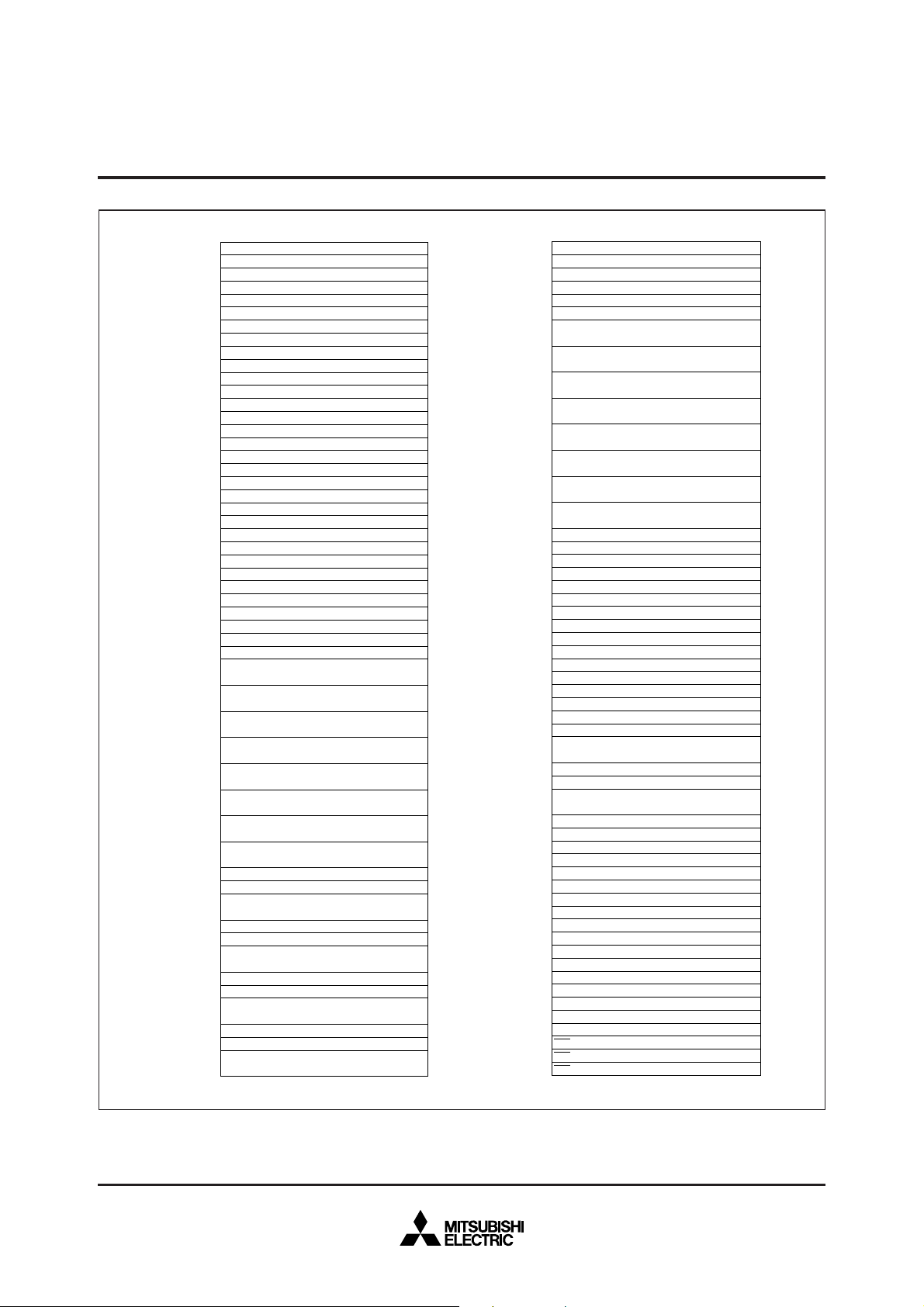

Outline 100P6Q-A

PRELIMINARY

Clock input

X

IN

Clock output

X

OUT

Clock Generating Circuit

Timer TA4(16)

RAM

2048 bytes

ROM

32 Kbytes

Timer TA3(16)

Timer TA2(16)

Timer TA1(16)

P8(8)

Input/Output

port P8

P7(8)

Input/Output

port P7

X

CIN

X

COUT

P6(8)

Input/Output

port P6

P5(8)

Input/Output

port P5

P4(8)

Input/Output

port P4

P3(4)

Input/Output

port P3

P2(8)

Input/Output

port P2

P1(8)

Input/Output

port P1

P0(8)

Input/Output

port P0

Timer TA0(16)

Watchdog Timer

Timer TB2(16)

Timer TB1(16)

Timer TB0(16)

UART2(9)

UART1(9)

UART0(9) A-D Converter(10)

Instruction Register(8)

Data Buffer DBH(8)

Data Buffer DB

L

(8)

Processor Status Register PS(11)

Direct Page Register DPR(16)

Stack Pointer S(16)

Index Register Y(16)

Index Register X(16)

Accumulator B(16)

Arithmetic Logic

Unit(16)

Accumulator A(16)

Instruction Queue Buffer Q0(8)

Instruction Queue Buffer Q

1

(8)

Incrementer(24)

Program Address Register PA(24)

Data Address Register DA(24)

Instruction Queue Buffer Q

2

(8)

Program Counter PC(16)

Incrementer/Decrementer(24)

Program Bank Register PG(8)

Data Bank Register DT((8)

Input Buffer Register IB(16)

Address Bus

Data Bus(Even)

Data Bus(Odd)

X

CINXCOUT

Enable output

E

Reset input

RESET

(0V)

V

SS

(0V)

AV

SS

CNV

SS

AV

CC

Reference

voltage input

V

REF

Bus method

selection input

BSEL

External data bus width

selection input

BYTE

V

CC

P9(8)

Output

port P9

P10(8)

Input/Output

port P10

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

2

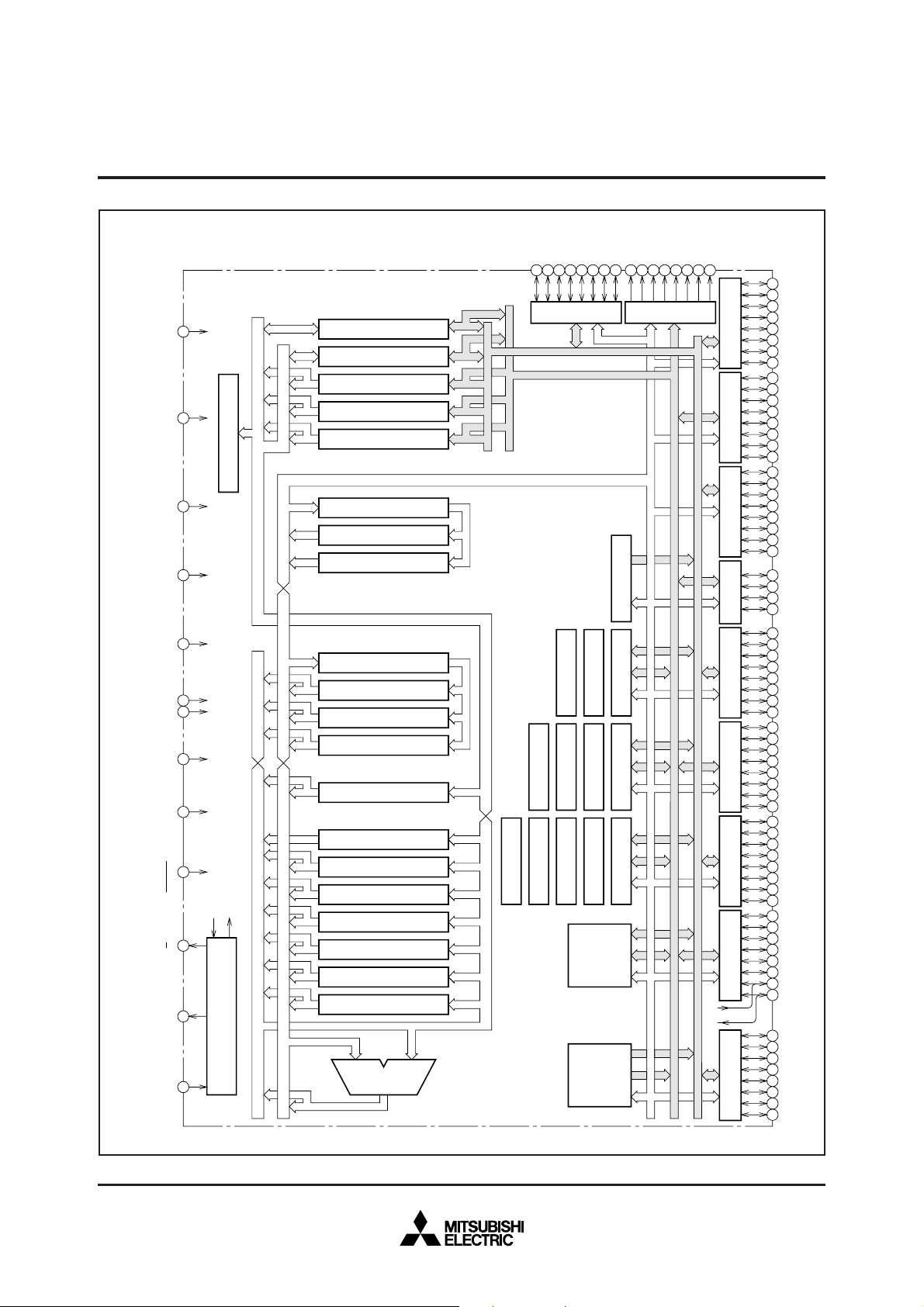

M37736M4LXXXHP BLOCK DIAGRAM

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

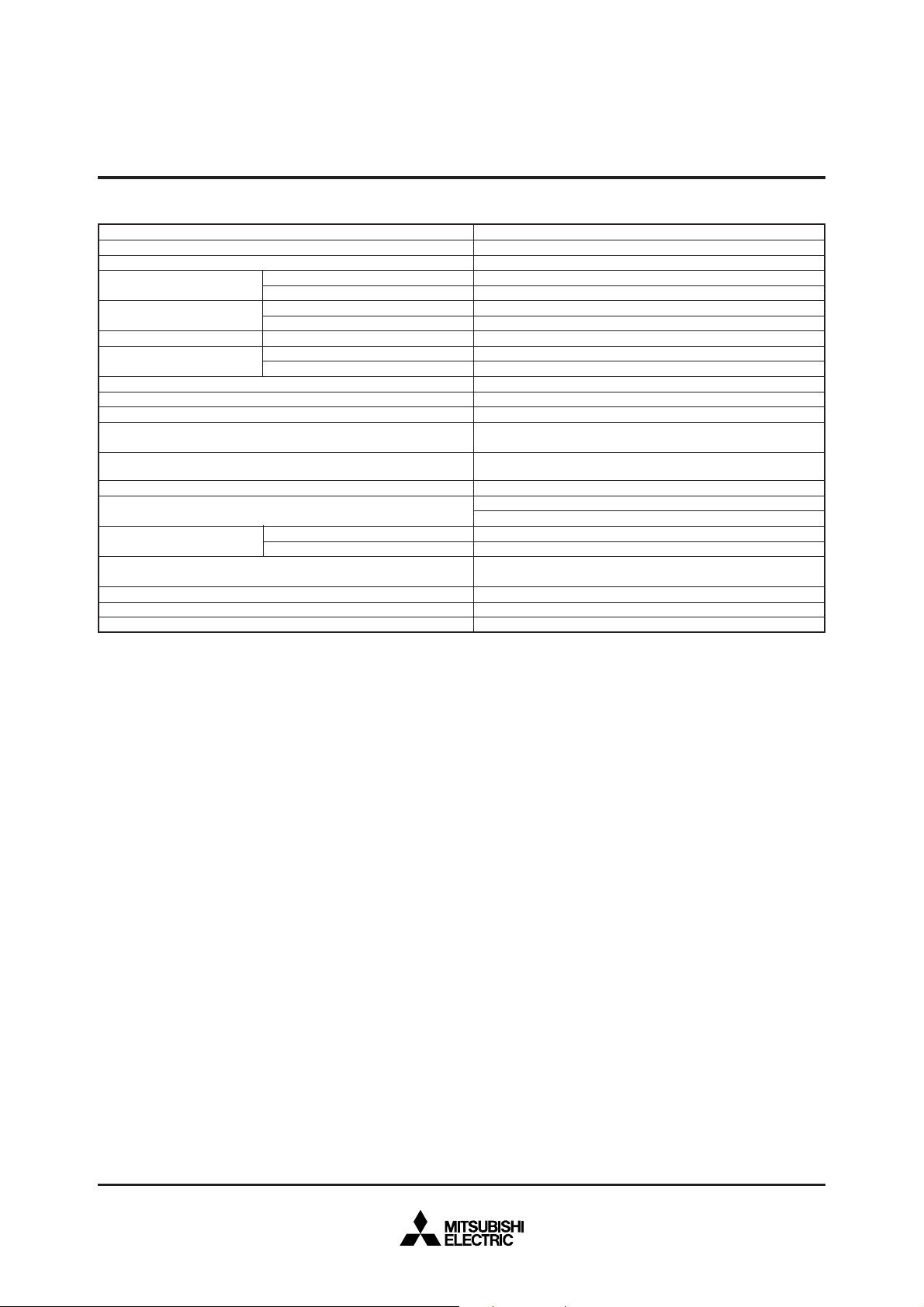

FUNCTIONS OF M37736M4LXXXHP

Number of basic instructions 103

Instruction execution time 333 ns (the fastest instruction at external clock 12 MHz frequency)

Memory size

Input/Output ports

Output port P9 8-bit ✕ 1

Multi-function timers

Serial I/O (UART or clock synchronous serial I/O) ✕ 3

A-D converter 10-bit ✕ 1 (8 channels)

Watchdog timer 12-bit ✕ 1

Interrupts

Clock generating circuit

Supply voltage 2.7 – 5.5 V

Power dissipation

Input/Output characteristic

Memory expansion

Operating temperature range –40 to 85 °C

Device structure CMOS high-performance silicon gate process

Package

Parameter Functions

ROM 32 Kbytes

RAM 2048 bytes

P0 – P2, P4 – P8, P10 8-bit ✕ 9

P3 4-bit ✕ 1

TA0, TA1, TA2, TA3, TA4 16-bit ✕ 5

TB0, TB1, TB2 16-bit ✕ 3

3 external types, 16 internal types

Each interrupt can be set to the priority level (0 – 7.)

2 circuits built-in (externally connected to a ceramic resonator or a

quartz-crystal oscillator)

9 mW (at 3 V supply voltage, external clock 12 MHz frequency)

22.5 mW (at 5 V supply voltage, external clock 12 MHz frequency)

Input/Output voltage 5 V

Output current 5 mA

External bus mode A; maximum 16 Mbytes,

External bus mode B; maximum 1 Mbytes

100-pin plastic molded fine-pitch QFP (100P6Q-A;0.5 mm lead pitch)

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

3

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

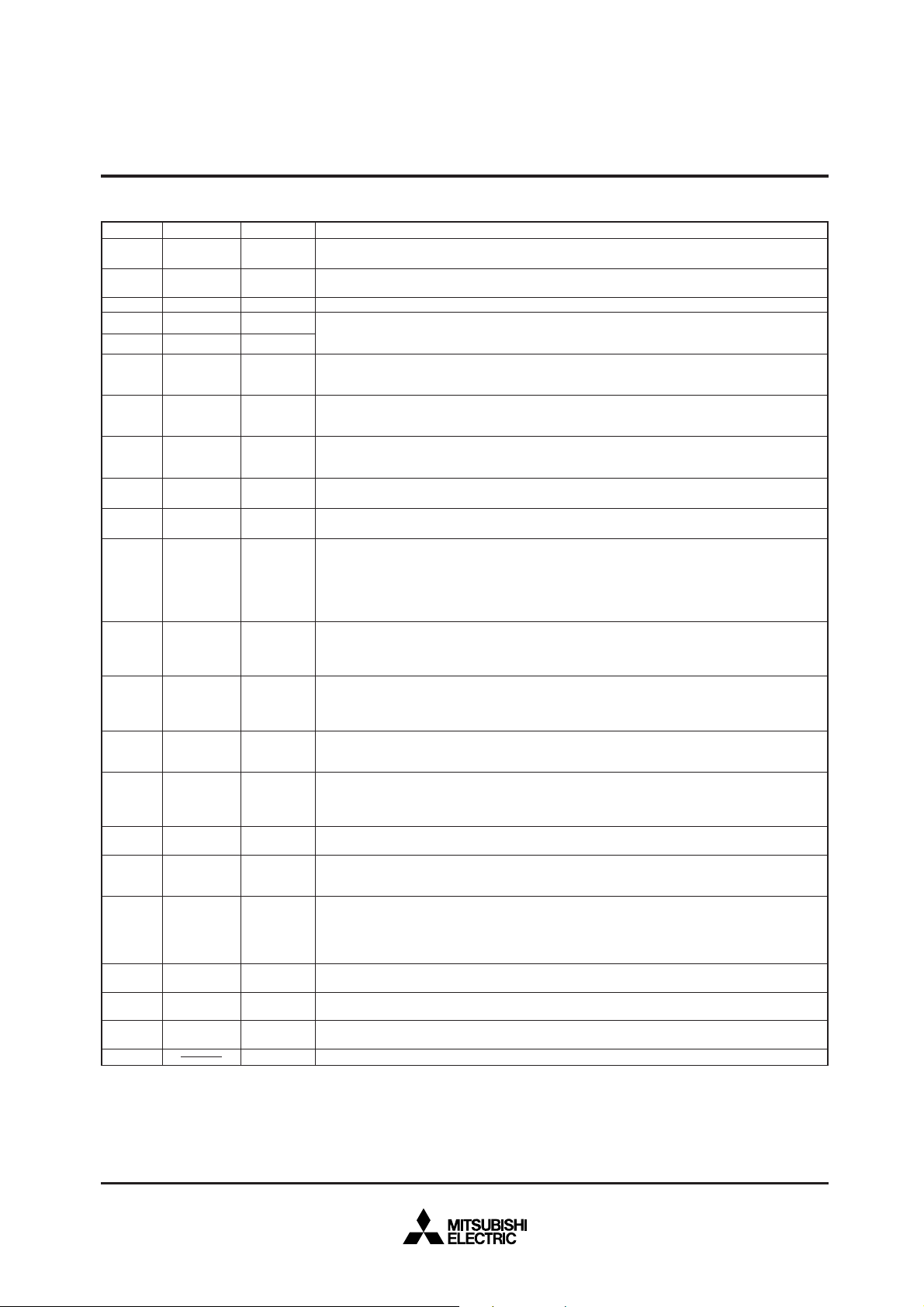

PIN DESCRIPTION

Pin Name Input/Output Functions

Vcc, Power source Apply 2.7 – 5.5 V to Vcc and 0 V to Vss.

Vss

CNVss CNVss input Input This pin controls the processor mode. Connect to Vss for the single-chip mode and the memory

_____

RESET Reset input Input When “L” level is applied to this pin, the microcomputer enters the reset state.

XIN Clock input Input

X

OUT Clock output Output

_

E Enable output Output This pin functions as the enable signal output pin which indicates the access status in the internal

BYTE

External data

Input In the memory expansion mode or the microprocessor mode, this pin determines whether the

bus width

selection input

BSEL Bus method Input In the memory expansion mode or the microprocessor mode, this pin determines the external bus

select input mode. The bus mode becomes the external bus mode A when “H” signal is input, and the external

AVcc, Analog power Power source input pin for the A-D converter. Externally connect AVcc to Vcc and AVss to Vss.

AVss source input

REF Reference Input This is reference voltage input pin for the A-D converter.

V

voltage input

0 – P07 I/O port P0 I/O In the single-chip mode, port P0 becomes an 8-bit I/O port. An I/O direction register is available so

P0

0 – P17 I/O port P1 I/O In the single-chip mode, these pins have the same functions as port P0. When the BYTE pin is set

P1

0 – P27 I/O port P2 I/O In the single-chip mode, these pins have the same functions as port P0. In the memory expansion

P2

P3

0 – P33 I/O port P3 I/O In the single-chip mode, these pins have the same function as port P0. In the memory expansion

0 – P47 I/O port P4 I/O In the single-chip mode, these pins have the same functions as port P0. In the memory expansion

P4

0 – P57 I/O port P5 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P5

0 – P67 I/O port P6 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P6

0 – P77 I/O port P7 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins function

P7

0 – P87 I/O port P8 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P8

0 – P97

P9

P100 – P107

EVL0, EVL1

Output port P9

Output Port P9 is an 8-bit I/O port. These ports are floating when reset. When writing to the port latch,

I/O port P10 I/O In addition to having the same functions as port P0 in the single-chip mode. P104 – P107 also

Output These pins should be left open.

expansion mode, and to Vcc for the microprocessor mode.

These are pins of main-clock generating circuit. Connect a ceramic resonator or a quartzcrystal oscillator between X

IN and XOUT. When an external clock is used, the clock source should

be connected to the XIN pin, and the XOUT pin should be left open.

bus. In the external bus mode B and the memory expansion mode or the microprocessor mode,

this pin output signal RDE.

___

external data bus has an 8-bit width or a 16-bit width. The data bus has a 16-bit width when “L”

signal is input and an 8-bit width when “H” signal is input.

bus mode B when “L” signal is input.

that each pin can be programmed for input or output. These ports are in the input mode when

reset.

In the memory expansion mode or the microprocessor mode, these pins output address (A

at the external bus mode A, and these pins output signals CS0 – CS4 and RSMP, and addresses

(A16, A17) at the external bus mode B.

to “L” in the memory expansion mode or the microprocessor mode and external data bus has a

16-bit width, high-order data (D8 – D15) is input/output or an address (A8 – A15) is output. When

the BYTE pin is “H” and an external data bus has an 8-bit width, only address (A8 – A15) is output.

mode or the microprocessor mode, low-order data (D

is output. When using the external bus mode A, the address is A

external bus mode B, the address is A0 – A7.

mode or the microprocessor mode, R/W, BHE, ALE, and HLDA signals are output at the external

bus mode A, and WEL, WEH, ALE, and HLDA signals are output at the external bus mode B.

________ ____________ ___ ___ __ __ ___ __ __

mode or the microprocessor mode, P40, P41, and P42 become HOLD and RDY input pins, and a

clock

φ1 output pin, respectively. Functions of the other pins are the same as in the single-chip

mode. However, in the memory expansion mode, P42 can be selected as an I/O port.

function as I/O pins for timers A0 to A3.

function as I/O pins for timer A4, input pins for external interrupt input (INT0 – INT2) and input pins

for timers B0 to B2. P67 also functions as sub-clock φSUB output pin.

as input pins for A-D converter. Additionally, P7

COUT) and the input pin (XCIN) of the sub-clock (32 kHz) oscillation circuit, respectively. When

(X

P7

6 and P77 are used as the XCOUT and XCIN pins, connect a resonator or an oscillator between

the both.

function as I/O pins for UART 0 and UART 1.

these ports become the output mode. P90 – P93 also function as I/O port for UART 2.

function as input pins for key input interrupt input (Kl0 – Kl3).

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

___ ___ ____

0 – D7) is input/output or an address

____________

______________

6 and P77 have the function as the output pin

__ __

16 – A23. When using the

______________

____ ___

___ ___

0 – A7)

4

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

BASIC FUNCTION BLOCKS

The M37736M4LXXXHP has the same fuanctions as the

M37736MHBXXXGP except for the memory allocation, the reset

circuit, the ROM area modification function, and the package.

Refer to the section on the M37736MHBXXXGP.

MEMORY

The memory map is shown in Figure 1. The address space has a

capacity of 16 Mbytes and is allocated to addresses from 0

FFFFFF

16. The address space is divided by 64-Kbyte unit called bank.

The banks are numbered from 0

However, banks 10

16 – FF16 cannot be accessed in the external bus

16 to FF16.

mode B.

Built-in ROM, RAM and control registers for internal peripheral devices

are assigned to bank 0

The 32-Kbyte area from addresses 8000

ROM. Addresses FFD6

16.

16 to FFFF16 is the built-in

16 to FFFF16 are the RESET and interrupt

vector addresses and contain the interrupt vectors. Refer to the section

on interrupts for details.

The 2048-byte area allocated to addresses from 80

000000

16

Bank 0

16

00FFFF

16

010000

16

16 to 87F16 is the

16 to

000000

00007F

000080

00087F

built-in RAM. In addition to storing data, the RAM is used as stack

during a subroutine call or interrupts.

Peripheral devices such as I/O ports, A-D converter, serial I/O, timer,

and interrupt control registers are allocated to addresses from 0

7F

16.

Additionally, the internal ROM area can be modified by software. Refer

to the section on ROM area modification function for details.

A 256-byte direct page area can be allocated anywhere in bank 0

by using the direct page register (DPR). In the direct page addressing

mode, the memory in the direct page area can be accessed with two

words. Hence program steps can be reduced.

16

16

16

16

Internal RAM

2048 bytes

000000

00007F

16

Internal peripheral

devices

control registers

refer to Fig. 2 for

detail information

16

16 to

16

Bank 1

16

01FFFF

16

• • • • • • • • • • • • • • • • • • •

008000

16

FE0000

Bank FE

Bank FF

16

16

FEFFFF

16

FF0000

16

16

FFFFFF

16

00FFD6

00FFFF

Internal ROM

32 Kbytes

16

16

Notes 1. Internal ROM area can be modified. (Refer to the section on ROM area modification function.)

2. Banks 10

16

– FF16 cannot be accessed in the external bus mode B.

Fig. 1 Memory map

00FFD6

00FFFE

Interrupt vector table

16

A-D/UART2 trans./rece.

UART1 transmission

UART1 receive

UART0 transmission

UART0 receive

Timer B2

Timer B1

Timer B0

Timer A4

Timer A3

Timer A2

Timer A1

Timer A0

INT

2/Key input

INT

1

INT

0

Watchdog timer

DBC

BRK instruction

Zero divide

16

RESET

5

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

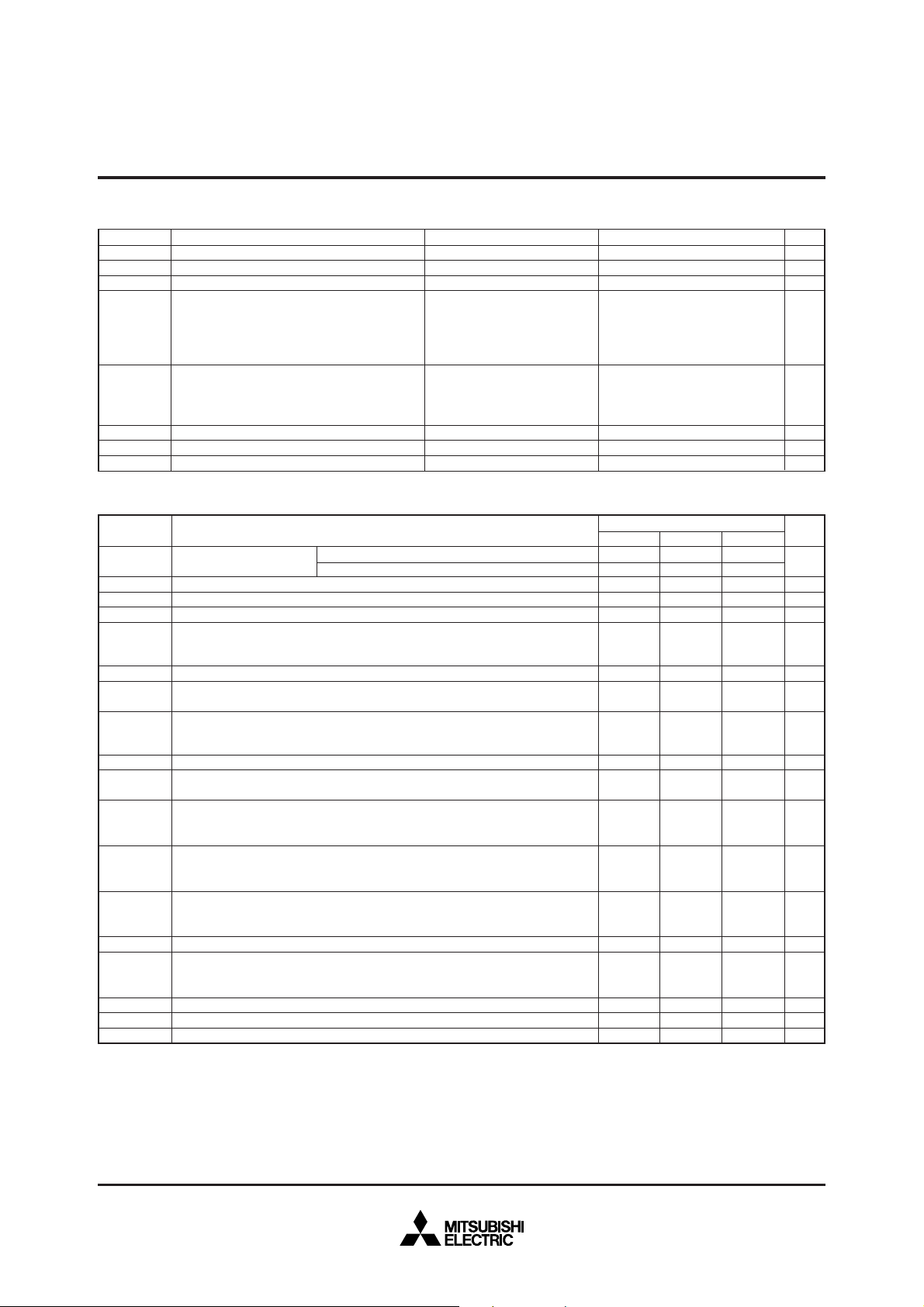

Address (Hexadecimal notation)

000000

000001

000002

000003

000004

000005

000006

000007

000008

000009

00000A

00000B

00000C

00000D

00000E

00000F

000010

000011

000012

000013

000014

Port P0 register

Port P1 register

Port P0 direction register

Port P1 direction register

Port P2 register

Port P3 register

Port P2 direction register

Port P3 direction register

Port P4 register

Port P5 register

Port P4 direction register

Port P5 direction register

Port P6 register

Port P7 register

Port P6 direction register

Port P7 direction register

Port P8 register

Port P8 direction register

000015

000016

000017

000018

000019

00001A

00001B

00001C

00001D

00001E

00001F

000020

000021

000022

000023

000024

000025

000026

000027

000028

000029

00002A

00002B

00002C

00002D

00002E

00002F

000030

000031

000032

000033

000034

000035

000036

000037

000038

000039

00003A

00003B

00003C

00003D

00003E

00003F

Reserved area (Note)

Reserved area (Note)

A-D control register 0

A-D control register 1

A-D register 0

A-D register 1

A-D register 2

A-D register 3

A-D register 4

A-D register 5

A-D register 6

A-D register 7

UART 0 transmit/receive mode register

UART 0 baud rate register

UART 0 transmission buffer register

UART 0 transmit/receive control register 0

UART 0 transmit/receive control register 1

UART 0 receive buffer register

UART 1 transmit/receive mode register

UART 1 baud rate register

UART 1 transmission buffer register

UART 1 transmit/receive control register 0

UART 1 transmit/receive control register 1

UART 1 receive buffer register

Address (Hexadecimal notation)

000040

000041

000042

000043

000044

Count start flag

One-shot start flag

Up-down flag

000045

000046

000047

000048

000049

00004A

00004B

00004C

00004D

00004E

00004F

000050

000051

000052

000053

000054

000055

000056

000057

000058

000059

00005A

00005B

00005C

00005D

00005E

00005F

000060

000061

000062

000063

000064

000065

000066

000067

000068

000069

00006A

00006B

00006C

00006D

00006E

00006F

000070

000071

000072

000073

000074

000075

000076

000077

000078

000079

00007A

00007B

00007C

00007D

00007E

00007F

Timer A0 register

Timer A1 register

Timer A2 register

Timer A3 register

Timer A4 register

Timer B0 register

Timer B1 register

Timer B2 register

Timer A0 mode register

Timer A1 mode register

Timer A2 mode register

Timer A3 mode register

Timer A4 mode register

Timer B0 mode register

Timer B1 mode register

Timer B2 mode register

Processor mode register 0

Processor mode register 1

Watchdog timer register

Watchdog timer frequency selection flag

Reserved area (Note)

Memory allocation control register

UART 2 transmit/receive mode register

UART 2 baud rate register

UART 2 transmission buffer register

UART 2 transmit/receive control register 0

UART 2 transmit/receive control register 1

UART 2 receive buffer register

Oscillation circuit control register 0

Port function control register

Serial transmit control register

Oscillation circuit control register 1

A-D/UART 2 trans./rece. interrupt control register

UART 0 transmission interrupt control register

UART 0 receive interrupt control register

UART 1 transmission interrupt control register

UART 1 receive interrupt control register

Timer A0 interrupt control register

Timer A1 interrupt control register

Timer A2 interrupt control register

Timer A3 interrupt control register

Timer A4 interrupt control register

Timer B0 interrupt control register

Timer B1 interrupt control register

Timer B2 interrupt control register

INT

0

interrupt control register

INT

1

interrupt control register

INT

2

/Key input interrupt control register

Note. Do not write to this address.

Fig. 2 Location of internal peripheral devices and interrupt control registers

6

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

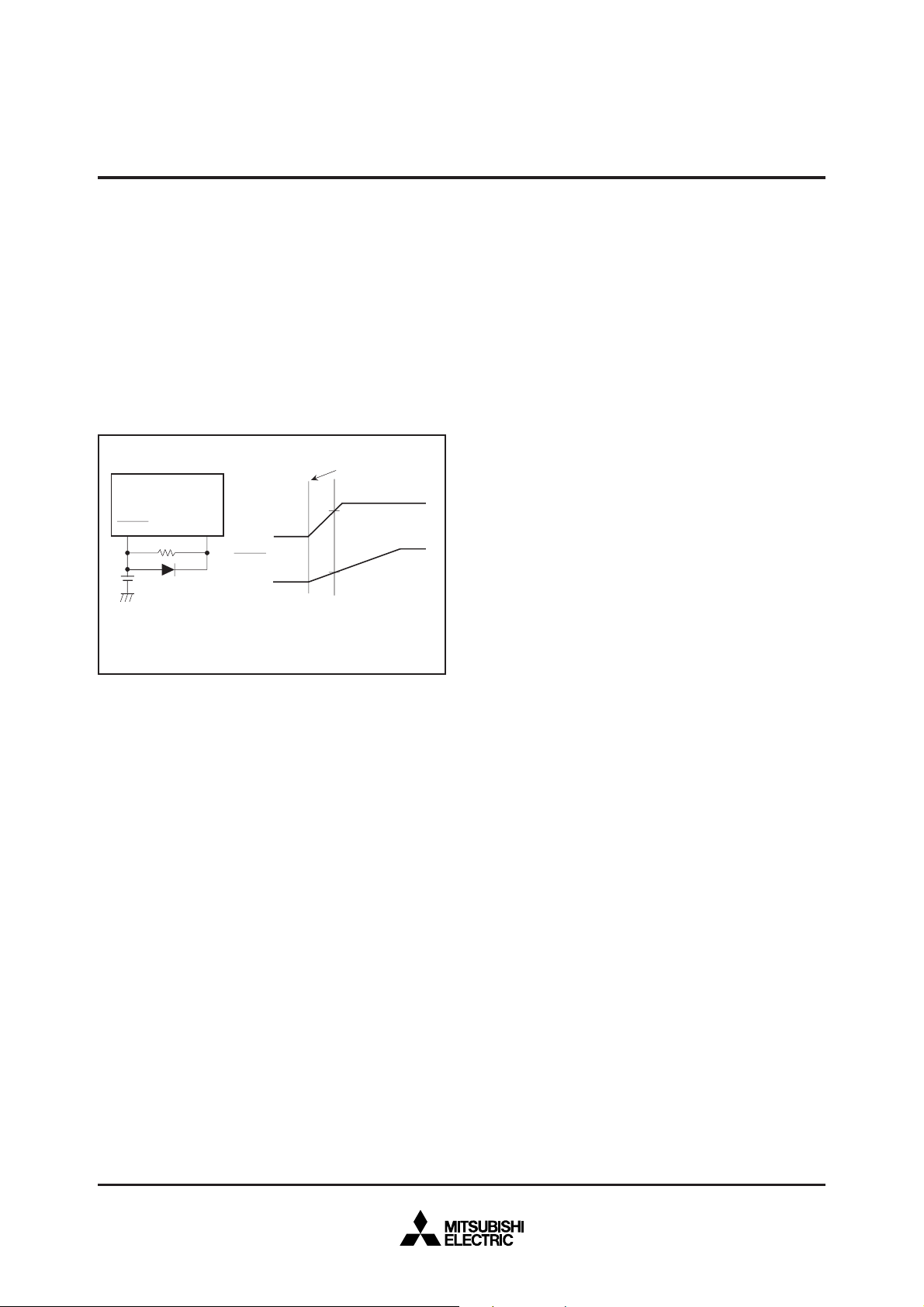

RESET CIRCUIT

The microcomputer is released from the reset state when the RESET

_____

pin is returned to “H” level after holding it at “L” level with the power

source voltage at 2.7 – 5.5 V. Program execution starts at the address

formed by setting address A

of address FFFF

16, and A7 – A0 to the contents of address FFFE16.

23 – A16 to 0016, A15 – A8 to the contents

Figure 3 shows an example of a reset circuit. When the stabilized

clock is input from the external to the main-clock oscillation circuit,

the reset input voltage must be 0.55 V or less when the power source

voltage reaches 2.7 V. When a resonator/oscillator is connected to

the main-clock oscillation circuit, change the reset input voltage from

“L” to “H” after the main-clock oscillation is fully stabilized.

Power on

2.7V

0.55V

RESET

V

CC

V

CC

0V

RESET

0V

Note. In this case, stabilized clock is input from the

external to the main-clock oscillation circuit.

Perform careful evalvation at the system design

level before using.

Fig. 3 Example of a reset circuit

7

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

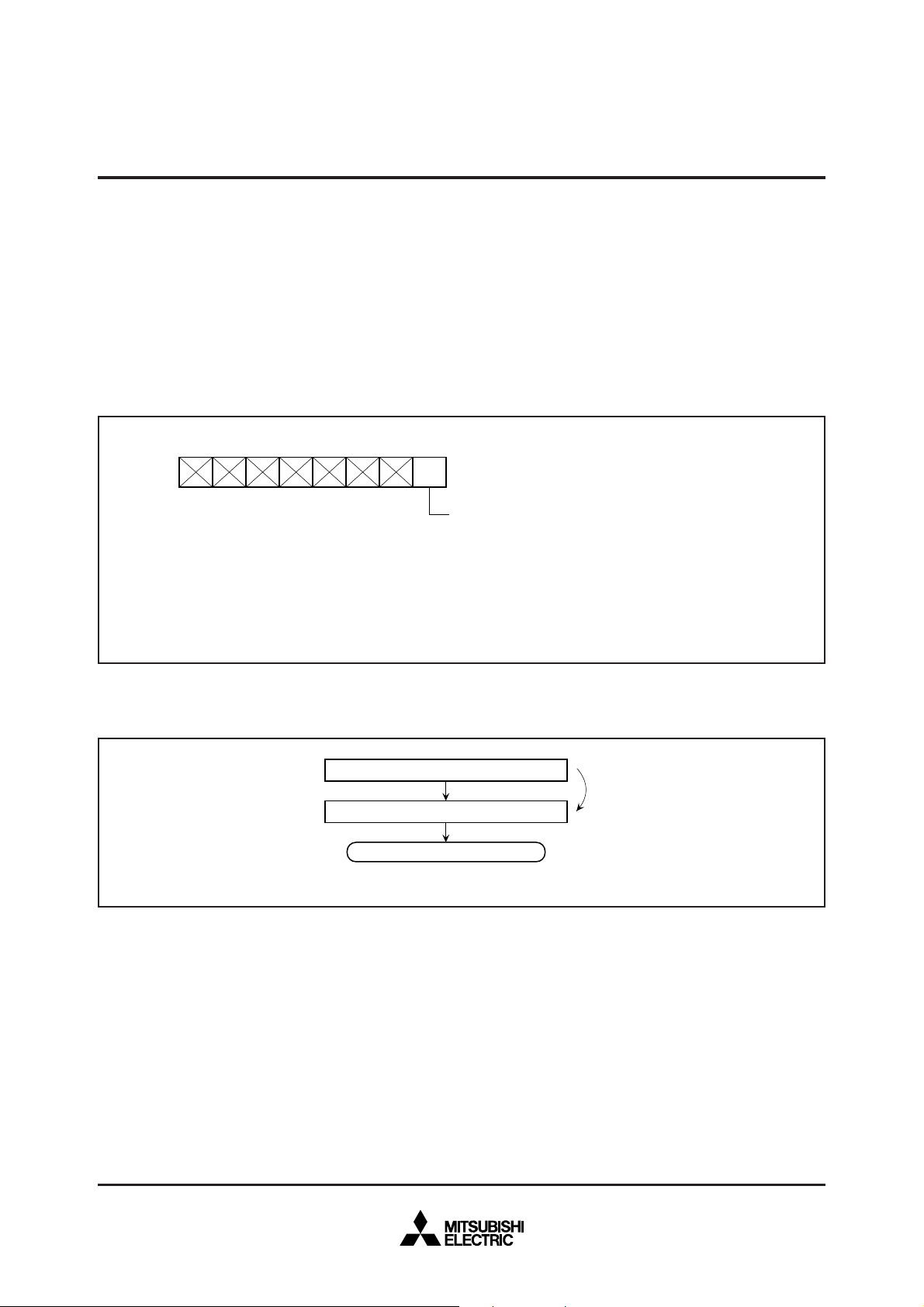

ROM AREA MODIFICATION FUNCTION

The internal ROM size and its address area of the M37736M4LXXXHP

can be modified by the memory allocation control register’s bit 0 shown

in Figure 4.

Figure 6 shows the memory allocation in which the internal ROM

size and its address area are modified.

Make sure to write data in the memory allocation control register as

the flow shown in Figure 5.

This ROM area modification function is valid in memory expansion

mode and single-chip mode.

Table 1 shows the relationship between memory allocation selection

76543210

ML

Note. Write to the memory allocation control register as the flow shown in Figure 5.

bits and address corresponding to chip-select signals CS0 and CS1

in the external bus mode B.

When ordering a mask ROM, Mitsubishi Electric corp. produces the

mask ROM using the data within 32 Kbytes (addresses 008000

00FFFF

16). It is regardless of the selected ROM size (refer to MASK

ROM ORDER CONFIRMATION FORM.) Therefore, program “FF

to the addresses out of the selected ROM area in the EPROM which

you tender when ordering a mask ROM.

Address 00FFFF

16 of this microcomputer corresponds to the lowest

address of the EPROM which you tender.

0

Memory allocation control register

Address

63

16

Memory allocation selection bit

ROM size (ROM area)

0 : 32 Kbytes (addresses 008000

1 : 16 Kbytes (addresses 00C000

16

– 00FFFF16)

16

– 00FFFF16)

___ ___

16 –

16”

Fig. 4 Bit configuration of memory allocation control register

Writing data “5516” (LDM instruction)

Writing data “0016” or “0116” (LDM instruction)

• How to write in memory allocation control register

Fig. 5 How to write data in memory allocation control register

0

selection bit

ML

Next instruction

8

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

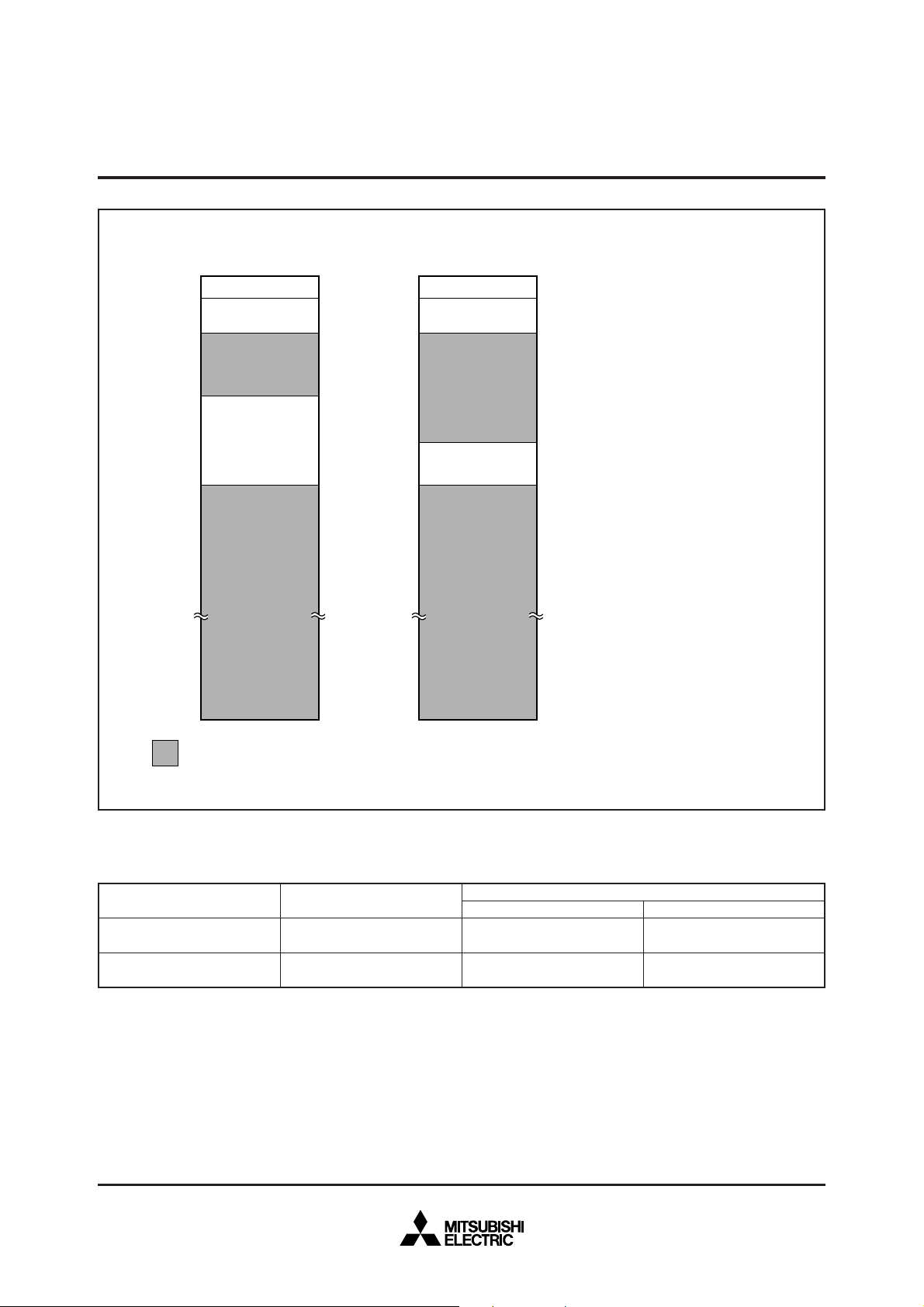

0

) = (0) (ML0) = (1)

(ML

ROM size : 32 kbytes ROM size : 16 Kbytes

000000

00007F

000080

00087F

008000

16

16

16

16

16

SFR

Internal RAM

2048 bytes

000000

00007F

000080

00087F

16

16

16

16

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

SFR

Internal RAM

2048 bytes

Internal ROM

00C000

00FFFF

010000

FFFFFF

32 Kbytes

16

16

16

00FFFF

010000

FFFFFF

16

16

16

16

Internal ROM

16 Kbytes

: External memory area

16

Note. Banks 10

to FF16 cannot be accessed in the external bus mode B.

Fig. 6 Memory allocation (modification of internal ROM area by memory allocation selection bit)

Table 1. Relationship between memory allocation selection bits and addresses corresponding to chip-select signals CS0 and CS1 in external bus mode B

Memory allocation select bit

ML0

0

1

Internal ROM area

00800016 – 00FFFF16

00C00016 – 00FFFF16

00088016 – 007FFF16

00088016 – 007FFF16

___

CS0

___ ___

Access address

___

CS1

01000016 – 03FFFF16

00800016 – 00BFFF16

01000016 – 03FFFF16

ADDRESSING MODES

The M37736M4LXXXHP has 28 powerful addressing modes. Refer

to the MITSUBISHI SEMICONDUCTORS DATA BOOK SINGLECHIP 16-BIT MICROCOMPUTERS for the details of each addressing

mode.

MACHINE INSTRUCTION LIST

The M37736M4LXXXHP has 103 machine instructions. Refer to the

MITSUBISHI SEMICONDUCTORS DATA BOOK SINGLE-CHIP 16BIT MICROCOMPUTERS for details.

DATA REQUIRED FOR MASK ROM ORDERING

Please send the following data for mask orders.

(1) M37736M4LXXXHP mask ROM order confirmation form

(2) 100P6Q mark specification form (100P6D mark specification form

is substituted.)

(3) ROM data (EPROM 3 sets)

9

MITSUBISHI MICROCOMPUTERS

M37736M4LXXXHP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Conditions Ratings Unit

Vcc Power source voltage –0.3 to +7 V

AVcc Analog power source voltage –0.3 to +7 V

VI

Input voltage RESET, CNVss, BYTE –0.3 to +12 V

Input voltage P0

V

I

_____

0 – P07, P10 – P17, P20 – P27,

0 – P33, P40 – P47, P50 – P57,

P3

0 – P67, P70 – P77, P80 – P87,

P6

0 – P92, P100 – P107, VREF,

P9

XIN, BSEL

VO

Output voltage

P00 – P07, P10 – P17, P20 – P27,

0 – P33, P40 – P47, P50 – P57,

P3

0 – P67, P70 – P77, P80 – P87,

P6

P90 – P97, P100 – P107, XOUT, E

_

Pd Power dissipation Ta = 25 °C 200 mW

Topr Operating temperature –40 to +85 °C

stg Storage temperature –65 to +150 °C

T

RECOMMENDED OPERATING CONDITIONS (Vcc = 2.7 – 5.5 V, Ta = –40 to +85 °C, unless otherwise noted)

Symbol Parameter

IN) : Operating 2.7 5.5

Vcc Power source voltage

AVcc Analog power source voltage Vcc V

Vss Power source voltage 0V

AVss Analog power source voltage 0 V

High-level input voltage P0

V

VIH

VIH

IH

High-level input voltage P10 – P17, P20 – P27 (in single-chip mode)

High-level input voltage P1

P70 – P77, P80 – P87, P90 – P92, P100 – P107, XIN, RESET,

CNVss, BYTE, BSEL, XCIN (Note 3)

(in memory expansion mode and microprocessor mode)

Low-level input voltage P0

VIL

P70 – P77, P80 – P87, P90 – P92, P100 – P107, XIN, RESET,

CNVss, BYTE, BSEL, XCIN (Note 3)

VIL

VIL

Low-level input voltage P10 – P17, P20 – P27 (in single-chip mode)

Low-level input voltage P1

(in memory expansion mode and microprocessor mode)

High-level peak output current P0

IOH(peak)

High-level average output current P00 – P07, P10 – P17, P20 – P27, P30 – P33,

IOH(avg)

P4

Low-level peak output current P00 – P07, P10 – P17, P20 – P27, P30 – P33,

IOL(peak)

IOL(peak)

Low-level peak output current P44 – P47, P100 – P103

Low-level average output current P00 – P07, P10 – P17, P20 – P27, P30 – P33,

IOL(avg)

IOL(avg) Low-level average output current P44 – P47, P100 – P103 12 mA

f(XIN) Main-clock oscillation frequency (Note 4) 12 MHz

CIN) Sub-clock oscillation frequency 32.768 50 kHz

f(X

f(X

f(XIN) : Stopped, f(XCIN) = 32.768 kHz 2.7 5.5

0 – P07, P30 – P33, P40 – P47, P50 – P57, P60 – P67,

0 – P17, P20 – P27

0 – P07, P30 – P33, P40 – P47, P50 – P57, P60 – P67,

0 – P17, P20 – P27

0 – P07, P10 – P17, P20 – P27, P30 – P33,

0 – P47, P50 – P57, P60 – P67, P70 – P77,

P4

P80 – P87, P90 – P97, P100 – P107

0 – P47, P50 – P57, P60 – P67, P70 – P77,

P80 – P87, P90 – P97, P100 – P107

0 – P43, P54 – P57, P60 – P67, P70 – P77,

P4

P80 – P87, P90 – P97, P104 – P107

0 – P43, P50 – P57, P60 – P67, P70 – P77,

P4

P80 – P87, P90 – P97, P104 – P107

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

–0.3 to Vcc + 0.3 V

–0.3 to Vcc + 0.3 V

_____

_____

Min. Typ. Max.

Limits

0.8 Vcc

0.8 Vcc

0.5 Vcc

0

0

0

0.2Vcc

0.2Vcc

0.16Vcc

Vcc

Vcc

Vcc

–10

–5

10

16

Unit

V

V

V

V

V

V

V

mA

mA

mA

mA

mA

5

Notes 1. Average output current is the average value of a 100 ms interval.

2. The sum of I

the sum of I

the sum of I

the sum of I

3. Limits V

4. The maximum value of f(X

OL(peak) for ports P0, P1, P2, P3, P8, and P9 must be 80 mA or less,

OH(peak) for ports P0, P1, P2, P3, P8, and P9 must be 80 mA or less,

OL(peak) for ports P4, P5, P6, P7, and P10 must be 100 mA or less, and

OH(peak) for ports P4, P5, P6, P7, and P10 must be 80 mA or less.

IH and VIL for XCIN are applied when the sub clock external input selection bit = “1”.

IN) = 6 MHz when the main clock division selection bit = “1”.

10

Loading...

Loading...