Mitsubishi M37733MHBXXXFP Datasheet

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

DESCRIPTION

The M37733MHBXXXFP is a single-chip microcomputer using the

7700 Family core. This single-chip microcomputer has a CPU and a

bus interface unit. The CPU is a 16-bit parallel processor that can be

an 8-bit parallel processor, and the bus interface unit enhances the

memory access efficiency to execute instructions fast. This

microcomputer also includes a 32 kHz oscillation circuit, in addition

to the ROM, RAM, multiple-function timers, serial I/O, A-D converter,

and so on.

FEATURES

●Number of basic instructions .................................................. 103

●Memory size ROM............................................... 124 Kbytes

RAM ................................................3968 bytes

●Instruction execution time

The fastest instruction at 25 MHz frequency ...................... 160 ns

●Single power supply ...................................................... 5 V ± 10%

●Low power dissipation (at 25 MHz frequency)

............................................47.5 mW (Typ.)

●Interrupts ............................................................ 19 types, 7 levels

●Multiple-function 16-bit timer ................................................. 5 + 3

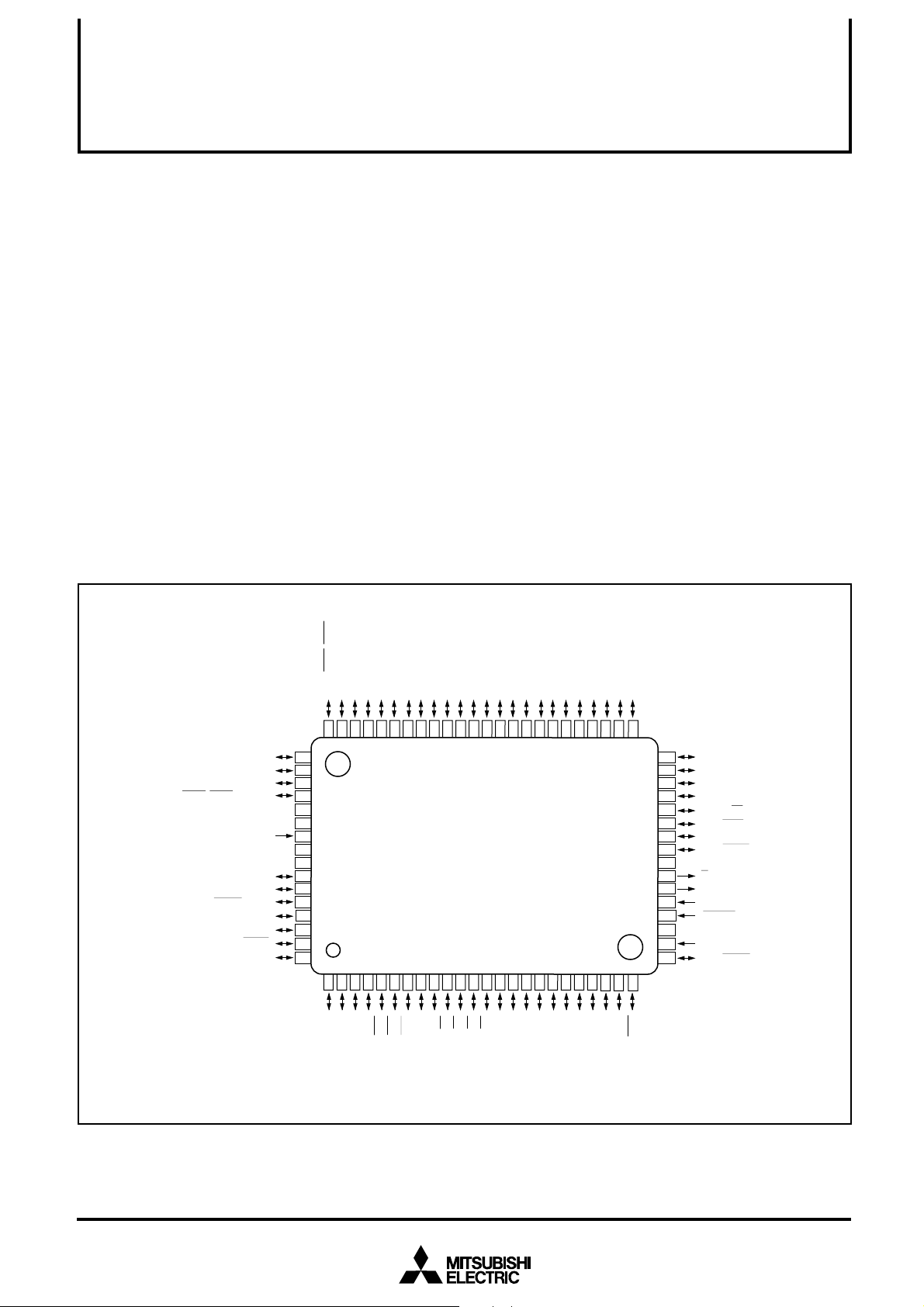

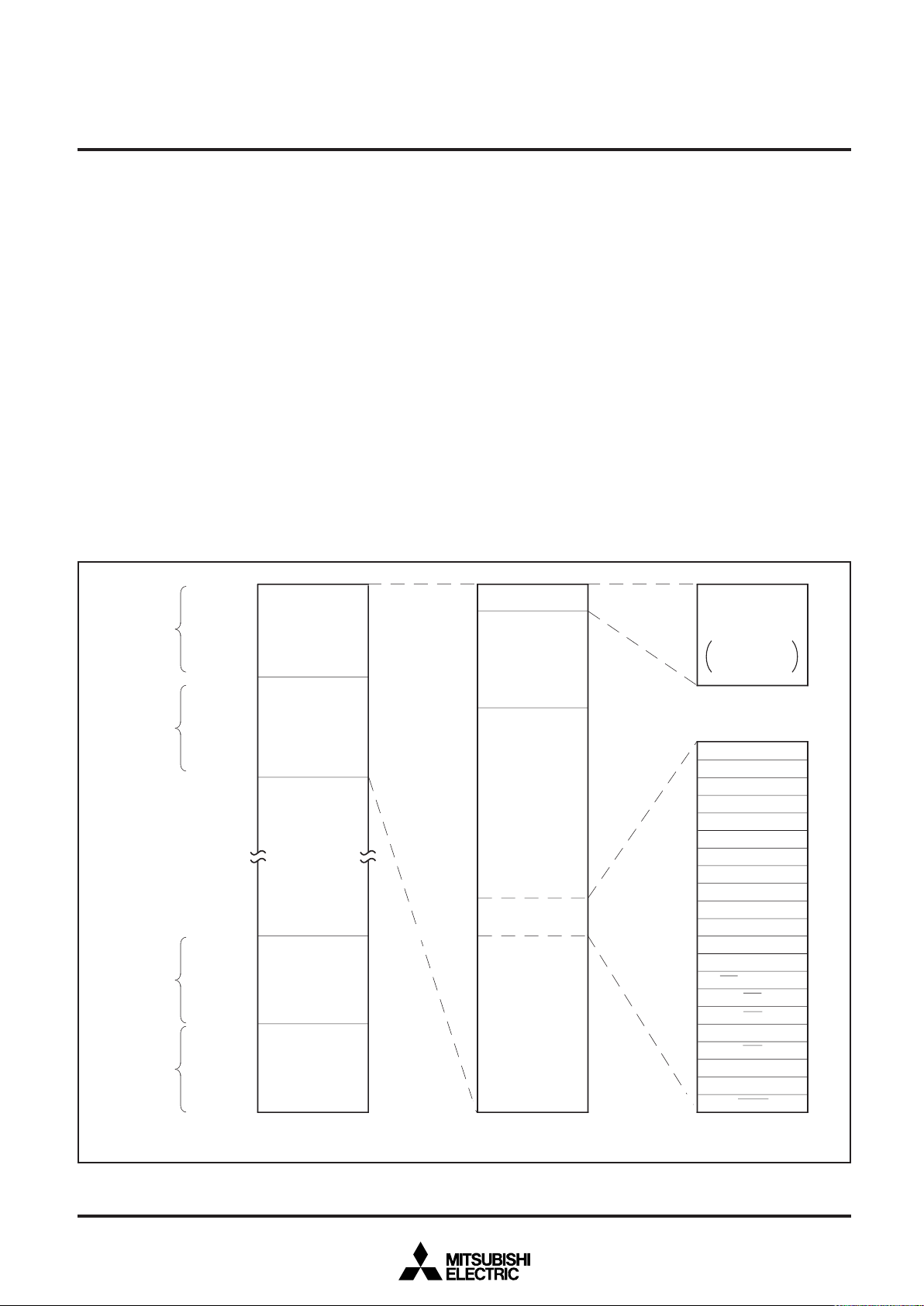

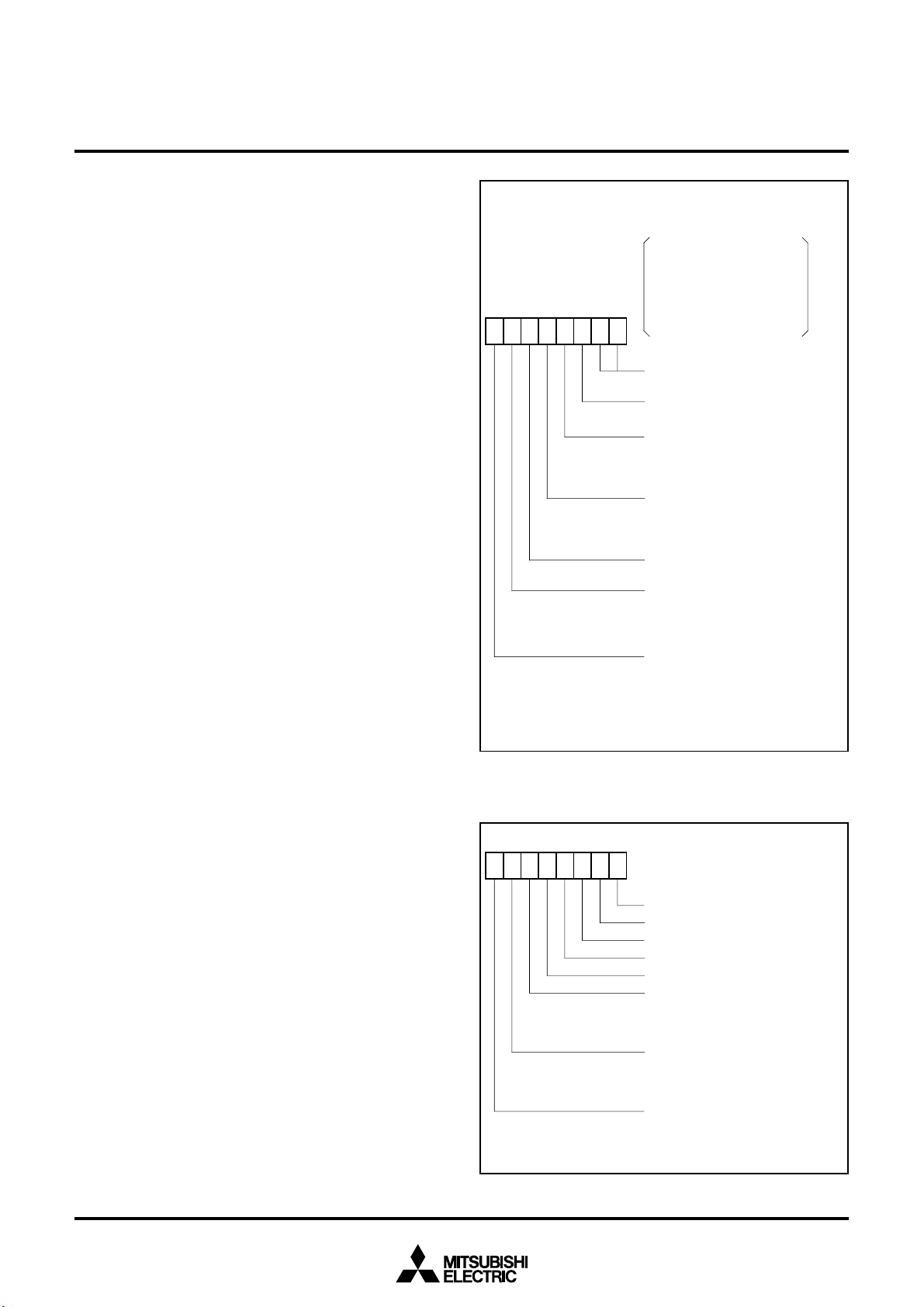

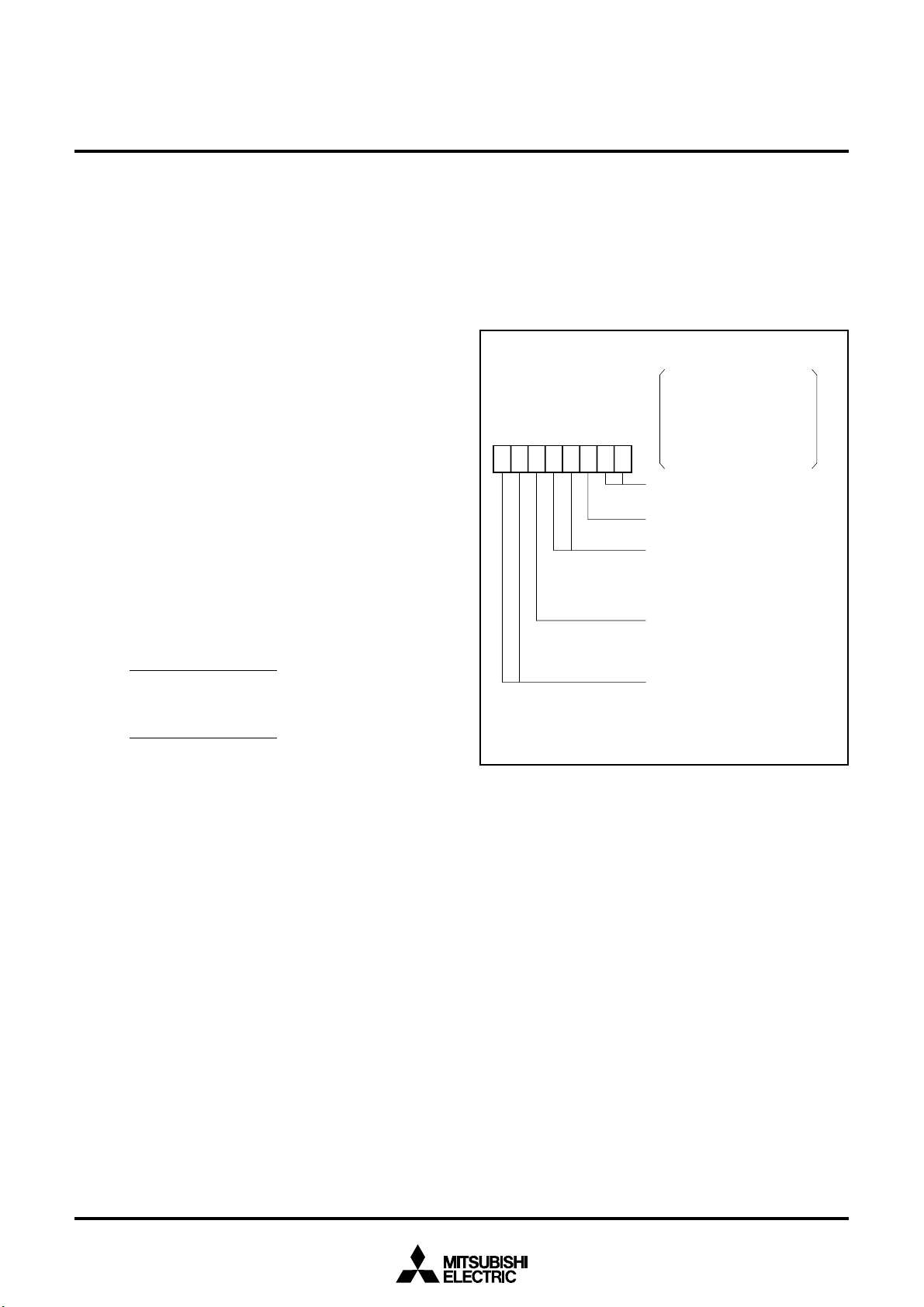

PIN CONFIGURATION (TOP VIEW)

1

RTS

/

1

1

1

1

D

D

CTS

/

4

P8

/CLK

5

P8

X

/R

6

P8

X

/T

7

P8

0

A

/

0

P0

1

A

/

1

P0

2

A

/

2

P0

3

A

/

3

P0

●Serial I/O (UART or clock synchronous) ..................................... 3

●10-bit A-D converter ............................................ 8-channel inputs

●12-bit watchdog timer

●Programmable input/output

(ports P0, P1, P2, P3, P4, P5, P6, P7, P8) ............................... 68

●Clock generating circuit ........................................ 2 circuits built-in

APPLICATION

Control devices for general commercial equipment such as office

automation, office equipment, and so on.

Control devices for general industrial equipment such as

communication equipment, and so on.

4

A

/

4

P0

5

A

/

5

P0

6

/A

6

P0

7

/A

7

P0

8

/D

8

/A

0

P1

9

/D

9

/A

1

P1

10

/D

10

/A

2

P1

11

/D

11

/A

3

P1

12

/D

12

/A

4

P1

13

/D

13

/A

5

P1

14

/D

14

/A

6

P1

15

/D

15

/A

7

P1

0

/D

16

/A

0

P2

1

/D

17

/A

1

P2

2

/D

18

/A

2

P2

3

/D

19

/A

3

P2

P83/TXD0

P82/RXD0/CLKS0

P81/CLK0

P80/CTS0/RTS0/CLKS1

VCC

AVCC

VREF

AVSS

VSS

P77/AN7/XcIN

P76/AN6/XcOUT

P75/AN5/ADTRG/TxD2

P74/AN4/RxD2

P73/AN3/CLK2

P72/AN2/CTS2

P71/AN1

51

14

IN

/TA1

3

P5

50

15

OUT

/TA1

2

P5

49

16

IN

/TA0

1

P5

48

17

OUT

/TA0

0

P5

47

46

18

19

6

7

P4

P4

64

61

62

60

63

65

66

67

6

8

69

70

71

72

73

74

75

76

77

78

79

80

2

5

4

3

1

SUB

φ

/

IN

/TB2

7

IN

/TB1

6

P6

IN

/TB0

5

P6

2

NT

/I

4

P6

0

/AN

0

P7

P6

56

59

58

54

57

55

53

M37733MHBXXXFP

12

9

7

0

NT

/I

2

P6

8

IN

/TA4

1

P6

OUT

/TA4

0

P6

10

3

KI

/

IN

/TA3

7

P5

11

2

KI

/

OUT

/TA3

6

P5

1

KI

/

IN

/TA2

5

P5

6

1

NT

/I

3

P6

52

13

0

KI

/

OUT

/TA2

4

P5

42

41

43

44

45

40

P24/A20/D4

39

P25/A21/D5

38

P26/A22/D6

37

P27/A23/D7

36

P30/R/W

35

P31/BHE

34

P32/ALE

33

P33/HLDA

32

Vss

31

E

30

XOUT

29

X

IN

28

RESET

27

CNVSS

26

BYTE

25

P40/HOLD

21

22

4

P4

3

P4

23

1

φ

/

2

P4

24

RDY

/

1

P4

20

5

P4

Outline 80P6N-A

0

PRELIMINARY

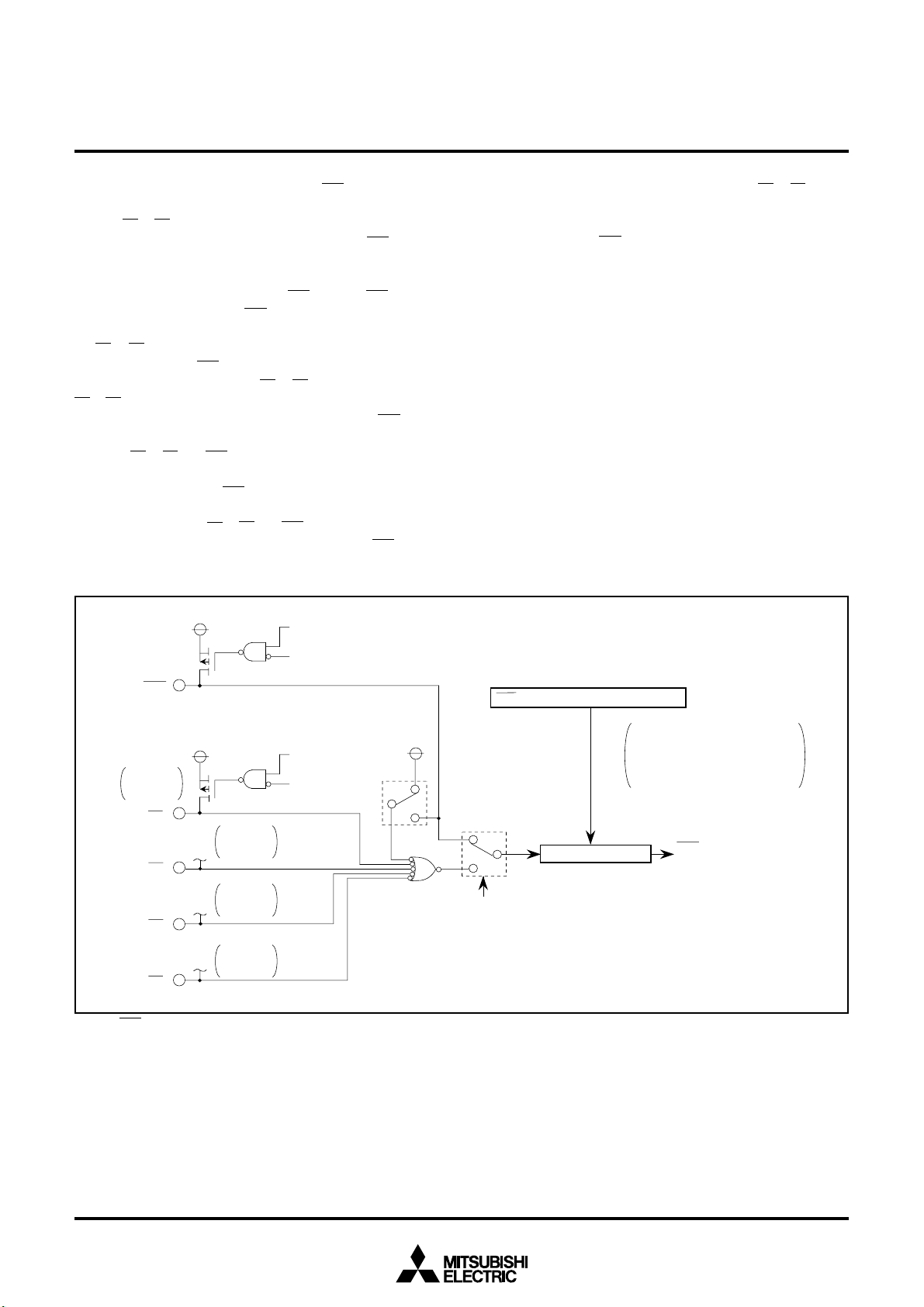

X

IN

X

OUT

E

RESET

Reset input

V

REF

P8(8) P7(8) P5(8)P6(8) P4(8) P3(4)

P2(8)

P1(8)

CNVss

BYTE

P0(8)

UART1(9)

UART0(9)

AV

SS

(0V)

AV

CC

(0V)

V

SS

V

CC

A-D Converter(10)

X

CIN

X

COUT

X

CIN

X

COUT

Clock input Clock output

Enable output

Reference

voltage input

External data bus width

selection input

Clock Generating Circuit

Instruction Register(8)

Arithmetic Logic

Unit(16)

Accumulator A(16)

Accumulatcr B(16)

Index Register X(16)

Index Register Y(16)

Stack Pointer S(16)

Direct Page Register DPR(16)

Processor Status Register PS(11)

Input Butter Register IB(16)

Data Bank Register DT(8)

Program Bank Register PG(8)

Program Counter PC(16)

Incrementer/Decrementer(24)

Data Address Register DA(24)

Program Address Register PA(24)

Incrementer(24)

Instruction Queue Buffer Q

2

(8)

Instruction Queue Buffer Q

1

(8)

Instruction Queue Buffer Q

0

(8)

Data Buffer DB

L

(8)

Data Buffer DB

H

(8)

ROM

124 Kbytes

RAM

3968 bytes

Timer TA3(16)

Timer TA4(16)

Timer TA2(16)

Timer TA1(16)

Timer TA0(16)

Watchdog Timer

Timer TB2(16)

Timer TB1(16)

Timer TB0(16)

Address Bus

Data Bus(Odd)

Data Bus(Even)

Input/Output

port P8

Input/Output

port P7

Input/Output

port P6

Input/Output

port P5

Input/Output

port P4

Input/Output

port P3

Input/Output

port P2

Input/Output

port P1

Input/Output

port P0

UART2(9)

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

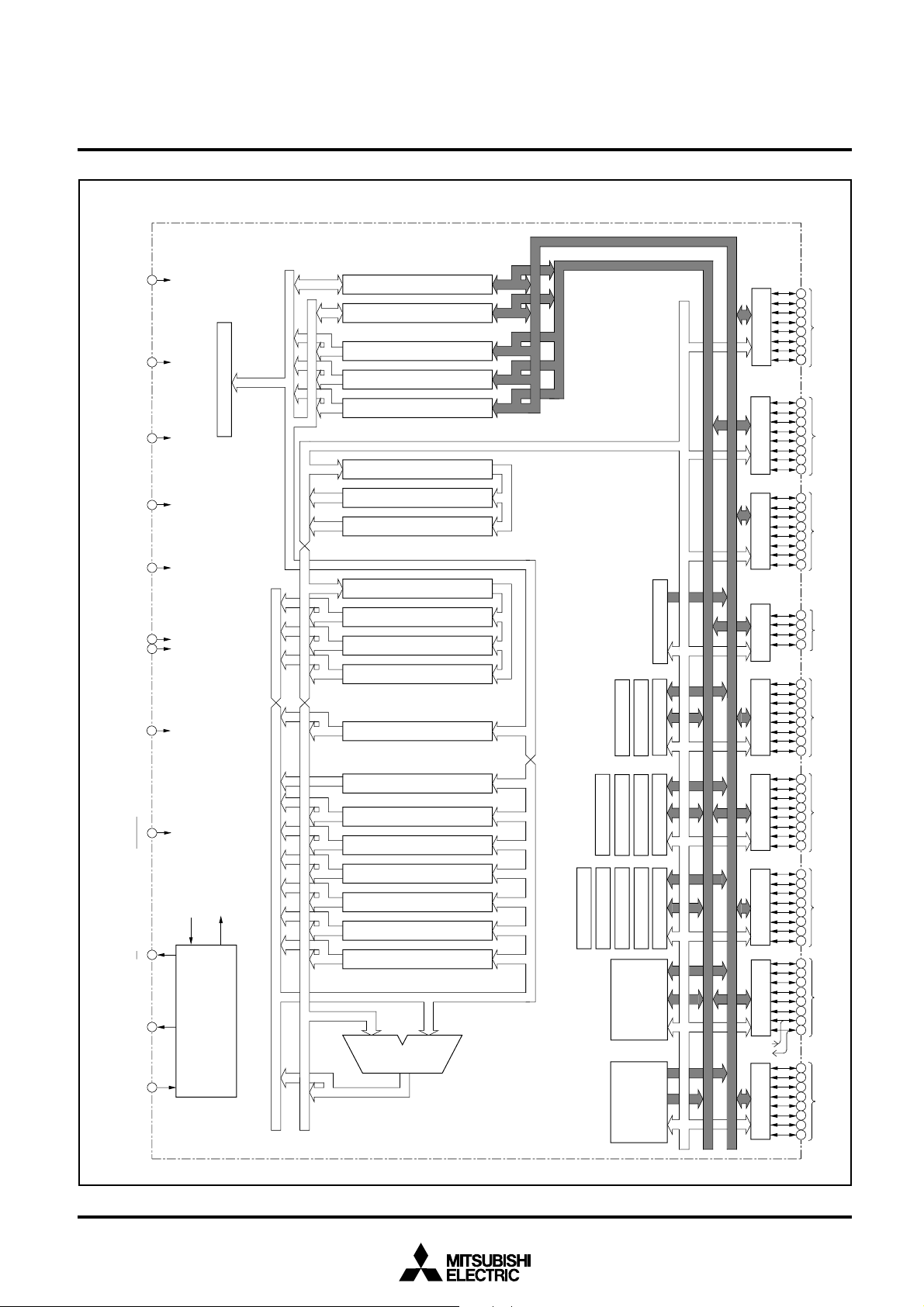

M37733MHBXXXFP BLOCK DIAGRAM

2

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

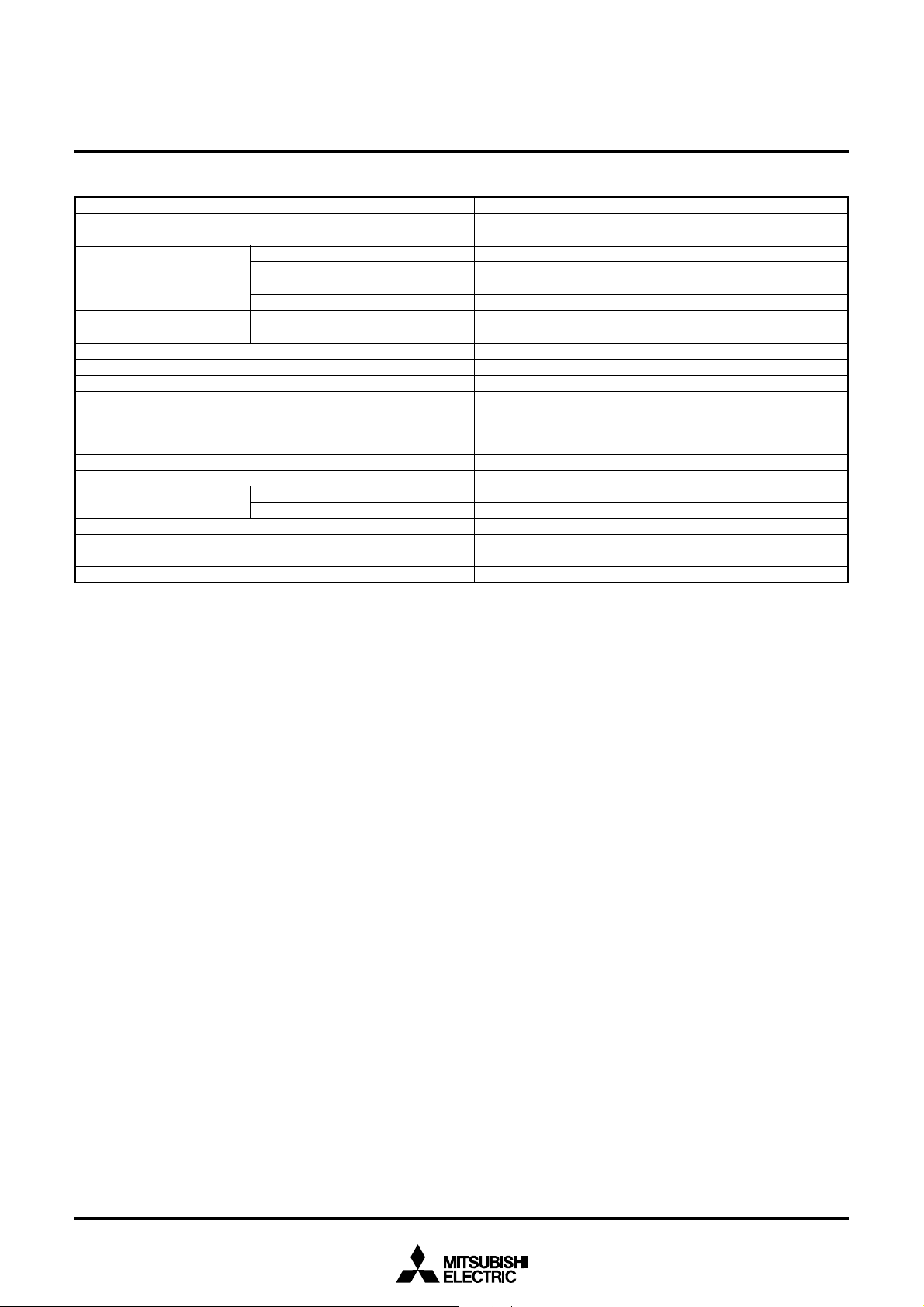

FUNCTIONS OF M37733MHBXXXFP

Parameter Functions

Number of basic instructions 103

Instruction execution time 160 ns (the fastest instruction at external clock 25 MHz frequency)

Memory size

Input/Output ports

Multi-function timers

Serial I/O (UART or clock synchronous serial I/O) ✕ 3

A-D converter 10-bit ✕ 1 (8 channels)

Watchdog timer 12-bit ✕ 1

Interrupts

Clock generating circuit

Supply voltage 5 V ± 10%

Power dissipation 47.5 mW (at external clock 25 MHz frequency)

Input/Output characteristic

Memory expansion Maximum 16 Mbytes

Operating temperature range –20 to 85 °C

Device structure CMOS high-performance silicon gate process

Package 80-pin plastic molded QFP (80P6N-A)

ROM 124 Kbytes

RAM 3968 bytes

P0 – P2, P4 – P8 8-bit ✕ 8

P3 4-bit ✕ 1

TA0, TA1, TA2, TA3, TA4 16-bit ✕ 5

TB0, TB1, TB2 16-bit ✕ 3

3 external types, 16 internal types

Each interrupt can be set to the priority level (0 – 7.)

2 circuits built-in (externally connected to a ceramic resonator or a

quartz-crystal oscillator)

Input/Output voltage 5 V

Output current 5 mA

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

3

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

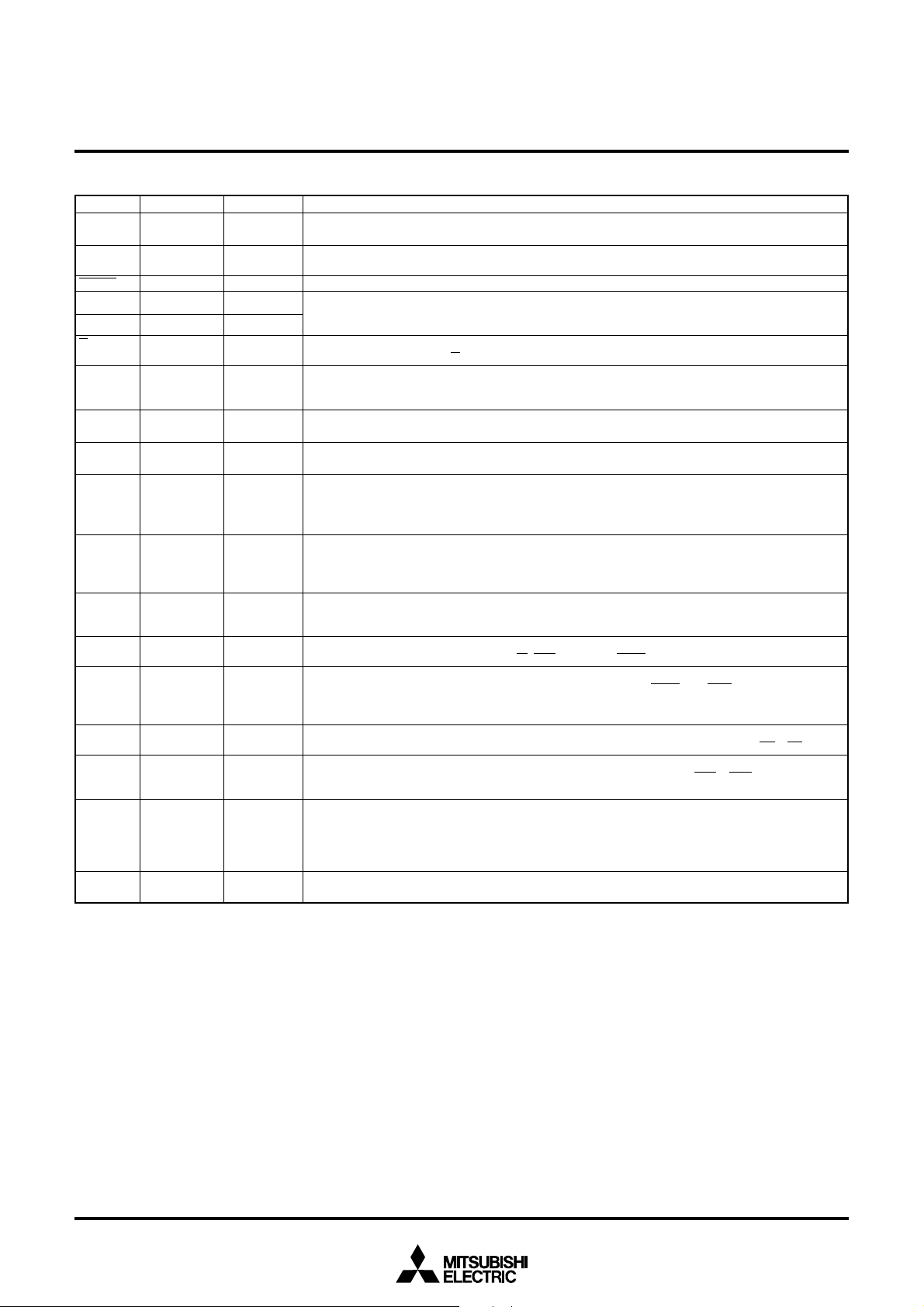

PIN DESCRIPTION

Pin Name Input/Output Functions

Vcc, Power source Apply 5 V ± 10% to Vcc and 0 V to Vss.

Vss

CNVss CNVss input Input This pin controls the processor mode. Connect to Vss for the single-chip mode and the memory

RESET Reset input Input When “L” level is applied to this pin, the microcomputer enters the reset state.

XIN Clock input Input

XOUT Clock output Output

E Enable output Output This pin functions as the enable signal output pin which indicates the access status in the internal

BYTE

External data

Input In the memory expansion mode or the microprocessor mode, this pin determines whether the

bus width

selection input

AVcc, Analog power Power source input pin for the A-D converter. Externally connect AVcc to Vcc and AVss to Vss.

AVss source input

VREF Reference Input This is reference voltage input pin for the A-D converter.

voltage input

P0

0 – P07 I/O port P0 I/O In the single-chip mode, port P0 becomes an 8-bit I/O port. An I/O direction register is available so

P1

0 – P17 I/O port P1 I/O In the single-chip mode, these pins have the same functions as port P0. When the BYTE pin is set

P20 – P27 I/O port P2 I/O In the single-chip mode, these pins have the same functions as port P0. In the memory expansion

P3

0 – P33 I/O port P3 I/O In the single-chip mode, these pins have the same function as port P0. In the memory expansion

P4

0 – P47 I/O port P4 I/O In the single-chip mode, these pins have the same functions as port P0. In the memory expansion

P5

0 – P57 I/O port P5 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P6

0 – P67 I/O port P6 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P7

0 – P77 I/O port P7 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins function as

P80 – P87 I/O port P8 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

expansion mode, and to Vcc for the microprocessor mode.

These are pins of main-clock generating circuit. Connect a ceramic resonator or a quartzcrystal oscillator between X

IN and XOUT. When an external clock is used, the clock source should

be connected to the XIN pin, and the XOUT pin should be left open.

bus. When output level of E signal is “L”, data/instruction read or data write is performed.

external data bus has an 8-bit width or a 16-bit width. The data bus has a 16-bit width when “L”

signal is input and an 8-bit width when “H” signal is input.

that each pin can be programmed for input or output. These ports are in the input mode when

reset.

In the memory expansion mode or the microprocessor mode, these pins output address (A0 – A7).

to “L” in the memory expansion mode or the microprocessor mode and external data bus has a

16-bit width, high-order data (D8 – D15) is input/output or an address (A8 – A15) is output. When

the BYTE pin is “H” and an external data bus has an 8-bit width, only address (A8 – A15) is output.

mode or the microprocessor mode, low-order data (D0 – D7) is input/output or an address

(A0 – A7) is output .

mode or the microprocessor mode, R/W, BHE, ALE, and HLDA signals are output.

mode or the microprocessor mode, P40, P41 and P42 become HOLD and RDY input pins, and a

clock

φ

1 output pin, respectively. Functions of the other pins are the same as in the single-chip

mode. However, in the memory expansion mode, P42 can be selected as an I/O port.

function as I/O pins for timers A0 to A3 and input pins for key input interrupt input (KI0 – KI3 ).

function as I/O pins for timer A4, input pins for external interrupt input (INT0 – INT2) and input pins

for timers B0 to B2. P67 also functions as sub-clock φ SUB output pin.

input pins for A-D converter. P72 to P75 also function as I/O pins for UART2. Additionally, P76 and

P77 have the function as the output pin (XCOUT) and the input pin (XCIN) of the sub-clock (32 kHz)

oscillation circuit, respectively. When P76 and P77 are used as the XCOUT and XCIN pins, connect

a resonator or an oscillator between the both.

function as I/O pins for UART 0 and UART 1.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

4

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

BASIC FUNCTION BLOCKS

The M37733MHBXXXFP contains the following peripheral devices

on a single chip: ROM, RAM, CPU, bus interface unit, timers, serial

I/O, A-D converter, I/O ports, clock generating circuit and others. Each

of these devices is described below.

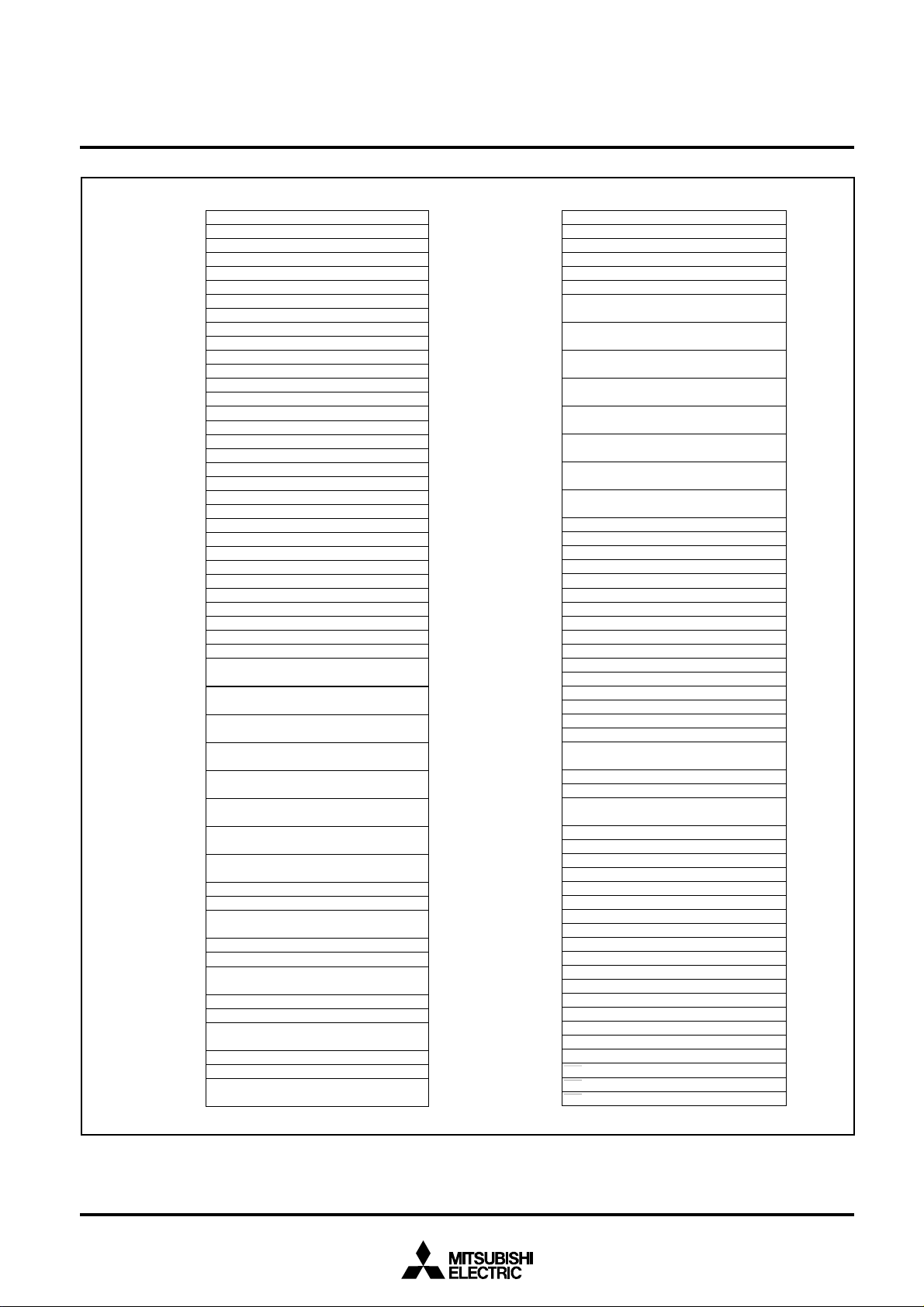

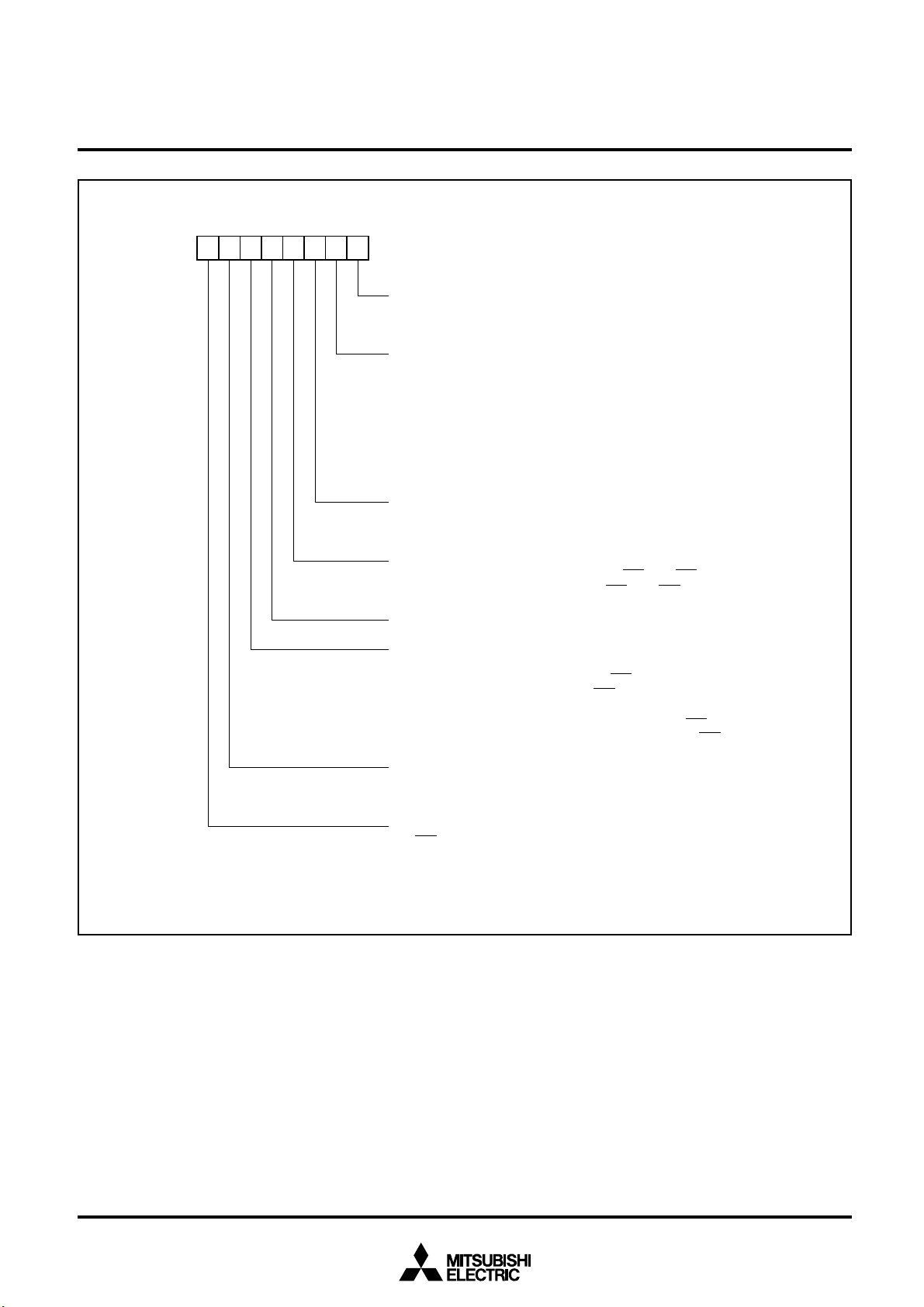

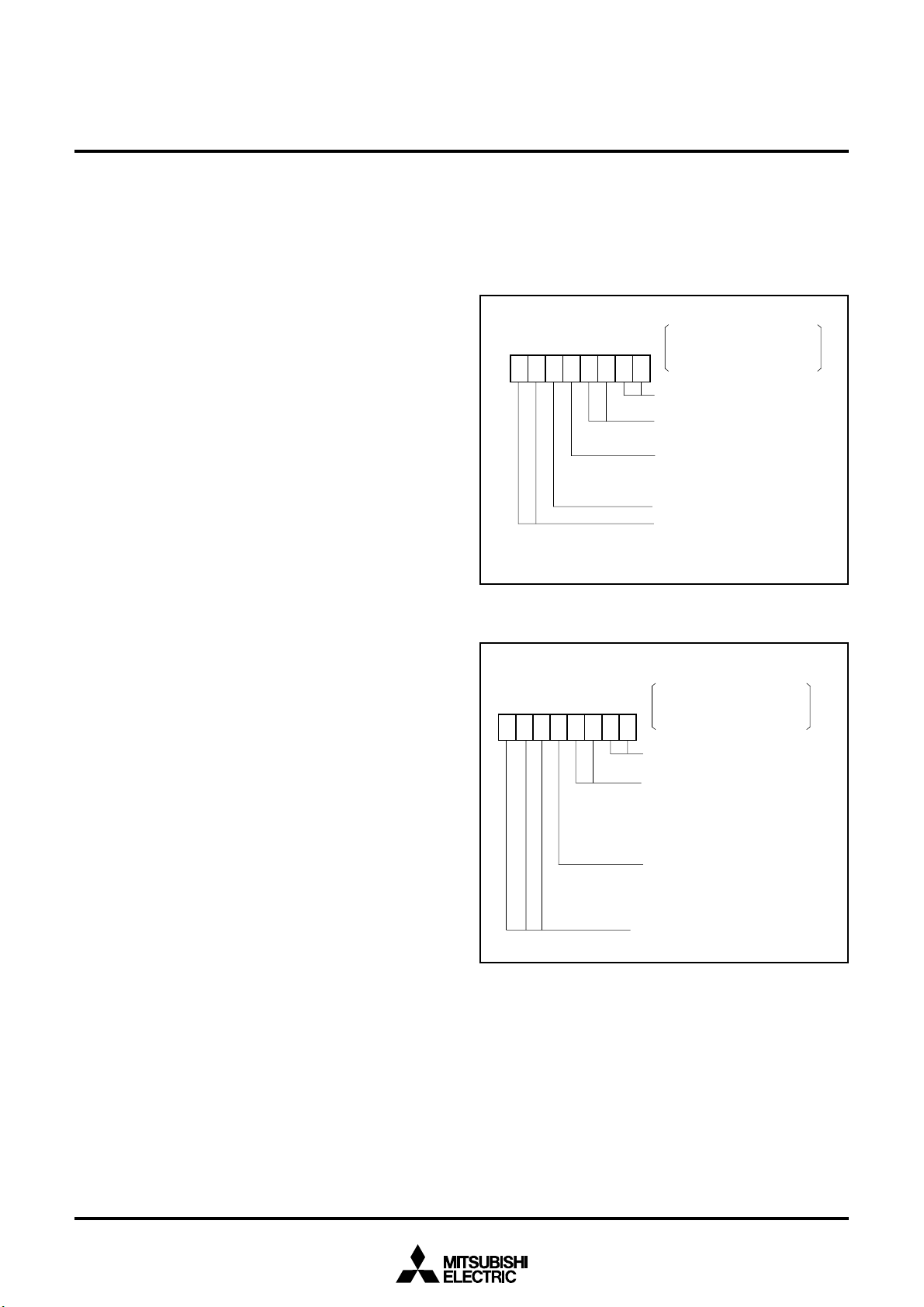

MEMORY

The memory map is shown in Figure 1. The address space has a

capacity of 16 Mbytes and is allocated to addresses from 0

FFFFFF

16. The address space is divided by 64-Kbyte unit called bank.

The banks are numbered from 0

16 to FF16.

Built-in ROM, RAM and control registers for internal peripheral devices

are assigned to banks 0

The 124-Kbyte area from addresses 1000

ROM. Addresses FFD6

16 and 116.

16 to 1FFFF16 is the built-in

16 to FFFF16 are the RESET and interrupt

vector addresses and contain the interrupt vectors. Refer to the section

on interrupts for details.

The 3968-byte area allocated to addresses from 80

16 to FFF16 is the

built-in RAM. In addition to storing data, the RAM is used as stack

during a subroutine call or interrupts.

000000

16

Bank 0

16

00FFFF

16

010000

16

Bank 1

16

01FFFF

16

• • • • • • • • • • • • • • • • • • •

FE0000

16

Bank FE

Bank FF

16

FEFFFF

16

FF0000

16

16

FFFFFF

16

16 to

000000

00007F

000080

000FFF

001000

00FFD6

00FFFF

01FFFF

Peripheral devices such as I/O ports, A-D converter, serial I/O, timer,

and interrupt control registers are allocated to addresses from 0

7F

16.

Additionally, the internal ROM and RAM area can be modified by

software. Refer to the section on ROM area modification function for

details.

A 256-byte direct page area can be allocated anywhere in bank 0

by using the direct page register (DPR). In the direct page addressing

mode, the memory in the direct page area can be accessed with two

words. Hence program steps can be reduced.

16

16

16

000000

16

Internal peripheral

devices

control registers

Internal RAM

3968 bytes

00007F

16

16

refer to Fig. 2 for

detail information

16

Interrupt vector table

00FFD6

16

16

16

16

Internal ROM

124 Kbytes

00FFFE

A-D/UART2 trans./

UART1 transmission

UART1 receive

UART0 transmission

UART0 receive

Timer B2

Timer B1

Timer B0

Timer A4

Timer A3

Timer A2

Timer A1

Timer A0

INT

Watchdog

BRK instruction

Zero divide

16

2

/Key input

1

INT

0

INT

timer

DBC

RESET

rece.

16 to

16

Note. Internal ROM and RAM area can be modified. (Refer to the section on ROM area modification function.)

Fig. 1 Memory map

5

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Address (Hexadecimal notation)

000000

000001

000002

000003

000004

000005

000006

000007

000008

000009

00000A

00000B

00000C

00000D

00000E

00000F

000010

000011

000012

Port P0 register

Port P1 register

Port P0 direction register

Port P1 direction register

Port P2 register

Port P3 register

Port P2 direction register

Port P3 direction register

Port P4 register

Port P5 register

Port P4 direction register

Port P5 direction register

Port P6 register

Port P7 register

Port P6 direction register

Port P7 direction register

Port P8 register

000013

000014

Port P8 direction register

000015

000016

000017

000018

000019

00001A

00001B

00001C

00001D

00001E

00001F

000020

000021

000022

000023

000024

000025

000026

000027

000028

000029

00002A

00002B

00002C

00002D

00002E

00002F

000030

000031

000032

000033

000034

000035

000036

000037

000038

000039

00003A

00003B

00003C

00003D

00003E

00003F

Reserved area (Note)

Reserved area (Note)

A-D control register 0

A-D control register 1

A-D register 0

A-D register 1

A-D register 2

A-D register 3

A-D register 4

A-D register 5

A-D register 6

A-D register 7

UART 0 transmit/receive mode register

UART 0 baud rate register (BRG0)

UART 0 transmission buffer register

UART 0 transmit/receive control register 0

UART 0 transmit/receive control register 1

UART 0 receive buffer register

UART 1 transmit/receive mode register

UART 1 baud rate register (BRG1)

UART 1 transmission buffer register

UART 1 transmit/receive control register 0

UART 1 transmit/receive control register 1

UART 1 receive buffer register

Address (Hexadecimal notation)

000040

Count start flag

000041

000042

One-shot start flag

000043

000044

Up-down flag

000045

000046

000047

000048

000049

00004A

00004B

00004C

00004D

00004E

00004F

000050

000051

000052

000053

000054

000055

000056

000057

000058

000059

00005A

00005B

00005C

00005D

00005E

00005F

000060

000061

000062

000063

000064

000065

000066

000067

000068

000069

00006A

00006B

00006C

00006D

00006E

00006F

000070

000071

000072

000073

000074

000075

000076

000077

000078

000079

00007A

00007B

00007C

00007D

00007E

00007F

Timer A0 register

Timer A1 register

Timer A2 register

Timer A3 register

Timer A4 register

Timer B0 register

Timer B1 register

Timer B2 register

Timer A0 mode register

Timer A1 mode register

Timer A2 mode register

Timer A3 mode register

Timer A4 mode register

Timer B0 mode register

Timer B1 mode register

Timer B2 mode register

Processor mode register 0

Processor mode register 1

Watchdog timer register

Watchdog timer frequency selection flag

Reserved area (Note)

Memory allocation control register

UART 2 transmit/receive mode register

UART 2 baud rate register (BRG2)

UART 2 transmission buffer register

UART 2 transmit/receive control register 0

UART 2 transmit/receive control register 1

UART 2 receive buffer register

Oscillation circuit control register 0

Port function control register

Serial transmit control register

Oscillation circuit control register 1

A-D/UART 2 trans./rece. interrupt control register

UART 0 transmission interrupt control register

UART 0 receive interrupt control register

UART 1 transmission interrupt control register

UART 1 receive interrupt control register

Timer A0 interrupt control register

Timer A1 interrupt control register

Timer A2 interrupt control register

Timer A3 interrupt control register

Timer A4 interrupt control register

Timer B0 interrupt control register

Timer B1 interrupt control register

Timer B2 interrupt control register

INT

0 interrupt control register

INT

1 interrupt control register

INT

2/Key input interrupt control register

Note. Do not write to this address.

Fig. 2 Location of internal peripheral devices and interrupt control registers

6

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

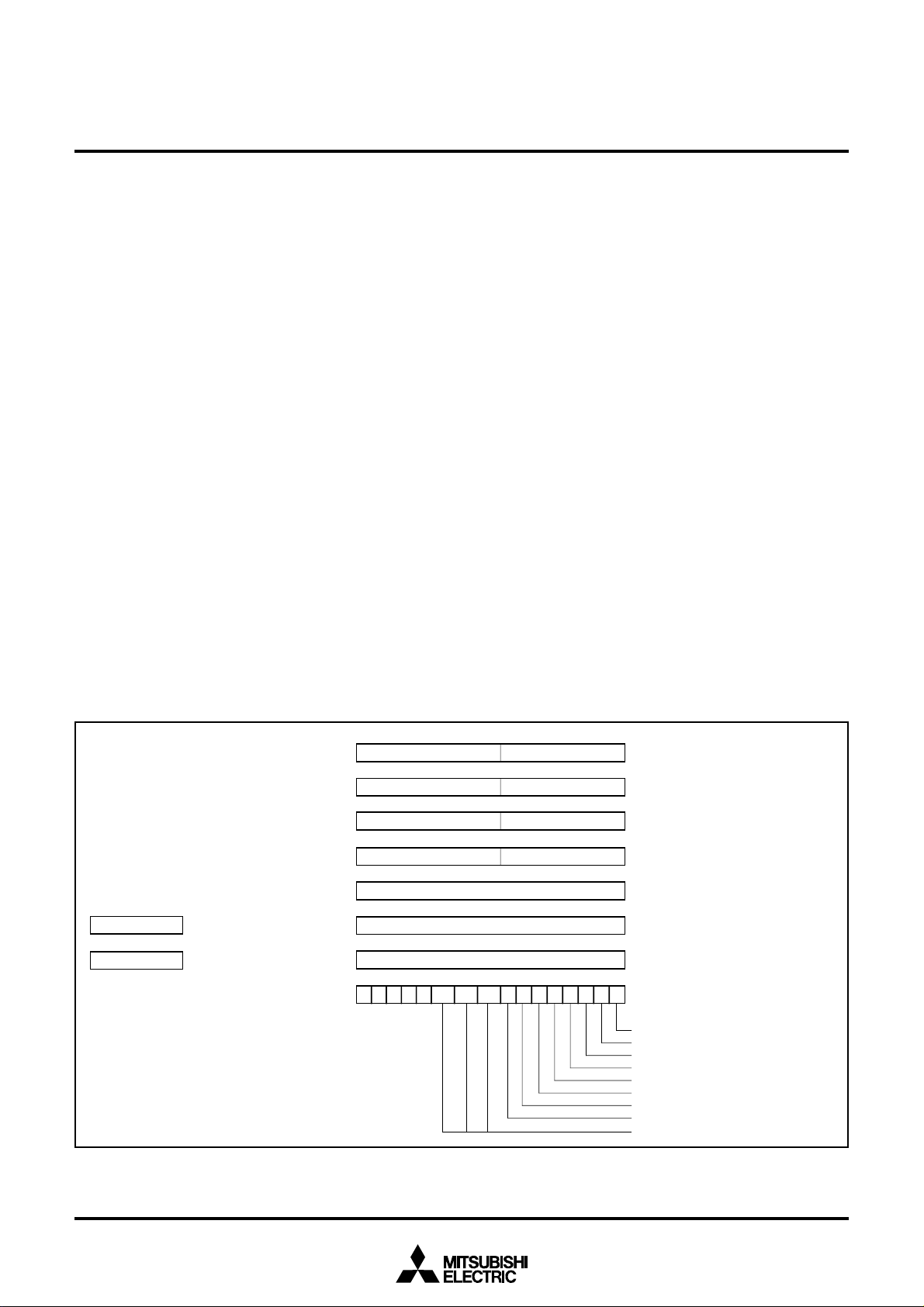

CENTRAL PROCESSING UNIT (CPU)

The CPU has ten registers and is shown in Figure 3. Each of these

registers is described below.

ACCUMULATOR A (A)

Accumulator A is the main register of the microcomputer. It consists

of 16 bits and the low-order 8 bits can be used separately. The data

length flag (m) determines whether the register is used as a 16-bit

register or as an 8-bit register. It is used as a 16-bit register when flag

m is “0” and as an 8-bit register when flag m is “1”. Flag m is a part of

the processor status register (PS) which is described later.

Data operations such as arithmetic operation, data transfer, input/

output, etc., are executed mainly through the accumulator A.

ACCUMULATOR B (B)

Accumulator B has the same functions as accumulator A, but the

use of accumulator B requires more instruction bytes and execution

cycles than accumulator A.

INDEX REGISTER X (X)

Index register X consists of 16 bits and the low-order 8 bits can be

used separately. The index register length flag (x) determines whether

the register is used as a 16-bit register or as an 8-bit register. It is

used as a 16-bit register when flag x is “0” and as an 8-bit register

when flag x is “1”. Flag x is a part of the processor status register

(PS) which is described later.

In an index addressing mode where register X is used as the index

register, the contents of this address is added to obtain the real

address.

Also, when executing a block transfer instruction (MVP, MVN), the

contents of index register X indicates the low-order 16 bits of the

source data address. The third byte of the MVP or MVN is the highorder 8 bits of the source data address.

INDEX REGISTER Y (Y)

Index register Y consists of 16 bits and the low-order 8 bits can be

used separately. The index register length flag (x) determines whether

the register is used as a 16-bit register or as an 8-bit register. It is

used as a 16-bit register when flag x is “0” and as an 8-bit register

when flag x is “1”. Flag x is a part of the processor status register

(PS) which is described later.

In an index addressing mode where register Y is used as the index

register, the contents of this address is added to obtain the real

address.

Also, when executing a block transfer instruction (MVP, MVN), the

contents of index register Y indicates the low-order 16 bits of the

destination data address. The second byte of the MVP or MVN is the

high-order 8 bits of the destination data address.

70

PG

70

DT

Fig. 3 Register structure

Program bank register (PG)

Data bank register (DT)

15 07

AH AL

15 07

BH BL

15 07

XH XL

15 07

YH YL

15 0

S

15 0

PC

15 0

DPR

715 0

NIPL2 IPL0IPL1 CZIDxmV0000

Accumulator A (A)

Accumulator B (B)

Index register X (X)

Index register Y (Y)

Stack pointer (S)

Program counter (PC)

Direct page register (DPR)

Processor status register (PS)0

Carry flag

Zero frag

Interrupt disable flag

Decimal mode flag

Index register length flag

Data length flag

Overflow flag

Negative flag

Processor interrupt priority level (IPL)

7

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

STACK POINTER (S)

Stack pointer (S) is a 16-bit register. It is used during a subroutine

call or interrupts. It is also used during stack, stack pointer relative,

or stack pointer relative indirect indexed Y addressing modes.

PROGRAM COUNTER (PC)

Program counter (PC) is a 16-bit counter that indicates the low-order

16 bits of the next program memory address to be executed. There

is a bus interface unit between the program memory and the CPU,

so that the program memory is accessed through the bus interface

unit. This is described later.

PROGRAM BANK REGISTER (PG)

Program bank register (PG) is an 8-bit register that indicates the highorder 8 bits of the next program memory address to be executed.

When a carry occurs by incrementing the contents of the program

counter, the contents of the program bank register (PG) is incremented

by 1. Also, when a carry or borrow occurs after adding or subtracting

the offset value to or from the contents of the program counter (PC)

by using a branch instruction, the contents of the program bank

register (PG) is incremented or decremented by 1 so that programs

can be written without worrying about bank boundaries.

DATA BANK REGISTER (DT)

Data bank register (DT) is an 8-bit register. With some addressing

modes, a part of the data bank register (DT) is used to specify a

memory address. The contents of data bank register (DT) is used as

the high-order 8 bits of a 24-bit address. Addressing modes that use

the data bank register (DT) to specify the address are direct indirect,

direct indexed X indirect, direct indirect indexed Y, absolute, absolute

bit, absolute indexed X, absolute indexed Y, absolute bit relative,

and stack pointer relative indirect indexed Y.

DIRECT PAGE REGISTER (DPR)

Direct page register (DPR) is a 16-bit register. Its contents is used as

the base address of a 256-byte direct page area. The direct page

area is allocated in bank 0

or more, the direct page area spans across bank 016 and bank 116.

All direct addressing modes use the contents of the direct page register

(DPR) to generate the data address. If the low-order 8 bits’ contents

of the direct page register (DPR) is “00

required to generate an address is minimized. Hence the low-order 8

bits’ contents of the direct page register (DPR) is usually set to “00

16, but when the contents of DPR is FF0116

16”, the number of cycles

16”.

1. Carry flag (C)

The carry flag contains the carry or borrow generated by the ALU

after an arithmetic operation. This flag is also affected by shift or

rotate instruction. This flag can be set or reset directly with the SEC,

CLC instructions or with the SEP, CLP instructions.

2. Zero flag (Z)

This zero flag is set when the result of an arithmetic operation or data

transfer is zero and reset when it is not. This flag can be set or reset

directly with the SEP or CLP instruction.

3. Interrupt disable flag ( I )

When the interrupt disable flag is “1”, all interrupts except watchdog

timer,

DBC, and software interrupt are disabled. This flag is

automatically set to “1” when an interrupt is accepted. It can be set or

reset directly with the SEI, CLI instructions or SEP and CLP

instructions.

4. Decimal mode flag (D)

The decimal mode flag determines whether addition and subtraction

are performed in the binary or the decimal system. Binary arithmetic

is performed when this flag is “0”. If it is “1”, decimal arithmetic is

performed with each word treated as the 2- or 4-digit number.

Arithmetic operation is performed with 4-digit number when the data

length flag (m) is “0” and with 2-digit number when it is “1”. Decimal

correction is automatically performed. (Decimal operation is possible

only with the ADC and SBC instructions.) This flag can be set or

reset with the SEP or CLP instruction.

5. Index register length flag (x)

The index register length flag determines whether index register X

and index register Y are used as 16-bit registers or as 8-bit registers.

The registers are used as 16-bit registers when flag x is “0” and as 8bit registers when it is “1”. This flag can be set or reset with the SEP

or CLP instruction.

6. Data length flag (m)

The data length flag determines whether the data has a length of 16

bits or that of 8 bits. The 16-bit length is selected when flag m is “0”

and the 8-bit length is selected when it is “1”. This flag can be set or

reset with the SEM, CLM instructions or with the SEP, CLP

instructions.

PROCESSOR STATUS REGISTER (PS)

Processor status register (PS) is an 11-bit register. It consists of flags

which indicate the result of operation and the processor interrupt

priority level (IPL).

Branch operations can be performed by testing flags C, Z , V, and N.

The details of each processor status register bit are described below.

8

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

7. Overflow flag (V)

The overflow flag is effective only when addition or subtraction is

performed with treating a word as a signed binary number. When the

data length flag (m) is “0”, the overflow flag is set if the result of

addition or subtraction is outside the range between – 32768 and

+32767. When the data length flag (m) is “1”, the overflow flag is set

if the result of addition or subtraction is outside the range between

–128 and +127. It is reset in the other cases. The overflow flag can

also be set or reset directly with the SEP or CLV, CLP instructions.

8. Negative flag (N)

The negative flag is set when the result of arithmetic operation or

data transfer is negative (If data length flag (m) is “0”, data bit 15 is

“1”. If data length flag (m) is “1”, data bit 7 is “1”.) It is reset in the

other cases. It can also be set or reset with the SEP or CLP

instructions.

9. Processor interrupt priority level (IPL)

The processor interrupt priority level (IPL) consists of 3 bits and

determines the processor interrupt priority level (0 to 7). Interrupt is

enabled when the interrupt priority level of the device requesting

interrupt (the priority can be set using the interrupt control register) is

higher than the processor interrupt priority level. When interrupt is

enabled, the current processor interrupt priority level is saved in a

stack and the processor interrupt priority level is replaced by the

interrupt priority level of the device requesting the interrupt. Refer to

the section on interrupts for more details.

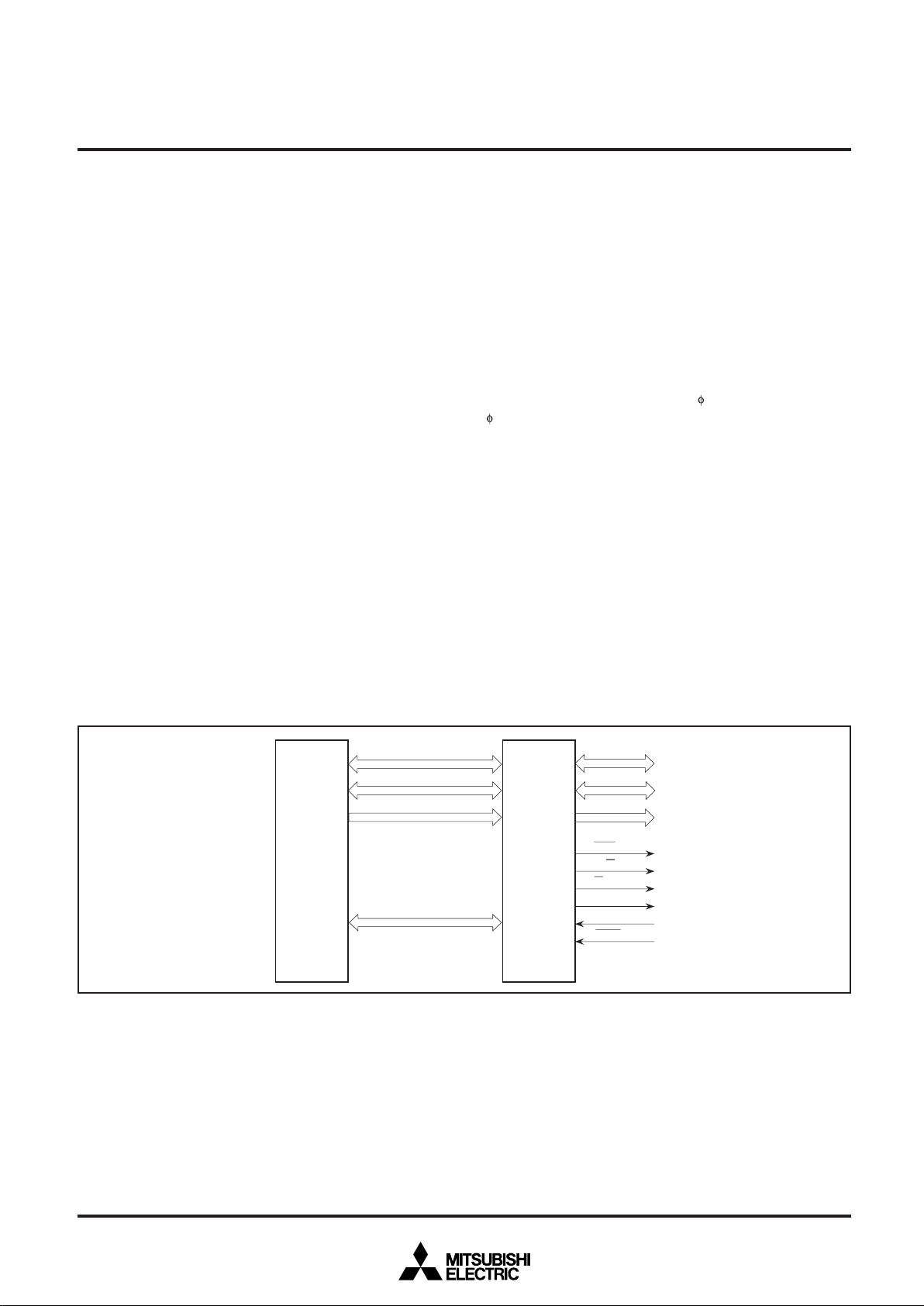

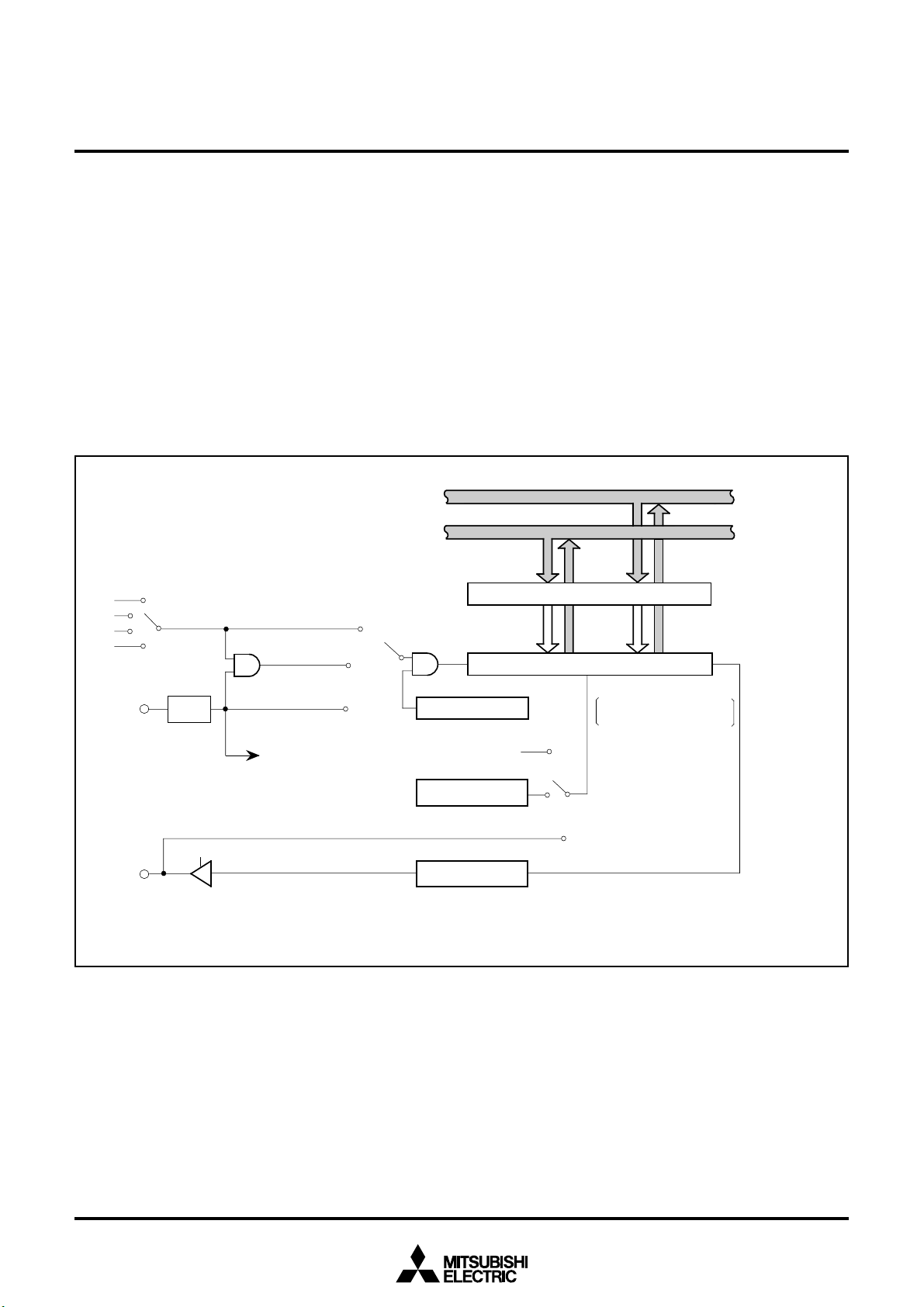

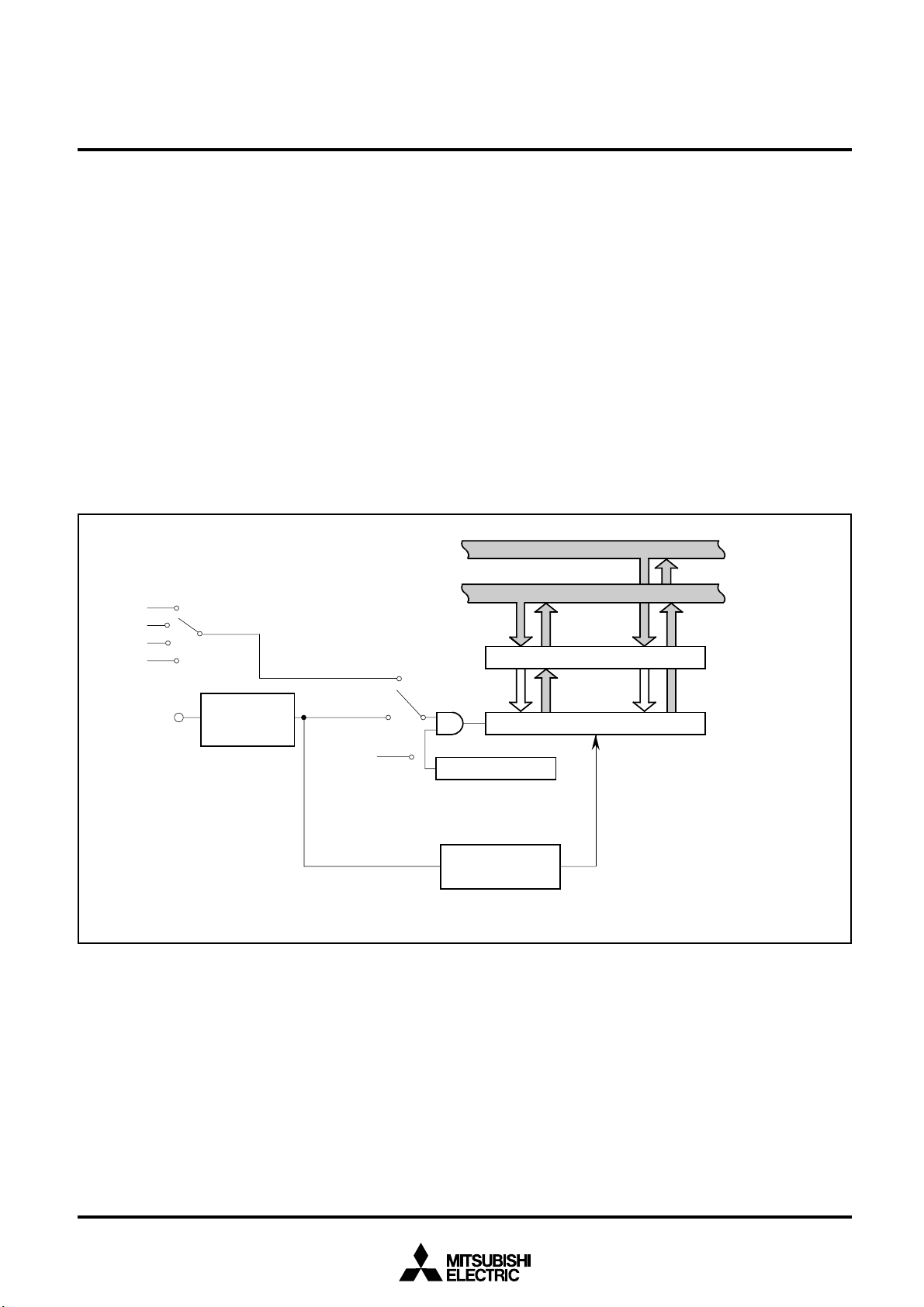

BUS INTERFACE UNIT

The CPU operates on an internal clock ’s frequency. Internal clock

’s frequency is twice the bus cycle frequency. In order to speed up

processing, a bus interface unit is used to pre-fetch instructions when

the data bus is idle. The bus interface unit synchronizes the CPU

and the bus and pre-fetches instructions. Figure 4 shows the

relationship between the CPU and the bus interface unit. The bus

interface unit has a program address register, a 3-byte instruction

queue buffer, a data address register, and a 2-byte data buffer.

The bus interface unit obtains an instruction code from the memory

and stores it in the instruction queue buffer, obtains data from the

memory and stores it in the data buffer, or writes the data from the

data buffer to the memory.

D'15 – D'8

D'7 – D'0

A'23 – A'0

CPU

Control signal

Fig. 4 Relationship between the CPU and the bus interface unit

Bus interface

unit

D15 – D8

D7 – D0

A23 – A0

BHE

R/W

E

ALE

BYTE

HOLD

9

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

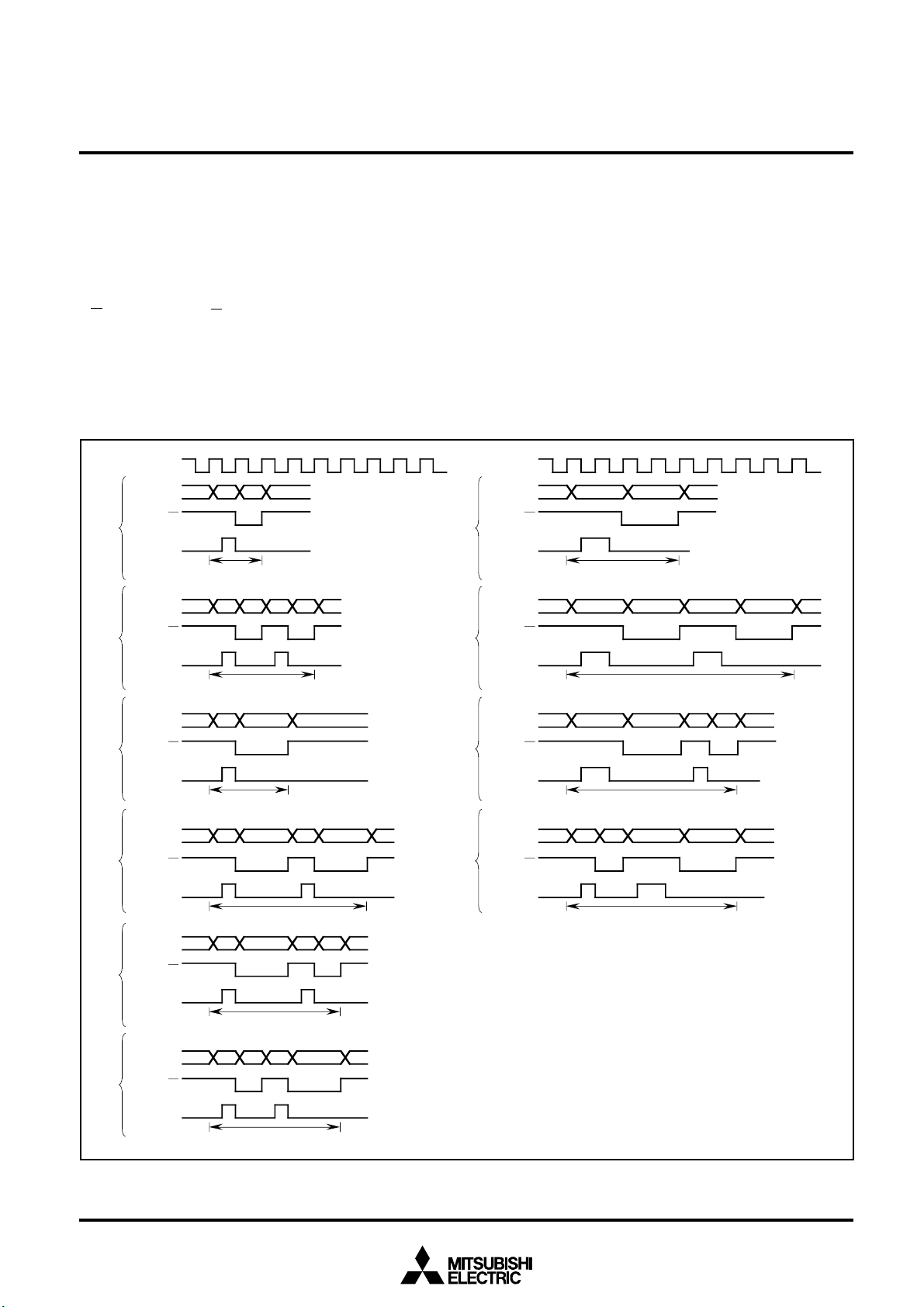

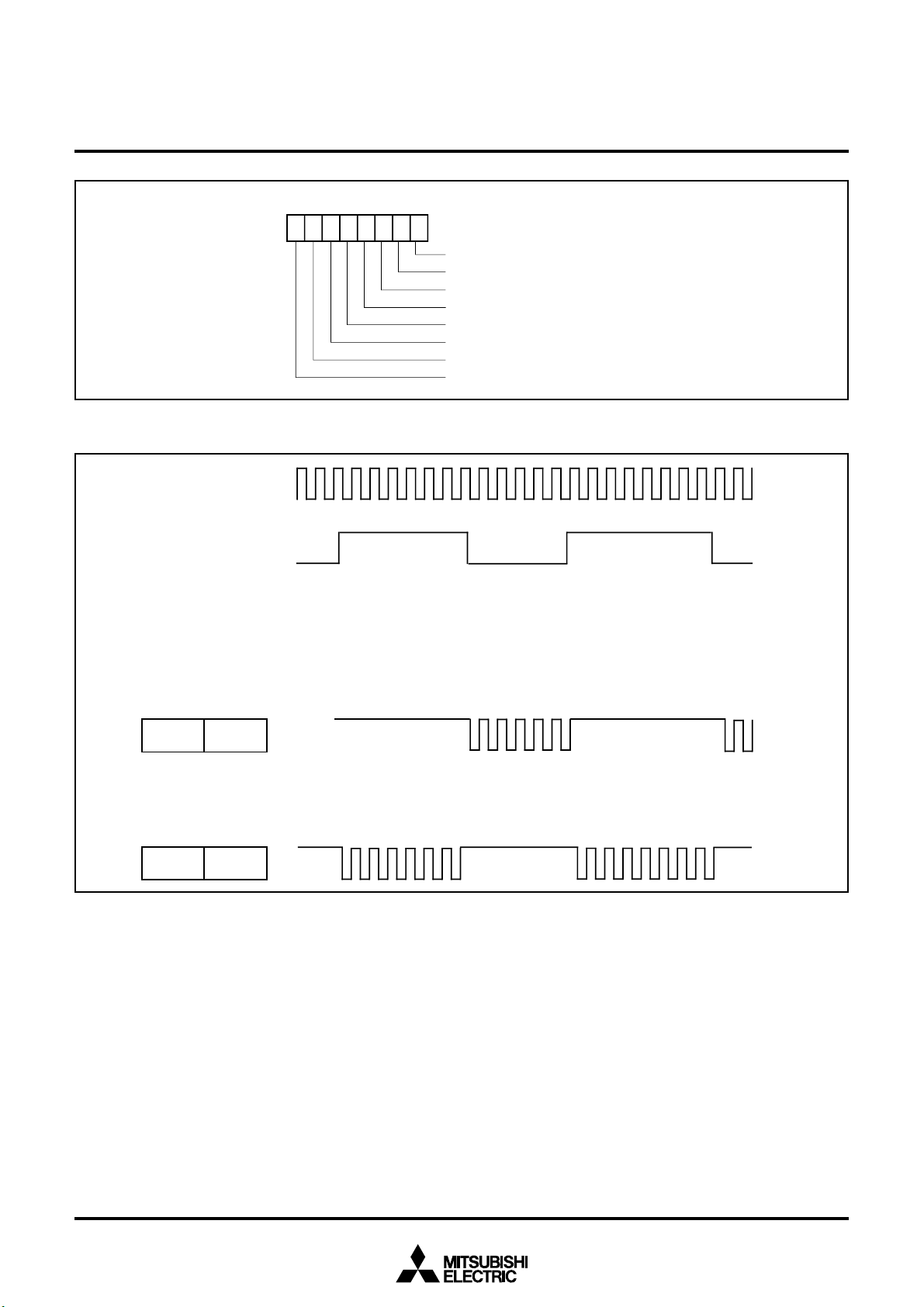

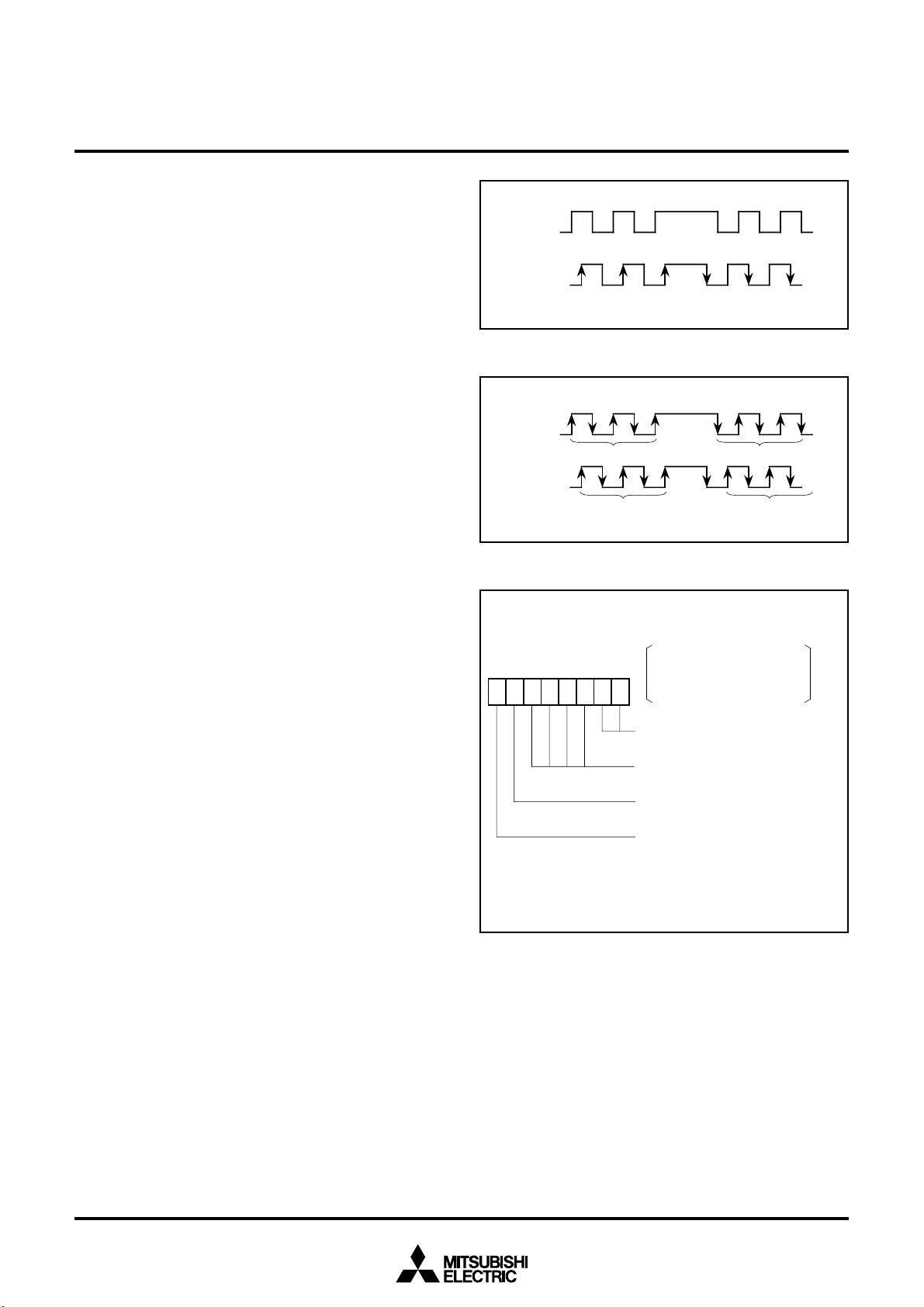

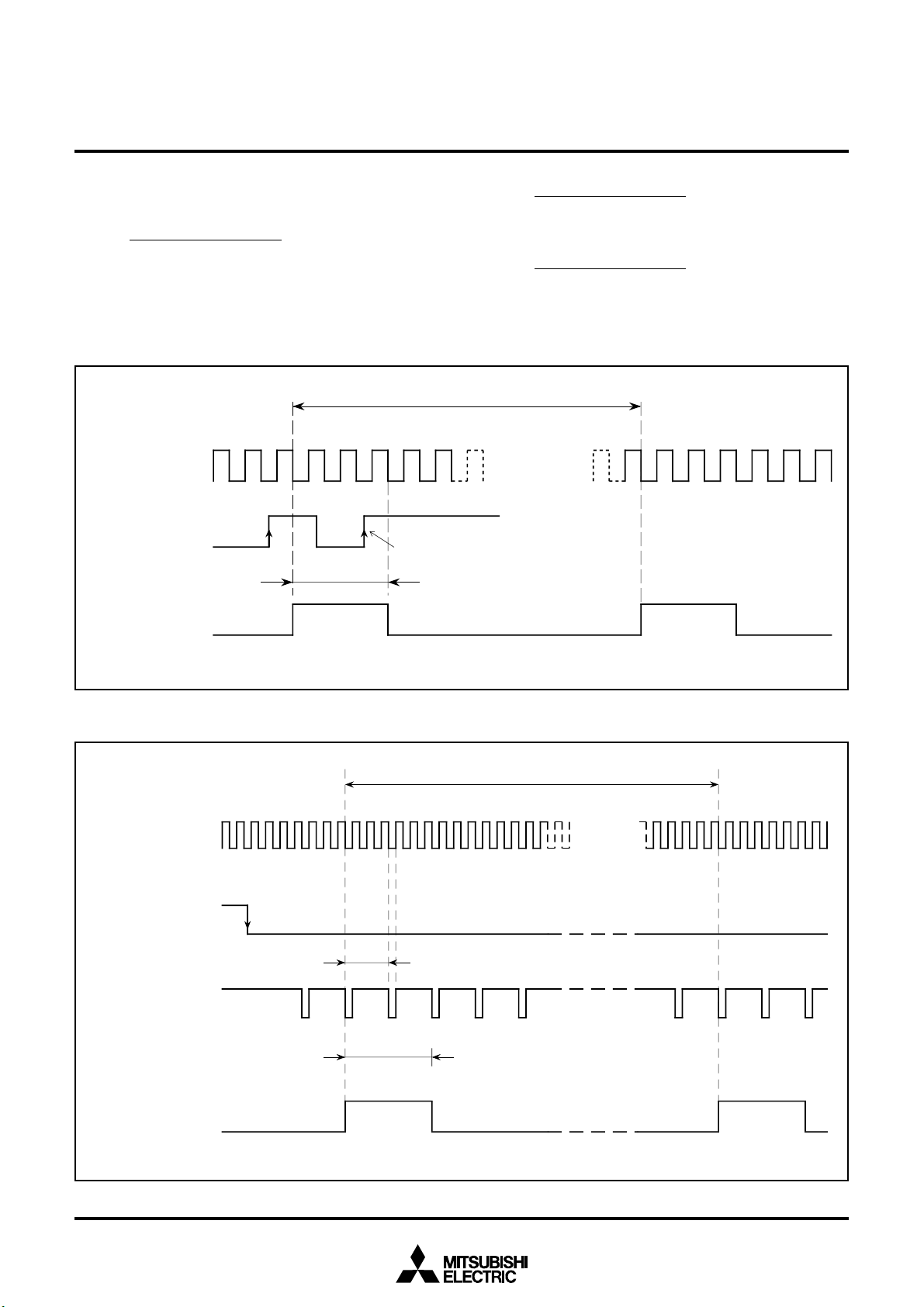

The bus interface unit operates using one of the waveforms (1) to

(10) shown in Figure 5. The standard waveforms are (1) and (2).

The

E

signal becomes “L” when the bus interface unit reads an

instruction code or data from the memory or when it writes data to

W

signal. When the R/

Waveform (1) in Figure 5 is used to access a single byte or two bytes

Internal clock

Port P2

(1)

W

signal is “H”, read is performed; when “L”,

write is performed.

φ

E

AD

The ALE signal is used to latch only the address signal from the

multiplexed signal containing data and address.

the memory. Whether to perform read or write is controlled by the

R/

simultaneously. To read or write two bytes simultaneously, the first

address accessed must be even. Furthermore, when accessing an

ALE

Access time

A+1

D

(2)

Port P2

AD

E

ALE

Access time

microprocessor mode, set the bus width selection input pin (BYTE)

to “L” (external data bus has a width of 16 bits). The data bus in the

external memory area in the memory expansion mode or the

Internal clock

(7)

(8)

Port P2

ALE

Port P2

φ

E

A

D

Access time

A

E

D

A + 1

ALE

Access time

D

internal memory area is always treated as the 16-bit bus independent

of BYTE.

Port P2

(3)

E

ALE

Port P2

(4)

E

ALE

Port P2

(5)

E

ALE

Port P2

(6)

E

ALE

Fig. 5 Bus access timing

AD

Access time

A

Access time

A

Access time

AD

Access time

A + 1

DD

A + 1

D

A+1

A + 1

D

D

(9)

Port P2

A

E

ALE

Access time

(10)

Port P2

E

AD

A + 1

D

ALE

Access time

D

A : Address

D : Data

D

10

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

When performing 16-bit data read or write, waveform (2) is used to

access each byte one by one if the conditions for simultaneously

accessing two bytes are not satisfied. However, when prefetching

the instruction code, if the address of the instruction code is odd,

waveform (1) is used, and only one byte is read in the instruction

queue buffer.

Access to the even/odd address is controlled by signals BHE and A0.

Bit 2 of processor mode register 0 (address 5E16) is the wait bit.

When the external memory area is accessed in the memory expansion

mode or the microprocessor mode with this bit set to “0”, the width of

the E signal is extended and access time can be extended.

There are two ways to extend the access time and they are selected

with bit 0 of the processor mode register 1 (address 5F16).

When this bit is set to “1”, the “L” width of the E signal in (1) becomes

twice as long as in (3) and the access time becomes 1.5 times (wait

1). When this bit is set to “0”, the ALE signal and E signal in (1) are

extended as in (7) and the access time is doubled (wait 0).

However, these signals are not extended when accessing the internal

memory area.

When the wait bit is set to “1”, these signals are not extended when

accessing any memory area regardless of the bit 0 of the processor

mode register 1.

Waveforms (4), (5), and (6) show the entire waveform, first half, and

last half respectively of waveform (2) for wait 1.

Waveforms (8), (9), and (10) show the entire waveform, first half,

and last half respectively of waveform (2) for wait 0.

Instruction code read, data read, and data write are described below.

Instruction code read will be described first.

The CPU obtains instruction codes from the instruction queue buffer

and executes them. The CPU notifies the bus interface unit that it is

requesting an instruction code during an instruction code request

cycle. If the requested instruction code is not yet stored in the

instruction queue buffer, the bus interface unit halts the CPU until

more instructions than requested is stored in the instruction queue

buffer. Even if there is no instruction code request from the CPU, the

bus interface unit reads instruction codes from the memory and stores

them in the instruction queue buffer when the instruction queue buffer

is empty or when only one instruction code is stored and the bus is

idle on the next cycle. This is referred to as instruction pre-fetching.

Normally , when reading an instruction code from the memory, if the

accessed address is even, the next odd address is read together

with the instruction code and stored in the instruction queue buffer.

However, in the memory expansion mode or the microprocessor

mode, only one byte is read and stored in the instruction queue buffer

if the following conditions are satisfied.

• The address to be read is in the external memory area when the

external data bus has an 8-bit width (BYTE = “H”).

• The address to be read is odd.

Therefore, waveform (1), (3) or (7) in Figure 5 is used for instruction

code read. Data read and write are described below.

The CPU notifies the bus interface unit when performing data read or

write. At this time, the bus interface unit halts the CPU if the bus

interface unit is already using the bus or if there is a request with

higher priority. When data read or write is enabled, the bus interface

unit uses one of the waveforms from (1) to (10) in Figure 5 to perform

the operation.

During data read, the CPU waits until the entire data is stored in the

data buffer. The bus interface unit sends the address received from

the CPU to the address bus. Then it reads the memory when the E

signal is “L” and stores the result in the data buffer.

During data write, the CPU writes the data in the data buffer and the

bus interface unit writes it to the memory . Therefore, the CPU can

proceed to the next step without waiting for write completed. The bus

interface unit sends the address received from the CPU to the address

bus. Then when the E signal is “L”, the bus interface unit sends the

data in the data buffer to the data bus and writes it to the memory.

11

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

INTERRUPTS

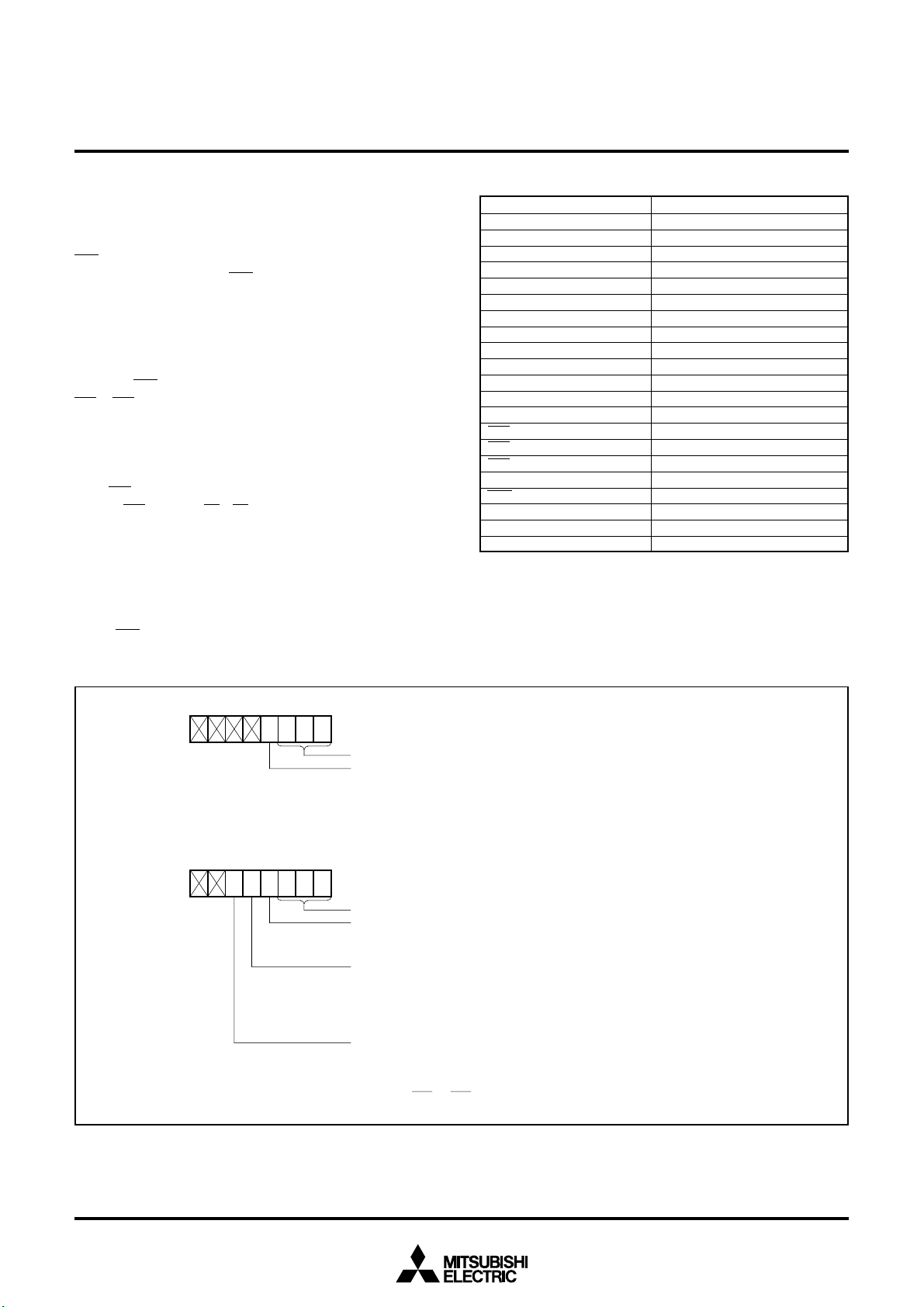

Table 1 shows the interrupt sources and the corresponding interrupt

vector addresses. Reset is also treated as a source of interrupt and

is described in this section.

DBC is an interrupt used only for debugging.

Interrupts other than reset, DBC, watchdog timer, zero divide, and

BRK instruction all have their respective interrupt control registers.

Table 2 shows the addresses of the interrupt control registers and

Figure 6 shows the bit configuration of the interrupt control register.

The interrupt request bit is automatically cleared by hardware during

reset or when processing an interrupt. Also, interrupt request bits

other than DBC and watchdog timer can be cleared by software.

INT0 to INT2 are external interrupts, and whether to cause an interrupt

at the input level (level sense) or at the edge (edge sense) can be

selected with the level sense/edge sense selection bit. Furthermore,

the polarity of the interrupt input can be selected with a polarity

selection bit.

In the INT2/Key input interrupt, whether to input an interrupt request

from the INT2 pin or the KI0 – KI3 pins can be selected by bit 7 of the

port function control register (refer to Figure 11).

Timer and UART interrupts are described in the respective section.

The priority of interrupts when multiple interrupts are caused

simultaneously is partially fixed by hardware, but it can also be

adjusted by software as shown in Figure 7. The hardware priority is

fixed as follows:

reset > DBC > watchdog timer > other interrupts

Table 1. Interrupt sources and the interrupt vector addresses

Interrupts Vector addresses

A-D/UART2 trans./rece. 00FFD616 00FFD716

UART1 transmit 00FFD816 00FFD916

UART1 receive 00FFDA16 00FFDB16

UART0 transmit 00FFDC16 00FFDD16

UART0 receive 00FFDE16 00FFDF16

Timer B2 00FFE016 00FFE116

Timer B1 00FFE216 00FFE316

Timer B0 00FFE416 00FFE516

Timer A4 00FFE616 00FFE716

Timer A3 00FFE816 00FFE916

Timer A2 00FFEA16 00FFEB16

Timer A1 00FFEC16 00FFED16

Timer A0 00FFEE16 00FFEF16

INT2/Key input 00FFF016 00FFF116

INT1 00FFF216 00FFF316

INT0 00FFF416 00FFF516

Watchdog timer 00FFF616 00FFF716

DBC (unusable) 00FFF816 00FFF916

BRK instruction 00FFFA16 00FFFB16

Zero divide 00FFFC16 00FFFD16

Reset 00FFFE16 00FFFF16

7

6543210

Interrupt control register configuration for timers A0 to A4, timers B0 to B2, UART0, UART1 and

A-D/UART2 trans./rece.

7

6543210

Interrupt control register configuration for

Fig. 6 Interrupt control register bit configuration

Interrupt priority level selection bits

Interrupt request bit

0 : No interrupt

1 : Interrupt

Interrupt priority level selection bits

Interrupt request bit

0 : No interrupt

1 : Interrupt

Polarity selection bit

0 : Interrupt request bit is set at “H” level for level sense or at the falling

edge for edge sence.

1 : Interrupt request bit is set at “L” level for level sense or at the rising

edge for edge sense.

Level sense/edge sense selection bit

0 : Edge sense

1 : Level sense

INT0 to INT2/Key input

12

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Table 2. Addresses of interrupt control registers

Interrupt control registers addresses

A-D/UART2 trans./rece. interrput control register

00007016

UART0 transmit interrput control register 00007116

UART0 receive interrput control register 00007216

UART1 transmit interrput control register 00007316

UART1 receive interrupt control register 00007416

Timer A0 interrupt control register 00007516

Timer A1 interrupt control register 00007616

Timer A2 interrupt control register 00007716

Timer A3 interrupt control register 00007816

Timer A4 interrupt control register 00007916

Timer B0 interrupt control register 00007A16

Timer B1 interrupt control register 00007B16

Timer B2 interrupt control register 00007C16

INT0 interrupt control register 00007D16

INT1 interrupt control register 00007E16

INT2/Key input interrupt control register 00007F16

Interrupts caused by a BRK instruction and when dividing by zero

are software interrupts and are not included in this list.

Other interrupts previously mentioned are A-D converter, UART,

Timer, INT interrupts. The priority of these interrupts can be changed

by changing the interrupt priority level selection bits of the

corresponding interrupt control register with software.

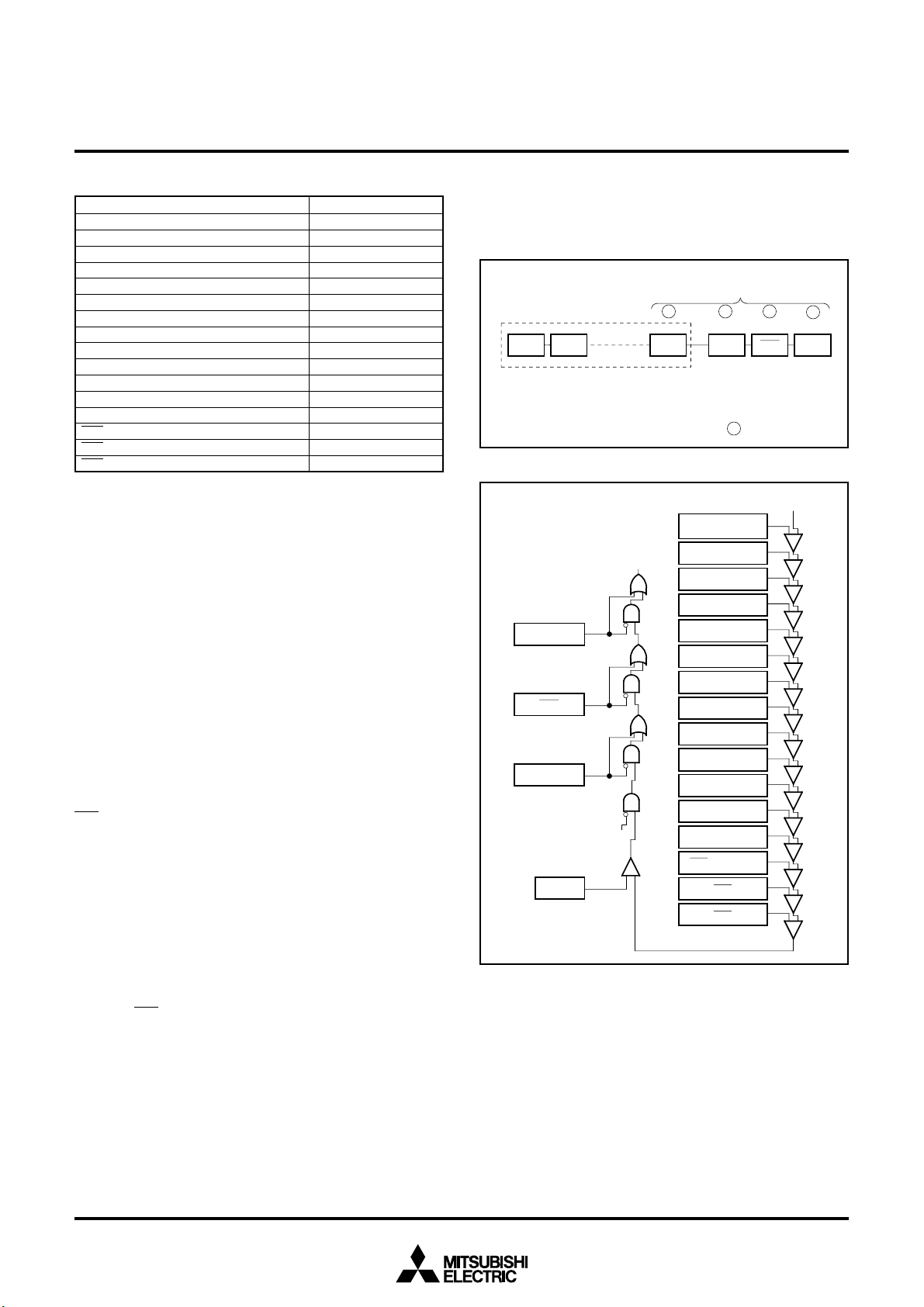

Figure 8 shows a diagram of the interrupt priority detection circuit.

When an interrupt is caused, the each interrupt device compares its

own priority with the priority from above and if its own priority is higher,

then it sends the priority below and requests the interrupt. If the

priorities are the same, the one above has priority.

This comparison is repeated to select the interrupt with the highest

priority among the interrupts that are being requested. Finally the

selected interrupt is compared with the processor interrupt priority

level (IPL) contained in the processor status register (PS), and the

request is accepted if it is higher than IPL and the interrupt disable

flag (I) is “0”. The request is not accepted if flag I is “1”. The reset,

DBC, and watchdog timer interrupts are not affected by the interrupt

disable flag (I).

When an interrupt is accepted, the contents of the processor status

register (PS) is saved to the stack and the interrupt disable flag (I) is

set to “1”.

Furthermore, the interrupt request bit of the accepted interrupt is

cleared to “0” and the processor interrupt priority level (IPL) in the

processor status register (PS) is replaced by the priority level of the

accepted interrupt.

Therefore, multiple interrupts are possible by resetting the interrupt

disable flag (I) to “0” and enable further interrupts.

For reset, DBC, watchdog timer, zero divide, and BRK instruction

interrupts, which do not have an interrupt control register, the

processor interrupt level (IPL) is set as shown in Table 3.

Priority detection is performed by latching the interrupt request bit

and interrupt priority level selection bits so that they do not change.

They are sampled at the first half and latched at the last half of the

operation code fetch cycle.

Because priority detection takes some time, no sampling pulse is

generated for a certain interval even if it is the next operation code

fetch cycle.

Priority is determined by hardware

3

2

4

➂➃

Watchdog

timer

DBC

1

Reset

A-D converter, UART, Timer, INT interrupts

Priority can be changed by software inside

4

Fig. 7 Interrupt priority

Level 0

A-D/UART2

trans./rece.

Interrupt request

Reset

DBC

Watchdog

timer

Interrupt disable flag(I)

IPL

UART1 transmit

UART1 receive

UART0 transmit

UART0 receive

Timer B2

Timer B1

Timer B0

Timer A4

Timer A3

Timer A2

Timer A1

Timer A0

INT

2

/Key input

INT

1

INT

0

Fig. 8 Interrupt priority detection circuit

13

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

As shown in Figure 9, there are three different interrupt priority

detection time from which one is selected by software. After the

selected time has elapsed, the interrupt which has the highest priority

is determined and is processed after the current instruction execution

has been completed.

The time is selected with bits 4 and 5 of the processor mode register

0 (address 5E16) shown in Figure 10. Table 4 shows the relationship

between these bits and the number of cycles. After a reset, the

processor mode register 0 is initialized to “0016”. Therefore, the longest

time is selected. However, the shortest time should be selected by

software.

Internal clock

Operation code fetch cycle

Sampling pulse

φ

Table 3. Value set in processor interrupt level (IPL) during an interrupt

Interrupt types Setting value

Reset 0

DBC 7

Watchdog timer 7

Zero divide Not change value of IPL.

BRK instruction Not change value of IPL.

Table 4. Relationship between interrupt priority detection time selec-

Interrupt priority detection time selection bits

φ : internal clock

tion bits and number of cycles

Bit 5 Bit 4

0 0 7 cycles of φ

0 1 4 cycles of φ

1 0 2 cycles of φ

Number of cycles

Priority detection time

Select one from 0 to 2 with

bits 4 and 5 of the

processor mode register 0

Fig. 9 Interrupt priority detection time

7

6 5 4 3 2 1 0

0

0

1

2

Processor mode register 0 (5E16)

Processor mode bits

0 0 : Single-chip mode

0 1 : Memory expansion mode

1 0 : Microprocessor mode

Wait bit

0 : Wait

1 : No wait

Software reset bit

The processor is reset when this bit is set to “1” .

Interrupt priority detection time selection bits

0 0 : Select 0 in Figure 9

0 1 : Select 1 in Figure 9

1 0 : Select 2 in Figure 9

Always “0”

Clock

φ

1

output selection bit

φ

1

φ

1

output

output

0 : No

1 :

Address

Fig. 10 Processor mode register 0 configuration

14

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

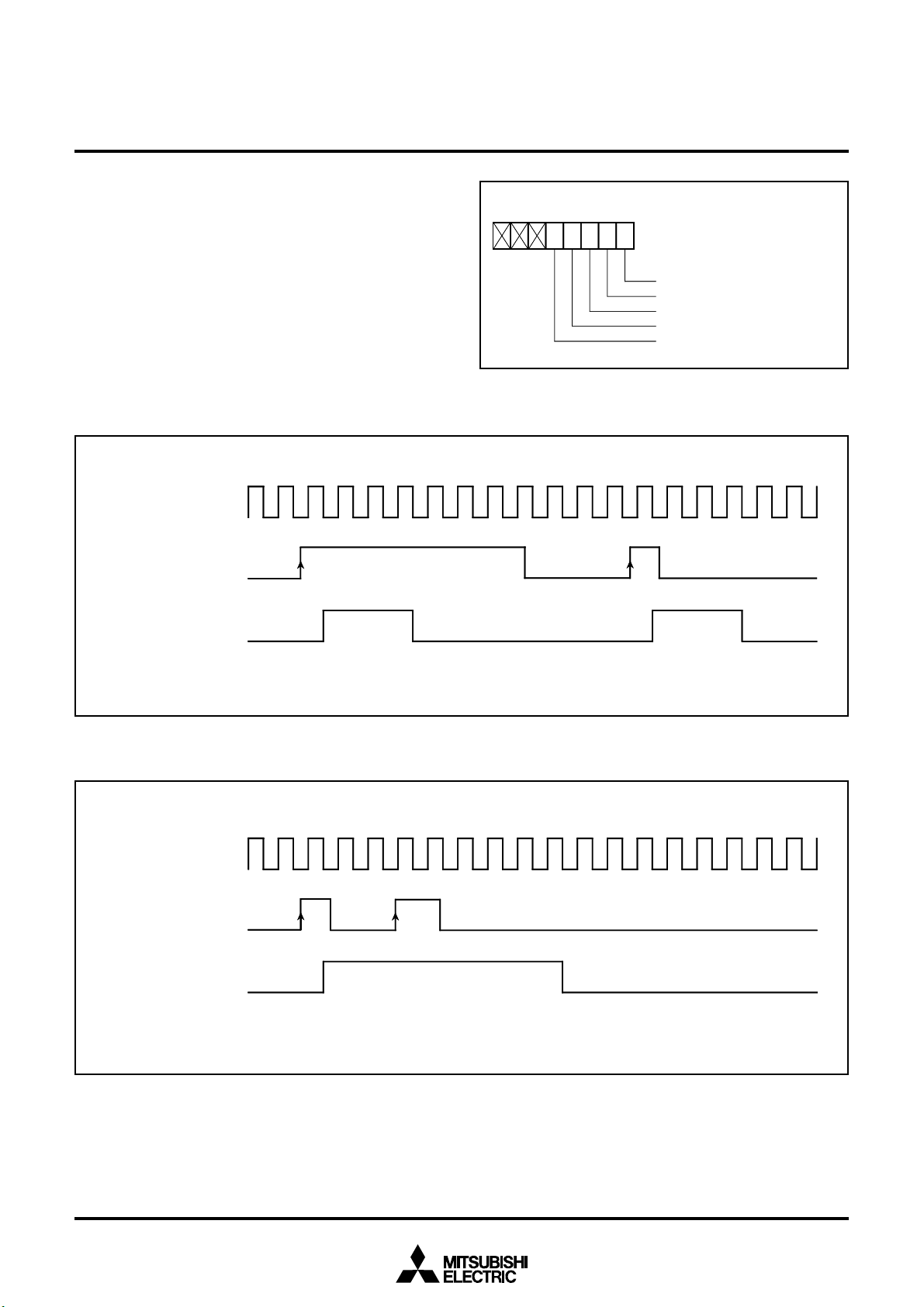

By setting the port function control register, the INT2/Key input interrupt

function can be switched to the key input interrupt function which

uses the KI0 to KI3 inputs. Figure 11 shows the bit configuration of the

port function control register, and Figure 12 shows the INT2/Key input

interrupt input circuit block diagram.

When the key input interrupt selection bit of the port function control

register is “0”, a signal is input from the INT2 pin to the INT2/Key input

interrupt control circuit and the INT2 interrupt is normally performed.

When the key input interrupt selection bit is “1”, signals input from

the KI0 to KI3 pins are inverted, and then the logical sum of these

signals is input to the INT2 interrupt control circuit. In this case, the

external interrupt which uses the KI0 to KI3 pins is performed. (Pins

KI0 to KI3 correspond to ports P54 to P57, respectively.) Additionally,

by setting the port P6 pull-up selection bit 1 to “1”, the INT2 input is

added to that logical sum, so that the external interrupt which uses

the inputs KI0 to KI3 and INT2 is performed. When using the key input

interrupt, it is necessary to select the edge sense which uses the

falling edge by setting the INT2 /Key input interrupt control register.

Because of this selection, a key input interrupt request occurs when

“L” is input to one of the KI0 to KI3 and INT2 pins. The interrupt vector

and the interrupt control register are common to the INT2 and key

input interrupts.

Port P6 pull-up

selection bit 1

4

direction register

Port P6

Pull-up resistors (transistors) can be added to the KI0 to KI3 pins by

setting “1” to the port P5 pull-up selection bit and “0” to the contents

of the port P5i (i = 4 to 7) direction register. Similarly, a pull-up resistor

can be added to the INT2 pin by setting “1” to the port P6 pull-up

selection bit 1 and “0” to the content of the port P64 direction register.

With the key input interrupt and the pull-up function, the key input

circuit is easily composed.

P64/

INT

2

Port P6 pull-up

selection bit 1

Port P5 pull-up

Pull–up

transistor

P57/

KI

3

selection bit

7

direction

Port P5

register

Pull–up

transistor

P56/

KI

2

Pull–up

transistor

P55/

KI

1

Pull–up

transistor

P54/

KI

0

Fig. 12 INT2/Key input interrupt input circuit block diagram

INT

2

/Key input interrupt control register

0

0

1

1

Key input interrupt selection bit

When the key input interrupt is

selected, it is necessary to

select the edge sense which

uses falling edge.

Interrupt control register

(Address 7F

INT

2

/Key input

interrupt request

16

)

15

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

76540321

0

Port function control register

Address

6D

16

Standby state selection bit

0: Pins P0 – P3 as external bus output

1: Pins P0 – P3 as port output

Sub-clock output selection bit/Timer B2 clock source selection bit

•

Port-Xc selection bit = “0” (sub-clock not used)

Timer B2 (event counter mode) clock source selection

0: TB2

IN

input

1: Main clock divided by 32

•

Port-Xc selection bit = “1” (sub-clock used)

Sub-clock output selection

0: Function as port P6

1: Output sub-clock φ

7

pin

SUB

from P67/TB2IN/ φ

Timer B1 internal connect selection bit

0: No internal connect

1: Internal connect to timer B2

Port P6 pull-up selection bit 0

0: With no pull-up transistor for pins P6

1: With pull-up transistor for pins P6

2

/

INT

0

/

INT

0

, P63/

, P63/

INT

2

0: Always “0”

Port P6 pull-up selection bit 1

•

Key input interrupt selection bit = “0”

0: With no pull-up transistor for P6

1: With pull-up transistor for P6

•

Key input interrupt selection bit = “1”

4

/

INT

2

/

INT

2

pin

pin

4

0: With port function, no pull-up transistor for P6

1: With key input interrupt, pull-up transistor for P6

SUB

INT

1

4

/

INT

4

pin

1

2

/

INT

pin

2

pin

Fig. 11 Bit configuration of port function control register

Port P5 pull-up selection bit

0: With no pull-up transistor for pins P5

1: With pull-up transistor for pins P5

4

Key input interrupt selection bit

0:

INT

2

interrupt

1: Key input interrupt

4

–

P5

7

–

P5

7

16

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

TIMER

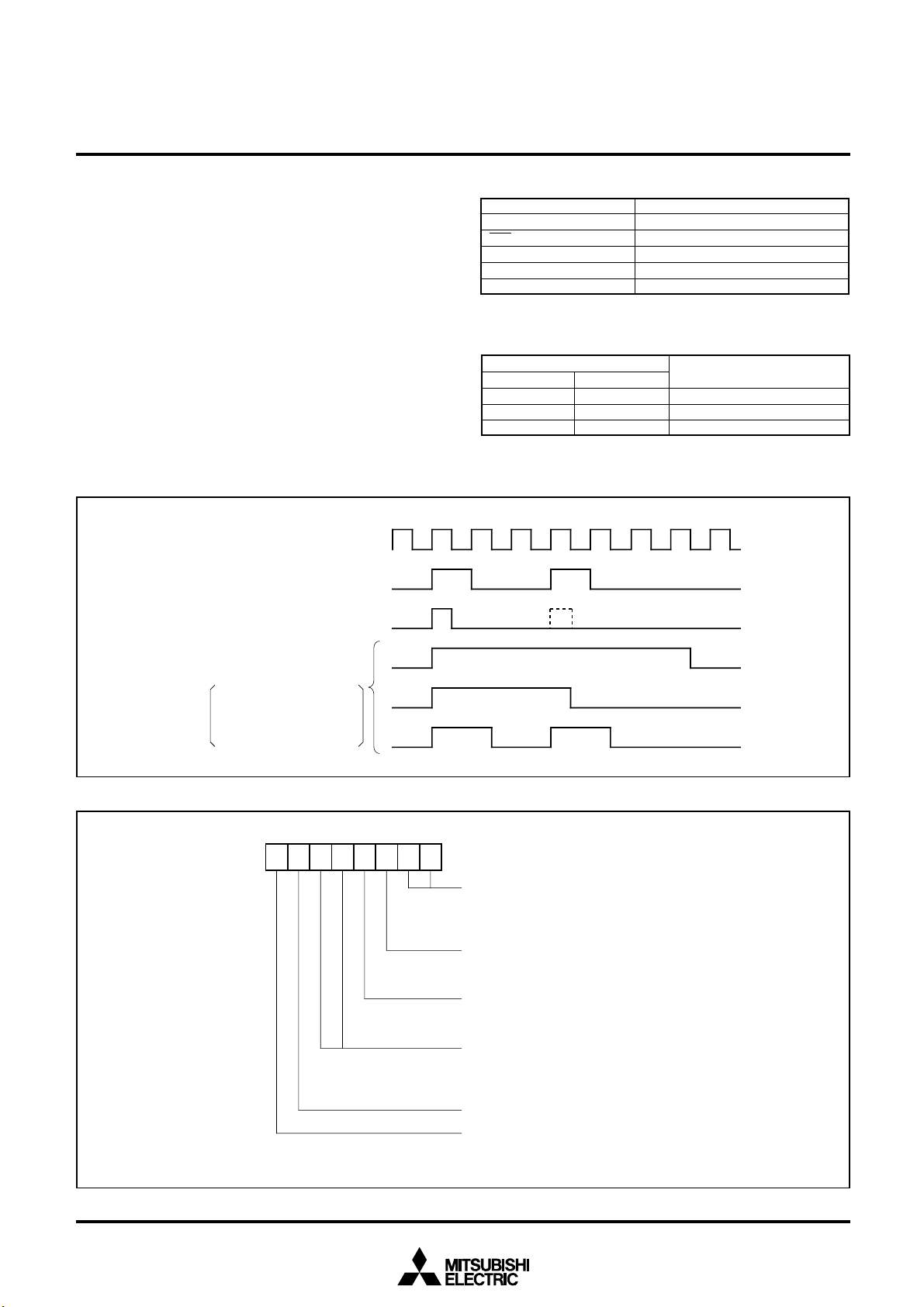

There are eight 16-bit timers. They are divided by type into timer A(5)

and timer B(3).

The timer I/O pins are also used as I/O pins for ports P5 and P6. To

use these pins as timer input pins, the port direction register bit

corresponding to the pin must be cleared to “0” to specify the input

mode.

TIMER A

Figure 13 shows a block diagram of timer A.

Timer A has four modes; timer mode, event counter mode, one-shot

pulse mode, and pulse width modulation mode. The mode is selected

with bits 0 and 1 of the timer Ai mode register (i = 0 to 4). Each of

these modes is described below.

Clock source selection

f

2

f

16

f

64

f

512

TAi

(i = 0 – 4)

IN

Polarity

selection

• Timer

• One-shot

• Pulse width modulation

Timer (gate function)

Event counter

External trigger

(1) Timer mode [00]

Figure 14 shows the bit configuration of the timer Ai mode register

during timer mode. Bits 0, 1, and 5 of timer Ai mode register must

always be “0” in the timer mode.

Bit 3 is ignored if bit 4 is “0”.

Bits 6 and 7 are used to select the timer counter source. The counting

of the selected clock starts when the count start flag is “1” and stops

when it is “0”.

Figure 15 shows the bit configuration of the count start flag. The

counter is decremented. An interrupt is caused and the interrupt

request bit of the timer Ai interrupt control register is set when the

contents becomes 000016. At the same time, the contents of the reload

register are transferred to the counter, and count is continued.

Count start flag

(Address 4016)

Down count

Data bus (odd)

Data bus (even)

(Low-order

8 bits)

Reload register(16)

Counter(16)

Up/Down

Always decremented

except in event count mode

(High-order 8 bits)

Address

Timer A0 4716 46

Timer A1 4916 48

Timer A2 4B16 4A

Timer A3 4D16 4C

Timer A4 4F16 4E

16

16

16

16

16

Pulse output

TAi

OUT

(i = 0 – 4)

Fig. 13 Block diagram of timer A

Up-down flag

(Address 4416)

Toggle flip-flop

17

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

When bit 2 of the timer Ai mode register is “1”, the output is generated

from TAiOUT pin. The output is toggled each time the contents of the

counter reaches to 000016. When the contents of the count start flag

is “0”, “L” is output from TAiOUT pin.

When bit 2 is “0”, TAiOUT can be used as a normal port pin.

When bit 4 is “0”, TAiIN can be used as a normal port pin.

When bit 4 is “1”, counting is performed only while the input signal

from the TAiIN pin is “H” or “L” as shown in Figure 16. Therefore, this

can be used to measure the pulse width of the TAiIN input signal.

Whether to count while the input signal is “H” or while it is “L” is

determined by bit 3. If bit 3 is “1”, counting is performed while the

TAiIN pin input signal is “H” and if bit 3 is “0”, counting is performed

while it is “L”.

Timer A0 mode register 56

Timer A1 mode register 57

Timer A2 mode register 58

623451

70

0

00

Timer A3 mode register 59

Timer A4 mode register 5A

0 0 : Always “00” in timer mode

Note that the duration of “H” or “L” on the TAiIN pin must be two or

more cycles of the timer count sourse.

When data is written to the timer Ai register with timer Ai halted, the

same data is also written to the reload register and the counter. When

data is written to timer Ai which is busy, the data is written to the

reload register, but not to the counter. The counter is reloaded with

new data from the reload register at the next reload time. The contents

of the counter can be read at any time.

When the value set in the timer Ai register is n, the timer frequency

dividing ratio is 1/(n + 1).

Addresses

16

16

16

16

16

0 ✕ : No gate function (TAi

1

1

0 : Always “0” in timer mode

Clock source selection bit

0

0 1 : Select f16

1 0 : Select f64

1 1 : Select f512

Fig. 14 Timer Ai mode register bit configuration during timer mode

0 : No pulse output (TAiOUT is normal port pin)

1 : Pulse output

IN is normal port pin)

0 : Count only while TAiIN input is “L”

1 : Count only while TAiIN input is “H”

0 : Select f2

18

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Fig. 15 Count start flag bit configuration

Selected clock source f

TAi

i

N

70654321

Count start flag

(Stop at “0”, Start at “1”)

Timer A0 count start flag

Timer A1 count start flag

Timer A2 count start flag

Timer A3 count start flag

Timer A4 count start flag

Timer B0 count start flag

Timer B1 count start flag

Timer B2 count start flag

Address

40

16

Timer mode register

Bit 4 Bit 3

10

Timer mode register

Bit 4 Bit 3

11

11

Fig. 16 Count waveform when gate function is available

19

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

(2) Event counter mode [01]

Figure 17 shows the bit configuration of the timer Ai mode register

during the event counter mode. In the event counter mode, the bit 0

of the timer Ai mode register must be “1” and bits 1 and 5 must be

“0”.

The input signal from the TAiIN pin is counted when the count start

flag shown in Figure 15 is “1” and counting is stopped when it is “0”.

Count is performed at the fall of the input signal when bit 3 is “0” and

at the rise of the signal when it is “1”.

In the event counter mode, whether to increment or decrement the

count can be selected with the up-down flag or the input signal from

the TAiOUT pin.

When bit 4 of the timer Ai mode register is “0”, the up-down flag is

used to determine whether to increment or decrement the count

(decrement when the flag is “0” and increment when it is “1”). Figure

18 shows the bit configuration of the up-down flag.

When bit 4 of the timer Ai mode register is “1”, the input signal from

the TAiOUT pin is used to determine whether to increment or decrement

the count. However, note that bit 2 must be “0” if bit 4 is “1”. Because

TAiOUT pin becomes an output pin with pulse output if bit 2 is “1”.

The count is decremented when the input signal from the TAiOUT pin

is “L” and incremented when it is “H”. Determine the level of the input

signal from the TAiOUT pin before an effective edge is input to the

TAiIN pin.

An interrupt request signal is generated and the interrupt request bit

of the timer Ai interrupt control register is set when the counter reaches

000016 (decrement count) or FFFF16 (increment count). At the same

time, timers A0 and A1 transfer the contents of the reload register to

the counter and continue counting.

Timers A2, A3, and A4 transfer the contents of the reload register to

the counter and continue count when bit 6 of the corresponding timer

Ai mode register is “0”, but when bit 6 is “1”, they continue counting

without transferring the contents of the reload register to the counter.

When bit 2 is “1”, the waveform of which polarity is reversed each

time the counter reaches 000016 (decrement count) or FFFF16

(increment count) is output from TAiOUT pin. If bit 2 is “0”, the TAiOUT

pin can be used as a normal port pin. However, if bit 4 is “1” and the

TAiOUT pin is used as an output pin, the output from the TAiOUT pin

changes the count direction. Therefore, bit 4 must be “0” unless the

output from the TAiOUT pin is used to select the count direction.

Data write and data read are performed in the same way as for the

timer mode. That is, when data is written to timer Ai which is halted,

it is also written to the reload register and the counter.

When data is written to timer Ai which is busy, the data is written to

the reload register, but not the counter. The counter is reloaded with

new data from the reload register at the next reload time and continues

counting. For timers A2, A3, and A4, the contents of the reload register

is not reloaded in the counter when bit 6 of the corresponding timer

Ai mode register is “1”. The contents of the counter can be read at

any time.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Addresses

Timer A0 mode register 56

Timer A1 mode register 57

Timer A2 mode register 58

7 6543210

Timer A3 mode register 59

Timer A4 mode register 5A

001

0 1 : Always “01” in event counter

mode

0 : No pulse output

1 : Pulse output

0 : Count at the falling edge of input

signal

1 : Count at the rising edge of input

signal

0 : Increment or decrement according

to up-down flag

1 : Increment or decrement according

to TAi

0 : Always “0” in event counter mode

This bit is available for times A2, A3,

and A4.

0 : Reload

1 : No reload

This bit is available for timer A3.

0 : Two-phase pulse signal processing

in the same manner as timer A2

1 : Two-phase pulse signal processing

in the same manner as timer A4

OUT

pin input signal level

Fig. 17 Timer Ai mode register bit configuration during event counter

mode

7 6543210

Up-down flag

Timer A0 up-down flag

Timer A1 up-down flag

Timer A2 up-down flag

Timer A3 up-down flag

Timer A4 up-down flag

Timer A2 two-phase pulse signal processing

selection bit

0 : Two-phase pulse signal processing disabled

1 : Two-phase pulse signal processing mode

Timer A3 two-phase pulse signal processing

selection bit

0 : Two-phase pulse signal processing disabled

1 : Two-phase pulse signal processing mode

Timer A4 two-phase pulse signal processing

selection bit

0 : Two-phase pulse signal processing disabled

1 : Two-phase pulse signal processing mode

16

16

16

16

16

Addresses

44

16

20

Fig. 18 Up-down flag bit configuration

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

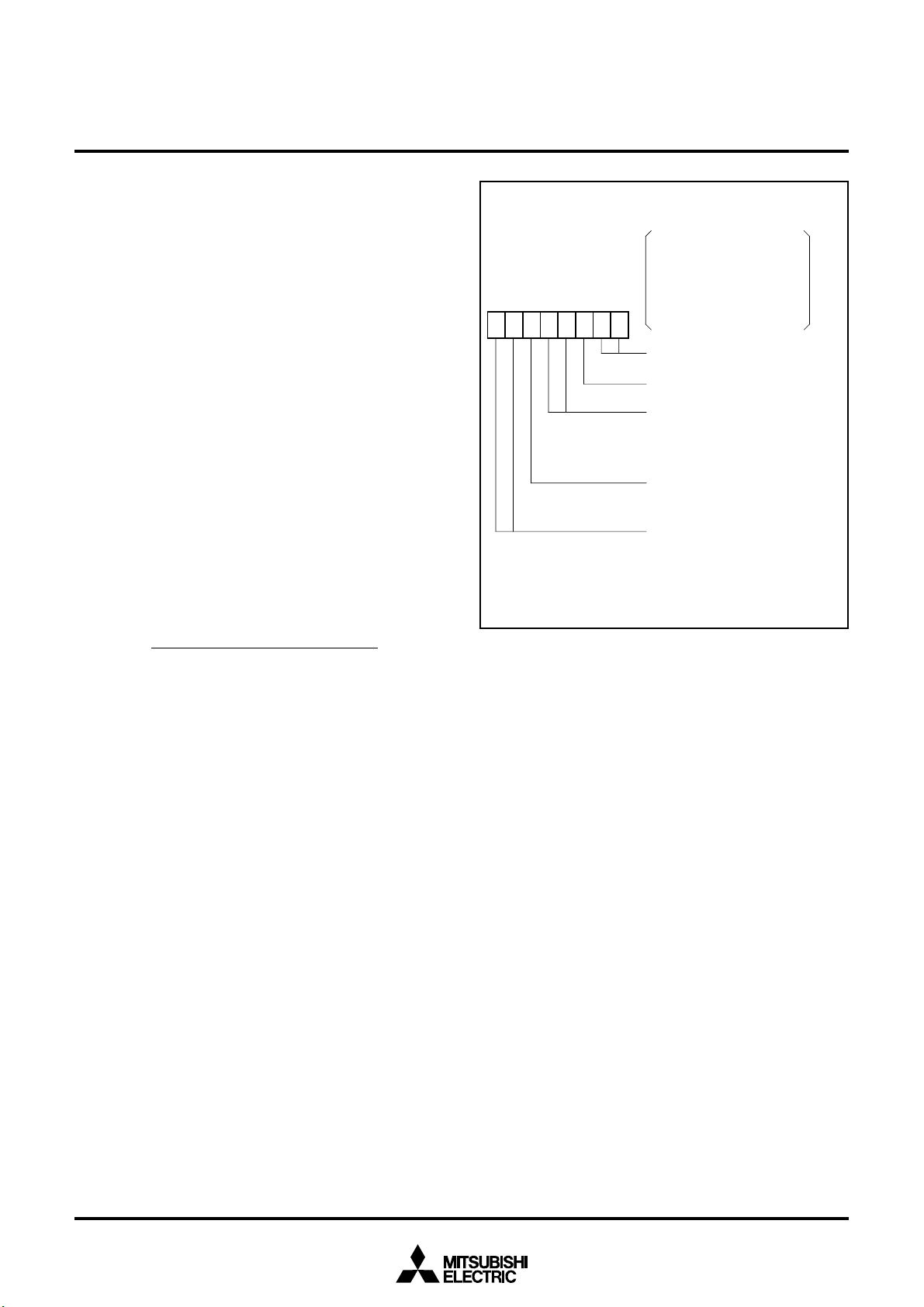

Furthermore, in the event counter mode, whether to increment or

decrement the counter can also be determined by supplying two kinds

of pulses of which phases differ by 90° to timer A2, A3, or A4. There

are two types of two-phase pulse signal processing operations. One

uses timer A2 and the other uses timer A4. Timer A3 can select one

of these two operations with bit 7 of the timer A3 mode register. In

both processing operations, two kinds of pulses of which phases differ

by 90° are input to the TAjOUT (j = 2 to 4) pin and TAjIN pin respectively.

After the level of the TA2OUT pin changes from “L” to “H” with timer

A2 used, as shown in Figure 19, the count is incremented when a

rising edge is input to the TA2IN pin and the count is decremented

when the falling edge is input.

For timer A4, as shown in Figure 20, when a phase related pulse

with a rising edge input to the TA4IN pin is input after the level of

TA4OUT pin changes from “L” to “H”, the count is incremented at the

respective rising edge and falling edge of the TA4OUT pin and TA4IN

pin. When a phase related pulse with a falling edge input to the TA4OUT

pin is input after the level of TA4IN pin changes from “H” to “L”, the

count is decremented at the respective rising edge and falling edge

of the TA4IN pin and TA4OUT pin.

When performing this two-phase pulse signal processing, bits 0 and

4 of the timer Aj mode register must be set to “1” and bits 1, 2, 3, and

5 must be set to “0” as shown in Figure 21.

Bit 7 is used to select whether to perform two-phase pulse signal

processing for timer A3 in the same manner as timer A2 or as timer

A4. When this bit is “0”, two-phase pulse signal processing for timer

A3 is performed in the same manner as timer A2 and when it is “1”, it

is performed in the same manner as timer A4. This bit is ignored for

timers A2 and A4.

Note that bits 5, 6, and 7 of the up-down flag (address 4416) are the

two-phase pulse signal processing selection bits for timers A2, A3,

and A4, respectively.

Each timer operates in the normal event counter mode when the

corresponding bit is “0” and performs two-phase pulse signal

processing when it is “1”.

Count is started by setting the count start flag to “1”. Data write and

read are performed in the same way as for the normal event counter

mode. Note that the port direction register of the input port must be

set to the input mode because two-phase pulse signal is input. Also,

there can be no pulse output in this mode.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

TA2

OUT

TA2

IN

Increment

Increment

Increment

Decrement

Decrement

count

count

count

count

Fig. 19 Two-phase pulse signal processing operation of timer A2

TA4

OUT

Increment count at each edge Decrement count at each edge

TA4

IN

Increment count at each edge Decrement count at each edge

Fig. 20 Two-phase pulse signal processing operation of timer A4

7 6543210

001

100

Timer A2 mode register 58

Timer A3 mode register 59

Timer A4 mode register 5A

0 1 : Always “01” in event counter

mode

0 1 0 0 : Always “0100” when processing

two-phase pulse signal

0 : Reload

1 : No reload

This bit is avilable for timer A3

0 : Two-phase pulse signal processing

in the same manner as timer A2

1 : Two-phase pulse signal processing

in the same manner as timer A4

count

Decrement

count

Addresses

16

16

16

Fig. 21 Timer Aj mode register bit configuration when performing

two-phase pulse signal processing in event counter mode

21

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

(3) One-shot pulse mode [10]

Figure 22 shows the bit configuration of the timer Ai mode resister

during the one-shot pulse mode. In the one-shot pulse mode, bit 0

and bit 5 must be “0” and bit 1 and bit 2 must be “1”.

The trigger is enabled when the count start flag is “1”. The trigger

can be generated by software, or it can be input from the TAi

Software trigger is selected when bit 4 is “0”, and the input signal

from the TAi

Bit 3 is used to determine whether to trigger at the fall of the trigger

signal or at the rise. The trigger is at the fall of the trigger signal when

bit 3 is “0” and at the rise of the trigger signal when bit 3 is “1”.

Software trigger is generated by setting the bit of the one-shot start

flag corresponding to each timer.

Figure 23 shows the bit configuration of the one-shot start flag.

As shown in Figure 24, when a trigger signal is received, the counter

counts the clock selected by bits 6 and 7.

If the contents of the counter is not 0000

when a trigger signal is received. The count direction is decrement.

When the counter reaches 0001

is stopped. The contents of the reload register is transferred to the

counter. At the same time, an interrupt request signal is generated,

and the interrupt request bit of the timer Ai interrupt control register is

set. This is repeated each time a trigger signal is received. The output

pulse width is

IN pin is used as the trigger when bit 4 is “1”.

16, the TAiOUT pin goes “H”

16, the TAiOUT pin goes “L” and count

IN pin.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Timer A0 mode register 5616

Timer A1 mode register 5716

Timer A2 mode register 5816

7 6543210

0101

Timer A3 mode register 5916

Timer A4 mode register 5A16

1 0 : Always “10” in one-shot

pulse mode

1 : Always “1” in one-shot pulse

mode

0 ✕ : Software trigger

1 0 : Trigger at the falling edge of

TAiIN input

1 1 : Trigger at the rising edge of

TAiIN input

0 : Always “0” in one-shot pulse

mode

Clock source selection

0 0 : Select f2

0 1 : Select f16

1 0 : Select f64

1 1 : Select f512

Addresses

1

pulse frequency of the selected clock

✕ (counter’s value at the time of trigger).

If the count start flag is “0”, the level of the TAiOUT pin goes “L”.

Therefore, the counter’s value corresponding to the desired pulse

width must be written to timer Ai before setting “1” to the timer Ai

count start flag.

As shown in Figure 25, a trigger signal can be received before the

operation for the previous trigger signal is completed. In this case,

the contents of the reload register is transferred to the counter by the

trigger, and then that value is decremented.

Except when retriggering while operating, the contents of the reload

register is not transferred to the counter by triggering.

When retriggering, there must be at least two timer count source

cycles before a new trigger can be issued.

Fig. 22 Timer Ai mode register bit configuration during one-shot

pulse mode

22

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

Data write is performed in the same way as for the timer mode. When

data is written in timer Ai halted, it is also written to the reload register

and the counter.

When data is written to timer Ai which is busy, the data is written to

the reload register, but not to the counter. The counter is reloaded

with new data from the reload register at the next reload time and

continues counting.

Undefined data is read when timer Ai is read.

MITSUBISHI MICROCOMPUTERS

M37733MHBXXXFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

70654321

70654321

One-shot start flag

One-shot start flag

Timer A0 one-shot start flag

Timer A0 one-shot start flag

Timer A1 one-shot start flag

Timer A1 one-shot start flag

Timer A2 one-shot start flag

Timer A2 one-shot start flag

Timer A3 one-shot start flag

Timer A3 one-shot start flag

Timer A4 one-shot start flag

Timer A4 one-shot start flag

Fig. 23 One-shot start flag bit configuration

Address

Address

16

16

42

42

Selected

Selected

clock source fi

clock source fi

TAiIN

TAiIN

(rising edge is

(rising edge is

selected)

selected)

TAi

TAi

OUT

OUT

In this case, the contents of the reload register is