MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

DESCRIPTION

The M37733EHBXXXFP is a single-chip microcomputer using the

7700 Family core. This single-chip microcomputer has a CPU and a

bus interface unit. The CPU is a 16-bit parallel processor that can be

an 8-bit parallel processor, and the bus interface unit enhances the

memory access efficiency to execute instructions fast. This

microcomputer also includes a 32 kHz oscillation circuit, in addition

to the PROM, RAM, multiple-function timers, serial I/O, A-D converter,

and so on.

The M37733EHBXXXFP has the same function as the

M37733MHBXXXFP except that the built-in ROM is PROM. (Refer

to the basic function blocks description.) For program development,

the M37733EHBFS with erasable ROM that is housed in a windowed

ceramic LCC is also provided.

FEATURES

●Number of basic instructions .................................................. 103

●Memory size PROM .............................................124 Kbytes

RAM................................................ 3968 bytes

●Instruction execution time

The fastest instruction at 25 MHz frequency ...................... 160 ns

M37733EHBFS

PROM VERSION OF M37733MHBXXXFP

●Single power supply ...................................................... 5 V ± 1 0%

●Low power dissipation (at 25 MHz frequency)

............................................47.5 mW (Typ.)

●Interrupts ............................................................ 19 types, 7 levels

●Multiple-function 16-bit timer ................................................. 5 + 3

●Serial I/O (UART or clock synchronous) ..................................... 3

●10-bit A-D converter ............................................ 8-channel inputs

●Watchdog timer

●Programmable input/output

(ports P0, P1, P2, P3, P4, P5, P6, P7, P8) ............................... 68

●Clock generating circuit ........................................ 2 circuits built-in

APPLICATION

Control devices for general commercial equipment such as office

automation, office equipment, and so on.

Control devices for general industrial equipment such as

communication equipment, and so on.

Note. Do not use the windowed EPROM version for mass production,

because it is a tool for program development (for evaluation).

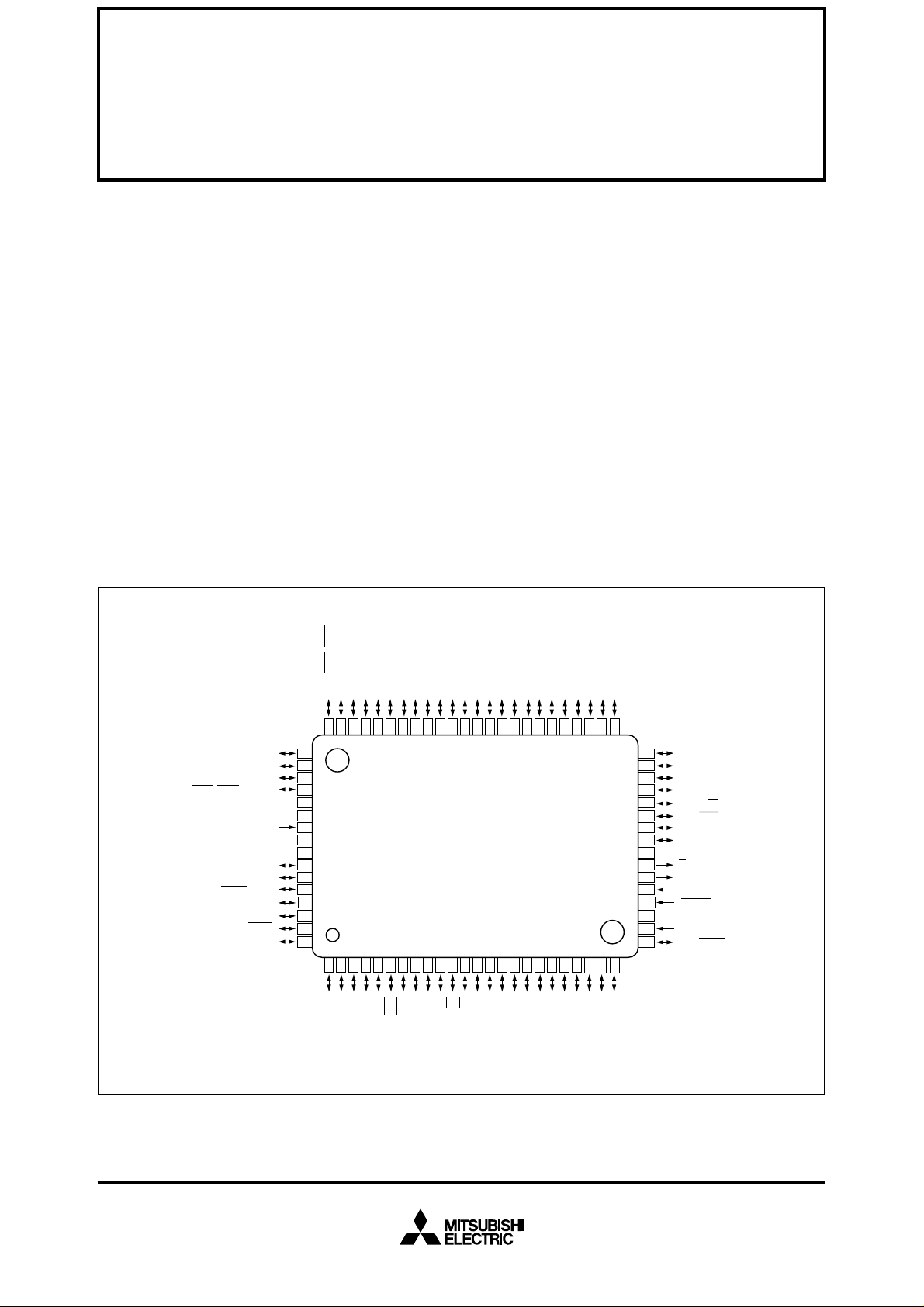

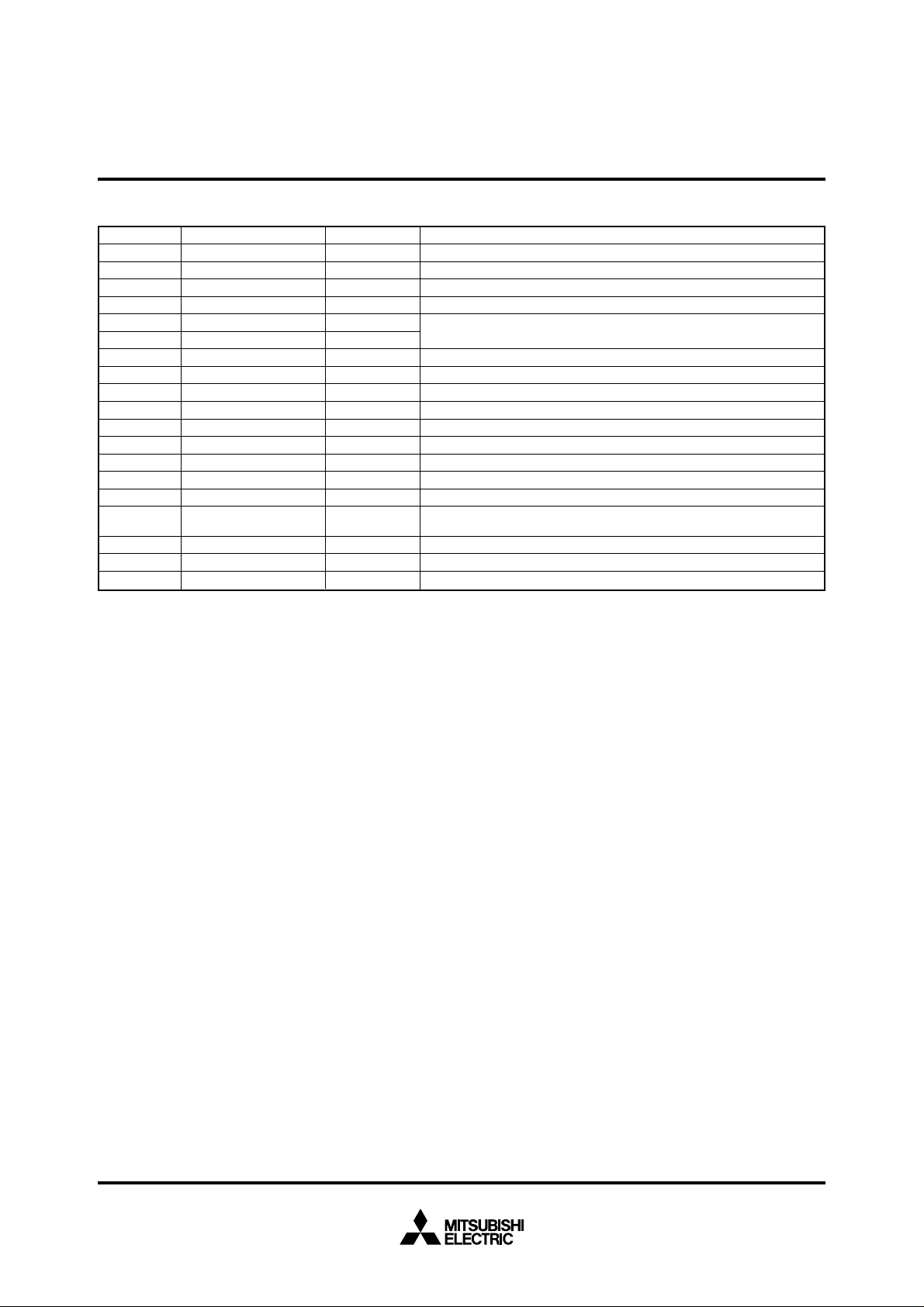

PIN CONFIGURATION (TOP VIEW)

1

RTS

/

1

1

CTS

/

/CLK

4

5

P8

P8

646362

V

REF

V

OUT

65

0

66

0

67

0

6

8

1

69

CC

70

CC

71

72

SS

73

SS

74

IN

75

76

2

77

2

78

2

79

2

80

1

1

2

0

SUB

/AN

/φ

0

IN

P7

/TB2

7

P6

P82/RXD0/CLKS

P8

0

/CTS0/RTS0/

P76/AN6/Xc

P75/AN5/

P83/TXD

P81/CLK

CLKS

AV

V

AV

P77/AN7/Xc

AD

TRG

/TxD

P74/AN4/RxD

P73/AN3/CLK

P72/AN2/CTS

P71/AN

1

D

X

/R

6

P8

3

IN

/TB1

6

P6

1

D

X

/T

7

P8

61

4

IN

/TB0

5

P6

0

1

2

3

4

A

A

/

/

0

1

P0

P0

59

60

5

A

A

A

A

/

/

/

/

2

3

4

5

P0

P0

P0

P0

57

58

56

55

M37733EHBXXXFP

9

8

10

7

6

5

2

1

0

3

IN

KI

OUT

NT

/I

2

P6

/TA4

1

P6

/TA4

0

P6

/

IN

/TA3

7

P5

NT

/I

4

P6

NT

/I

3

P6

6

/A

6

P0

54

11

2

KI

/

OUT

/TA3

6

P5

7

/A

7

P0

53

12

1

KI

/

IN

/TA2

5

P5

8

/D

8

/A

0

P1

52

13

0

KI

/

OUT

/TA2

4

P5

9

/D

9

/A

1

P1

51

14

IN

/TA1

3

P5

10

/D

10

/A

2

P1

50

15

OUT

/TA1

2

P5

11

/D

11

/A

3

P1

49

16

IN

/TA0

1

P5

12

/D

12

/A

4

P1

48

17

OUT

/TA0

0

P5

13

14

15

0

/D

/D

/D

/D

13

14

15

16

/A

/A

/A

/A

5

6

7

0

P1

P1

P1

P2

47

46

44

45

21

18

20

19

P47P46P45P44P4

1

2

3

/D

/D

/D

17

18

19

/A

/A

/A

1

2

3

P2

P2

P2

41

42

43

40

P24/A20/D

39

P25/A21/D

38

P26/A22/D

37

P27/A23/D

36

P30/

35

P31/

34

P32/

33

P33/

32

V

31

E

30

X

29

X

28

RESET

27

CNV

26

BYTE

25

P40/

24

23

22

1

3

/φ

2

RDY

/

1

P4

P4

Outline 80P6N-A

ss

OUT

IN

R/W

BHE

ALE

HLDA

SS

HOLD

4

5

6

7

1

XIN

XOUT

E

RESET

Reset input

VREF

P8(8) P7(8) P5(8)P6(8) P4(8) P3(4)

P2(8) P1(8)

CNVss

BYTE

P0(8)

UART1(9)

UART0(9)

AVSS

(0V)

AVCC

(0V)

V

SS

V

CC

A-D Converter(10)

XCIN

XCOUT

X

CIN

X

COUT

Clock input Clock output

Enable output

Reference

voltage input

External data bus width

selection input

Clock Generating Circuit

Instruction Register(8)

Arithmetic Logic

Unit(16)

Accumulator A(16)

Accumulatcr B(16)

Index Register X(16)

Index Register Y(16)

Stack Pointer S(16)

Direct Page Register DPR(16)

Processor Status Register PS(11)

Input Butter Register IB(16)

Data Bank Register DT(8)

Program Bank Register PG(8)

Program Counter PC(16)

Incrementer/Decrementer(24)

Data Address Register DA(24)

Program Address Register PA(24)

Incrementer(24)

Instruction Queue Buffer Q

2

(8)

Instruction Queue Buffer Q

1

(8)

Instruction Queue Buffer Q

0

(8)

Data Buffer DB

L

(8)

Data Buffer DB

H

(8)

PROM

124 Kbytes

RAM

3968 bytes

Timer TA3(16)

Timer TA4(16)

Timer TA2(16)

Timer TA1(16)

Timer TA0(16)

Watchdog Timer

Timer TB2(16)

Timer TB1(16)

Timer TB0(16)

Address Bus

Data Bus(Odd)

Data Bus(Even)

Input/Output

port P8

Input/Output

port P7

Input/Output

port P6

Input/Output

port P5

Input/Output

port P4

Input/Output

port P3

Input/Output

port P2

Input/Output

port P1

Input/Output

port P0

UART2(9)

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

PROM VERSION OF M37733MHBXXXFP

M37733EHBFS

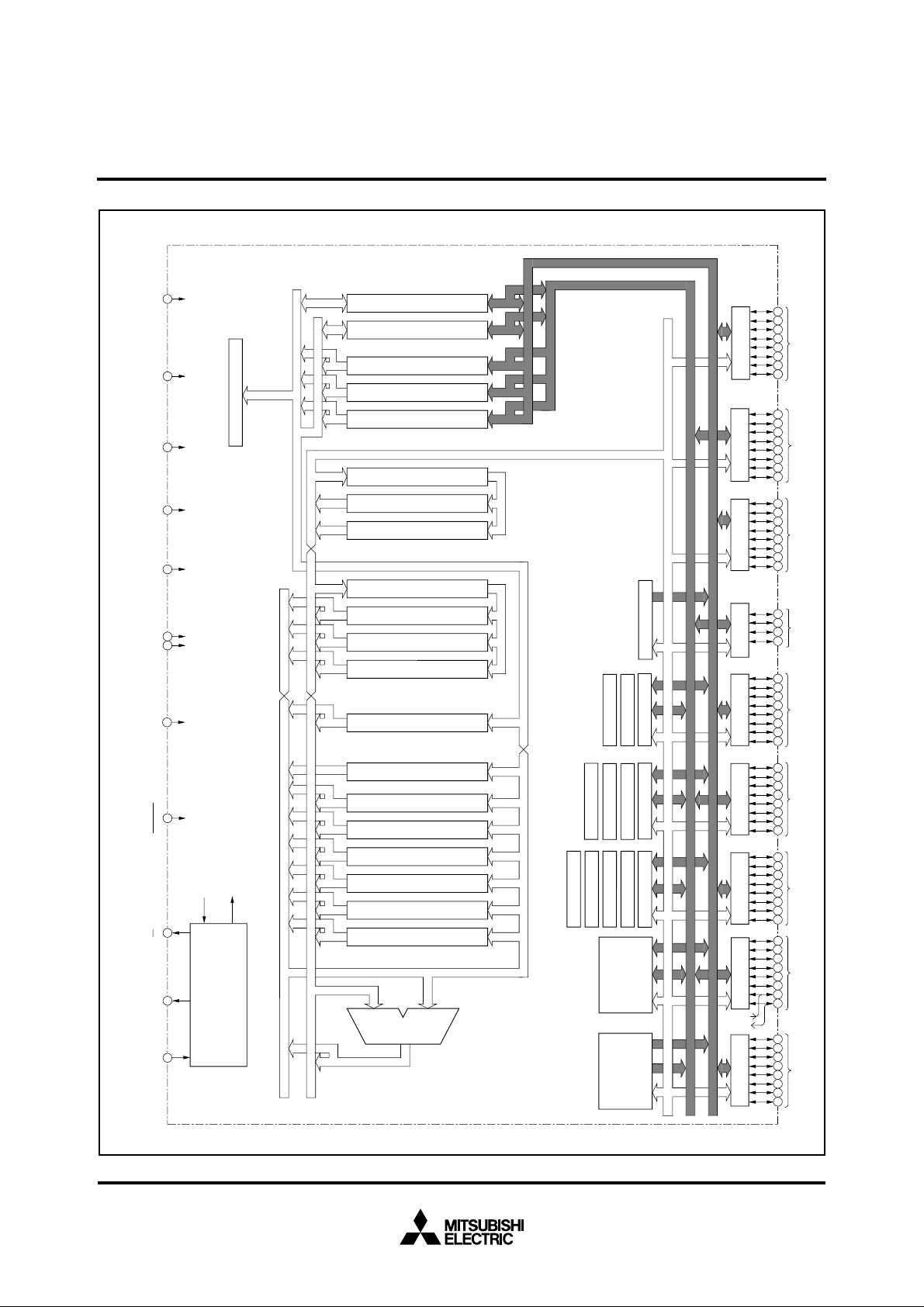

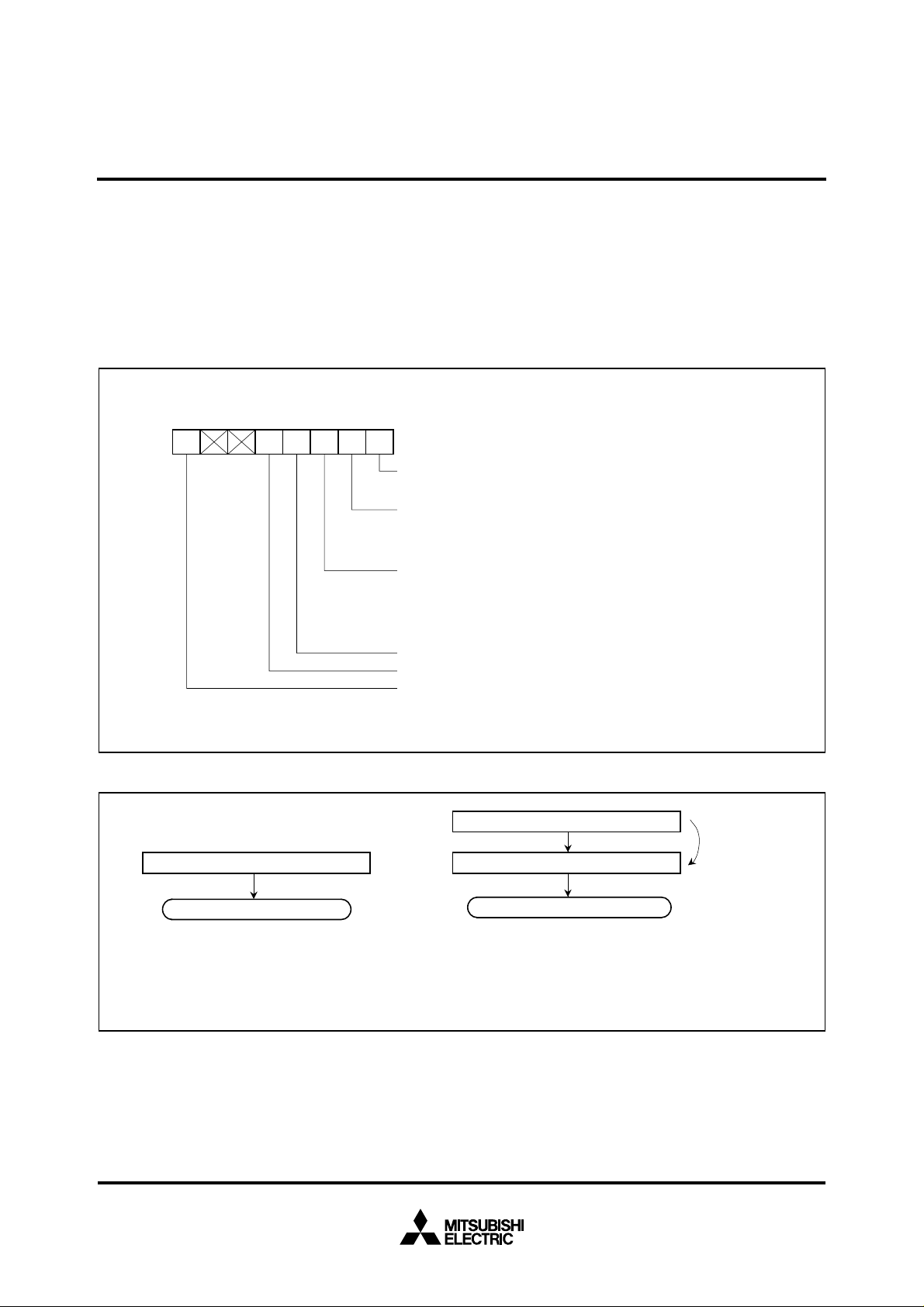

M37733EHBXXXFP BLOCK DIAGRAM

2

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

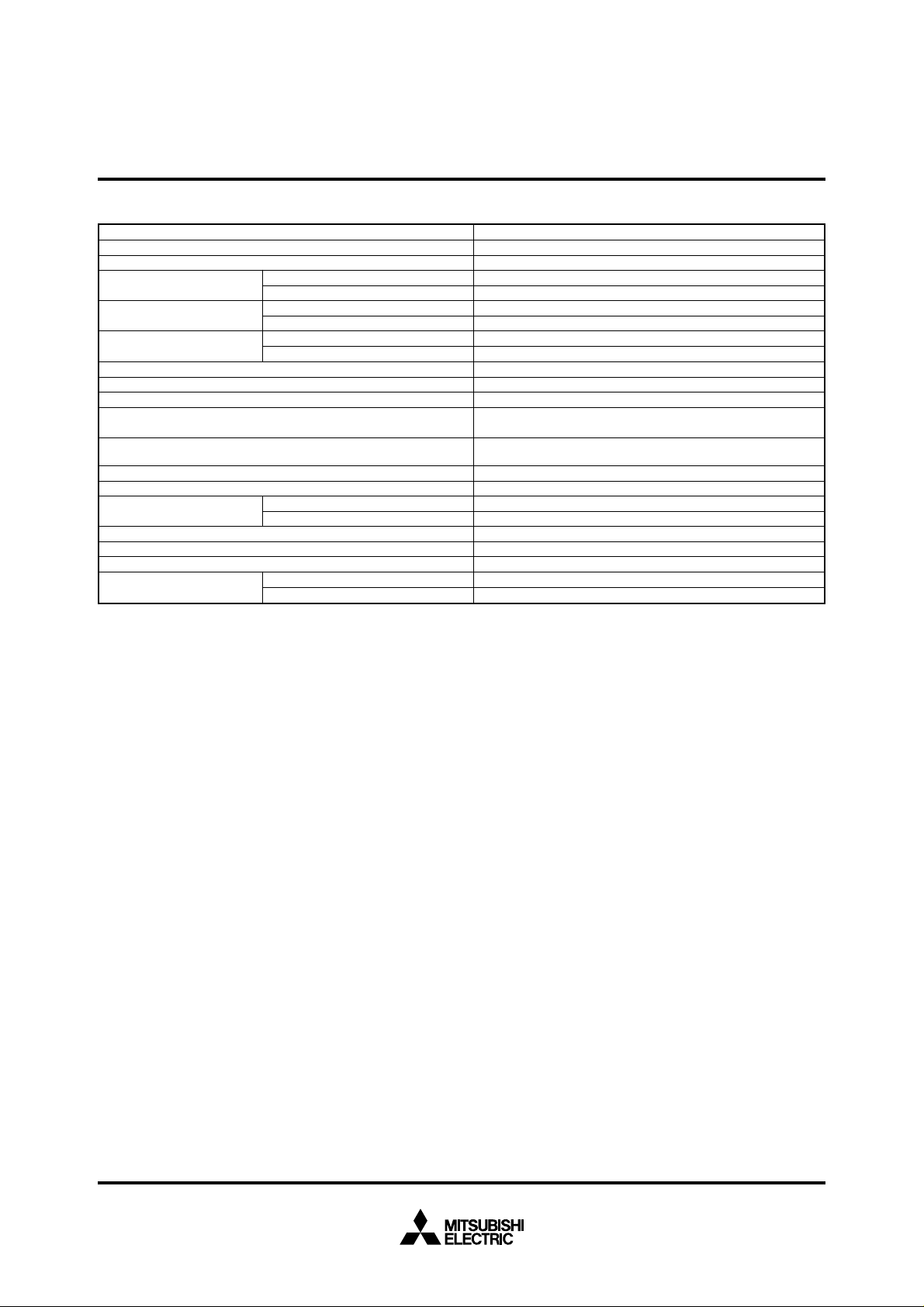

FUNCTIONS OF M37733EHBXXXFP

Number of basic instructions 103

Instruction execution time 160 ns (the fastest instruction at external clock 25 MHz frequency)

Memory size

Input/Output ports

Multi-function timers

Serial I/O (UART or clock synchronous serial I/O) ✕ 3

A-D converter 10-bit ✕ 1 (8 channels)

Watchdog timer 12-bit ✕ 1

Interrupts

Clock generating circuit

Supply voltage 5 V ± 10%

Power dissipation 47.5 mW (at external clock 25 MHz frequency)

Input/Output characteristic

Memory expansion Maximum 16 Mbytes

Operating temperature range –20 to 85 °C

Device structure CMOS high-performance silicon gate process

Package

Parameter Functions

PROM 124 Kbytes

RAM 3968 bytes

P0 – P2, P4 – P8 8-bit ✕ 8

P3 4-bit ✕ 1

TA0, TA1, TA2, TA3, TA4 16-bit ✕ 5

TB0, TB1, TB2 16-bit ✕ 3

3 external types, 16 internal types

Each interrupt can be set to the priority level (0 – 7.)

2 circuits built-in (externally connected to a ceramic resonator or a

quartz-crystal oscillator)

Input/Output voltage 5 V

Output current 5 mA

M37733EHBXXXFP 80-pin plastic molded QFP (80P6N-A)

M37733EHBFS 80-pin ceramic LCC (with a window) (80D0)

PROM VERSION OF M37733MHBXXXFP

M37733EHBFS

3

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

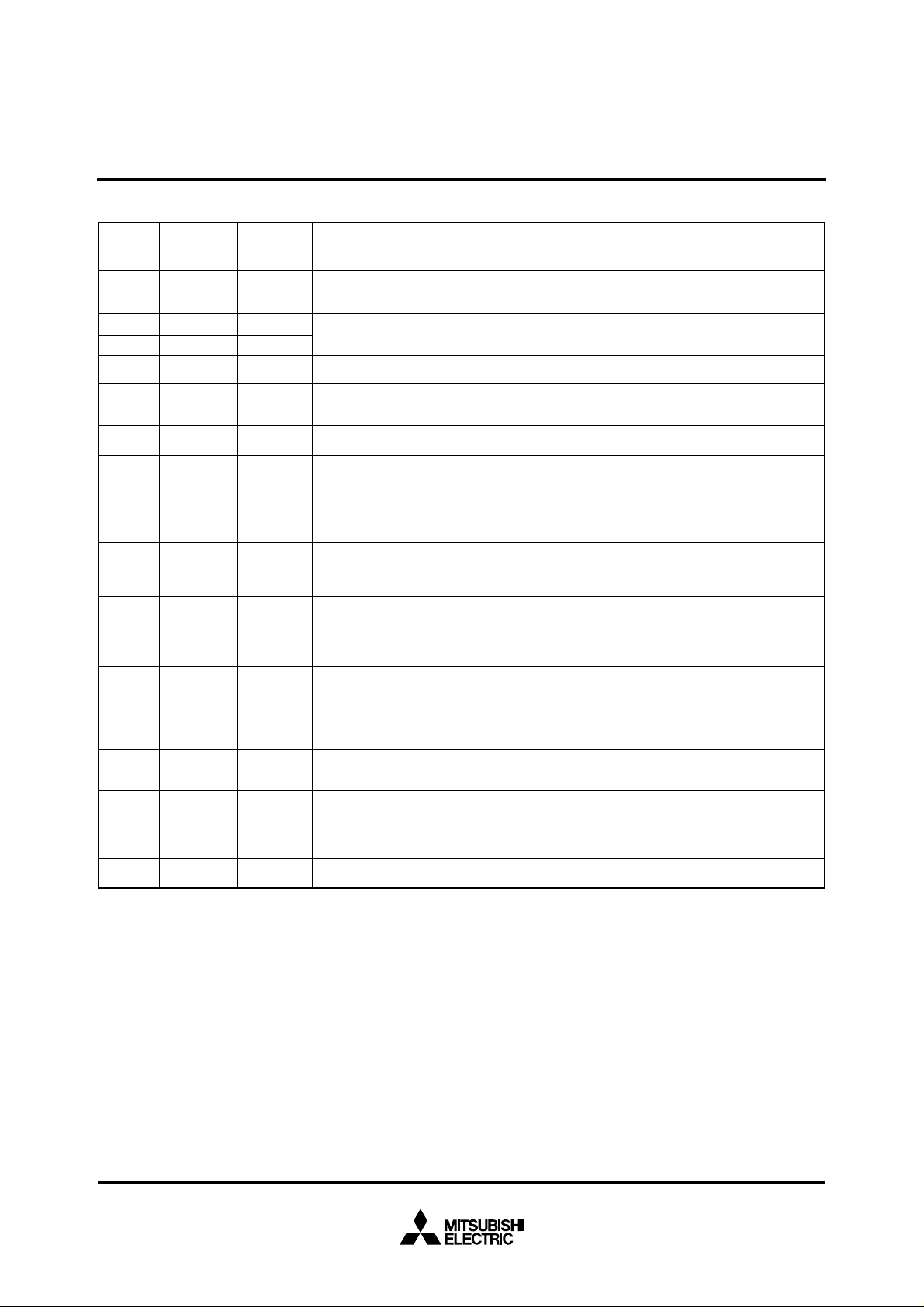

PIN DESCRIPTION

Pin Name Input/Output Functions

Vcc, Power source Apply 5 V ± 10% to Vcc and 0 V to Vss.

Vss

CNVss CNVss input Input This pin controls the processor mode. Connect to Vss for the single-chip mode and the memory

_____

RESET Reset input Input When “L” level is applied to this pin, the microcomputer enters the reset state.

XIN Clock input Input

XOUT Clock output Output

_

E Enable output Output This pin functions as the enable signal output pin which indicates the access status in the internal

BYTE

External data

Input In the memory expansion mode or the microprocessor mode, this pin determines whether the

bus width

selection input

AVcc, Analog power Power source input pin for the A-D converter. Externally connect AVcc to Vcc and AVss to Vss.

AVss source input

REF Reference Input This is reference voltage input pin for the A-D converter.

V

voltage input

0 – P07 I/O port P0 I/O In the single-chip mode, port P0 becomes an 8-bit I/O port. An I/O direction register is available so

P0

0 – P17 I/O port P1 I/O In the single-chip mode, these pins have the same functions as port P0. When the BYTE pin is set

P1

0 – P27 I/O port P2 I/O In the single-chip mode, these pins have the same functions as port P0. In the memory expansion

P2

0 – P33 I/O port P3 I/O In the single-chip mode, these pins have the same function as port P0. In the memory expansion

P3

0 – P47 I/O port P4 I/O In the single-chip mode, these pins have the same functions as port P0. In the memory expansion

P4

0 – P57 I/O port P5 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P5

0 – P67 I/O port P6 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P6

0 – P77 I/O port P7 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins function as

P7

0 – P87 I/O port P8 I/O In addition to having the same functions as port P0 in the single-chip mode, these pins also

P8

expansion mode, and to Vcc for the microprocessor mode.

These are pins of main-clock generating circuit. Connect a ceramic resonator or a quartzcrystal oscillator between X

IN and XOUT. When an external clock is used, the clock source should

be connected to the XIN pin, and the XOUT pin should be left open.

bus. When output level of E signal is “L”, data/instruction read or data write is performed.

_

external data bus has an 8-bit width or a 16-bit width. The data bus has a 16-bit width when “L”

signal is input and an 8-bit width when “H” signal is input.

that each pin can be programmed for input or output. These ports are in the input mode when

reset.

In the memory expansion mode or the microprocessor mode, these pins output address (A0 – A7).

to “L” in the memory expansion mode or the microprocessor mode and external data bus has a

16-bit width, high-order data (D8 – D15) is input/output or an address (A8 – A15) is output. When

the BYTE pin is “H” and an external data bus has an 8-bit width, only address (A8 – A15) is output.

mode or the microprocessor mode, low-order data (D

(A0 – A7) is output .

mode or the microprocessor mode, R/W, BHE, ALE, and HLDA signals are output.

__ ____ _____

mode or the microprocessor mode, P40, P41, and P42 become HOLD and RDY input pins, and a

clock

φ1 output pin, respectively. Functions of the other pins are the same as in the single-chip

mode. However, in the memory expansion mode, P42 can be selected as an I/O port.

function as I/O pins for timers A0 to A3 and input pins for key input interrupt input (KI0 – KI3 ).

function as I/O pins for timer A4, input pins for external interrupt input (INT0 – INT2) and input pins

for timers B0 to B2. P67 also functions as sub-clock φSUB output pin.

input pins for A-D converter. P7

7 have the function as the output pin (XCOUT) and the input pin (XCIN) of the sub-clock (32 kHz)

P7

oscillation circuit, respectively. When P7

2 to P75 also function as I/O pins for UART2. Additionally, P76 and

6 and P77 are used as the XCOUT and XCIN pins, connect

a resonator or an oscillator between the both.

function as I/O pins for UART 0 and UART 1.

PROM VERSION OF M37733MHBXXXFP

0 – D7) is input/output or an address

M37733EHBFS

_____ ____

__ __

____ ____

4

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

PIN DESCRIPTION (EPROM MODE)

Pin

VCC, VSS

CNVSS

BYTE

_____

RESET

XIN

XOUT

_

E

AVCC, AVSS

VREF

P00 – P07

P10 – P17

P20 – P27

P30

P31 – P33

P40 – P47

P50 – P57

P60 – P67

P70 – P77

P80 – P87

Power supply

VPP input

VPP input

Reset input

Clock input

Clock output

Enable output

Analog supply input

Reference voltage input

Address input (A0 – A7)

Address input (A8 – A15)

Data I/O (D0 – D7)

Address input (A16)

Input port P3

Input port P4

Control signal input

Input port P6

Input port P7

Input port P8

Name

Input/Output

Input

Input

Input

Input

Output

Output

Input

Input

Input

I/O

Input

Input

Input

Input

Input

Input

Input

PROM VERSION OF M37733MHBXXXFP

Functions

Supply 5V±10% to VCC and 0V to VSS.

Connect to VPP when programming or verifing.

Connect to VPP when programming or verifing.

Connect to VSS.

Connect a ceramic resonator between XIN and XOUT.

Keep open.

Connect AVCC to VCC and AVSS to VSS.

Connect to VSS.

Port P0 functions as the lower 8 bits address input (A0 – A7).

Port P1 functions as the higher 8 bits address input (A8 – A15).

Port P2 functions as the 8 bits data input/output (D0 – D7).

P30 functions as the most significant bit address input (A16).

Connect to VSS.

Connect to VSS.

P50, P51, and P52 function as PGM, OE, and CE input pins respectively.

Connect P5

Connect to VSS.

Connect to VSS.

Connect to VSS.

3, P54, P55, and P56 to VCC. Connect P57 to VSS.

_____ ___ ___

M37733EHBFS

5

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

PROM VERSION OF M37733MHBXXXFP

M37733EHBFS

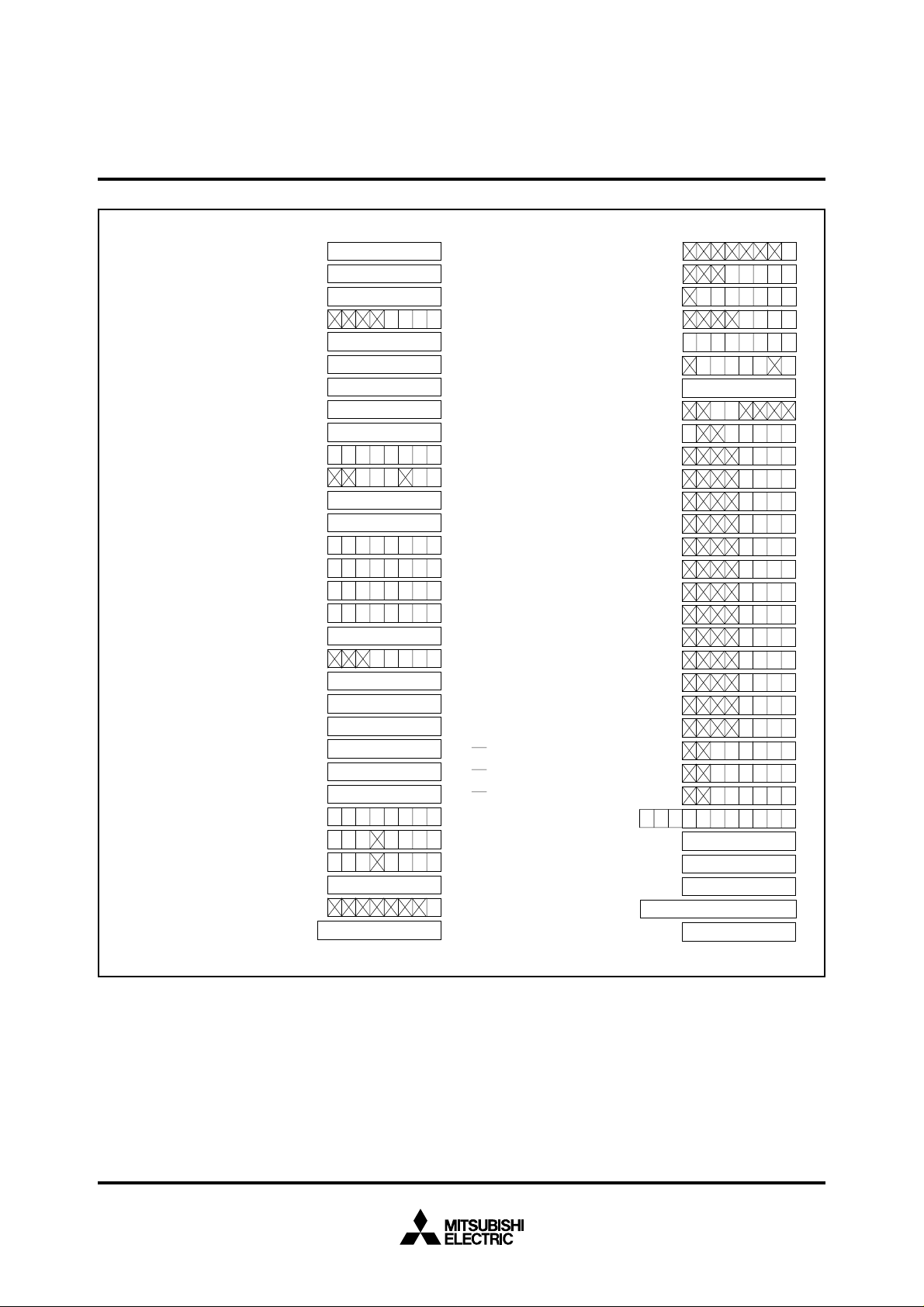

BASIC FUNCTION BLOCKS

The M37733EHBXXXFP has the same functions as the

M37733MHBXXXFP except for the following:

(1) The built-in ROM is PROM.

(2) The status of bit 3 of the oscillation circuit control register 1 (address

6F

16) at a reset is different.

(3) The usage condition of bit 3 of the oscillation circuit control register

1 is different.

76543210

1

0

CC

CC

2

Oscillation circuit control register 1

CC

0

1

Main clock division selection bit

0 : Main clock is divided by 2.

1 : Main clock is not divided by 2.

Main clock external input selection bit

0 : Main-clock oscillation circuit is operating by itself.

Watchdog timer is used at returning from STP state.

1 : Main-clock is input externally.

Watchdog timer is not used at returning from STP state.

Sub clock external input selection bit

0 : Sub-clock oscillation circuit is operating by itself.

Port P7

Watchdog timer is used at returning from STP state.

1 : Sub-clock is input externally.

Port P7

Watchdog timer is not used at returning from STP state.

1 : Always “1” (“1” at reset)

0 : Always “0” (However, writing data “55

Clock prescaler reset bit

Accordingly, refer to the basic function blocks description in the

M37733MHBXXXFP except for Figure 1 (bit configuration of the

oscillation circuit control register 1) and Figure 3 (microcomputer

internal status during reset).

In the M37733EHBXXXFP, bit 3 of the oscillation circuit control

register 1 must be “1”. (Refer to Figure 1.) The status of this bit at

a reset is “1”.

Address

16

6F

Note. Write to the oscillation circuit control

register 1 as the flow shown in Figure 2.

6

functions as X

6

functions as I/O port.

COUT

pin.

16

” shown in Figure 2 is possible.)

Fig. 1 Bit configuration of oscillation circuit control register 1 (corresponding to Figure 63 in data sheet “M37733MHBXXXFP”)

Writing data “55

16

” (LDM instruction)

Next instruction

16

Writing data “8016” (LDM instruction)

Reset clock prescaler

Writing data “0Y

CC

• How to reset clock prescaler • How to write in CC

” (LDM instruction)

2

to CC0 selection bits

2

to CC0 selection bits

Note. “Y” is the sum of bits to be set. For example, when

setting bits 2 and 1 to “1”, “Y” becomes “6”.

Fig. 2 How to write data in oscillation circuit control register 1 (identical with Figure 64 in data sheet “M37733MHBXXXFP”)

6

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

PROM VERSION OF M37733MHBXXXFP

M37733EHBFS

Address

Port P0 direction register

Port P1 direction register

Port P2 direction register

Port P3 direction register

Port P4 direction register

Port P5 direction register

Port P6 direction register

Port P7 direction register

Port P8 direction register

A-D control register 0

A-D control register 1

UART 0 transmit/receive mode register

UART 1 transmit/receive mode register

UART 0 transmit/receive

control register 0

UART 1 transmit/receive

control register 0

UART 0 transmit/receive

control register 1

UART 1 transmit/receive

control register 1

Count start flag

One- shot start flag

Up-down flag

Timer A0 mode register

Timer A1 mode register

Timer A2 mode register

Timer A3 mode register

Timer A4 mode register

Timer B0 mode register

Timer B1 mode register

Timer B2 mode register

Processor mode register 0

Processor mode register 1

Watchdog timer register

(0416)

(0516)

(0816)

(0916)

(0C16)

(0D16)

(1016)

(1116)

(1416)

(1E16)

(1F16)

(3016)

(3816)

(3416)

(3C16)

(3516)

(3D16)

(4016)

(4216)

(4416)

(5616)

(5716)

(5816)

(5916)

(5A16)

(5B16)

(5C16)

(5D16)

(5E16)

(5F16)

(6016)

•••

•••

•••

•••

•••

•••

•••

•••

•••

0000

•••

0

•••

•••

•••

•••

0000

•••

0000

•••

0000

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

001

•••

001 00 00

•••

•••

•••

•••

00

16

00

16

00

16

0000

00

16

00

16

00

16

00

16

00

16

0

00

16

00

00

16

1000

000010

16

00

000 00

00

16

00

16

00

16

00

16

00

16

00

16

0001 00 00

00 00

00

16

FFF

16

???

11

0000

0010

10

0

Address

Watchdog timer frequency selection flag

Memory allocation control register

UART2 transmit/receive mode register

UART2 transmit/receive control register 0

UART2 transmit/receive control register 1

Oscillation circuit control register 0

Port function control register

Serial transmit control register

Oscillation circuit control register 1

A-D/UART2 trans./rece. interrupt control register

UART 0 transmission interrupt control register

UART 0 receive interrupt control register

UART 1 transmission interrupt control register

UART 1 receive interrupt control register

Timer A0 interrupt control register

Timer A1 interrupt control register

Timer A2 interrupt control register

Timer A3 interrupt control register

Timer A4 interrupt control register

Timer B0 interrupt control register

Timer B1 interrupt control register

Timer B2 interrupt control register

INT

0

interrupt control register

INT

1

interrupt control register

INT

2

/Key input interrupt control register

Processor status register (PS)

Program bank register (PG)

H

Program counter (PC

Program counter (PC

Direct page register (DPR)

Data bank register (DT)

)

L

)

(6116)

(6316)

(6416)

(6816)

(69

(6C16)

(6D16)

(6E16)

(6F16)

(7016)

(7116)

(7216)

(7316)

(7416)

(7516)

(7616)

(7716)

(7816)

(7916)

(7A16)

(7B16)

(7C16)

(7D16)

(7E16)

(7F16)

16)•••

•••

0 0

•••

0 000000

•••

•••

0 0100000

0

00

0 01000

0

•••

0

•••

00

00

•••

0

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

•••

0

•••

0

•••

0

•••

?000

?

Content of FFFF

Content of FFFE

0000

000

00

1

0

00

16

1

0

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0

0

0

0

0

0

0

00

16

00

16

00

16

0

0

0

001

00

000

001

000

000

000

000

1??

16

16

Fig. 3 Microcomputer internal status during reset

Contents of other registers and RAM are undefined during reset. Initialize them by software.

7

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

PROM VERSION OF M37733MHBXXXFP

M37733EHBFS

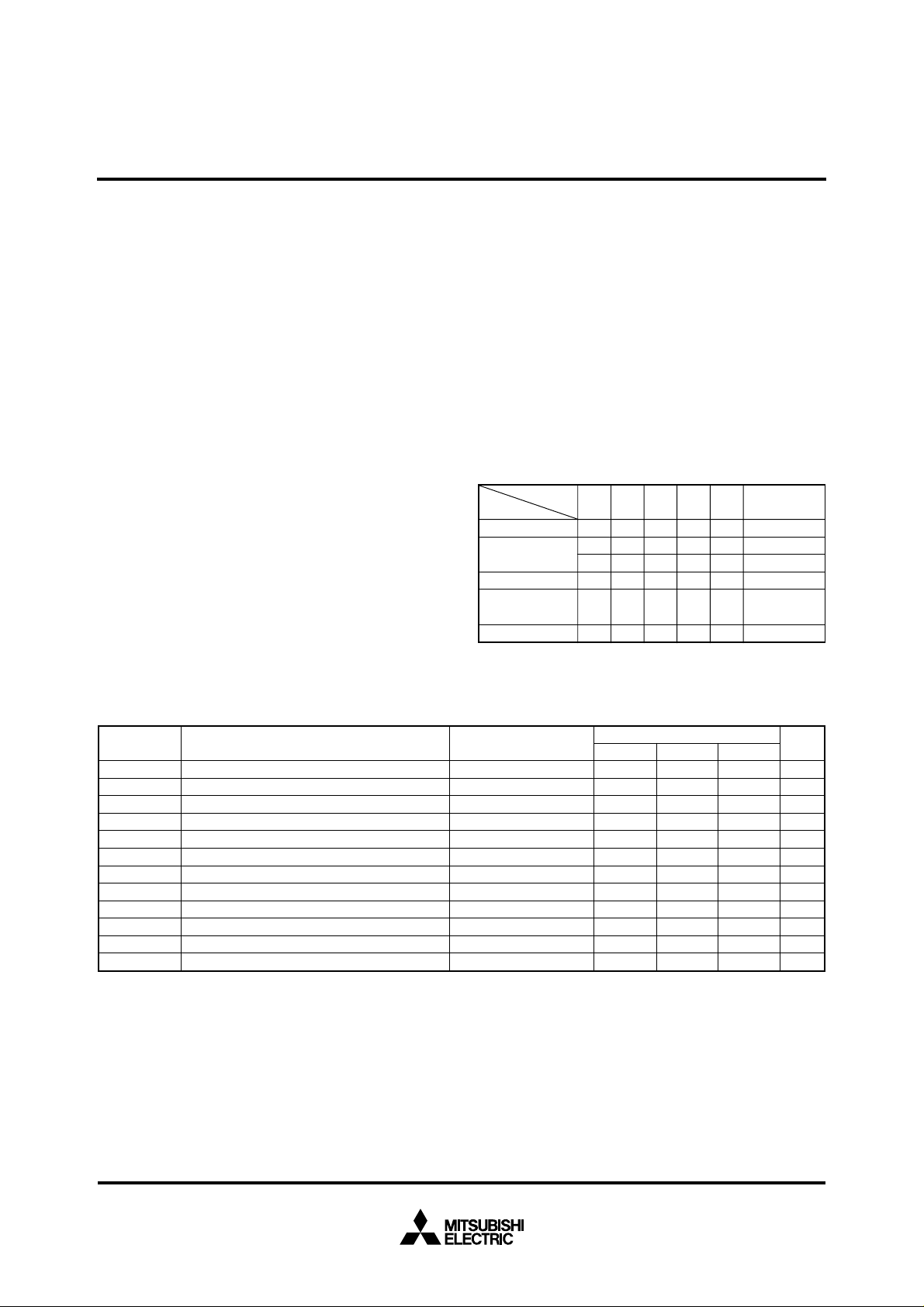

EPROM MODE

The M37733EHBXXXFP features an EPROM mode in addition to its

normal modes. When the RESET signal level is “L”, the chip

automatically enters the EPROM mode. Table 1 list the

correspondence between pins and Figure 4 shows the pin

connections in the EPROM mode.

The EPROM mode is the 1M mode for the EPROM that is equivalent

to the M5M27C101K.

When in the EPROM mode, ports P0, P1, P2, P3

CNV

SS, and BYTE are used for the EPROM (equivalent to the

Table 1 Pin function in EPROM mode

M37733EHBXXXFP

VCC

VPP

VSS

Address input

Data I/O

___

CE

___

OE

_____

PGM

_____

VCC

CNVSS, BYTE

VSS

Ports P0, P1, P30

Port P2

P52

P51

P50

0, P50, P51, P52,

M5M27C101K

VCC

VPP

VSS

A0 – A16

D0 – D7

___

CE

___

OE

_____

PGM

M5M27C101K).

When in this mode, the built-in PROM can be programmed or read

from using these pins in the same way as with the M5M27C101K.

This chip does not have Device Identifier Mode, so that set the

corresponding program algorithm. The program area should specify

address 01000

16 – 1FFFF16.

Connect the clock which is either ceramic resonator or external clock

to X

IN pin and XOUT pin.

8

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

PROM VERSION OF M37733MHBXXXFP

A6

A7

A0

A1

A2

A3

A8

A4

A9

A5

A10

A11

D0

D1

D2

A13

A14

A12

D3

A15

M37733EHBFS

P81/CLK0

VCC

P80/CTS0/RTS 0/CLKS1

VCC

AVCC

VREF

AVSS

VSS

Fig. 4 Pin connection in EPROM mode

P04/A4

P84/CTS1/RTS 1

P86/RXD1

P87/TXD1

P00/A0

P85/CLK1

↔

↔

↔

↔

↔

62

61

63

64

65

↔ P83/TXD0

66

↔ P82/RXD0/CLKS0

67

↔

68

↔

69

70

71

→

72

73

74

↔ P77/AN7/XCIN

75

↔ P76/AN6/XCOUT

76

↔ P75/AN5/ADTRG /TXD2

77

↔ P74/AN4/RXD2

78

↔ P73/AN3/CLK2

79

↔ P72/AN2/CTS2

80

↔ P71/AN1

60

3

4

5

1

2

↔

↔

↔

↔

↔

P64/INT2

P70/AN0

P66/TB1IN

P65/TB0IN

P67/TB2IN/φSUB

P05/A5

P06/A6

P03/A3

P01/A1

P02/A2

↔

↔

↔

↔

↔

↔

58

57

56

59

54

55

M37733EHBXXXFP

7

8

9

6

10

11

↔

↔

P63/INT1

↔

↔

↔

↔

P62/INT0

P61/TA4IN

P60/TA4OUT

P57/TA3IN/KI3

P56/TA3OUT/KI2

P13/A11/D11

P10/A8/D8

P11/A9/D9

P07/A7

P12/A10/D10

↔

↔

↔

↔

↔

53

52

49

51

50

12

13

14

15

16

↔

↔

↔

↔

↔

P51/TA0IN

P53/TA1IN

P52/TA1OUT

P55/TA2IN/KI1

P54/TA2OUT/KI0

CE

OE

48

17

P14/A12/D12

↔

↔

P50/TA0OUT

PGM

P20/A16/D0

P21/A17/D1

P15/A13/D13

↔

47

18

↔

P47

P22/A18/D2

P16/A14/D14

↔

46

19

↔

P46

P23/A19/D3

P17/A15/D15

↔

↔

↔

↔

↔

45

44

41

42

43

40

↔P24/A20/D4

39

↔P25/A21/D5

38

↔P26/A22/D6

37

↔P27/A23/D7

36

↔P30/R/W

35

↔P31/BHE

34

↔P32/ALE

33

↔P33/HLDA

32

VSS

31

→ E

30

→ XOUT

29

← XIN

28

← RESET

27

CNVSS

26

← BYTE

25

21

20

↔

↔

P45

P44

↔P40/HOLD

22

23

24

↔

↔

↔

φ1

P43

P42/

P41/RDY

D4

D5

D6

D7

A16

VSS

∗

VPP

✽ : Connect to ceramic oscillation circuit.

Outline 80P6N-A

: It is used in the EPROM mode.

9

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

PROM VERSION OF M37733MHBXXXFP

M37733EHBFS

FUNCTION IN EPROM MODE

1M mode (equivalent to the M5M27C101K)

Reading

To read the EPROM, set the CE and OE pins to a “L” level. Input the

address of the data (A

to the I/O pins D

__ __

the CE or OE pins are in the “H” state.

0 – D7. The data I/O pins will be floating when either

___ ___

0 – A16) to be read, and the data will be output

Programming

Programming must be performed in 8 bits by a byte program. To

program to the EPROM, set the CE pin to a “L” level and the OE pin to

a “H” level. The CPU will enter the programming mode when 12.5 V

is applied to the V

with pins A

– D7. Set the PGM pin to a “L” level to being programming.

PP pin. The address to be programmed to is selected

0 – A16, and the data to be programmed is input to pins D0

_____

___ ___

Erasing

To erase data on this chip, use an ultraviolet light source with a 2537

Angstrom wave length. The minimum radiation power necessary for

erasing is 15 J/cm

2

.

Programming operation

To program the M37733EHBXXXFP, first set VCC = 6 V, VPP = 12.5

V, and set the address to 01000

pulse, check that the data can be read, and if it cannot be read OK,

repeat the procedure, applying a 0.2 ms programming pulse and

checking that the data can be read until it can be read OK. Record

the accumulated number of pulse applied (X) before the data can be

read OK, and then write the data again, applying a further once this

number of pulses (0.2 ✕ X ms).

When this series of programming operations is complete, increment

the address, and continue to repeat the procedure above until the

last address has been reached.

Finally, when all addresses have been programmed, read with V

V

PP = 5 V (or VCC = VPP = 5.5 V).

Table 2. I/O signal in each mode

___CE___OE_____

Pin

Mode

Read-out

Output

Disable

Programming

Programming

Verify

Program Disable

VIL

VIL

VIH

VIL

VIL

VIH

Note 1 : An X indicates either V

16. Apply a 0.2 ms programming

PGM VPP VCC Data I/O

VIL

X

5 V

5 V

VIH

X

5 V

5 V

X

X

5 V

5 V

VIH

VIL

12.5 V

6 V

VIL

VIH

12.5 V

6 V

VIH

VIH

12.5 V

6 V

IL or VIH.

CC =

Output

Floating

Floating

Input

Output

Floating

Programming operation (equivalent to the M5M27C101K)

AC ELECTRICAL CHARACTERISTICS (Ta = 25 ± 5 °C, VCC = 6 V ± 0.25 V, VPP = 12.5 ± 0.3 V, unless otherwise noted)

Symbol Parameter Test conditions

tAS

tOES

tDS

tAH

tDH

tDFP

tVCS

tVPS

tPW

tOPW

tCES

tOE

Address setup time

___

OE setup time

Data setup time

Address hold time

Data hold time

Output enable to output float delay

VCC setup time

VPP setup time

_____

PGM pulse width

_____

PGM over program pulse width

___

CE setup time

Data valid from OE

__

Min.

0.19

0.19

Limits

Typ.

2

2

2

0

2

0

2

2

0.2

2

Max.

130

0.21

5.25

150

Unit

µs

µs

µs

µs

µs

ns

µs

µs

ms

ms

µs

ns

10

MITSUBISHI MICROCOMPUTERS

M37733EHBXXXFP

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

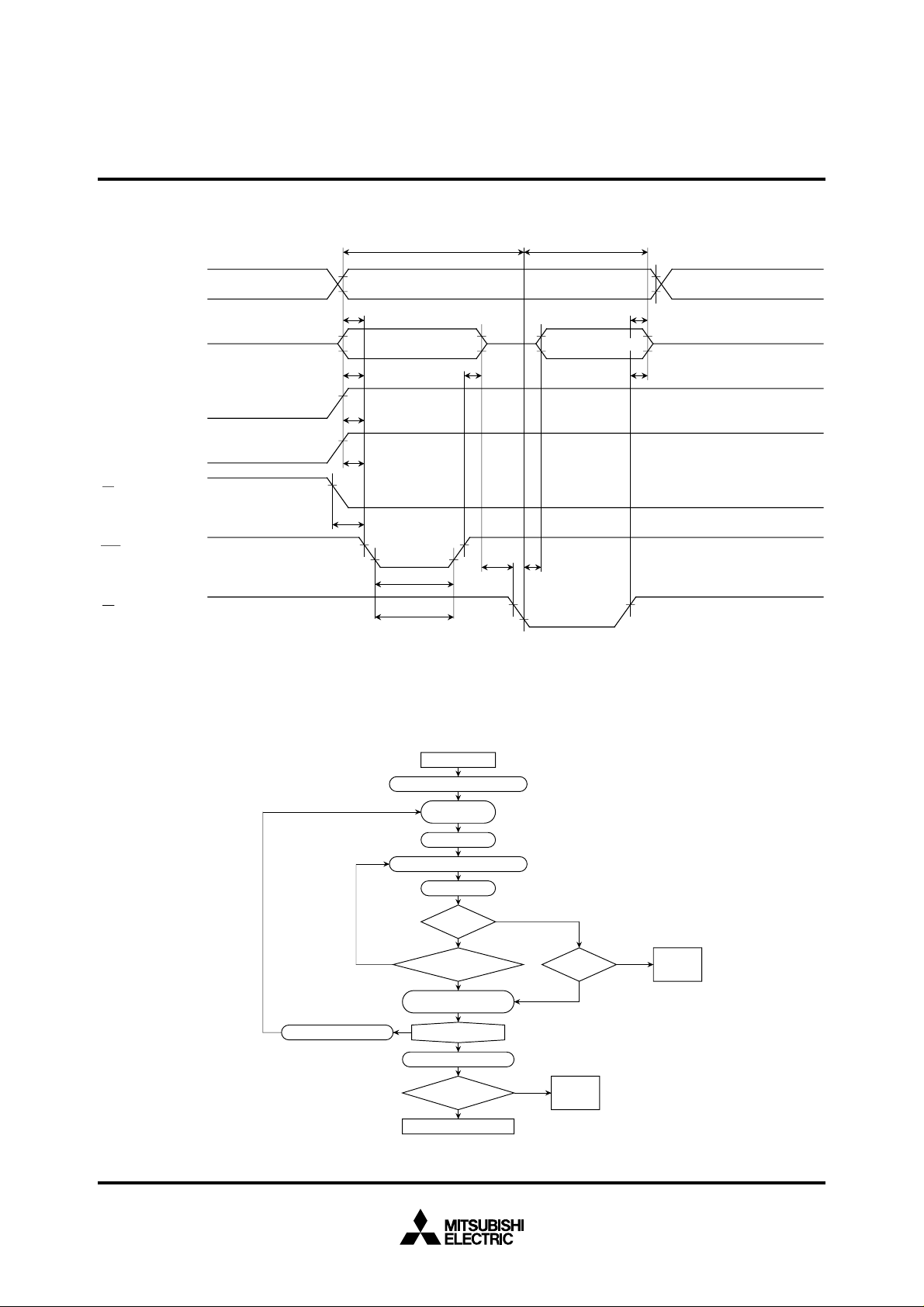

AC waveforms

V

VIH/VOH

VIL/VOL

VPP

VCC

VCC +1

V

VIH

VIH

VIH

IH

VIL

CC

VIL

VIL

VIL

ADDRESS

DATA

PP

V

VCC

CE

PGM

OE

tAS

tVPS

tVCS

tCES

PROGRAM VERIFY

DATA SET

DATA OUTPUT VALID

tDH tDS

tOES tOE

tPW

tOPW

PROM VERSION OF M37733MHBXXXFP

M37733EHBFS

tAH

tDFP

Programming algorithm flow chart

INCREMENT ADDR

START

ADDR=FIRST LOCATION

V

CC

PP

=12.5 V

V

X=0

PROGRAM ONE PULSE OF 0.2 ms

X=X+1

X=25?

NO

FAIL

VERIFY

BYTE

PROGRAM PULSE OF

0.2X ms DURATION

NO

LAST ADDR?

V

CC=VPP

VERIFY

ALL BYTE

DEVICE PASSED

Test conditions for A.C. characteristics

Input voltage : V

IL = 0.45 V, VIH = 2.4 V

Input rise and fall times (10 % – 90 %) : ≤ 20 ns

Reference voltage at timing measurement : Input, Output

“L” = 0.8 V, “H” = 2 V

=6.0 V

YES

PASS

=*5.0 V

PASS

YES

FAIL

VERIFY

BYTE

DEVICE

FAILED

PASS

FAIL

DEVICE

FAILED

*4.5 V ≤ VCC = VPP ≤ 5.5 V

11

Loading...

Loading...