Page 1

SERVICE MANUAL

PART NO. 599910644

The First Edition

CRT DISPLAY

DPro2070SB / DPro2070SB-BK

(C22BW711)

Southern Hemisphere Version

NEC-MITSUBISHI ELECTRIC VISUAL SYSTEMS CORPORATION

FEBRUARY 2003

Page 2

Contents

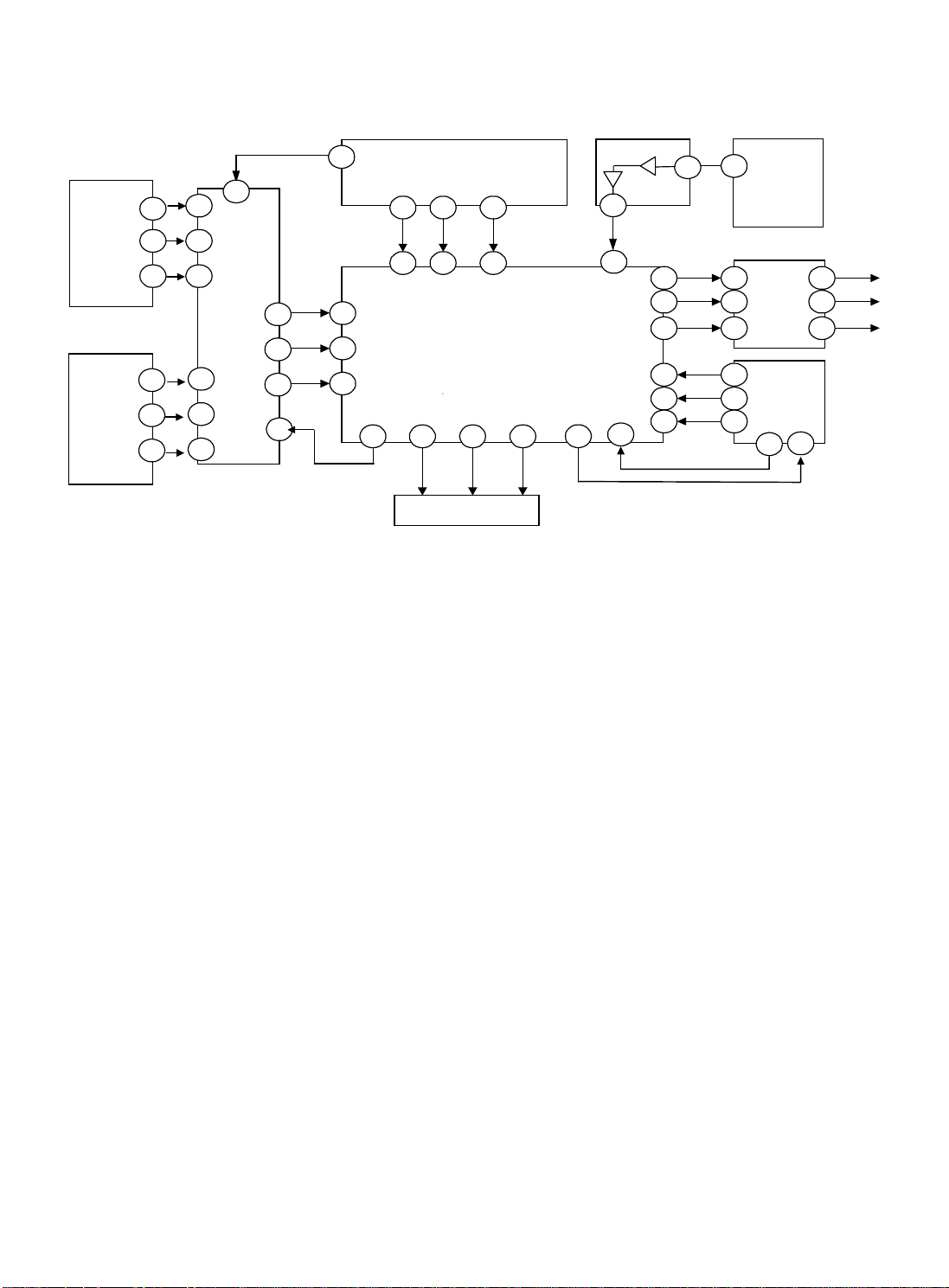

1. Circuit description ............................................................................................................................ 1-1

1.1 Power block ............................................................................................................................ 1-1

1.1.1 Outline ........................................................................................................................... 1-1

1.1.2 Rectifying circuit and higher harmonics suppression (active filter)

circuit ............................................................................................................................. 1-1

1.1.3 Sub power circuit ......................................................................................................... 1-2

1.1.4 Main power circuit........................................................................................................ 1-2

1.1.5 Demagnetizing circuit .................................................................................................. 1-2

1.1.6 Power management circuit ......................................................................................... 1-2

1.2 Deflection processor block................................................................................................... 1-3

1.2.1 Deflection processor (IC601) ..................................................................................... 1-3

1.2.2 Pressure-reduction type horizontal deflection power circuit (IC5C0) .................. 1-3

1.2.3 Horizontal width control circuit .................................................................................. 1-3

1.2.4 Vertical deflection circuit ............................................................................................ 1-3

1.2.4.1 Sawtooth waveform generation, vertical size/position control, and

linearity control circuit.................................................................................. 1-3

1.2.4.2 Vertical output amplification circuit ............................................................ 1-4

1.2.5 High voltage block ....................................................................................................... 1-4

1.2.6 DBF (Dynamic Beam Focus) circuit .......................................................................... 1-5

1.3 Video block ............................................................................................................................. 1-6

1.3.1 Video signal amplifier circuit ...................................................................................... 1-6

1.3.1.1 Video clamp.................................................................................................... 1-6

1.3.1.2 Video blanking ............................................................................................... 1-6

1.3.1.3 Video mixing/amplifying ............................................................................... 1-6

1.3.1.4 Control of contrast and white balance ....................................................... 1-6

1.3.2 Cut-off control circuit ................................................................................................... 1-7

1.3.2.1 Control of brightness .................................................................................... 1-7

1.3.2.2 Control of BIAS .............................................................................................. 1-7

1.3.3 OSM (On Screen Manager) ........................................................................................ 1-7

1.3.4 2 Input change circuit .................................................................................................. 1-8

1.3.5 Sync on Green circuit .................................................................................................. 1-8

1.3.6 Asset circuit .................................................................................................................. 1-8

1.3.7 AUTO-SIZE function .................................................................................................... 1-8

1.3.8 SB MODE (Super Bright Mode) function .................................................................. 1-8

1.3.8.1 Adjustment item/operating function in selecting SB Mode ..................... 1-8

1.3.8.2 Circuit (cathode) operation in selecting SB Mode [Window pattern] .... 1-9

1.3.8.3 SB Mode setting data and control method ................................................ 1-9

1.3.9 CONSTANT BRIGHTNESS function ....................................................................... 1-10

iii

Page 3

1.4 CRT compensation block .................................................................................................. 1-10

1.4.1 Earth magnetism cancel circuit.............................................................................. 1-10

1.4.2 Rotation circuit ......................................................................................................... 1-11

1.4.3 East-west horizontal magnetic field vertical position

canceling function ................................................................................................... 1-11

1.4.4 Corner purity circuit ................................................................................................. 1-11

1.4.4.1 Corner purity circuit operation.................................................................. 1-12

1.4.5 Vertical magnetic field landing cancel circuit ...................................................... 1-12

1.4.6 Digital dynamic convergence clear (DDCC) circuit ............................................ 1-12

1.4.6.1 Production of compensation current waveform ..................................... 1-13

1.4.6.2 Waveform, and operation on the picture ................................................ 1-13

1.4.6.3 Adjustment method .................................................................................... 1-14

1.4.6.4 Block diagram ............................................................................................. 1-14

1.4.7 East-west horizontal convergence canceling function ....................................... 1-19

1.5 USB circuit........................................................................................................................... 1-19

1.5.1 Outline ....................................................................................................................... 1-19

1.5.2 USB downstream power supply ............................................................................. 1-19

1.5.3 HUB controller power output .................................................................................. 1-19

1.5.4 USB power on reset ................................................................................................ 1-19

1.6 Control block ....................................................................................................................... 1-20

1.6.1 Function of control circuit ....................................................................................... 1-20

1.6.2 Auto-tracking process ............................................................................................. 1-20

1.6.3 EEPROM ................................................................................................................... 1-20

1.6.4 On-Screen-Manager (OSM) controller.................................................................. 1-20

1.6.5 Heater voltage control ............................................................................................. 1-20

1.6.6 Protection circuit operation .................................................................................... 1-20

1.6.6.1 X-ray protector ............................................................................................ 1-20

1.6.6.2 High voltage data error detection ............................................................ 1-21

1.6.6.3 Beam current protector.............................................................................. 1-21

1.6.6.4 Power-On Indicator (LED) flickering pattern

in each protector operating ...................................................................... 1-21

1.6.6.5 Operating time ............................................................................................ 1-21

1.6.6.6 The DDC communication .......................................................................... 1-21

1.6.6.7 Microcomputer pin assignment ................................................................ 1-22

1.7 X-ray protection circuit and safety protection circuit ................................................... 1-23

1.7.1 X-ray protection circuit ............................................................................................ 1-23

1.7.2 Beam current protection circuit.............................................................................. 1-23

1.7.3 IC701 overcurrent protection circuit ..................................................................... 1-23

1.7.4 IC701 overload protection circuit .......................................................................... 1-23

1.7.5 IC902 overcurrent protection circuit ..................................................................... 1-23

iv

Page 4

1.7.6 Short-circuit protection circuit on secondary power side .................................... 1-23

1.7.7 Overvoltage protection circuit .................................................................................. 1-23

1.8 Adjustment............................................................................................................................ 1-24

1.8.1 Adjustment mode ....................................................................................................... 1-24

1.8.2 User mode (Normal mode) ....................................................................................... 1-24

1.8.3 Factory mode .............................................................................................................. 1-27

1.8.3.1 How to entering to Factory mode.............................................................. 1-27

1.8.3.2 How to cancel Factory mode ..................................................................... 1-27

1.8.3.3 How to enter FACTORY-HV mode............................................................ 1-27

2. Adjustment procedure ................................................................................................................... 2-1

2.1 Measuring instruments ....................................................................................................... 2-1

2.2 Preparatory inspections ..................................................................................................... 2-1

2.3 Names of each monitor part .............................................................................................. 2-2

2.3.1 Configuration of front control panel ....................................................................... 2-2

2.3.2 Configuration of rear input connector (signal input) ........................................... 2-2

2.3.3 OSM display matrix .................................................................................................. 2-3

2.3.3.1 User mode ................................................................................................... 2-3

2.3.3.2 Factory mode .............................................................................................. 2-4

2.4 Adjustment ........................................................................................................................... 2-7

2.4.1 How to select the factory adjustment (FACTORY) mode ................................... 2-7

2.4.1.1 Selecting with front panel switches ......................................................... 2-7

2.4.2 Adjustments before aging ........................................................................................ 2-7

2.4.2.1 Adjusting the high voltage and high voltage protector ......................... 2-7

2.4.2.2 FOCUS adjustment (Rough adjustment) ................................................ 2-8

2.4.2.3 Shock test .................................................................................................... 2-8

2.4.2.4 Preadjustment before aging...................................................................... 2-8

2.4.2.5 Adjusting the landing (ITC/4 corner purity adjustment)........................ 2-9

2.4.3 Adjusting the picture size, position and distortion, DBF amplitude and phase 2-9

2.4.3.1 Adjusting the picture inclination ............................................................... 2-9

2.4.3.2 Adjusting the back raster position ........................................................... 2-9

2.4.3.3 Adjusting the left/right distortion, picture width, picture position (LEFT/

RIGHT) and vertical linearity (all preset) ................................................ 2-10

2.4.3.4 Adjusting the DBF amplitude and phase ................................................ 2-10

2.4.4 Adjusting the cut off ................................................................................................. 2-11

2.4.4.1 Adjusting BTCEN (BRIGHT-CENT), BTMAX (BRIGHT-MAX) and BS1

(BIAS-H)....................................................................................................... 2-11

2.4.4.2 Adjusting BS2 (BIAS-M) / BS3 (BIAS-L).................................................. 2-12

2.4.5 Setting CONSTANT BRIGHTNESS circuit (Factory mode) ................................ 2-13

2.4.5.1 Reading beam current default data ......................................................... 2-13

2.4.5.2 Confirming CONSTANT BRIGHTNESS function ................................... 2-13

v

Page 5

2.4.6 Adjusting the RGB drive signal............................................................................... 2-13

2.4.6.1 Adjusting GN1 (GAIN-H) (adjustment of 9300K) .................................. 2-13

2.4.6.2 Adjusting ABL .............................................................................................. 2-15

2.4.7 Adjusting the focus ................................................................................................... 2-15

2.4.8 Adjusting the convergence ...................................................................................... 2-16

2.4.8.1 Adjusting with ITC ...................................................................................... 2-16

2.4.8.2 Adjusting DDCP .......................................................................................... 2-18

2.4.9 Default settings (With factory mode) ..................................................................... 2-23

2.5 Inspections (In normal mode) ............................................................................................ 2-24

2.5.1 Electrical performance ............................................................................................. 2-24

2.5.1.1 Withstand voltage ....................................................................................... 2-24

2.5.1.2 Grounding conductivity check .................................................................. 2-24

2.5.1.3 Degaussing coil operation......................................................................... 2-24

2.5.1.4 IPM OFF MODE function operation (Set the AC power input to 230V) ....... 2-24

2.5.1.5 Confirming the GLOBAL SYNC (CORNER-Purity) function................. 2-25

2.5.1.6 Focus, picture performance ...................................................................... 2-25

2.5.1.7 Misconvergence .......................................................................................... 2-25

2.5.1.8 Picture distortion ........................................................................................ 2-26

2.5.1.9 Linearity ....................................................................................................... 2-28

2.5.1.10 Adjustment value list................................................................................ 2-29

2.5.1.11 Confirming EDGELOCK and SYNC GREEN........................................ 2-30

2.5.1.12 Checking the functions during Composite Sync input ........................ 2-30

2.5.1.13 Confirming the reset operation .............................................................. 2-30

2.5.1.14 Confirming the full white luminance/color coordination...................... 2-30

2.5.1.15 Confirming CONVERGENCE compensation function ......................... 2-30

2.5.1.16 Confirming ROTATION compensation function ................................... 2-31

2.5.1.17 Luminance/color coordination uniformity.............................................. 2-31

2.5.1.18 Confirming the color tracking ................................................................. 2-31

2.5.1.19 CRT installation position......................................................................... 2-31

2.5.1.20 Confirming SB MODE operation ............................................................ 2-31

2.5.1.21 Confirming AUTO-ADJUST operation ................................................... 2-32

2.5.1.22 Confirming USB........................................................................................ 2-32

2.5.1.23 Others......................................................................................................... 2-32

2.6 DDC function, check of asset management.................................................................... 2-33

2.6.1 DDC write data contents .......................................................................................... 2-34

2.6.2 Self-diagnosis shipment setting ............................................................................. 2-35

2.7 Default inspection ............................................................................................................... 2-35

2.7.1 Default setting of switches ...................................................................................... 2-35

2.7.2 Default setting of OSM ............................................................................................. 2-35

2.7.3 Checking the labels .................................................................................................. 2-35

vi

Page 6

2.7.4 Packaging .................................................................................................................. 2-35

2.8 Degaussing with handy-demagnetizer............................................................................. 2-36

2.8.1 General precautions ................................................................................................. 2-36

2.8.2 How to hold and use the handy-demagnetizer ................................................... 2-36

2.9 Caution ................................................................................................................................. 2-36

2.10 Timing chart ....................................................................................................................... 2-37

2.11 Adjustment timing ............................................................................................................. 2-38

3. Trouble shooting

4. Wave form

5. Schematic diagram

6. Removal instruction sheet

7. Exploded view / Packing view

<Appendix>

Serial number information

Specification

User's guide

All parts list

vii

Page 7

1. Circuit description

1. 1 Power block

1.1.1 Outline

The power block is compatible with the business electric power, 100 to 120VAC/220 to 240VAC (50/60Hz).

The active filter circuit is adopted to suppress the higher harmonic current.

The circuit block is composed of two switching regulators, the main power which is the configuration used

the flyback converter system of pseudo resonance operation and the sub power which is the configuration

used PWM (pulse wise modulation) system.

The output on the secondary side is shown in Table 1.

Power block Output voltage Mai load

+215V H. deflection circuit, Cut-off circuit

+80V Video circuit, DBF circuit, High voltage circuit

Main power side

+15V H. deflection circuit, Rotation circuit

-15V Convergence circuit, Corner purity circuit

+12V Video circuit, H. deflection circuit

+8V Heater

Sub power side

+5V Microcomputer (MPU)

P-OFF+5V VIDEO circuit

Table 1

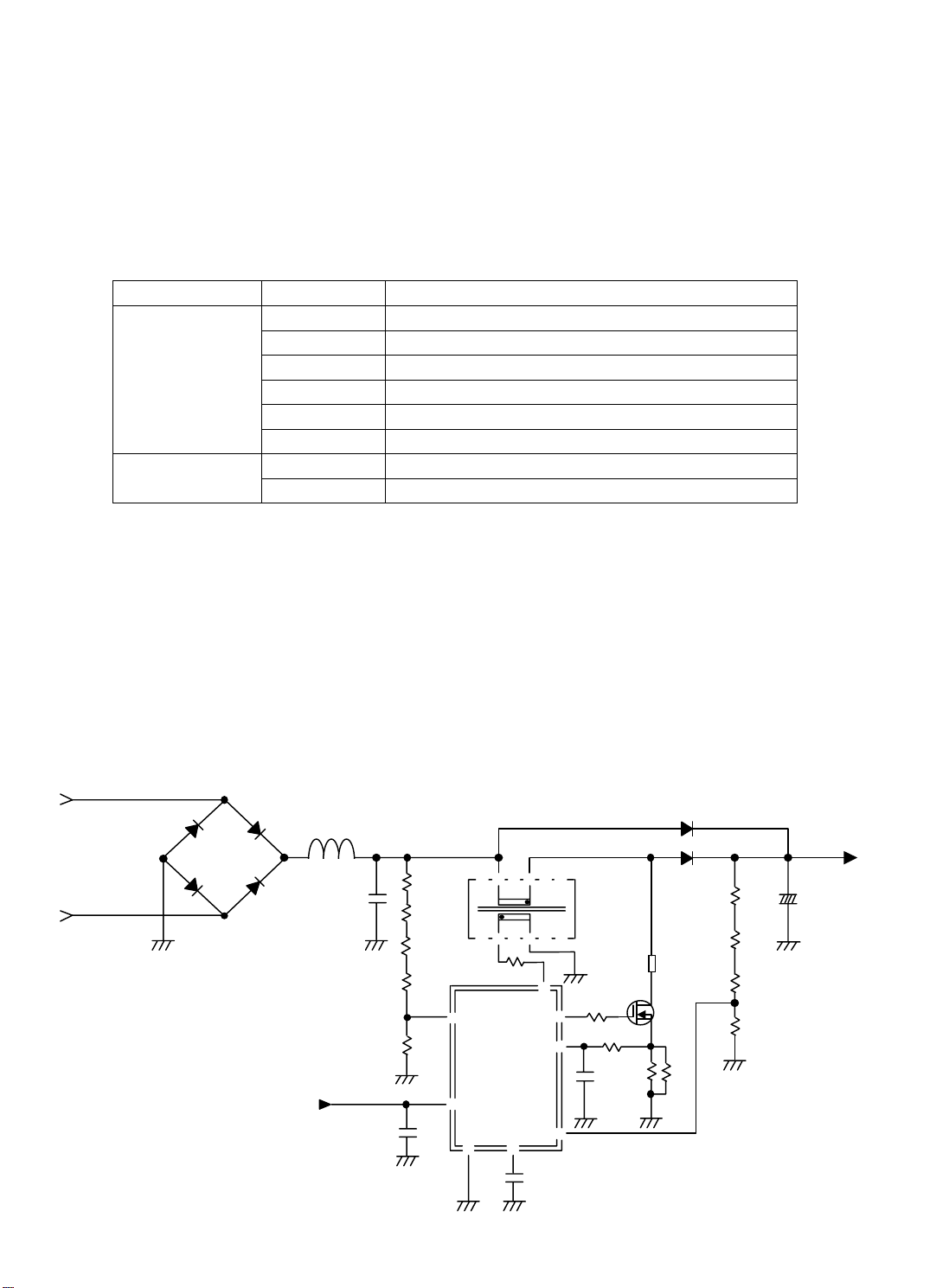

1.1.2 Rectifying circuit and higher harmonics suppression (active filter) circuit

The AC input voltage is rectified in the full wave mode with the diode bridge in D901 and input to pin 5 of

L903. The voltage of both end of C911 is the DC voltage approx. 390VDC boosted with the booster

circuit (active filter circuit) composed of IC901, Q901, L903 and D902. The active filter circuit compares

the voltage input to pin 1, pin 3 and pin 4 of IC901 and controls Q901 ON/OFF period so that the current

flows to L903 be sine-waved. The AC input current is sine-waved in the same phase with the input

voltage so as to improve the power factor, and the harmonic current is controlled consequently.

AC

D901

AC

From Sub power

Vcc

L902

C906

R908

C907

R904

R905

R906

R907

③

⑧

⑤

⑥

⑦ ⑧ ⑨ ⑩

R911

IC901

② ⑥

③ ④

②

⑪

⑤

C908

⑦

①

④

①

⑫

L903

R912

R909

R937

C910

D902

L905

Q901

R910

D933

R913

R914

R915

R917

To Main p o w e r

and sub power

+

C911

Fig. 1

Page 8

1.1.3 Sub power circuit

When the power switch is turned ON, the rectified and smoothed DC voltage (AC voltage x √2) is

supplied to pin 5 of IC903, and is charged to C930 through pin 1. When pin 1 reaches 5.7V, oscillation is

started in IC903, and the built-in output FET is put into operation to add the pulse voltage between pin 5

and pin 3 on the primary side of T902. The flyback voltage in proportion to the voltage on the primary

side is generated on the secondary side, then the DC voltage is generated with the half-wave rectifier

circuit composed of D971 and C971. The DC voltage generated at the secondary side is monitored by

IC922 through R976, R977 and R978. This information detected at IC922 is fed back to pin 1 of IC903

via PC902, and the ON period of output FET internal IC903 is controlled to keep the DC voltage on the

secondary side constantly. The flyback voltage in proportion to the voltage on the primary side is also

generated at pin 2 of T902. The pulse voltage generated at pin 2 of T902 is converted to the DC voltage

at D932 and C931, and supplied to pin 8 of IC901 and pin 4 of IC902 via Q902.

1.1.4 Main power circuit

When the P-SUS signal from microcomputer is turned to HI, Q902 is turned to ON, and the voltage approx.

+18V is supplied to pin 4 (Vcc terminal) of IC902 from pin 2 of T902.

When the voltage of pin 4 of IC902 reaches approx. +16V, oscillation is started in the circuit, and the

built-in output FET is put into operation to add the pulse voltage between pin 5 and pin 2 on the primary

side of T901. The flyback voltage generated at the secondary side in proportion to the one in the primary

side is rectified at D961, D963, D964, D965 and D967 and smoothed at C961, C963, C964, C965 and

C969 to generate the DC voltage. The DC voltage generated at the secondary side is monitored by

IC921 through R960, R961, R962 and R985. The information detected at IC921 is fed back to pin 1 of

IC902 via PC901, and the ON period of output FET internal IC902 is controlled to keep the DC voltage on

the secondary side constantly.

1.1.5 Demagnetizing circuit

When the power is turned ON or the manual demagnetizing function on OSM menu is set to ON, pin 47 of

IC102 on the main board is turned to HI, and Q950 and RL901 are also turned ON.

When RL901 is turned ON, the current flows to the demagnetizing coil, however, the demagnetizing

current gradually converges with the fever of TH902.

1.1.6 Power management circuit

This monitor carries the power management function. This function is effective only when being

connected with the personal computer carrying the power management function.

Mode H-SYNC V-SYNC State Display

NORMAL ON ON Displaying a picture Displaying a picture

SUSPENSION

The power consumption and the indication of Power-On Indicator for each mode are as follows.

Mode Power consumption Power-On Indicator

NORMAL 135W Green

SUSPEND 3W or less Orange

The control signal executes the power management function is output from microcomputer IC102. The

control signal is composed of two signals, SUSPEND and P-OFF. The operating state of each signal is

as follows.

Control signal name Pin of IC102 Normal Suspension

SUSPEND Pin 5 H L

P-OFF Pin 42 H L

OFF

ON

OFF

ON

OFF

OFF

No picture

CRT heater is

decreased voltage

mode (approx. 1.5V)

No raster

Page 9

1.2 Deflection processor block

1.2.1 Deflection processor (IC601)

Deflection processor IC601 horizontally compensates wise, position and distortion, and vertically controls

heights, position and linearity.

IC601 automatically tracks the frequency to output the appropriate horizontal/vertical drive pulse.

IC601 also outputs the horizontal parabola waveform for focus and the waveform for convergence

compensation.

1.2.2 Pressure-reduction type horizontal deflection power circuit (IC5C0)

IC5C0 compares the parabola waveform output from pin 64 of IC601 (this waveform controls the

horizontal width and distortion) with the sawtooth waveform (this waveform is synchronized with the

horizontal frequency) in order to output the +B drive pulse. The +B drive pulse output from pin 9 of IC5C0

will accumulate the 215V energy in T550 during Q5F1 ON period. During Q5F1 OFF period, the

accumulated energy will be released, and integrated by T550 and the S-shaped compensation capacitor.

The duty of this drive pulse depends on the DC level of the parabola waveform that is output from IC601.

1.2.3 Horizontal width control circuit

Q550 is controlled by the horizontal drive pulse that is output from IC601. When Q550 is ON, the energy

will be accumulated in the horizontal deflection yoke. When Q550 is OFF, the energy will flow into C550.

While repeating this operation, horizontal deflection will be carried out.

The collector pulse of Q550 will be subject to voltage division by C590 and C591, and the voltage-divided

pulse will be used for switching synchronization of the high-voltage control IC701 and also used as the

AFC pulse.

The duty of the +B drive pulse output from pin 9 of IC5C0 will be subject to change in order to control the

horizontal width. The parabola waveform output from IC601 is compared with the feedback waveform

output from T5C0 to obtain the comparison waveform, and this comparison waveform threshes the

sawtooth waveform inside IC5C0 in order to control the duty. If the duty is changed, the rectified voltage of

the S-shaped compensation capacitor will be changed, and the horizontal width will be also changed. The

vertical parabola waveform is generated inside IC601, and then mixed with the DC level for horizontal

width control. After that, the mixed parabola waveform will be output from 64 pin of IC601, and added to

IC5C0. This parabola output will be used for compensation of pin-cushion distortion, barrel distortion,

trapezoidal distortion, and upper/lower distortion.

1.2.4 Vertical deflection circuit

1.2.4.1 Sawtooth waveform generation, vertical size/position control, and linearity control circuit

If the vertical synchronization signal is input to 42 pin of IC601, the bipolar sawtooth waveform having the

same frequency as the input will be output from pins 1 and 11 of IC601. IC601 receives compensation

data from the MPU (IC102) to compensate the vertical size, vertical position, vertical raster position,

vertical linearity, and vertical linearity balance, and then outputs the compensated sawtooth waveforms

from pins 1 and 11. Pin 2 outputs the voltage to show the vertical deflection intermediate point.

The OP amplifier at the next stage outputs a signal to show the difference of the bipolar sawtooth

waveform. For this output, the RC low pass filter is adopted to eliminate the digital gradation of the output

waveform. In addition, pins 62 and 63 of IC601 will be turned ON during retracing operation in order to

prevent deterioration of the linearity and dispersion of scanning lines. Moreover, Q603 and Q604 are

switched depending on the vertical frequency in order to improve the linearity.

Page 10

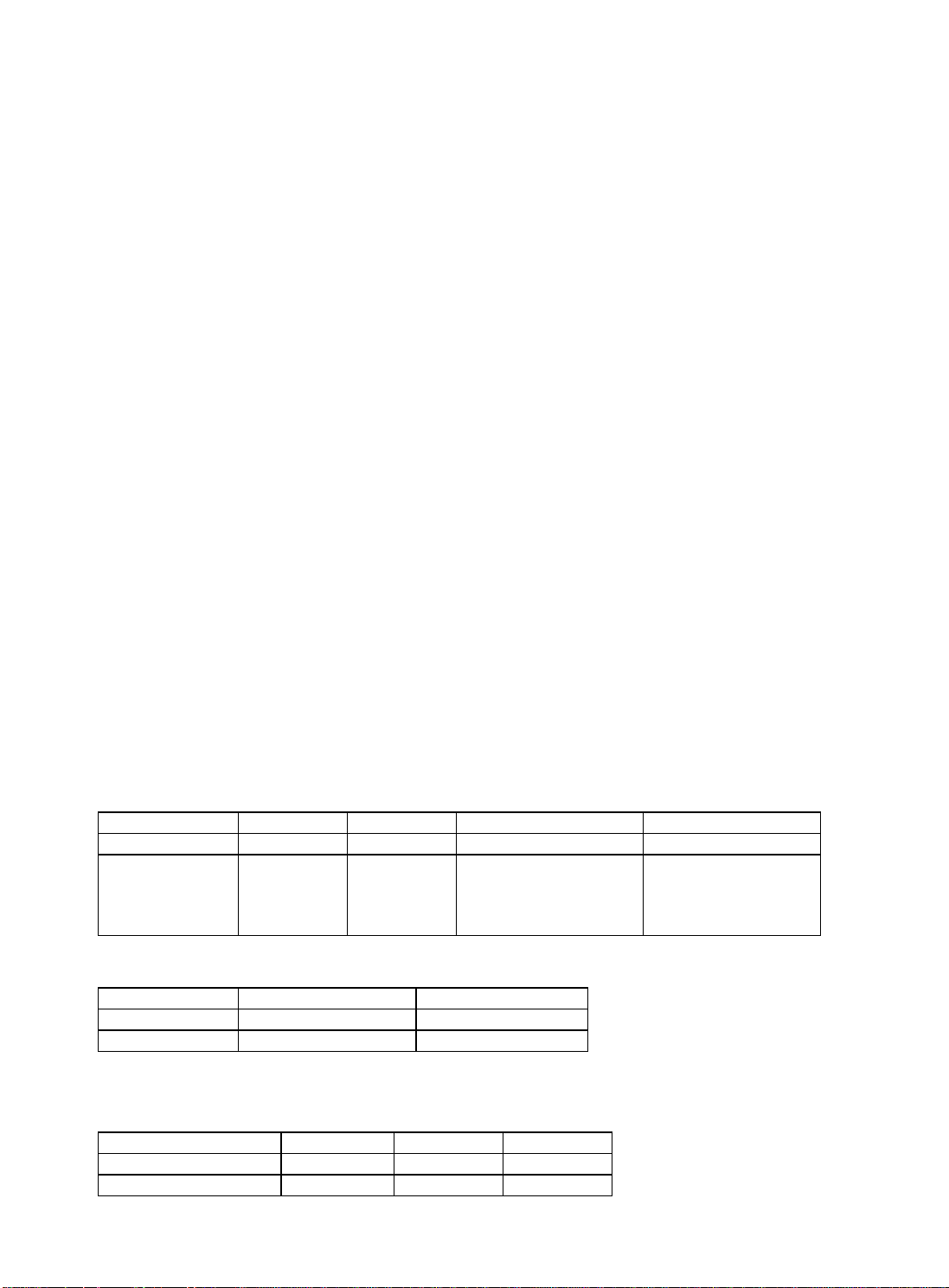

IC601

VSAW-P

VSAW-N

IMID

11

63

62

1

2

R652

R650

R651

R637

R658

2

3

IC603

1

R645+R646

R642

R648+R649

R647

C628

IC603

5

6

Q604

Q603

7

SW-VLIN1

SW-VLIN2

Fig. 2 Vertical sawtooth waveform output circuit

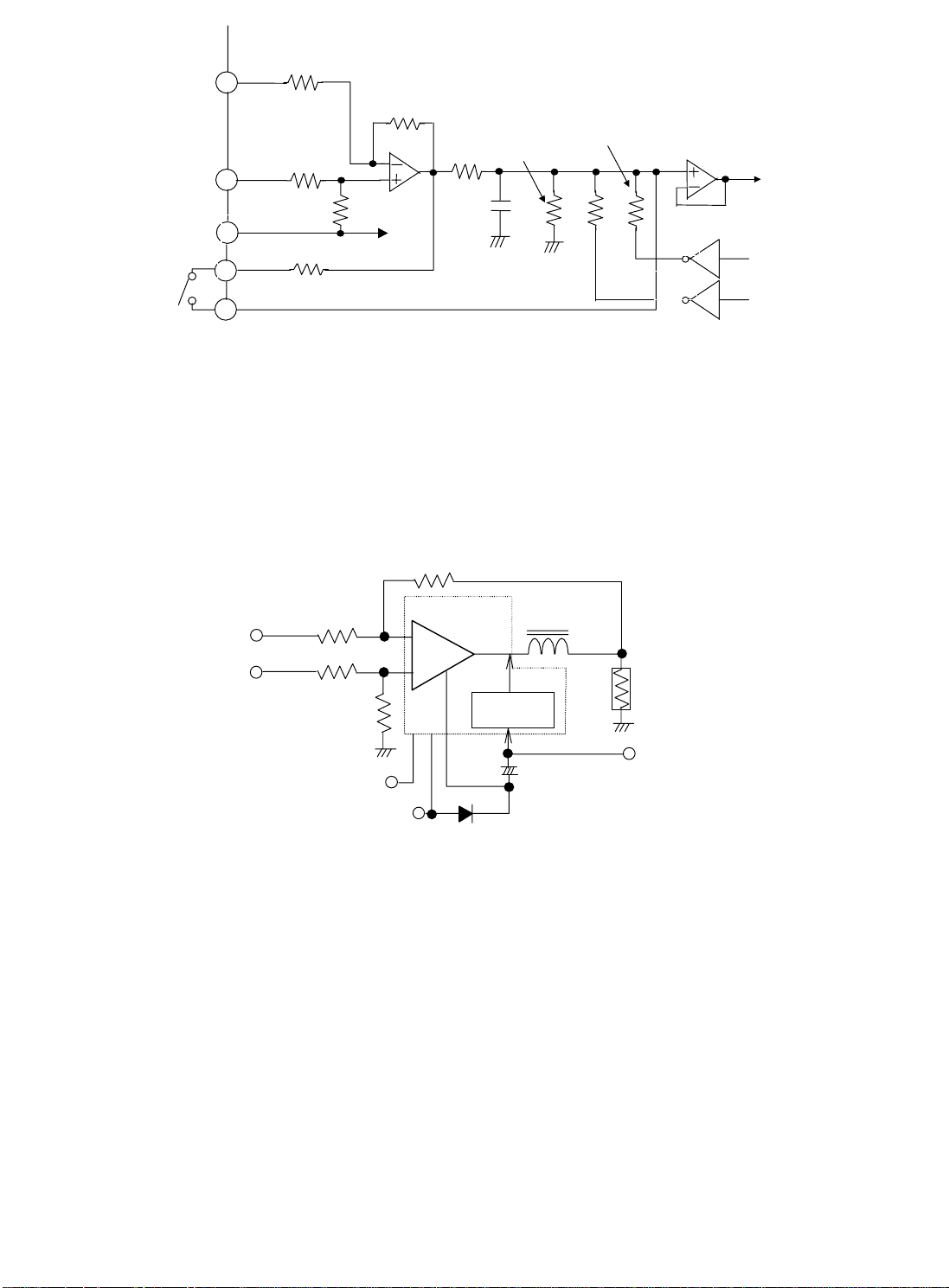

1.2.4.2 Vertical output amplification circuit

A current proportional to the waveform of the voltage input to IC401 will flow to the vertical deflection coil

(V-DY). R410 reads out the voltage waveform of the vertical deflection current, and then feeds back it to

IC401.

R419+R409

IMID

V SAW Input

R411

R405

R406+R418

-15.0V

5

4

+15.0V

-

+

1 6 3

IC451

D401

V-DY

2

Pump Up

7

C404

R410

VFLY

Fig. 3 Vertical output amplifier circuit

1.2.5 High voltage block

The high voltage block applies PWM control system that controls ON/OFF time of the high voltage

generation FET.

IC701 is the control IC that executes PWM control. The pulse voltage generated at Q701 is boosted at

T701 (FBT) to generate 27kV. To keep the high voltage stably, the feedback voltage from pin 10 of T701

is adopted, the control voltage from pin 56 of microcomputer IC102 is returned to pin 5 of IC701 and the

pulse wise of PWM output is controlled. PWM synchronizes with the horizontal frequency. Trigger pulse

for synchronizing is output from the divided collector pulse of the horizontal deflection output TR Q550,

and is input to pin 8 of IC701.

For adjustment of high voltage value, the voltage of pin 56 of IC102 is adjusted with the adjustment item

HV-ADJ-CAUTION on the OSM menu.

Page 11

1.2.6 DBF (Dynamic Beam Focus) circuit

The horizontal/vertical DBF voltage is respectively generated and amplified, then synthesized at T7A1.

As for the horizontal DBF voltage waveform, the parabola waveform voltage (approx. 0.5Vp-p) is output

with IC601, and amplified about 10 times with OP-AMP IC6A2. After that, it is amplified to 50-60Vp-p

with Q7B5 (the amplification factor is about 10 times), then it is amplified about 10 times with T7A1.

On the other hand, as for the vertical DBF voltage waveform, the parabola waveform voltage (approx.

1.0Vp-p) is output from IC601. It is amplified about 40 times at Q7A1, and the vertical parabola wave is

superposed to the horizontal parabola wave on the secondary side of T7A1, then consequently

synthesized. The collector pulse voltage of the high voltage output TR (Q701) rectified at D7A1 and

C7A1 is used for the power source of Q7A1. The synthesized DBF waveform is input to pin 12 of T701.

Page 12

1.3 Video block

1.3.1 Video signal amplifier circuit

D-SUB

CN216

B

2

1

G

2

4

R

3

6

D-SUB

CN215

B

1

10

G

2

12

R

3

14

1.3.1.1 Video clamp

SEL

13

IC 216

Anal og-sw

31

28

25

23

B

G

R

2

MPU

IC102

35 43 44

16 17 13

Retrace

BLK in

15

6

1

3

DAC

S/G SEL

18

SCL SDA

DAC

R-Bias

CLP-IN

IC 211

Pre - Amp

DAC

DAC

G-Bias

B-Bias

21 19 20

BIAS circuit

Fig. 4 Video signal amplifier circuit

10

14

IC 215

8

13

G

29

R

27

B

25

B OSD

11

G OSD

9

R OSD

10

OSD BLK

DET

40

11

8

9

17

19

18

IC 601

IC 210

MAIN

Amp

IC212

OSD

16

11

G

5

R

3

B

1

The clamp signal (positive polarity, 3.3 Vo-p) output from pin 35 of the MPU (IC102) is input to pin 13 of

IC211. The clamp signal is normally set to the back of the video signal (clamp position of OSM menu:

BACK). To correspond to the Sync on Green signal, the clamp signal can be set to the front of the video

signal (clamp position of OSM menu: FRONT). If the signal is a separate signal, changing the clamp

position of the OSM menu to FRONT or BACK will not change anything.

1.3.1.2 Video blanking

The horizontal/vertical retrace line (blanking) signal (positive polarity, 3.3 Vo-p) output from pin 40 of IC601

is input to pin 13 of IC215. IC215 reverses the polarity and amplifies the waveform (positive polarity,

3.3Vo-p -> negative polarity, 5.0Vo-p), and then reverses the polarity again (negative polarity, 5.0Vo-p ->

positive polarity, 5.0Vo-p) to output the blanking signal. This blanking signal is input to pin 14 of IC211 to

perform blanking operation during horizontal/vertical retracing operation.

To perform image blanking at switching the signal mode or at turning ON or OFF the power, the contrast

and the brightness will be set to MINIMUM.

1.3.1.3 Video mixing/amplifying

IC211 mixes the video signal with the OSM signal (G, R, and B signals of pins 9, 10, and 11) and with the

video blanking signal described in Sec. 1.3.1.2. I2C bus (pins 16 and 17 of SCL and SDA) fixes the black

level of the mixed video signal to 1.8V, and amplifies the mixed video signal (0.7Vp-p -> approx. 2.6Vp-p).

After that, the B, R, and G signals are output from pins 25, 27, and 29, respectively. The video signal

output from IC211 is input to IC210, where the signal is amplified (approx. 2.6Vp-p -> approx. 36Vp-p),

and the black level is fixed to 67V. After that, the B, R, and G signals are respectively output from pins 1, 3,

and 5.

1.3.1.4 Control of contrast and white balance

The MPU (IC102) sends the 8-bit contrast/white balance control data to IC211 with I2C bus (SCL, SDA

line). The contrast data simultaneously control 3 channels to simultaneously control the gains of the R, G,

and B, and the white balance data respectively controls the gains of the R, G, and B.

Page 13

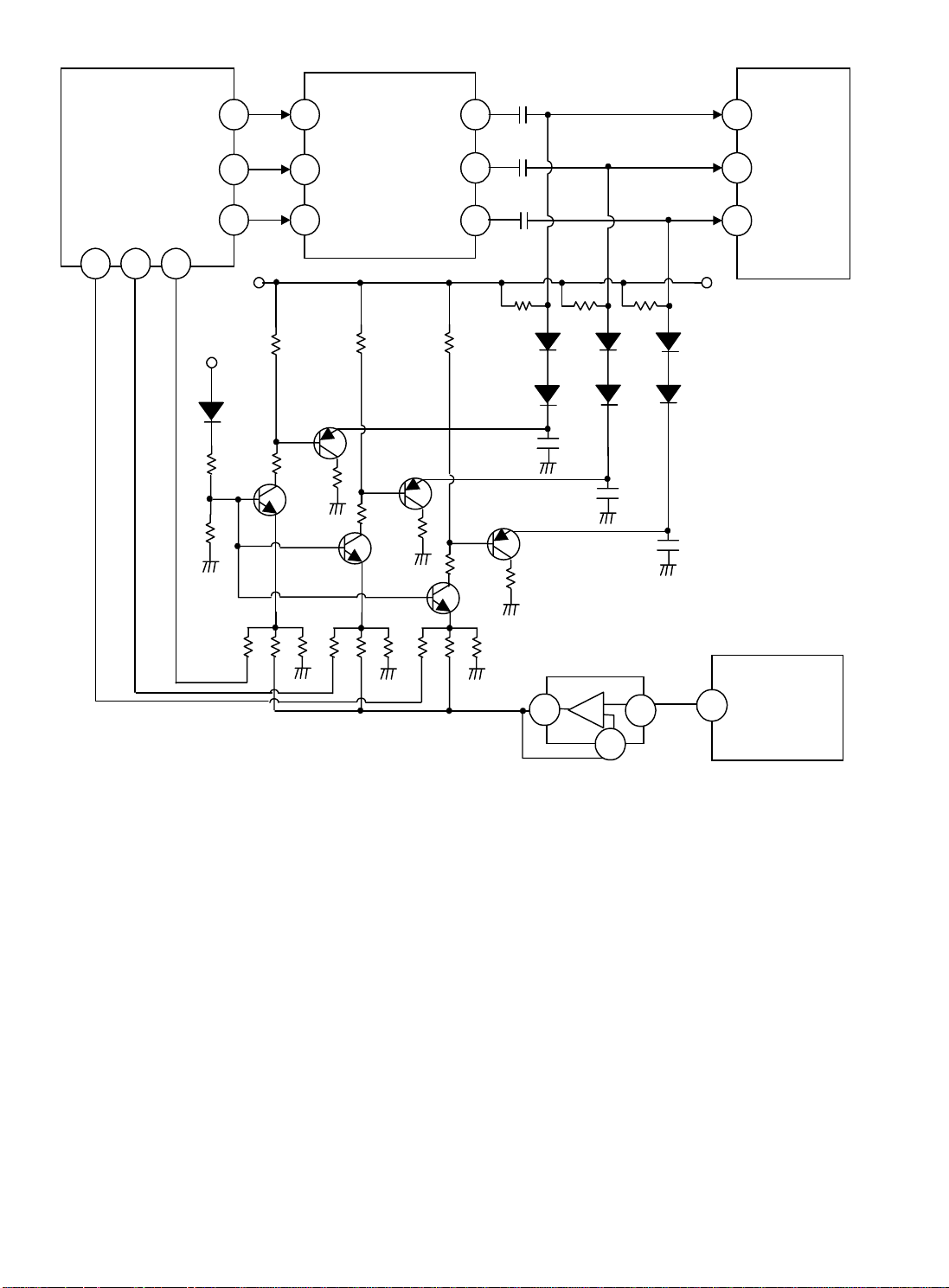

1.3.2 Cut-off control circuit

p

G

5 GK

B

1

R

3

R250G R250R R250B

D250G D250B

R251R

D251G

C250G

Q251R

R253B

R252R

Q250R

C250B

R253R

D250R

D251R D251B

C250R

BK

RK

215V LINE

CRT

Pre-Am

R.BIAS

IC211

21 19 20

G.BIAS

B.BIAS

12V LINE

G

29

25 11

27

D264

R261

R260

B

R

Q250G

8

9

R251G

Q251G

R252G

IC210

MAIN-Amp

R251B

Q251B

R253G

R252B

Q250B

R255G

R256G

R255B

R254G

R256B

R254B

BRIGHT

R255R

R254R

R256R

IC213

IC102

1

3

55

MPU

2

Fig. 5 Cut-off control circuit

The cut-off control circuit consists of Q250R, Q250G, Q250B, Q251R, Q251G, and Q251B, and

simultaneously adjusts 3 colors (brightness), or individually adjusts 3 colors (biases of R, G, and B). The

microcomputer controls both types of adjustment.

1.3.2.1 Control of brightness

To simultaneously adjust 3 colors (brightness), the DAC voltage (0 to 5V, variable) line of microcomputer

pin 55 is connected to the emitters of Q250R, Q250G, and Q250B via IC213. This connection enables

simultaneous control of three TR collector currents and adjustment of the brightness.

1.3.2.2 Control of BIAS

To individually adjust 3 colors (biases of R, G, and B), the DAC output (1.5 to 5.5V, variable) lines (pins 19,

20, and 21 of IC211) are respectively connected to the emitters of Q250R, Q250G, and Q250B via I2C

bus of the microcomputer. This connection enables respective control of three TR collector currents and

adjustment of biases of the R, G, and B.

1.3.3 OSM (On Screen Manager)

IC212 is the OSM (On-Screen Manager), and displays the screens for screen adjustment, etc. The data to

be displayed on the OSM screens is sent to the MPU (IC102) via I2C bus.

Page 14

1.3.4 2 Input change circuit

The analog switch IC216 carries out the signal selection at the time of SIGNAL-A and B simultaneous

input. The signal selection is carried out by the SELECT signal of pin 3 of microcomputer IC102. By the

SELECT signal of pin 3, the input signal of SIGNAL-A is selected when pin 13 (SELECT SW) of the

analog switch IC206 is HIGH, and SIGNAL-B is selected when pin 13 (SELECT SW) of the analog switch

IC206 is LOW.

1.3.5 Sync on Green circuit

The Sync on Green signal input needs to make an image signal and a composite sync signal separate.

The separation method of the image signal and the composite sync signal is as follows. If a

microcomputer IC102 detects a Sync on Green signal, pin 18 S/G-SEL signals of IC211 will be set to

HIGH (5V), a transistor Q280 turns off, and the Sync on Green signal is output from pin 23 of IC216. The

Sync on Green signal output from pin 23 is input to pin 22 of IC216, it is divided to the image signal and

the composite sync signal at the inside of IC216, and only composite sync signal is output from pin 21.

1.3.6 Asset circuit

If the monitor power is turned OFF, 5V power will be supplied to pin 14 of EEPROM (IC217) from the PC

via pin 9 of CN216, and the data stored in the EEPROM (IC217) can be read out from I2C bus.

1.3.7 AUTO-SIZE function

The AUTO-SIZE function detects the phase data of RGB OR signal (output to pin 11 of OSM (IC212) from

pin 15 of AMP (IC211) from H-OSM and V-S signals input to pins 5 and 16 of IC212 in order to

automatically adjust the screen to the optimum width and position.

Using the OSM, select AUTO SIZE ADJUST, and then press (+) button to perform automatic size

adjustment.

1.3.8 SB MODE (Super Bright Mode) function

1.3.8.1 Adjustment item/operating function in selecting SB Mode

(*4): See (*4) mentioned in item 1.3.8.3.

→SUPER BRIGHT MODE OFF (in factory adjustment state)

↓

SUPER BRIGHT MODE-1 ON (PICTURE)

↓

SUPER BRIGHT MODE-2 ON (MOVIE)

↓

User adjustment items related to luminance/color coordination

Adjustment of

SUPER BRIGHT MODE

OFF

SUPER BRIGHT MODE-1

ON

SUPER BRIGHT MODE-2

ON

(*1): Brightness and contrast are common among three display mode.

(*2): For color temperature, the adjustment value is memorized in every display mode.

brightness

Adjustable (*1) Adjustable (*1) Selectable Selectable (*2) Adjustable (*4)

Adjustable (*1) Adjustable (*1) Not-selectable Selectable (*2) Not-adjustable

Adjustable (*1) Adjustable (*1) Not-selectable Selectable (*2) Not-adjustable

Adjustment of

contrast

Color mode

selection

Color

temperature

selection

Individual GAIN

adjustment

Page 15

SUPER BRIGHT MODE

OFF

SUPER BRIGHT MODE-1

ON

Back raster luminance GAIN UP

Normal Normal --- ---

Normal UP Presence ---

SUPER BRIGHT MODE-2

ON

UP UP Presence Presence

compensation

γ

1.3.8.2 Circuit (cathode) operation in selecting SB Mode [Window pattern]

SUPER BRIGHT MODE

SUPER BRIGHT MODE-1

ccordance

Amplitude: Approx. 36V

Amplitude: Approx. 44V

Same amplitude

GND

Sharpness

SUPER BRIGHT MODE-2

Amplitude: Approx. 44V

1.3.8.3 SB Mode setting data and control method

(OSM FACT3) Data name Data (hex)

Setting of back raster

luminance

Setting of GAIN UP

SBBR1 0 BRT UP value in SUPER BRIGHT MODE-1 ON "0"=No UP

SBBR2 32 BRT UP value in SUPER BRIGHT MODE-2 ON

SBCN1 3C

SBCN2 3C

Amplified value in SUPER BRIGHT MODE-1 ON

(see the following formula)

Amplified value in SUPER BRIGHT MODE-2 ON

(see the following formula)

GAIN UP formula = GAIN adjustment value (hex)(*3) x {1+ (Data (hex) of SBCN1 or SBCN2)/FF (hex) }

(*3): GAIN adjustment value is the following data (in OSM FACT3).

9300K R-GN1 G-GN1 B-GN1

6500K R-GN2 G-GN2 B-GN2

5000K R-GN3 G-GN3 B-GN3

(*4): When the SUPER BRIGHT MODE-1 or MODE-2 is ON, the GAIN cannot be adjusted as shown in the

table in Sec. 1.3.6.1 "Adjustment item/operating function in selecting SB Mode". However, when the

SUPER BRIGHT MODE is OFF, the MAX GAIN value calculated with the following formula will be written in

the following EEP address so that the GAIN value cannot be increased above that of the SUPER BRIGHT

MODE-1 and MODE-2 ON status.

MAX GAIN = Maximum value (hex) for R/G/B GAIN adjustment (*5) x {1 + (SBCN1 or SBCN2 data

(hex))/FF (hex)}

Page 16

(*5): R/G/B GAIN MAX value is the maximum one among GAIN adjustment value mentioned (*3) above.

EEP address (hex)

R G B

MAX GAIN 89 8a 8b

* Every R/G/B MAX GAIN data applied to the address listed above table are totally same.

In case of repair, after CRT, Pre-AMP (IC211), MAIN-AMP (IC210), etc. are replaced and the

luminance/color coordination is adjusted, the MAX GAIN value mentioned above should be rewritten.

1.3.9 CONSTANT BRIGHTNESS function

The brightness and color coordination of the screen will be deteriorated due to secular deterioration of the

CRT. The CONSTANT BRIGHTNESS function, however, will recover the deteriorated brightness close to

the initial level (level ensured at outgoing the factory).

If the CONSTANT BRIGHTNESS function is activated, operation will be performed at 106kHz horizontally

and at 85Hz vertically while ignoring the input signal, and the OSM-IC (IC212) will output the reference

image signal. In this condition, R744 detects the beam current flowing to pin 9 of the flyback transformer

T701. This beam current is inverted and amplified by IC703, and then converted into a voltage value by

the current/voltage conversion circuit. After that, the converted voltage value will be input to the A/D

converter (pin 27 of IC102 (microcomputer)). To individually detect the beam current values of 3 colors (R,

G, and B), the desired color only will be brightened by increasing the cut-off voltages of the other 2 colors.

After obtaining the beam current values of 3 colors in this way, the obtained beam current values will be

compared with the beam current values used for factory adjustment (beam current values stored in the

EEPROM). After that, the cut-off voltage values of 3 colors (R, G, and B) will be adjusted so that the beam

current values close to the factory adjustment values can be obtained. In this way, the cut-off conditions of

the CRT will be recovered close to the factory adjustment level.

In addition, if the CONSTANT BRIGHTNESS function is activated, the C_TIME_SEL signal input to the

base of Q704 will be set to the low level, Q704 is turned OFF, and the bias voltage will be applied to pin 5

of IC703. As a result, voltage proportional to the beam current value will be output from pin 7 of IC703. By

the way, difference in the flyback transformer or the CRT may cause difference in the beam current. To

eliminate such difference in the beam current, the DAC voltage (commonly used for the 6H-DC signal) can

adjust the bias voltage input to pin 5 of IC703 described above. During normal operation, the

C_TIME_SEL signal is set to the high level, Q704 is turned ON, and pin 5 of IC703 is grounded via the

GND line so that the output of IC703 pin 7 can be kept at the low level. The signal output from pin 7 of

IC703 is added to ABL signal with MD717 (Diode). When the CONSTANT BRIGHTNESS function is

activated, the ABL signal is input to pin 27 of IC102 as the beam current signal.

1.4 CRT compensation block

1.4.1 Earth magnetism cancel circuit

This model carries IC2S0 (geomagnetism sensor unit) that carries out the voltage conversion of the

magnetic field intensity of a north-south magnetic field and an east-west magnetic field. IC2S0 detects

the detected voltage and controls the various canceling functions described below automatically.

•South-north horizontal magnetic field rotation canceling function

•East-west horizontal magnetic field raster vertical position canceling function

•South-north horizontal magnetic field landing canceling function

•East-west horizontal magnetic field landing canceling function

•South-north horizontal magnetic field convergence canceling function

•East-west horizontal magnetic field convergence canceling function

Here, the output voltage of IC2S0 (earth magnetism sensor unit) operates as follows.

•South-north horizontal magnetic field (IC2S0 pin 5): 1.0V (-0.04mT) to 2.5V (+/-0.00mT) to

•Vertical magnetic field (IC2S0 pin 4): 4.0V (-0.04mT) to 2.5V (+/-0.00mT) to 1.0V (+0.04mT).

<Vertical magnetic field canceling function>

(a) Landing compensation

V-6H (Schematic Diagram) and PWB-V-6H (PWB) are added so that the CRT specified for Northern

Hemisphere ITC can be adjusted to the spec for Southern Hemisphere ITC.

4.0V(+0.04mT).

Page 17

Some circuits are also added to DEFL-SUB (Schematic Diagram) and PWB-DEFLSUB (PWB).

In PWB-V-6H a vertical sync. parabola waveform output from pin 59 of IC601 (1 bit DAC) is supplied

from pin 1 of CN804 and 300mAp-p parabola waveform (vertical sync.) current flows to the speed

modulating coil from pin 1 of CN8P2 via Q8P0 and Q8P1.

In PWB-DEFLSUB a vertical sync. parabola waveform output from pin 59 of IC601 (1 bit DAC) is

reversed and amplified via Q600 and it is associated to the horizontal phase deflection compensation

waveform output from pin 57 of IC601 to compensate side pin balance.

(b) Vertical magnetic filed landing cancel

The vertical magnetic field landing cancel circuit is the one to compensate the color shade and

deviation that reaches its maximum at the center in the horizontal axis direction and its minimum at

the upper and lower ends on the monitor surface.

The automatic adjustment is done by controlling DC level of the above 300mAp-p parabola waveform

flowing to the speed modulating coil installed in the neck part of CRT.

It is controlled by pin 46 of IC 102 (DAC "V CANCEL"), and controls the speed modulating coil with

DC level of +/-50mA by Q8P0 and Q8P1.

(c) Vertical magnetic field convergence cancel

The vertical magnetic field convergence cancel circuit is the circuit to compensate for the

misconvergence that results after the vertical convergence of RED and BLUE reversed at the upper

and lower ends on the whole display area of the monitor deteriorates, and it is automatically adjusted

by the saw-toothed waveform (vertical-frequency) current flowing to the 4V convergence

compensation coil mounted on DY. It is controlled with the AC component (YVJT & YVJB, vertical

frequency saw-toothed waveform) by pin 60 of IC601 (4V_SC), and saw-toothed waveform (vertical

frequency) current of +/-45mA (peak) is made to flow to the 4V convergence compensation coil by pin

6 of IC8A1 (PowerOpamp).

1.4.2 Rotation circuit

The rotation circuit is a circuit to compensate the picture inclination caused by the earth magnetism by

letting DC current flow to the rotation coil wound on the front side of DY for adjustment. It is controlled to

0 to 5V with the reference of 2.5V by IC102 pin 45 (PWM_DAC), and DC current of +/-100mA (max) is

made to flow to the rotation coil by IC804 pin 2.

This compensation circuit has two functions; (1) User adjustment (OSM display) and (2)

Southern/Northern horizontal magnetic field rotation cancellation.

1.4.3 East-west horizontal magnetic field vertical position canceling function

It is the function that detects the detection voltage change from IC2S0 (geomagnetism sensor unit) by

east-west horizontal magnetic field change, and cancels a changed part of a raster vertical position

automatically.

1.4.4 Corner purity circuit

The corner purity circuit is a circuit to compensate for the color shade and color deviation of the picture

corner. On the rear side of CRT, it is adjusted by DC current flowing to the corner purity coils installed in

the four corners on the display surface.

The compensation circuit is composed of the following five functions of (1) User adjustment (OSM display),

(2) Aging variation compensation, (3) High/low temperature drift compensation, (4) South-north horizontal

magnetic field landing cancel and (5) East-west horizontal magnetic field landing cancel.

(1) User adjustment (OSM display)

The user causes DC current of +/-60mA (max) to flow to the purity coil of each corner according to the

value displayed on OSM.

(2) Aging variation compensation

As the electronic beam collides with the aperture grille, it is thermally expanded and contracted. The

thermal expansion/contraction is varied according to the elapse of the power ON/OFF time of the

monitor. The color shade and deviation of the picture corner thus generated are automatically

adjusted.

The voltage of the beam current supply pin (T701 pin 9) is detected with R723/R724, and the voltage

that detects the time elapse of the power ON/OFF of the monitor is read from the CR charge

(integration) circuit composed of C723 and R738, and CR discharge (integration) circuit composed of

C723 and R737 through IC702 (buffer amplifier) by IC102 pin 26 (CPU_ADC), then, the DC current of

+/-19mA (max) flows to the purity coil on each corner according to the specified control program.

Page 18

(3) High/low temperature drift compensation

The front panel (glass) is thermally expanded and contracted as the temperature varies in the

installation environments of the monitor. The color shade and deviation of the picture corner are

automatically adjusted. The voltage that detects the temperature variation of the installation

environments of the monitor is read from the environment temperature detection circuit composed of

TH100 (thermistor) arranged near the front panel (glass) by IC102 pin 25 (CPU_ADC), and DC current

of +/-13mA (max) is made to flow to the purity coil on each corner according to the specified control

program.

(4) South-north horizontal magnetic field landing canceling function

North-south magnetic field landing canceling adjusts automatically the color irregularity and color

shading/impurity which are generated horizontal direction served as an opposite direction at the upper

end and lower end of a monitor display side. Detection voltage and a direction of the north-south

magnetic field (IC2S0 pin 5) are detected by IC2S0 (geomagnetism sensor unit) and pin 29

(CPU_ADC) of IC102 reads the detection voltage, and DC current of ±21mA (Max) is passed in each

corner purity coil according to the predetermined control program.

(5) East-west horizontal magnetic field landing canceling function

East-west horizontal magnetic field landing canceling adjusts automatically the color irregularity and

color shading/impurity which are generated horizontal direction served as an opposite direction at the

upper end and lower end of a monitor display side. Detection voltage and a direction of the

north-south magnetic field (IC2S0 pin 4) are detected by IC2S0 (geomagnetism sensor unit) and pin

28 (CPU_ADC) of IC102 reads the detection voltage, and DC current of ±21mA (Max) is passed in

each corner purity coil according to the predetermined control program.

1.4.4.1 Corner purity circuit operation

<TL: Upper left corner>

Pin 50 (PWM_DAC) of IC102 controls the TL in the range of 0 to 5V while regarding 2.5V as the reference

voltage, and the DC current of the above value will flow from pin 2 of IC803 to the upper left corner purity

coil.

<TR: Upper right corner>

Pin 49 (PWM_DAC) of IC102 controls the TR in the range of 0 to 5V while regarding 2.5V as the reference

voltage, and the DC current of the above value will flow from pin 8 of IC803 to the upper right corner purity

coil.

<BL: Lower left corner>

Pin 52 (PWM_DAC) of IC102 controls the BL in the range of 0 to 5V while regarding 2.5V as the reference

voltage, and the DC current of the above value will flow from pin 2 of IC801 to the lower left corner purity

coil.

<BR: Lower right corner>

Pin 51 (PWM_DAC) of IC102 controls the BR in the range of 0 to 5V while regarding 2.5V as the

reference voltage, and the DC current of the above value will flow from pin 8 of IC801 to the lower right

corner purity coil.

1.4.5

The vertical magnetic field landing cancel circuit is the circuit to compensate for the color shade and

deviation that reaches its maximum at the center in the horizontal axis direction and its minimum at the

upper and lower ends on the monitor surface, and the adjustment is done by DC current according to the

value displayed on OSM flowing to the speed modulating coil installed in the neck part of CRT.

It is controlled with 0 to 5V of 2.5V reference by IC102 pin 46 (PWM-DAC), and DC current of +/-150mA

(max) is made to flow to the speed modulating coil by IC804 pin 8.

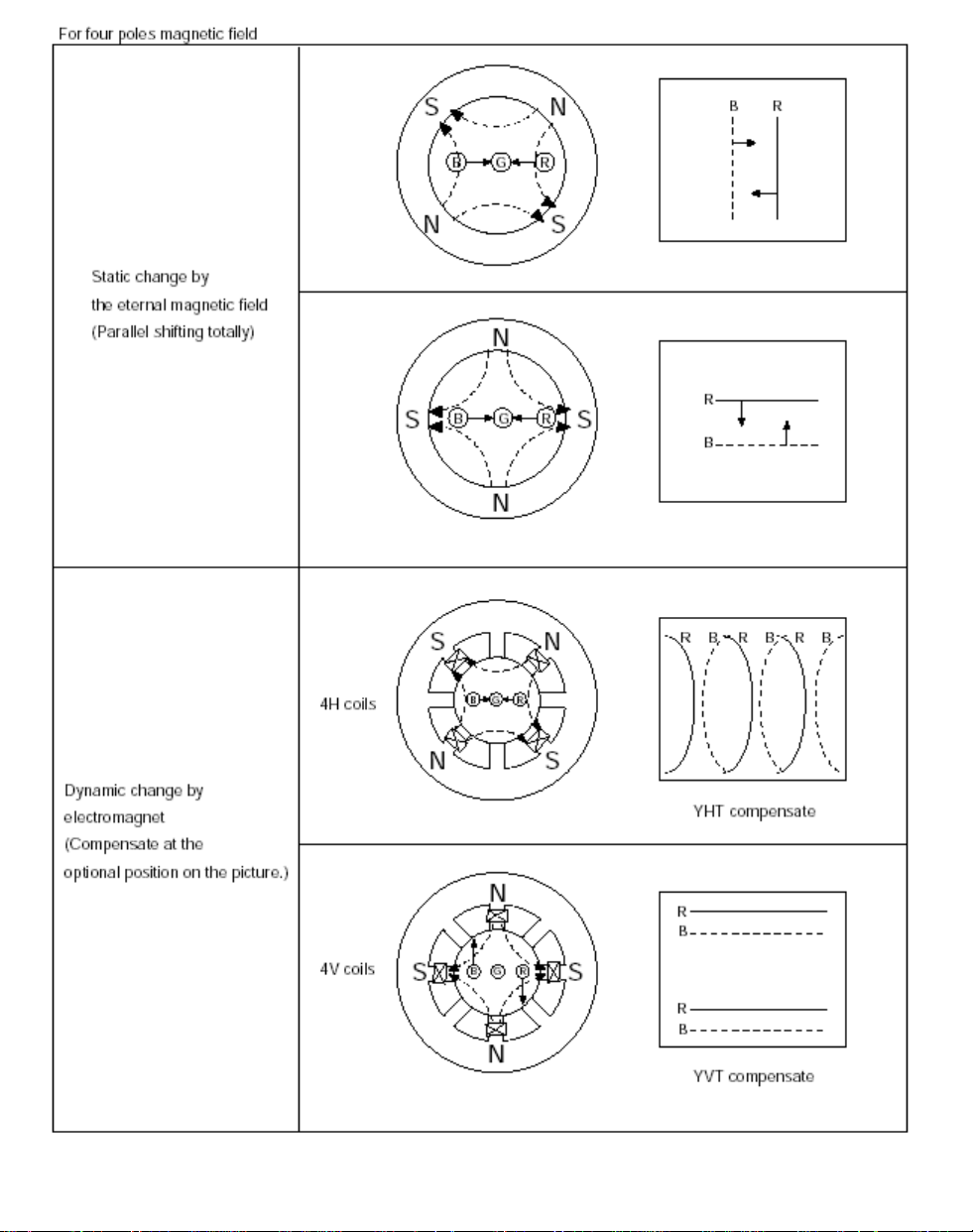

1.4.6 Digital dynamic convergence clear (DDCC) circuit

In the digital dynamic convergence clear (hereafter called DDCC) circuit, the convergence compensating

current waveform is produced and amplified, and the convergence is compensated by the compensation

current flowing to the sub yoke that is installed as the rear unit of the deflection yoke.

Though the principle of the convergence compensation with the sub yoke is same as the CP ring, the CP

Vertical magnetic field landing cancel circuit

Page 19

ring is used for the static variation with the parallel movement in the whole picture in the uniform magnetic

field with the permanent magnet but the sub yoke is used for dynamic variation that compensates a

desired position on the picture by controlling the current waveform that flows to the coil of the electric

magnet. (See Fig. 7)

1.4.6.1 Production of compensation current waveform

There are 30 kinds of compensation elements, and they are programmed in IC601 one by one using the

function. Inputting the compensation coefficient into the function controls the amplitude of the current.

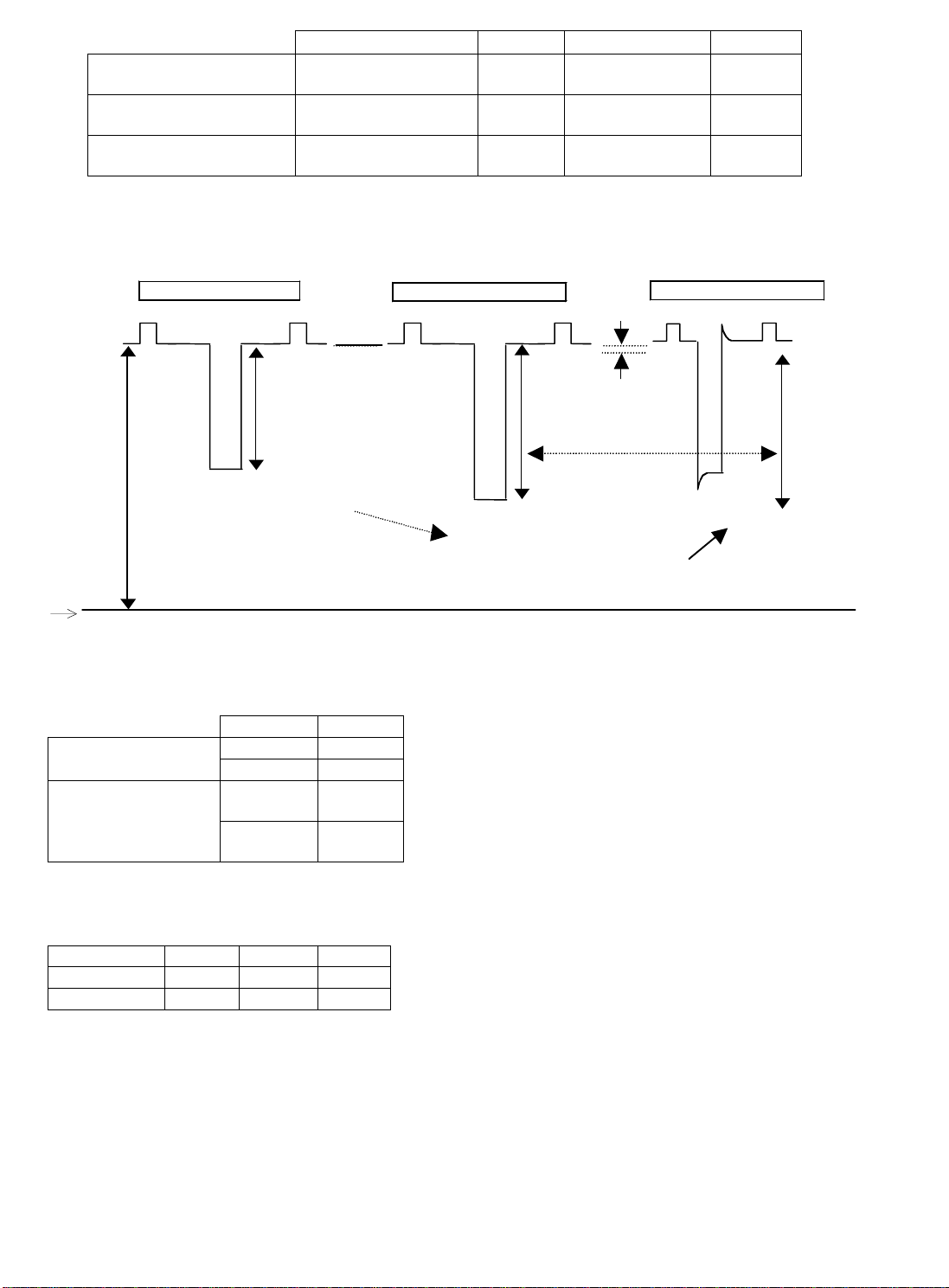

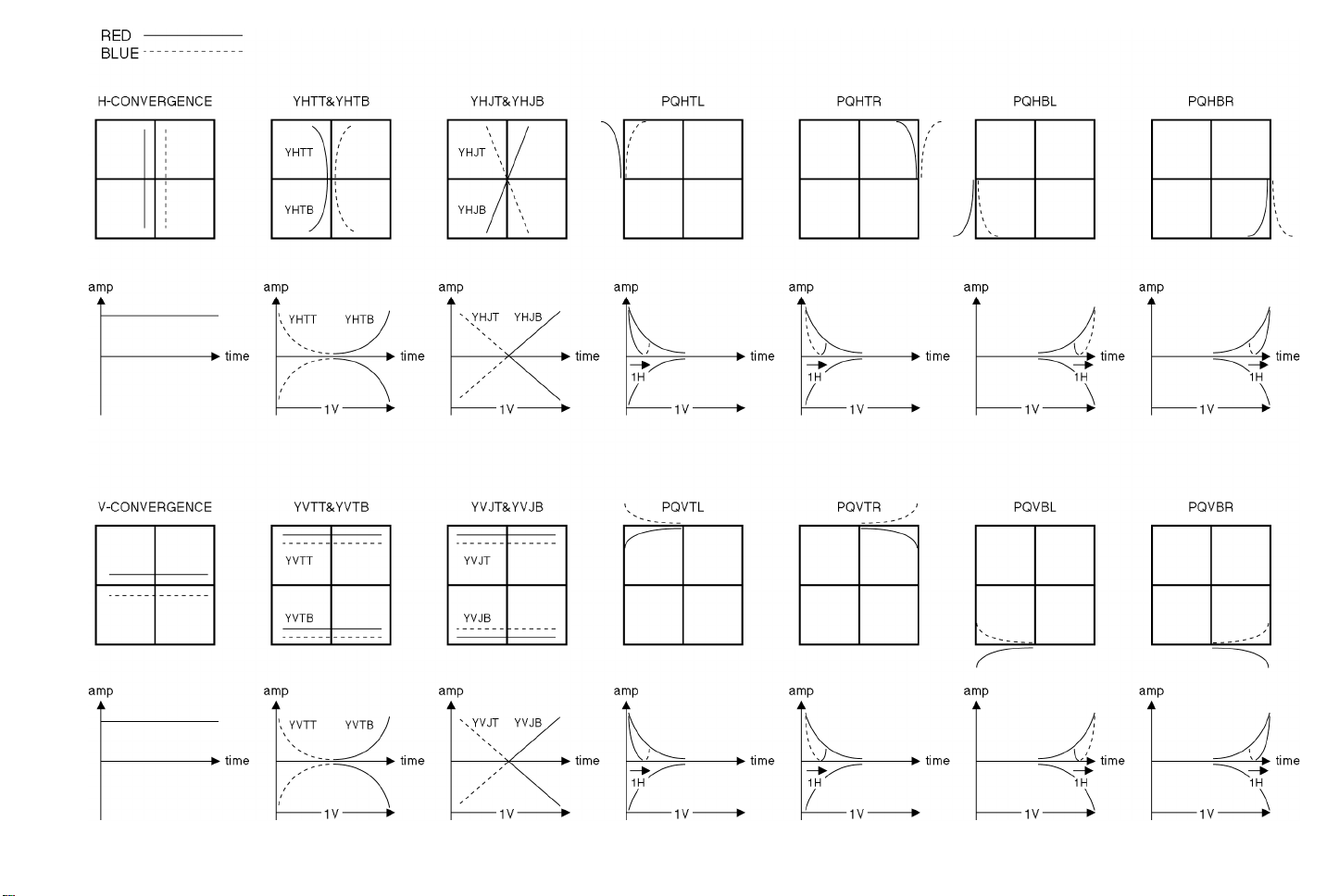

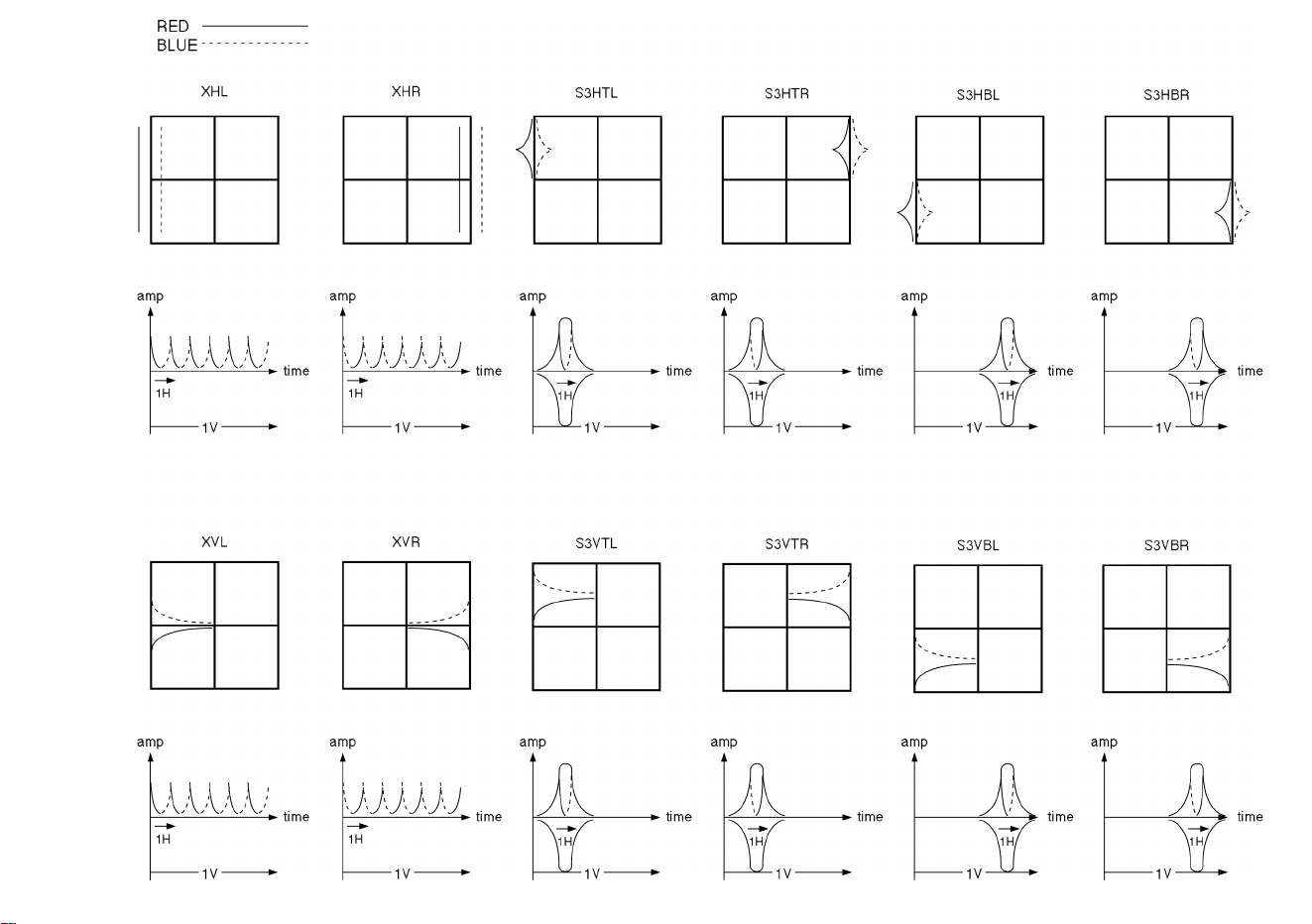

Examples of the functions and current waveform/compensation operation of YH (YHTT, THTB, YHJT,

YHJB) are shown as follows.

In the above formulas, b11T, b11B, b12T and b12B express the compensation coefficients, and y and y^2

express the primary and secondary functions of the vertical frequencies.

The other parts except the compensation coefficients are programmed, and desired amplitudes (=

compensation amount) are gained by varying the coefficients.

YHTT and YHTB compensate the upper and lower parts of the picture of the characteristic components of

their DYs to compensate the upper and lower parts of the picture of the axis deviation component. The

component gained by adding YHT and YHJ is multiplied by the offset compensation coefficient a11. The

resultant component is regarded as 4H_SC, and is output from IC601 pin 61.

1.4.6.2 Waveform, and operation on the picture

The case in which the currents flow through 4H coils of the sub yoke is explained. Regarding YHT

(secondary function in the vertical frequency), in case of Fig. 6 as an example, the current is large in the

same direction at the start (upper end of the picture) and the end (lower end of the picture) of the vertical

frequency, and is zeroed on the X axis of the picture. Therefore, the magnetic field that is proportional to

it is generated, and RED and BLUE vary in the same direction only at the upper and lower ends of the

picture. As aforementioned, YHT can be independently controlled at the upper part (b11t・y^2) and lower

part (b11B・y^2).

Moreover, regarding YHJ (primary function in the vertical frequency), if the flowing direction of the current

is opposite at the start (upper end of the picture) and the end (lower end of the picture) of the vertical

frequency as an example, RED and BLUE vary in the opposite direction only at the upper and lower ends

of the picture. Making the current flow to the 4V coil can do compensation in the vertical direction.

Fig. 8 (a) and (b) shows the image of each adjustment item of the DDCC adjustment.

Fig. 6 DDCC compensation image

Page 20

1.4.6.3 Adjustment method

Before the adjustment with the compensation circuit, it is necessary that they are properly adjusted at the

center (H-STATIC and V-STATIC), on the X axis (XH slider, B-Bow 4P, XV differential coil) and on the Y

axis (YH volume, YV volume).

Though DC current is superimposed on the sub yoke, H-STATIC and V-STATIC are pushed to the greatest

possible extent by the adjustment with CP ring in order to reduce the stress of the driver IC8A1

(STK391-110).

Moreover, although 6H coil is carried in the case of this chassis, in addition to 4H and 4V coils, since the

range which can be adjusted is a range used as fine adjustment, it is a premise that the convergence

between Red, Blue and Green (6H and 6V) is in a standard as a performance of ITC (CRT&DY) in the

state where 6H coil is not used.

As the adjustment procedure, the adjustment values of 30 elements are not respectively zeroed but they

are adjusted to nearest to zero with a total balance in good order.

In other words, the balance (compromise) adjustment with each adjustment item is applied.

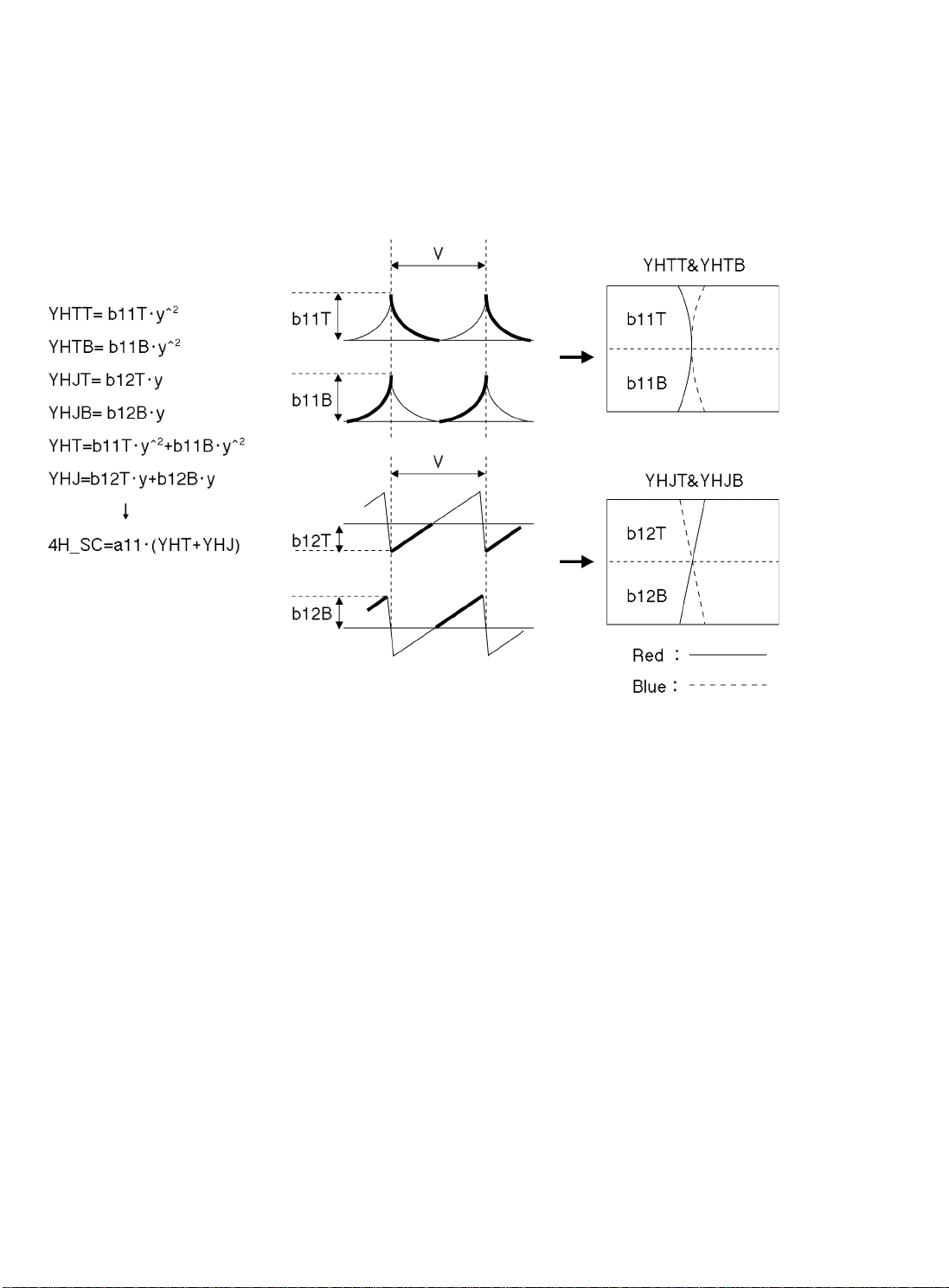

The correspondence of the names of DDCC adjustment mode to the coefficients of all 30 elements is

shown below.

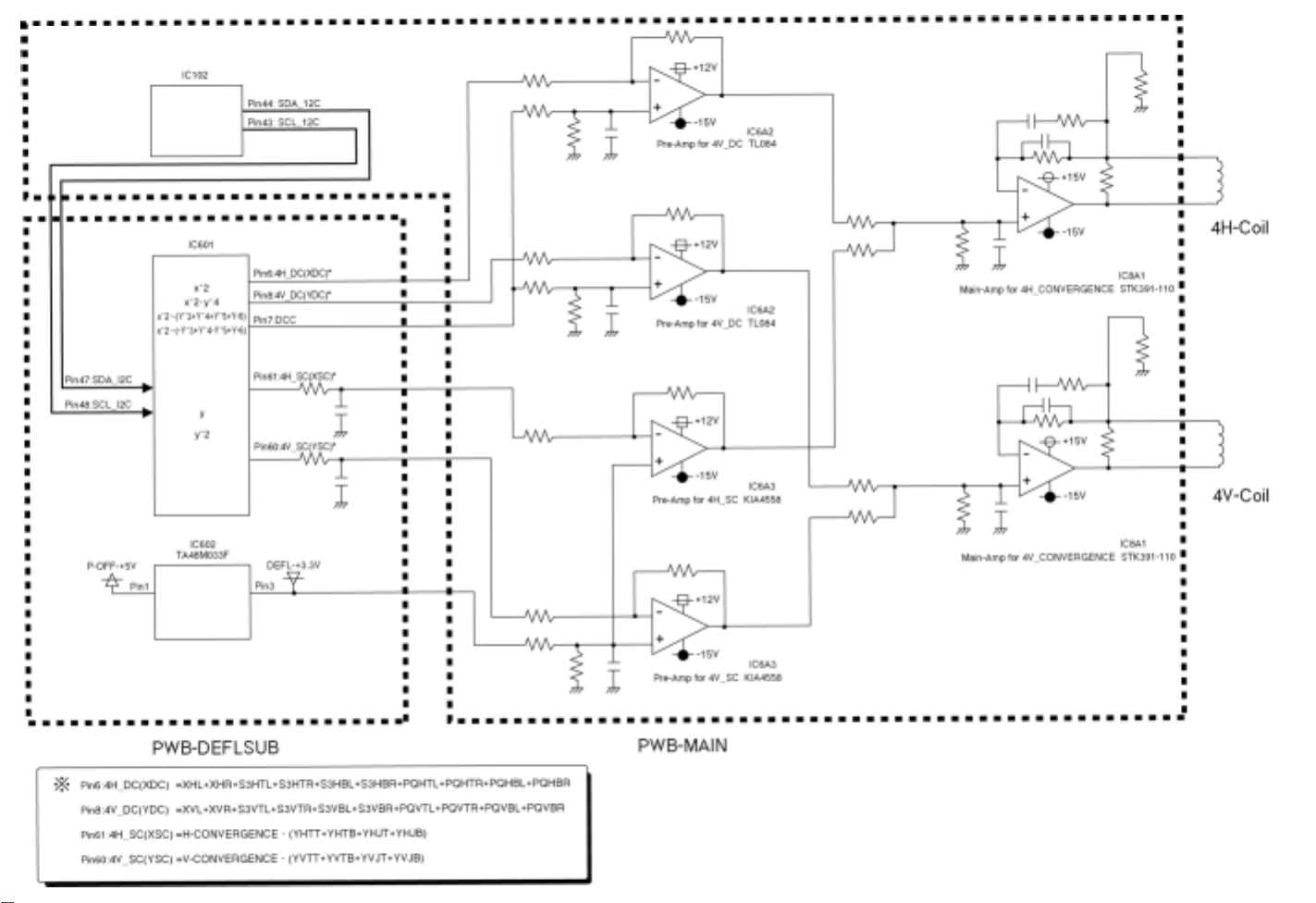

1.4.6.4 Block diagram

Fig. 9 shows the block diagram of the DDCC circuit.

The components 4H_DC (pin 6), 4H_SC (pin 61), 4V_DC (pin 8) and 4V_SC (pin 60) supplied from IC601

to 4H-Coil and 4V-Coil are output, the dynamic component (4H_DC, 4V_DC) is amplified with IC6A2, and

the static component (4H_SC, 4V_SC) is amplified with IC6A3.

DDC (pin 7) output from IC601 and DEFL_+3.3V (pin 3) output from IC602 are respectively the reference

voltage of Op-Amp (IC6A2) that amplifies the above dynamic component (4H_DC, 4V_DC) and the

reference voltage of Op-Amp (IC6A3) that amplifies the static component (4H_SC, 4V_SC).

On each of 4H and 4V, the waveform added with the dynamic component and static component is input to

IC8A1 pin 3 and pin 4, and it allows the specified current to flow to each convergence compensation coil.

Page 21

Fig. 7 The principle of DDCC compensation

Page 22

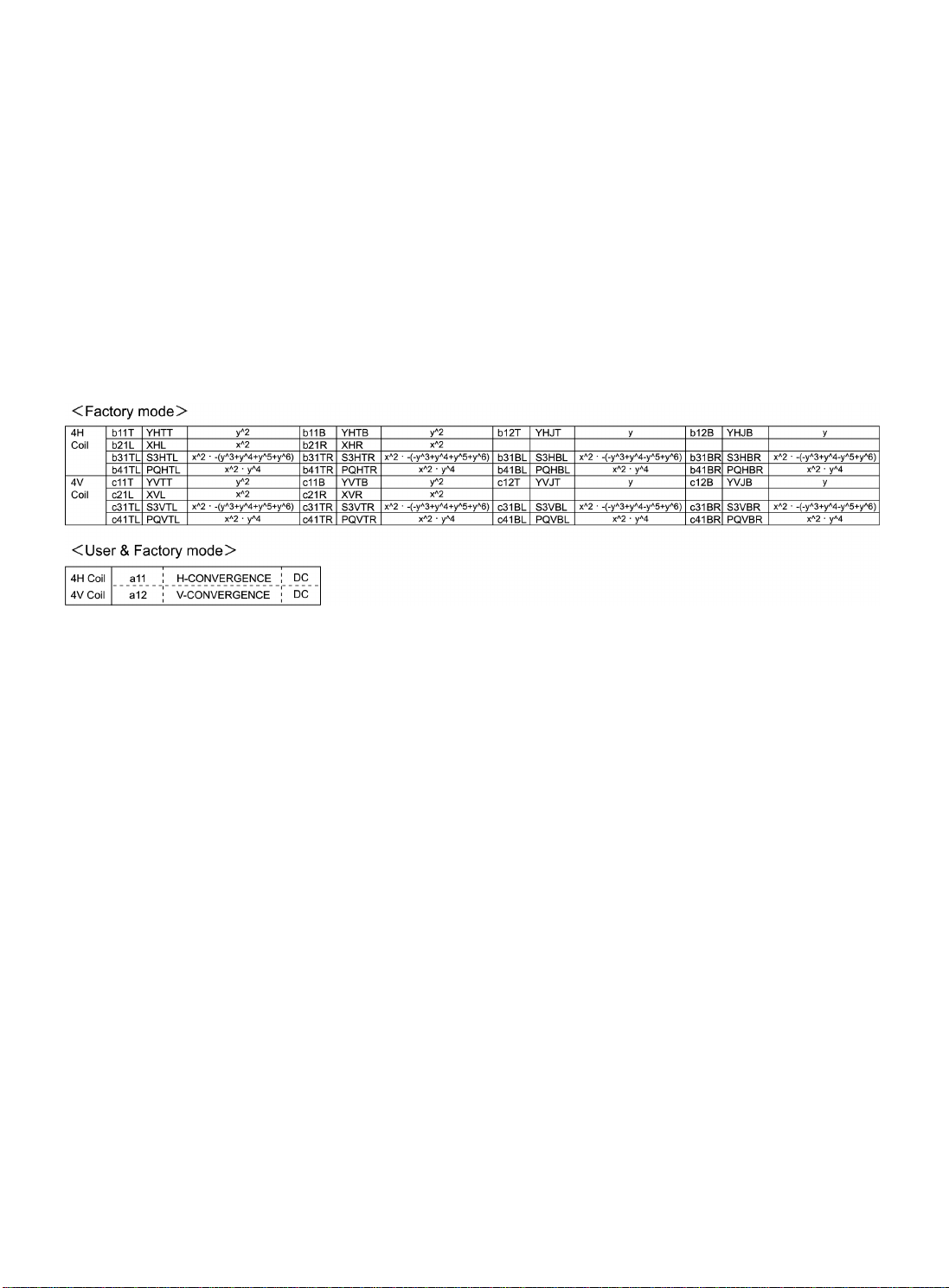

Fig. 8 (a) DDCC adjustment item

Page 23

Fig. 8 (b) DDCC adjustment item

Page 24

Page 25

1.4.7 East-west horizontal convergence canceling function

It is the function which rectifies automatically change of YHJT, YHJB and XVL, and XVR (between Red

and Blue) by east-west magnetic field change, detects the detection voltage change from IC2S0

(geomagnetism sensor unit), and is carrying out automatic compensation.

1.5 USB circuit

1.5.1 Outline

This monitor loads the standard USB SELF POWERED HUB with 1 upstream and 4 downstreams.

(1) Serial data bus

Data bus is connected from upstream connector CN1A0 to upstream port of HUB controller IC1A0, and

downstream connectors CN1A1 to CN1A4 are connected from HUB controller.

HUB controller relays data communication between the upstream side (PC) and the downstream side

(device).

Downstream connection of HUB controller

Port on circuit diagram Connector Silk indication

Port 1 CN1A1 1

Port 2 CN1A2 4

Port 3 CN1A3 3

Port 4 CN1A4 2

(2) Power supply to downstream

USB HUB of this monitor is SELF POWERED HUB, and it can supply the power of +5V 500mA (max)

to each downstream from transformer T902 on PWB-MAIN. Further, HUB controller IC1A0 has the

function of detecting overcurrent, and stops supplying the power to each downstream port when

overcurrent (500mA or more) is detected at each port.

1.5.2 USB downstream power supply

(1) Supply of Vpp power

When HUB controller IC1A0 is recognized from the direction of upstream, the signal which functions

as a switch of power output for a downstream port is output (IC1A0 pins 2, 16, 17 and 32).

When IC1A0 pins 2, 16, 17 and 32 become LOW, FET gates are turned ON (LOW), and EFT

transistors Q1A1, Q1A2, Q1A3 and Q1A4 supply the power to the downstream ports (CN1A1 to

CN1A4) respectively.

(2) Detection of overcurrent

HUB controller IC1A0 has the function of detecting overcurrent. If the current output at each port

exceeds 550mA (min), gates of FET transistors Q1A1, Q1A2, Q1A3 and Q1A4 turn OFF (HIGH),

automatically output of current stops only to the port that overcurrent is detected.

In order to re-operate the port that overcurrent is detected, either of the followings should be carried

out:

1.OFF/ON of monitor power supply

2.Pulling-out and pulling-in of upstream cable

3.Restart of PC

1.5.3 HUB controller power output

HUB controller IC1A0 has a built-in 3.3V regulator, and outputs from IC1A0 pin 1.

1.5.4 USB power on reset

At the time of a power ON and spark detection circuit operation, the reset pulse to USB is output to pin 21

of IC1A0 from pin 2 of IC102. At pin 21 of IC1A0, it is reset by LOW and is reset release by HIGH.

Page 26

1.6 Control block

1.6.1 Function of control circuit

The control block is mainly on MAIN board and DEFL-SUB board, and the function is as follows.

(1) Auto-tracking

(2) Control of picture size, distortion and position

(3) Adjustment data memory

(4) Sync. signal detection

(5) OSM control

(6) Video pre-amp control and clamp pulse position control

(7) Power ON/OFF control

(8) Heater voltage control

(9) DDC 1 / 2B / 2Bi

(10) Operating time display

The control block is composed of the following four components.

(1) Microcomputer: IC102 (MAIN board)

(2) OSM IC: IC212 (VIDEO board)

(3) EEPROM: IC104 (MAIN board)

(4) Sync. signal input: IC215 (VIDEO board)

1.6.2 Auto-tracking process

The microcomputer (IC102) calculates the frequency of the sync. signal input and outputs the distortion

compensation data corresponding to the input signal timing to the deflection IC (IC600).

Control with IC600 is carried out via I2C bus.

1.6.3 EEPROM

The capacity of the EEPROM (IC104) is 32 kilobits (4 kilobytes). The factory adjustment data, user

adjustment data, and EDID data are stored in the EEPROM.

Up to 10 items can be stored as the factory preset data, and up to 16 items can be stored as the user

preset data. Regarding the factory preset timing, if the user reset the memory, the factory adjustment data

will be called up.

The EDID data is stored in the last 128-byte area.

1.6.4 On-Screen-Manager (OSM) controller

The On-Screen-Manager (OSM) controller IC IC212 displays the picture used for picture adjustment and

so on. OSM display data is sent from the microcomputer (IC102) via I2C bus.

1.6.5 Heater voltage control

In the normally ON status, the heater voltage is supplied from the +8V line of the main power circuit.

Heater resistor R203H connected in series adjusts this supplied voltage to +6.15V (typ) (rated voltage for

the CRT) before application. In the suspend mode, the sub-power circuit applies the voltage so that the

screen can be instantaneously recovered. (In the suspend mode, the heater voltage is low compared with

that of the normally ON status.)

1.6.6 Protection circuit operation

This monitor can detect the following problems, and can stop the monitor operation after detection of a

problem. If the protector function is activated, the Power-On Indicator (LED) will flicker so that you can

localize the activated protector.

1.6.6.1 X-ray protector

The CRT monitor radiates X-rays, and exposure to too much radiation is very dangerous. For this reason,

the CRT monitor incorporates an X-ray protector. If the high voltage value rises above the specified value,

the protector will automatically stop applying the high voltage. For this model, the X-ray protector

activation point is set to 31.0kV (entirely black screen).

To disable the X-ray protector for the reason of repair, etc., set the monitor in the factory mode.

Page 27

1.6.6.2 High voltage data error detection

Important safety data, such as the high voltage adjustment value and the X-ray protector activation

voltage, are stored in the EEPROM. For each safety data, there is backup data. If both data values differ

from each other, the monitor will enter the power saving mode (the high voltage will not be applied).

1.6.6.3 Beam current protector

If too much beam current flows (1.5mA or more), "H" will be input to the ABL terminal (pin 27 of the

microcomputer (IC102)). From this terminal, the microcomputer will detect overflow of the beam current,

and will set the monitor in the power saving mode.

1.6.6.4 Power-On Indicator (LED) flickering pattern in each protector operating

If a protector is activated, the Power-On Indicator (LED) will flicker as shown below to indicate the

activated protector (to show the cause of the problem).

Table 2 Power-On Indicator (LED) flickering pattern in each protector operating

Protector state

X-ray protector 1 1

High voltage circuit latch

detection

Data protector 3 1

Short (0.5s) lighting times Long (2s) lighting times

Power-On Indicator (LED) state

2 1

Beam protector 5 1

+B short-circuit 7 1

1.6.6.5 Operating time

If "DIAGNOSIS" is selected from the menu in the factory mode, the monitor operation time will appear. 0.5

hours will be added to this value every 30 minutes.

P: Indicates the power-on time (including the operation time in the power saving mode).

K: Indicates the heater power-on time.

1.6.6.6 The DDC communication

The microcomputer carries out the DDC communication. For this communication, the microcomputer

reads out the EDID data from the EEPROM, and stores the data in the RAM. When receiving a request

from the PC, the microcomputer will output the data from pins 8 and 11.

Page 28

1.6.6.7 Microcomputer pin assignment

#

1 H_LOCK

2

3 INPUT SEL

4 HSK

5 SUSPEND

6 C TIME SEL

7 OPTION

8 DDC_DATA

9 FLASH_TX

10 BEAM/SHORT RxD0/P50

11 DDC_SCL

12 RESET

13 NMI

14 (+) 5V

15 STBY

16 GND

17 X'TAL

18 X'TAL

19 MODE SW1

20 MODE SW2

21 GND

22 KEY1

23 KEY2

24 X RAY PRO

25 TEMP

26 BEAM TIME

27 ABL/C TIME

28 EW_SENSE

29 SN_SENSE

30 Vcc

31 LED

32 VSYNC OUT VSYNCO/P61 O V. sync. output

USB-SPARK

USB-RESET

PORT

ASSIGN I/O

IRQ2/P40

IRQ1/P41

IRQ0/P42

RD/P43

WR/P44

IOS/AS/P45

EXCL/o/P46

SDA0/WAIT

TxD0/P50

SCL0/SCK0

RES

MNI

Vcc

STBY

GND

XTAL

EXTAL

SW1

SW2

AVs s

AN0/P70

AN1/P71

AN2/P72

AN3/P73

AN4/P74

AN4/P75

AN6/P76

AN7/P77

AVc c

HFBACK/P60 O LED output

I H_UNLOCK detection

I/O For FLASH writ ing

O Power cut detection

O SOA output

O Suspend

O

I

I/O DDC data

O PZTAT

I Beam protector

I/O DDC clock

I Reset

I NMI

I

A/D Key input

A/D Key input

A/D X-ray protector

A/D Temp. detection

A/D Time detection

A/D Heater voltage detection 38 Hsync OUT

A/D

A/D

FUNCTION

(available as input port)

Mode setting

Mode setting

H. magnetic field detection

V. magnetic field detection

#

64 CS8

63 CS7

62 CS6

61 CS5

60 CS4

59 CS3

58 CS2

57 CS1

56 HVADJ

55 BRIGHTNESS P11/PWMX1 P Brightness

54 SW LIN2

53 SW LIN1

52 PURITY_BL

51 PURITY_BR

50 PURITY_TL

49 PURITY_TR

48 GND

47 DEGAUSS

46 V_CANCEL

45 ROTATION

44 IIC_SDA

43 IIC_SCL

42 P OFF

41 LIN PWM1

40 6H

39 Vcc

37 SOG IN

36 HSYNC IN

35 CLAMP OUT

34 HSYNC SEL

33 VSYNC IN

PORT

ASSIGN I/O

P37

P36

P35

P34

P33

P32

P31

P30

P10/PWMX0 P HVADJ

O CS switching 8

O CS switching 7

O CS switching 6

O CS switching 5

O CS switching 4

O CS switching 3

O CS switching 2

O CS switching 1

FUNCTION

P12/PW2

P13/PW3

P14/PW4

P15/PW5

P16/PW6

P17/PW7

Vss

P20/PW8

P21/PW9

P22/PW10

SDA1

SCL1

P25/PW13

P26/PW14

P27/PW15

Vcc

P67/HSYNCO O H. sync. output

P66/CSYNCI I SYNC ON G input

P65/HSYNCI I H. sync. input

P64/CLAMPO O CLAMP OUT

P63/VFBACKI O HSYNC SEL

V_SYNCI

O SW LIN2

O SW LIN1

P Corner purity BL

P Corner purity BR

P Corner purity TL

P Corner purity TR

O

P

P Rotation

I/O Internal IIC data

I/O Internal IIC clock

O POWER OFF

P H. linearity

P 6H

I V. sy nc . i np u t

DEGAUSS

V. m agnetic field cancel output

Page 29

1.7 X-ray protection circuit and safety protection circuit

1.7.1 X-ray protection circuit

This circuit prevents X-ray radiation from exceeding the dangerous level due to the abnormal rise of high

voltage.

Do not modify the high voltage circuit and the safety protection circuit.

The upper limit of the high voltage value and the beam current value are determined by the X-ray radiation

upper limit curve of CRT.

In the X-ray protection circuit, the X-ray protector activation voltage depends on the beam current. The

X-ray protector, however, is normally activated at approximately 30kV (when the beam current is

approximately 1mA). D709 and C704 rectify the increase in the pulse voltage output from pin 6 of T701.

Pin 24 of IC102 detects this rectified voltage. If the detected voltage exceeds the specified value, the

SUSPEND signal output from pin 5 of IC102 will be set to 'Low', and the P-OFF signal output from pin 42

will be also set to 'Low' (power-off mode). In addition, operation of IC701 will be stopped. This condition of

the protection circuit will be retained until the power switch is turned OFF.

1.7.2 Beam current protection circuit

When the current supplied to the high voltage generating winding of FBT exceeds approx. 1.5mA, the

protection circuit functions. The detection of the beam current is executed by the voltage fall of R722

connected between T901 pin 9 and the 12V.

Resistors R723 and R724 divide the potential of this voltage. The divided voltage is then input to pin 27 of

IC102 via IC703. If the input voltage exceeds the specified value, the SUSPEND signal output from pin 5

of IC102 will be set to 'Low', and the P-OFF signal output from pin 42 will be also set to 'Low' (power-off

mode). In addition, operation of IC701 will be stopped. This condition of the protection circuit will be

retained until the power switch is turned OFF.

1.7.3 IC701 overcurrent protection circuit

The peak value of the drain current of Q701 and the both-end voltages of source resistors R708 and R709

are detected by pin 2 of IC701. If the voltage of this pin exceeds 1.2V (typ), pin 9 of IC701 will stop

outputting the drive waveform. If the voltage of IC701 pin 2 drops below 1.2V (typ), pin 9 of IC701 will

output the drive waveform again.

1.7.4 IC701 overload protection circuit

If overload occurs consecutively and the overcurrent protection circuit is activated consecutively, this

overload protection circuit will enter the latch mode to stop operation. If the voltage of IC701 pin 2 exceeds

1.0V (typ), C709 will be charged. If the voltage of IC701 pin 13 exceeds 2.5V (typ), IC701 will enter the

latch mode to stop the control operation. This condition of the protection circuit will be retained until the

power switch is turned OFF.

1.7.5 IC902 overcurrent protection circuit

IC902 is equipped with an overcurrent protection circuit. R928 detects the drain current of the incorporated

FET. If the voltage of IC902 pin 1 exceeds approximately 0.7V, this overcurrent protection circuit will be

activated.

1.7.6 Short-circuit protection circuit on secondary power side

The output line of each secondary power (+215V, +80V, +15V, +8V, -15V) is equipped with a short-circuit

detection circuit. If a secondary line is overloaded and the output voltage drops by 30 to 40% of the normal

voltage, this short-circuit protection circuit will be activated.

1.7.7 Overvoltage protection circuit

The harmonic suppression circuit (active filter circuit) and the main power circuit are respectively equipped

with an overvoltage protection circuit. If the voltage between both ends of C911 rises by 10% of the normal

voltage, or if the voltage of the main power secondary output line rises by 30 to 40% of the normal voltage,

operations of IC901 and IC902 will be stopped.

Page 30

1.8 Adjustment

1.8.1 Adjustment mode

This monitor has the following adjustment modes.

(1) User mode (Normal mode)

(2) Factory mode (Factory adjustment mode)

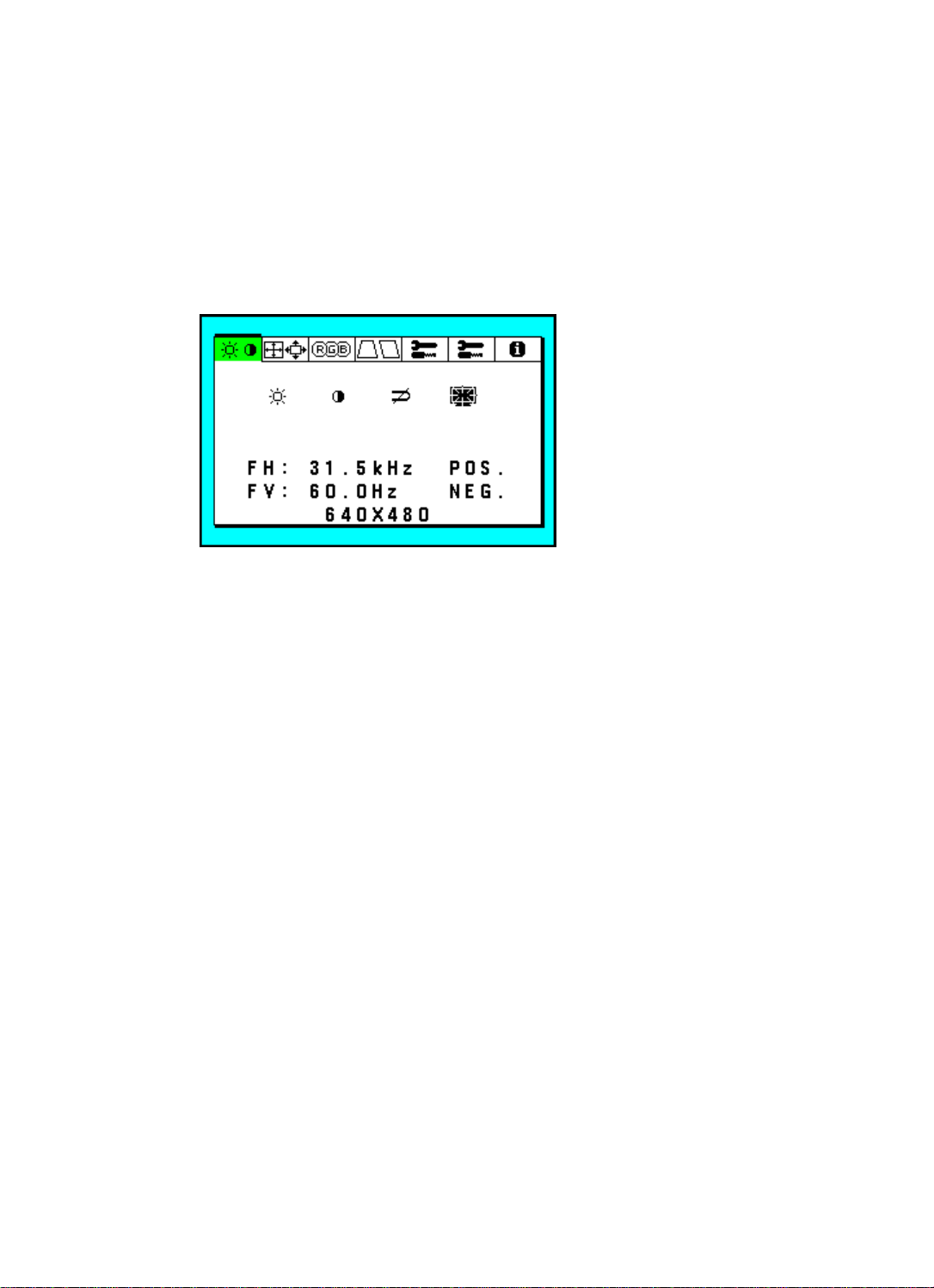

1.8.2 User mode (Normal mode)

This is the mode user executing the adjustment and setting. When pressing button of EXIT, (<), (>), (-),

(+) and SELECT on the front panel, the following menu picture is displayed on the screen.

The adjusted data in the user mode is memorized to EEPROM automatically.

The adjustment group can be selected with (<), (>), (-) and (+) buttons.

(+) and (-) buttons have the functions of the variable of the adjustment value.

The items can be adjusted in the user mode are as following table.

Page 31

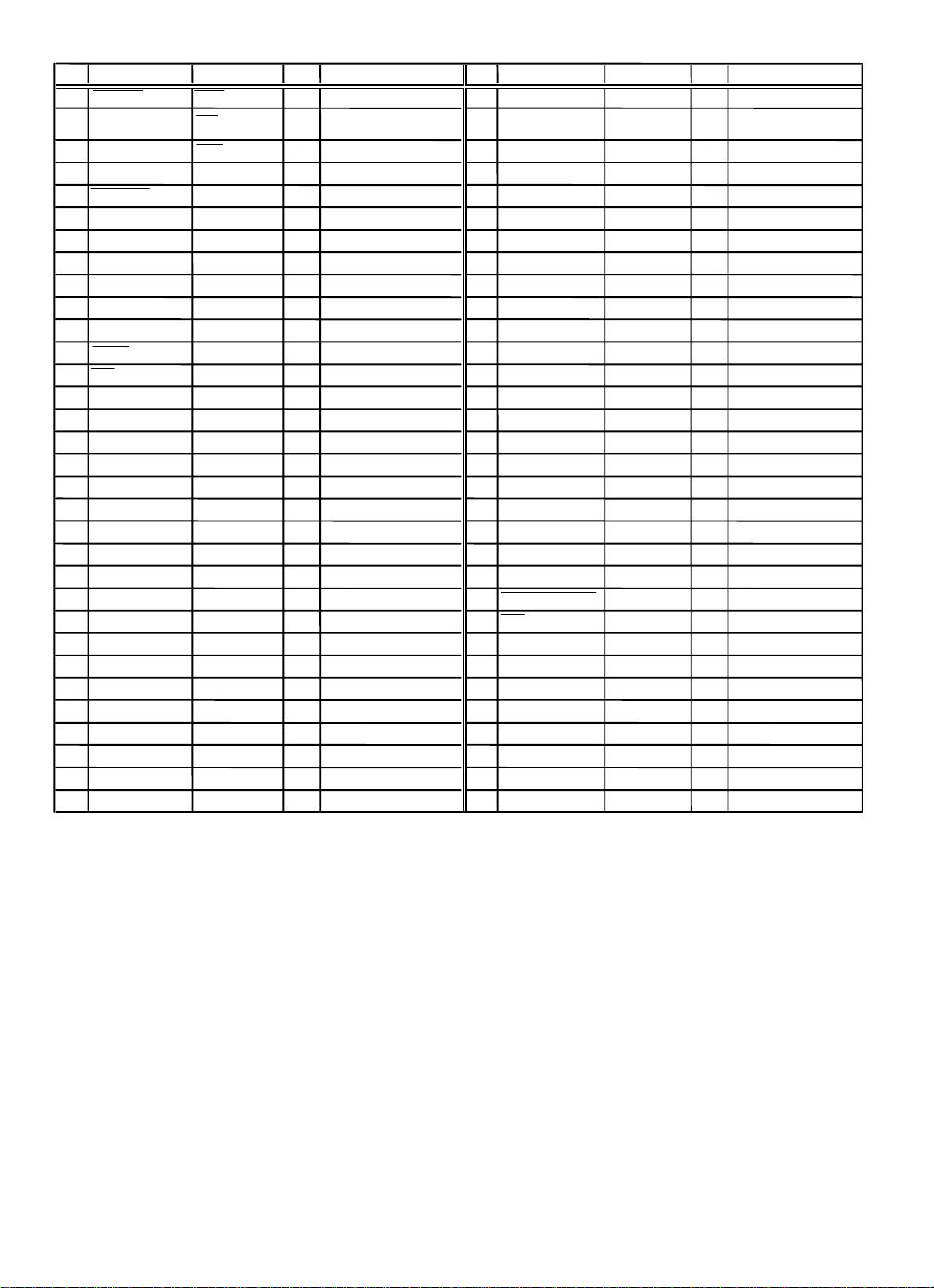

OSM menu (User mode)

Item

Group icon

icon

Group 1

RESET

Item

BRIGHTNESS

CONTRAST

DEGAUSS

CONSTANT BRIGHTNESS

AUTOADJUST

LEFT / RIGHT

Adjustment

− +

To decrease the

brightness.

To decrease the contrast.

N/A

N/A

Restore to factory preset level with RESET

button.

N/A

To move the image

to the left.

To increase the brightness.

To increase the contrast.

To eliminate possible

color shading or impurity.

Activates the constant

brightness function.

To adjust the screen

size automatically

based on input timing.

To move the image to

the right.

Group 2