MITEL WL600KG, WL600GP1R, WL600C Datasheet

The WL600C is a 2.4-2.5GHz RF transmitter and

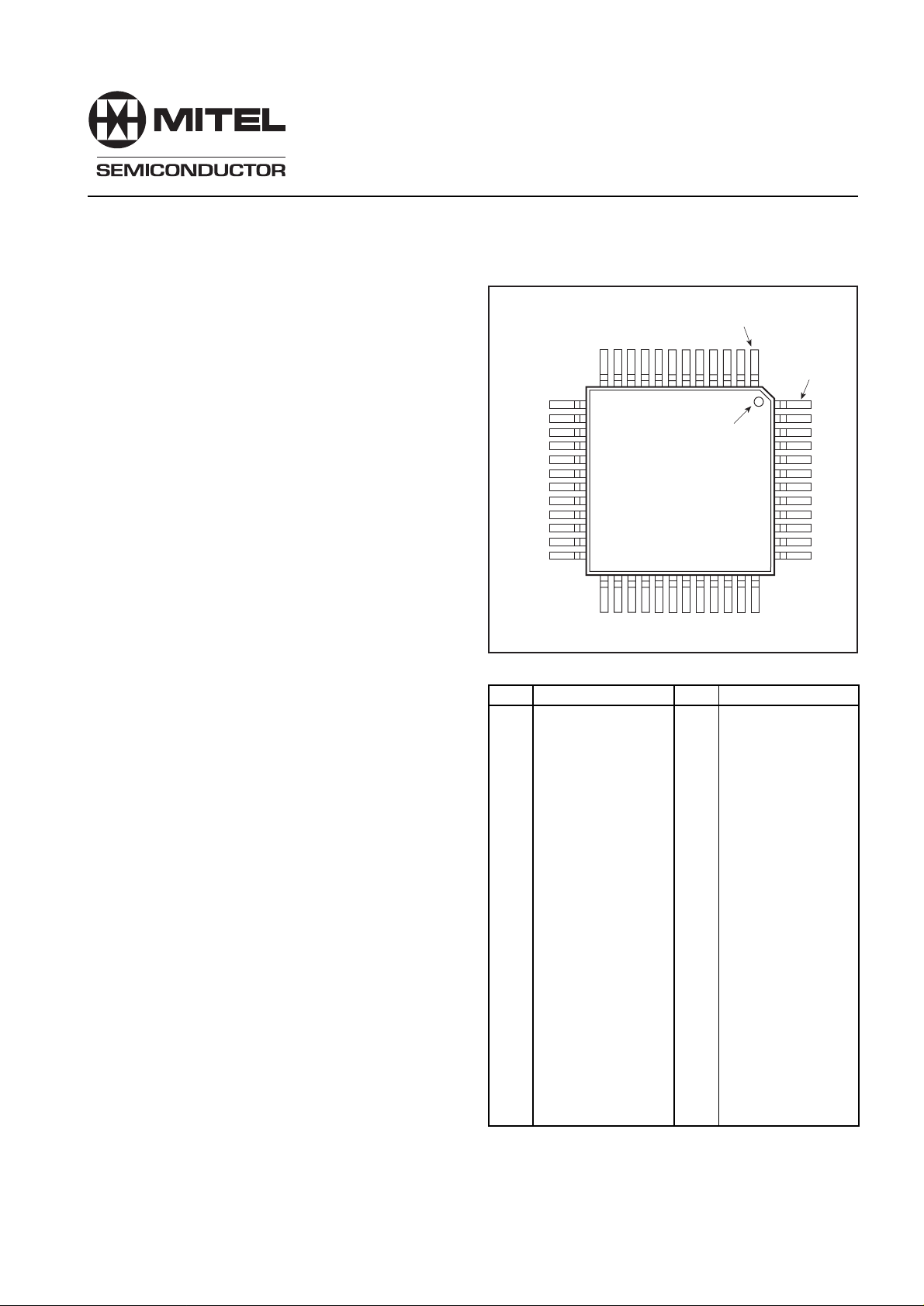

PIN 48

PIN 1 IDENT

PIN 1

receiver chip for use in digital radio, and operates from a

supply voltage of 2.7 - 3.6V. It is designed to work with the

Mitel Semiconductor WL800 frequency synthesiser and

the WL102 WLAN controller chip which together make up

the DE6038 frequency hopping Wireless Local Area

Network (WLAN) transceiver.

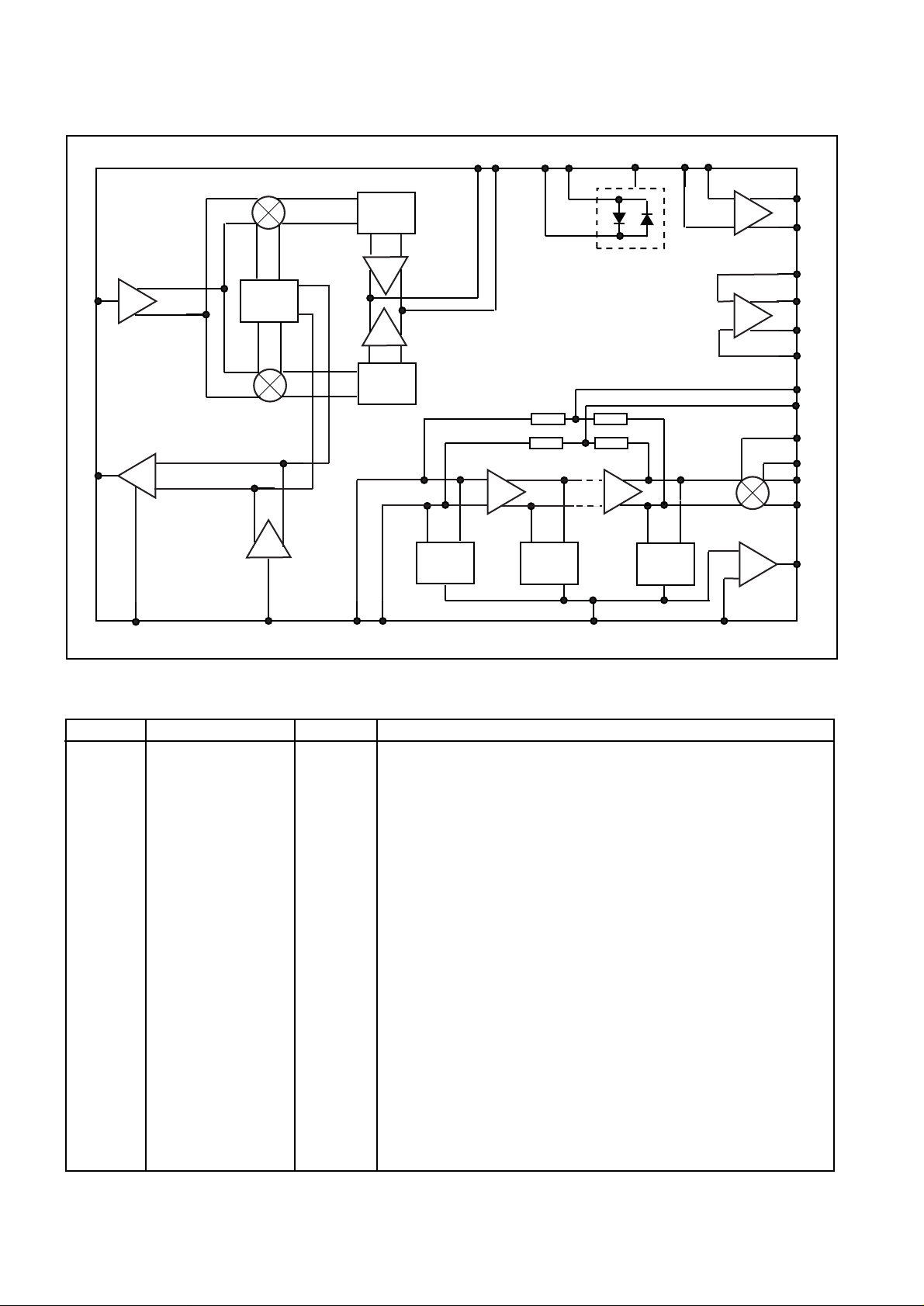

The receiver circuit contains a low noise amplifier,

image rejecting mixer, IF limiting strip with RSSI and a

quadrature demodulator. There is also a power amplifier

driver stage and ramp control facility for use in transmit.

FEATURES

■ Part of DE6038 chipset (WL800, WL102)

■ High level of integration

■ Low noise figure

■ Low power consumption

■ High data rates with comparator for 2 level FSK

■ Minimal external components

■ 48 lead LQFP package

WL600C

2.4 - 2.5GHz RF and IF Circuit

Preliminary Information

DS4581 2.1 August 1997

LQFP48

Fig.1 Pin connections - top view

ABSOLUTE MAXIMUM RATINGS

Supply voltage Vcc 4V

Transmit/Receive and standby input -0.5 to Vcc +0.5V

Current consumption TBD

Junction temperature Tj 150°

ESD protection 2KV

ORDERING INFORMATION

WL600C/KG/GP1R

RELATED DOCUMENTS

Datasheets WL800/102 DE6038

Pin Description Pin Description

1 QUAD+ 25 VCC_RF

2 QUAD- 26 GND_RF

3 GND_IF 27 VCC_LNA

4 DEMOD_OUT+ 28 GND_RF

5 DEMOD_OUT- 29 RF_IN

6 RSSI 30 LNA_DEGEN

7 CLAMP_SET 31 LNA_DEGEN

8 CCA_THRESHOLD 32 DRIVE

9 VCC_IFSTRIP 33 VCC_PA

10 DECOUPLE_LOG- 34 GND_RF

11 DECOUPLE_LOG+ 35 RAMP_CAP

12 IF_IN+ 36 PA_ON

13 IF_IN- 37 STDBYB

14 CCAB 38 TX/RXB

15 GND_IF 39 GND_LO

16 BUFFER_IN+ 40 LO_IN

17 BUFFER_IN- 41 VCC_LO

18 VCC_DATA 42 DATA_IN+

19 RXD 43 DATA_IN20 RXDB 44 BUFFER_OUT21 GND_RF 45 BUFFER_OUT+

22 IF_OUT- 46 CLAMP23 IF_OUT+ 47 CLAMP+

24 GND_PADDLE 48 GND_PADDLE

WL600C

29

LNA

32

35

IMAGE

REJECT

MIXER

IMAGE

REJECT

MIXER

PA DRIVE

BUFFER

LO

BUFFER

40 12

PHASE

SHIFT

PHASE

SHIFT

PHASE

SHIFT

13

22 23 46 47 7

ACTIVE

CLAMP

CIRCUIT

IF STRIP

DETECTORS

6

42

BUFFER

AMP

COMPARATOR

43

DATA

SLICE

19

20

16

44

X2

45

17

10

11

1

2

4

5

14

8

Fig. 2 WL600C block diagram

DEVICE PIN OUT

Pin Ref Type Description

1 QUAD+ I/O Quadrature demodulator tank circuit connection

2 QUAD - I/O Quadrature demodulator tank circuit connection

3 GND_IF GND Ground for IF strip circuitry

4 DEMOD_OUT + OUT Demodulator output

5 DEMOD_OUT - OUT Demodulator output

6 RSSI OUT RSSI detector analogue output

7 CLAMP_SET IN Sets clamp knee voltage

8 CCA_THRESHOLD IN Sets level at which CCA comparator will switch

9 VCC_IFSTRIP VCC Power supply for log amp, demod, and internal references

10 DECOUPLE_LOG - I/O Decoupling for log amp feedback network, AC couple

11 DECOUPLE_LOG + I/O Decoupling for log amp feedback network, AC couple

12 IF_IN + IN Log amp input, AC couple

13 IF_IN - IN Log amp input, AC couple

14 CCAB OUT CCA comparator output: signal = logic high, clear = logic low

15 GND_IF GND Ground for IF strip circuitry

16 BUFFER_IN + IN x 2 buffer input

17 BUFFER_IN - IN x 2 buffer input

18 VCC_DATA VCC Power supply for clamp, data comparator and buffer amp

19 RXD OUT Data comparator output

2

WL600C

Pin Ref Type Description

20 RXDB OUT Data comparator output

21 GND_RF GND Ground for LNA, mixer, IF summation, and PA driver circuits

22 IF_OUT- OUT Downconverter output, requires external load and RFC

23 IF_OUT+ OUT Downconverter output, requires external load and RFC

24 GND_PADDLE GND Ground for substrate and package paddle

25 VCC_RF VCC Power supply for mixer, summation, and PA ramp circuits

26 GND_RF GND Ground for LNA, mixer, IF summation, and PA driver circuits

27 VCC_LNA VCC Power supply for LNA

28 GND_RF GND Ground for LNA, mixer, IF summation, and PA driver circuits

29 RF_IN IN LNA input, AC couple

30 LNA_DEGEN I/O LNA degeneration, connect to ground

31 LNA_DEGEN I/O LNA degeneration, connect to ground

32 DRIVE OUT Power amplifier driver output, requires external load and RFC

33 VCC_PA VCC Power supply for power amplifier driver

34 GND_RF GND Ground for LNA, mixer, IF summation, and PA driver circuits

35 RAMP_CAP I/O PA ramp circuit timing capacitor connection

36 PA_ON IN PA ramp circuit control input:

PA on = logic high, PA off = logic low

37 STDBYB IN Power down control input:

active= logic high, standby = logic low

38 TX/RXB IN Transmit/Receive control input:

transmit = logic high, receive = logic low

39 GND_LO GND Ground for LO buffer, phaseshifter, and standby circuitry

40 LO_IN IN Local oscillator input, AC couple

41 VCC_LO VCC Power supply for LO buffer, phaseshifter, and standby circuitry

42 DATA_IN+ IN Data comparator input

43 DATA_IN- IN Data comparator input

44 BUFFER_OUT- OUT x2 buffer output

45 BUFFER_OUT+ OUT x2 buffer output

46 CLAMP - I/O Data clamp, knee voltage set by pin 7, AC couple

47 CLAMP + I/O Data clamp, knee voltage set by pin 7, AC couple

48 GND_PADDLE GND Ground for substrate and package paddle

3

Loading...

Loading...