MITEL WL102TP1R, WL102PR1R, WL102PR, WL102IG, WL102BC Datasheet

...

Features

● Complete CMOS, single chip, radio transceiver

controller

● Hardware implemented Communication Control

Block (CCB)

● Protocol independent design using external flash

memory

● Internal 8051 and external processor options

● Internal/external buffer and processor RAM

● Block power down facility

● PCMCIA/8bit processor host interface to buffer

RAM

● Up to 1Mbps/2 level or 2 Mbps/4 level operation

Ordering Information

WL102B/IG/TP1R 100 pin package

WL102BC/PR/FP1R 144 pin package

The WL102B is a highly integrated CMOS wireless data

controller designed to dramatically reduce the cost of

radio data applications. It works with the WL600C RF IF

chip and WL800 synthesiser chip to offer a complete

solution for a frequency hopping, spread spectrum radio

in the 2.4 to 2.45GHz ISM band.

Its flexible design means that it can also be used in a

wide range of other applications using a range of "processor", protocols and additional memory options as well

as radios at other frequencies.

Related Documents

WL600C, WL800 and WL102B (DS4837) Datasheets

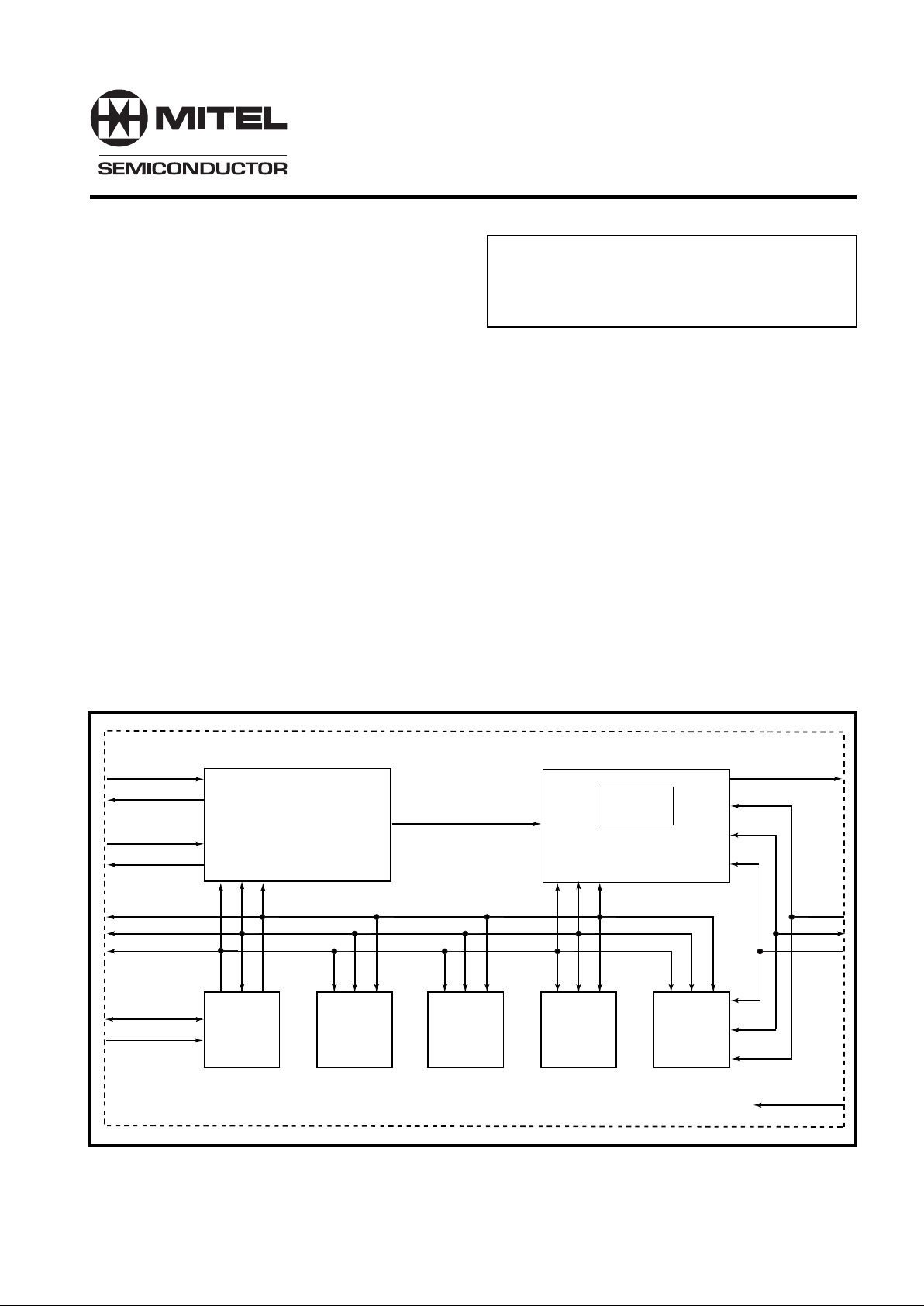

Communications

Control Block

Receive

Transmit

Status

Control

Address

Data

Control

Port Pins

Interrupt

Buffer RAM

6K4

8051

System RAM

4K

Counters

Power Down

Control

Attribute

Memory

Configuration

Control

Data

Address

Memory Control Block

Interrupt

DMA

WL102

Figure 1 WL102 Minimum configuration block diagram

WL102B

Wireless Data Controller

Advance Information

DS4582 - 3.0 July 1999

2

WL102 Advance Information

HRDY

HD1

HD0

HA1

HREGB

HA2

HA3

HWAITB

HA4

HRESET

HA5

HA6

HA7

HA0

HWRB

HWEB

HRDB

HVdd

HGnd

HOEB

HCEB

HD7

HD6

HD5

HD4

CCAB

SYSCLK

SYSCLK_GND

AGnd

AVdd

RXD_L

RXD_LB

RXD_H

RXD_HB

THREEV

SWAKEUP / EPTCNT2

EPRDYB

ENIBRAMB

SPSENB

SRDB

SA10

CCEB

SD7

SD6

SD5

SD4

SD3

SD2

P1[5] / EPTCNT1

P1[3] / EPCINTR

HD2

HGnd

TEST0

TEST1

ENI8051B

RSSISTRB

MOD2LEVB

SVdd

SGnd

TXD_L

TXD_H / TXD

SYSCLK_D

RXD_D

P3[1] / EPMINTR

SYSCLK_X

CS_DATA / PWR_LOB

CS_CLK / ANT_SEL

CS_LOADB / LOADB

TX/RXB / RX/TXB

SVdd

SGnd

STDBYB

PA_ON

LCK_DETB

HVdd

132

456

798

101112

131514

161718

192120

222324

25

27

26

28

37

39

38

40

41

42

43

45

44

46

47

48

49

50

757473

29

30

31

33

32

34

35

36

515253545557565859606163626465666769687071

72

100

99

98

97

96

94

95

93

92

91

90

88

89

87

86

85

84

82

83

81

80

79

78

76

77

HD3

SA11

SA9

SA8

SA13

SVdd

SGnd

SA14

SWRB

SA15

SA12

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

SD0

SD1

SVdd

SGnd

P3[0] / EPSYSINC

EPRSTB

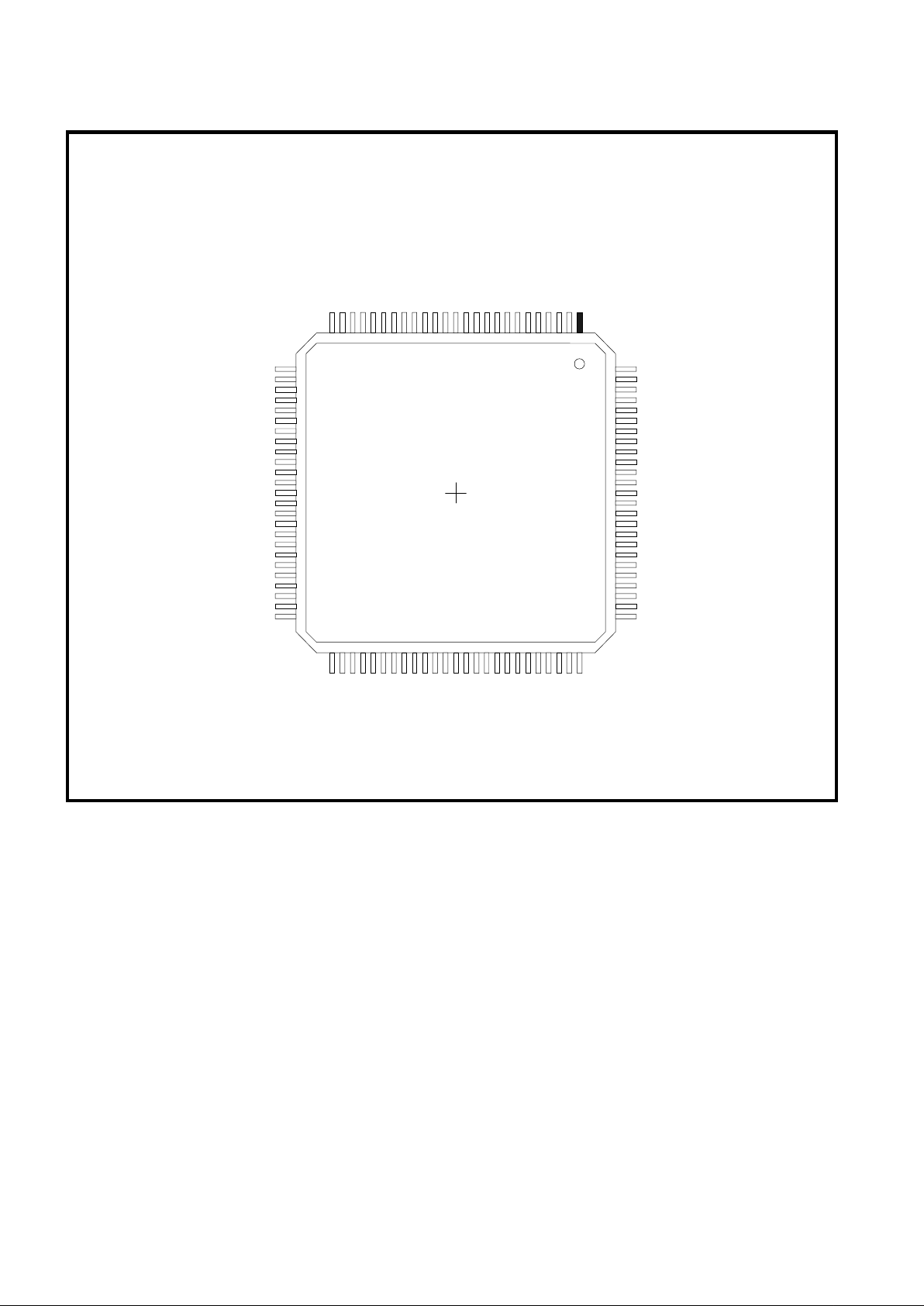

Fig.ure 2 100 Pin package

3

Advance Information WL102

HRDY

HD1

HD0

HA1

HREGB

n/c

CSD6

HA2

HA3

CSD5

HWAITB

n/c

HA4

HRESET

HA5

CSD4

HA6

HA7

CSD3

HA0

HWRB

CSD2

HWEB

n/c

HRDB

HVdd

n/c

HGnd

CSD1

HOEB

HCEB

CSD0

HD7

HD6

HD5

HD4

HD3

SA11

SA9

SA8

EBA4

SA13

EBA5

SVdd

EBA6

SGnd

n/c

SA14

SWRB

EBD3

SA15

SA12

EBD2

SA7

SA6

EBD1

SA5

SA4

EBD0

SA3

EBA7

SA2

SA1

SA0

EBA8

SD0

SD1

EBA9

SVdd

SGnd

P3[0] / EPSYSINC

EPRSTB

CCAB

SYSCLK

SYSCLK_GND

AGnd

AVdd

EBA15

RXD_L

RXD_LB

RXD_H

RXD_HB

EBA14

THREEV

n/c

SWAKEUP / EPTCNT2

EBA13

EPRDYB

EBCEB

ENIBRAMB

EBWRB

EBRDB

SPSENB

EBA12

SRDB

SA10

CCEB

SD7

n/c

SD6

EBA11

SD5

SD4

EBA10

SD3

SD2

P1[5] / EPTCNT1

P1[3] / EPCINTR

n/c

HD2

HGnd

TEST0

TEST1

ENI8051B

n/c

EBD7

RSSISTRB

MOD2LEVB

EBD6

SVdd

SGnd

EBD5

TXD_L

EBD4

TXD_H / TXD

SYSCLK_D

EBA3

RXD_D

P3[1] / EPMINTR

SYSCLK_X

EBA2

CS_DATA / PWR_LOB

CS_CLK / ANT_SEL

EBA1

CS_LOADB / LOADB

n/c

TX/RXB / RX/TXB

SVdd

EBA0

SGnd

STDBYB

PA_ON

LCK_DETB

HVdd

132

456

798

101112

131514

161718

192120

222324

252726

282930

313332

343536

37

39

38

40

41

42

43

45

44

46

47

48

49

51

50

52

53

54

55

57

56

58

59

60

61

63

62

64

65

66

67

69

68

70

71

72

100

101

102

103

104

105

106

107

108

144

142

143

141

140

139

138

136

137

135

134

133

132

130

131

129

128

127

126

124

125

123

122

121

120

118

119

117

116

115

114

112

113

111

110

109

999897

969495

93

9291908889

878685

848283

818079

787677

757473

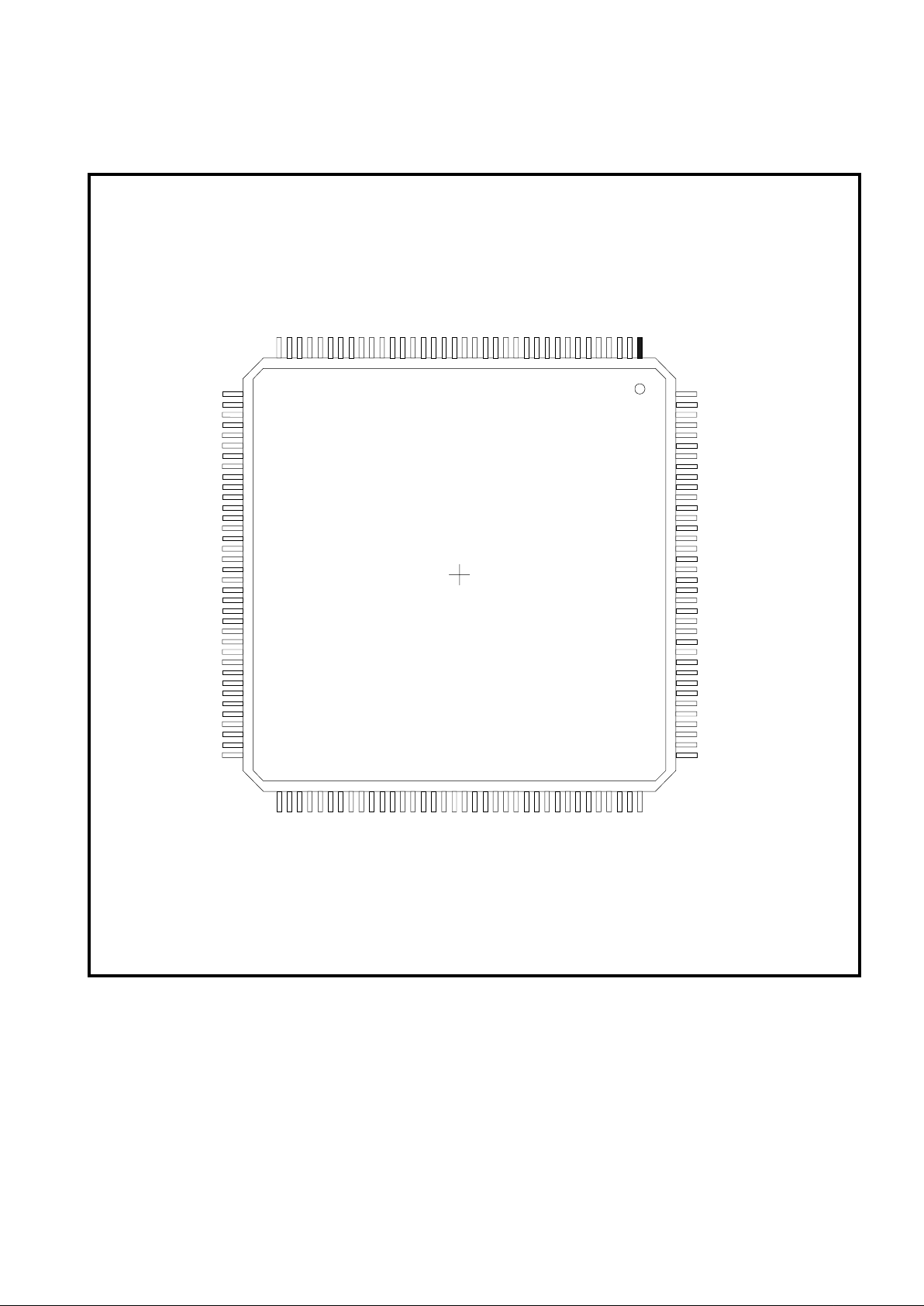

Figure 3 144 Pin package

Loading...

Loading...