MITEL SP8853A, SP8853B, SP8853HC Datasheet

SP8853A/B

1·3GHz Professional Synthesiser

The SP8853 is a low power single chip synthesiser

intended for professional radio applications, containing all the

elements (apart from the loop amplifier) required to build a PLL

frequency synthesis loop

The device is serially programmable by a three-wire data

highway and contains three independent buffers to store one

reference divider word and two local oscillator divider words.

A digital phase detector with two charge pumps,

programmable in phase and gain, are provided to improve

lock-up performance. The preset operation of the charge

pumps can be overwritten or the comparison frequencies

switched to output ports under control of the divider word. The

dual modulus ratio and so operating range is also

programmable through the same word.

A power down mode is incorporated as a battery economy

feature.

The SP8853 is specified at 1·3GHz at 255°C to1125°C (A

grade) and 240°C to185°C (B grade).

Supersedes March 1997 version, DS2352 - 3.0 DS2352 - 4.0 March 1998

FEATURES

■ Improved Digital Phase Detector Eliminates

‘Dead Band’ Effects

■ Low Operating Power, Typically 175mW

■ 1·3GHz Operating Frequency

■ Complete Phase Locked Loop

■ High Input Sensitivity

■ Programmed throughThree-Wire Bus

■ Wide Range of Reference Division Ratios

■ Local Storage for Two Frequency Words, giving

Rapid Frequency Toggling

■ Programmable Phase Detector Gain

■ Power Down Mode

ABSOLUTE MAXIMUM RATINGS

Supply voltage

Storage temperature

Prescaler input voltage

20·3V to 17V

255°C to 1150°C

2·5V p-p

Fig. 1 Pin identification diagram (top view)

ORDERING INFORMATION

SP8853/A/HC Military temperature range

SP8853/B/HC Industrial temperature range

4321282726

12 13 14 15 16 17 18

5

6

7

8

9

10

11

25

24

23

22

21

20

19

PD2 OUTPUT

RPD

V

CC

3

GROUND

XTAL 1

XTAL2

V

EE

2

F

REF

*

POWER DOWN

V

EE

4

V

CC

4

V

CC

1

RF INPUT

RF INPUT

F

PD

*

PD1 OUTPUT

V

EE

3

ICCdLOCK DETECT

NC

V

EE

1

F1/F2

DATA

CLOCK

ENABLE

NC

V

CC

2

SP8853

HC28

*FPD and F

REF

outputs are reversed by the phase

detector sense bit in the F1/F2 programming word. The

above diagram is correct when the sense bit is low. See

Table 2 and Fig. 7.

V

CC

1, VEE1 – preamplifier and prescaler supplies

VCC2, VEE2 – oscillator supplies

V

CC

3, VEE3 – charge pump 2 supplies

VCC4, VEE4 – ECL supplies

2

SP8853A/B

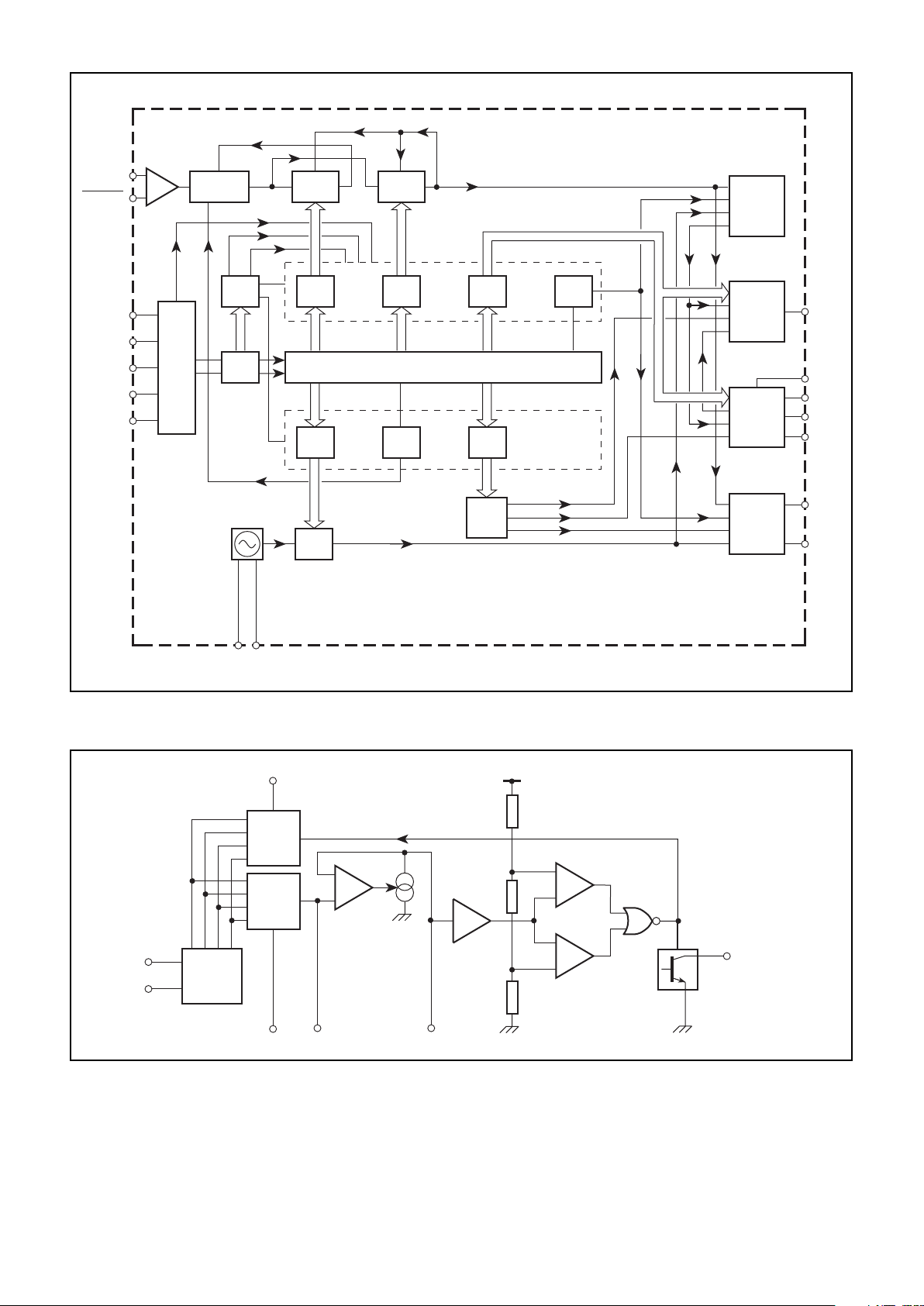

Fig. 2 SP8853 block diagram

Fig. 3 Detailed block diagram of lock detect circuit

f

PD

11

15 BIT

M COUNT

1LOGIC

4 BIT

A COUNT

1LOGIC

2 BIT 1 BIT

DUAL

F1/F2

DATA

BUFFER

N0 N3 N4 N18 N19 N20 N21

22 BIT SHIFT REGISTER

1 BIT13 BIT 2 BIT

N0 N12 N14 N15N13

SINGLE

REFERENCE

BUFFER

LOGIC

2-BIT

SR

DATA

INPUT

16/17 OR 8/9

CONTROL

f

REF

PHASE

DETECTOR

LOGIC

R

COUNT

OUTPUT

INTERFACE

CHARGE

PUMP 1

CHARGE

PUMP 2

PD1

3

LOCK

DETECT

RF INPUT

10

F1/F2

DATA

CLOCK

ENABLE

POWER

DOWN

13

14

15

16

6

PD2

25

27

Cd

28

RPD

24

20

21

CRYSTAL

F

REF

*

5

4

FPD*

*

F

REF

and FPD outputs are reversed by the phase detector

sense bit in the F1/F2 programming word. The pin allocations

shown are correct when the sense bit is low (see Table 2 and Fig. 7).

RF INPUT

REFERENCE

DIVIDER

−

+

V

CC

PHASE

DETECTOR

f

PD

f

REF

CHARGE

PUMP 2

TRANSCONDUCTANCE

AMPLIFIER

31

CHARGE

PUMP 1

−

+

−

+

31

31 BUFFER

10k

45k

45k

DUAL VOLTAGE

COMPARATOR

PD1

3

CHARGE PUMP 1 DISABLE

(SEE TABLE 4)

RPD

24

PD2

25

Cd

28

LOCK DETECT

27

Output current at pin 27 is proportional to

voltage difference between pins 25 and 28,

I

MAX

= 625µA

3

SP8853A/B

tS1t

CH

2V

t

S

t

CH

t

CL

t

REP

2V

2V

t

E

LAST DATA BITFIRST DATA BIT

DATA

CLOCK

ENABLE

t

REP

= 1µs min., t

S

= 50ns min., tCH = 50ns min., tCL = 100ns min., tE = 50ns min.

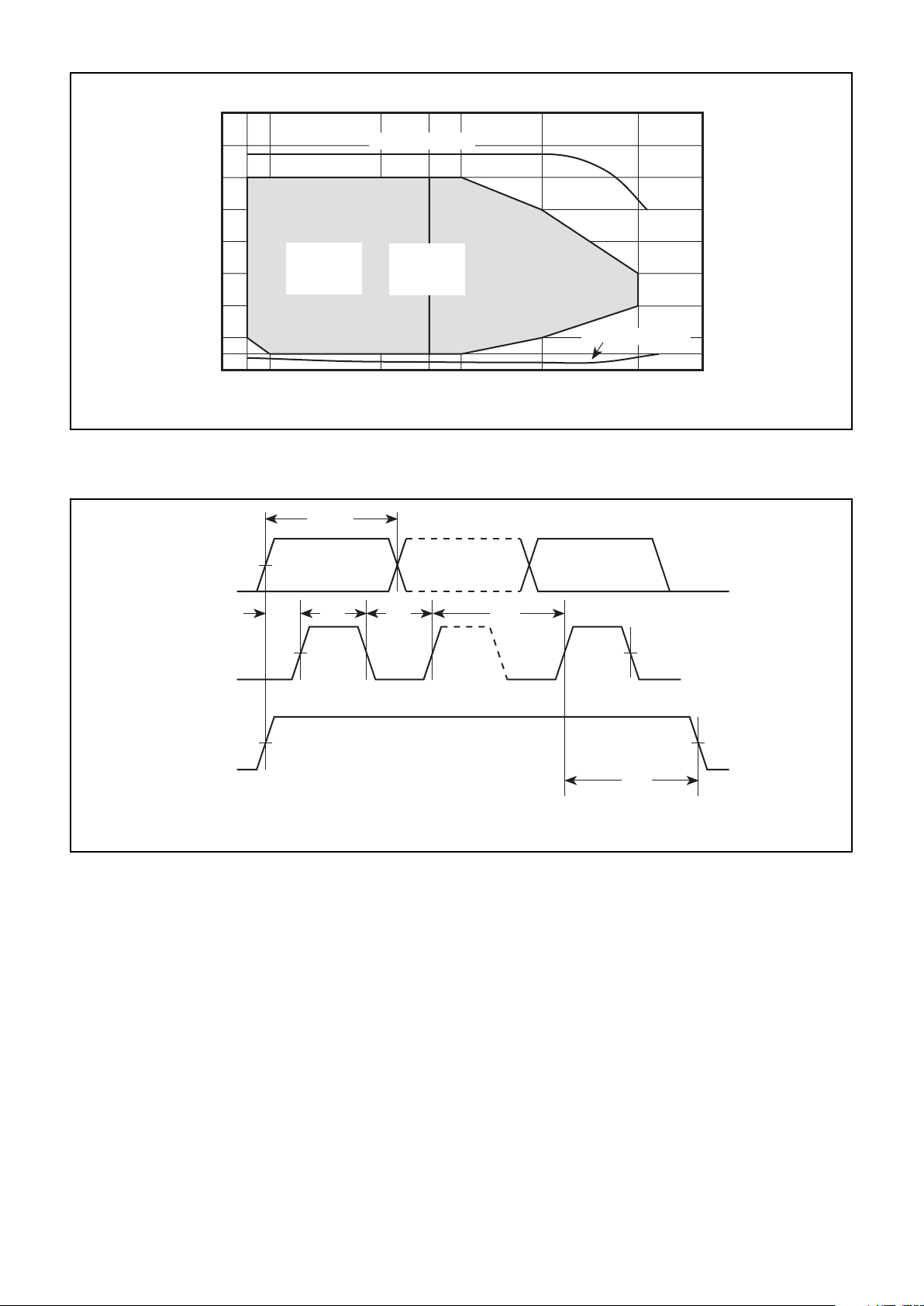

FREQUENCY (MHz)

400

350

300

250

200

150

100

50

0

0

INPUT VOLTAGE (mV RMS)

25

500

650 750

1000 1300 150015080

GUARANTEED

OPERATING

WINDOW

4

16/17 MODE

GUARANTEED

OPERATING

WINDOW

4

8/9 MODE

TYPICAL OVERLOAD

TYPICAL SENSITIVITY

Fig. 4 Typical input characteristics and input drive requirements for SP8853 A and B

Fig. 5 Data and clock timing requirements

4

SP8853A/B

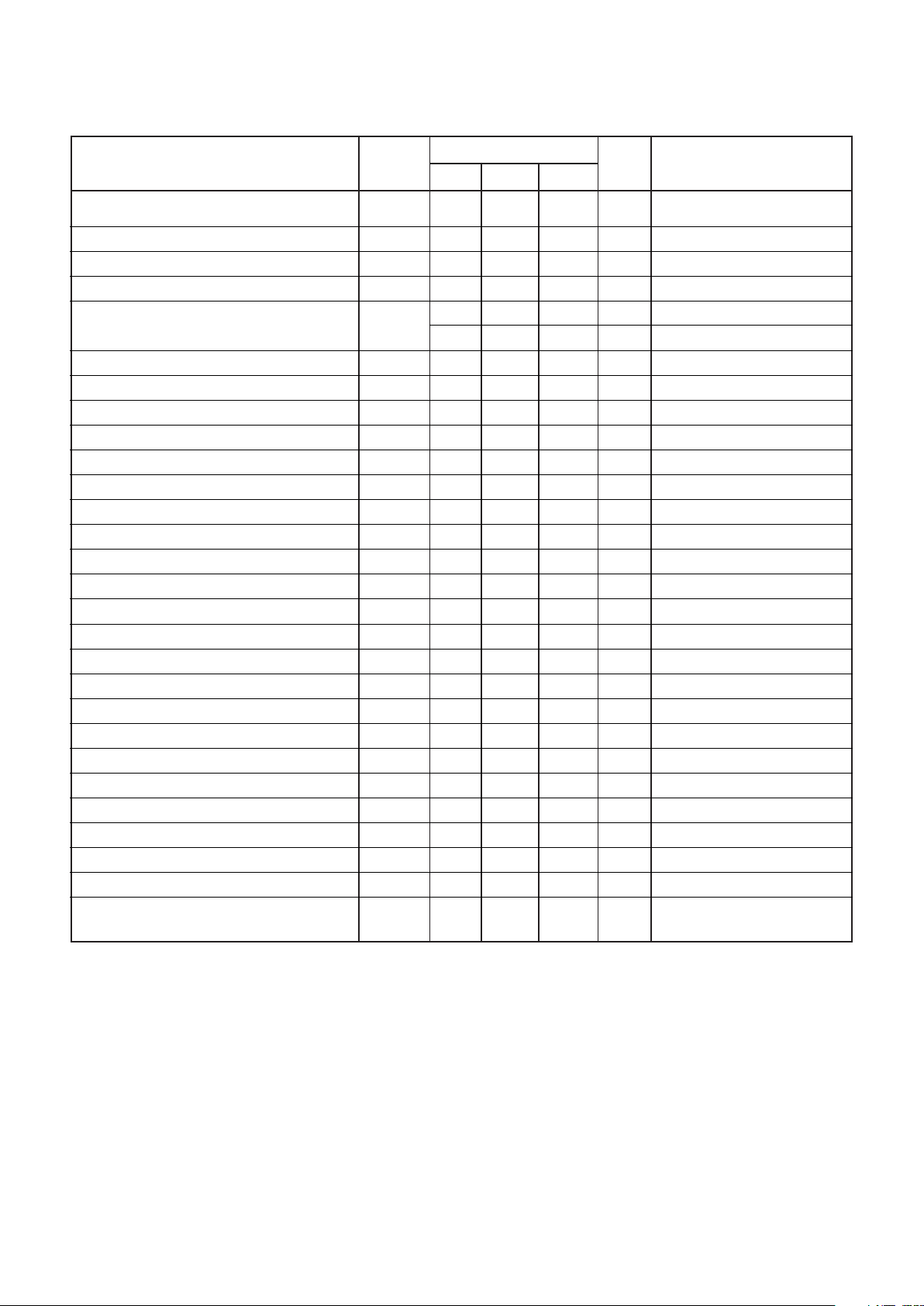

ELECTRICAL CHARACTERISTICS

These characteristics are guaranteed over the following range of operating conditions unless otherwise stated:

Supply voltage VCC = 14·75V to 15·25V. T

AMB

= 255°C to 1125°C (A Grade), 240°C to 185°C (B Grade)

Characteristic Conditions

Supply current

Supply current in power down mode

Input sensitivity

Input overload

RF input division ratio

Comparison frequency

Reference oscillator input frequency

External reference input voltage

Reference division ratio

Data clock repetition rate, t

REP

Minimum setup time, t

S

DATA input high

DATA input low

CLOCK input high

CLOCK input low

Data ENABLE high

Data ENABLE low

F1/F2 input high

F1/F2 input low

POWER DOWN input high

POWER DOWN input low

F1/F2 input current

POWER DOWN input current

RDP external resistance

LOCK DETECT output voltage when in lock

LOCKDETECT switching voltage high

LOCK DETECT switching voltage low

F

PD

and F

REF

output voltage swing

256

56

4

10

1

50

0·6V

CC

V

EE

0·6V

CC

V

EE

0·6V

CC

V

EE

0·6V

CC

V

EE

0·6V

CC

V

EE

68

2·7

40

7·5

524287

262143

5

20

500

8191

1

V

CC

0·3V

CC

V

CC

0·3V

CC

V

CC

0·3V

CC

V

CC

0·3V

CC

0·9V

CC

0·3V

CC

5

5

330

1

2·3

33

4·5

0·9

Pin

8,9,18,23

8

10,11

10,11

10,11,4

4,5

20,21

20

20,5

15

14,15

14

14

15

15

16

16

13

13

6

6

13

6

24

27

25

25

Typ. Max.

Min.

mA

mA

MHz

MHz

mVrms

µs

ns

V

V

V

V

V

V

V

V

V

V

µA

µA

kΩ

V

V

V

V

Units

Value

See Fig. 4

See Fig. 4

With 416/17 selected

With 48/9 selected

See Fig. 5

See Fig. 5

F1 buffer selected

F2 buffer selected

V pin 13 = 5·0V

V pin 6 = 4·5V

I pin 27 = 1mA

V

CC

= 5V

V

CC

= 5V

V

CC

= 5V, external pulldown

may be required

5

SP8853A/B

DESCRIPTION

Prescaler and AM Counter

The programmable divider chain is of AM counter design

and therefore contains a dual modulus front end prescaler, an

A

counter which controls the dual modulus ratio and an

M

counter which controls the bulk multi-modulus division.

A programmable divider of this type has a division ratio of

MN1A

and a minimum integer steppable division ratio

of N(N21).

In the SP8853, the dual modulus front end prescaler is a

dual

N

ratio device, capable of being statically switched

between 416/17 and 48/9 ratios. The controlling A counter is

of four-bit design, allowing a maximum count sequence of 15

(2

4

21), which begins with the start of the M counter sequence

and stops when it has counted by the pre-loaded number of

cycles. While the A counter is counting, the dual modulus

prescaler is held in the

N

11 mode then reverts to the N mode

at the completion of the sequence.

The

M

counter is a 15-bit asynchronous divider which

counts with a ratio set by a control word. In both A and

M

counters the controlling data from the F1/F2 buffer is loaded

in sequence with every

M

count cycle. The N ratio of the dual

modulus prescaler is selected by a one-bit word in the

reference divider buffer and, when when a ratio of 48/9 is

selected, the A counter requires only three programming bits,

having an impact on the frequency bit allocation as described

in the data entry section.

Reference Source and Divider

The reference source in the SP8853 is obtained from an

on-chip oscillator which is frequency controlled by an external

crystal. The oscillator can also function as a buffer amplifier to

allow the use of an external reference source. In this mode, the

source is simply AC-coupled into the oscillator transistor base

on pin 20.

The oscillator output is coupled to a programmable reference

counter (

R

) whose output is the reference for the phase

detector. The reference divider is a fully programmable 13-bit

asynchronous design and can be set to any division ratio

between 1 and 8191. The actual division ratio is controlled by

a data word stored in the internal reference buffer.

Phase Detector

The SP8853 contains a digital phase detector which feeds

two charge pump circuits. Charge pump 1 has preset currents

which are programmble as shown in Table 1. Charge pump 2

has a current level set by an external resistor RPD; the current

is multiplied by a factor which is determined by bits G1 and G2

of the F1 or F2 word (see Table 1). Note that charge pump 2

current is pin 24 current 3 muliplication factor, where

I pin 24 =

A lock detect circuit is connected to the output of charge

pump 2. when the voltage level at pin 25 is between

approximately 2·25V and 2·75V, LOCK DETECT (pin 27) will

be low and charge pump 1 disabled, depending on the PD1

and PD2 programming bits as shown in Table 4.

The output signals from the

R

and M counters are available

on pins 4 and 5 (FPD and F

REF

) when programmed by the

reference programming word; the various options are shown

in Table 4. An external phase detector may be connected to

pins 4 and 5 and may be used independently or in conjunction

with the on-chip phase detector.

To allow for control direction changes introduced by the

design of the control loop, a control bit in the F1/F2 programming

word interchanges the inputs to the on-chip phase detector

and reverses the functions on pins 4 and 5 (see Table 2).

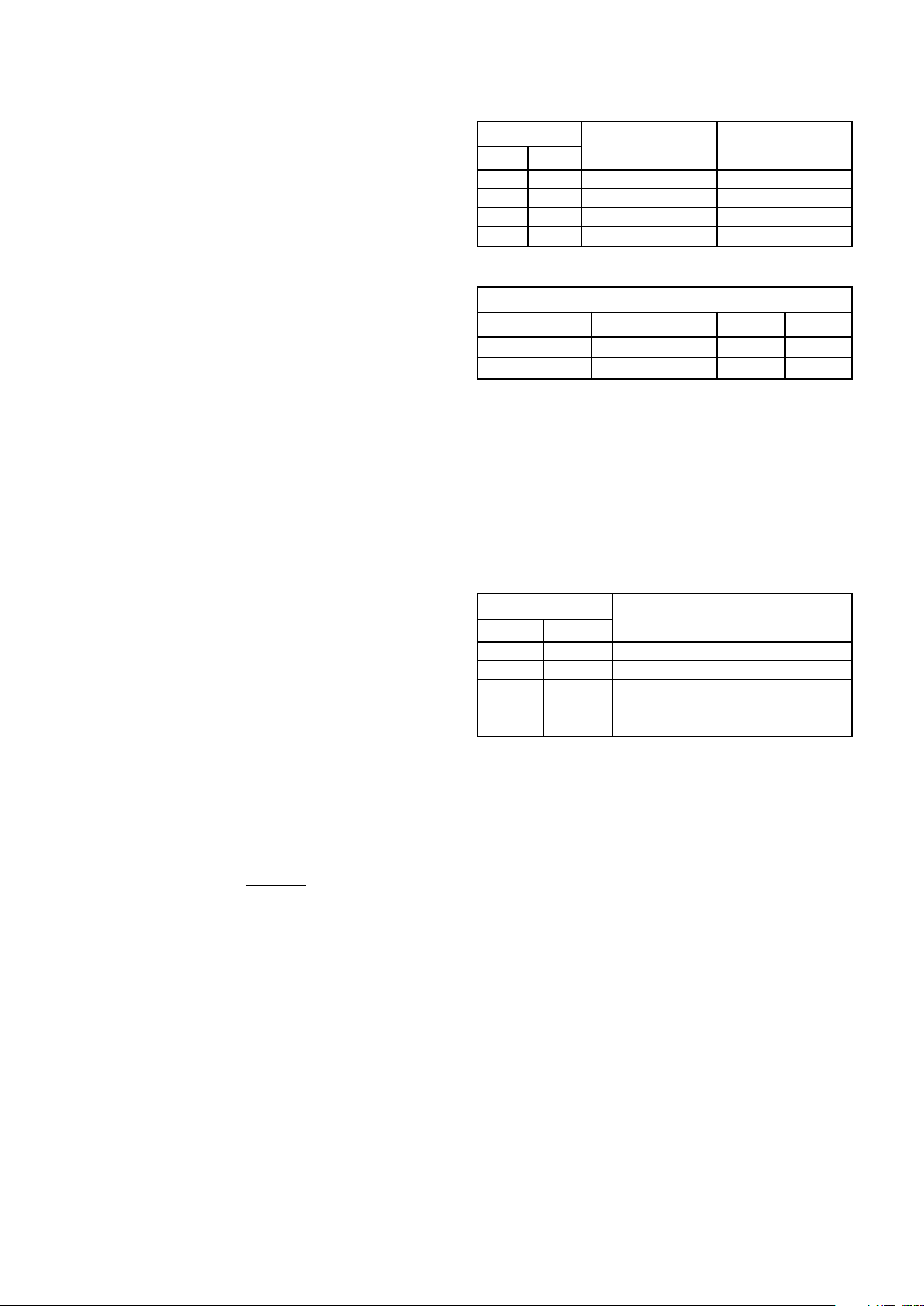

V

CC

21·5V

RPD

F1 or F2 word

G2 G1

Charge pump 1

current (

µA)

Charge pump 2

multiplier

0

1

Current source

Current sink

F

PD

F

REF

F1/F2 sense bit Pins 3 and 25 Pin 4

Output for RF phase lag

F

REF

F

PD

Pin 5

0

1

0

1

0

0

1

1

50

75

125

200

1

1·5

2·5

4

Table 1 Charge pump currents

Table 2

Data Entry and Storage

The data section of the SP8853 consists of a data input

interface, a data shift register and three data buffers.

Data is entered to the data input interface via a three-wire

highway, with DATA (pin 24), CLOCK (pin 15) and ENABLE

(pin16) inputs. The input interface routes the data into a 24bit shift register with bus connections to three data buffers.

Data entered via the serial bus is transferred to the appropriate

data buffer on the negative transition of the data enable input

according to the two final data bits C1 and C2 as shown in

Table 3. The MSB of the data is entered first.

2-bit SR contents

C2 C1

0

1

0

1

F1

F2

Transfer A counter bits (N0:N3)

into 4-bit buffer (see Figs. 2 and 7)

Reference

0

0

1

1

Buffer loaded

Table 3

The dual F1/F2 buffer can receive two 22-bit words and

controls the programmable divider A and M counters using 19

bits, the phase detector gain with two bits and the phase

detector sense with one bit. A fourth input from the synthesiser

control system selects the active buffer.

The third buffer contains only 16 bits, 13 being used to set

the reference divider division ratio and 2 to control the phase

detector enable logic. The remaining bit sets the dual modulus

prescaler

N

ratio.

The data words may be entered in any individual multiple

sequence and the shift register can be updated whils the data

buffers retain control of the synthesiser with the previously

loaded data. This enables four unique data words to be stored

in the device, with three in the data buffers and a fourth in the

shift register, while the chip is enabled. The F1 word may also

be updated while F2 is controlling the programmable divider

and vice-versa.

The dual F1/F2 buffer enables allows the device to be

toggled between two frequencies using the F1/F2 select input

at a rate determined by the comparison frequency and also

permits random frequency hopping at a rate determined by a

btye load period; this is possible because the loop can be

locked to F1 while F2 is updated by entering new data via the

shift register. The F1/F2 input is high to select F1.

Loading...

Loading...