MITEL SL1711, SL1711B, SL1711KG, SL1711MH1P, SL1711MH1Q Datasheet

...

The SL1711 is a quadrature downconverter, intended

primarily for application in professional and consumer digital

satellite tuners.

The device contains all elements necessary, with the

exception of external local oscillator tank to form a complete

system operating at standard satellite receiver intermediate

frequencies. It is intended for use with external carrier

recovery.

The device includes a low noise RF input amplifier, a

reference VCO with prescaler output buffer and In-phase and

Quadrature mixers with baseband buffer amplifiers containing

AGC gain control.

The SL1711 is optimised to drive a dual ADC converter

such as the VP216.

The SL1711 utilises a power MP package, whereas the

SL1711B variant uses a standard MP16 plastic package and

features a revised operating temperature.

FEATURES

■ Single chip system for wideband quadrature

downconversion

■ Compatible with all standard high IF frequencies

■ Excellent gain and phase match up to 30MHz

baseband

■ High output referred linearity for low distortion and

multi channel application

■ Simple low component application

■ Fully balanced low radiation design with fully

integrated quadrature generation

■ High operating input sensitivity

■ On-board AGC facility

■ On chip oscillator for varactor tuning or SAW

resonator operation

■ ESD protection (Normal ESD handling procedures

should be observed)

MH16

SL1711

116

VCCC

AGC

IOUT

VEEA

IFINB

IFIN

IVCCA

QOUT

VEEC

VCCB

VCODIS

VCO B

VCO A

VEEB

PSCAL

PSCALB

APPLICATIONS

■ Satellite receiver systems

■ Data communications systems

■ Cable systems

ORDERING INFORMATION

SL1711/KG/MH1P (Sticks)

SL1711/KG/MH1Q (Tape and Reel)

SL1711B/KG/MP1S (Sticks)

SL1711B/KG/MP1T (Tape and Reel)

Fig. 1 Pin allocation

MP16

SL1711B

116

VCCC

AGC

IOUT

VEEA

IFINB

IFIN

IVCCA

QOUT

VEEC

VCCB

VCODIS

VCO B

VCO A

VEEB

PSCAL

PSCALB

SL1711

Quadrature Downconverter

Preliminary Information

Supersedes November 1996 version, DS4032 - 1.6 DS4032 - 4.0 October 1997

2

SL1711

QUICK REFERENCE DATA

Characteristic Value Units

Input noise figure, DSB 17 dB

Maximum conversion gain 44 dB

Minimum conversion gain 28 dB

IP32T output referred +8 dBV

Output clip voltage 1.5 Vp-p

Gain match up to 22MHz ± 0.3 dB

Gain match up to 30MHz ± 0.5 dB

Phase match up to 30MHz ± 1.5 deg

Gain flatness up to 30MHz ± 0.5 dB

VCO phase noise, SSB @ 10kHz offset - 96 dBc/Hz

Prescaler division ratio 32

Prescaler output swing 1.6 Vp-p

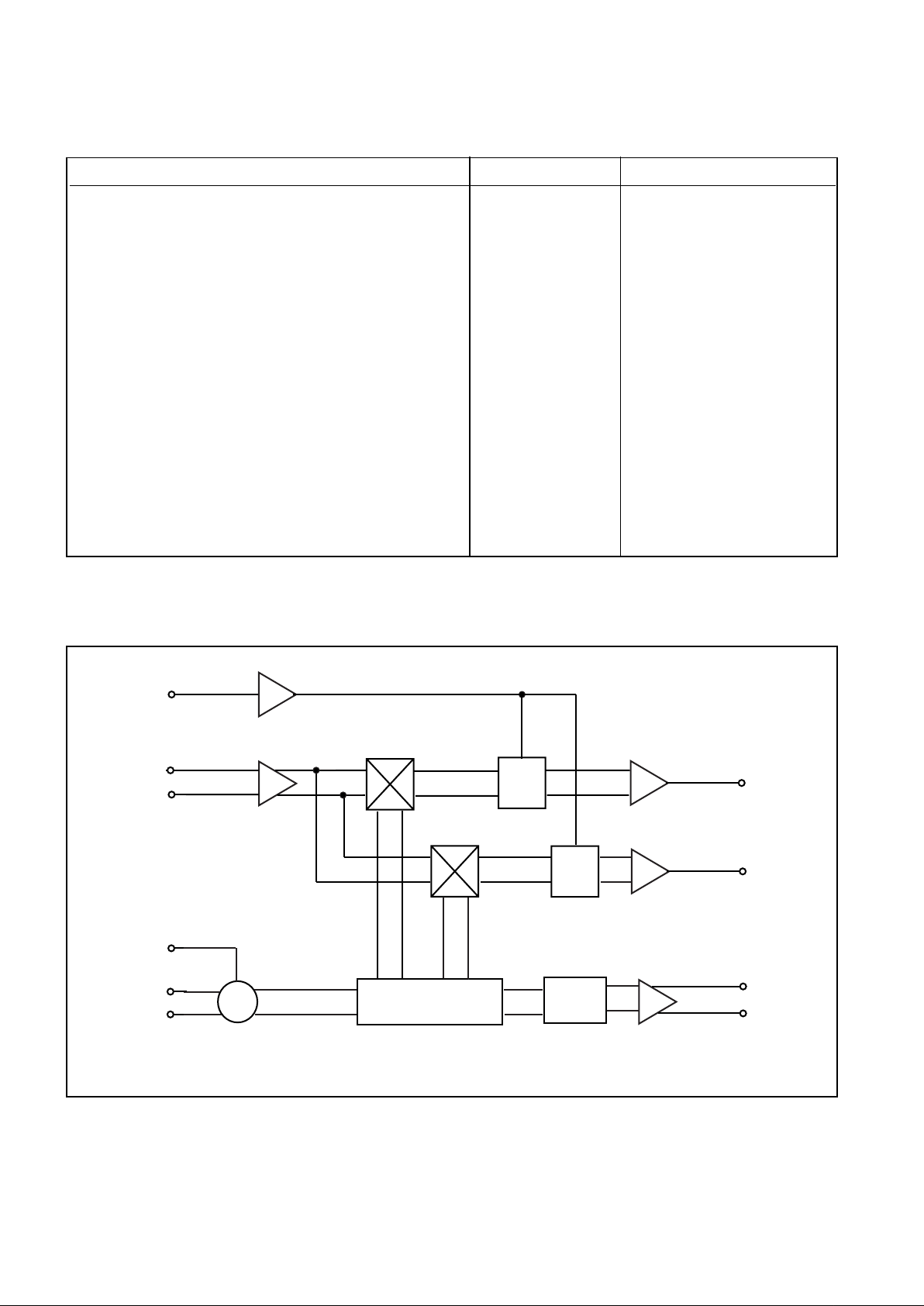

Fig. 2 SL1711 block diagram

AGC

IFIN

VCODIS

VCOA

AGC

AGC

÷32

LO

0 deg 90 deg

Quadrature

generator

PSCALB

PSCAL

Q OUT

I OUT

IFINB

VCOB

3

SL1711

FUNCTIONAL DESCRIPTION

The SL1711 is a wideband quadrature downconverter,

optimised for application in both professional and consumer

digital satellite receiver systems and requiring a minimum

external component count. It contains all the elements

required for construction of a quadrature demodulator, with

the exception of tank circuit for the local oscillator.

A block diagram is shown in Fig. 2.

The SL1711 oscillator can be used with either a varator

tuned tank circuit or with a SAW resonator. Both

configurations are described in the Application Notes section

of this Data Sheet.

A typical digital satellite tuner application from tuner input

to data transport stream is shown in Fig. 13

In normal application the second satellite IF frequency of

typically 402.75 or 479.5 MHz is fed from the tuner SAW filter

to the RF preamplifier, which is optimised for impedance

match and signal handling. The amplifier output signal is then

split into two balanced channels to drive the In-phase and

Quadrature mixers. The typical RF input impedance is shown

in Fig. 3

In-phase and Quadrature LO signals for the mixers are

derived from the on board local oscillator, which uses an

external varactor tuned resonant network and is optimised for

low phase noise. The VCO also drives an on board divide by

32 prescaler whose outputs can be used for driving an external

PLL control loop for the VCO, where the PLL loop is contained

within the QPSK demodulator, for example the VP305. For

optimum performance in the varactor tuned application the

VCO should be fully symmetric. The VCO has a disable facility

by grounding pin 15, VCODIS; in normal applications this pin

is pulled to Vcc via a 4K7 resistor.

The mixer outputs are fed to balanced baseband AGC

amplifier stages, which provide for a minimum of 16 dB of AGC

control. The typical AGC characteristic is shown in Fig. 4.

These amplifiers then feed a low output impedance true

differential to single-ended converter output stage. In normal

application the output can be either directly AC coupled to the

ADC converter such as the VP216, which will generally have

a high input impedance, or to drive an anti alias filter. In this

later case the maximum load presented to the SL1711 must

not exceed a parallel combination of 1KΩ and 20pF. The

typical baseband output impedance is contained in Fig. 5.

It is recommended that the device is operated with an

output amplitude of 760mV under lock conditions.

Under transient conditions the output should not exceed

the clipping voltage.

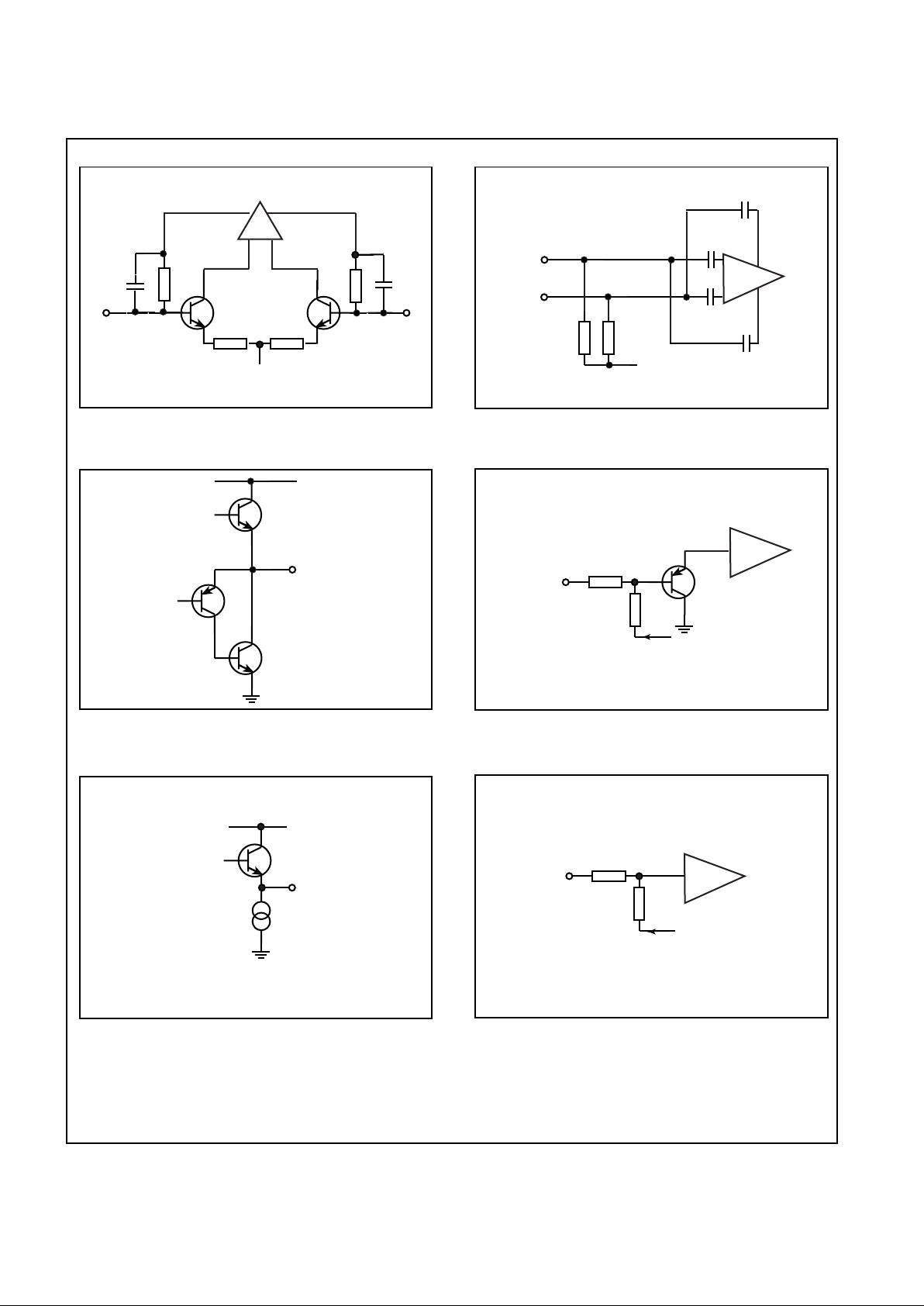

Input and output interface circuitry is contained in Fig. 6.

The typical key performance figures at 480 MHz IF, 5V Vcc,

1 kΩ load and 25 deg C ambient are contained in table headed

'QUICK REFERENCE DATA'. With SAWR oscillator

application the gain and phase match performance will

typically exceed these numbers.

4

SL1711

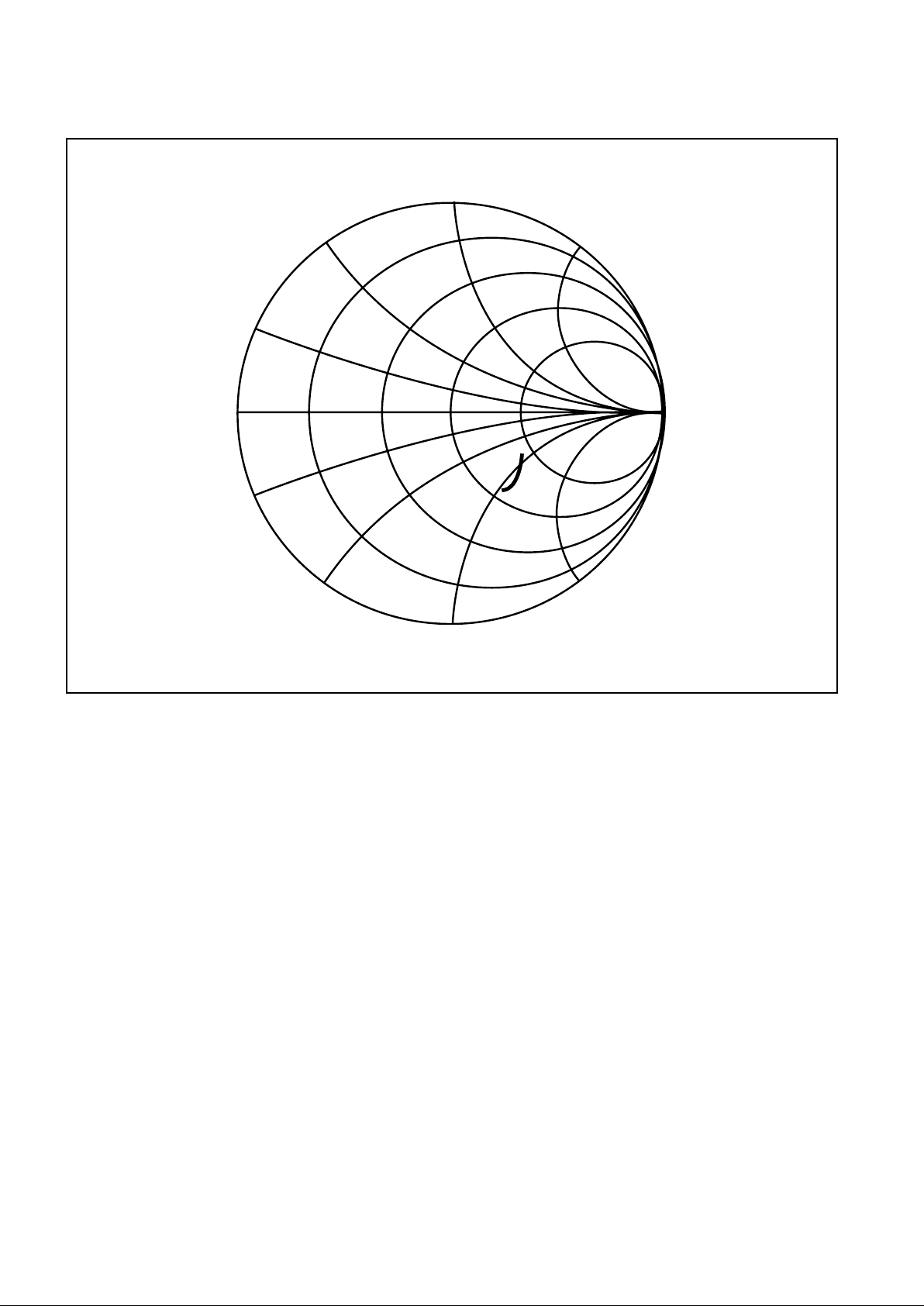

Fig.3 Typical RF input impedance

-j0.2

0

+j0.2

+j0.5

+j1

+j2

-j2

-j1

-j0.5

0.2 0.5

1

START 350 MHz

STOP 650 MHz

Marker 1 480MHz

Zreal = 96Ω

Zimag = 54Ω

X

5

SL1711

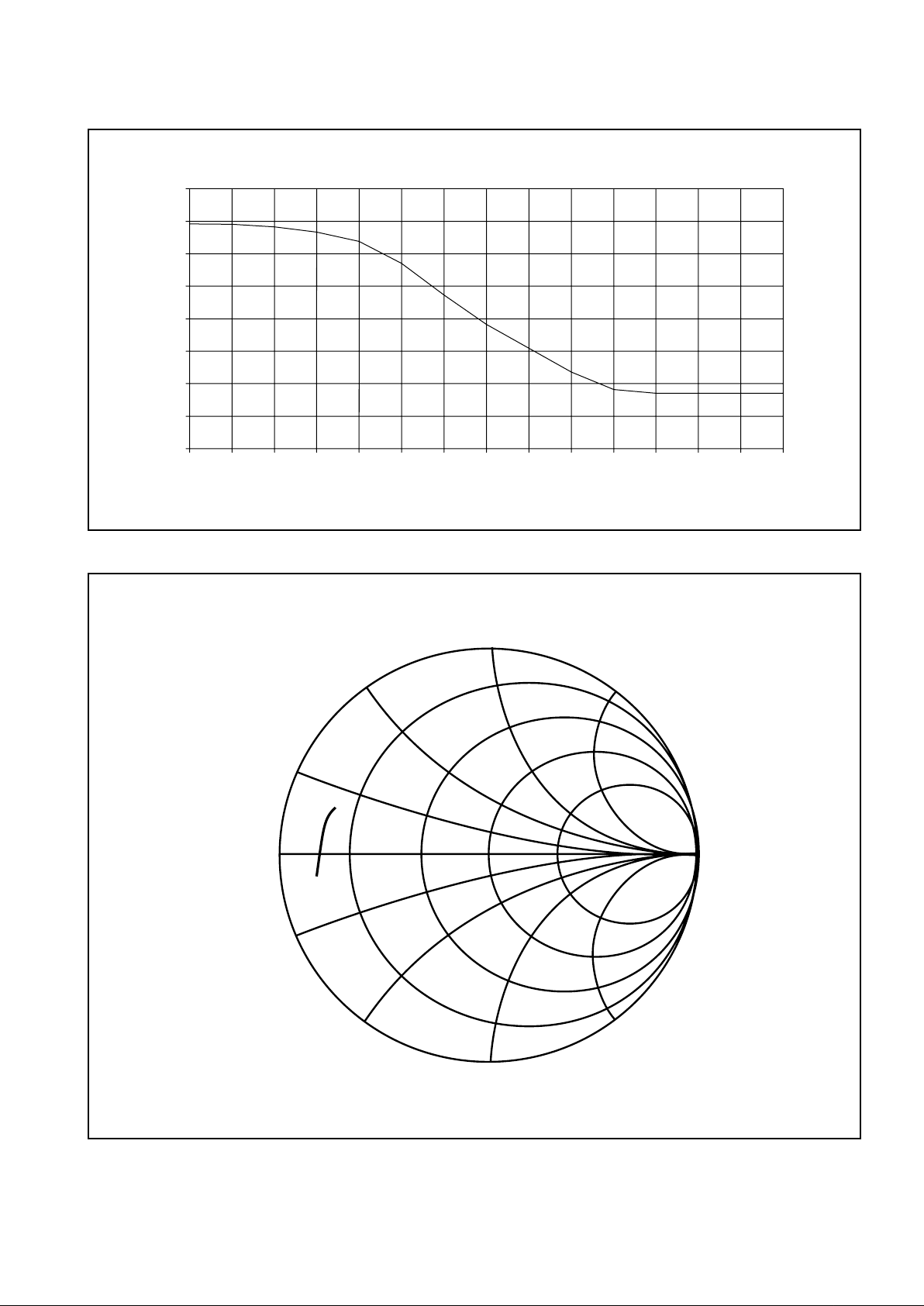

Fig.4 Typical AGC characteristic

Fig. 5 Typical baseband output impedance

-j0.2

0

+j0.2

+j0.5

j1

+j2

-j2

-j1

-j0.5

0.2

0.5

1

X

X

1

2

1 1MHz

2 15MHz

3 30MHz

X

3

CONVERSION GAIN dB

15

20

25

30

35

40

45

50

55

1

1.25

1.5

1.75

2

2.25

2.5

2.75

3

3.25

3.5

3.75

4

4.25

4.5

AGC CONTROL VOLTS

6

SL1711

IF Input

VCO

I & Q baseband output

VCO disable input

Prescaler outputs

AGC input

Fig. 6 I/O port peripheral circuitry

IFINB

IFIN

Vcc

O/P

O/P

Vcc

Vref

AGC

50k

Vref

VCO

VCO

2x20k

VCODIS

55k

Vref

Loading...

Loading...