PDSP16350

1

PDSP16350

I/Q Splitter/NCO

Supersedes version in December 1993 Digital Video & DSP IC Handbook, HB3923-1 DS3711 - 2.3 September 1996

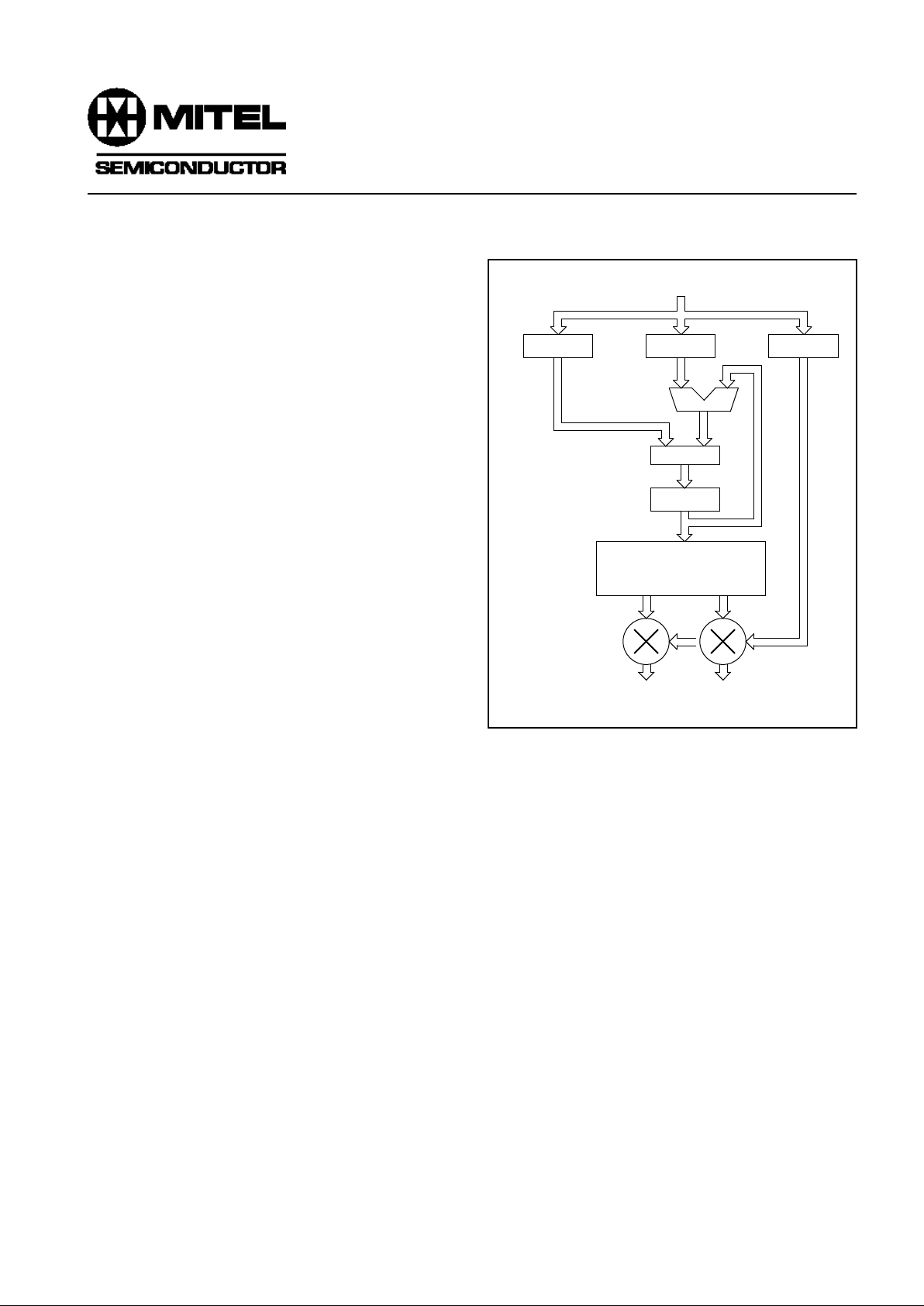

Fig. 1 Block Diagram

CORDIC PROCESSOR ARRAY

SIN COS

DIN

MUX

PHASE ACCUM

REGISTER

ACCUM

SCALING

REGISTER

PHASE OFFSET

REGISTER

PHASE INCR

REGISTER

The PDSP16350 provides an integrated solution to the

need for very accurate, digitised, sine and cosine waveforms.

Both these waveforms are produced simultaneously, with 16

bit amplitude accuracy, and are synthesised using a 34 bit

phase accumulator. The more significant bits of this provide

16 bits of phase accuracy for the sine and cosine look up

tables.

With a 20 MHz system clock, waveforms up to 10 MHz can

be produced, with 0.001 Hz resolution. If frequency modulation is required with no discontinuities, the phase increment

value can be changed linearly on every clock cycle. Alternatively absolute phase jumps can be made to any phase value.

The provision of two output multipliers allows the sine and

cosine waveforms to be amplitude modulated with a 16 bit

value present on the input port. This option can also be used

to generate the in-phase and quadrature components from an

incoming signal. This I/Q split function is required by systems

which employ complex signal processing.

FEATURES

■ Direct Digital Synthesiser producing simultaneous sine

and cosine values

■ 16 bit phase and amplitude accuracy, giving spur levels

down to - 90 dB

■ Synthesised outputs from DC to 10 MHz with accuracies

better than 0.001 Hz

■ Amplitude and Phase modulation modes

■ 84 pin PGA or 132 pin QFP

APPLICATIONS

■ Numerically controlled oscillator (NCO)

■ Quadrature signal generator

■ FM, PM, or AM signal modulator

■ Sweep Oscillator

■ High density signal constellation applications with simul-

taneous amplitude and phase modulation

■ VHF reference for UHF generators

■ Signal demodulator

ASSOCIATED PRODUCTS

PDSP16256/A Programmable FIR Filter

PDSP16510A FFT Processor

PDSP16488A 2D Convolver

PDSP16350

2

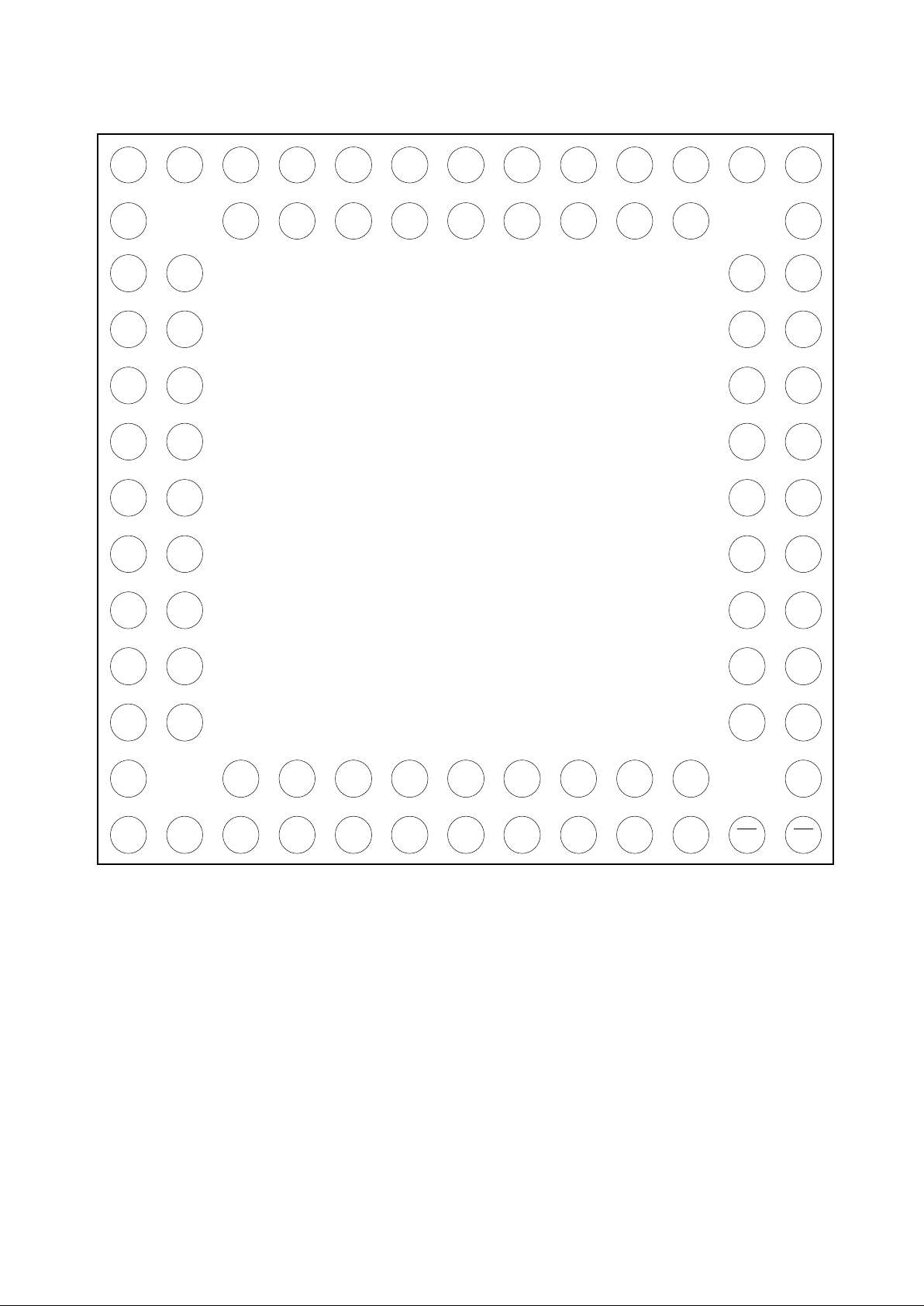

JUMP MODE DIN19 DIN21 DIN23 VDD DIN26 GND DIN28 DIN30 DIN32 VOUT RES

DIN17 DIN18 DIN20 DIN22 DIN24 DIN25 DIN27 DIN29 DIN31 DIN33 VIN

DIN15 DIN16 SIN15 SIN14

DIN13 DIN14 SIN13 SIN12

DIN11 DIN12 SIN11 SIN10

GND DIN10 SIN9 GND

DIN9 DIN8 SIN8 SIN7

VDD DIN7 SIN6 VDD

DIN6 DIN5 SIN4 SIN5

DIN4 DIN3 SIN2 SIN3

DIN2 DIN1 SIN0 SIN1

DIN0 COS15 COS13 COS11 COS9 COS7 COS6 COS4 COS2 COS0 CEN

CLOCK

GND COS14 COS12 COS10 VDD COS8 GND COS5 COS3 COS1 OES OEC

1 2 3 4 5 6 7 8 9 10 11 12 13

A

B

C

D

E

F

G

H

J

K

L

M

N

Fig. 2 A. Pin out - bottom view (84 pin PGA - AC84)

PDSP16350

3

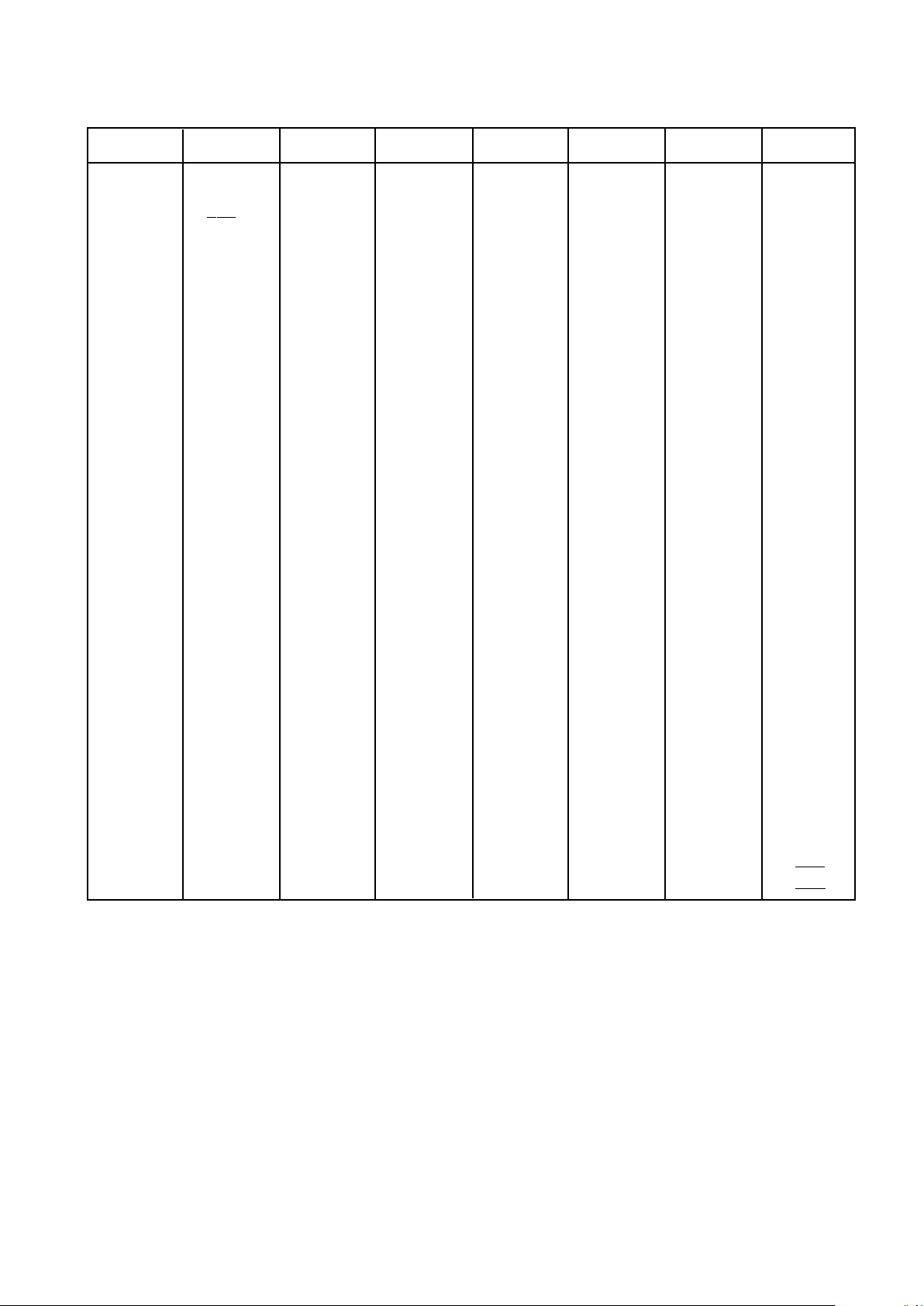

GC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

SIG

N/C

CEN

N/C

SIN0

SIN1

SIN2

GND

VDD

SIN3

SIN4

N/C

SIN5

SIN6

N/C

SIN7

SIN8

VDD

GND

SIN9

N/C

SIN10

SIN11

N/C

SIN12

SIN13

SIN14

VDD

GND

SIN15

VIN

N/C

N/C

RESET

GC

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

SIG

N/C

VOUT

DIN33

GND

VDD

DIN32

N/C

DIN31

DIN30

N/C

DIN29

DIN28

N/C

DIN27

GND

VDD

DIN26

DIN25

DIN24

DIN23

VDD

DIN22

GND

DIN21

VDD

DIN20

DIN19

GND

VDD

DIN18

MODE

JUMP

VDD

GC

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

SIG

GND

DIN17

N/C

DIN16

DIN15

GND

VDD

DIN14

DIN13

DIN12

N/C

DIN11

DIN10

N/C

DIN9

GND

VDD

DIN8

DIN7

DIN6

N/C

DIN5

N/C

DIN4

DIN3

VDD

GND

DIN2

DIN1

N/C

DIN0

N/C

CLK

GC

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

SIG

GND

VDD

GND

N/C

COS15

COS14

N/C

COS13

COS12

N/C

COS11

N/C

COS10

COS9

VDD

GND

COS8

COS7

N/C

COS6

COS5

N/C

COS4

N/C

COS3

COS2

N/C

COS1

VDD

GND

COS0

OES

OEC

Fig.2B Pin out (132 pin ceramic QFP - GC132)

PDSP16350

4

SIGNAL DESCRIPTION

DIN33:0 Data bus for the input register. This input register provides a 34 bit, incremental or absolute, phase

value, if the mode pin is low. Alternatively if the mode pin is high, it provides either an 18 bit phase

increment value, via D17:0, and a 16 bit scale value via D33:18 or a 34 bit phase increment value

depending on the JUMP input see below.

SIN15:0 16 bit sine output data in fractional two’s complement format.

COS15:0 16 bit cosine output data in fractional two’s complement format.

CEN Clock enable for the data input register. When low, data will be latched on the rising edge of the clock.

When high data will be retained in the input register.

MODE Mode control input. When low, data in the input register is interpreted as either a 34 bit phase increment

value or a 34 bit absolute phase value. When high, the output multipliers are enabled and will scale the

waveforms with the upper 16 bits in the input register. The phase increment is loaded from the the lower

18 bits. The full 34 bit phase increment register can also be loaded using JUMP see below.

JUMP With MODE low (Frequency or Phase Modulation)

When low JUMP will allow normal phase incrementing to occur. When high, the data on the input pins

will be interpreted as a 34 bit absolute phase value to replace the present value in the accumulator.

JUMP is internally latched to match the delay through the data input register, and to allow data in the

internal pipeline to be correctly processed. CEN must also be low to latch the required data from DIN.

When Mode is high (Amplitude Modulation)

When low JUMP will allow normal phase incrementing to occur, with the phase increment value taken

from the lower 18 data inputs. When high, the data on the input pins will replace the full 34 bits of the

phase increment register. CEN must also be low to latch the required data.

RES When high will clear the phase accumulator and phase increment registers, after data in the internal

pipeline has been correctly processed.

CLK Input clock.

OES Output enable for SIN 15:0. Outputs are high impedance when OES is high.

OEC Output enable for COS15:0. Outputs are high impedance when OEC is high.

VIN Valid input flag. A delayed version of this input is available on the VOUT pin, with the delay matching

the data processing pipeline delay. This input has no other internal function.

VOUT Valid output flag. See above.

GND Five ground pins. All must be connected.

VCC Four +5V pins. All must be connected.

Table 1. Pin Description

PDSP16350

5

4) DC can be generated since the increment value can be

zero.

5) Frequency stability will match the stability of the incoming

frequency when the increment is fixed.

The residual noise characteristics of an oscillator are very

important in modern communication systems. This parameter

defines how well the device maintains its set frequency for

very short periods (nanoseconds to seconds) of time. Poor

figures will significantly affect the system signal to noise ratio

and limit the dynamic range.

The PDSP16350 will, of course, inherit the residual noise

characteristics of the source of the incoming frequency. The

output frequency is, however, always less than half the

incoming frequency in order to satisfy the Nyquist criterion.

This is in contrast to a phase locked loop synthesiser, when a

small input frequency controls a high output frequency.

The commonly used 20 log N rule states that the phase

noise at the output of a synthesiser will be no better than

twenty times the log of the ratio of the output frequency to the

input frequency. In a phase locked loop synthesiser N is large,

in the PDSP16350 it is less than half. Log N is thus less than

zero and phase noise improvement is obtained.

The output waveforms are produced after a pipeline delay

with respect to the DIN inputs. The effects of the JUMP or RES

commands are delayed such that all data in the internal pipe

will be processed before the discontinuity occurs. New data

may be presented to the device on the cycle following the

JUMP or RES and a valid result will be obtained after 31 clock

cycles.

DEVICE OPERATION

Sine and cosine are simultaneously produced by the

Cordic processor, which is addressed by the upper 16 bits of

the output from a 34 bit phase accumulator. The accumulator

divides the digital phase circle into a number of steps, one step

for each state of the accumulator. When the accumulator

reaches its maximum value it overflows back to zero and the

sequence is repeated.

The accumulator is incremented once per incoming clock

cycle, by an amount which defines the frequency which is to

be generated. The increment required is defined by :

Desired O/P Frequency

Increment = x 2

N

Incoming Clock Frequency

where N is the number of bits in the accumulator. Since the

Nyquist criteria for proper waveform reconstruction must still

be obeyed, the maximum output frequency is half the incoming frequency. In practice, when a return is made to the analog

world, just meeting the minimum Nyquist requirement would

require a ‘brick wall’ low pass filter to remove the alias signals.

A more useful ‘rule of thumb’ is to limit the generated waveforms to less than 40% of the clock frequency.

The resolution, or tuning sensitivity, of the waveform

generator is given by :

Incoming Clock Frequency

Resolution = Hz

2

N

These equations illustrate some very important features of

direct digital synthesisers :-

1) Tuning sensitivity is defined by both the number of bits in

the accumulator and the incoming time base frequency.

2) The oscillator tunes linearly over its entire range.

3) The frequency accuracy matches the accuracy of the

incoming increment value.

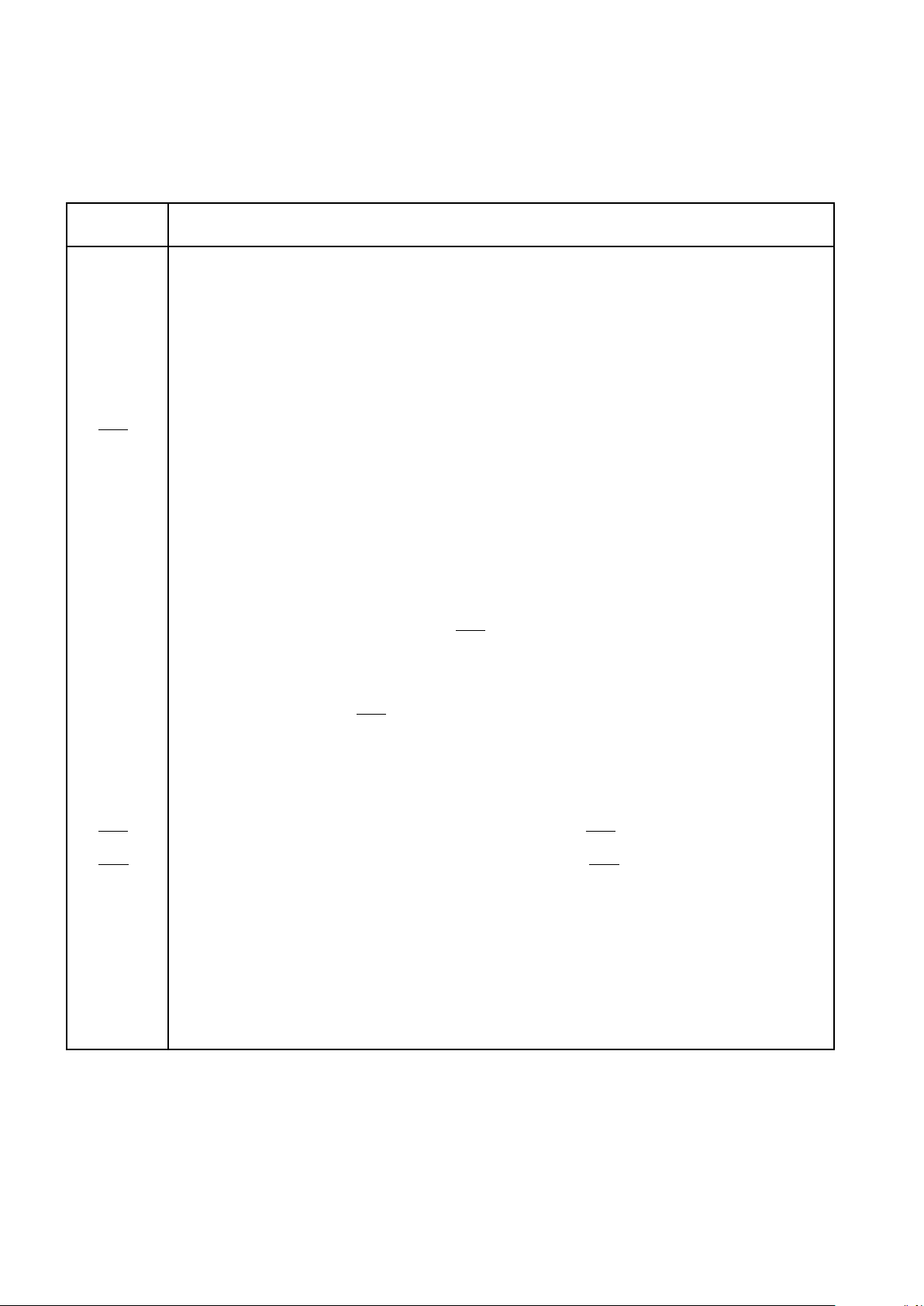

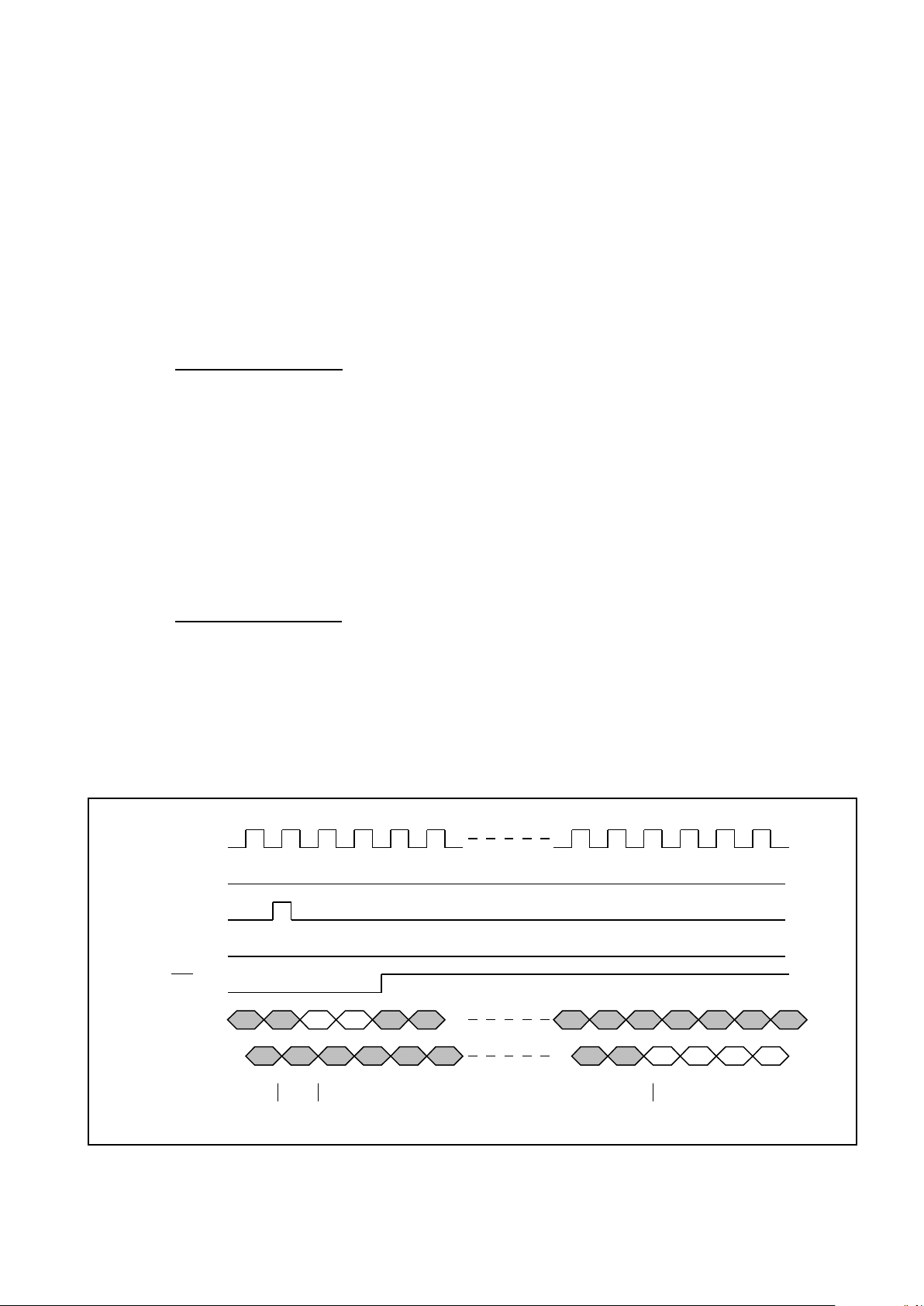

1 2 3 4 5

CLK

RESET

DATA IN

RESULT

30 31 32 33 34 35

PI PI

A B

Device Reset Apply phase increment First Result Available

C D

JUMP

MODE

CEN

Fig. 3 Fixed Frequency Timing Diagram

Loading...

Loading...