MITEL PDSP16256A, PDSP16256AC, PDSP16256AC1R, PDSP16256B0, PDSP16256C0 Datasheet

...

PDSP16256/A

Programmable FIR Filter

DS3709 Issue 7.1 June 1999

Features

● Sixteen MACs in a Single Device

● Basic Mode is 16-Tap Filter at up to 25MHz

Sample Rates

● Programmable to give up to 128 Taps with

Sampling Rates Proportionally Reducing to

3·125MHz

● 16-bit Data and 32-bit Accumulators

● Can be configured as One Long Filter or Two

Half-Length Filters

● Decimate-by-two Option will Double the Filter

Length

● Coefficients supplied from Host System or local

EPROM

Applications

● High Performance Digital Filters

Description

The PDSP16256 contains sixteen multiplier accumulators, which can be multi cycled to provide

from 16 to 128 stages of digital filtering. Input data

and coefficients are both represented by 16-bit

two’s complement numbers with coefficients

converted internally to 12 bits and the results being

accumulated up to 32 bits.

In 16-tap mode the device samples data at the

system clock rate of up to 25MHz. If a lower sample

rate is acceptable then the number of stages can be

increased in powers of two up to a maximum of 128.

Each time the number of stages is doubled, the

sample clock rate must be halved with respect to the

system clock. With 128 stages the sample clock is

therefore one eighth of the system clock.

In all speed modes devices can be cascaded to

provide filters of any length, only limited by the

possibility of accumulator overflow. The 32-bit

results are passed between cascaded devices

without any intermediate scaling and subsequent

loss of precision.

Ordering Information

Commercial (0°C to 170°C)

PDSP16256A/C0/AC 25MHz, PGA package

Industrial (240°C to 185°C)

PDSP16256 B0/AC 20MHz, PGA package

PDSP16256 B0/GC 20MHz, QFP package

Military (255°C to 1125°C)

PDSP16256 MC/AC1R 20MHz, MIL-STD-883*

(latest revision), PGA package

PDSP16256 MC/GC1R 20MHz, MIL-STD-883*

(latest revision), QFP package

*See notes following Electrical Characteristics for further

information on MIL-STD-883 screening

Associated Products

PDSP16350 I/Q Splitter/NCO

PDSP16510A FFT Processor

The device can be configured as either one long

filter or two separate filters with half the number of

taps in each. Both networks can have independent

inputs and outputs.

Both single and cascaded devices can be operated

in decimate-by-two mode. The output rate is then

half the input rate, but twice the number of stages

are possible at a given sample rate. A single device

with a 20MHz clock would then, for example,

provide a 128-stage low pass filter, with a 5MHz

input rate and 2·5MHz output rate.

Coefficients are stored internally and can be down

loaded from a host system or an EPROM. The latter

requires no additional support, and is used in stand

alone applications. A full set of coefficients is then

automatically loaded at power on, or at the request

of the system. A single EPROM can be used to

provide coefficients for up to 16 devices.

PDSP16256

CHANGE

COEFF

POWER-ON

RESET

RES

PDSP

16256

EPROM

GNDSCLK

OUTPUT

DATA

INPUT

DATA

EPROM

ADDR DATA

Figure. 1 A dual filter application

ANALOG

INPUT

EPROM

ADDR DATA

COEFFICIENTS

CHANGE

COEFF

POWER-ON

RESET

RES

PDSP

16256

ADC

CLKOP

EPROM

GNDSCLK

OUTPUT

Figure. 2 Typical system application

DATA

2

PDSP16256

Signal

Description

DA15:0 16-bit data input bus to Network A.

DB15:0 Delayed data output bus in the single filter mode. Connected to the data input bus of the next device in a

cascaded chain. Input to Network B in the dual filter modes.

X31:0 Expansion input bus in the single filter mode. Connected to the previous filter output in a cascaded chain.

The inputs are not used on a single device system or on the Termination device in a cascaded chain. The

X bus provides the output from Network B in both dual modes.

F31:0 In single filter mode this bus holds the main device output. In dual mode it holds the output from Network A.

FEN Filter enable. The first high present on an SCLK rising edge defines the first data sample. The control register

and coefficient memory must be configured befor FEN is enabled.The signal must stay active whilst valid

data is being received and must be low if FRUN is high.

DFEN Delayed filter enable. This output is connected to the Filter Enable input of the next device in a cascaded

chain when moving towards the termination device and with multiple stand-alone EPROM-loaded

configurations. It is used to coordinate the control logic within each device.

SWAP Selects either the upper or lower set of coefficients for Bank Swap. A low selects the lower bank, a high the

upper bank.

FRUN In EPROM load mode, when high this signal allows continuous filter operations to occur without the need for

the initial FEN edge. If the device is not a single, interface or master device then this pin must be tied low.

DCLR

A low on this signal on the SCLK rising edge will clear all the internal accumulators.

low for a single cycle, signal BUSY will indicate when the internal clearing is complete. After a clear the

need only remain

DCLR

device must be re-synchronised to the data stream using FEN. It is recommended that FEN is taken low

at the same time as clear. FEN may then be taken high to synchronise the data stream once BUSY has

returned low.

C15:0 16-bit coefficient input bus. In the Byte mode of operation, C15:8 have alternative uses as explained in the

text.

A7:0 Coefficient address bus. In the EPROM mode A7:0 are address outputs for an EPROM. In the remote host

mode they are inputs from the host. A7 is not used when coefficients are loaded as 16-bit words.

CCS This pin is similar in operation to A7:0 and provides a higher order address bit. When low the coefficients

WEN

CS

BYTE

EPROM

are loaded, when high the control register is loaded.

In the remote mode this pin is an input which when low enables the load operation. In the EPROM mode

it is an output which provides the write enable for other slave devices.

This pin is always an input and must also be low for the internal write operation to occur.

When this pin is tied low, coefficients are loaded as two 8-bit bytes. When the pin is high they are loaded

as 16-bit words. In the EPROM mode this pin is ignored.

When this pin is tied low coefficients are loaded as bytes from an external EPROM. The device outputs an

address on A7:0. When the pin is high coefficients must be loaded from a remote master. They can then

be transferred individually rather than as a complete set.

SCLK The main system clock; all operations are synchronous with this clock. The clock rate must be either 1, 2,

4, or 8 times the required data sampling rate. The factor used depends on the required filter length.

CLKOP This output, when used to enable SCLK, can provide a data sampling clock. It has the effect of dividing the

OEN

SCLK rate by 1, 2, 4 or 8 depending on the filter mode selected.

Tri-state enable for the F bus. When high the outputs will be high impedance.

device and does not therefore take effect until the first SCLK rising edge

OEN

is registered onto the

BUSY A high on this signal indicates that the device is completing internal operations and is not yet able to accept

RES

new data. The signal is used during automatic EPROM loading, reset and accumulator clearing.

When this pin is low the control logic and accumulators are reset. In the EPROM mode it will initiate a load

sequence when it goes high.

NOTES

1. Unused buses (e.g. X31:0 when the device is configured in single or termination mode) can be set to any value. They should however be

maintained at a valid logic level to avoid an increase in power consumption.

2. To ensure correct input voltage thresholds are maintained all the VDD and GND pins must be connected to adequate power and ground planes.

Table 1 Pin descriptions

3

PDSP16256

EXTRA PIN D4,

CONNECTED TO D3

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

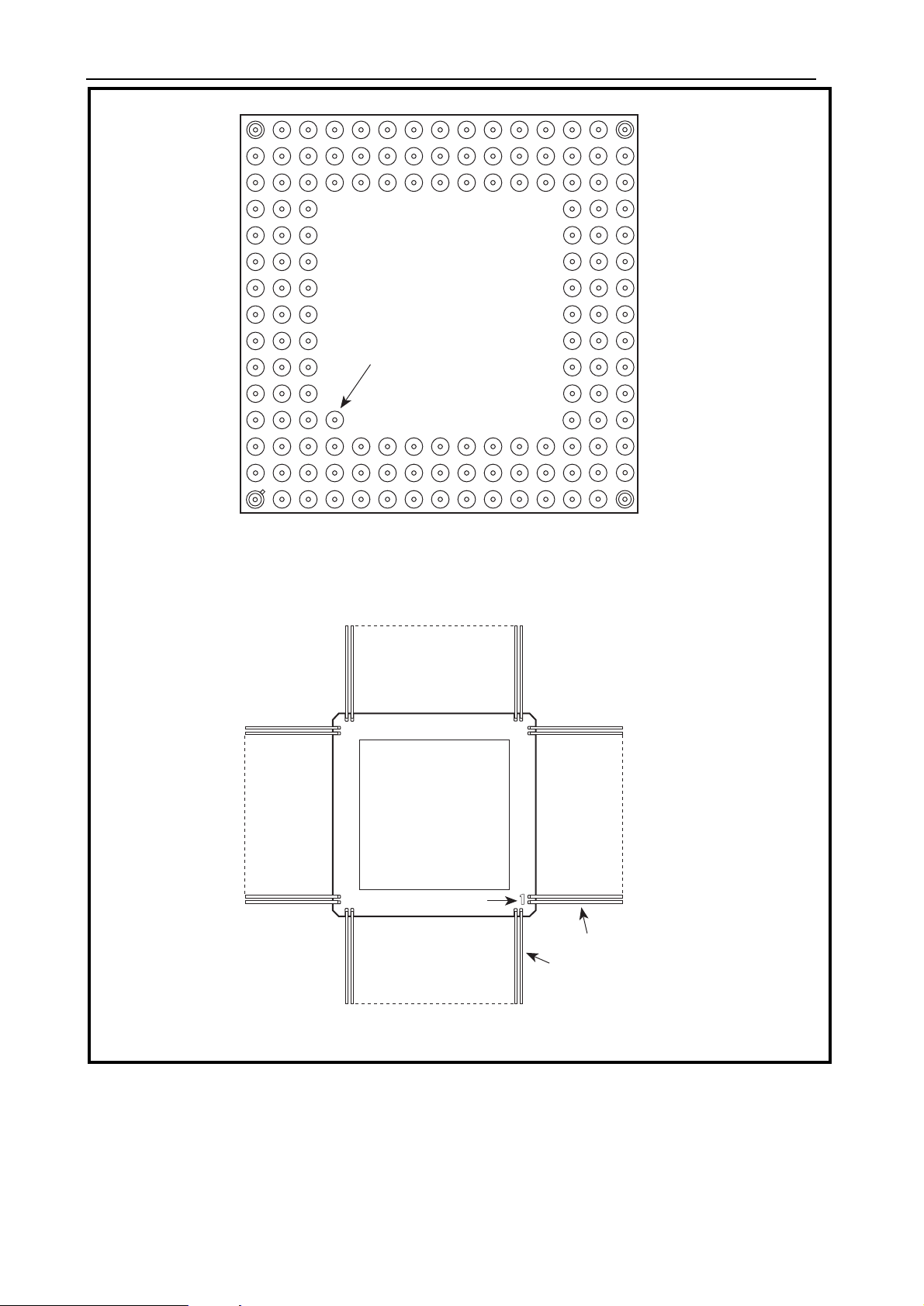

AC144

Fig. 3a Pin connections for 144 pin PGA package (bottom view)

PIN 1 INDEX

PIN 1

PIN 172

GC172

Fig. 3b Pin connections for 172 pin QFP (top view)

Figure. 3 Pin connection diagrams (not to scale). See T able 1 for signal descriptions and Table 2 for

pinouts.

4

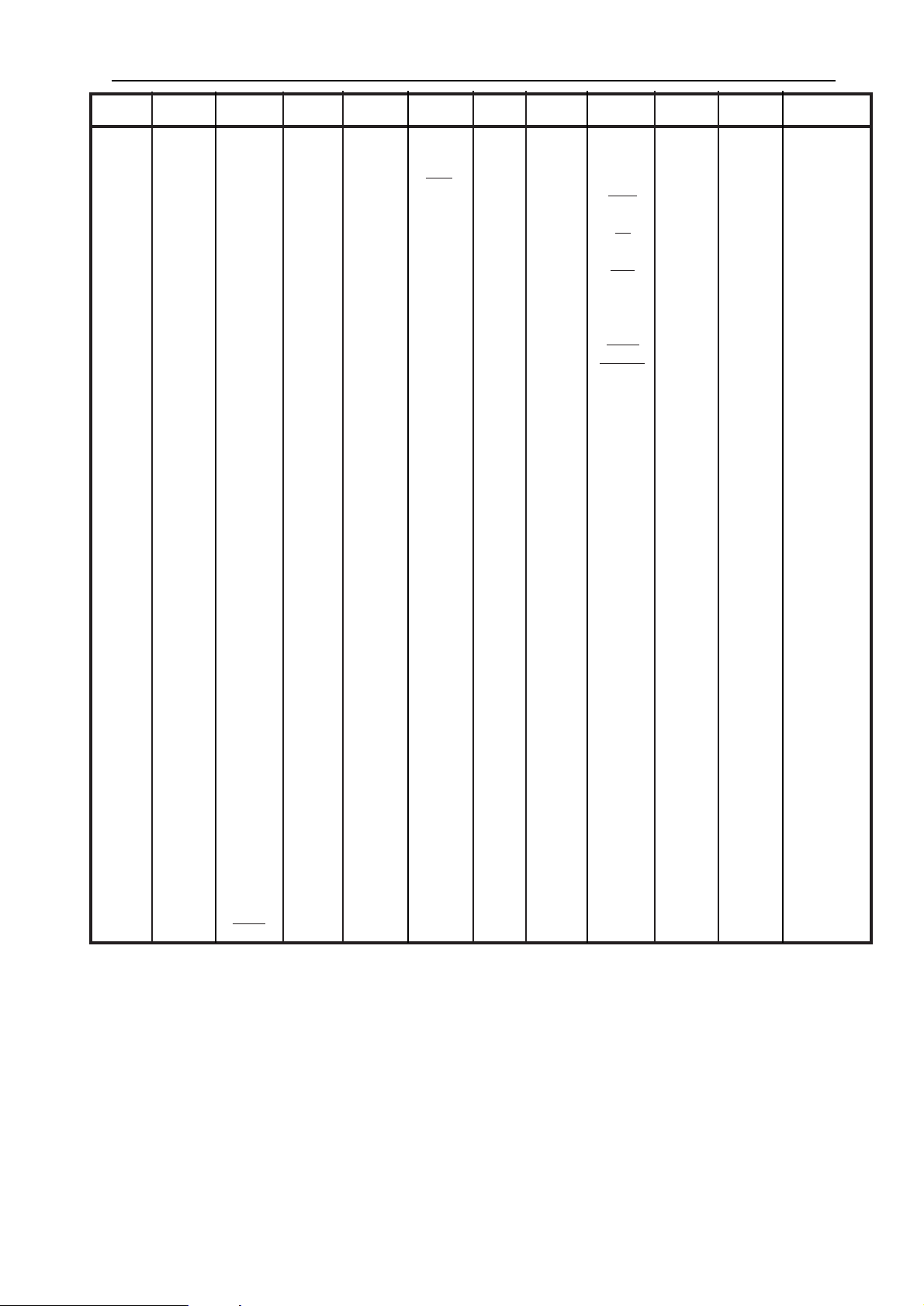

PDSP16256

GG

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

AC

A15

B15

D13

C14

G15

C15

D14

J15

E13

D15

E14

E15

F13

F14

F15

G14

G13

H14

H15

H13

J14

K15

-

J13

K14

L15

K13

L14

M15

L13

M14

N15

-

N14

M13

P15

P14

N13

R15

Signal

F0

F1

F2

F3

V

DD

F4

F5

GND

F6

F7

F8

F9

F10

F11

F12

GND

F13

F14

F15

V

DD

F16

F17

F18

F19

V

DD

F20

F21

GND

F22

F23

F24

F25

F26

F27

F28

GND

F29

F30

F31

V

DD

FEN

DFEN

DCLR

GG

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

AC

R14

N12

P13

R13

P12

N11

R12

P11

R11

R9

N10

P10

R10

P9

R7

N9

P8

R8

N8

P7

R6

-

N7

P6

R5

N6

P5

R4

-

N5

P4

R3

P3

N4

-

R2

P2

N3

-

-

R1

Signal

SWAP

GND

OEN

CLKOP

V

DD

DA0

DA1

DA2

DA3

DA4

DA5

GND

DA6

DA7

DA8

DA9

V

DD

DA10

DA11

DA12

DA13

DA14

DA15

GND

C0

C1

C2

C3

C4

C5

V

DD

C6

C7

C8

C9

C10

GND

C11

C12

C13

V

DD

GND

C14

GG

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

AC

P1

N2

N1

M2

L3

M1

M3

L2

L1

K3

K2

K1

J2

J3

G1

H2

H1

J1

H3

G2

F1

G3

F2

E1

F3

E2

D1

E3

D2

C1

C2

D3

B1

B2

C3

Signal

C15

-

-

GND

GND

WEN

CCS

CS

-

V

DD

RES

SLCK

GND

-

V

DD

BYTE

EPROM

A0

A1

A2

A3

A4

V

DD

A5

A6

GND

A7

DB0

DB1

DB2

-

GND

DB3

DB4

DB5

DB6

DB7

-

V

DD

DB8

DB9

DB10

DB11

DB12

DB13

DB14

-

GND

DB15

-

V

DD

GG

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

AC

A1

A2

C4

B3

A3

B4

C5

A4

B5

A5

A7

C6

B6

A6

B7

C7

B8

A9

A8

C8

B9

A10

C9

B10

A11

C10

-

B11

A12

C11

-

B12

A13

B13

C12

A14

-

B14

-

C13

Signal

GND

BUSY

X0

V

DD

X1

X2

X3

X4

X5

X6

GND

X7

X8

V

DD

X9

X10

X11

X12

X13

X14

GND

X15

X16

X17

X18

X19

X20

X21

X22

GND

X23

X24

X25

V

DD

X26

X27

X28

X29

X30

GND

X31

V

DD

FRUN

NOTE. All GND and VDD pins must be used

T able 2 Pin connections for AC144 and GC172 packages

5

PDSP16256

DA15:0 F31:0 OEN

SCLK FRUN

SWAP

A7:0

C15:0

CCS

WEN

CS

BYTE

EPROM

FEN

DFEN

DCLR

RES

COEFFICIENT

STORAGE

AND

CONTROL

CLKOP BUSY

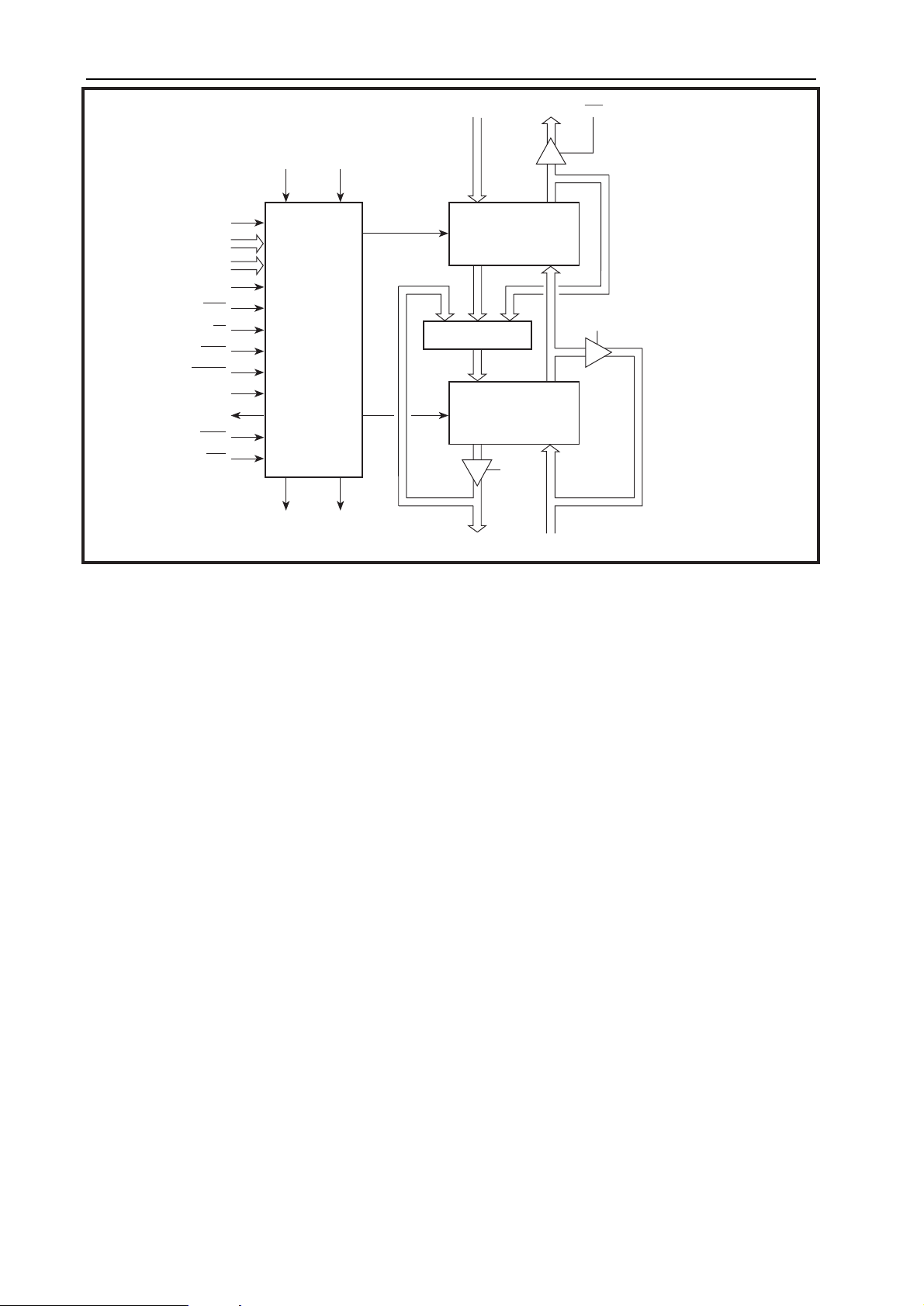

Figure. 4 Block Diagram

Operational Overview

The PDSP16256 is an application specific FIR filter for

use in high performance digital signal processing

systems. Sampling rates can be up to 25MHz. The

device provides the filter function without any software

development, and the options are simply selected by

loading a control register. The device can be user

configured as either a single filter, or as two separate

filters. The latter can provide two independent filters for

the in-phase and quadrature channels after IQ splitting,

or can provide two filters in cascade for greater stop

band rejection.

The device operates from a system clock, with rates up

to 25MHz. This clock must be 1, 2, 4, or 8 times the

required sampling frequency, with the higher

multiplication rates producing longer filter networks at

the expense of lower sampling rates. Devices can be

connected in cascade to produce longer filter lengths.

This can be accomplished without the need for any

additional external data delays, and all the single device

options remain available.

Continuous inputs are accepted, and continuous results

produced after the internal pipeline delay. Connection

can be made directly to an A-D converter. The filter

operation can be synchronised to a Filter Enable signal

(FEN) whose positive going edge marks the first data

sample. The internal multiplier accumulator array can be

cleared with a dedicated input. This is necessary if

erroneous results obtained during the normal data ‘flush

6

NETWORK

A

DUAL

MUX

NETWORK

B

SINGLE

MODE

DB15:0 X31:0

MODE

through’ are not permissible in the system.

Coefficients can be loaded from a host system using a

conventional peripheral interface and separate data

bus. Alternatively, they can be loaded as a complete set

from a byte wide EPROM. The device produces

addresses for the EPROM and a BUSY output indicates

that the transfer is occurring. Up to sixteen devices can

have their coefficients supplied from a single EPROM.

These devices need not necessarily be part of the same

filter network.

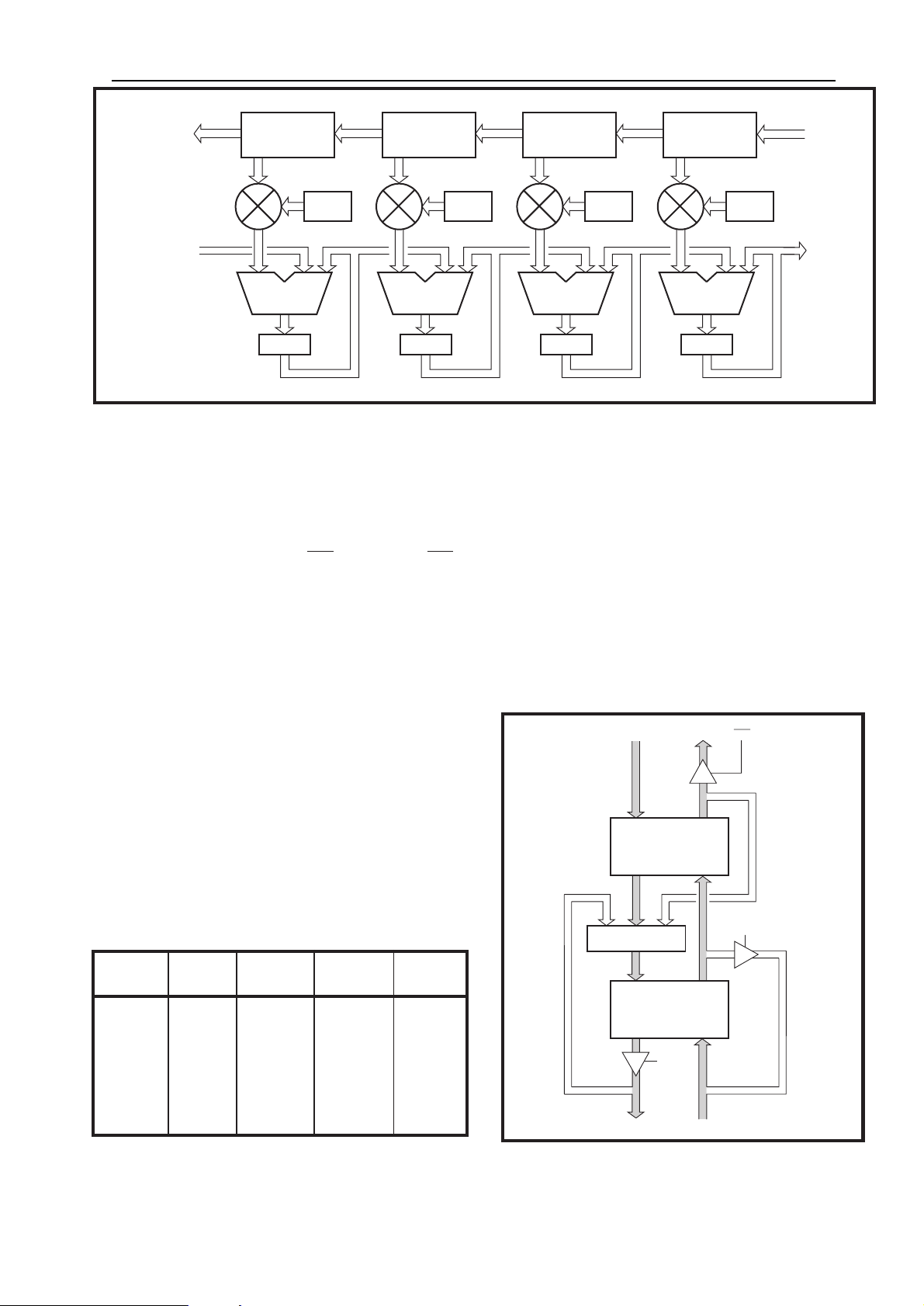

Each of the filter networks shown in Fig. 4 contains eight

systolic multiplier accumulator stages; an example with

four stages is shown in Fig. 5. Input data flows through

the delay lines and is presented for multiplication with the

required coefficient. This is added to either the last result

from this accumulator or the result from the previous

accumulator. The filter results progress along the adders

at the data sample rate. If the sample rate equals SCLK

divided by four, for example, then the accumulated result

is passed onto the next stage every fourth cycle. The

structure described is highly efficient when used to

calculate filtered results from continuous input data.

A comprehensive digital filter design program is

available for PC compatible machines. This will optimise

the filter coefficients for the filter type required and

number of taps available at the selected sample rate

within the PDSP16256 device. An EPROM file can be

automatically generated in Motorola S-record format.

PDSP16256

DATA

OUT

ACCUMULATE

EXPANSION

IN

DATA

DELAY LINE

COEFF

ADDER

2

1

Z

RAM

DATA

DELAY LINE

COEFF

ADDER

2

1

Z

RAM

Figure. 5 Filter network diagram

Single Filter Options

When operating as a single filter the device accepts data

on the 16-bit DA bus at the selected sample rate, see

Figs. 5 and 6. Results are presented on the 32-bit F bus,

which may be tristated using the

registered onto the device and does not therefore take

effect until the first SCLK rising edge. Devices may be

cascaded this allows filters with more taps than available

from a single device. To accomplish this two further

buses are utilised. The DB bus presents the input data to

the next device in cascade after the appropriate delay,

while, partial results are accepted on the X bus.

input. Signal

OEN

OEN

DATA

DELAY LINE

COEFF

ADDER

2

1

Z

RAM

DATA

DELAY LINE

COEFF

ADDER

2

1

Z

RAM

the higher frequency components present in the input.

The Nyquist criterion, specifying that the sampling rate

must be at least double the highest frequency component, can still then be satisfied even though the sampling

rate has been halved.

is

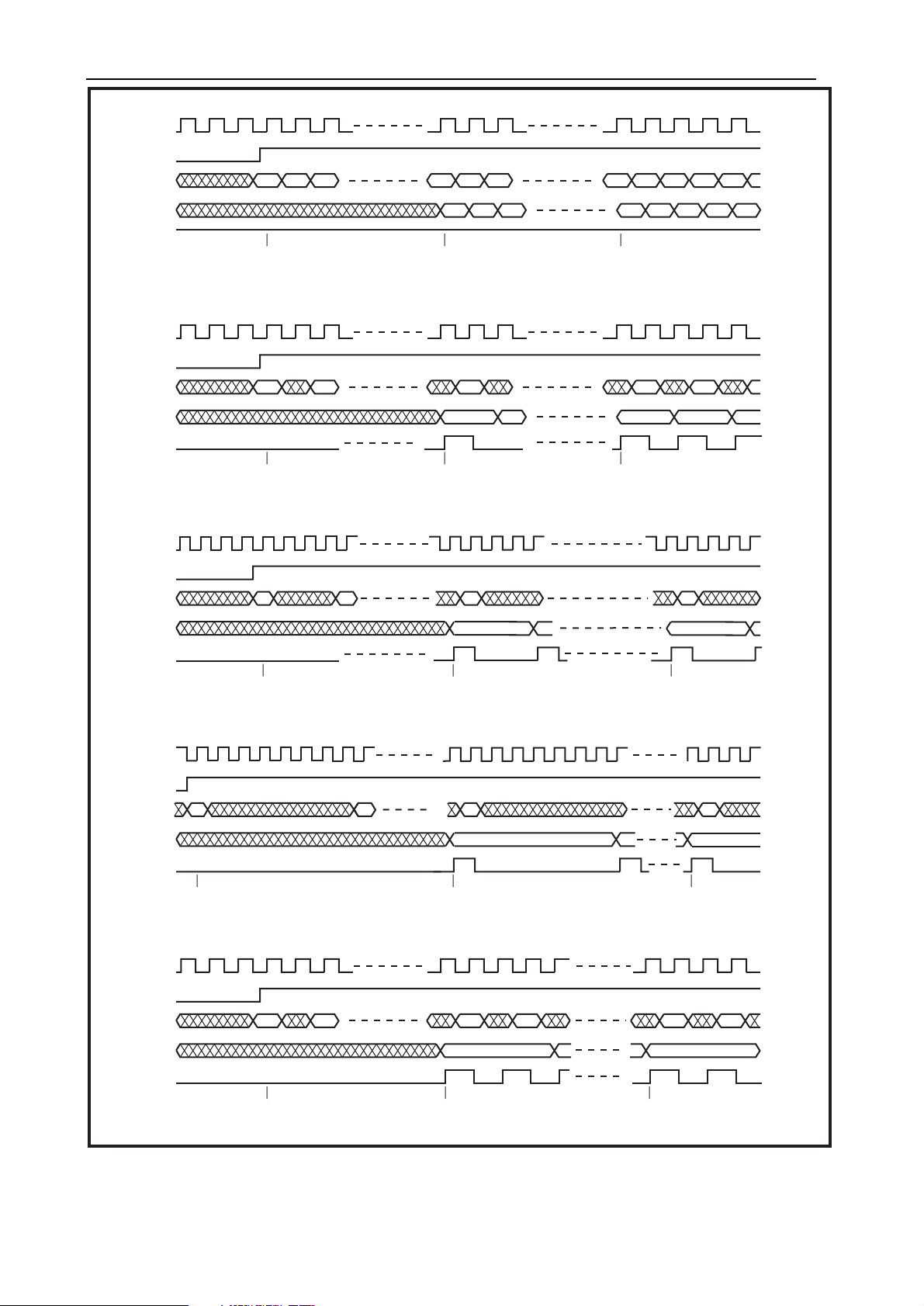

The system clock latency for a single device is shown in

Table 3. This is defined as the delay from a particular data

sample being available on the input pins to the first result

including that input appearing on the output pins. It does

not include the delay needed to gather N samples, for an

N tap filter, before a mathematically correct result is

obtained.

DATA

IN

RESULT

OUT

Single filter mode is selected by setting control register bit

15 to a one. The required filter length is then selected

using control register bits 14 and 13 as summarised in

Table 3. The options define the number of times each

multiplier accumulator is used per sample clock period.

This can be once, twice, four times, or eight times.

In addition a normal/decimate bit (CR12) allows the filter

length to be doubled at any sample rate. This is possible

when the filter coefficients are selected to produce a low

pass filter, since the filtered output would then not contain

CR Input Output Filter Setup

14 13 12 Rate Rate Length Latency

0 0 0 SCLK SCLK 16 Taps 16

0 0 1 SCLK SCLK/2 32 Taps 17

0 1 0 SCLK/2 SCLK/2 32 Taps 16

0 1 1 SCLK/2 SCLK/4 64 Taps 18

1 0 0 SCLK/4 SCLK/4 64 Taps 20

1 0 1 SCLK/4 SCLK/8 128 Taps 24

1 1 0 SCLK/8 SCLK/8 128 Taps 24

Table 3 Single Filter options Figure. 6 Single Filter bus utilisation

DA15:0 F31:0 OEN

NETWORK

A

DUAL

MUX

NETWORK

B

SINGLE

MODE

DB15:0 X31:0

MODE

7

PDSP16256

SPEED MODE 0 (Data input and output at f

SCLK

FEN

DA15:0

F31:0

CLKOP

123

ABC

) CR14:13 = 00, CR12 = 0. CLKOP held high.

SCLK

16 17 18

First data point (A)

is read on edge 1

SPEED MODE 1 (Data input and output at half f

SCLK

FEN

DA15:0

F31:0

CLKOP

123

AB

SCLK

16 17 18

First data point (A)

is read on edge 1

SPEED MODE 2 (Data input and output at a quarter f

SCLK

FEN

DA15:0

123

AB

45 23 24

A′ B′ C′

First valid result

including data point (A)

available after edge 16

) CR14:13 = 01, CR12 = 0

A′ B′

First valid result

including data point (A)

available after edge 16

) CR14:13 = 10, CR12 = 0

SCLK

20 21 22

31 32 33

A′′ B′′ C′′

34 35

D′′ E′′

Valid result contains

the first 16 data points

available after edge 31

78 79 80

A′′ B′′ C′′

81 82

Valid result contains

the first 32 data points

available after edge 78

272 273

274 275 276

F31:0

CLKOP

First data point (A)

is read on edge 1

SPEED MODE 3 (Data input and output at an eighth f

SCLK

FEN

DA15:0

F31:0

CLKOP

SPEED MODE 1 Decimating (Data input at half f

SCLK

FEN

DA15:0

F31:0

123

A

45

First data point (A)

is read on edge 1

123

AB

6789

B

SCLK

18 19 20

A′ B′

First valid result

including data point (A)

available after edge 20

) CR14:13 = 11, CR12 = 0

SCLK

24 25 26

A′ B′

27 28

29 30 31 32

First valid result

including data point (A)

available after edge 24

and output at a quarter f

21 22

B′

SCLK

A′′ B′′

Valid result contains

the first 64 data points

available after edge 272

1040

1041 1042 1043

A′′

Valid result contains

the first 128 data points

available after edge 1040

) CR14:13 = 01, CR12 = 1.

142 143 144

B′′

145

CLKOP

First data point (A)

is read on edge 1

First valid result

including data point (A)

available after edge 18

Valid result contains

the first 64 data points

available after edge 142

Figure. 7 Single Filter timing diagrams

8

PDSP16256

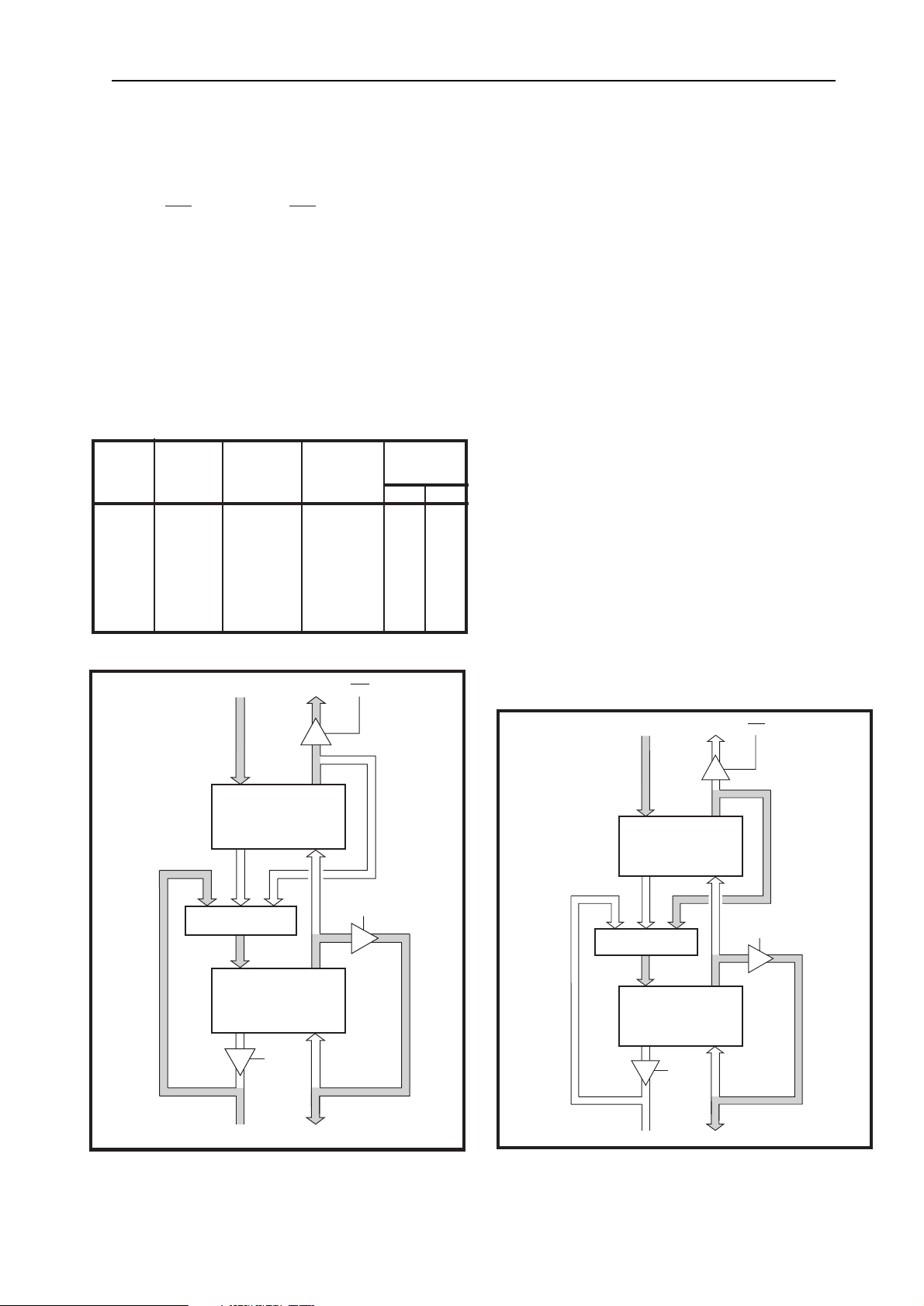

Dual Indipendant Filter Options

When operating as two independent filters the device

accepts 16 bit data on both the DA and DB buses at the

selected sample rate, see Fig. 8. Results are available

from both the F and X buses. The F bus may be tristated

using the

OEN

input. Signal

device and does not therefore take effect until the first

SCLK rising edge

Each filter must be configured in the same manner, and

multiple device expansion is not possible due to the pin

re-organization. The latter requirement can, of course,

still be satisfied by several devices configured as single

filters.

Dual independent filter mode is selected by setting

control register bits 15 and 4 to a zero. The required filter

CR Input Output Filter Setup

141312 Rate Rate Length Latency

0 0 0 SCLK SCLK 8 Taps 16 27

0 0 1 SCLK SCLK/2 16 Taps 17 0 1 0 SCLK/2 SCLK/2 16 Taps 16 28

0 1 1 SCLK/2 SCLK/4 32 Taps 18 1 0 0 SCLK/4 SCLK/4 32 Taps 20 36

1 0 1 SCLK/4 SCLK/8 64 Taps 24 1 1 0 SCLK/8 SCLK/8 64 Taps 24 40

Table 4. Dual Filter options

DA15:0 F31:0 OEN

OEN

is registered onto the

Ind Cas

length is selected using control register bits 14 and 13 as

summarised in Table 4, which also shows the resulting

latency. As in single filter mode normal or decimate-bytwo operation can be selected using control register bit

12.

Dual Cascaded Filter Options

When operating as two cascaded filters the device accepts 16 bit data on the DA bus at the selected sample

rate. Results are presented on the 32-bit X bus, see Fig.

9. Each filter must be configured in the same manner.

Multiple device expansion is not possible in this mode.

Dual cascaded filter mode is selected by setting control

register bit 15 to a zero and bit 4 to a one. The required

filter length is selected using control register bits 14 and

13 as summarised in Table 4, which also shows the

resulting latency. The decimate-by-two option is not

available in this mode.

The data for the second filter network is extracted as the

middle 16 bits from the first networks accumulated result.

For successful operation the first filter network must have

unity gain. See the section on filter accuracy for more

details.

The cascade option is used to increase the stop band

rejection in a practical filter application. Theoretically,

increasing the number of taps in an FIR filter will increase

the stop band rejection, but this assumes floating point

calculations with no accuracy limitations. In practice, with

fixed point arithmetic, better performance is achieved

with two smaller filters in series.

NETWORK

A

MUX

NETWORK

B

SINGLE

MODE

DB15:0 X31:0

DUAL

MODE

DA15:0 F31:0 OEN

NETWORK

A

DUAL

MUX

NETWORK

B

SINGLE

MODE

DB15:0 X31:0

MODE

Figure. 9 Dual cascaded filter bus utilisationFigure. 8 Dual independent filter bus utilisation

9

Loading...

Loading...