MITEL PDSP1601GC1R, PDSP1601MC Datasheet

PDSP1601 MC

PDSP1601 MC

ALU and Barrel Shifter

Supersedes April 1993 version, DS3763 - 1.1 DS3763 - 2.1 November 1998

The PDSP1601 is a high performance 16-bit arithmetic

logic unit with an independent on-chip 16-bit barrel shifter.

The PDSP1601 supports Multicycle multiprecision

operation. This allows a single device to operate at 10MHz for

16-bit-bit-fields, 5MHz for 32-bit fields and 2.5MHz for 64-bit

fields. The PDSP1601 can also be cascaded to produce wider

words at the 10MHz rate using the Carry Out and Carry In pins.

The Barrel Shifter is capable of extension, for example the

PDSP1601 can used to select a 16-bit field from a 32-bit input

in 100ns.

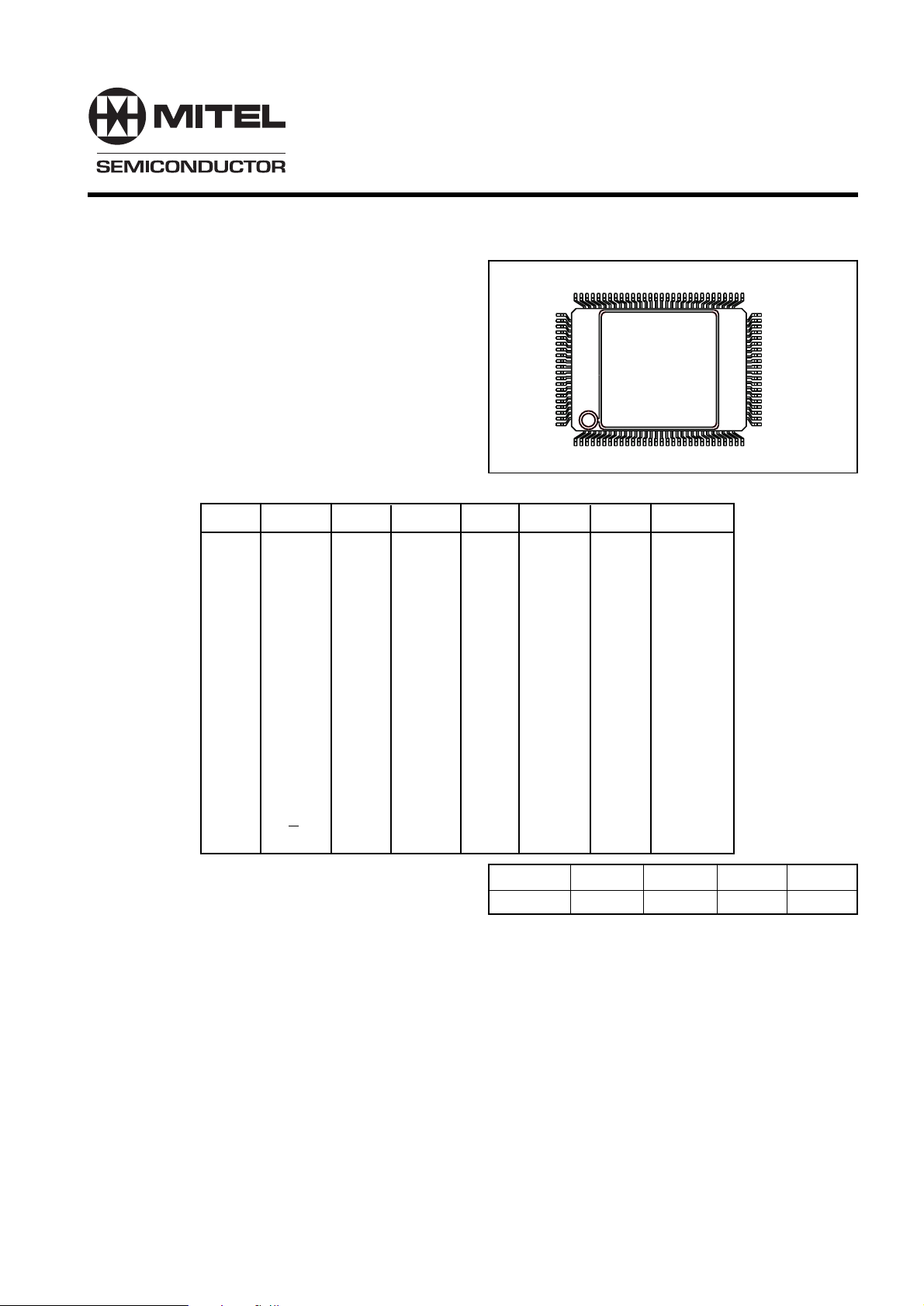

GC100

Fig.1 Pin connections

GC pin

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

Function

VCC

RS2

C0

C1

C2

C3

C4

C5

C6

C7

GND

C8

C9

C10

C11

C12

C13

C14

C15

OE

BFP

GC pin

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

Function

5

6

7

8

9

VCC

RA0

RA1

RA2

MSB

MSS

B15

B14

B13

B12

B11

B10

FEATURES

■ 16-bit, 32 instruction 10MHz ALU

■ 16-bit, 10MHz Logical, Arithmetic or Barrel Shifter

■ Independent ALU and Shifter Operation

■ 4 x 16-bit On Chip Scratchpad Registers

■ Multiprecision Operation; e.g. 200ns 64-bit

Accumulate

■ Three Port Structure with Three Internal Feedback

Paths Elimates I/O Bottlenecks

■ 300mW Maximum Power Dissipation

■ 100-pin Ceramic Quad Flatpack

CO

CI

IA0

IA1

IA2

IA3

IA4

B9

B8

GC pin

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

Function

B7

B6

B5

B4

B3

B2

B1

B0

CEB

CLK

GND

MSA0

MSA1

A15

A14

A13

A12

A11

A10

A9

A8

GC pin

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

Function

A7

A6

A5

A4

A3

A2

A1

A0

CEA

MSC

IS0

IS1

IS2

IS3

SV0

SV1

SV2

SV3

SVOE

RS0

RS1

Rev A B C D

Date MAR 1993 NOV 1998

NOTE

Polyimide is used as an inter-layer dielectric and glassivation.

APPLICATIONS

■ Digital Signal Processing

■ Array Processing

■ Graphics

■ Database Addressing

■ High Speed Arithmetic Processors

ORDERING INFORMATION

PDSP1601/MC/GC1R (Ceramic QFP Package -

MIL STD 883 Class B

Screening)

1

PDSP1601 MC

PIN DESCRIPTIONS

Symbol

MSB

Pin No.

(GG100

Package)

16

ALU B-input multiplexer select control.

of CLK.

Description

1

This input is latched internally on the rising edge

MSS

B15 - B0

CEB

CLK

MSA0 - MSA1

A15 - A0

CEA

MSC

IS0 - IS3

SV0 - SV3

SVOE

RS0, RS1

RS2

C0 - C15

17

18 - 25

30 - 37

38

39

41 - 42

43 - 50

55 - 62

63

64

65 - 68

69 - 72

73

74 - 75

81

82 - 98

Shifter Input multiplexer select control.1 This input is latched internally on the rising edge

of CLK.

B Port data Input. Data presented to this port is latched into the input register on the rising

edge of CLK. B15 is the MSB.

Clock enable, B Port input register. When low the clock to this register is enabled.

Common clock to all internal registered elements. All registers are loaded, and outputs

change on the rising edge of CLK.

ALU A-input multiplexer select control.1 This input are latched internally on the rising edge

of CLK.

A Port data Input. Data presented to this port is latched into the input register on the rising

edge of CLK. B15 is the MSB.

Clock enable, A Port input register. When low the clock to this register is enabled.

C-Port multiplexer select control.1 This input is latched internally on the rising edge

of CLK.

Instruction inputs to Barrel Shifter, IS3 = MSB.1 This input is latched internally on the

rising edge of CLK.

Shift Value I/O Port. This port is used as an input when shift values are supplied form

external sources, and as an output when Normalise operations are invoked. The I/O functions

are determined by the IS0 - IS3 instruction inputs, and by the

The shift value is latched internally on the rising edge of CLK.

SVOE control.

SV Output enable. When high the SV port can only operate as an input. When low the SV

port can act as an input or as an output, according to the IS0 - IS3 instruction. This pin should

be tied high or low, depending upon the application.

Instruction inputs to Barrel Shifter registers.

1

These input are latched internally on the

rising edge of CLK.

C Port data output. Data output on this port is selected by the C output multiplexer.

C15 is the MSB

OE

BFP

CO

RA0 - RA2

CI

IA0 - IA3

IA4

Vcc

GND

99

100

6

7 - 9

10

11 - 14

80, 5

90 & 40

Output enable. The C Port outputs are in high impedance condition when this control is high

Block Floating Point Flag from ALU, active high.

Carry out from MSB of ALU

Instruction inputs to ALU registsers.1 These inputs are latched interally on the rising

edge of CLK.

Carry in to LSB of ALU

Instruction inputs to ALU.1 IA4 = MSB. These inputs are latched internally on the rising

edge of CLK.

+5V supply: Both Vcc pins must be connected.

0V supply: Both GND pins must be connected.

NOTES

1. All instructions are executed in the cycle commencing with the rising edge of the CLK which latches the inputs.

2

PDSP1601 MC

A INPUT

A REG

A MUX

BFP

AB

CO

LEFT REG. RIGHT REG.

FUNCTIONAL DESCRIPTION

16

ALU REG FILE

CEA

MSA0-1

ALU

RAD-2

IA0-4

MSB

5

CI

3

C MUX

OE

16

COUT

B MUX

2

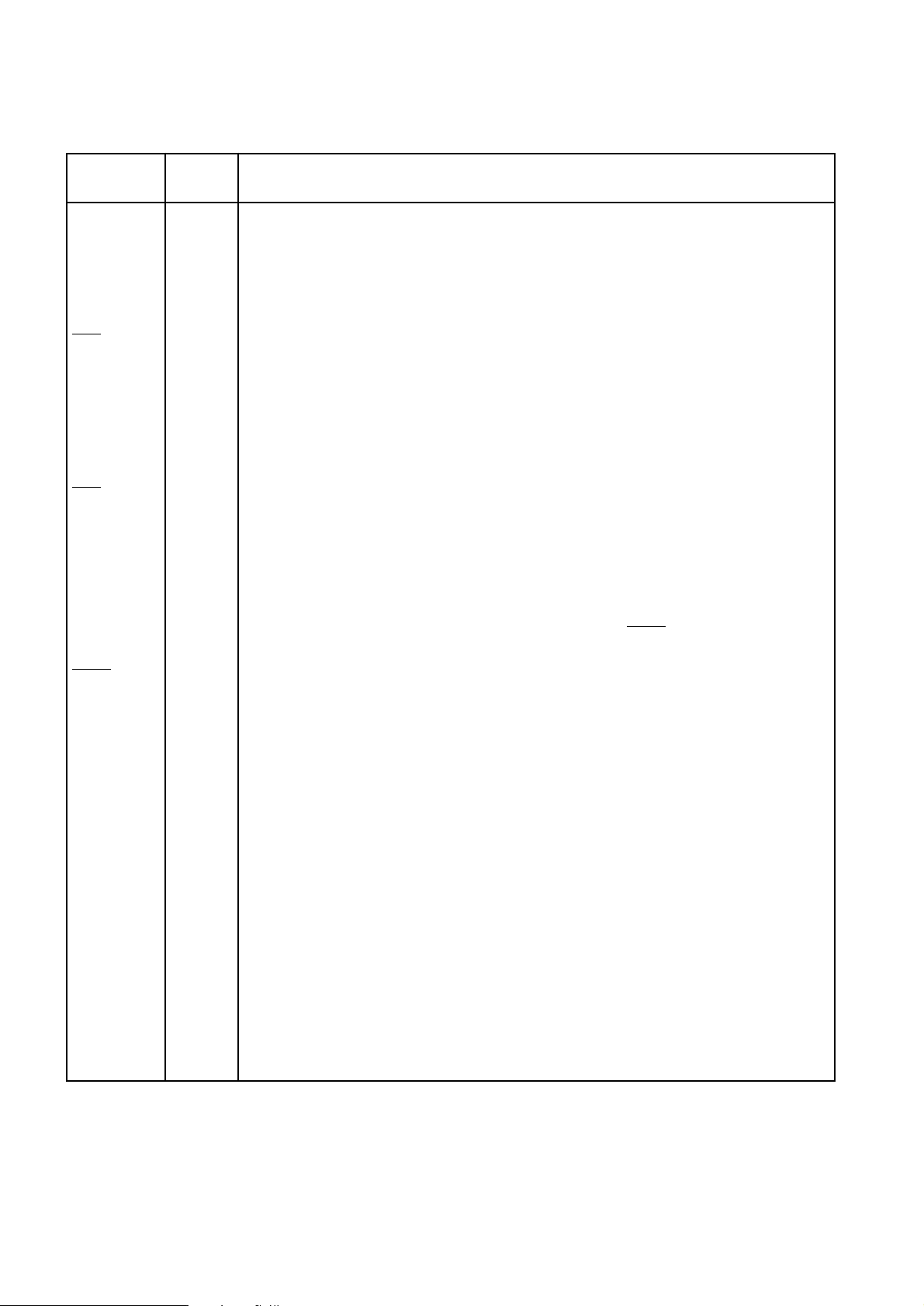

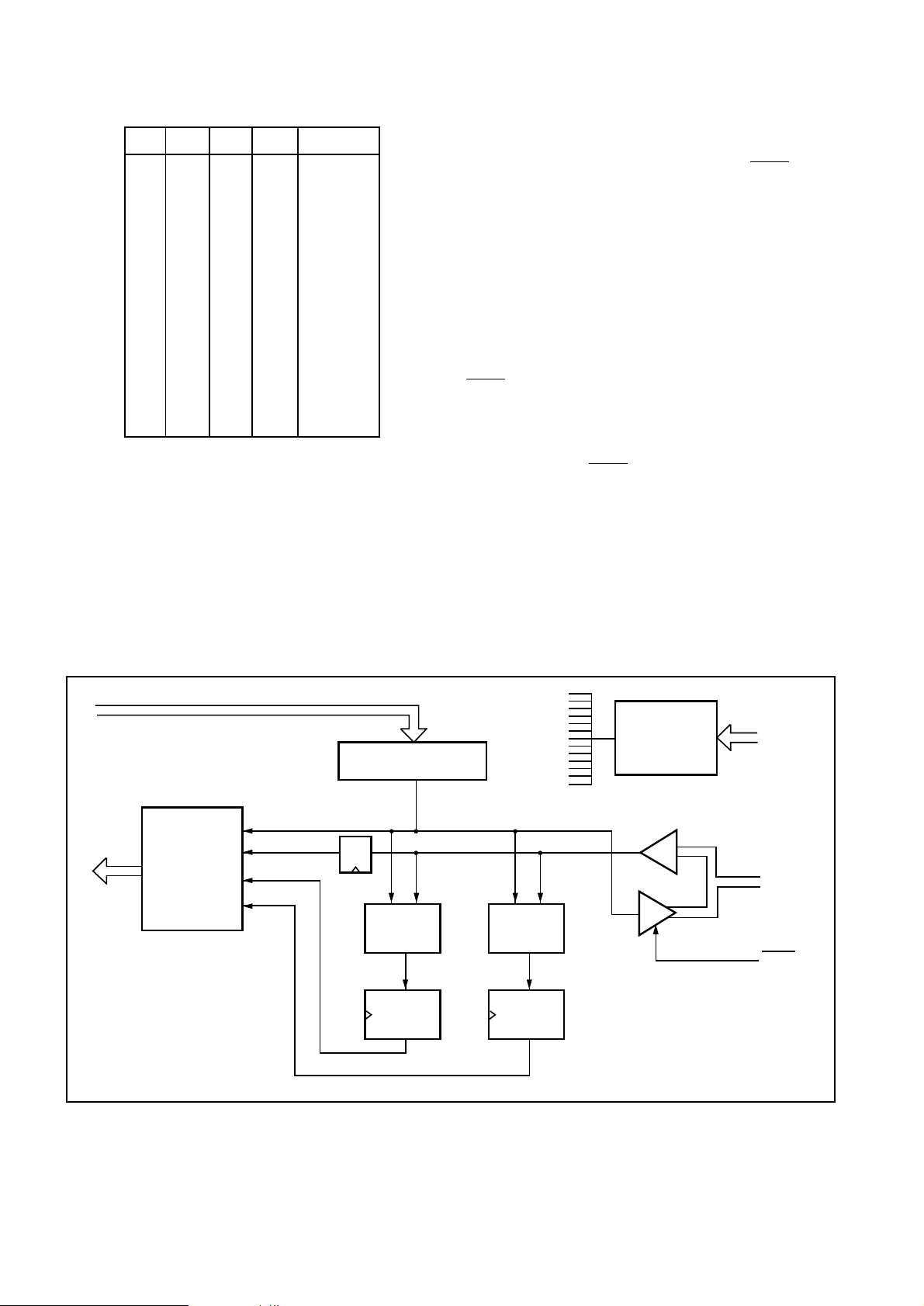

Fig.2 PDSP1601 block diagram

MSC

RS0-2

3

LEFT REG. RIGHT REG.

B INPUT

16

B REG

S MUX

BARREL SHIFTER

SHIFTER REG FILE

CEB

MSS

SHIFT

CONTROL

SVOE

IS0-3

SV0-3

The PDSP1601 contains four main blocks: the ALU, the

Barrel Shifter and the two Register Files.

The ALU

The ALU supports 32 instructions as detailed in Table 1.

The inputs to the ALU are selected by the A and B MUXs.

Data will fall through from the selected register through the A

or B input MUXs and the ALU to the ALU output register file in

100ns.

The ALU instructions are latched, such that the instruction

will not start executing until the rising edge of CLK latches the

instruction into the device.

The ALU accepts a carry in from the CI input and supplies

a carry out to the CO output. Additionally, at the end of each

cycle, the carry out from the ALU is loaded into an internal 1

bit register, so that it is available as an input to the ALU on the

next cycle. In the manner, Multicycle, multiprecisiion

operations are supported. (See MULTICYCLE CASCADE

OPERATIONS).

BFP Flag

The ALU has a user programmable BFP flag. This flag

may be programmed to become active at any one of four

conditions. Two of these conditions are intended to support

Block Floating Point operations, in that they provide flags

indicating that the ALU result is within a factor of two or four of

overflowing the 16 bit number range. For multiprecision

operations the flag is only valid whilst the most significant 16

bit byte is being processed. In this manner the BFP flag may

be used over any extended word width.

The remaining two conditions detect either an overflow

condition or a zero result. For the overflow condition to be

active the ALU result must have overflowed into the 16th (sign)

bit, (this flag is only valid whilst the most significant 16 bit byte

is being processed). The zero condition is active if the result

from the ALU is equal to zero. For multiprecision operations

the zero flag must be active for all of the 16 bit bytes of an

extended word.

The BFP flag is programmed by executing on of the four

SBFXX instructions (see Table 1). During the execution of any

of these four instructions, the output of the ALU is forced to

zero.

Multicycle/Cascade Operation

The ALU arithmetic instructions contain two or three

options for each arithemtic operation.

The ALU is designed to operate with two's complement

arithmetic, requiring a one to be added to the LSB for all

subtract operations. The instructions set includes instructions

that will force a one into the LSB, e.g. MIAX1, AMBX1, BMAX1

(see Table 1).

These instructions are used for the least significant 16 bits

of any subtract operation.

The user has an option of cascading multiple devices, or

multicycling a single device to extend the arithmetic precision.

Should the user cascade multiple devices, then the cascaded

arithmetic instructions using the external CI input should be

employed for all but the least significant 16 bits, e.g. MIACI,

APBCI, BMACI (see Table 1).

Should the user multicycle a single device, then the

Multicycle Arithmetic instructions, using the internally

registered CO bit should be employed for all but the least

significant 16 bits, e.g. MIACO, APBCO, AMBCO, BMACO

(see Table 1).

3

PDSP1601 MC

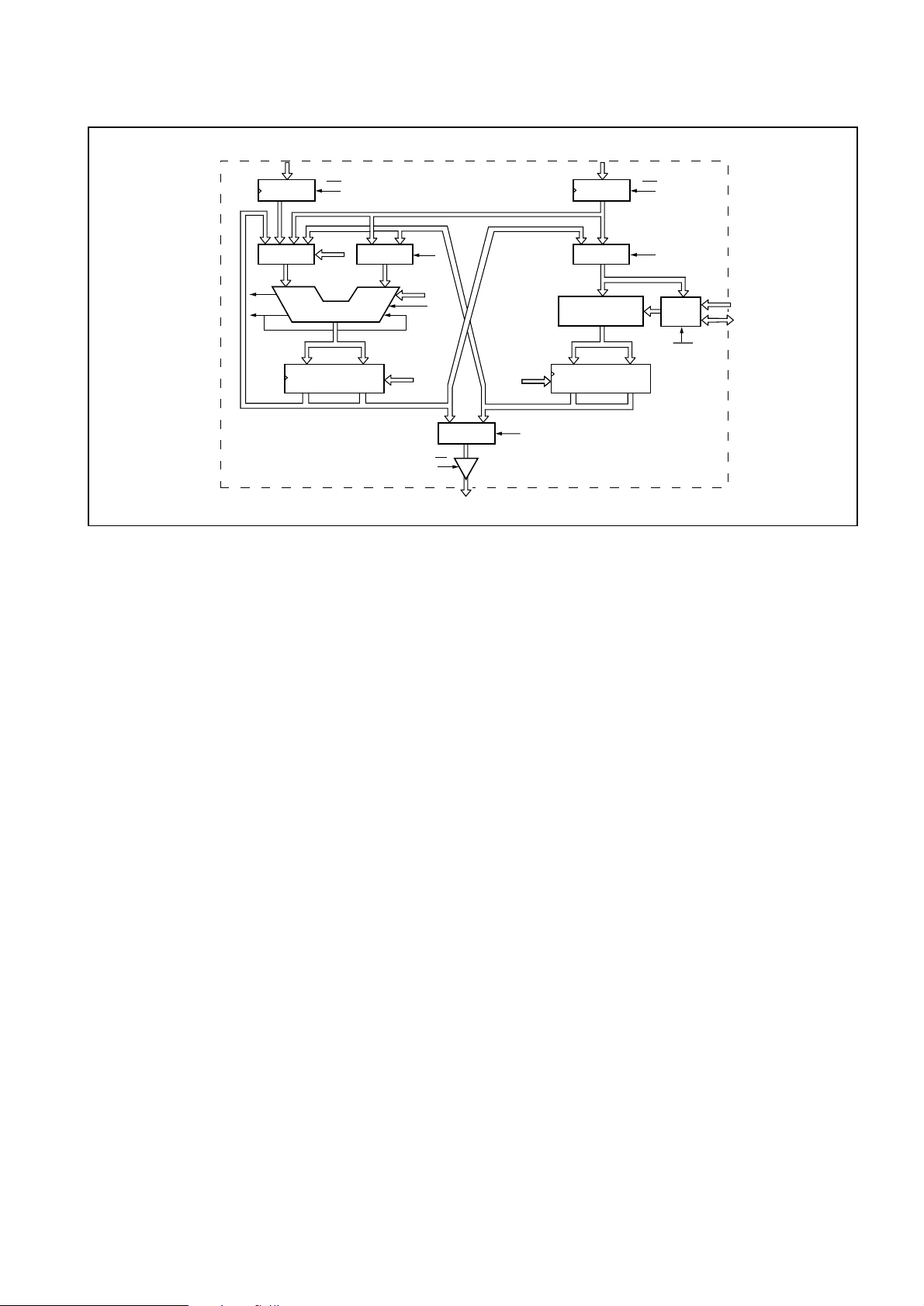

Table 1 ALU instructions

Inst

IA4-IA0

Mnemonic

1a. ARITHMETIC INSTRUCTIONS

Operation

Function

Mode

00

01

02

03

04

05

06

07

08

09

0A

0B

0C

0D

0E

0F

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

01111

CLRXX

MIAX1

MIACI

MIACO

A2SGN

A2RAL

A2RAR

A2RSX

APBCI

APBCO

AMBX1

AMBCI

AMBCO

BMAX1

BMACI

BMACO

Inst

10

11

12

13

14

15

16

17

RESET

MINUS A

MINUS A

MINUS A

A/2

A/2

A/2

A/2

A PLUS B

A PLUS B

A MINUS B

A MINUS B

A MINUS B

B MINUS A

B MINUS A

B MINUS A

1b. LOGICAL INSTRUCTIONS

IA4-AI0

10000

10001

10010

10011

10100

10101

10110

10111

Mnemonic

ANXAB

ANANB

ANNAB

ORXAB

ORNAB

XORAB

PASXA

PASNA

CLEAR ALL REGISTERS

NA Plus 1

NA Plus CI

NA Plus CO

A/2 Sign Extend

A/2 with Ral LSB

A/2 with RAR LSB

A/2 with RSX LSB

A Plus B Plus CI

A Plus B Plus CO

A Plus NB Plus 1

A Plus NB Plus CI

A Plus NB Plus CO

NA Plus B Plus 1

NA Plus B Plus CI

NA Plus B Plus CO

Operation

A AND B

A AND NB

NA AND B

A OR B

NA OR B

A XOR B

PASS A

INVERT A

Function

A. B

A. NB

NA. B

A + B

NA + B

A XOR B

A

NA

---------

LSBYTE

CASCADE

MULTICYCLE

MSBYTE

MULTICYCLE

MULTICYCLE

MULTICYCLE

CASCADE

MULTICYCLE

LSBYTE

CASCADE

MULTICYCLE

LSBYTE

CASCADE

MULTICYCLE

1c. CONTROL INSTRUCTIONS

Inst

18

19

1A

1B

1C

1D

1E

1F

IA4-AI0

11000

11001

11010

11011

11100

11101

11110

11111

Mnemonic

SBFOV

SBFU1

SBFU2

SBFZE

OPONE

OPBYT

OPNIB

OPALT

KEY

A = A input to ALU

B = B input to ALU

CI = External Carry in to ALU

CO = Internally Registered Carry out from ALU

RAL = ALU Register (Left)

RAR = ALU Register (Right)

RSX = Shifter Register (Left or Right)

Operation

Set BFP Flag to OVR, Force ALU output to zero

Set BFP Flag to UND 1 Force ALU output to zero

Set BFP Flag to UND 2 Force ALU output to zero

Set BFP Flag to ZERO Force ALU output to zero

Output 0001 Hex

Output 00FF Hex

Output 000F Hex

Output 5555 Hex

MNEMONICS

CLRXX Clear All Registers to zero

MIAXX Minus A, XX = Carry in to LSB

A2XXX A Divided by 2, XXX = Source of MSB

APBXX A Plus B, XX = Carry in to LSB

AMBXX A Minus B, XX = Carry in to LSB

BMAXX B Minus A, XX = Carry in to LSB

ANX-Y AND X = Operand 1, Y = Operand 2

ORX-Y OR X = Operand 1, Y = Operand 2

XORXY Exclusive OR X = Operand 1, Y = Operand 2

PASXX Pass XX = Operand

SBFXX Set BFP Flag XX = Function

OPXXX Output Constant XXX

4

Divide by Two

PDSP1601 MC

The Barrel Shifter

The ALU has four (A2SGN, A2RAL, A2RAR, A2RSX)

instructions used for right shifting (dividing by two) extended

precision words. These words, (up to 64 bits) may be stored

in the two on-chip register files. When the least significant 16

bit word is shifted, the vacant MSB must be filled with the LSB

from the next most significant 16 bit byte. This is achieved via

the A2RAL, A2RAR or A2RSX instructions which indicate the

source of the new MSB (see SLU INSTRUCTION SET).

When the most significant 16 bit byte is right shifted, the

MSB must be filled with a duplicate of the original MSB so as

to maintain the correct sign (Sign Extension). This operation

is achieved via the A2SGN instruction (see Table 1).

Constants

The ALU has four instructions (OPONE, OPBYT, OPNIB,

OPALT) that force a constant value onto the ALU output.

These values are primarily intended to be used as masks, or

the seeds for mask generation, for example, the OPONE

instruction will set a single bit in the least significant position.

This bit may be rotated any where in the 16 bit field by the

Barrel Shifter, allowing the AND function of the ALU to perform

bit-pick operations on input data.

CLR

The ALU instruction CLRXX is used as a Master Reset for

the entire device. This instruction has the effect of:

The Barrel Shifter supports 16 instructions as detailed in

Table 2. The input to the Barrel Shifter is selected by the S

MUX. Data will fall through from the selected register, through

the S MUX and the Barrel Shifter to the shifter output register

file in 100ns.

The Barrel Shifter instructions are latched, such that the

instructions will not start executing until the rising edge of CLK

latches the instruction into the device.

The Barrel Shifter is capable of Logical Arithmetic or Barrel

Shifts in either direction.

A. Logical shifts discard bits that exit the 16 bit field and fill

spaces with zeros.

B. Arithmetic shifts discard bits that exit the 16 bit field and

fill spaces with duplicates of the original MSB.

C. Barrel Shifts rotate the 16 bit fields such that bits tha exit

the 16 bit field to the left or right reappear in the vacant

spaces on the right or left.

The amount of shift applied is encoded onto the 4 bit Barrel

Shifter input as illustrated in Table 3. The type of shift and the

amount are determined by the shift control block. The shift

control block (see Fig.3) accepts and decodes the four bit ISO3 instruction. The shift control block contains a priority

encoder and two, user programmable 4 bit registers R1 and

R2.

There are four possible sources of shift value that can be

passed onto the Barrel Shifter, there are:

1. Clearing ALU and Barrel Shifter register files to zero.

2. Clearing A and B port input registers to zero.

3. Clearing the R1 and R2 shift control registers to zero.

4. Clearing the internally registered CO bit to zero.

5. Programming the BFP flag to detect

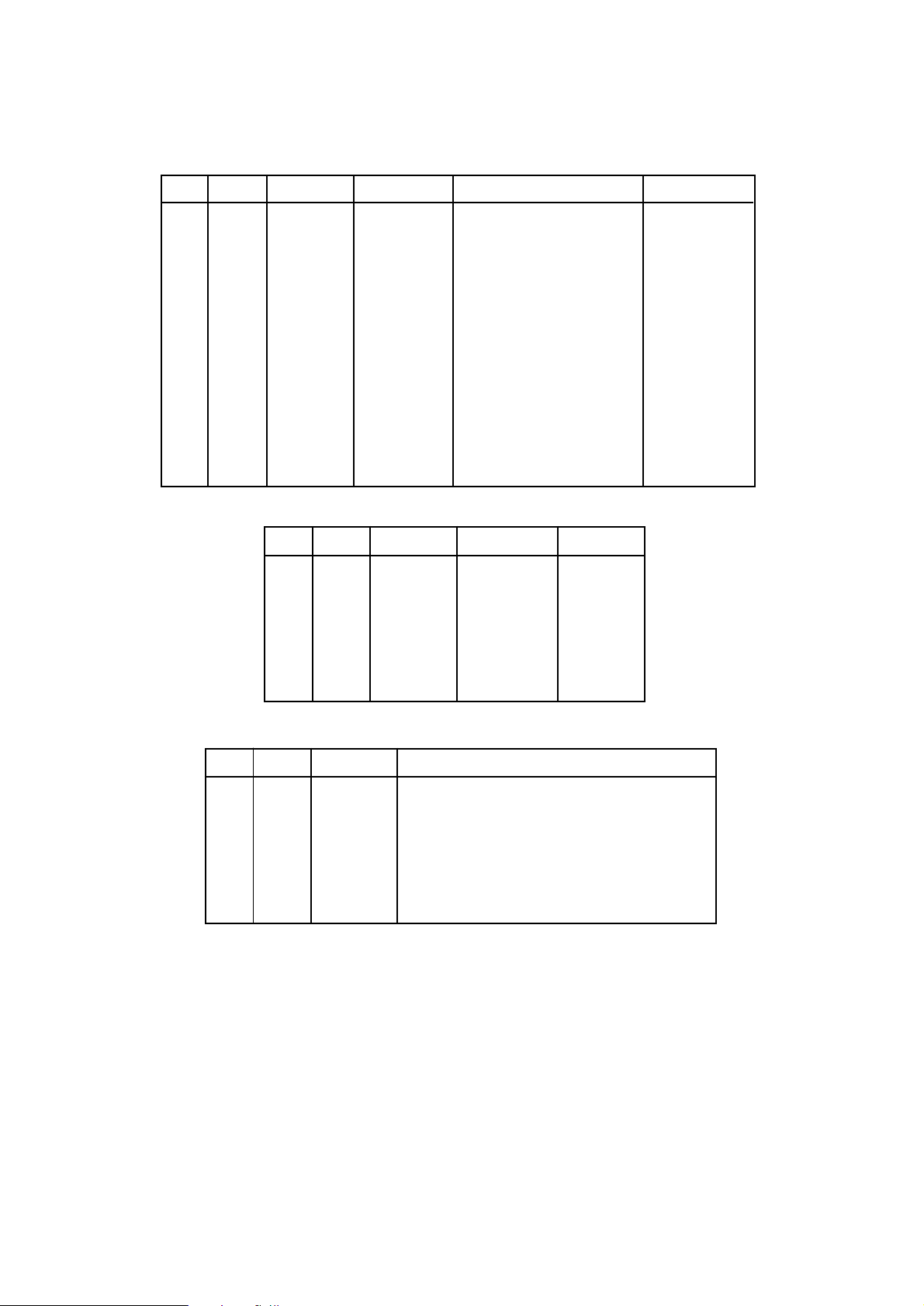

Inst

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

overflow

IS3-IS0

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

conditions.

Mnemonic

LSRSV

LSLSV

BSRSV

BSLSV

LSRR1

LSRR2

LSLR1

LSLR2

LR1SV

LR2SV

ASRSV

ASRR1

ASRR1

NRMXX

NRMR1

NRMR2

Table 2 Barrel shifter instructions

KEY

SV = Shift Value

R1 = Register 1

R2 = Register 2

PE = Priority Encoder Output

I => SV Port operates as an Input

O => SV Port operates as an Output

X => SV Port in a High Impedance State

1. The Priority Encoder

2. The SV input

3. The R1 register

4. The R2 register

Operation

Logical Shift Right by SV

Logical Shift Left by SV

Barrel Shift Right by SV

Barrel Shift Left by SV

Logical Shift Right by R1

Logical Shift Left by R1

Logical Shift Right by R2

Logical Shift Left by R2

Load Register 1 From SV

Load Register 2 From SV

Arithmetic Shift Right by SV

Arithmetic Shift Right by R1

Arithmetic Shift Right by R2

Normalise Output PE

Normalise Output PE, Load R1

Normalise Output PE, Load R2

MNEMONICS

LSXYY Logical Shift, X = Direction YY = Source of Shift Value

BSXYY Barrel Shift, X = Direction YY = Source of Shift Value

ASXYY Arithmetic Shift, X = Direction YY = Source of Shift Value

LXXYY Load XX = Target YY = Source

NRMYY Normalise by PE, Output PE value on SV Port, Load YY Reg

I/O

I

I

I

I

X

X

X

X

I

I

I

X

X

O

O

O

5

PDSP1601 MC

SV3

SV2

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

SV1

SV0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

Shift

No shift

1 place

2 places

3 places

4 places

5 places

6 places

7 places

8 places

9 places

10 places

11 places

12 places

13 places

14 places

15 places

Table 3 Barrel shifter codes

Priority Encoder

If the priority encoder is selected as the source of the shift

value (instructions:- NRMXX, NRMR1, MRMRZ), then within

one 200ns cycle or two 100ns cycles, the shift circuitry will:

(1) Priority encode the 16 bit input to the Barrel Shifter and

place the 4 bit value in either of the R1 or R2 registers and

output the value on the SV port (if enabled by

SVOE).

(2) Shift the 16 bit input by the amount indicated by the

Priority Encoder such that the output from the Barrel Shifter is

a normalised value.

SV Input

If the SV port is selected as the source of the shift value,

then the input to the Barrel Shifter is shifted by the value stored

in the internal SV register.

SVOESVOE

SVOE

SVOESVOE

The SV port acts as an input or an output depending upon

the IS0-3 instruction. If the user does not wish to use the

normalise instructions, then the SV port mat be forced to be

input only by typing SVOE control high. In this mode the SV

port may be considered an extension of the instruction inputs.

R1 and R2 Registers

The R1 and R2 registers may be loaded from the Priority

Encoder (NRMR1 and NRMR2) or from the SV input (LR1SV,

LR2SV).

Whilst the latter two instructions are executing, the Barrel

Shifter will pass its input to the output unshifted.

16

INSTRUCTION

PRIORITY ENCODER

4

MUX

MUX

R1

MUX

R2

DECODE

4

IS0-3

4

SV

SVOE

Fig.3 Shift control block

6

Loading...

Loading...