MITEL MT91L62AN, MT91L62AE, MT91L62AS Datasheet

2

ISO

-CMOS

MT91L62

3 Volt Single Rail Codec

Advance Information

Features

• Single 2.7-3.6 volt supply

• Programmable µ−law/A-law Codec and filters

• Fully differential to output driver

• SSI digital interface

• Individual transmit and receive mute controls

• 0dB gain in receive path

• 6dB gain in transmit path

• Low power operation

• ITU-T G.714 compliant

Applications

• Cellular radio sets

• Local area communications stations

• Line cards

• Battery operated equipment

DS5179 ISSUE 4 August 1999

Ordering Information

MT91L62AE 20 Pin Plastic DIP (300 mil)

MT91L62AS 20 Pin SOIC

MT91L62AN 20 Pin SSOP

-40°C to +85°C

Description

The MT91L62 3V single rail Codec incorporates a

built-in Filter/Codec, transmit anti-alias filter, a

reference voltage and bias source. The device

supports both A-law and µ-law requirements. The

MT91L62 is a true 3V device employing a fully

differential architecture to ensure wide dynamic

range.

An analog output driver is provided, capable of

driving a 20k ohm load.

The MT91L62 is fabricated in Mitel's ISO2-CMOS

technology ensuring low power consumption and

high reliability.

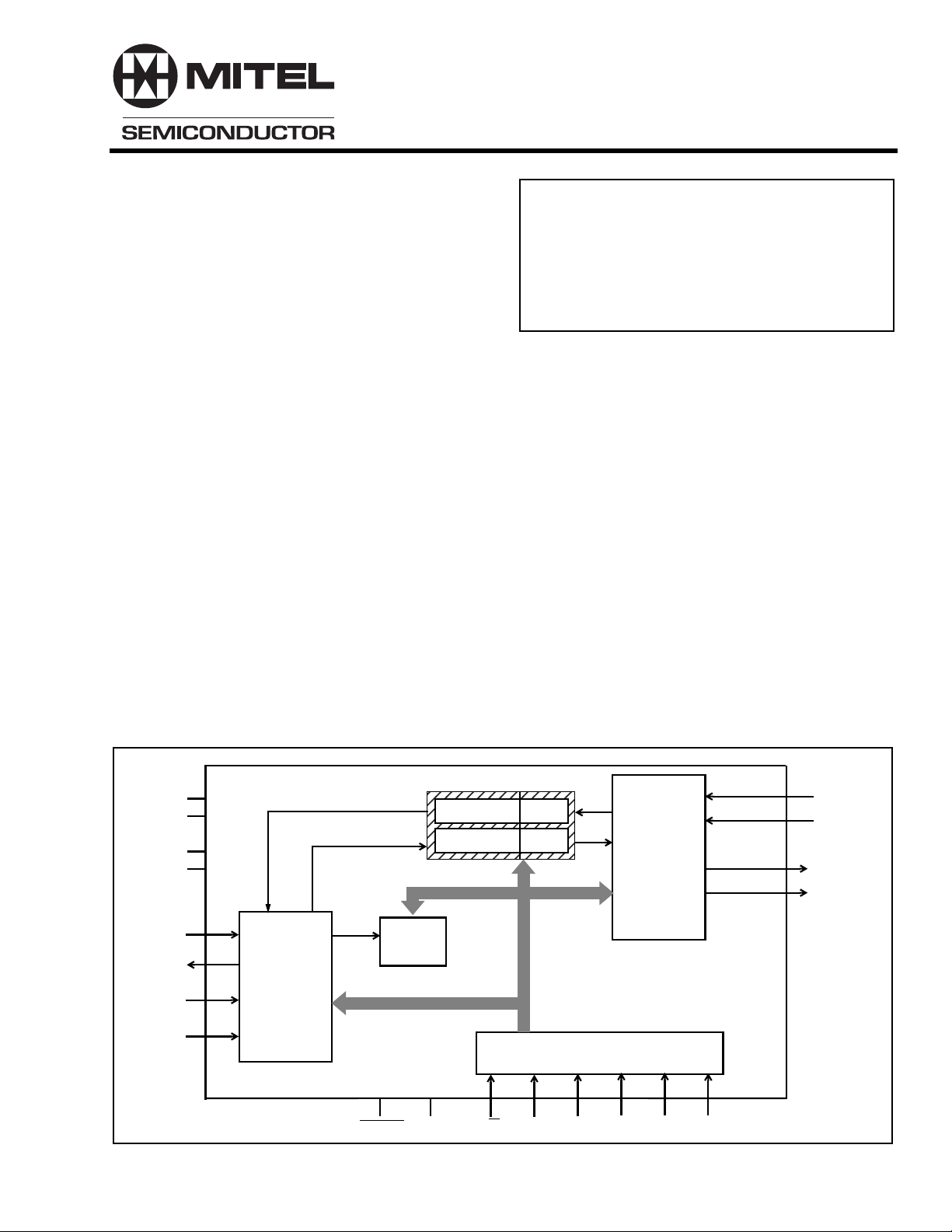

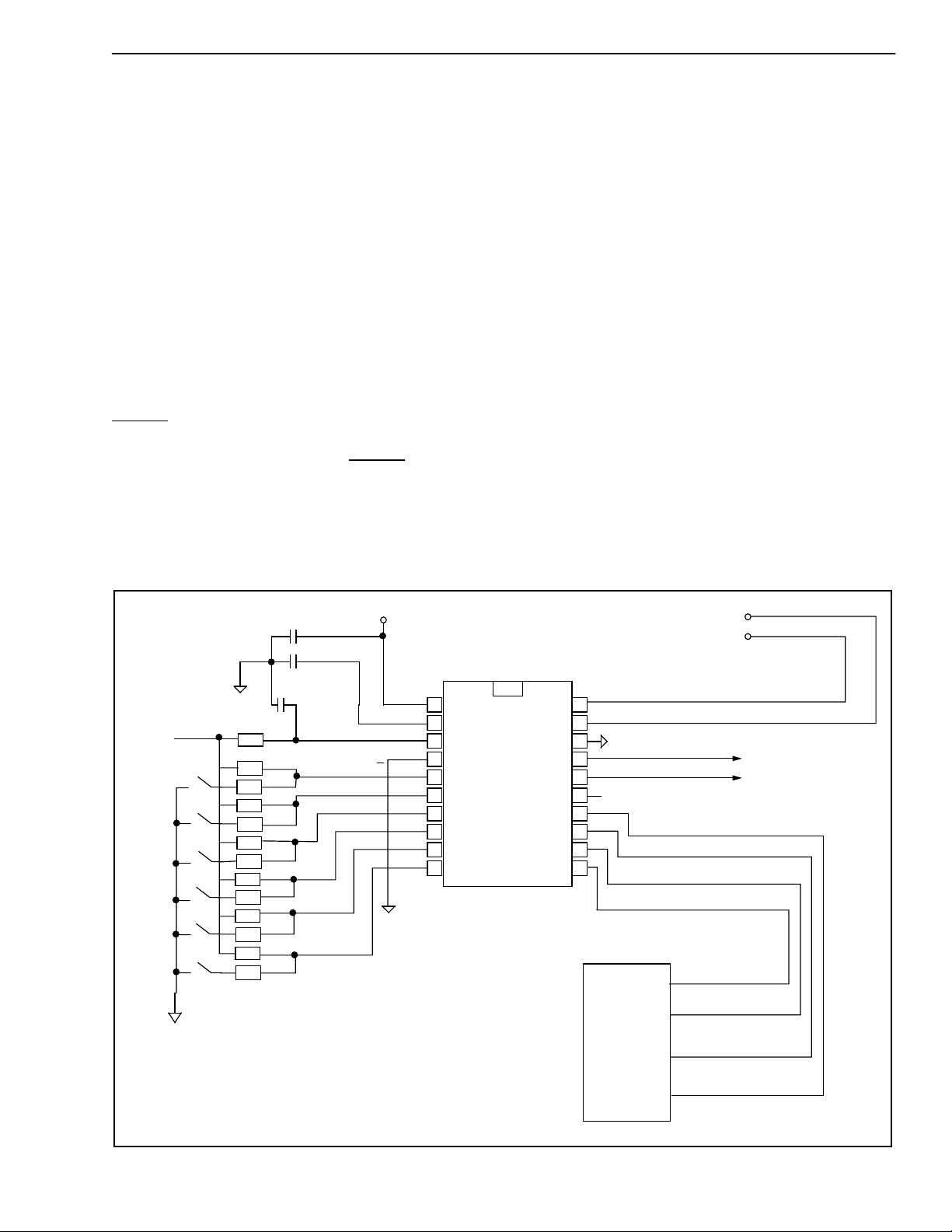

VDD

VSSA

VBias

VRef

Din

Dout

STB

CLOCKin

PCM

Serial

Interface

FILTER/CODEC GAIN

PWRST

Timing

IC

ENCODER

DECODER

A/µ CSL0 CSL1 CSL2 RXMute TXMute

6dB

0 dB

Control

Figure 1 - Functional Block Diagram

Analog

Interface

AIN+

AIN-

AOUT +

AOUT -

7-173

MT91L62 Advance Information

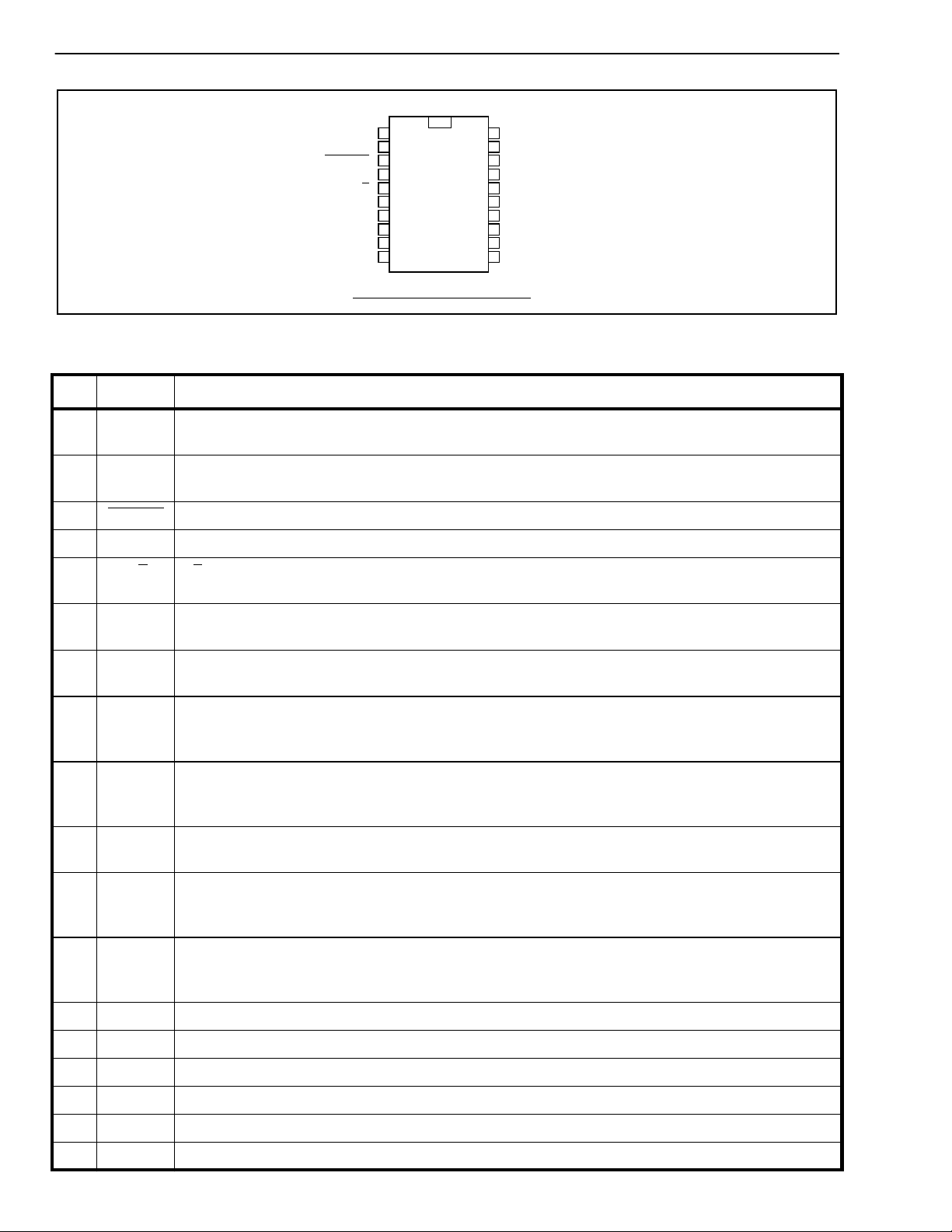

VBias

VRef

PWRST

A/

RXMute

TXMute

CSL0

CSL1

CSL2

1

2

3

4

IC

5

µ

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

AIN+

AINVSS

AOUT +

AOUT VDD

CLOCKin

STB

Din

Dout

20 PIN PDIP/SOIC/SSOP

Figure 2 - Pin Connections

Pin Description

Pin # Name Description

13 V

14 V

Bias

Ref

15 PWRST Power-up Reset. Resets internal state of device via Schmitt Trigger input (active low).

16 IC Internal Connection. Tie externally to VSS for normal operation.

17 A/µ A/µ Law Selection. CMOS level compatable input pin gov erns the companding law used by the

Bias Voltage (Output). (VDD/2) volts is available at this pin for biasing external amplifiers.

Connect 0.1 µ F capacitor to VSS.

Reference Voltage for Codec (Output). Nominally [(VDD/2)-1.1] volts. Used internally.

Connect 0.1 µ F capacitor to VSS.

device. A-law selected when pin tied to VDDor µ-law selected when pin tied to VSS.

18 RXMute Receive Mute. When 1, the transmit PCM is forced to negative zero code. When 0, normal

operation. CMOS level compatable input.

19 TXMute Transmit Mute. When 1, the transmit PCM is forced to negative zero code. When 0, normal

operation. CMOS level compatable input.

20

21

22

23 D

CSL0

CSL1

CSL2

out

Clock Speed Select. These pins are used to program the speed of the SSI mode as well as the

conversion rate between the externally supplied MCL clock and the 512 KHz clock required by a

filter/codec. Refer to Table 2 for details. CMOS level compatable input.

Data Output. A tri-state digital output for 8-bit wide channel data being sent to the Layer 1

device. Data is shifted out via the pin concurrent with the rising edge of BCL during the timeslot

defined by STB.

24 D

Data Input. A digital input for 8-bit wide data from the layer 1 device. Data is sampled on the

in

falling edge of BCL during the timeslot defined by STB. CMOS level compatable input.

13 STB Data Strobe. This input determines the 8-bit timeslot used by the device for both transmit and

receive data. This active high signal has a repetition rate of 8 kHz. CMOS level compatable

input.

14 CLOCKin Clock (Input). The clock provided to this input pin is used by the internal device functions.

Connect bit clock to this pin when it is 512 kHz or greater. Connect a 4096 kHz clock to this pin

when the bit clock is 128 kHz or 256 kHz. CMOS level compatable input.

15 V

Positive Power Supply. Nominally 3 volts.

DD

16 AOUT- Inverting Analog Output. (balanced).

17 AOUT+ Non-Inverting Analog Output. (balanced).

18 V

Ground. Nominally 0 volts.

SS

19 Ain- Inverting Analog Input. No external anti-aliasing is required.

20 Ain+ Non-Inverting Analog Input. Non-inverting input. No external anti-aliasing is required.

7-174

Advance Information MT91L62

Overview

The 3V Single-Rail Codec features complete Analog/

Digital and Digital/Analog conversion of audio

signals (Filter/Codec) and an analog interface to a

standard analog transmitter and receiver (analog

Interface). The receiver amplifier is capable of

driving a 20k ohm load.

Functional Description

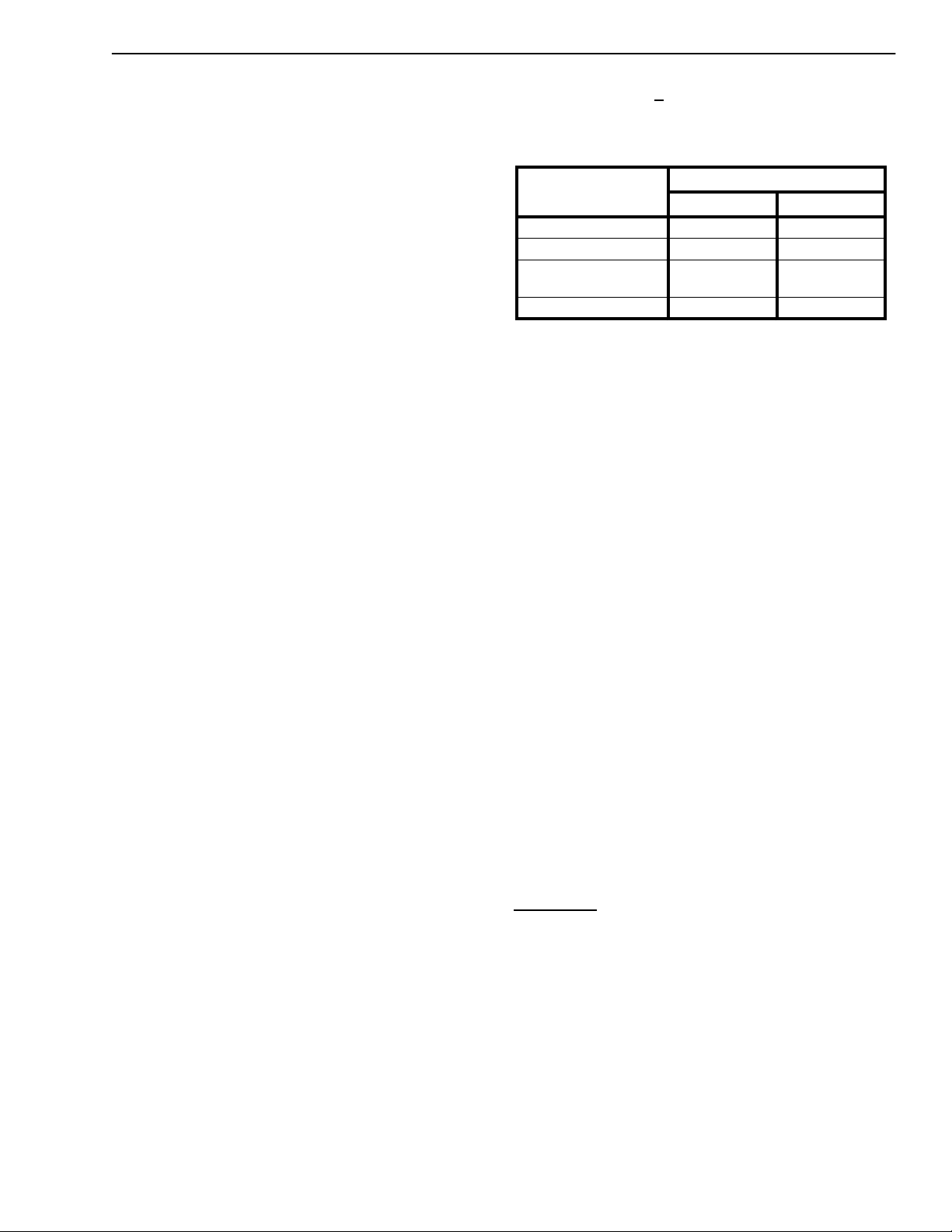

Filter/Codec

The Filter/Codec block implements conversion of the

analog 0-3.3 kHz speech signals to/from the digital

domain compatible with 64 kb/s PCM B-Channels.

Selection of companding curves and digital code

assignment are programmable. These are ITU-T

G.711 A-law or µ-Law, with true-sign/Alternate Digit

Inversion.

The Filter/Codec block also implements a transmit

audio path gain in the analog domain. Figure 3

depicts the nominal half-channel for the MT91L62.

The internal architecture is fully differential to provide

the best possible noise rejection as well as to allow a

wide dynamic range from a single 3 volt supply

design. This fully differential architecture is

continued into the Analog Interface section to

provide full chip realization of these capabilities for

the external functions.

A reference voltage (V

requirements of the Codec section, and a bias

voltage (V

), for biasing the internal analog

Bias

sections, are both generated on-chip. V

brought to an external pin so that it may be used for

biasing external gain setting amplifiers. A 0.1µF

capacitor must be connected from V

ground at all times. Likewise, although V

be used internally, a 0.1µF capacitor from the V

pin to ground is required at all times. The analog

ground reference point for these two capacitors must

be physically the same point. To facilitate this the

V

Ref

and V

pins are situated on adjacent pins.

Bias

The transmit filter is designed to meet ITU-T G.714

specifications. An anti-aliasing filter is included. This

is a second order lowpass implementation with a

corner frequency at 25 kHz.

), for the conversion

Ref

is also

Bias

to analog

Bias

may only

Ref

Ref

Companding law selection for the Filter/Codec is

provided by the A/

µ companding control pin. Table

1 illustrates these choices.

ITU-T (G.711)

Code

µ-Law A-Law

+ Full Scale 1000 0000 1010 1010

+ Zero 1111 1111 1101 0101

-Zero

(quiet code)

- Full Scale 0000 0000 0010 1010

0111 1111 0101 0101

Table 1: Law Selection

Analog Interfaces

Standard interfaces are provided by the MT91L62.

These are:

• The analog inputs (transmitter), pins AIN+/AIN-.

The maximum peak to peak input is 2.123Vpp

µ−law across AIN+/AIN- and 2.2Vpp A-law

across these pins.

• The analog outputs (receiver), pins AOUT+/

AOUT-.This internally compensated fully

differential output driver is capable of driving a

load of 20k ohms.

PCM Serial Interface

A serial link is required to transport data between the

MT91L62 and an external digital transmission

device. The MT91L62 utilizes the strobed data

interface found on many standard Codec devices.

This interface is commonly referred to as Simple

Serial Interface (SSI).

The bit clock rate is selected by setting the CSL2-0

control pins as shown in Figure 2.

Quiet Code

The PCM serial port can be made to send quiet code

to the decoder and receive filter path by setting the

RxMute pin high. Likewise, the PCM serial port will

send quiet code in the transmit path when the

The receive filter is designed to meet ITU-T G.714

specifications. Filter response is peaked to

compensate for the sinx/x attenuation caused by the

8 kHz sampling rate.

7-175

MT91L62 Advance Information

In SSI mode the MT91L62 supports only B-Channel

operation. Hence, in SSI mode transmit and receive

B-Channel data are always in the channel defined by

the STB input.

CSL

CSL1CSL

2

0

External

Clock Bit

Rate

(kHz)

CLOCKin

(kHz)

1 0 0 128 4096

1 0 1 256 4096

0 0 0 512 512

0 0 1 1536 1536

0 1 0 2048 2048

0 1 1 4096 4096

Table 2: Bit Clock Rate Selection

TxMute pin is high. When either of these pins are low

their respective paths function normally. The -Zero

entry of Table 1 is used for the quiet code definition.

SSI Mode

The SSI BUS consists of input and output serial data

streams named Din and Dout respectively, a Clock

input signal (CLOCKin), and a framing strobe input

(STB). A 4.096 MHz master clock is also required for

SSI operation if the bit clock is less than 512 kHz.

The timing requirements for SSI are shown in

Figures 5 & 6.

The data strobe input STB determines the 8-bit

timeslot used by the device for both transmit and

receive data. This is an active high signal with an 8

kHz repetition rate.

SSI operation is separated into two categories based

upon the data rate of the available bit clock. If the bit

clock is 512 kHz or greater then it is used directly by

the internal MT91L62 functions allowing

synchronous operation. If the available bit clock is

128 kHz or 256 kHz, then a 4096 kHz master clock is

required to derive clocks for the internal MT91L62

functions.

Applications where Bit Clock (BCL) is below 512 kHz

are designated as asynchronous. The MT91L62 will

re-align its internal clocks to allow operation when

the external master and bit clocks are asynchronous.

Control pins CSL2, CSL1 and CSL0 are used to

program the bit rates.

For synchronous operation, data is sampled from

Din, on the falling edge of BCL during the time slot

defined by the STB input. Data is made available, on

Serial Port

PCM

D

in

PCM

D

out

Decoder

Encoder

Filter/Codec and Analog Interface

Default Bypass

Receive

Filter Gain

0 dB

Transmit Gain

6 dB

Internal To Device

0 dB

Receiver

Driver

Aout +

Aout-

AIN+

AIN-

External To Device

20kΩ

Analog

Input

7-176

Figure 3 - Audio Gain Partitioning

Advance Information MT91L62

Dout, on the rising edge of BCL during the time slot

defined by the STB input. Dout is tri-stated at all

times when STB is not true. If STB is valid, then quiet

code will be transmitted on Dout during the valid

strobe period. There is no frame delay through the

PCM serial circuit for synchronous operation.

For asynchronous operation Dout and Din are as

defined for synchronous operation except that the

allowed output jitter on Dout is larger. This is due to

the resynchronization circuitry activity and will not

affect operation since the bit cell period at 128 kb/s

and 256 kb/s is relatively large. There is a one frame

delay through the PCM serial circuit for

asynchronous operation. Refer to the specifications

of Figures 5 & 6 for both synchronous and

asynchronous SSI timing.

PWRST

While the MT91L62 is held in PWRST no device

control or functionality is possible.

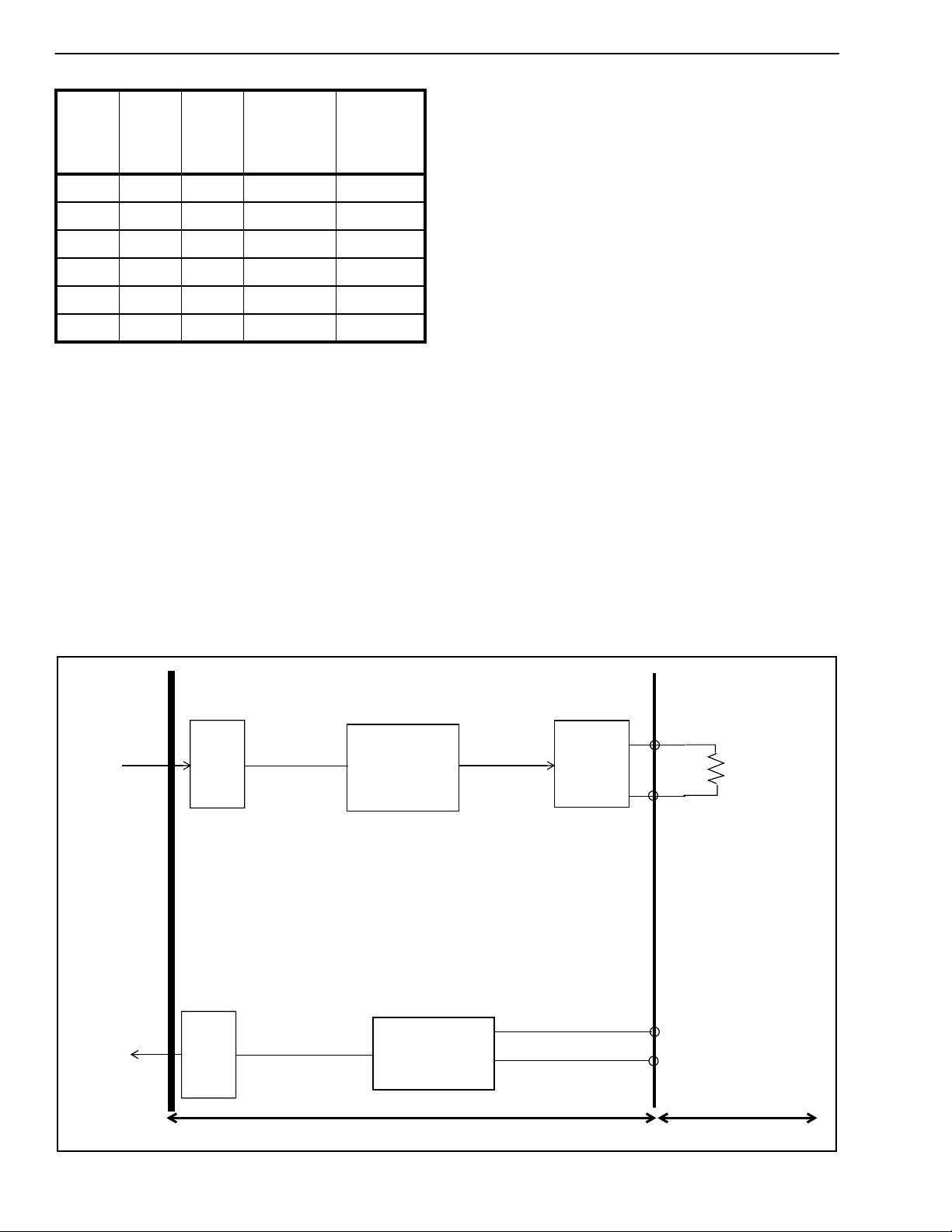

Applications

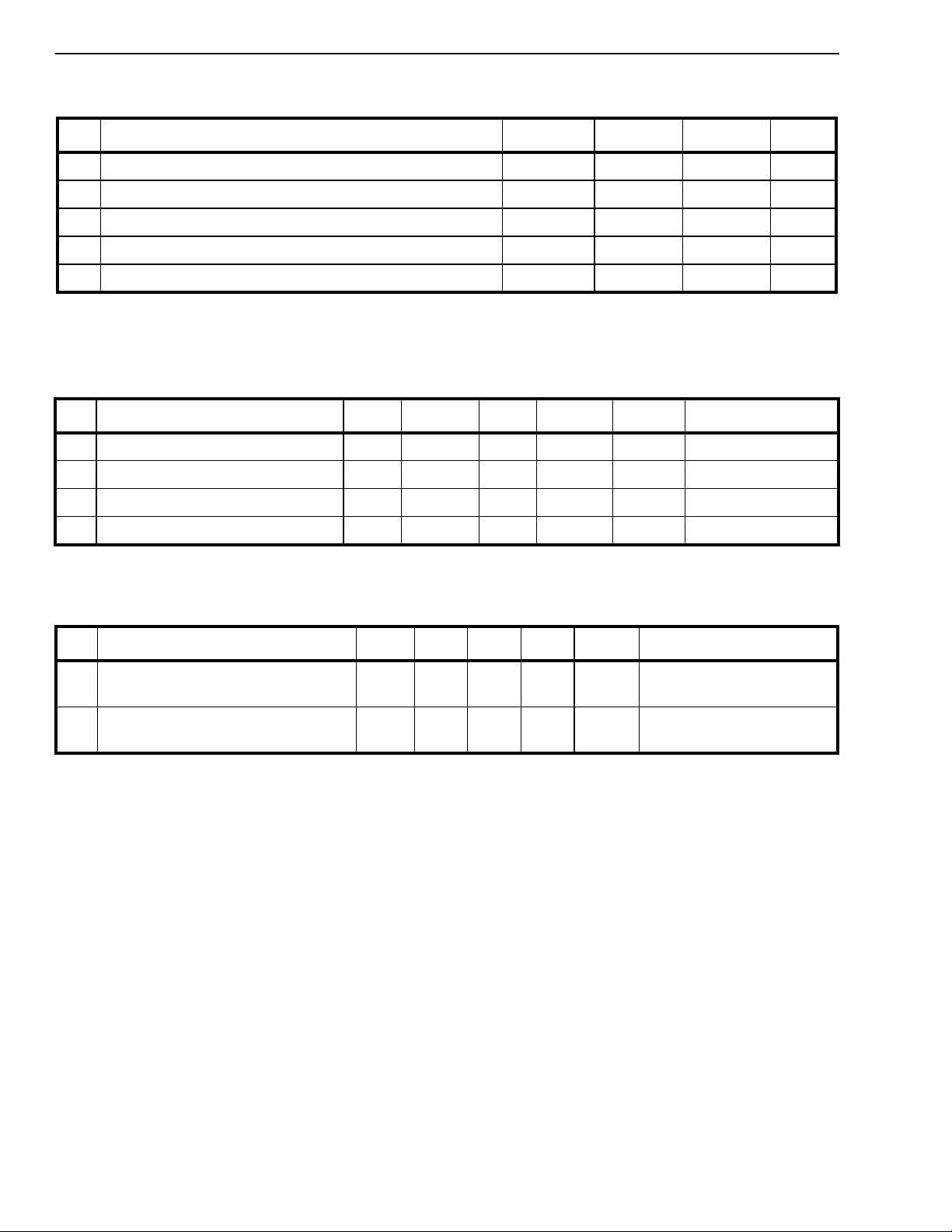

Figure 4 shows an application of the MT91L62 in a

line card.

+3V

0.1 µF

100k

100k

1k

100k

1k

100k

1k

100k

1k

100k

1k

100k

1k

0.1 µF

0.1 µF

CS0

CS1

CS2

VBias

A/µ

RxMUTE

TxMUTE

1

2

3

4

MT91L62

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Input from Subscriber

Line Interface

Output to Subscriber

Line Interface

+3V

Din

Dout

Timing

Frame Pulse

Block

Clock

Figure 4 - Line Card Application

7-177

MT91L62 Advance Information

Absolute Maximum Ratings

†

Parameter Symbol Min Max Units

1 Supply Voltage VDD - V

2 Voltage on any I/O pin VI/V

3 Current on any I/O pin (transducers excluded) II/I

4 Storage Temperature T

5 Power Dissipation (package) P

†

Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

Recommended Operating Conditions - Voltages are with respect to V

SS

O

O

S

D

SS

- 0.3 5 V

VSS - 0.3 VDD + 0.3 V

- 65 + 150 °C

unless otherwise stated

Characteristics Sym Min Typ Max Units Test Conditions

1 Supply Voltage V

2 CMOS Input Voltage (high) V

3 CMOS Input Voltage (low) V

4 Operating Temperature T

DD

IHC

ILC

A

2.7 3 3.6 V

0.9*V

V

SS

DD

V

DD

0.1*V

DD

- 40 + 85 °C

V

V

± 20 mA

750 mW

Power Characteristics

Characteristics Sym Min Typ Max Units Test Conditions

1 Static Supply Current (clock

disabled)

2 Dynamic Supply Current:

Total all functions enabled

Note 1: Power delivered to the load is in addition to the bias current requirements.

I

DDC1

I

DDFT

220µA Outputs unloaded, Input

6 10 mA See Note 1.

signals static, not loaded

7-178

Loading...

Loading...