MITEL MT9196AP, MT9196AE, MT9196AS Datasheet

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

A

A

A

A

A

A

A

A

A

A

AAA

AAAA

AAAA

AAAA

AAAA

AAAA

A

A

A

A

A

A

A

A

A

A

A

ISO2-CMOS

MT9196

Integrated Digital Phone Circuit (IDPC)

Preliminary Information

Features

• Programmable µ-Law/A-Law COD EC an d

Filte rs

• Program mable CCITT (G .711)/sign-magni tude

coding

• Program mab le trans mit , receiv e and si de-t one

gains

• Digital DTMF and single tone generation

• Fully di fferential in terfac e to han dse t

transduce rs

• Auxiliary anal og inte rface

• Interface to ST-BUS/SSI (compatible with GCI)

• Serial mi croport co ntrol

• Single 5 v olt sup ply, low power opera tion

• Anti-how l circ uit fo r group l istenin g

speaker pho ne applic atio ns

Applications

• Digita l telep hone s ets

• Wireles s tel epho nes

• Local area com m unications s t atio ns

ISSUE 3 May 1995

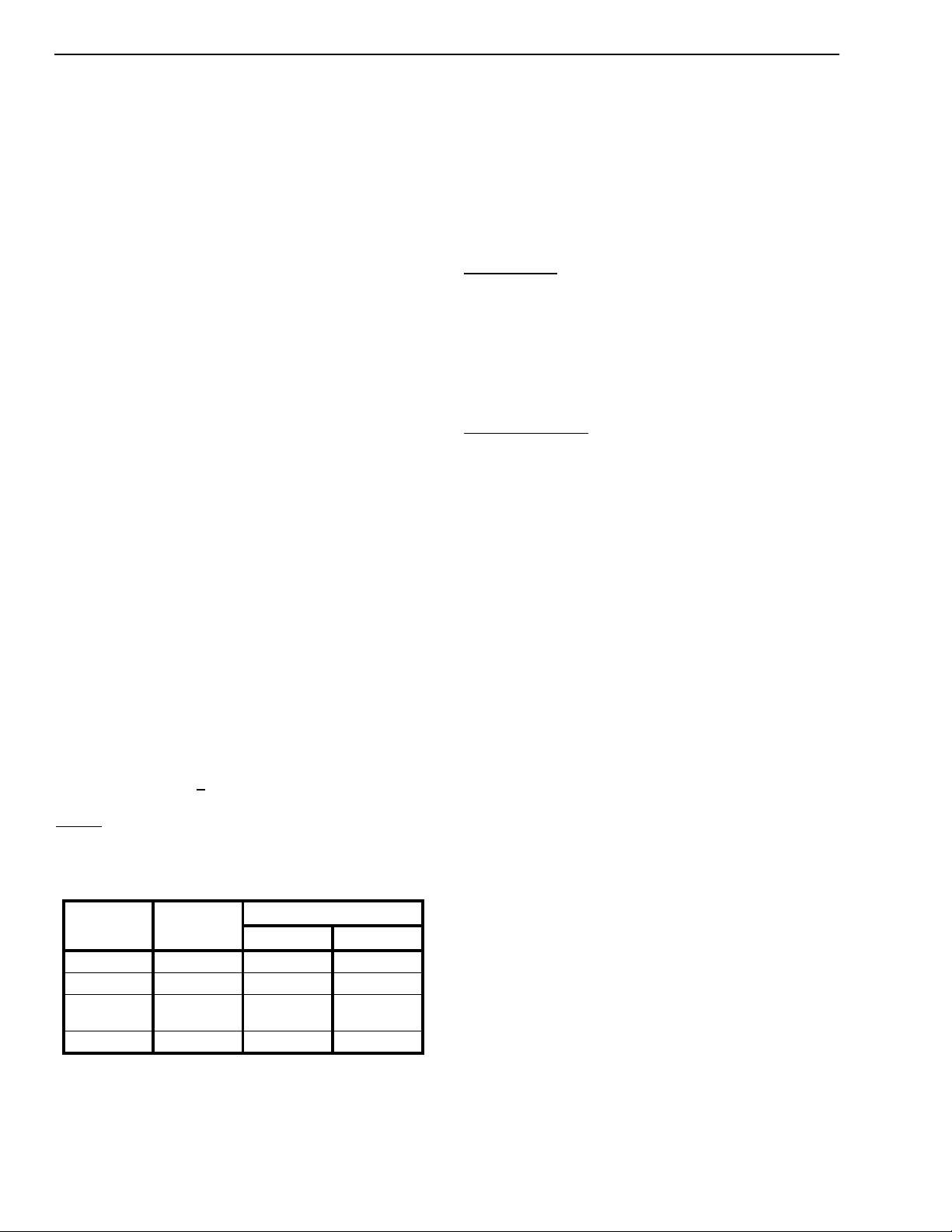

Ordering Information

MT9196AE 28 Pin Plastic D IP

MT9196AP 28 Pin Plastic LCC

MT9196AS 28 Pin SOIC

-40°C to +85°C

Description

The MT9196 Integrated Digital Phone Circuit (IDPC)

is designed for use in digital phone products. The

device incorporates a built-in Filter/Codec, digital

gain pads, DTMF generator and tone ringer.

Complete telephony interfaces are provided for

connecting to handset and speakerphone

transducers. Internal register access is provided

through a serial microport compatible with various

industry standard micro-controllers.

2

The device is fabricated in Mitel's ISO

technology ensuring low power consumption and

high reliability.

-CMOS

VSS SPKR

STB/F0i

CLOCKin

VSSD

VDD

VSSA

VBias

VRef

Din

Dout

XSTL2

Digital Gain &

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

Tone Generator

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

21/ - 24dB

AAAA

AAAA

AAAA

AAAA

∆3.0dB

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

Tx & Rx

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

Flexible

Digital

Interface

WD PWRST

Filter/Code c Gain

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

Encoder

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

Decoder

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

7dB

-7dB

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

Transducer

Interface

Timing

ST-BUS

C & D

Channels

Serial Microport

IC CS DATA1 DATA2 SCLK

IRQ

Figure 1 - Functional Block Diagram

AUXin

AUXout

MIC +

M M +

HSPKR +

HSPKR SPKR +

SPKR -

7-127

MT9196 Preliminary Information

M-

M+

VBias

432

PWRST

VSSD

SCLK

DATA1

DATA2

5

6

IC

7

8

CS

9

10

11

12 13 14 15 16 17 18

28 PIN PLCC 28 PIN SOIC/PDIP

Pin Description

VRef

WD

1

Din

IRQ

Dout

MIC+

VSSA

STB/F0i

CLOCKin

25

24

23

22

21

20

19

AUXin

262728

XSTAL2

AUXout

VSS SPKR

SPKR+

SPKRHSPKR+

HSPKRVDD

Figure 2 - Pin Connections

M-

M+

VBias

V

R

PWRST

IC

VSSD

CS

SCLK

DATA1

DATA2

WD

IRQ

Dout

1

2

3

4

f

e

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VSSA

MIC+

AUXin

AUXout

VSS SPKR

SPKR+

SPKRHSPKR+

HSPKRVDD

XSTAL2

CLOCKin

STB/F0i

Din

Pin # Name Description

1M-Inverting Microphone (Input). Inverting input t o microphone amp lifier from the handset

microphone.

2M+Non-Inverting Microphone (Input). Non-inverting input to microphone amplifier from the

handset microphone.

3V

4V

Bias

Ref

5 PWRST

6ICInternal Co nne ctio n. Tie externally to V

7V

SSD

8CS

Bias Voltage (Output). (VDD/2) volts is available at this pin for biasing external am plif iers.

Connect 0.1 µF capacitor to V

SSA

.

Reference voltage for cod ec (Outpu t). Nominall y [ (VDD/2)-1.5] volts. Used internally.

Connect 0.1 µF capacitor to V

SSA

.

Power-up Reset (Input). CMOS compat ible inp ut with Schmit t Trigger (active low).

for normal operation.

SS

Digital Groun d. Nomi nally 0 volts.

Chip Select (Input). This input sign al is used to select the device for microport data

transfers. Active low. TTL level compatible.

9SCLKSerial Port Synch ronou s Clo ck (In put). Data clock for microport. TTL level compat ible.

10 DATA1 Bidirectional Serial Data. Port for microprocessor serial data transfer. In Motorola/National

mode of operatio n, this pin become s the data tra nsmi t pin only and data receive is

performed on the DATA2 pin. TTL level compatible input levels.

11 DATA2 Serial Data Receive. In Motorola/Natio nal mo de of operation, this pin is used for dat a

receive to the IDPC. In Intel mode, serial data transmit and rece ive are perform ed on the

DATA1 pin and DATA2 is disconnected. Input level TTL compatib le.

12 WD Watchdog (Output). Watchdog timer output. Active high.

13

14 D

IRQ

out

Interrupt Request (Ope n Drain Output). Low true inte rrupt output to microcontrolle r.

Data Output. A tri-state digital output for 8 bit wide channel dat a being sent to the Layer 1

device. Data is shifted out via this pin concurrent with the rising edge of BCL during the

timeslot define d by STB, or according to sta ndard ST-BUS timing.

15 D

Data Input. A digital input for 8 bit wide channel data received from the Layer 1 device.

in

Data is sampled on the falling edge of BCL during the timeslot defined by STB, or according

to standard ST-BUS timing. Input level is CMOS compatible.

7-128

Preliminary Information MT9196

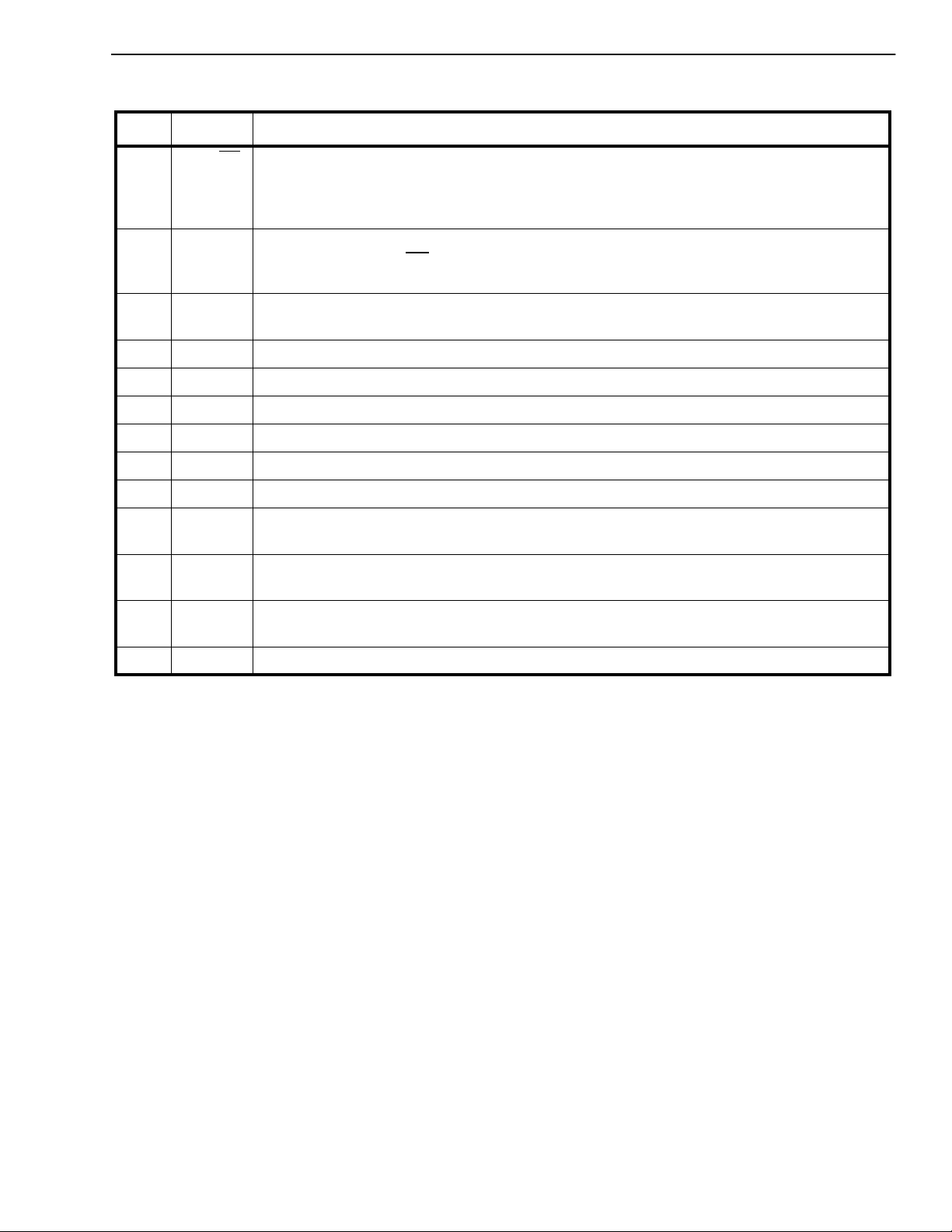

Pin Description (continued)

Pin # Name Description

16 STB/F0i Data Strobe/Frame Pulse (Input). For SSI mode this input determ ines the 8 bit timeslot

used by the device for both transmit and receive d ata. This a ctive high signa l has a

repetition rate of 8 kHz. Standard fram e pulse def init ions apply in ST-BUS mode. CMO S

level compatibl e input .

17 CLOCKin Clock Input. The clock provided to this input is used by the internal phone function s. In ST-

BUS mode this is t he C 4i

SSI-asynchronous mode this is an asynchronous 4 MHz Master Clock input.

18 XSTL2 Crystal Input (4.096 MHz). Used in conjunction with the CLOCKin pin to provide the master

clock signal via external crystal.

input. In SSI synchronous mode , this is the Bit Clock input. In

19 V

Positive Po wer Supply (Inp ut). Nominally 5 volts.

DD

20 HSPKR- Inverting Handset Speaker (Outpu t). Output to the handset speaker (balanced).

21 HSPKR+ Non-Inverting Handset Speaker (Output). O ut put to the handset speaker (balanced).

22 SPKR- In vertin g Speake r (Outpu t). Out put to the speakerphone speaker (balanced).

23 SPKR+ Non-I nver ting Speaker (Outpu t). Output to the speakerphone speaker (balanced).

24 V

25 AUX

SPKR Power Sup ply Rail for Speaker Dri ver. Nominally 0 Volts.

SS

Auxiliary Port (Outp ut). Access point to the D/A (analog) signals of the receive path as

out

well as to the various analog inputs.

26 AUX

Auxiliary Port (Input). An analog signal may be fed to the filter/codec transmit section and

in

various loopback paths via this pin. No external anti-aliasing is required.

27 MIC+ Non-inverting on-hoo k answ er back M icr op hon e (Input). Microphone amplif ier non-

inverting input pin.

28 V

SSA

Analog Gr ou nd (In pu t). Nominally 0 V.

7-129

MT9196 Preliminary Information

Overview

The functional block diagram of Figure 1 depicts the

main operations performed by the MT9196 IDPC.

Each of these functional blocks will be described

individually in the sections to follow. This overview

will describe some of the end-user features which

may be implemented as a direct result of the level of

integration found within the IDPC.

The main feature required of a digital telephone is to

convert the digital Pulse Code Modulated (PCM)

information, be ing rece ived by the telephon e set, into

an analog electrical signal. This signal is then

applied to an appropriate audio transducer such that

the information is finally converted into intelligible

acoustic energy. The same is true of the reverse

direction where acoustic energy is converted first

into an electrical analog and then digitized (into

PCM) before being transmitted from the set. Along

the way if the signals can be manipulated, either in

the analog or the digital domains, other features

such as gain control and signal generation may be

added. Finally, most electro-acoustic transducers

(loudspeakers) require a large amount of power if

they are to develop an acoustic signal. The inclusion

of audio amplifiers to provide this power is required.

The IDPC features complete Analog/Digital and

Digital/Analog conversion of audio signals (Filter/

CODEC) and an analog interface to electro-acoustic

devic es (Tra n sd u ce r In te r f a ce ). Fu l l pro g ra m m a bil i ty

of the receive path and side-tone gains is available

to set comfortable listening levels for the user.

Transmit path gain control is available for setting

nominal transmit levels into the network. A digital,

anti-feedback circuit permits both the handset

microphone and the speaker-phone speaker to be

enabled at the same time for group listening

applications. This anti-feedback circuit limits the

total loop gain there by preventing a singing

condition from developing.

signalling protocol it may be necessary to use inband DTMF signalling to manipulate your personal

answering machine in order to retrieve messages.

Thus the locally generated tones must be of network

quality. The IDPC can generate the required tone

pairs as well as single tones to accommodate any inband signalling requirement.

Each of the programmable parameters within the

functional blocks is accessed through a serial

microcontroller port compatible with Intel MCS-51

Motorola SPI

Microwire

®

®

and National Semiconductor

specifications.

®

Functional Descripti on

In this section each of the functional blocks within

IDPC is described along with all of the associated

control/status bits. Each time a control/status bit(s) is

described it is followed by the address register

where it will be found. The reader is referred to the

section titled 'Register Summary' for a complete

listing of all address registers, the control/status bits

associated with each register and a definition of the

function of each control/status bit. The Register

Summary is useful for future reference of control/

status bits without the need to locate them in the text

of the functional descriptions.

Filter/CODEC

The Filter/CODEC block implements conversion of

the analog 3.3 kHz speech signals to/from the digital

domain compatible with 64 kb/s PCM B-Channels.

Selection of companding curves and digital code

assignment are register programmable. These are

CCITT G.711 A-law or µ-Law, with true-sign/

Alternate Digit Inversion or true-sign/Inverted

Magnitude coding, respectively. Optionally, signmagnitude coding may also be selected for

proprietary applications.

,

Signalling in digital telephone systems, behind the

PBX or standard ISDN applications, is handled on

the D-channel and generally does not require DTMF

tones. Locally generated tones, in the set, however,

can be used to provided “comfort tones” or “key

confirmation” to the user, similar to the familiar

DTMF tones generated by conventional phones

during initial call set-up. Also, as the network slowly

evolves from the dial pulse/DTMF methods to the DChannel protocols it is essential that the older

The Filter/CODEC block also implements transmit

and receive audio path gains in the analog domain.

These gains are in addition to the digital gain pad

section and provide an overall path gain resolution of

1.0dB. A programmable gain, voice side-tone path is

also included to provide proportional transmi t speech

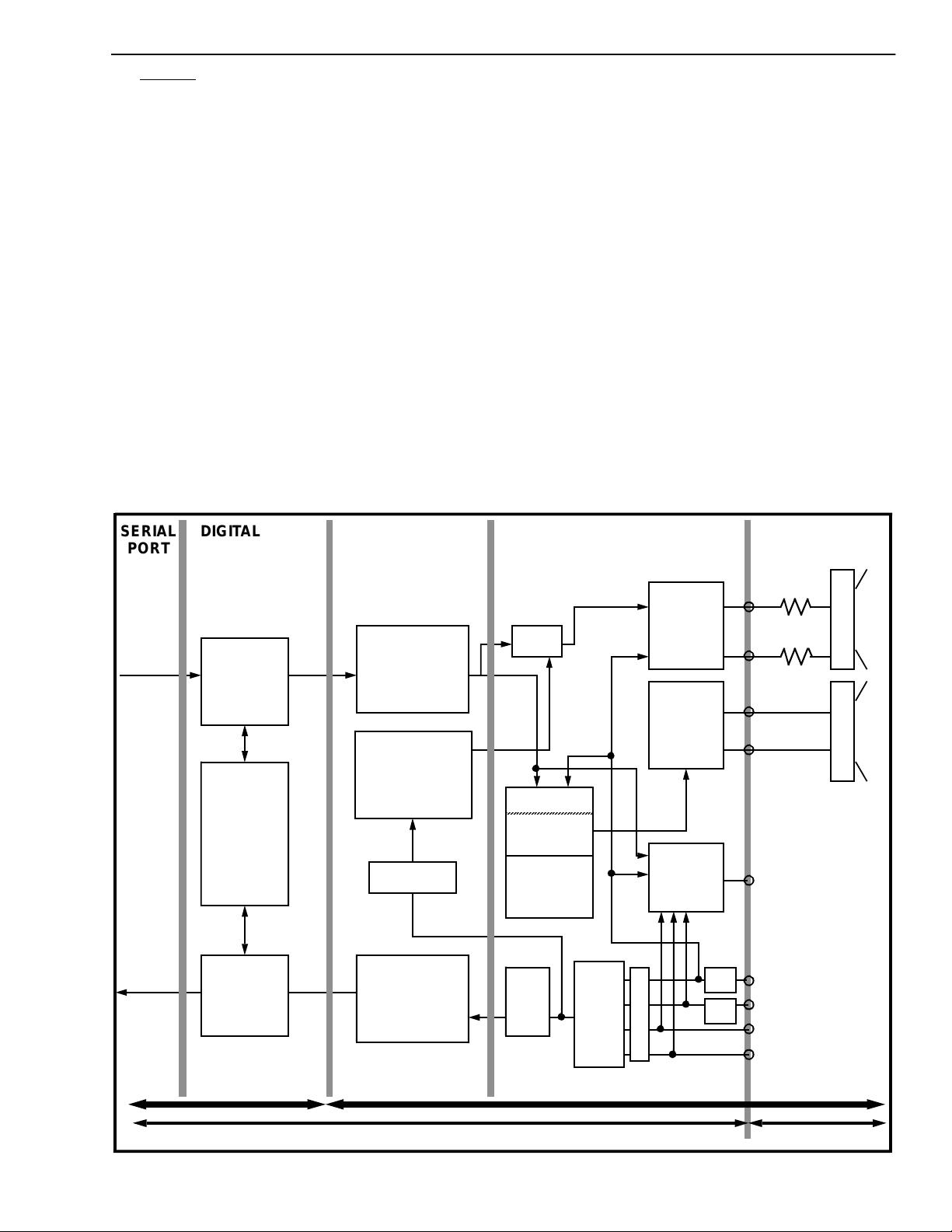

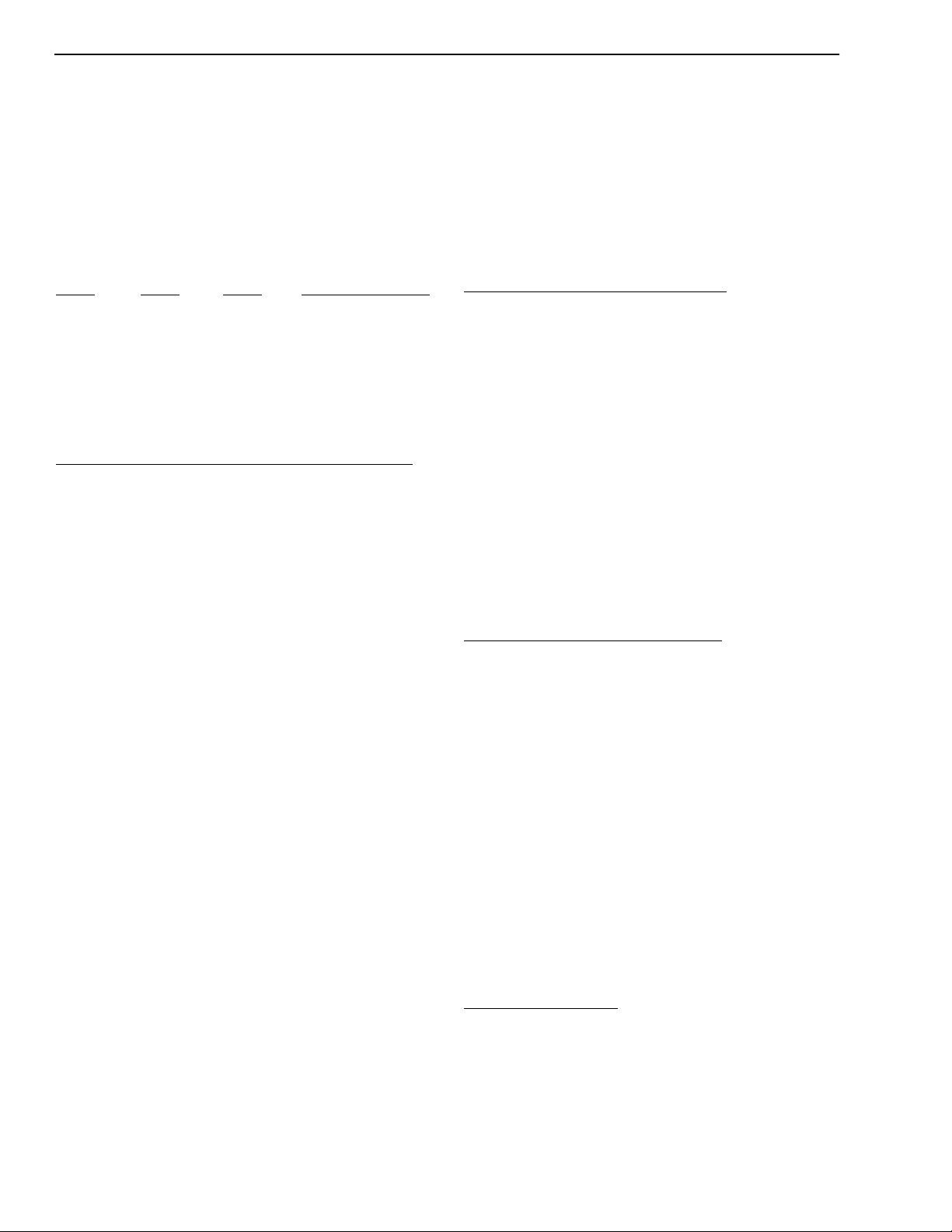

feedback to the handset receiver. Figure 3 depicts

the nominal half-channel and side-tone gains for the

IDPC.

methods be available for backward compatibility. As

an example, once a call has been established (i.e.,

from your office to your home) using the D-Channel

Intel® and MCS-51® are registered trademarks of Intel Corporation

Motorola® and SPI® are registered trademarks of Motorola Corporation

National® and Microwire® are trademarks of National Semiconductor Corporation

7-130

Preliminary Information MT9196

On PWRS T (pin 5) the Filter/CODEC defaults such

that the side-tone path, dial tone filter and 400 Hz

transmit filter are off, all programmable gains are set

to 0dB and CCITT µ-Law is selected. Further, the

Filter/CODEC is powered down due to the control

bits of the Path Control Registers (addresses 12h

and 13h) being reset.

The internal architecture is fully differential to provide

the best possible noise rejection as well as to allow a

wide dynamic range from a single 5 volt supply

design. This fully differential architecture is

continued into the Transducer Interface section to

provide full chip realization of these capabilities for

the handset and loudspeaker functions.

A reference voltage (V

), for the conversion

Ref

requirements of the CODEC section, and a bias

voltage (V

sections, are both generated on-chip. V

), for biasing the internal analog

Bias

Bias

is also

brought to an external pin so that it may be used for

biasing external gain plan setting amplifiers. A 0.1 µF

SERIAL

PORT

PCM

D

in

DIGITAL GAIN

& TONES

Receive

-24 to

+21 dB

(3dB steps)

DTMF,

Tone

Ringe r

FILTER/CODEC TRANSDUCER INTERFACE

Receive

Filter Gain

0 to -7 dB

(1 dB steps)

Side-ton e

-9.9 6 to

+9 96dB

(3.32 dB steps)

-11 dB

capacitor must be connected from V

ground at all times. Likewise, although V

to analog

Bias

may only

Ref

be used internally, a 0.1 µF capacitor from the V

pin to ground is required at all times. The analog

ground reference point for these two capacitors must

be physically the same point. To facilitate this the

V

Ref

and V

pins are situated on adjacent pins.

Bias

The transmit filter is designed to meet CCITT G.714

specifications. The nominal gain for this filter path is

0 dB (gain control = 0 dB). Gain control allows the

output signal to be increased up to 7 dB. An antialiasing filter is included. This is a second order

lowpass implementation with a corner frequency at

25 kHz. Attenuation is better than 32 dB at 256 kHz

and less than 0.01 dB within the passband.

An optional 400Hz high-pass function may be

included into the transmit path by enabling the Tfhp

bit in the Control Register 1 (address 0Eh). This

option allows the reduction of transmitted

background noise such as motor and fan noise.

Handset

Receiver

(150Ω)

75

75

Speakerphone

Speaker

(40Ω nominal)

34Ω min)

-6 dB

0/+8dB

+8 to -20dB

(4 dB steps)

RINGER

0 to -28 dB

(4 dB steps)

-6.1 dB or

-3.6 dB

Receiver

Driver

Speaker

Phone

Driver

0 dB

Auxiliary

Out

Driver

-12 dB

HSPKR +

HSPKR -

SPKR +

SPKR -

AUXout

Ref

PCM

D

out

-24 to

+21 dB

(3 dB steps)

Transmit

Digital Domain Analog Domain

Internal To Device External To Device

Transmit Filter

Gain

0 to +7 dB

(1 dB steps)

Trans-

mit

Gain

-0.37 dB

or 8.93 dB

Trans-

mit

Gain

6.37 dB

M

U

X

Figure 3 - Audio Gain Partitioning

5 dB

5 dB

AUXin

MIC+

M +

Transitter

microphone

M -

AUX input

H/F answer-

back mic

7-131

MT9196 Preliminary Information

The receive filter is designed to meet CCITT G.714

specifications. The nominal gain for this filter path is

0 dB (gain control = 0dB). Gain control allows the

output signal to be attenuated up to 7 dB. Filter

response is peaked to compensate for the sinx/x

attenuation caused by the 8 kHz sampling rate.

The Rx filter function can be altered by enabling the

Dial EN control bit in Control Register 1 (address

0Eh). This causes another low-pass function to be

added with a 3 dB point at 1000 Hz. This function is

intended to improve the sound quality of digitally

generated dial tone received as PCM.

Side-tone is derived from the Tx filter before the LP/

HP filter section and is not subject to the gain control

of the Tx filter section. Side-tone is summed into the

receive handset transducer driver path after the Rx

filter gain control section so that Rx gain adjustment

will not affect side-tone levels. The side-tone path

may be enabled/disabled with the Voice sidetone bit

located in the Receive Path Control Register

(address 13h).

Transmit and receive filter gains are controlled by the

-TxFG2 and RxFG0-RxFG2 control bits,

TxFG

0

respectively. These are located in the FCODEC

Control Register 1 (address 0Ah). Transmit filter gain

is adjustable from 0 dB to +7 dB and receive filter

gain from 0 dB to -7 dB, both in 1 dB increments.

Side-tone filter gain is controlled by the STG

-ST G

0

control bits located in the FCODEC Control Register

2 (address 0Bh). Side-tone gain is adjustable from

-9.96 dB to +9.96 dB in 3.32 dB increments.

Companding law selection for the Filter /CODE C is

provided by the A/µ

companding control bit while

the coding scheme is controlled by the sign-mag/

CCITT

control bit. Both of these reside in Control

Register 2 (address 0Fh). Table 1 illustrates these

choices.

Code

+ Full Scale 1111 1111 1000 0000 1010 1010

+ Zero 1000 0000 1111 1111 1101 0101

-Zero

(quiet code)

- Full Scale 0111 1111 0000 0000 0010 1010

Sign/

Magnitude

0000 0000 0111 1111 0101 0101

CCITT (G.7 11)

µ-Law A-Law

Ta ble 1

Digital Gain and Tone Generation

The Digital gain and Tone generator block is located,

functionally, between the serial FDI port and the

Filter/CODEC block. Its main function is to provide

digital gain control of the transmit and receive audio

signals and to generate digital patterns for DTMF

and tone ringer signals.

Gain Control

Gain control is performed on linear code for both the

receive and the transmit PCM. Gain control is set via

the Digital Gain Control Register at address 19h.

Gain, in 3.0 dB increments, is available within a

range of +21.0 dB to -24 dB.

DTMF Ge nerat or

The digital DTMF circuit generates a dual sine-wave

pattern which may be routed into the receive path as

comfort tones or into the transmit path as network

signalling. In both cases the digitally generated

signal will undergo gain adjustment as programmed

into the transmit and receive gain control registers.

Gain control is assigned automatically as functions

are selected via the transmit and receive path control

registers.

The composite signal output level in the transmit

direction is -4 dBm0 (µ-Law) and -10 dBm0 (A-law)

2

with programmable gains at zero dB. Pre-twist of 2.0

dB is incorporated into the composite signal resulting

in a low tone output level of -8.12 dBm0 and a high

group level of -6.12dBm0 (for µ-Law, 6 dB lower for

A-Law). Note that these levels will be influenced by

the Anti-Howling circuit when it is enabled (see AntiHowling section for more details). DTMF side-tone

levels are se t to - 2 8 dB m0 from the gene ra to r circuit.

Other receive path gains must be included when

calculating the analog output signal levels.

Adjustments to these levels may be made by altering

the settings of the Gain Control register (address

19h).

The frequency of the low group tone is programmed

by writing an 8-bit coefficient into the Low Tone

Coefficient Register (address 1Ah) while the high

group tone frequency uses the 8-bit coefficient

programmed into the High Tone Coefficient Register

(address 1Bh). Both coefficients are determined by

the following equation:

The Filter/CODEC autonull circuit ensures that

transmit PCM will contain no more than ±1 bit of

offset due to i n te rn a l circuitry.

7-132

Frequency (in Hz) = 7.8125 x COEFF

Where COEFF is an integer between 0 and 255.

Frequency resolution is 7.8125 Hz in the range 0 to

1992 Hz.

Preliminary Information MT9196

Low and high tones are enabled individually via the

LoEn and HiEN control bits (DTMF/Ringer Control

Register, address 18h). This not only provides

control over dual tone generation but also allows

single tone generation using either of the enable bits

and its associated coefficient register.

After programming and enabling the tone generators

as described, selection of transmit and/or receive

path destinations are carried out via the Path Control

Registers (see Path Control section). In addition

receive sidetone DTMF must be selected via the

DTMF StEN bit (DTMF/Tone ringer Register, address

18h) so that it replaces the received PCM in the Rx

Filter path.

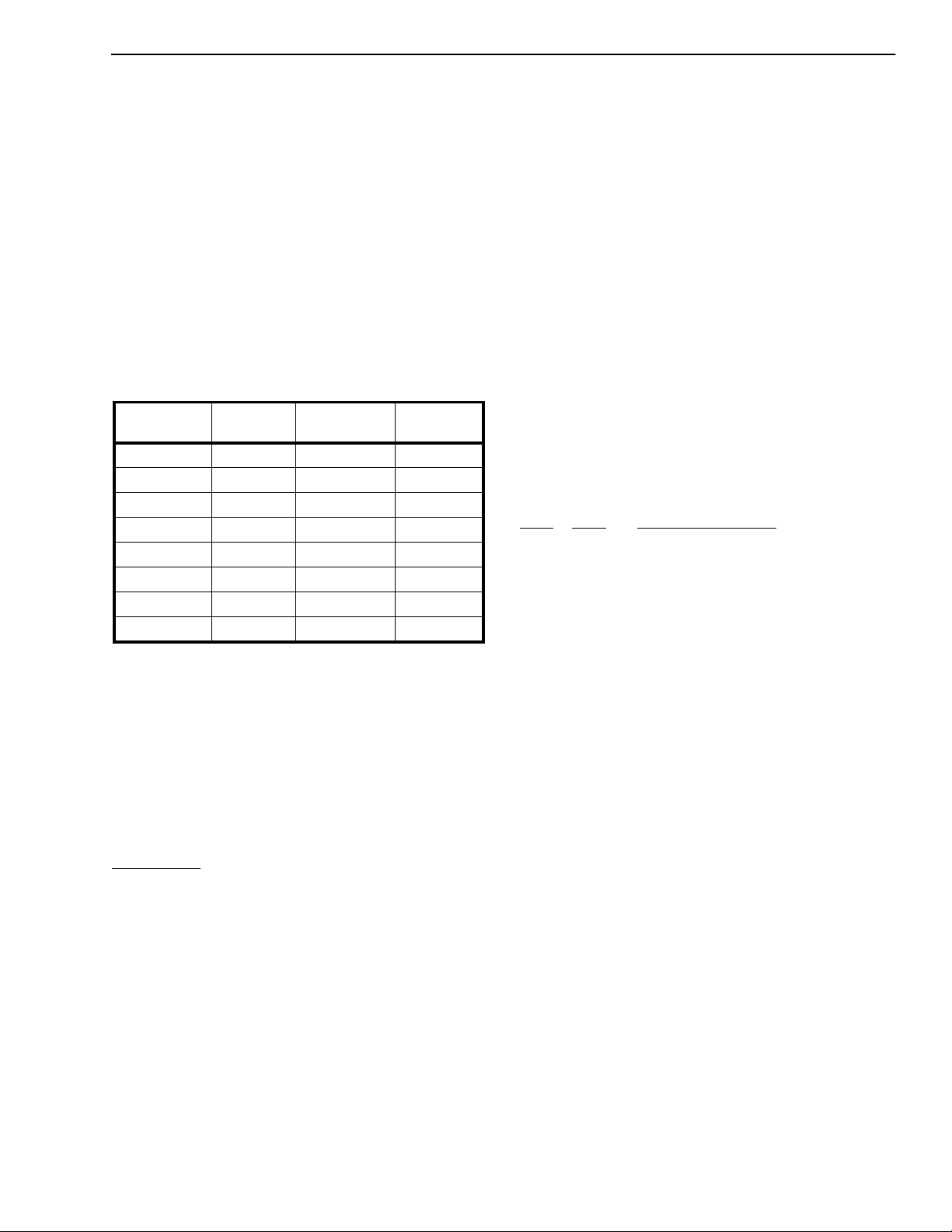

Frequency

(Hz)

COEFF

Actual

Frequency%Deviation

697 59h 695.3 -.20%

770 63h 773.4 +.40%

852 6Dh 851.6 -.05%

941 79h 945.3 +.46%

1209 9Bh 1210.9 +.20%

1336 ABh 1335.9 .00%

1477 BDh 1476.6 -.03%

1633 D1h 1632.8 -.01%

Table 2 - DTMF Frequencies

DTMF Signal to distortion:

The sum of harmonic an d no is e po w er in t he freq uency band

from 50 Hz to 3500 Hz is typically more than 30 dB below the

power in th e ton e pair. All indiv idual ha rm on ic s ar e ty p ic al ly

more th an 4 0 d B b elow the l ev el o f the low group ton e.

Table 2 gives the standard DTMF frequencies, the

coefficient required to generate the closest

frequency, the actual frequency generated and the

percent deviation of the generated tone from the

nominal.

Tone Ring er

A dual frequency squarewave ringing signal may be

applied to the handsfree speaker driver to generate a

call alerting signal. To enable this mode the Ring En

bit (address 18h) must be set as well as the ringer

function to the loudspeaker via the Receive Path

Control Register (address 13h). Ring En is

independent of the DTMF enable control bits (see Lo

EN and Hi EN). Since both functions use the same

coefficient registers they are not usually enabled

simultaneously.

The digital tone generator uses the values

programmed into the low and high Tone Coefficient

Registers (addresses 1Ah and 1Bh) to generate two

different squa rewave freque n cie s.

Both coefficients are determined by the following

equation:

COEFF = [32000/Frequency (Hz)] - 1

where COEFF is an integer between 1 and 255. This

produces frequencies between 125 - 16000 Hz with

a non-linear resolution.

The ringer program switches between these two

frequencies at a 5 Hz or 10 Hz rate as selected by

the WR bit in the DTMF/Tone ringer register (address

18h).

Anti-Howl

IDPC includes an Anti-Howling circuit plus speaker

gain control circuit to allow for group listening

operation. Although this is the main function of the

circuit there are additional modes in which it may be

used as defined by the MS1 and MS0 control bits

(address 1Ch).

MS1

MS0 Op er ati o na l M o d e

0 0 Tx noise reduction (squelch)

0 1 Rx noise reduction (squelch)

1 0 switched loss group listening

(anti-howling)

1 1 Tx/R x s w itch e d los s

The circuit is enabled by setting the Anti-howl Enable

bit (address 1Ch) and selecting the required

operational mode (MS0 & MS1) as described.

For all modes of operation the switching levels and

inserted loss are programmed as follows.

Switching decisions are made by comparing either

the transmit or the receive signal level to threshold

levels stored in the High Threshold Register

(address 1Dh) and the Low Threshold Register

(address 1Eh). Threshold data is encoded in PCM

sign-magnitude format excluding the sign bit. For

example; THh0 - THh3 encode the PCM step

number while THh4 - THh6 encode the PCM chord

number for the high threshold. Similarily for the THl0

- THl6 bits of the low threshold. The difference

between the high and low threshold levels provides

the circuit with hysteresis to prevent uncontrolled

operation. The low level threshold must never be

programmed to a value higher than the one stored in

the high level threshold. If this occurs the circuit will

becom e unsta ble.

Loss is implemented, in the chosen path, by

subtracting the value set by the Pad0 - Pad3 control

bits from the appropriate gain value set by the RxG0

- RxG3 or TxG0 - TxG3 control bits (see Digital Gain

7-133

MT9196 Preliminary Information

Register, address 19h). The minimum digital gain is

limited to -24 dB regardless of the mathematical

result of this operation. The path without loss reverts

to the gain value programmed into the Digital Gain

Register.

The magnitude of the switched loss defaults to 12 dB

on power up but c an be programmed to between 0

and 21 dB using the Pad0 - Pad2 control bits

(address 1Ch).

Pad2

0 0 0 0

0 0 1 3

0 1 0 6

0 1 1 9

1 0 0 12

1 0 1 15

1 1 0 18

1 1 1 21

Switched Loss fo r Group L isten ing (a nti-h owling)

Group listening is defined as a normal handset

conversation with received speech also directed to

the loudspeaker for third party observation. In this

mode, if the handset microphone is moved into close

proximity of the loudspeaker a feedback path will

occur resulting in a singing connection. To prevent

this the anti-howling circuit introduces a switched

loss into either the transmit or receive paths

dependent upon the transmit path speech activity.

Pad1 Pad0 Attenuation (dB)

comfortable group listening level after the handset

user has adjusted their listening level as required.

Since the anti-howling circuit has dynamic control

over the transmit and receive gain control registers,

it is recommended that this function be turned off

momentarily when DTMF tone generation is

required. This will ensure that the proper transmit

levels are attained.

Transmit Noise Reduction (squelch)

The transmit signal may be muted to eliminate

transmission of excessive background noise.

In this mode the signal level in the transmit path is

compared with the high level threshold stored at

address 1Dh. When the transmit signal level

exceeds this threshold no loss is inserted into the

transmit path. After exceeding the high level

threshold the transmit signal level is then compared

to a low level threshold stored at address 1Eh. When

the transmit signal level falls below this threshold the

transmit digital gain is reduced by the programmed

amount (Pad0-2) and comparison reverts back to the

high threshold level. The receive path gain is not

altered by transmit noise reduction.

Receive Noise Reduction (squelch)

Loss switching is determined by comparing the

signal level in the transmit path with the high level

threshold stored at address 1Dh. When the transmit

signal level exceeds this threshold the programmed

loss is s witched from th e tr a n sm it path to th e receive

path. Once switching has occurred the transmit

signal level is then compared to a low level threshold

stored at address 1Eh. When the transmit signal

level falls below this threshold the programmed loss

is switched from the received path back to the

transmit path and comparison reverts back to the

high threshold level.

Since the received digital gain control is used to set

the listening level of the received speech, for both

handset receiver and loudspeaker, it is necessary to

provide additional gain in the loudspeaker path so

that its receive level can be controlled independently

from the receiver out put. T he Gai n0 to Gain3 cont rol

bits (address 0B h) are used to boost the loudspeaker

output to a comfortable listening level for the third

parties in group listening. Generally the Gain3 bit

should be set to logic 1 in this mode. This increases

the gain programmed via the Gain0 - Gain2 bits by a

factor of 8 dB. In group listening a speaker gain

setting of 4 to 16 dB will be required to set a

The receive signal may be muted to eliminate

background noise resulting from a poor trunk

connection.

In this mode the signal level in the receive path is

compared with the high level threshold stored at

address 1Dh. When the receive signal level exceeds

this threshold no loss is inserted into the receive

path. After exceeding the high level threshold the

receive signal level is then compared to a low level

threshold stored at address 1Eh. When the receive

signal level falls below this threshold the receive

digital gain is reduced by the programmed amount

(Pad2-0) and comparison reverts back to the high

threshold level. The transmit path gain is not altered

by receive noise reduction.

Tx/Rx Switched Loss

In this mode the programmed switched loss is

inserted into either the transmit or receive path

dependent only upon activity in the receive path. If

receive path activity is above the programmed high

level threshold then the switched loss is inserted into

the transmit path. If receive path activity is below the

programmed low level threshold then the switched

loss is inserted into the receive path.

7-134

Preliminary Information MT9196

This mode can be used to im plement a loudspeaking

function where the receive audio is routed to the

SPKR± pins and transmit audio is sourced from the

MIC+ pin. In this mode there is no algorithmic

cancellation of echo so it is recommended that this

switched loss program be used only in 4-wire

systems (i. e. , d i gital s e t to d i g ital s e t).

Transducer Interfaces

Four standard telephony transducer interfaces plus

an auxiliary I/O are provided by the IDPC. These are:

➧ The handset microphone inputs (transmitter),

pins M+/M- and the answerback microphone

input MIC+. The nominal transmit path gain

may be adjusted to either 6.0dB or 15.3dB.

Control of this gain is provided by the TxINC

control bit (Control register 2, address 0Fh).

This gain adjustment is in addition to the

programmable gain provided by the transmit

filter and Digital Gain circuit.

➧ The handset speaker outputs (receiver), pins

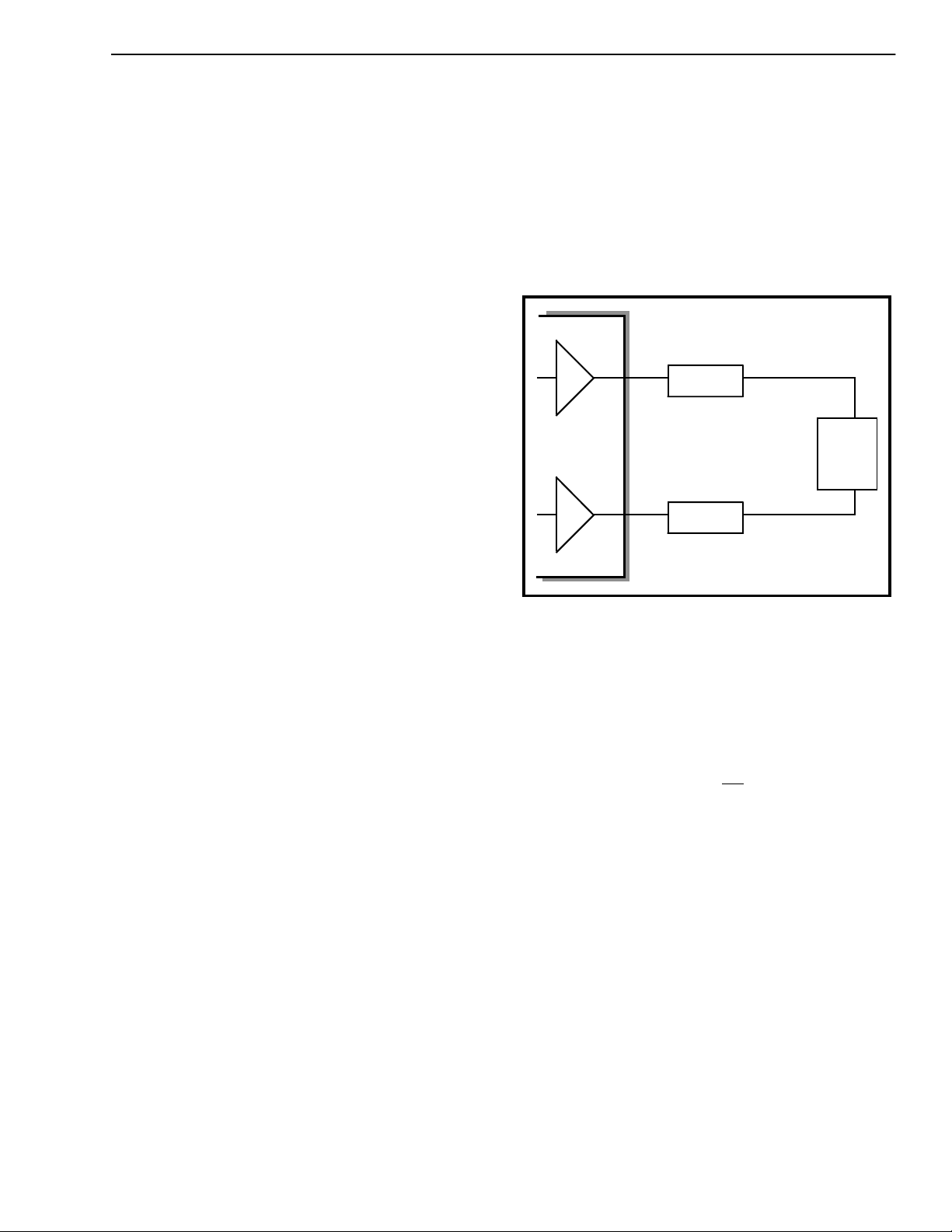

HSPKR+/HSPKR-.Thisinternallycompensated,

fully differential output driver is capable of

driving the load shown in Figure 4. The nominal

handset receive path gain may be adjusted to

either -12.1 dB or -9.6 dB. Control of this gain is

provided by the RxINC control bit (Control

register 2, address 0Fh). This gain adjustment

is in addition to the programmable gain

provided by the receive filter and Digital Gain

circuit.

➧ The loudspeaker outputs, pins SPKR+/SPKR-.

This internally compensated, fully differential

output driver is capable of directly driving 6.5v

p-p into a 40 ohm load.

➧ Auxiliary port path gains are:

AUXin to Dout

Din to AUXout

AUXin to AUXout

AUXin to HSPKR±

AUXin to SPKR±

11 dB

20.3 dB

-12 dB

-7.0 dB

-1.1 dB

1.4 dB

5.0 dB

TxINC=0

TxINC=1

RxINC=0

RxINC=1

Refer to the application diagrams of Figures 10 and

11 for typical connections to this analog I/O section.

HSPKR +

75 Ω

IDPC

75 Ω

HSPKR -

150 ohm

load

(speaker)

Figure 4 - Handset Speaker Driver

Microport

The serial microport, compatible with Intel MCS-51

(mode 0), Motorola SPI (CPOL=0,CPHA=0) and

National Semiconductor Microwire specifications

provides access to all IDPC internal read and write

registers. This microport consists of a transmit/

receive data pin (DATA1), a receive data pin

(DATA2), a chip select pin (CS

) and a synchronous

data clock pin (SCLK).

➧ The Auxiliary Port provides an analog I/O, pins

AUXin and AUXout, for connection of external

equipment to the CODEC path as well as

allowing access to the speaker driver circuits.

➧ AUXin is a single ended high impedance

input (>10 Kohm). This is a self-biased

input with a maximum input range of

2.5vp-p. Signals should be capacitorcoupled to this input.

➧ AUXout is a buffered output capable of

driving 40 Kohm s//150 pF. Signals for this

output are derived from the receive path or

from the AUXin and transmit microphones.

The microport dynamically senses the state of the

serial clock each time chip select becomes active.

The device then automatically adjusts its internal

timing and pin configuration to conform to Intel or

Motorola/National requirements. If SCLK is high

during chip select activation then Intel mode 0 timing

is assumed. The DATA1 pin is defined as a bidirectional (transmit/receive) serial port and DATA2

is internally disconnected. If SCLK is low during chip

select activation then Motorola/National timing is

assumed. Motorola processor mode CPOL=0,

CPHA=0 must be used. DATA1 is defined as the data

transmit pin while DATA2 becomes the data receive

pin. Although the dual port Motorola controller

configuration usually supports full-duplex

communication, only half-duplex communication is

possible in IDPC. The micro must discard non-valid

data wh ich it cloc ks in dur ing a v alid w rit e tra nsfer to

7-135

MT9196 Preliminary Information

IDPC. During a valid read transfer from IDPC data

simultaneously clocked out by the micro is ignored

by IDPC.

All data transfers through the microport are two-byte

transfers requiring the transmission of a Command/

Address byte followed by the data byte written or

read from the addressed register. CS

must remain

asserted fo r th e duration o f this two- byte transfer. As

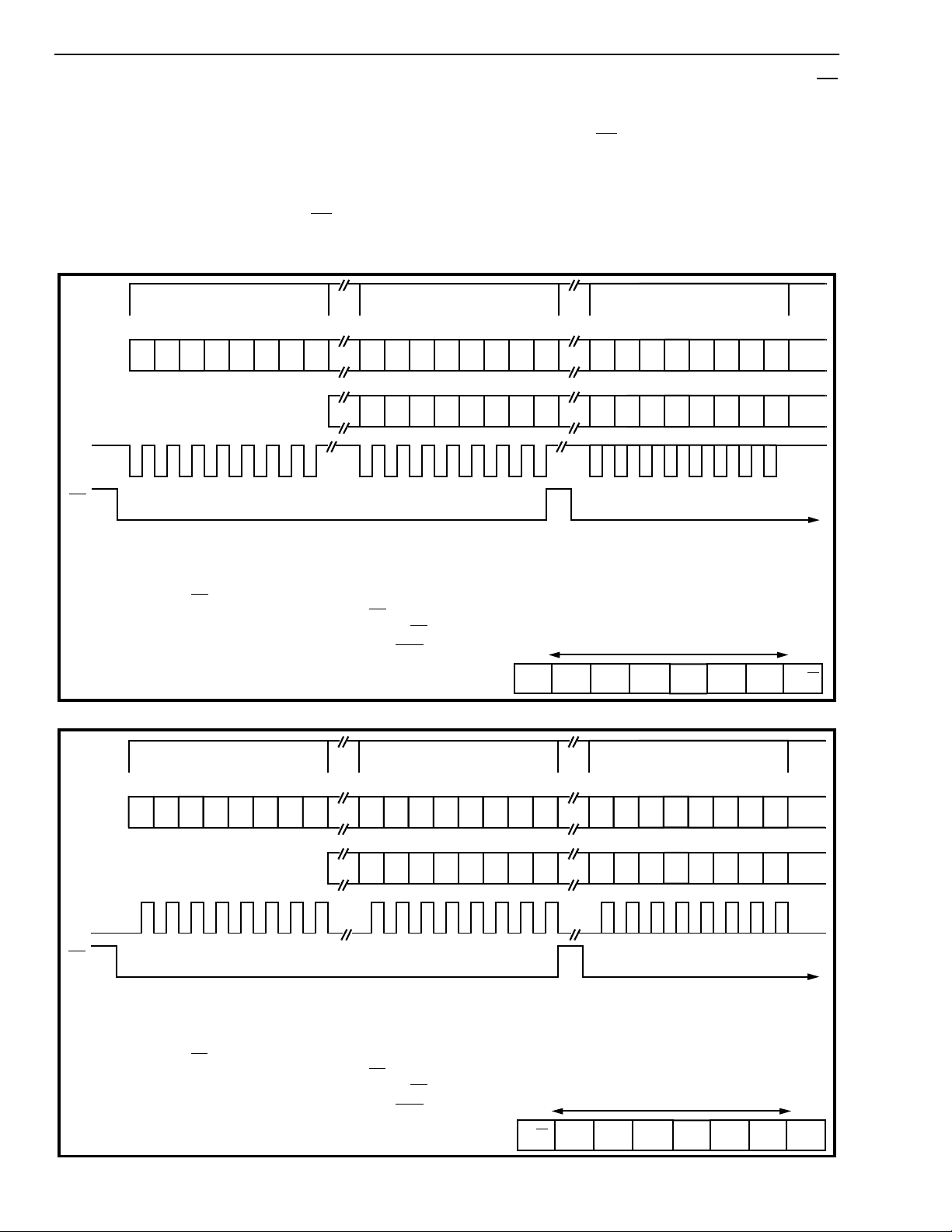

COMMAND/ADDRESS DATA INPUT/OUTPUT COMMAND/ADDRESS:

DATA 1

RECEIVE

DATA 1

TRANSMIT

SCLK

CS

➀ Delays due to internal processor timing which are transparent to IDPC.

② The IDPC:- latches received data on the rising edge of SCLK.

➂ The falling edge of CS

subsequent byte is always data until terminated via CS

➃ A new COMMAND/ADDRESS byte may be loaded only by CS

➄ The COMMAND/ADDRESS byte contains:

D0D1D2D3D4D5D6D

②

➂

- outputs transmit data on the falling edge of SCLK.

indicates that a COMMAND/ADDRESS byte will be transmitted from the microprocessor. The

➄

➀

D0D1D2D3D4D5D6D

7

D0D1D2D3D4D5D6D

returning high.

1 bit - Read/Write

5 bits - Addressing Data

2 bits - Unused

cycling high then low again.

shown in Figures 5 and 6 the falling edge of CS

indicates to the IDPC that a microport transfer is

about to begin. The first 8 clock cycles of SCLK after

the falling edge of CS

are always used to receive the

Command/Address byte from the microcontroller.

The Command/Address byte contains information

detailing whether the sec ond byte transfer will be a

read or a write operation and at what address. The

next 8 clock cycles are used to transfer the data byte

➀

7

7

➃

➂

D

7

XXA4A3A2A1A0R/W

➃

D0D1D2D3D4D5D6D

D0D1D2D3D4D5D6D

7

7

D

0

Figure 5 - Serial Port Relative Timing for Intel Mode 0

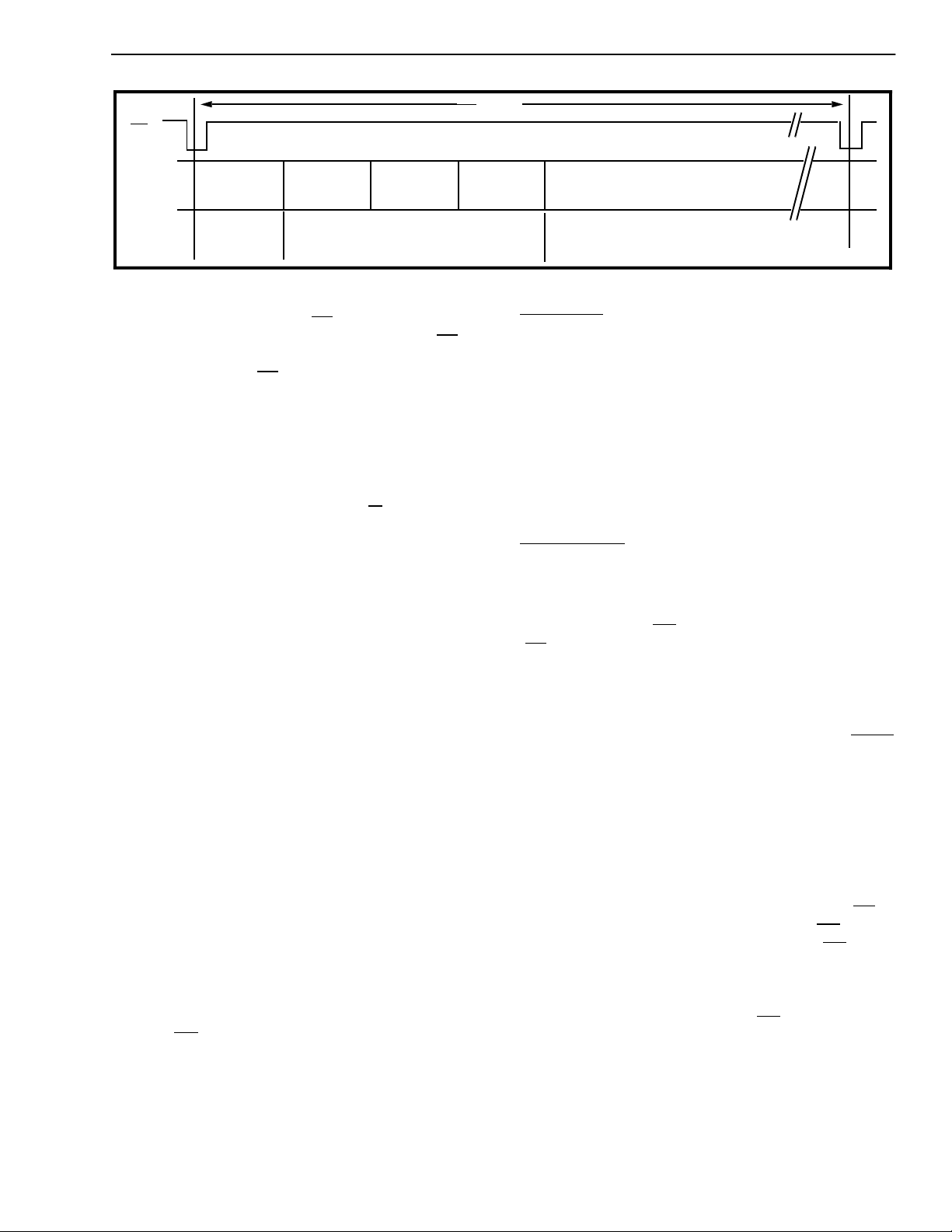

COMMAND/ADDRESS DATA INPUT/OUTPUT COMMAND/ADDRESS:

DATA 2

RECEIVE

DATA 1

TRANSMIT

SCLK

CS

➀Delays due to internal processor timing which are transparent to IDPC.

② The IDPC:- latches received data on the rising edge of SCLK.

➂ The falling edge of CS

subsequent byte is always data until terminated via CS

➃ A new COMMAND/ADDRESS byte may be loaded only by CS

➄ The COMMAND/ADDRESS byte contains:

D7D6D5D4D3D2D1D

②

➂

- outputs transmit data on the falling edge of SCLK.

indicates that a COMMAND/ADDRESS byte will be transmitted from the microprocessor. The

➄

➀

D7D6D5D4D3D2D1D

0

D7D6D5D4D3D2D1D

returning high.

1 bit - Read/Write

5 bits - Addressing Data

2 bits - Unused

cycling high then low again.

➀

0

0

➃

D

7

R/W XA4A3A2A1A0X

➃

D7D6D5D4D3D2D1D

D7D6D5D4D3D2D1D

➂

0

0

D

0

7-136

Figure 6 - Serial Port Relative Timing for Motorola Mode 00/National Microwire

Preliminary Information MT9196

125 µ s

F0i

DSTi,

DST o

CHANNEL 0

D-channel

LSB first

for D-

Channel

CHANNEL 1

C-channel

CHANNEL 2

B1-channel

MSB first for C, B1- & B2-

Channels

CHANNEL 3

B2-channel

Figure 7 - ST-BUS Channel Assignment

between the IDPC and the microcontroller. At the

end of the two-byte transfer CS

to terminate the session. The rising edge of CS

is brought high again

will

tri-state the output driver of DATA 1 which will remain

tri-stated as long as CS

is high.

Intel processors utilize least significant bit first

transmission while Motorola/National processors

employ most significant bit first transmission. The

IDPC microport automatically accommodates these

two schemes for normal data bytes. However, to

ensure timely decoding of the R/W

and address

information, the Command/Address byte is defined

differently for Intel operation than it is for Motorola/

National operation. Refer to the relative timing

diagrams of Figures 5 and 6.

Receive data is sampled on the rising edge of SCLK

while transmit data is made available concurrent with

the falling edge of SCLK.

Detailed microport timing is shown in Figure 15.

Flexible Digital Interface

CHANNELS 4-31

Not Used

Quiet Co de

The FDI can be made to send quiet code to the

decoder and receive filter path by setting the

RxMUTE bit high. Likewise, the FDI will send quiet

code in t he transmit (DSTo) path when the TxMUTE

bit is high. Both of these control bits reside in Control

Register 1 at address 0Eh. When either of these bits

are low their respective paths function normally. The

-Zero entry of Table 1 is used for the quiet code

definition.

ST-BUS Mode

The ST-BUS consists of output (DSTo) and input

(DSTi) serial data streams, in FDI these are named

Dout and Din respectively, a synchronous clock input

signal CLOCKin (C4i

). These signals are direct connections to the

(F0i

), and a framing pulse input

corresponding pins of Mitel basic rate devices. Note

that in ST-BUS mode the XSTL2 pin is not used. The

CSL1 and CSL0 bits, as described in the SSI Mode

section, are also ignored since the data rate is fixed

for ST-BUS operation . However, the Async h/Synch

bit must be set to logic “ 0” fo r ST-BUS operation .

A serial link is required to transport data between the

IDPC and an external digital transmission device.

IDPC utilizes the ST-BUS architecture defined by

Mitel Semiconductor but also supports a strobed

data interface found on many standard CODEC

devices. This interface is commonly referred to as

Synchronous Serial Interface (SSI). The combination

of ST-BUS and SSI provides a Flexible Digital

Interface (FDI) capable of supporting all Mitel basic

rate transmission devices as well as many other

2B + D transceivers.

The required mode of operation is selected via the

ST-BUS/SSI

control bit (FDI Control Register,

address 10h). Pin definitions alter dependent upon

the operational mode selected, as described in the

following subsections as well as in the Pin

Description tables.

The data streams operate at 2048 kb/s and are Time

Division Multiplexed into 32 identical channels of 64

kb/s bandwidth. A frame pulse (a 244 nSec low going

pulse) is used to parse the continuous serial data

streams into the 32 channel TDM frames. Each

frame has a 125 µSecond period translating into an 8

kHz frame rate. A valid frame begins when F0i is

logic low coincident with a falling edge of C4i

to Figure 12 for detailed ST-BUS timing. C4i

. Refer

has a

frequency (4096 kHz) which is twice the data rate.

This clock is used to sample the data at the 3/4 bitcell position on DSTi and to make data available on

DSTo at the start of the bit-cell. C4i

is also used to

clock the ID PC inte r na l fu n cti o n s (i.e ., Filte r/CODEC,

Digital gain and tone generation) and to provide the

channel timing requirements.

The IDPC uses only the first four channels of the 32

channel frame. These channels are always defined,

7-137

MT9196 Preliminary Information

beginning with Channel 0 after the frame pulse, as

shown in Figure 7 (ST-BUS channel assignments).

The first two (D & C) Channels are enabled for use

by the DEN and CEN bits respectively, (FDI Control

Register, address 10h). ISDN basic rate service

(2B+D) defines a 16kb/s signalling (D) Channel.

IDPC supports transparent access to this signalling

channel. ST-BUS basic rate transmission devices,

which may not employ a microport, provide access to

their int ernal control/status registers through the STBUS Control (C) Channel. IDPC supports microport

access to this C-Channel.

DEN - D-Channe l

In ST-BUS mode ac cess to the D -Channel ( transmit

and receive) data is provided through an 8-bit read/

write register (address 15h) D-Channel data is

accumulated in, or transmitted from this register at

the rate of 2 bits/frame for 16 kb/s operation (1 bit/

frame for 8 kb/s operation). Since the ST-BUS is

asynchronous, with respect to the microport, valid

access to this register is controlled through the use

of an interrupt (IRQ

enabled via the (DEn) bit.

) output. D-Channel access is

These di-bits are composed of the two D-Channel

bits received during each of frames n, n-1, n-2 and n-

3. Referrin g to Fig. 8a: di- bit I is mappe d from frame

n-3, di-bit II is mapped from frame n-2, di-bit III is

mapped from frame n-1 and di-bit IV is mapped from

frame n.

The D-Channel read register is not preset to any

particular value on power-up (PWRST

reset (RST).

(b) A microport write to Address 15hex will result in a

byte of data being loaded which is composed of four

di-bits (designated by roman numerals I, II, III, IV).

These di-bits are destined for the two D-Channel bits

transmitted during each of frames n+1, n+2, n+3,

n+4. Referring to Fig.8a: di-bit I is mapped to frame

n+1, di-bit II is mapped to frame n+2, di bit III is

mapped to frame n+3 and di bit IV is mapped to

frame n+4.

If no new data is written to address 15hex , the

current D-channel register contents will be

continuously re-transmitted. The D-Channel write

register is preset to all ones on power-up (PWRST

or softwa re r es e t ( RS T).

) or software

)

DEn:

When 1, ST-BUS D-channel dat a (1 or 2 bits/frame

depending on the state of the D8 bit) is shifted into/

out of the D-channel (READ/WRITE) register.

When 0, the receive D-channel data (READ) is still

shifted into the proper register while the DSTo Dchannel timeslot and IRQ

(default).

outputs are tri-stated

D8:

When 1, D-Channel data is shifted at the rate of 1 bit/

frame (8 kb /s ).

When 0, D-Channel data is shifted at the rate of 2

bits/frame (16 kb/s default ).

16 kb/s D-Channel operation is the default mode

which allows the microprocessor access to a full byte

of D-Channel information every fourth ST-BUS

frame. By arbitrarily assigning ST-BUS frame n as

the reference frame, during which the

microprocessor D-Channel read and write operations

are performed, then:

(a) A microport read of address 15 hex will result in a

byte of data being extracted which is composed of

four di-bits (designated by roman numerals I,II,III,IV).

An interrupt output is provided (IRQ

microprocessor access to the D-Channel register

during valid ST-BUS periods only. IRQ

every fourth (eighth in 8 kb/s mode) ST-BUS frame

at the beginning of the third (second in 8 kb/s mode)

ST-BUS bit cell period. The interrupt will be removed

following a microprocessor Read or Write of Address

15 hex or upon encountering the following frames’s

FP

input, whichever occurs first. To ensure DChannel data integrity, microport read/write access

to Address 15 hex must occur before the following

frame pulse. See Figure 8b for timing.

8 kb/s operation expands the interrupt to every eight

frames and processes data one-bit-per-frame. DChannel register data is mapped according to Figure

8c.

) to synchro nize

will occur

CEn - C-Chan nel

Channel 1 conveys the control/status information for

the layer 1 transceiver. C-Channel data is transferred

MSB first on the ST-BUS by IDPC. The full 64 kb/s

bandwidth is available and is assigned according to

which transceiver is being used. Consult the data

sheet for the selected transceiver for its C-Channel

bit definitions and order of bit transfer.

When CEN is high, data written to the C-Channel

register (address 14h) is transmitted, most

7-138

Loading...

Loading...