MITEL MT91610AQ Datasheet

MT91610

Analog Ringing SLIC

Preliminary Information

Features

• Transformerless 2W to 4W conversion

• Controls battery feed to line

• Programmable line impedance

• Programmable network balance impedance

• Off-hook and dial pulse detection

• Protects against GND short circuit

• Programmable gain

• Programmable constant current mode with

constant voltage fold over

• Transformerless balanced ringing with

automatic ring trip circuit. No mechanical relay

• Supports low voltage ringing

• Line polarity reversal

• On-hook transmission

• Power down and wake up capability

• Meter pulse injection

• Ground Key detection

Applications

Line interface for:

• PABX

• Intercoms

• Key Telephone Systems

• Control Systems

DS5181 ISSUE 2 February 2000

Package Information

MT91610AQ 36 Pin QSOP Package

-40°C to +85°C

Description

The Mitel MT91610, with an external bipolar driver

(Figure 4), provides an interface between a switching

system and a subscriber loop. The functions

provided by the MT91610 include battery feed,

programmable constant current with constant voltage

fold over for long loop, 2W to 4W conversion, offhook and dial pulse detection, direct balance ringing

with built in ring tripping, unbalance detection, user

definable line and network balance impedance’s and

gain, and power down and wake up. The device is

fabricated as a CMOS circuit in a 36 pin QSOP

package.

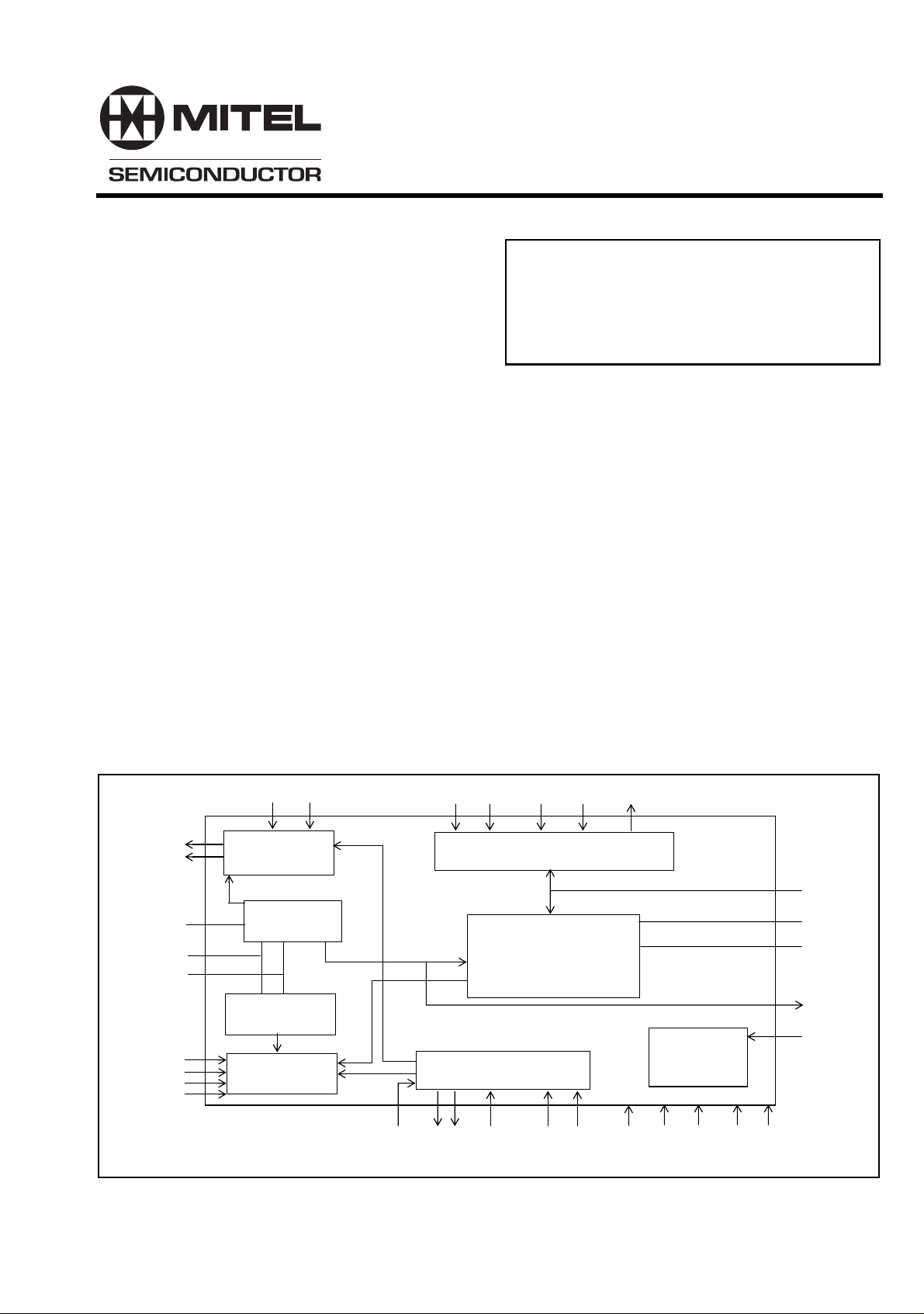

TD

RD

TIP

RING

RF1, RF2

RC

CP4

CP6

CP7

RV

PD

Tip/Ring Drive

Controller

Line Sense

Over-Current

Protection Circuit

Ring Drive

Controller

GTX1 GTX0 VX

Loop Supervision

UD

SHK

VREF

ESIESE

Audio Gain & Network

Balance Circuit

2 W to 4 W

Conversion & Line

Impedance

CP3

CP1

CP2

Figure 1 - Functional Block Diagram

DCRI

Line

Reverse

Driver

VDD

GND

VEE

VR

Z3

Z2

CP5

LR

VBAT

1

MT91610 Preliminary Information

VDD

VREF

RING

RF1

CP1

CP2

CP3

CP4

ESE

DCRI

TD

TF1

NC

TIP

LR

NC

RD

PD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

Figure 2 - Pin Connections

Pin Description

Pin # Name Description

1 VDD Positive supply rail, +5V.

VEE

RV

CP7

SHK

VBAT

UD

RC

CP6

VR

GTX1

ESI

VX

GTX0

Z3

Z2

CP5

Z1

AGND

2TDTip Drive (Output). Controls the Tip transistor. Connects 150nF cap to GND.

3 TF1 Tip Feed 1 (Output). Connects to the Tip transistor and to TIP via the Tip feed resistor.

4NCNo Connection Left open

5 Tip Tip. Connects to the TIP lead of the telephone line.

6 VREF Reference Voltage (Input). Used to set the subscribers loop constant current. A 0.1uF

cap should be connected between this pin and GND for noise decoupling.

7LRLine Reverse (Input). This pin should be set to 0V for NORMAL polarity. Setting the pin

to +5V reverses the polarity of Tip and Ring

8 Ring Ring. Connects to the RING lead of the telephone line

9 RF1 Ring Feed 1 (Output). Connects to the RING lead via the Ring feed resistor

10 NC No Connection Left open

11 RD Ring Drive (Output). Controls the Ring transistor. Connects 150nF cap to GND.

12 CP1 CP1. A 220nF capacitor should be connected between this pin and pin 13

13 CP2 CP2. A 330nF capacitor for loop stability is connected between this pin and pin 14

14 CP3 CP3. A 330nF capacitor for loop stability is connected between this pin and pin 13

15 CP4 CP4. A 100nF cap should be connected between this pin and GND

16 ESE External Signal Enable (Input). A logic ’1’ enable the MPI (Meter Pulse Input) to Tip /

Ring. This pin should be set to logic ’0’ when not used.

17 PD Power Do wn (Input). A logic ’1’ pow er down the de vice . This pin should be set to logic ’0’

for normal operation.

18 DCRI DC voltage for Ringing Input (Input) The positive voltage supply for balance ringing.

The input DC voltage range is from 0V to +72V.

19 AGND Analog Ground. 4 Wire Ground, normally connected to system ground.

2

Preliminary Information MT91610

Pin Description (continued)

Pin # Name Description

20 Z1 Line Impedance Node 1. A resistor of scaled value "k" is connected between Z1 and Z2.

This connection can not be left open circuit.

21 CP5 Line Impedance AC couple. A 0.1uF cap must be connected between this pin and Z1

(pin 16)

22 Z2 Line Impedance Node 2. This is the common connection node between Z1 and Z3.

23 Z3 Line Impedance Node 3. A network either resistive or complex of scaled value "k" is

connected between Z3 and Z2. This connection can not be left open circuit.

24 GTX0 Gain Node 0. This is the common node between Z3 and VX where resistors are

connected to set the 2W to 4W gain.

25 VX Transmit Audio. 4W analog signal from the SLIC.

26 ESI External Signal Input. 12 / 16 KHz signal input

27 GTX1 Gain Node 1. The common node between VR and the audio input from the CODEC or

switching network where resistors are fitted to sets the 4W to 2W gain

28 VR Receive Audio. 4W analog signal to the SLIC.

29 CP6 Ringing Cap. A 0.47uF cap should be connected between this pin and GND for ringing

voltage filtering.

30 RC Ringing Control. An active high (+5V) on this pin will set up the DC feed and gain of the

SLIC to apply 20 Hz ringing. When low (0V) set the SLIC in normal constant current mode

of operation.

31 UD UnBalance Detect. To indicate an offset current between Tip and Ring

32 VBAT VBAT. The negative battery supply, typically at -48V

33 SHK Switch Hook. This pin indicates the line state of the subscribers telephone. The output

can also be used for dial pulse monitoring. This pin is active high

34 CP7 Deglitching Cap. A 33nF should be connected between this pin and GND

35 RV Ringing Voltage. 20 Hz sinusoidal or square wave AC in for balance ringing

36 VEE Negative supply rail, -5V.

Functional Description

Refer to Figure 4 for MT91610 components

designation.

The MT91610, with external bipolar transistors,

functions as an Analog Line SLIC for use in a 4 Wire

switched system. The SLIC performs all of the

BORSH functions whilst interfacing to a CODEC or

switching system.

2 Wire to 4 Wire conversion

The SLIC performs 2 wire to 4 wire conversion by

taking the 4 wire signal from an analog switch or

voice CODEC, and converting it to a 2 wire

differential signal at Tip and Ring. The 2 wire signal

applied to tip and ring by the phone is converted to a

4 wire signal, which is the output from the SLIC to

the analog switch or voice CODEC.

Gain Control

It is possible to set the Transmit and Receive gains

by the selection of the appropriate external

components.

The gains can be calculated by the following

formulae:

2W to 4W gain

Gain 2 - 4 = 20 Log [ R8 / R7]

4W to 2W gain

Gain 4 - 2 = 20 Log [0.891 * [R10 / R9)]

3

MT91610 Preliminary Information

Impedance Programming

The MT91610 allows the designer to set the device’s

impedance across TIP and RING, (ZTR), and

network balance impedance, (ZNB), separately with

external low cost components.

The impedance (ZTR) is set by R4, R5, whilst the

network balance, (ZNB), is set by R6, R8, (see Figure

4.)

The network balance impedance should be

calculated once the 2W - 4W gain has been set.

Line Impedance

For optimum performance, the characteristic

impedance of the line, (Zo), and the device’s

impedance across TIP and RING, (ZTR), should

match. Therefore:

Zo = Z

TR

The relationship between Zo and the components

that set ZTR is given by the for mula:

Loop Supervision

The Loop Supervision circuit monitors the state of

the phone line and when the phone goes "Off Hook"

the SHK pin goes high to indicate this state. This pin

reverts to a low state when the phone goes back "On

Hook" or if the loop resistance is too high (>2.3KΩ)

When loop disconnect dialing is being used, SHK

pulses to logic 0 indicate the digits being dialled.

This output should be debounced.

Constant Current Control & Voltage

Fold Over Mode

The SLIC employs a feedback circuit to supply a

constant feed current to the line. This design is

accomplished by sensing the sum of the voltages

across the feed resistors, Ra and Rb, and comparing

it to the input reference voltage, Vref, that

determines the constant current feed current.

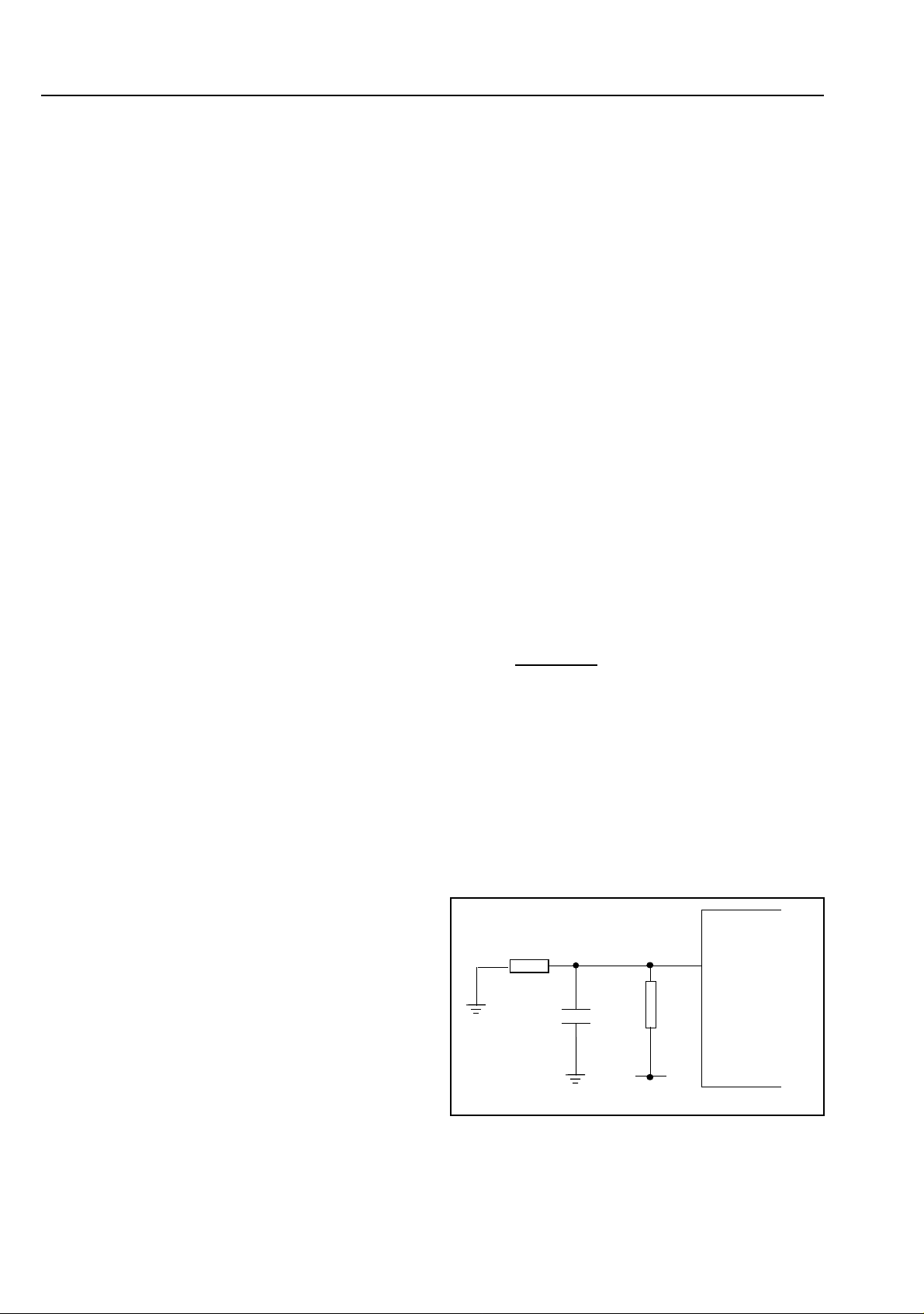

By using a resistive divider network, (Figure 3), it is

possible to generate the required voltage to set the

I

. This voltage can be calculated by the formula:

LOOP

Zo / ( Ra+Rb) = kZo / R4

where kZo = R5

Ra = Rb

The value of k can be set by the designer to be any

value between 20 and 250. R4 and R5 should be

greater than 50kΩ.

Network Balance Impedance

The network balance impedance, (ZNB), will set the

transhybrid loss performance for the circuit. The

transhybrid loss of the circuit depends on both the 4 2 Wire gain and the 2 - 4 Wire gain.

The method of setting the values for R6 (or Z6... it

can be a complex impedance) is given as below:

R6 = R7 * (R9 / R10) * 2.2446689 * ( ZNB / ZNB + Zo)

Please note that in the case of Zo not equal to Z

(the THL compromized case) R6 is a complex

impedance. In the general case of Zo matches to Z

(the THL optimized case) R6 is just a single resistor.

NB

NB

I

= [ G * 5] * 3

LOOP

(Ra +Rb)

where, G = R2 / (R1 + R2)

I

is in Ampere.

LOOP

R1= 200KΩ

From Figure 3 with Ra = Rb = 100 Ω

For I

For I

For I

= 20mA, R2 = 72.73 KΩ

LOOP

= 25mA, R2 = 100 KΩ

LOOP

= 30mA, R2 = 133.33 KΩ

LOOP

R2

**kΩ

C2

0.1uF

** See Figure 6

R1

200K

+5V

6

V

REF

MT91610

Figure 3 - Loop Setting

For convenience, a graph which plots the value of

R2 (KΩ) versus the expected loop current is shown

in Figure 6.

4

Preliminary Information MT91610

As +5V is used as the reference voltage to generate

the loop current, any noise on the +5V rail will

deteriorate the PSR (Power Supply Rejection)

parameter of the SLIC. It is therefore impor tant to

decouple +5V to GND. A 0.1uF cap at Vref pin (pin6)

is recommended.

The MT91610 operating current mode is

recommended to be between 20mA and 30mA. The

device will automatically switch to voltage hold over

mode should an unexpected long loop situation

occur for a given programmed loop current. The

lowest operational current should be 16mA with

VBAT set at -48V. A typical Operating Current versus

Loop Resistance with VBAT at -48V is shown in

Figure 7.

UD & Line Drivers Overcurrent

Protection

The Line Drivers control the external Battery Feed

circuit which provide power to the line and allows bidirectional audio transmission.

Balanced Ringing & Automatic Ring

Tripping

Balanced Ringing is applied to the line by setting the

RC to +5V (pin 25) and connecting ringing signal

(20Hz) to RV (pin 35) as shown in Figure 4. A

1.2Vrms input will give approximately about 60Vrms

output across Tip and Ring, sufficient for short loop

SLIC application. The SLIC is capable of detecting

an Off Hook condition during ringing by filtering out

the large A.C. component. A 0.47uF cap should be

connected to pin CP6 (pin 29) to form such filter.

This filter allows a true Off Hook condition to be

monitored at pin SHK (pin 33). When an Off Hook

condition is detected by the SLIC, it will remove the

20Hz AC ringing voltage and revert to constant

current mode. The local controller will, however, still

need to deselect RC (set it to 0V).

The MT91610 supports short burst of ringing

cadence. A deglitching input (CP7) is provided to

ensure that the SHK pin is glitch free during the

assertion and de-assertion of RC. A 33nF cap

should be connected at this pin to GND.

The loop supervision circuitry provides bias to the

line drivers to feed a constant current. Overcurrent

protection is done by the following steps:

(A) External bipolar transistors to limit the current of

the NPN drivers to 50mA (Figure 5).

(B) The local controller should monitor the

Unbalance Detection output (UD) for any extended

period of assertion (>5 seconds). In such case the

controller should power down the de vice by asserting

the PD pin, and polls the device every 5 seconds.

The UD output can be used to support GND START

LOOP in a PaBX operation.

Please note that this UD output should be

disregarded and masked out if RC pin is active (ie

set to +5V).

Powering Up / Down Sequence

AGND is always connected

Powering Up: +5V, -5V, VBAT

PD to +5V for 100ms; PD to 0V

Powering Down: VBAT, -5V, +5V

A positive voltage source is required to be

connected to the pin DCRI (Figure 5) for normal

Ringing generation. The SLIC can perform ringing

even with the DCRI input connected to 0V. However,

it does require the VBAT to be lower than -48V (ie at

-53V or lower) and the 20Hz AC input should be a

square wave at 2Vrms.

Line Reversal

The MT91610 can deliver Line Reversal, which is

required in operation such as ANI, by simply setting

LR (pin 7) to +5V. The device transmission

parameters will cease during the reversal. The LR

(pin 7) should be set to 0V for all normal loop

operations.

Power Down And Wake Up

The MT91610 should normally be powered down to

conserve energy by setting the PD pin to +5V. The

SHK pin will be asserted if the equipment side (2

wire) goes off hook. The local controller should then

restore power to the SLIC for normal operations by

setting the PD pin to 0V.

Please note that there will be a short break (about

80ms) in the assertion time of SHK due to the time

required for the loop to power up and loop current to

flow. The local controller should be able to mask out

this time fairly easily.

5

MT91610 Preliminary Information

Meter Pulse Injection

The MT91610 provides a gain path input (ESI) for

meter pulse injection and an independent control

logic input (ESE) for turning the meter pulse signal

on and off.

Additional circuit can be used to ensure good

cancellation of meter pulse signal (Figure 4) should it

becomes audible at the 4 wire side. Usually, the

optional circuit is not required.

Gain (meter pulse) = 20 Log [0.891 * (R10 / R11)]

Components Selection

Feed Resistors

The selection of feed resistors, Ra and Rb, can

significantly affect the performance of the MT91610.

The value of 100 Ω is used for both Ra and Rb.

The resistors should have a tolerance of 1% (0.1%

matched) and a power rating of 0.5 Watt.

Calculating Components Value

Step 2: Impedance Matching (R4, R5)

Zo / ( Ra+Rb) = kZo / R4 where kZo = R5

R5 / R4 = 3

∴ choose R4 = 100kΩ => R5 = 300kΩ

Step 3: Network Balance Impedance (R6)

Optimized Case Zo = Z

R6 = R7 * (R9 / R10) * 2.2446689 * ( ZNB / ZNB + Zo)

R6 = 300kΩ * (1) * 1.1223344

= 336.7kΩ

Step 4: The Loop Current (R2)

In order to remain in constant current mode during

normal operation, it is necessary that the following

equation holds:

{| I * Zt |} V < { | VBAT | - 6*VREF - 2} V

where,

I = Desirable Loop Current

Zt = Ra + Rb + maximum loop impedance

VBAT = Battery voltage

VREF= DC voltage at VREF pin

NB

There are five parameters a designer should know

before starting the component calculations. These

five parameters are:

1) characteristic impedance of the line Z

2) network balance impedance Z

3) value of the feed resistors (Ra and Rb)

4) 2W to 4W transmit gain

5) 4W to 2W receive gain

The following example will outline a step by step

procedure for calculating component values. Given:

Zo = 600Ω, ZNB= 600Ω, Ra=Rb= 100Ω

Gain 2 - 4 = -6dB, Gain 4 - 2 = -1 dB

Step 1: Gain Setting (R7, R8, R9, R10)

Gain 2 - 4 = 20 Log [ R8 / R7]

-6 dB = 20 Log [R8 / R7]

∴ choose R7 = 300kΩ, R8 = 150kΩ.

Gain 4 - 2 = 20 Log [0.891 * [R10 / R9)]

-1 dB = 20 Log [0.891 * [R10/ R9)]

∴ choose R9 = 200kΩ, R10 = 200kΩ.

NB

o

Given the parameters as follows:

Ra = Rb = 100 Ω

Expected maximum loop impedance = 1.6kΩ

(including Ra and Rb)

Desirable Loop Current = 20mA

6*Vref=8V

Then | VBAT | (min) = 1600 * 0.020 +10 = 42V

Assume that the VBAT of 42V is available, then read

the value of R2 from Figure 6, which is 50kΩ.

Step 5: Calculation Of Non-Clipping Sinusoidal

Ringing Voltage At Tip Ring (VTR)

Assume the Ringing Current is less than 40mA, the

ringing voltage (20Hz) at Tip and Ring is given as:

VTR (rms) = 0.707 * {| VBAT | + VDCRI - (15.6 *

VREF)}

VDCRI= Positive DC voltage at DCRI pin

VBAT = Negative Battery voltage

VREF= Positive DC voltage at VREF pin

AC voltage at the RV input pin is therefore

RV (rms)~= VTR (rms) / 50

6

Loading...

Loading...