MITEL MT9092AP Datasheet

AAAA

AAAA

AAAA

AAAA

A

A

A

A

A

A

A

A

A

A

AA

AAAA

AAAA

AAAA

AAAA

AAAA

A

A

A

A

A

A

A

A

A

A

2

ISO

-CMOS ST-BUS FAMILY

MT9092

Digital Telephone with HDLC (HPhone-II)

Features

• Programmable µ-Law/A-Law codec and filters

• Program mable CCITT (G .711)/sign-magni tude

coding

• Program mab le trans mit , receiv e and si de-t one

gains

• DSP-based:

i) Speakerphone switching algorithm

ii) DTMF and single tone generator

iii) Tone Ringer

• Differential interf ace to telepho ny tra nsdu cers

• Differential audio paths

• Singl e 5 volt pow er su ppl y

• X.25 Level 2 HD LC data form at ting

Applications

• Fully f eatu red dig ital t eleph one set s

• Cellula r phone sets

• Local area com m unications stations

ISSUE 2 May 1995

Ordering Information

MT9092AP 44 Pin PLCC

-40°C to +85°C

Description

The MT9092 HPhone-II is a fully featured integrated

digital telephone circuit which includes an HDLC

data formatter. Voice band signals are converted to

digital PCM and vice versa by a switched capacitor

Filter/Codec. The Filter/Codec uses an ingenious

differential architecture to achieve low noise

operation over a wide dynamic range with a single

5V supply. A Digital Signal Processor provides

handsfree speaker-phone operation. The DSP is

also used to generate tones (DTMF, Ringer and Call

Progress) and control audio gains. Internal registers

are accessed through a serial microport conforming

to INTEL MCS-51™ specifications. The device is

fabricated in Mitel's low power ISO

technology.

2

-CMOS

DSTo

DSTi

F0i

C4i

VSSD

VDD

VSSA

VSS

SPKR

VBias

VRef

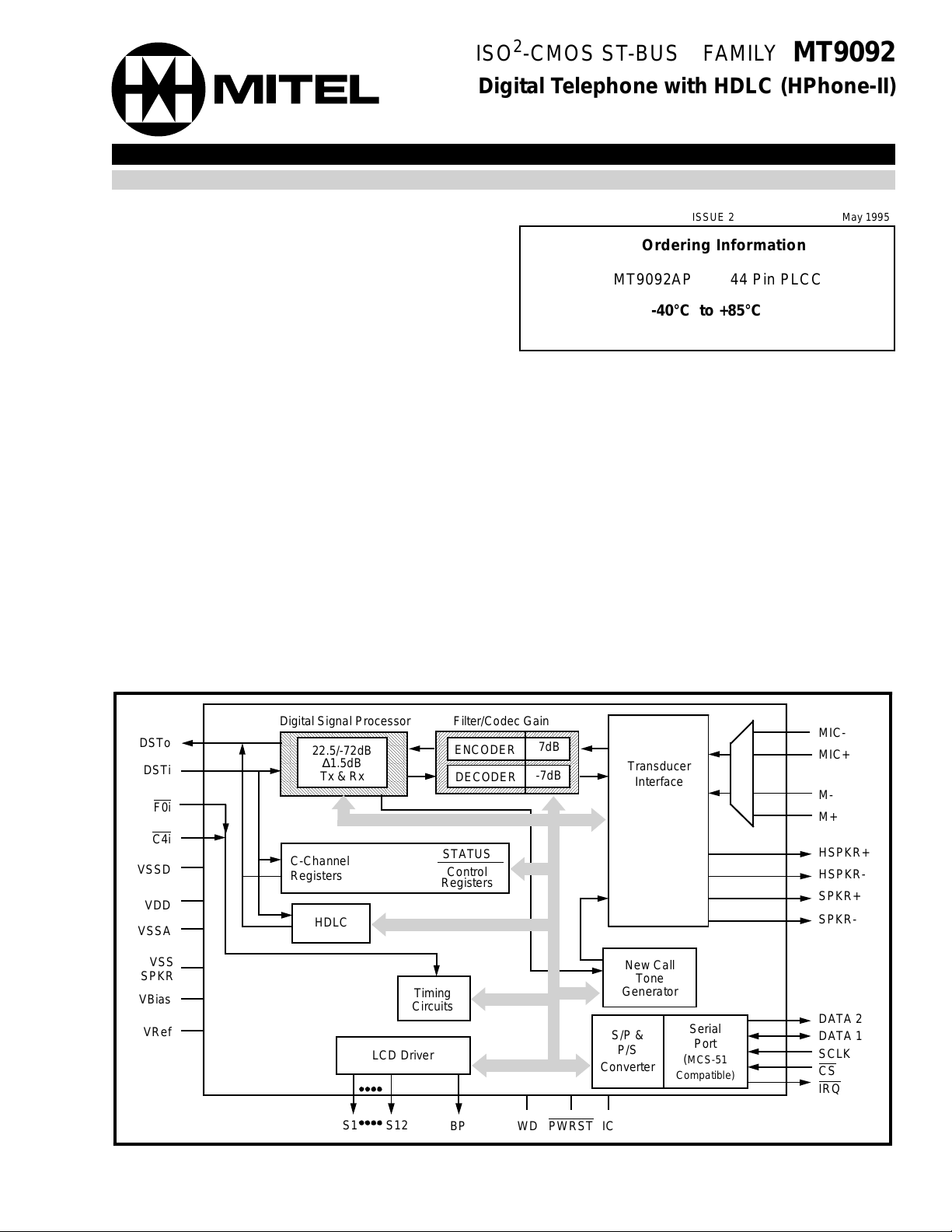

Digital Signal Processor Filter/Codec Gain

AAA

AAAA

AAAA

AAAA

AAAA

A

AAA

AAAA

AAAA

AAAA

AAA

AAAA

AAA

AAAA

22.5/-72dB

AAA

AAAA

AAA

AAAA

∆1.5dB

AAA

AAAA

AAA

AAAA

Tx & Rx

AAA

AAAA

AAA

AAAA

AAA

AAAA

C-Channel

Registers

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

A

AAA

AAAA

AAA

AAAA

ENCODER

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAA

AAAA

DECODER

AAA

AAAA

AAA

AAAA

AAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

A

A

A

A

A

A

A

A

STATUS

Control

Registers

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

-7dB

AAAA

AAAA

AAAA

HDLC

Timing

Circuits

LCD Driver

S1 S12

BP WD PWRST

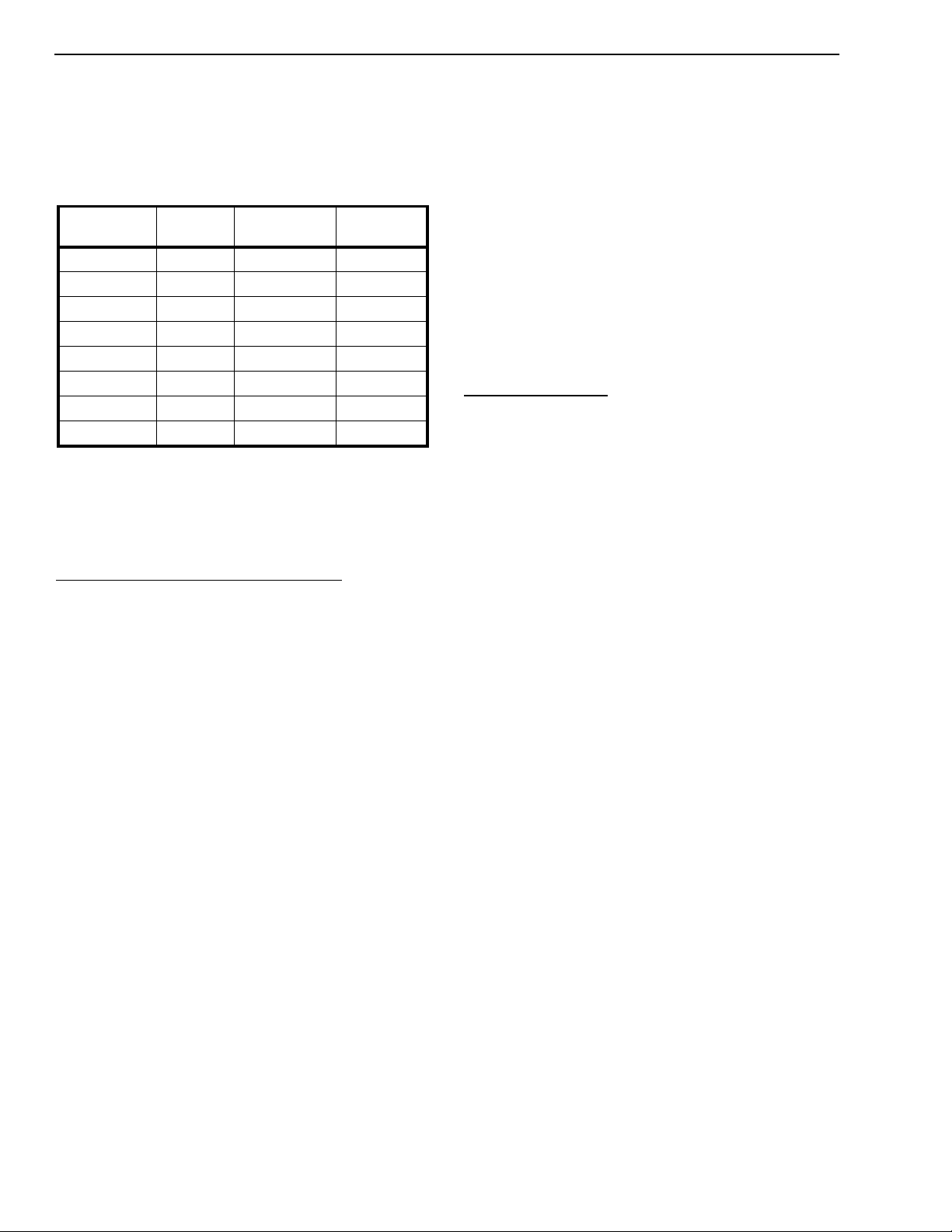

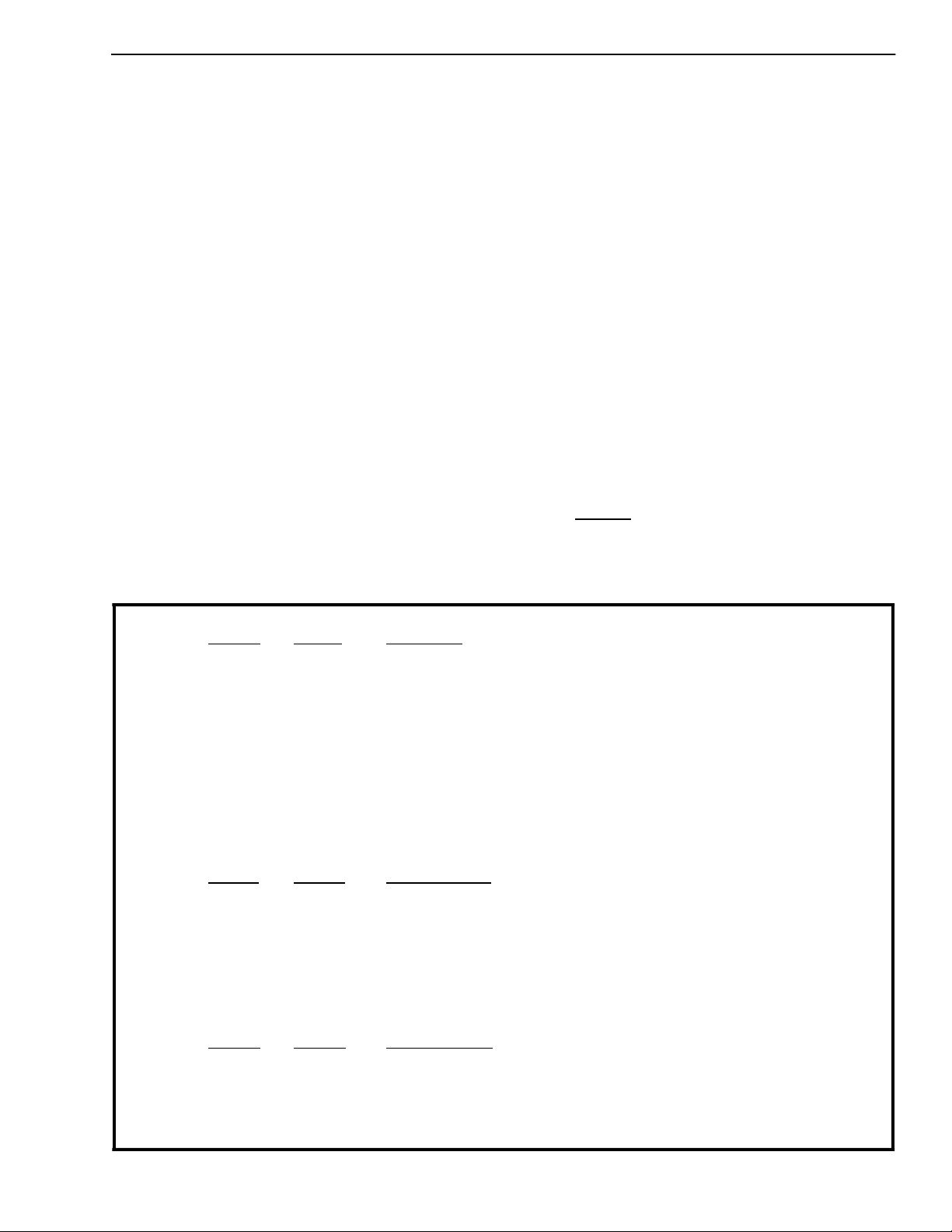

Figure 1 - Functional Block Diagram

7dB

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

Transd ucer

Interface

New Call

Tone

Generator

S/P &

P/S

Converter

IC

Serial

Port

MCS-51

(

Compatible)

MICMIC+

MM+

HSPKR+

HSPKRSPKR+

SPKR-

DATA 2

DATA 1

SCLK

CS

IRQ

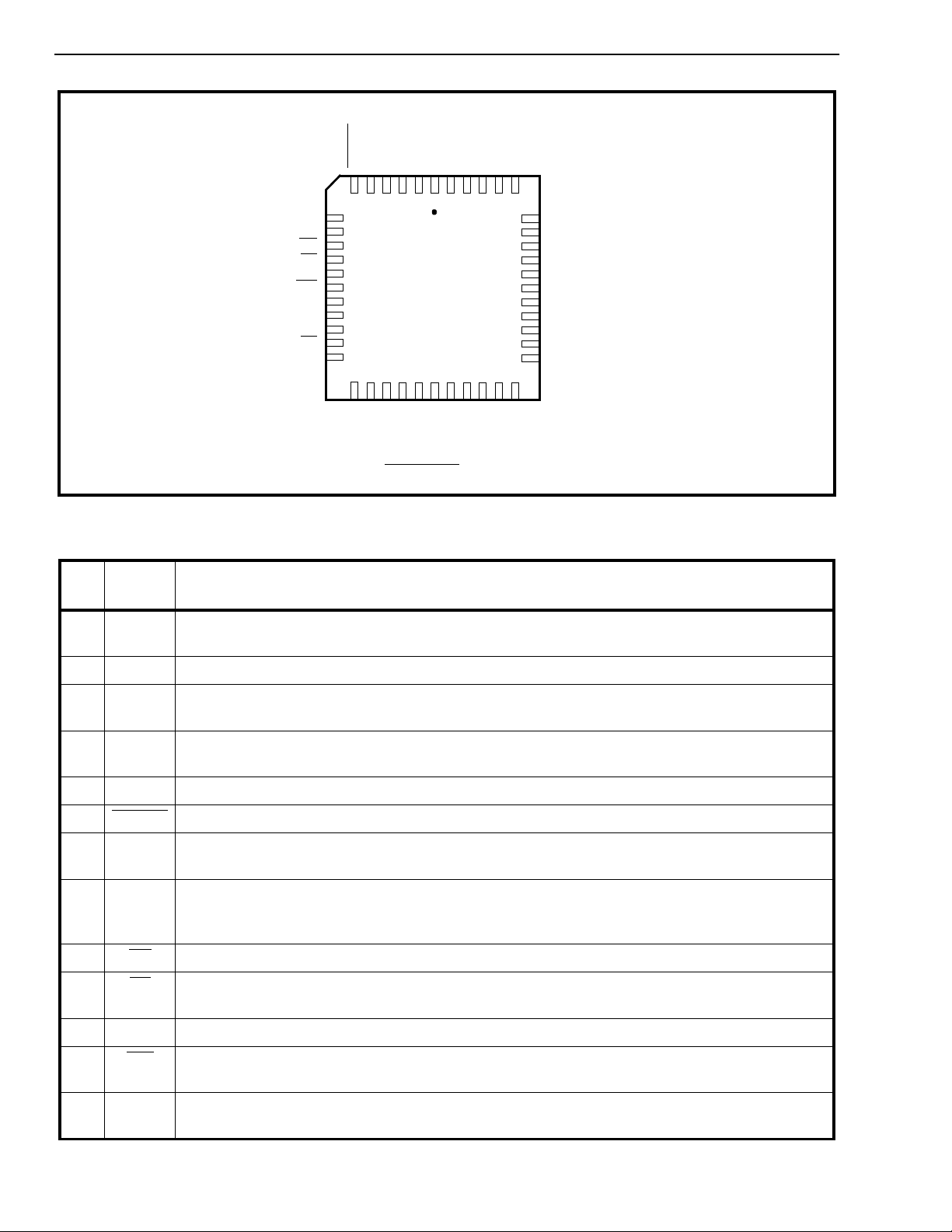

7-3

MT9092

PWRST

IC

VBias

VRef

NCM-VSSA

M+

MIC+

MIC-

VSS SPKR

VSSD

1

4443424140

23

2425262728

S1

S3S4S5S6S7

S2

39

38

37

36

35

34

33

32

31

30

29

SPKR+

SPKRHSPKR+

HSPKRVDD

BP

S12

S11

S10

S9

S8

DSTi

DSTo

C4i

F0i

VSSD

IRQ

SCLK

DATA 2

DATA 1

CS

WD

65432

7

8

9

10

11

12

13

14

15

16

17

1819202122

IC

NC

NC

44 PIN PLCC

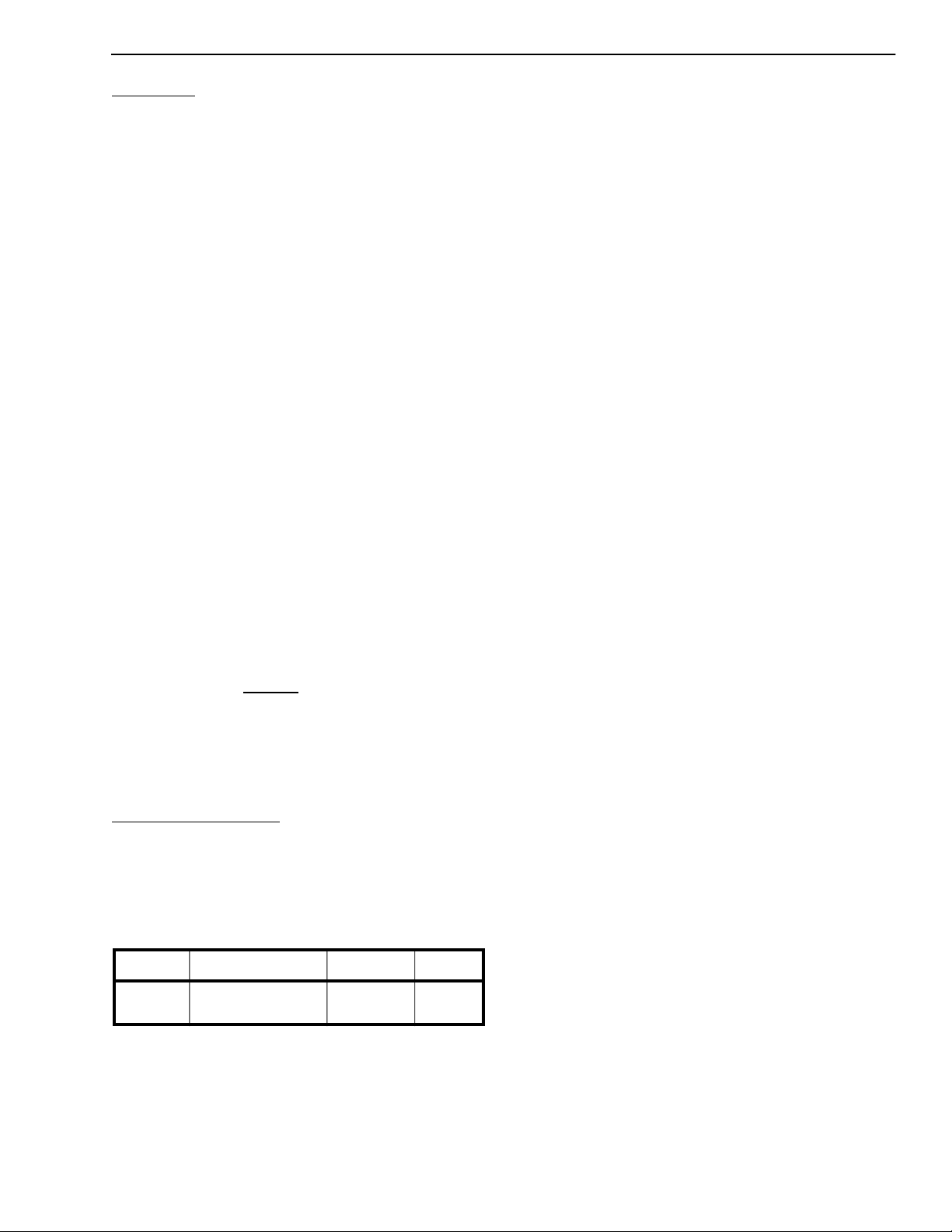

Figure 2 - Pin Connections

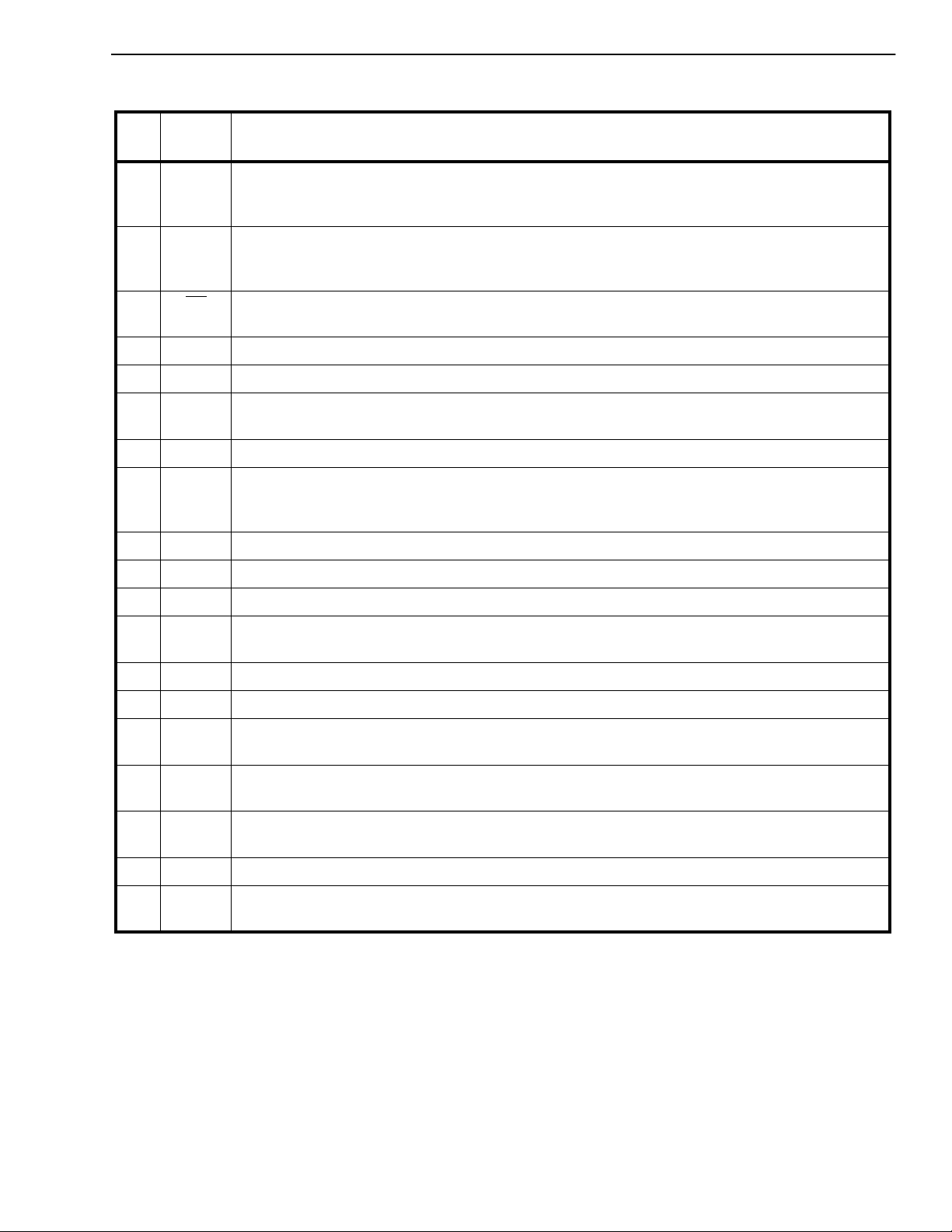

Pin Description

Pin

Name Description

#

1M+Non-Inver tin g Micro ph one (Input). Non-inverti ng input to microphone am plif ier from the

handset microphone.

2NCNo Connect. No internal connecti on to this pin.

3V

Bias

4V

5ICInternal Connection. Tie externally to V

6 PWRST

Bias Voltage (Outpu t). (VDD/2) volts is available at this pin for biasing external ampli fier s.

Connect 0.1 µF capacitor to V

Reference voltage for codec (Output). Nominally [(VDD/2)-1.5] volts. Used internally.

Ref

Connect 0.1 µF capacit or to V

SSA

SSA

.

.

for normal operation.

SS

Power-up Reset (Input). CMOS compatible input with Schmit t Trigger (active low).

7DSTiST-BUS Serial Stream (Input). 2048 kbit/s input stream composed of 32 eight bit channels;

the first four of which are used by the MT9092. Input level is TTL compat ibl e.

8DSToST-BUS Serial Stream (Output). 2048 kbit/s output stream composed of 32 eight bit

channels. The MT9092 sources digital signals during the appropriate channel, time coincident

with the channels used for DSTi.

9C4i

10 F0i

4096 kHz Clock (Input). CMOS level compatible.

Frame Pul se (Inp ut ). CMOS level compatible. This input is the frame synchronization pulse

for the 2048 kbit/ s ST-BUS stream.

11 V

SSD

12 IRQ

Digital Ground . Nominally 0 volts.

Interrupt Request (Open Drain Output). An active low output indicating an unmasked HDLC

interrupt event. Req uires 1 kΩ pull-up to V

DD

.

13 SCLK Serial Po rt Syn chro no us Cl ock (In pu t). Data clock for MCS-51 compa tibl e micropo rt. TTL

level compatible.

7-4

Pin Description (continued)

MT9092

Pin

Name Description

#

14 DATA 2 Serial Data Transmit. In an alternate mode of operation, this pin is used for data transmit

from MT9092. In the default mode, serial data transmi t and receive are performed on the

DATA 1 pin and DATA 2 is tri-stated.

15 DATA 1 Bidirectional Serial Data. Port for microprocessor serial data transfer compatible wit h MCS-

51 standard (default mode). In an alternat e mode of operati on , this pin becomes the data

receive pin only and data transmit is performed on the DATA 2 pin. Input level TTL compatible.

16 CS

Chip Select (Input). This input signal is used to select the device for microport data

transfers. Active low. (TTL level compatible .)

17 WD Watchdog (Output). Watchdog timer output. Active high.

18 IC Internal Connection. Tie externally to V

19,

NC No Connection. No internal connection to these pins.

for normal operation.

SS

20

21 V

SSD

Digital Ground. Nominall y 0 volt s.

22-33S1-S12 Segment Drivers (Output). 12 independently controlled, two level, LCD segment drivers. An

in-phase signal, with respect to the BP pin, produces a non-energized LCD segment . An out-

of-phase signal, with respect to the BP pin, energizes its respective LCD segment.

34 BP Backplane Drive (Output). A two-level output voltag e for biasing an LCD backplane.

35 V

Positive Po wer Supply (Inp ut). Nominally 5 volt s .

DD

36 HSPKR- I nvertin g Hand set Speaker (Outpu t). Output to the handset speaker (balanced).

37 HSPKR+Non-Inver tin g Handset Sp eaker (Outp ut). Output to the handset speaker (balanced).

38 SPKR- Inverting Speake r (Outpu t). Output to the speakerphone speaker (balanced).

39 SPKR+ Non-Inverting Speaker (Outpu t). Output to the speakerphone speaker (balanced).

40 V

Power Supply Rail for Analog Output Drivers. N o min ally 0 Volts.

SS

SPK R

41 MIC- Inve rtin g Handsfree M icr oph on e (Inp ut). Handsfree microphone amplif ier invert ing input

pin.

42 MIC+ No n-inver tin g Hand sfree Micro ph on e (Inp ut). Handsfree microphone amplifier non-

inverting input pin.

43 V

SSA

Anal og G round. Nominall y 0 V.

44 M- Inve rtin g Micro ph on e (Inp ut). Inverting input to microphone am plif ier from the handse t

microphone.

NOTES:

Intel and MCS-51 are registered trademarks of Intel Corporation, Santa Clara, CA, USA.

7-5

MT9092

Overview

The functional block diagram of Figure 1 depicts the

main operations performed within the HPhone-II.

Each of these functional blocks will be described in

the sections to follow. This overview will describe

some of the end-user features which may be

implemented as a direct result of the level of

integration found within the HPhone-II.

The main feature required of a digital telephone is to

convert the digital Pulse Code Modulated (PCM)

information, be ing rece ived by the telephon e set, into

an analog electrical signal. This signal is then

applied to an appropriate audio transducer such that

the information is finally converted into intelligible

acoustic energy. The same is true of the reverse

direction where acoustic energy is converted first

into an electrical analog and then digitized (into

PCM) before being transmitted from the set. Along

the way if the signals can be manipulated, either in

the analog or the digital domains, other features

such as gain control, signal generation and filtering

may be added. More complex processing of the

digital signal is also possible and is limited only be

the processing power available. One example of this

processing power may be the inclusion of a complex

handsfree switching algorithm. Finally, most electroacoustic transducers (loudspeakers) require a large

amount of power to develop an effective acoustic

signal. The inclusion of audio amplifiers to provide

this power is required.

The HPhone-II features Digital Signal Processing

(DSP) of the voice encoded PCM, complete Analog/

Digital and Digital/Analog conversion of audio

signals (Filter/CODEC) and an analog interface to

the external world of electro-acoustic devices

(T ransducer Interface). These three functional blocks

combine to provide a standard full-duplex telephone

conversation utilizing a common handset. Selecting

transducers for handsfree operation, as well as

allowing the DSP to perform its handsfree switching

algorithm, is all that is required to convert the fullduplex handset conversation into a half-duplex

speakerphone conversation. In each of these

modes, full programmability of the receive path and

side-tone gains is available to set comfortable

listening levels for the user as well as transmit path

gain control for setting nominal transmit levels into

the network.

The ability to generate tones locally provides the

designer with a familiar method of feedback to the

telephone user as they proceed to set-up, and

ultimately, dismantle a telephone conversation. Also,

as the network slowly evolves from the dial pulse/

DTMF methods to the D-Channel protocols it is

essential that the older methods be available for

backward compatibility. As an example; once a call

has been established, say from your office to your

home, using the D-Channel signalling protocol it may

be necessary to use in-band DTMF signalling to

manipulate your personal answering machine in

order to retrieve messages. Thus the locally

generated tones must be of network quality and not

just a reasonable facsimile. The HPhone-II DSP can

generate the required tone pairs as well as single

tones to accommodate any in-band signalling

requirement.

Each of the programmable parameters within the

functional blocks is accessed through a serial

microcontroller port compatible with Intel MCS-51

specifications.

Functional Descripti on

In this section, each functional block within the

HPhone-II is described along with all of the

associated control/status bits. Each time a control/

status bit(s) is described it is followed by the address

register where it will be found. T he reader is r eferred

to the section titled ‘Register Summary' for a

complete listing of all address map registers, the

control/status bits associated with each register and

a definition of the function of each control/status bit.

The Register Summary is useful for future reference

of control/status bits without the need to locate them

within th e tex t o f th e f unctional des crip ti o ns.

Filter-CODEC

The Filter/CODEC block implements conversion of

the analog 3.3kHz speech signals to/from the digital

domain compatible with 64kb/s PCM B-Channels.

Selection of companding curves and digital code

assignment are register programmable. These are

CCITT G.711 A-law or µ-Law, with true-sign/

Alternate Digit Inversion or true-sign/Inverted

Magnitude coding, respectively. Optionally, signmagnitude coding may also be selected for

proprietary applications.

The HPhone-II’s HDLC block is easy to use in

proprietary signalling protocols such as those within

PABXs and Key Systems. A fully interrupt driven

interface, buffered by 19 byte FIFOs in each

direction, simplifies the microcontroller's

asynchronous ac cess to the D-Cha n nel in fo rm at ion.

7-6

The Filter/CODEC block also implements transmit

and receive audio path gains in the analog domain.

These gains are in addition to the digital gain pad

provided in the DSP section and provide an overall

path gain resolution of 0.5dB. A programmable gain,

MT9092

voice side-tone path is also included to provide

proportional transmit speech feedback to the

handset receiver so that a dead sounding handset is

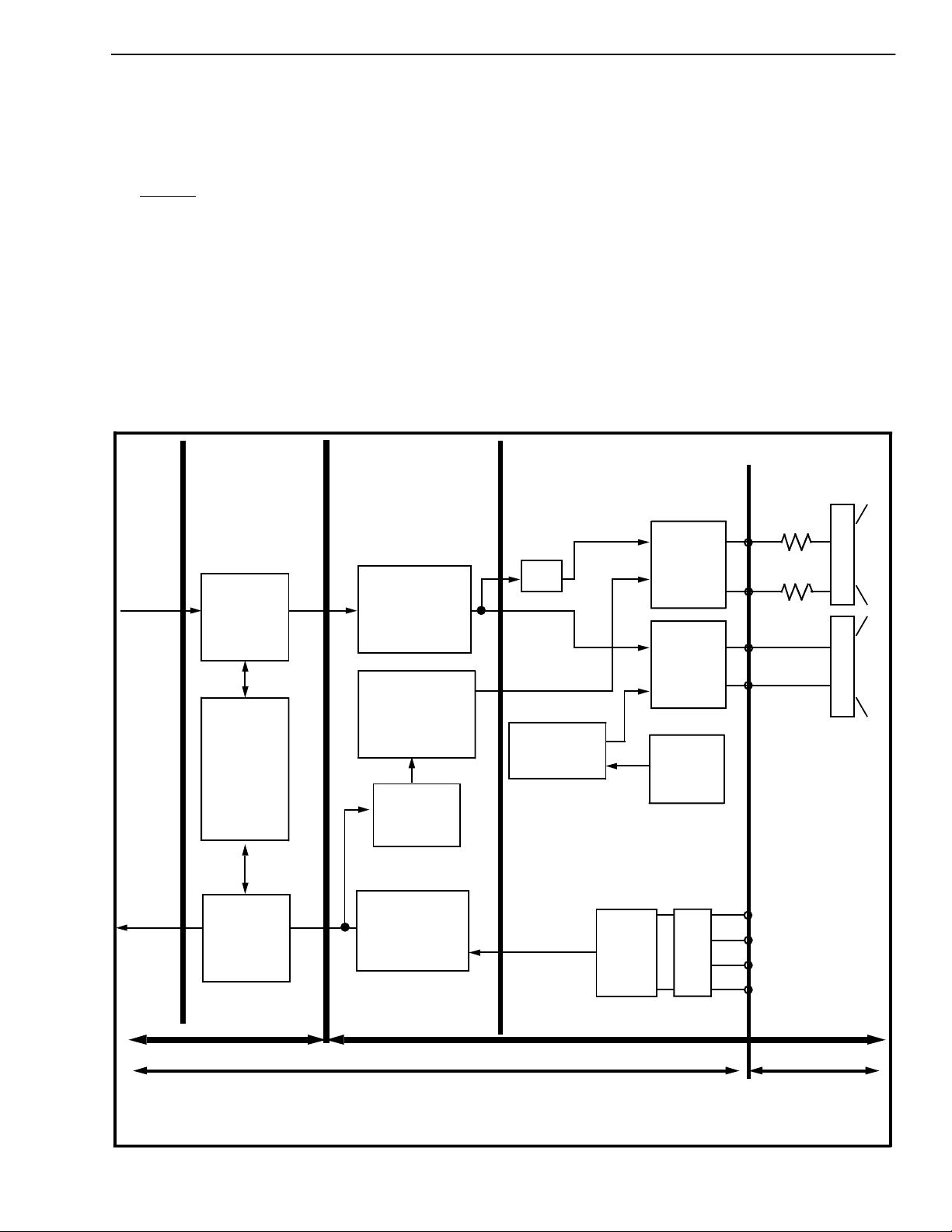

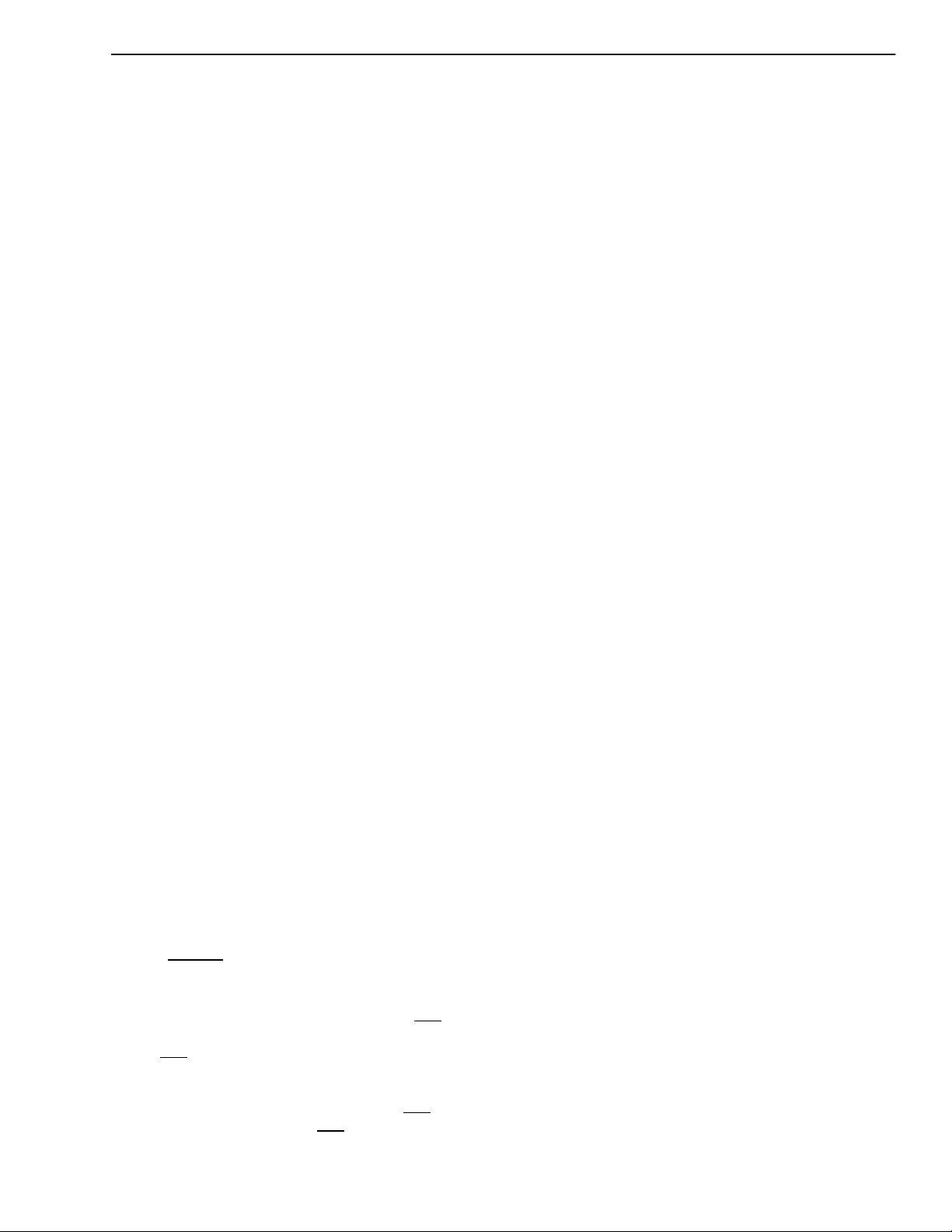

not encountered. Figure 3 depicts the nominal halfchannel and side-tone gains for the HPhone-II.

On PWRS T

(pin 6) the Filter/CODEC defaults such

that the side-tone path, dial tone filter and 400Hz

transmit filter are off, all programmable gains are set

to 0dB and µ-Law companding is selected. Further,

the Filter/CODEC is powered down due to the PuFC

bit (Transducer Control Register, address 0Eh) being

reset. This bit must be set high to enable the Filter/

CODEC.

The internal architecture is fully differential to provide

the best possible noise rejection as well as to allow a

SERIAL

PORT

DSP GAIN*

FILTER/CODEC

wide dynamic range from a single 5 volt supply

design. This fully differential architecture is

continued into the Transducer Interface section to

provide full chip realization of these capabilites.

A reference voltage (V

), for the conversion

Ref

requirements of the CODER section, and a bias

voltage (V

sections, are both generated on-chip. V

), for biasing the internal analog

Bias

Bias

is also

brought to an external pin so that it may be used for

biasing any external gain plan setting amplifiers. A

0.1µF capacitor must be connected from V

analog ground at all times. Likewise, although V

Bias

to

Ref

may only be used internally, a 0.1µF capacitor from

the V

pin to ground is required at all times. It is

Ref

suggested that the analog ground reference point for

these two cap ac ito r s b e ph y si cal ly the same p o int.

TRANSDUCER INTERFACE

µ-Law –6.3 dB

Α-Law –3.7 dB

-6 dB

HSPKR+

Handset

Receiver

(150Ω)

PCM

PCM

Receive

–72 to

+22.5 dB

(1.5dB

steps)

DTMF,

Tone

Ringer &

Handsfree

–72 to

+22.5 dB

(1.5dB

steps)

Transmit

Receive

Filter Gain

0 to –7 dB

(1 dB steps)

Side-tone

–9.96 to

+9.96d B

(3.32 dB steps)

Side-tone

Nominal

Gain

µ-Law –11 dB

Α-Law –18.8 dB

Transmit

Filter Gain

0 to +7dB

(1 dB steps)

-6 dB

Speaker Gain

0 to –24 dB

(8 dB steps)

µ-Law 6.1dB

Α-Law 15.4dB

Transmit

Gain

Receiver

Driver

Speaker

Phone

Driver

0.2dB*

Tone

Ringer

(input

from DSP)

M

U

X

HSPKR–

SPKR+

SPKR–

MIC+

MIC–

M+

M–

75

75

Speakerphone

Speaker

(40Ω nominal)

(32Ω min)

Handsfree

mic

Transmitter

microphone

DIGITAL DOMAIN

Internal to Device External to Device

Note: *gain the same for A-Law and µ−Law

ANALOG DOMAIN

Figure 3 - Audio Gain Partitioning

7-7

MT9092

To facili tate this the V

Ref

and V

pins are situated

Bias

on adjacent pins.

The transmit filter is designed to meet CCITT G.714

specifications. The nominal gain for this filter path is

0dB (gain control = 0dB). An anti-aliasing filter is

included. This is a second order lowpass

implementation with a corner frequency at 25kHz.

Attenuation is better than 32dB at 256 kHz and less

than 0.01dB within the passband.

An optional 400Hz high-pass function may be

included into the transmit path by enabling the Tfhp

bit in the Transducer Control Register (address 0Eh).

This option allows the reduction of transmitted

background noise such as motor and fan noise.

The receive filter is designed to meet CCITT G.714

specifications. The nominal gain for this filter path is

0 dB (gain control = 0dB). Filter response is peaked

to compensate for the sinx/x attenuation caused by

the 8 kH z sam p li ng rat e.

The Rx filter function can be altered by enabling the

DIAL EN control bit in the Transducer Control

Register (address 0Eh). This causes another

lowpass function to be added, with a 3dB point at

1000Hz. This function is intended to improve the

sound quality of digitally generated dial tone

received a s PCM.

Transmit sidetone is derived from the Tx filter and is

subject to the gain control of the Tx filter section.

Sidetone is summed into the receive path after the

Rx filter gain control section so that Rx gain

adjustment will not affect sidetone levels. The sidetone path may be enabled/disabled with the SIDE

EN bit located in the Transducer Control Register

(address 0Eh). See also STG

-STG2 (address 0Bh).

0

Transmit and receive filter gains are controlled by the

TxFG0-TxFG2 and RxFG0-RxFG2 control bits

respectively. These are loc ated in the FCODEC Gain

Control Register 1 (address 0Ah). Transmit filter gain

is adjustable from 0dB to +7dB and receive filter gain

from 0dB to -7dB, both in 1dB increments.

Side-tone filt er gain is controlled by the STG

-ST G

0

control bits located in the FCODEC Gain Control

Register 2 (address 0Bh). Side-tone gain is

adjustable from -9.96dB to +9.96dB in 3.32dB

increments.

Law selection for the Filter/CODEC is provided by

the A/µ companding control bit while the coding

scheme is controlled by the sign-mag/CCITT

bit.

Both of these reside in the General Control Register

(address 0Fh).

Digital Signal Processor

The DSP block is located, functionally, between the

serial ST-BUS port and the Filter/CODEC block. Its

main purpose is to provide both a digital gain control

and a half-duplex handsfree switching function. The

DSP will also generate the digital patterns required

to produce standard DTMF signalling tones as well

as single tones and a tone ringer output. A

programmable (ON/OFF) offset null routine may also

be performed on the transmit PCM data stream. The

DSP can generate a ringer tone to be applied to the

speakerphone speaker during normal handset

operation so that the existing call is not interrupt ed.

The main functional control of the DSP is through

two hardware registers which are accessible at any

time via the microport. These are the Receive Gain

Control Register at address 1Dh and the DSP

Control Register at address 1Eh. In addition, other

functional control is accomplished via multiple RAMbased registers which are accessible only while the

DSP is held in a reset state. This is accomplished

with the DRESET

bit of the DSP Control Register.

Ram-based registers are us ed to store transmit gain

levels (20h for transmit PCM and 21h for transmit

DTMF levels), the coefficients for tone and ringer

generation (addresses 23h and 24h), and tone ringer

warble rates (address 26h). All undefined addresses

below 20h are reserved for the temporary storage of

interim variables calculated during the execution of

the DSP algorithms. These undefined addresses

should not be written to via the microprocessor port.

The DSP can be programmed to execute the

following micro-programs which are stored in

instruction ROM, (see PS0 to PS2, DSP Control

Register, address 1Eh). All program execution

begins at the frame pulse boundary.

PS2

PS1 PS0 Micro-program

0 0 0 Power up r e se t p ro g r am

0 0 1 Transmit and receive gain control

program; with autonulling of the

transmit PCM, if the AUTO bit is

2

0 1 0 DTMF generation plus transmit

set (see address 1Dh)

and receive gain control

program (autonull available via

the AUTO control bit)

0 1 1 Tone ringer plus transmit and

receive gain control program

(autonull available via the

AUTO control bit )

7-8

MT9092

PS2 PS1 PS0 Micro-program

1 0 0 handsfree switching program

10 1

1 1 0 Last three selections reserved

11 1

Note: For the DSP to function it must be selected to

operat e, in co njunction with the Filter/C odec, in

one of t he B-C hannel s. Th erefor e, on e of the B Channel enable bits must be set (see Timing

Contro l, a d d ress 1 5 h : bi ts CH

EN and CH3EN).

2

Power Up reset Pro gram

A hardware power-up reset (pin 6, PWRST) will

initialize the DSP hardware registers to the default

values (all zeros) and will reset the DSP program

counter. The DSP will then be disabled and the PCM

streams will pass transparently through the DSP. The

RAM-based registers are not reset by the PWRST

pin but may be initialized to their default settings by

programming the DSP to execute the power up reset

program. None of the micro-programs actually

require the execution of the power up reset program

but it is useful for pre-setting the variables to a

known condition. Note that the reset program

requires one full frame (125µSec) for execution.

Gain Contr ol Progra m

Gain control is performed on converted linear code

for both the receive and the transmit PCM. Receive

gain control is set via the hardware register at

address 1Dh (see bits B0 - B5) and may be changed

at any time. Gain in 1.5dB increments is available

within a range of +22.5dB to -72dB. Normal

operation usually requires no more than a +20 to -20

dB range of control. However, the handsfree

switching algorithm requires a large attenuation

depth to maintain stability in worst case

environments, hence the large (-72 dB) negative

limit. Transmit gain control is divided into two RAM

registers, one for setting the network level of transmit

speech (address 20h) and the other for setting the

transmit level of DTMF tones into the network

(address 21h). Both registers provide gain control in

1.5dB increments and are encoded in the same

manner as the receive gain control register (see

address 1Dh, bits B0 - B5). The power up reset

program sets the default values such that the receive

gain is set to -72.0 dB, the transmit audio gain is set

to 0.0dB and the transmit DTMF gain is set to -3.0

dB (equivalent to a DTMF output level of -4dBm0 into

the network).

Optional Offset Nulling

Transmit PCM may contain residual offset in the form

of a DC component. An offset of up to ±fifteen linear

bits is acceptable with no degradation of the

parameters defined in CCITT G.714. The HPhone-II

filter/CODEC guarantees no more than ±ten linear

bits of offset in the transmit PCM when the autonull

routine is not enabled. By enabling autonulling (see

AUTO in the Receive Gain Control Register, address

1Dh) offsets a re reduced to within ±one bi t of zero.

Autonulling circuitry was essential in the first

generations of Filter/Codecs to remove the large DC

offsets found in the linear technology. Newer

technology has made nulling circuitry optional as

offered in the HPhone-II.

DTMF and Gai n Cont rol Prog ram

The DTMF program generates a dual cosine wave

pattern which may be routed into the receive path as

comfort tones or into the transmit path as network

signalling. In both cases, the digitally generated

signal will undergo gain adjustment as programmed

into the Receive Gain Control and the Transmit

DTMF Gain Control registers. The composite signal

output level in both directions is -4dBm0 when the

gain controls are set to 2Eh (-3.0 dB). Adjustments to

these levels may be made by altering the settings of

the gain control registers. Pre-twist of 2.0dB is

incorporated into the composite signal. The

frequency of the low group tone is programmed by

writing an 8-bit coefficient into Tone Coefficient

Register 1 (address 23h), while the high group tone

frequency uses the 8-bit coefficient programmed into

Tone Coefficient Register 2 (address 24h). Both

coefficients are determined by the following

equation:

COEFF = 0.128 x Frequency (in Hz)

where COEFF is a rounded off 8 bit binary integer

A single frequency tone may be generated instead of

a dual tone by programming the coefficient at

address 23h to a value of zero. In this case the

frequency of the single output tone is governed by

the coefficient stored at address 24h.

7-9

MT9092

Table 1 gives the standard DTMF frequencies, the

coefficient required to generate the closest

frequency, the actual frequency generated and the

percent deviation of the generated tone from the

nominal.

Frequency

(Hz)

COEF

Actual

Frequency%Deviation

697 59h 695.3 -.20%

770 63h 773.4 +.40%

852 6Dh 851.6 -.05 %

941 79h 945.3 +.46%

1209 9Bh 1210.9 +.20%

1336 ABh 1335. 9 .00%

1477 BD h 1476. 6 -.03%

1633 D1h 1632.8 -.01%

Ta ble 1

DTMF Signal to distortion:

The sum of harm onic and no is e po w er in th e

freque nc y ba nd from 50Hz to 3 50 0H z i s ty pi ca ll y

more t ha n 30 dB below th e p ower in the to n e p ai r. All

individual harmonics are typica lly more than 40dB

below the level of the low group tone.

Tone Ring er and G ain Co ntrol P rogram

A locally generated alerting (ringing) signal is used to

prompt the user when an incoming call must be

answered. The DSP uses the values programmed

into Tone Coefficient Registers 1 and 2 (addresses

23h and 24h) to generate two different squarewave

frequencies in PCM code. The amplitude of the

squarewave frequencies is set to a mid level before

being sent to the receive gain control block. From

there the PCM passes through the decoder and

receive filter, replacing the normal receive PCM data,

on its way to the loudspeaker driver. Both

coefficients are determined by the following

equation:

COEFF = 8000/Frequency (Hz)

where COEFF is a rounded off 8 bit binary integer.

The ringer program switches between these two

frequencies at a rate defined by the 8-bit coefficient

programmed into the Tone Ringer Warble Rate

Register (address 26h). The warble rate is defined

by the equation:

Tone duration (warble frequency

in Hz) = 500/COEFF

An alternate method of generating ringer tones to the

speakerphone speaker is available. With this method

the normal receive speech path through the decoder

and receive filter is uninterrupted to the handset,

allowing an existing conversation to continue. The

normal DSP and Filter/CODEC receive gain control

is also retained by the speech path. When the OPT

bit (DSP Control Register address 1Eh) is set high

the DSP will generate the new call tone according to

the coefficients programmed into registers 23h, 24h

and 26h as before. In this mode the DSP output is no

longer a PCM code but a toggling signal which is

routed directly through the New Call Tone gain

control section to the loudspeaker driver. Refer to

the secti o n ti tle d ‘Ne w Call To ne ’.

Handsfree Program

A half-duplex speakerphone program, fully contained

on chip, provides high quality gain switching of the

transmit and receive speech PCM to maintain loop

stability under most network and local acoustic

environments. Gain switching is performed in

continuous 1.5dB increments and operates in a

complimentary fashion. That is, with the transmit

path at maximum gain the receive path is fully

attenuated and vice versa. This implies that there is

a mid position where both transmit and receive paths

are attenuated equally during transition. This is

known as the idle state.

Of the 64 possible attenuator states, the algorithm

may rest in only one of three stable states; full

receive, full transmit and idle. The maximum gain

values for full transmit and full receive are

programmable through the microport at addresses

20h and 1Dh respectively, as is done for normal

handset operation. This allows the user to set the

maximum volumes to which the algorithm will

adhere. The algorithm determines which path should

maintain control of the loop based upon the relative

levels of the transmit and receive audio signals after

the detection and removal of background noise

energy. If the algorithm determines that neither the

transmit or the receive path has valid speech energy

then the idle state will be sought. The present state

of the algorithm plus the result of the Tx vs. Rx

decision will determine which transition the algorithm

will take toward its next stable state. The time

durations required to move from one stable state to

the next are parameters defined in CCITT

Recommendation P.34 and are used by default by

this algorith m (i.e ., b u ild- u p time , h a ng- ov e r time a nd

switching time).

where 0 < COEFF < 256, a warble rate of 5-20Hz is

suggested.

7-10

MT9092

Quiet Code

The DSP can be made to send quiet code to the

decoder and receive filter path by setting the

RxMUTE bit high. Likewise, the DSP will send quiet

code in the transmit (DSTo) path when the TxMUTE

bit is high. Both of these control bits reside in the

DSP Control Register at address 1Eh. When either

of these bits are low, their respective paths function

normally.

HDLC

The High-level Data Link Control (HDLC) block is

located, functionally, between the serial ST-BUS port

and the serial Microcontroller port. This functional

block handles the bit oriented protocol requirements

of layer 2 X.25 packet switching and Q.921 link

access protocols defined by CCITT. The HDLC is

dedicated to D-Channel operation at 16kb/s and

offers buffered access to the serial D-Channel data

through separate 19 byte transmit and receive

FIFOs.

The HDLC generat es and det ects the flags, various

link channel states and abort sequences as well as

performing a cyclic redundancy check on data

packets according to the CCITT defined polynomial.

Lastly, the protocol functions may be disabled to

provide transparent access, of the serial port DChannel, to the microport.

generates flags and appends them to the packet to

be transmitted. The receiver searches the incoming

data stream for flags on a bit-by-bit basis to establish

frame synchronization. The receiver uses flags for

synchronization only and does not transfer them to

the Rx FIFO.

Address F ield

The address field consists of one or two 8-bit bytes

directly following the opening flag. Address, Control

and Information fields are known collectively as the

Data field.

Control Fi eld

The control field consists of one 8-bit byte directly

following the address field. The HDLC does not

distinguish between the control field and the

informatio n field.

Information Field

The information field immediately follows the control

field and consists of N bytes of data where one by te

contains 8 bits. A packet does not need to contain an

information field to be valid. The HDLC does not

distinguish between the control field and the

informatio n field.

Frame Checking Sequence Field

A power up reset (PWRST

via RST (address 0Fh) will cause the HDLC

transceiver to be initialized. This results in the

transmitter and receiver being disabled and all HDLC

registers defaulting to their power reset values.

HDLC Frame Stru cture

A valid HDLC frame begins with an opening flag,

contains at least 16 bits of address, control or

information, ends with a 16 bit FCS followed by a

closing flag. Data formatted in this manner is also

referred to a s a " packet". Refer to Fi gu re 4 .

FLAG DATA FIELD FCS FLAG

One

Byte

n Bytes

(n≥2)

Figure 4 - Frame Format

, pin 6) or a softwar e reset

Two

Bytes

One

Byte

Flag Sequ ence

All HDLC frames start and end with a unique

sequence of 8 bits. This sequence is 0111 1110

(7Eh). The closing flag of one frame can be the

opening flag of the next frame. The transmitter

The 16 bits preceding a closing flag are the FCS

field. A cyclic redundancy check utilizing the CRCCCITT standard generator polynomial X

+1 produces the 16-bit FCS. In the transmitter the

FCS is calculated on all bits of the address, control

and information fields. The complement of the FCS

is transmitted, most significant bit first, in the FCS

field. The receiver calculates the FCS on the

incoming packet's address, control, information and

FCS fields and compares the result to 'F0B8'. This

result verif ies no transm ission errors occu rred. If the

packet, between flags, is also at least 32 bits in

length then t he address, control and information field

data are entered into the receive FIFO minus the

FCS which is discarded.

16

+ X12 +X

Order of Bit Transmission

Address, control and information field data are

entered into the transmit FIFO. This data is then

transmitted and received on the serial bus least

significant bit first. The FCS is sent most significant

bit first on the serial bus. Note that it is the

complement of the calculated FCS which is

transmitted. The HDLC does not distinguish

ADDRESS/CONTROL/INFORMATION bytes except

5

7-11

MT9092

to determine if the packet is of minimum valid length.

These fields are transferred transparently through

the FIFO's.

Data Transparency (Ze ro inserti on/d eletio n)

Transparency ensures that the contents of a data

packet do not imitate a flag, go-ahead, frame abort

or idle channel. The content s of a transmitted frame,

between the flags, is examined on a bit-by-bit basis

and a 0 bit is inserted after all sequences of five

contiguous 1 bits (including the last five bits of the

FCS). Upon receiving five contiguous 1s within a

frame the re ce ive r d ele te s th e fo llow i n g 0 bit.

Invalid Frames

A frame is invalid if one of the following four

conditions exists. Inserted zeros are not part of a

valid bit count:

1. If the FCS pattern generated from the received

data does not match the 'F0B8' pattern then the

last data byte of the packet is written to the

receive FIFO with a 'bad packet' indication.

2. A short frame exists if there are less than 25 bits

between the flags. Short frames are ignored by

the receiver and nothing is written into the

receive FIFO.

3. P ackets which are at least 25 bits in length but

less than 32 bits (between the flags) are also

invalid. In this case the data is written to the

FIFO but the last byte is tagged with a 'bad

packet' indication.

4. If a frame abort sequence is detected the packet

is invalid. Some or all of the current packet will

reside in the receive FIFO, assuming the packet

length before t he abort sequence was at least 26

bits long.

Frame Ab ort

The transmitter will abort a current packet by

substituting a zero followed by seven contiguous 1s

in place of the normal data. The receiver will abort

upon reception of seven contiguous 1s occurring

between the flags of a packet which contains at least

26 bits.

Note that should the last receive byte before the

frame abort end with contiguous 1s, these are

included in the seven 1s required for a receiver

abort. This means that the location of the abort

sequence in the receiver may occur before the

location of the abort sequence in the originally

transmitted packet. If this happens, t hen the last data

written to the receive FIFO will not correspond

exactly with the last byte received before the frame

abort.

Interframe T ime F ill and L ink Cha nne l State s

When the HDLC transmitter is not sending packets it

will wait in one of two states.

Interframe Time Fill: This is a continuous series of

flags occurring between

frames indicating that the

channel is active but that no

data is being sent.

Idle: An idle channel occurs when at least fifteen

contiguous 1s are transmitted or received.

In both cases the transmitter will exit the wait state

when data is loaded into the transmit FIFO.

Go-Ahead

A go-ahead is defined as the pattern ‘011111110’

(contiguous 7F’s) and is the occurrence of a frame

abort sequence followed by a zero, outside of the

boundaries of a normal packet. Being able to

distinguish a proper (in packet) frame abort

sequence from one occurring outside of a packet

allows a higher level of signalling protocol which is

not part of the HDLC specifications.

Transmitter

Following initialization and enabling, via the HTxEN

bit (address 03h), the transmitter is in the Idle

Channe l State (Mark Idle ). Interf rame time fill may

be selected by setting the Mark Idle bit (address 03h)

high. The transmitter remains in its programmed

state until data is written to the Tx FIFO. The

transmitter will then proceed as follows:

1) If the transmitter is in the idle state the present

byte of ones will be completely transmitted

before the opening flag and packet data is

sent.

2) If the transmitter is in the interframe time fill

state the flag currently being transmitted will be

used as the opening flag followed by the

packet data.

To assist in loading multiple packets into the transmit

FIFO the last packet byte is tagged with either EOP

(to indicate the end of the current packet) or FA.

Control Register 1 (address 03h) bits EOP (end of

7-12

MT9092

packet) and FA (frame abort) are set before writing

the last packet byte to the Tx FIFO. The act of

loading the last packet byte will then automatically

reset the EOP and FA bits. Tx FIFO bytes are

continuously transmitted until the FIFO is empty, by

which time an EOP or FA tag should have been

encounte r ed b y the transmitter.

After the last bit of the EOP byte has been

transmitted a 16 bit FCS is sent followed by a closing

flag. When multiple packets of data are loaded into

the Tx FIFO only one flag is sent between packets.

When the transmitter encounters a byte tagged FA

then a frame abort sequence is sent instead of the

tagged byte. All bytes previous to but not including

the tagged byte are sent.

The transm itter r eturns to its p rogramm ed wai t state

after concluding the transmission of EOP or FA if the

Tx FIFO is empty.

Transmit FIFO Status

The transmit FIFO is 19 bytes deep (address 02h).

As data is loaded into (from the microport) and

extracted from (via the serial port) the Tx FIFO the

present 'fill state' can be monitored using the Txstat1

and Txstat2 bits found in the HDLC Status Register

(address 04h). These states are encoded as shown

in Table 2. Note that the FIFO emptying threshold,

where an interrupt (TxFL if unmasked) will occur, can

be set to a low level 4 (default) or to a high level 14

by the Fltx bit in the HDLC Control Register 2

(address 05h).

Command/Address byte which indicates a microport

read of address 07h. Since all interrupts are

generated by the occurrence of an HDLC event (i.e.,

a transition), this register informs that an event has

occurred but does not guarantee that it is still valid.

To determine current validity the HDLC Status

Register (address 04h) should be read. Due to the

asynchronous nature of the interrupts an interrupt

occurring during a read of the Interrupt Status

register will be held until the read cycle is over,

unless it is an interrupt which is already valid.

There are three interrupts associated with the

transmitter.

TEOP Transmit End Of Packet:

Set when the transmitter has finished

sending the closing f lag of a packet or

after an abort sequence has been

completed.

TxFL Transmit FIFO Low:

Set when a transit ion from 5 to 4 bytes

in the Tx FIFO has occurred. This is an

early warning to the microprocessor

that the FIFO is emptying and should

be serviced before it empties

completely; a condition which will

result in a transmit underrun unles s an

EOP or FA byte has been written to the

FIFO. By setting the Fltx bit (address

05h) high the FIFO emptying condition

will occur at the transition from 15 to 14

bytes. This will allow the microport

more time to react to this interrupt

condition.

A Tx FIFO underrun occurs if the Tx FIFO empties

without the oc currence of an EOP or FA tagged byte.

A frame abort sequence is automatically transmitted

under this condition.

Transm it Interrupts

The HDLC Interrupt Enable Register (address 06h)

is used to select (unmask) only those interrupts

which are deemed important to the microprocessor.

After a PWRST

be cleared causing all interrupts to be masked.

All selected i n te rrup t e vents will c ause the IRQ pin to

become active. Unselected interrupt events will not

cau se IRQ

still be represented by the appropriate bit in the

HDLC Interrupt Status Register (address 07h). This

register must be read after receiving an IRQ

be polled at any time. The IRQ

coincident with the first SCLK falling edge following a

or software RST all enable bits will

to become active however, the event will

or may

output pin is reset

Txunder Transmit underrun:

Set when the Tx FIFO empties without

the occurrence of an EOP or FA

tagged byte. A frame abort sequence

is automatically transmitted under this

condition. Note that this register bit

position is shared with the frame abort

(FA) interrupt (see receive interrupts).

For this b it to r eflect T xund er t he Ints el

bit in Control Register 2 (address 05h)

must be set high.

Disabling, Res et, Transparent Operat ion an d CRC

Disabling the transm itter via the HTxEn bit will occur

after the current packet is completely transmitted.

The status and Interrupt registers may still be read

and the Tx FIFO and control registers written while

the transm it te r is d isa ble d .

7-13

MT9092

The Tx FIFO may be reset by setting the Txfrst bit in

the HDLC Control Register 2 (address 05h). The

HDLC Status Register will identify the Tx FIFO as

being empty although the actual data in the FIFO will

not be reset. Txfrst will be cleared by the next write

to the Tx FIFO.

Transparent data may be sent by setting the TRANS

bit (address 03h) high. The transmitter will no longer

generate the flag, abort and idle sequences, nor will

it insert zeros and append the FCS. Data will still be

transmitted LSB first. If there is no data in the Tx

FIFO or the Tx FIFO empties the last byte

transmitted will be repetitively sent until new data is

presented to the FIFO. It will t ake typically two STBUS frames, af ter writing TRANS, before this mode

begins. Note that CH

Transmission of the FCS field CRC may be inhibited

using the Tcrci (Transmit Crc Inhibit) bit at address

05h. W hile this bit is set the o pe n in g fl a g fo ll o we d b y

the data fields and closing flag is transmitted,

including zero insertion, but the calculated CRC is

not. This allows the processor to insert the CRC as

part of the data field. This usage is for V.120 terminal

adaptation for synchronous protocol sensitive UI

frames.

Receiver

Following initialization and enabling, via the HRxEN

bit at address 03h, the receiver begins clocking in

serial data checking for flags (0111 1110), go-aheads

( 0111 1111 0), and idl e c hannel states (at l eas t f ifteen

contiguous ones). Upon detecting a flag the receiver

synchronizes itself to the data stream and begins

calculating the CRC. If the packet length, between

the flags and after zero deletion, is less than 25 bits

the packet is ignored and nothing is written to the Rx

FIFO. If the packet length, after zero deletion, is

between 25 and 31 bits a last byte, bad packet

indication is written into the Rx FIFO.

EN must also be set.

0

Idle Channel

When the receiver detects at least 15 contiguous

ones it declares an idle channel condition exists and

sets the IdleChan bit in the HDLC status register

high (address 04h). This bit remains set until the

received condition changes.

If address recognition is required, Receive Address

Recognition Registers 1 and/or 2 (addresses 00h

and 01h respectively) are loaded with the desired

address comparison information, the Adrec bit is set

high and A1EN and A2EN are set as required. Bit 0

(A1EN and A2EN) of both recognition registers is

used as an enable for that by te. When either of these

bits are low their respective address mask

information is ignored. In this way either or both of

the first two received bytes can be compared to the

expected mask values. Only those packets passing

the appropriate comparison test will be loaded into

the Rx FIFO. The appropriate comparison test

(single/dual byte address, All-call) is defined by the

logic state of bit 0 of the first byte received after the

opening flag.

Bit 0 of the first received address byte (address

extension bit) is monitored to determine if a single or

dual byte address is being received.

1. If the address extension bit is 1 then a single

byte address is being received. If A1EN is high

the stored bit mask (Adr11 - Adr16 and

sometimes Adr10) is compared to the received

first address byte. Any packet failing this

address comparison will not be stored in the Rx

FIFO except for the All-call condition. A1EN

must be set high for a single-byte All-call

(11111111) address to be recognized. The

second mask byte is ignored. Seven bits of

address comparison may be realized for single

byte recognition by setting the SEVEN bit

(address 05h) high. This mode will then include

Adr10 as part of the mask information. The first

received byte must also have bit 0 set to a 1

indicating single byte addressing.

2. If the address extension bit is 0 then a two byte

address is being received and the six most

significant bits of the first received byte are

compared. The seven most signif icant bits of the

second received byte are compared (Adr20 Adr26, note A2EN must be set high also). Any

packet failing this address comparison will not

be stored in the Rx FIFO. An All-call condition

(1111111x) is also monitored for in the s econd

received address byte and, if found, the first and

second byte masks are ignored (not compared

with the mask byte). Packets addressed with Allcall are written into the Rx FIFO.

Address Recognition

When Adrec (HDLC Control Register 1, address

03h) is low all valid received packets, regardless of

the address field inform ation, are loaded into the Rx

FIFO.

7-14

In CCITT Q.921 parlance the Adr11 - Adr16 bits are

defined as Sapi0 - Sapi5 (Service Access Point

Identifier n). Adr10 is defined as C/R (Command/

Response). Adr20 - Adr26 are defined as Tei0 - Tei6

(Terminal Endpoint Identifier n).

MT9092

Receive Byte Status

As each received pack et byte is wr itten into th e Rx

FIFO two bits are appended to indicate the status of

that byte. As these bytes are read from the Rx FIFO

the status bits are made available to the

microprocessor in the HDLC Status Register

(address 04h) as RxBS1 and RxBS2. Since the

information contained in RxBS1 & RxBS2 pertains to

the byte about to be read from the Rx FIFO, it is

important that this information be read before

reading the data byte from the FIFO. RxBS1 and

RxBS2 are encoded as shown in Table 2. A good

packet indication means a good FCS and no frame

abort whereas a bad packet indication means either

an incorrect FCS or a frame abort occurred.

Receive F IFO Status

The receive FIFO is 19 bytes deep (address 02h). A s

data is loaded into (from the serial port) and

extracted from (via the microport) the Rx FIFO the

present 'fill state' can be monitored using the Rxstat1

and Rxstat2 bits found in the HDLC Status Register

(address 04h). These states are encoded as shown

in Table 2. Note that the FIFO filling threshold, where

an interrupt (RxFf if unmasked) will occur, can be set

to a high level 15 (default) or to a low level 5 by the

Flrx bit in the HDLC Control Register 2 (address

05h).

In the case of an Rx FIFO overflow, an attempt by

the receiver to write data into an already full FIFO,

the receiver is disabled causing it to stop writing to

the Rx FIFO. The remainder of the current receive

packet is therefore ignored. The receiver will be reenabled when the next flag is detected but will

overflow again if the Rx FIFO level has not been

reduced to less than full. If two 'first byte' (RxBS1

and RxBS2) conditions are observed in the FIFO

without an intervening 'last byte' then an overflow

occurred for the first packet.

Receive Interrupt s

The HDLC Interrupt Enable Register (address 06h)

is used to select (unmask) only those interrupts

which are deemed important to the microprocessor.

After a PWRST

be cleared causing all interrupts to be masked.

or software RST all enable bits will

RxBS2, Are status bits from the Rx FIFO.

RxBS1 RxBS2

1 1 last byte (bad packet)

0 1 first byte

1 0 last byte (good packet)

0 0 packet byte

Note - If two consecutive first byte signals are received without an inte rven ing last byte, then an

overflow has occurred and the first packet (or packets) are bad. A bad packet indicates that

either a frame abort had occurred or the FCS did not match.

- On power-up these bits are in an indeterminate state until the first byte is writte n to Rx FIFO.

Txstat2,

Txstat1 These two bits are encoded to indicate the present state of Tx FIFO. This is an asynchronous

event.

Txstat2

0 0 TxFULL

0 1 5 OR MORE BYTES (15 if Fltx set)

1 1 4 OR LESS BYTES (14 if Fltx set)

1 0 TxEMPTY

Rxstat2,

Rxstat1 These two bits are encoded to indicate the present state of Rx FIFO. This is an asynch ronous

event.

Rxstat2

0 0 RxEMPTY

0 1 14 OR LESS BYTES (4 if Flrx set)

1 1 15 OR MORE BYTES (5 if Flrx set)

1 0 RxOVERFLOW EXISTS

RxBS1 Byte stat us

Txstat1 Tx FIFO Status

Rxstat1 Rx FIFO Status

Ta ble 2 - HDLC S tatus Bits

7-15

Loading...

Loading...