MITEL MT90840AK, MT90840AP Datasheet

MT90840

Distributed Hyperchannel Switch

Advance Information

Features

• Time-slot interc han ge func tion be twee n 8 p airs

of ST-BUS/GCI/MVIP stre ams (5 12 ch annel s)

and a Parallel Data Po rt (PDP)

• Supports st ar, point to poin t conn ectio ns a nd

unidirectional or bidirectional ring topologies for

distributed systems

• Input to Ou tput B ypas s funct ion with mi nim um

delay for shar ed ring app licatio ns

• Provides an i ntern al late ncy ad justm ent bu ffer

for ring applica tio ns

• Parallel port data rates up to 19.44Mbyte/s

• Pro gr am ma bl e dat a rat es on the se ria l por t si de

(2.048 Mb/s , 4.0 96 Mb /s or 8. 192 M b/s)

• Unidirection al Para llel switch ing mo de for up to

2430 chann els non-bl ocking

• Per-channel direct ion co ntrol on the ser ial po rt

side

• Per-channel message mode and highimpedance contro l on bot h para llel and seri al

port sides

• 8-bit multiplexed port compatible with Intel and

Motorola micr ocontro llers

• Guarantee s fram e integ rity wh en sw itching

wideband c hanne ls su ch as ISDN H0 ch an nel

• Provides ex ternal cont rol lines a ll owing the fas t

parallel inte rface to be sh ared wi th othe r

devices

ISSUE 1 June 1995

Ordering Information

MT90840AK 100 Pin PQFP

MT90840AP 84 Pin PLCC

-40°C to 85°C

• Special diagnostic alarm functions for statistical

analysis

• JTAG bounda ry sc an

Applications

• Bridging ST-BUS/MVIP buses to high speed

Time Division Multiplex backplanes at SONET

rates (STS-1/3)

• High speed isochro nou s back bones for

distributed PBX and Local Area Network

systems

• Switch platfo rms of up to 243 0 ch annel s with

guaranteed fram e integ rity for wi deba nd

channels

• Serial bus co ntrol and moni toring

• Data multi p lexer

• High speed communications interface

• Isochronous switching/multiplexing to support

IEEE 802.9 standards

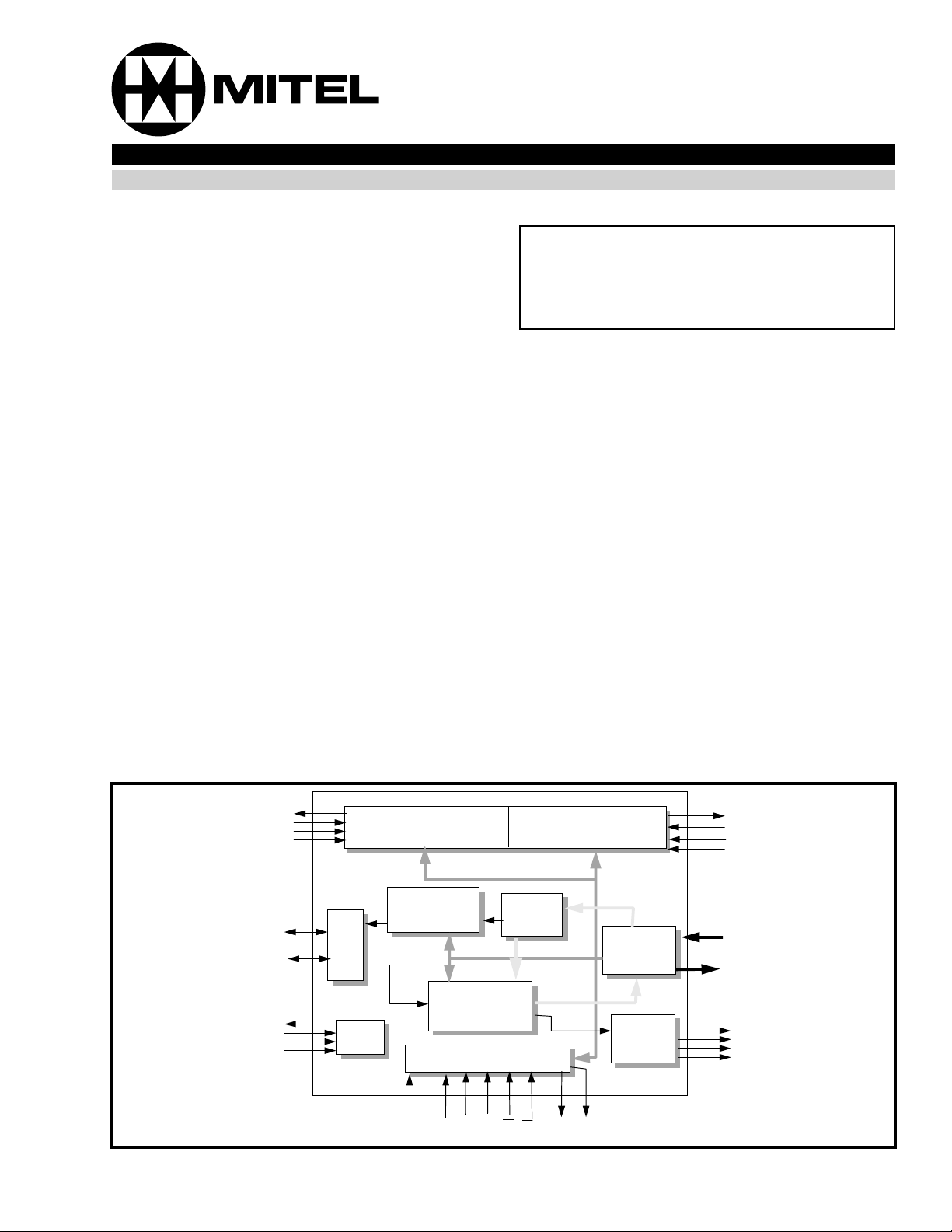

C4OUT

C4REF1

C4REF2

FO

Serial

Data Data

DSo[0:7]

DSi[0:7]

SERIAL PORT TIMING

CONTROL

RECEIVE PATH

DATA & CONN

S-P

&

P-S

MEMORIES

PARALLEL PO RT TIMING

CONTROL

RECEIVE

LATENCY

BUFFER

INTERFACE

PARALLEL

PORT

Port

TRANSMIT P ATH

DATA & CONN

TCK

TMS

TDI

TDO

JTAG

RESET

MEMORIES

Microprocessor Interface

WR/

AD[0:7]

ALE

R/W

RD/

DS

CS DTACK

INT

EXTERNAL

CONTROL

PPFRo

PCKT

PPFRi

PCKR

PDi0-7

PDo0-7

CT0

CT1

CT2

CT3

Parallel

Port

Figure 1 - Functional Block Diagra m

2-189

MT90840 Advance Information

Functional Description

Real time multimedia applications require the

transmission of mixed voice and data transmission

into the same integrated network and transmission

media. The netw ork must simultaneously ensure that

data (at N x 64 kbit/s) m aintains t ime slot seq uence

integrity and provide constant delay through the

switch.

The MT90840 device bridges existing Mitel ST-BUS

components into a new networking environment.

Mixed data, voice and video signals can be timeinterchanged or multiplexed from serial PCM

streams onto a serial high speed Time Division

Multiplex (TDM) isochronous backbone operating at

SONET rates such as 51 (STS-1) or 155 Mb/s (STS-

3). Figure 1 shows the MT90840 functional block

diagram.

Today, transmission links operating at SONET rates

utilize Serial-to-Parallel and Parallel-to-Serial

converter devices (or framers) which perform

embedded framing functions and give the user the

access to the payload of the high speed frame.

The MT90840 device provides an 8-bit bidirectional

parallel data port (PDP) which directly interfaces to

the user data interface of typical high speed framers,

allowing designers to build distributed networking

systems with interconnection speeds up to 155 Mb/s.

Figure 2 depicts an example of distributed

networking application in Computer Telephony

Integration (CTI) systems. Figure 3 shows an

example of interconnection between the MT90840

and high speed S/P & P/S framers used when

implementing 155 Mb/s transmission links.

The MT90840 device is designed to switch 64 kbit/s

or wideband N x 64 kb/s channels from a Serial Data

Port (SDP) to the Parallel Data Port (connected to

high speed framers) and vice versa. The MT90840

Parallel Data Port is designed to accept data rates

up to 19.44 Mbyte/s and the Serial Data Port can be

programmed to connect to PCM serial streams at

2.048, 4.096 and 8.192 Mb/s.

Since the parallel and serial ports of the MT90840

device operate at different rates, an internal rate

converter circuit associated with a multiple buffer

time interchange block is employed to achieve the

rate adaptation between the two ports.

The internal time interchange block allows the

switching of 512 64 kb/s channels on the serial

interface in a flexible connection scheme. This is

accomplished by a feature called "per channel

direction control" available on the 16 serial streams.

For example, in some applications up to 512

channels from the serial port can be time

interchanged t o the parallel port side. In the opposite

direction up t o 512 channels coming from the parallel

port can be dropped or time interchanged to the

serial port side.

The device's clock synchronization and reference

options al low many applications and topologies when

isochronous TDM backbones are required. Two

major clock synchronization schemes provided by

the MT90840 allow the serial port interface (ST-BUS)

to provide the master clock and frame reference

signals for the distributed high speed backbone

(master operation) or to derive the entire ST-BUS

clock and frame reference signals from the high

speed backbone (slave operation). Figure 3 depict s

an example of Master Operation.

This type of synchronization scheme may be used in

applications such as MVIP multi-chassis level 3

interface (MC-3 system) utilizing point to point or

point to multipoint switching connections.

When the MT90840 device operates in a ring type of

application like the system depicted in Figure 2, a

special mode called Parallel Data B ypass is provided

to allow all or part of the received input parallel data

to be bypassed t o the output parallel port feeding the

ring back with the data which is not destined (to be

dropped) to the local station. The selection of the

data destined (dropped) for the local station can be

done through CPU programming. In this mode, the

CPU has the full control on managing the outgoing

bandwidth (from the serial interface to the high

speed link) so that it does not contend with the

bypassed data .

For CPU access t o the serial channels, the MT90840

device can be programmed using message mode

with fast memory access times. By using the Mitel

message mode, the microprocessor can access

serial input and output TDM data on a per channel

basis to control devices such as the Mitel’s digital

transceivers like MT8972B, MT8930/1, MT8910 and

T1/CEPT tru n ks t hr o ugh th e ST-BUS interface.

2-190

Loading...

Loading...