MITEL MT90820AL, MT90820AP Datasheet

CMOS ST-BUS FAMILY

MT90820

Large Digital Switch (LDX)

Advance Information

Features

• 2,048 channel non-blocking switch

• Maint ains fr ame integri ty on co ncat enate d

channels.

• Per-chan nel s electi on of mi nim um or co nstan t

throughput delay

• Serial s treams a t 2.0 48, 4. 096 or 8.1 92Mb /s

• Frame offset delay measurement

• Program mab le fr ame d elay offs et

• Per-chan nel thre e-stat e cont rol

• Per-chan nel m essa ge mo de

• Control interface compatible to Intel/Motorola

CPUs

• Block pro gramm ing feature for con nec tion

memory

• ST-BUS/MVIP and GCI interfaces

• Test Port compatible to IEEE-1149.1 standard

Applications

• Medium and l arge swi tchi ng platf orm s

• C.O. switches

• CTI application

• Voice/data mult iple xer

• Digital cross connects

• ST-BUS/HMVIP interface functions

ISSUE 1 May 1995

Ordering Information

MT9082 0A P 84 Pin P L CC

MT90820AL 100 Pin QFP

-40 to +85°C

Description

The Large Digital Switch (LDX) is an advanced

digital switch allowing the users to build up to 2048

channel non-blocking switch. The serial interface can

be at 2, 4 or 8 Mb/s compatible to ST-BUS/MVIP/

HMVIP or GCI standards. The LDX can be

programmed to provide either minimum or constant

throughput delay on all its channels. The device also

features three-state control and message mode on

per-channel basis.

To manage the problem of line delays, each input

stream can have an individually programmed input

frame offset delay. The offset delay can be calibrated

with a dedicated frame measurement facility inside

the device.

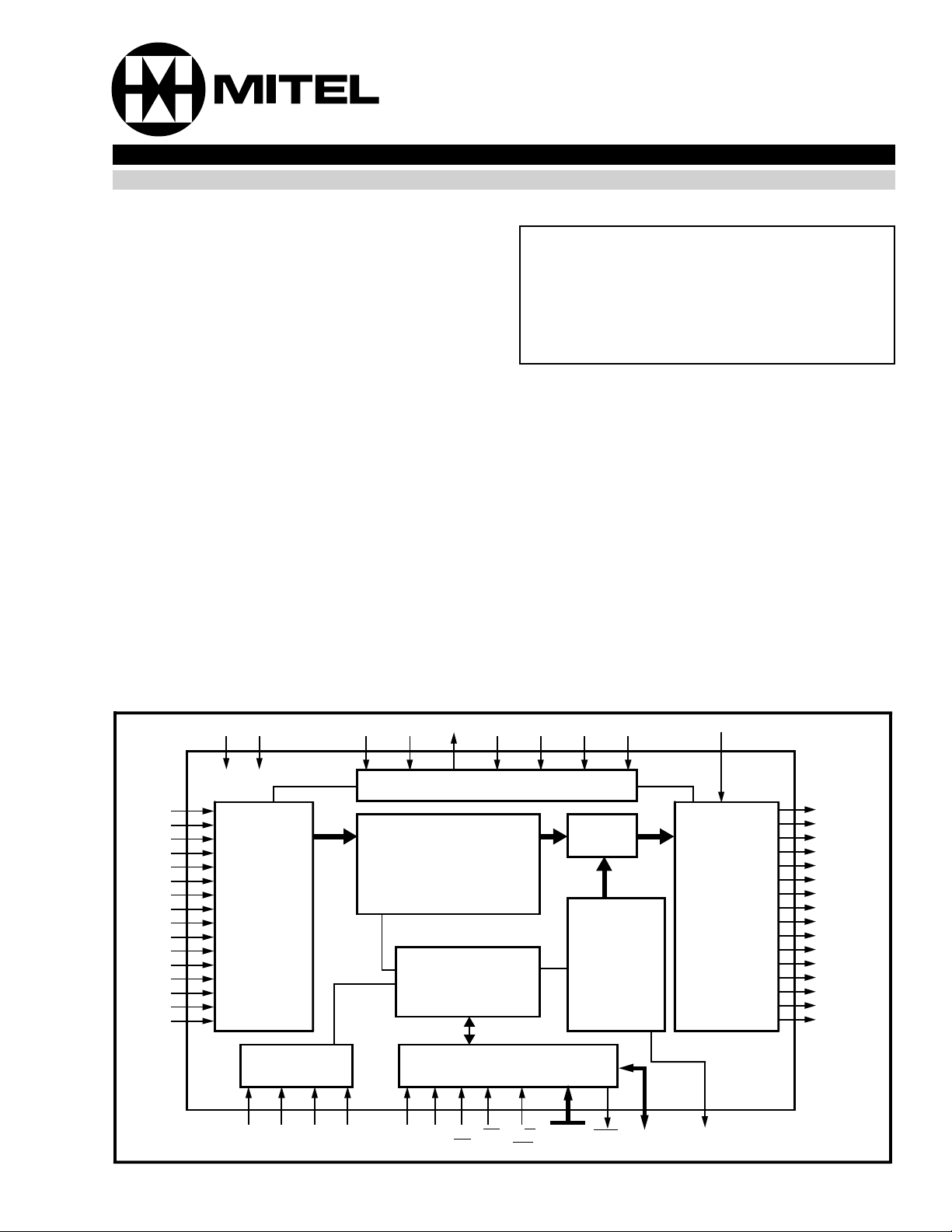

STi0

STi1

STi2

STi3

STi4

STi5

STi6

STi7

STi8

STi9

STi10

STi11

STi12

STi13

STi14

STi15

V

DD

Paralle l

Converter

CLK

V

SS

Serial

to

Timing

Unit

FRM FE/ AS/ IM DS

HMVIP

HCLK

TMS

TDI TDO TEST RESETBTCK TRSTB

Multi pl e Buf fer

Data Mem ory

ALE

Figure 1 - Functional Block Diagram

Test Port

Interna l

Registers

Microprocessor Interface

RD

CS R/W

WR

A7-A0

Output

MUX

Connectio n

Memory

D15-D8/

DTA

AD7-AD0

ODE

Parallel

to

Serial

Converter

CSTo

STo0

STo1

STo2

STo3

STo4

STo5

STo6

STo7

STo8

STo9

STo10

STo11

STo12

STo13

STo14

STo15

2-179

MT90820 CMOS Advance Information

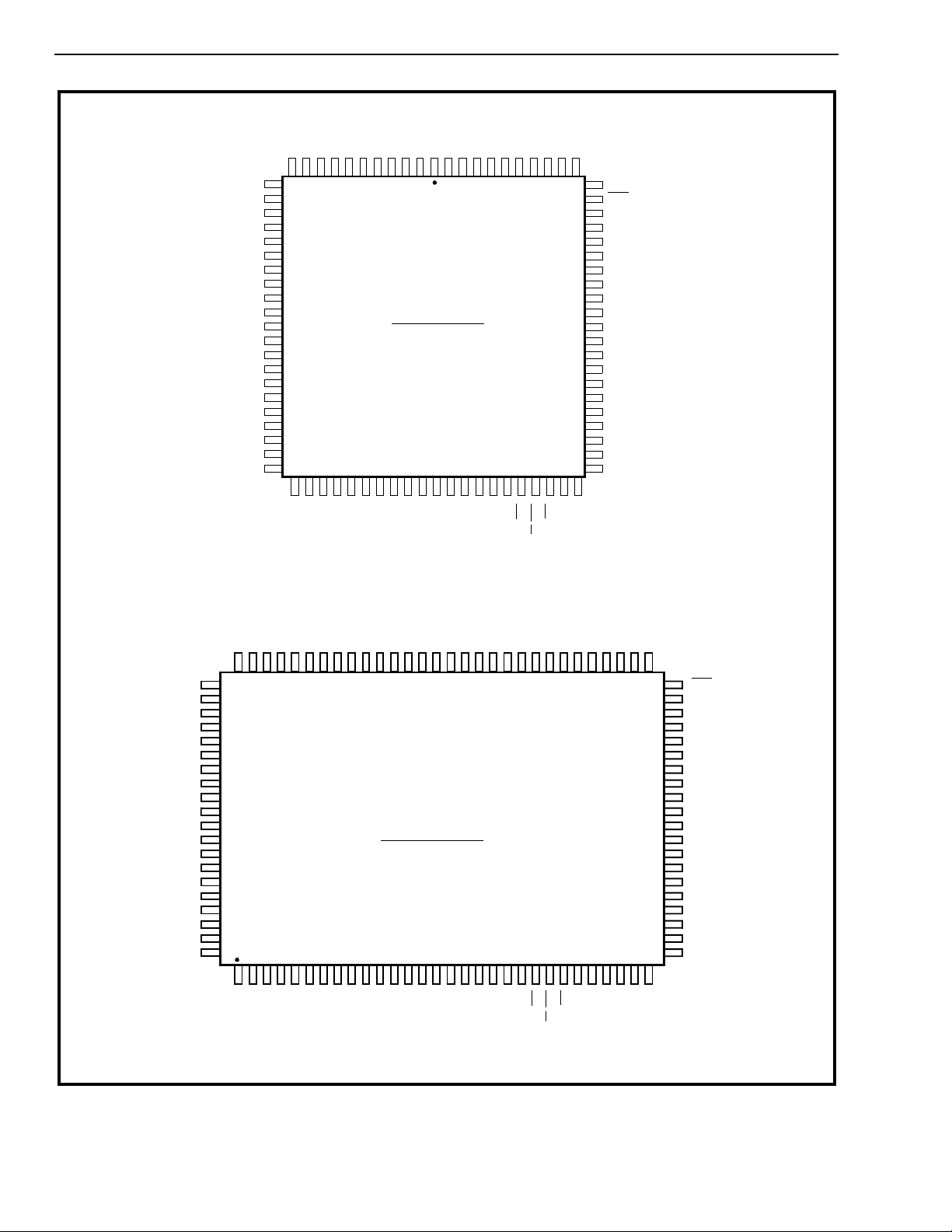

ODE

STo0

STo1

STo2

STo3

STo4

STo5

STo6

STo7

VSS

STi0

STi1

STi2

STi3

STi4

STi5

STi6

STi7

STi8

STi9

STi10

STi11

STi12

STi13

STi14

STi15

FRM

FE/HCLK

VSS

CLK

VDD

VDD

STo8

STo9

ST o10

STo11

ST012

ST o13

ST o14

ST015

VSS

8

6

4

12

10

14

16

18

20

22

24

26

28

30

32

34

36

38

2

84

84 PIN PLCC

40

44

42

82

80

46

48

VSS

CSTo

74

78

76

DTA

D15

72

D14

D13

70

D12

D1 1

68

D10

D9

66

D8

64

VSS

VDD

62

AD7

AD6

60

AD5

AD4

58

AD3

AD2

56

AD1

AD0

54

50

52

VSS

STi0

STi1

STi2

STi3

STi4

STi5

STi6

STi7

STi8

STi9

STi10

STi1 1

STi12

STi13

STi14

STi15

FRM

FE/HCLK

VSS

CLK

82

84

86

88

90

92

94

96

98

100

NC

NC

NC

NC

TMS

VSS

TDI

ST015

TDO

STo14

TCK

TEST

TRSTB

RESETB

STo10

ST o11

ST012

STo13

100 PIN PQFP

\RW

R/W

ST o1

CS

ST o0

IM

AS/ALE

ODE

VSS

CSTo

NC

NC

NC

NC

525456586062646668707274767880

50

DTA

A7

A6

A5

A4

A3

A2

A1

A0

HMVIP

ST o6

ST o7

VSS

VDD

ST o8

ST o9

DS/RD

ST o2

ST o3

ST o4

ST o5

D15

48

D14

D13

46

D12

D11

44

D10

D9

42

D8

VSS

40

VDD

AD7

38

AD6

AD5

36

AD4

AD3

34

AD2

AD1

32

AD0

22 24 26 28 30

2018161412108642

VSS

2-180

NC

NC

NC

NC

A1

TDI

TCK

TDO

TMS

VDD

TRSTB

A0

TEST

HMVIP

RESETB

Figure 2 - Pin Connections

A2

A3

A4

A5

A6

A7

DS/RD

\RW

R/W

CS

AS/ALE

IM

NCNCNC

NC

Advance Information CMOS MT90820

Pin Description

Pin #

84 100

Name Description

1, 11,

30, 54

64, 75

31,

41,

56,

V

SS

Ground.

66,

76, 99

2, 32,635, 40,

V

DD

+5 Volt Power Sup ply.

67

3 - 10 68-75 STo8 - 15 Data Strea m Output 8 to 15: Serial data Ou tput stream . These stream may

have data rates of 2.048, 4.096 or 8.192 M b/s.

12 - 2781-96 STi0 - 15 Data Stream Input 0 to 15: Serial data input stream. These stream may have

data rates of 2.048, 4.096 or 8.192 .

28 97 FRM Frame Pulse (input): This input accepts and automatically identifies frame

synchronization signals formatted according to ST-BUS and GCI interface

specificatio ns, when HM VIP pin =0.

When HMVIP pin =1, FRM input accepts a negative frame pulse which confo rms

to HMVIP form a ts.

29 98 FE/HCLK Frame Measurement input, when HMVIP pin = 0.

4.096MHz Clock in put, when HMVIP pin = 1.

31 100 CLK Clock (input): Serial clock for shifting data in/out on the serial stream.

33 6 TMS When 1, enable test mod e for production test ing.

34 7 TDI Test Data Input.

35 8 TDO Test Data Output.

36 9 TCK Test Clock input.

37 10 TRSTB Test Reset Input: When 0, resets the test circuit.

38 11 IC Internal Connection: keep at 0 for normal operation.

39 12 RESETB Device Reset Input: When 0, resets the device.

40 13 HMVIP HMVIP mode input. When 1, enables HMVI P interf a ce.

When 0, the device operates in ST-BUS/GCI mode.

41 - 4814-21 A0 - A7 Address 0 - 7(Input): When non-multiplexed CPU bus is selected, t hese lines

provide the A0 - A7 address lines to internal memories.

49 22 DS/RD Data Strobe/Read (input): When non-mul tiplexed CP U bus or Motorola

multiplexed bus are selected, this input is DS. This active high input works in

conjunction with CSB to enable read and write operation .

For Intel multiplexed bus, this input is RDB. This active low input sets the data bus

lines (AD0-AD7, D8-D15) as outputs.

50 23 R/W\WR Read/Write \ Write (Input): In case of non-multiplexed and Motorola m ultiplexed

buses, this input is Read/Write. This input controls the dire ction of the data bus

lines (AD0 - AD7, D8-D15) during a microprocessor access.

51 24 CS Chip Select (Input ): Active low input enabling a microprocessor access of the

device.

2-181

Loading...

Loading...