MITEL MT9079AP, MT9079AC, MT9079AE, MT9079AL Datasheet

CMOS ST-BUS FAMILY

MT9079

Advanced Controller for E1

Features

• Meets appl icabl e requi reme nts of CCIT T

G.704, G. 706, G.732, G.7 75, G. 796, I.431 a nd

ETSI ETS 300 011

• HDB3, RZ, NRZ (fibre interf ace) an d bipo lar

NRZ line code s

• Data link acce ss an d na tional bit buffers (f ive

bytes each)

• Enhanced al arms, perform anc e mon itorin g and

error insertion

• Maskable interrupts for alarms, receive CAS bit

changes, exception conditions and counter

overflow s

• Automatic in terw orking b etwe en C RC-4 and

non-CRC-4 m u lti fram in g

• Dual transm it and re cei ve 16 by te circ ular

channel b uffers

• Two frame receive elastic buffer with controlled

slip directi on ind icat ion an d 26 ch annel

hysteresi s (208 UI wande r tole rance)

• CRC-4 updating algorithm for intermediate path

points of a messa ge- based dat a link app licati on

Applications

• Primary rate ISDN netw ork node s

• Digital Access Cross-connect (DACs)

• CO and PABX switching equipment interfaces

• E1 add/dr op mu ltiple xers a nd ch annel bank s

• Test equipme nt and satel lite in terfac es

ISSUE 2 May 1995

Ordering Information

MT9079AC 40 Pin Cerami c DIP

MT9079A E 40 Pin Pl astic D IP

MT9079A L 44 Pin QFP

MT9079A P 44 Pin PLC C

-40° to 85°C

Descript io n

The MT9079 is a feature rich E1 (PCM 30, 2.048

Mbps) link framer and controller that meets the latest

CCITT and ETSI requirements.

The MT9079 will interface to a 2.048 Mbps

backplane and can be controlled directly by a

parallel processor, serial controller or through the

ST-BUS.

Extensive alarm transmission and reporting, as well

as exhaustive performance monitoring and error

diagnostic features make this device ideal for a wide

variety of applications.

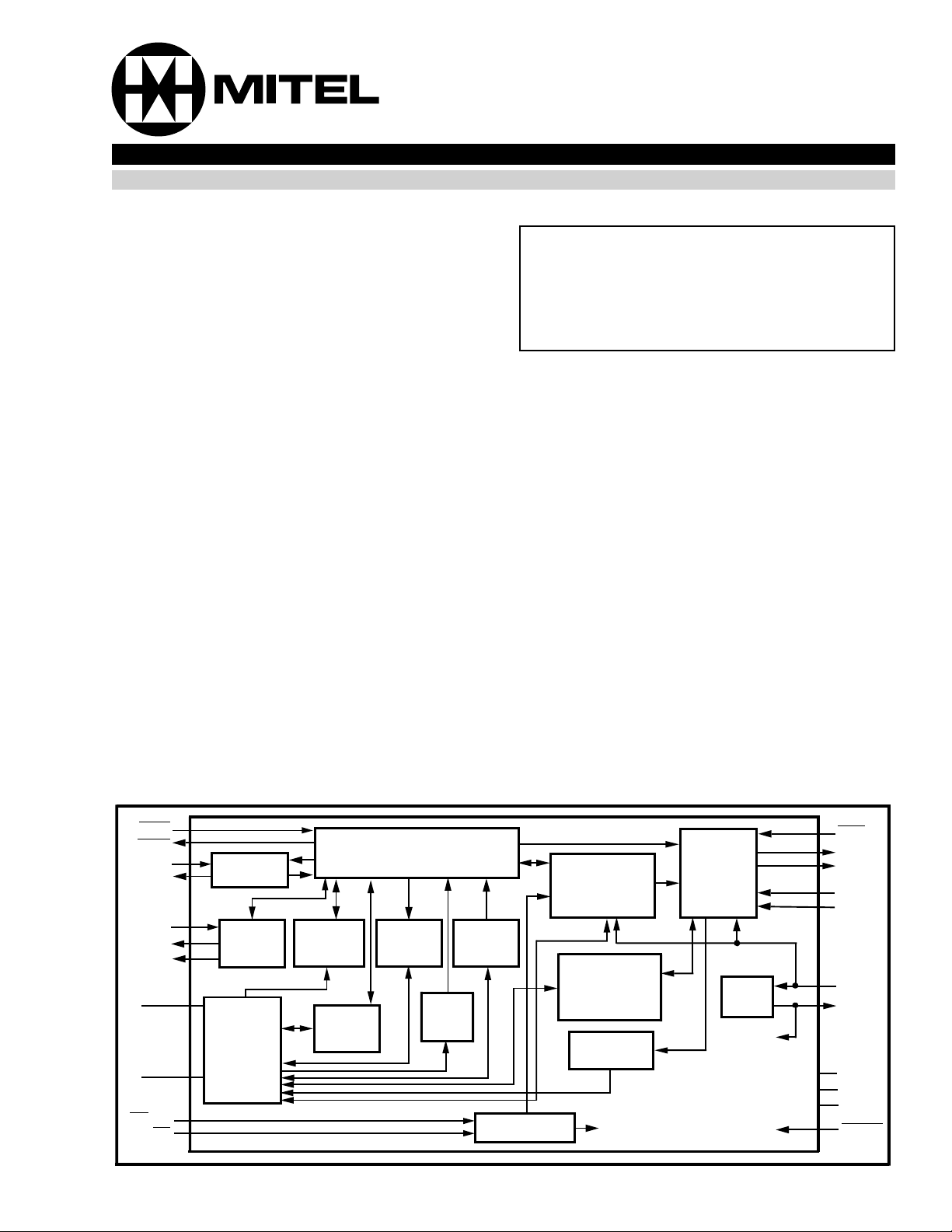

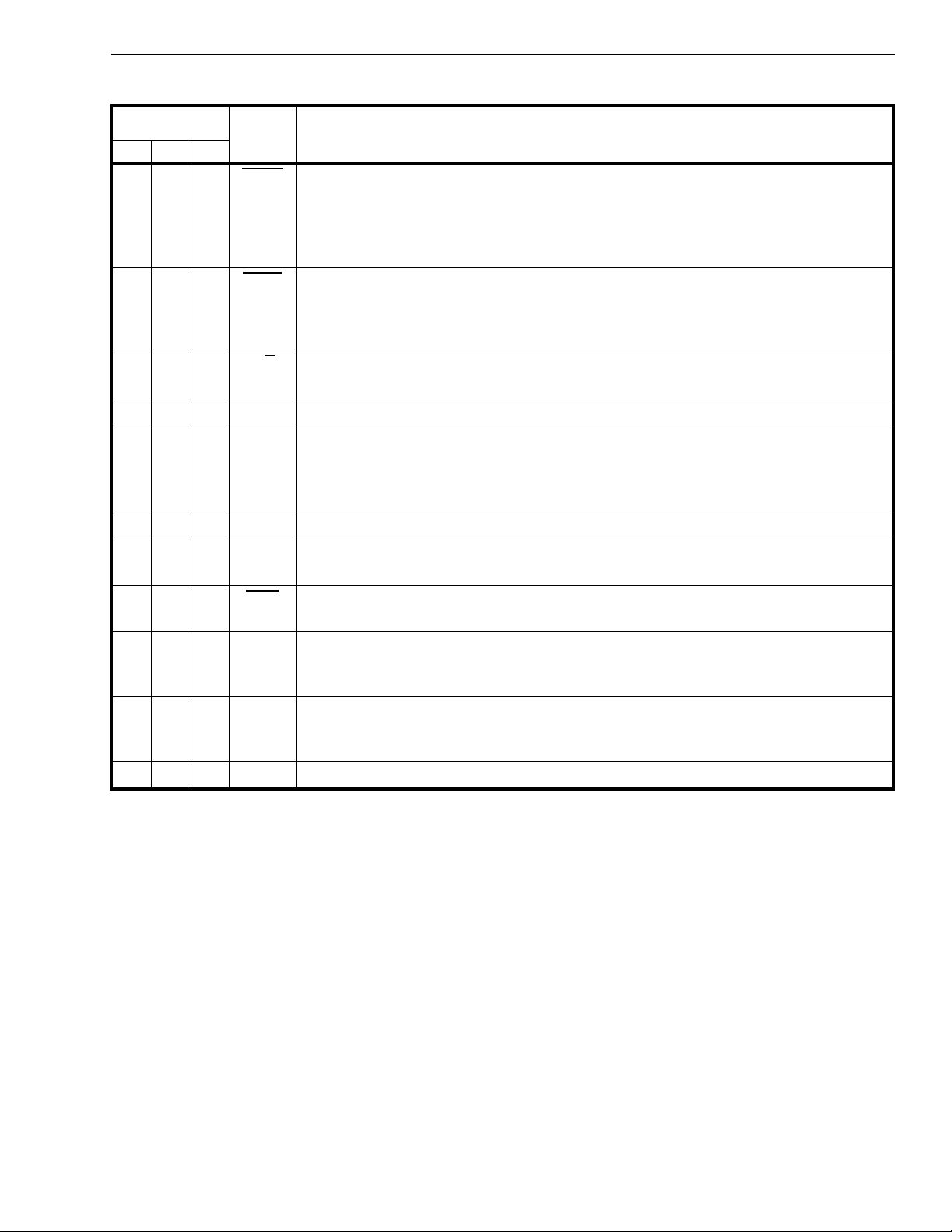

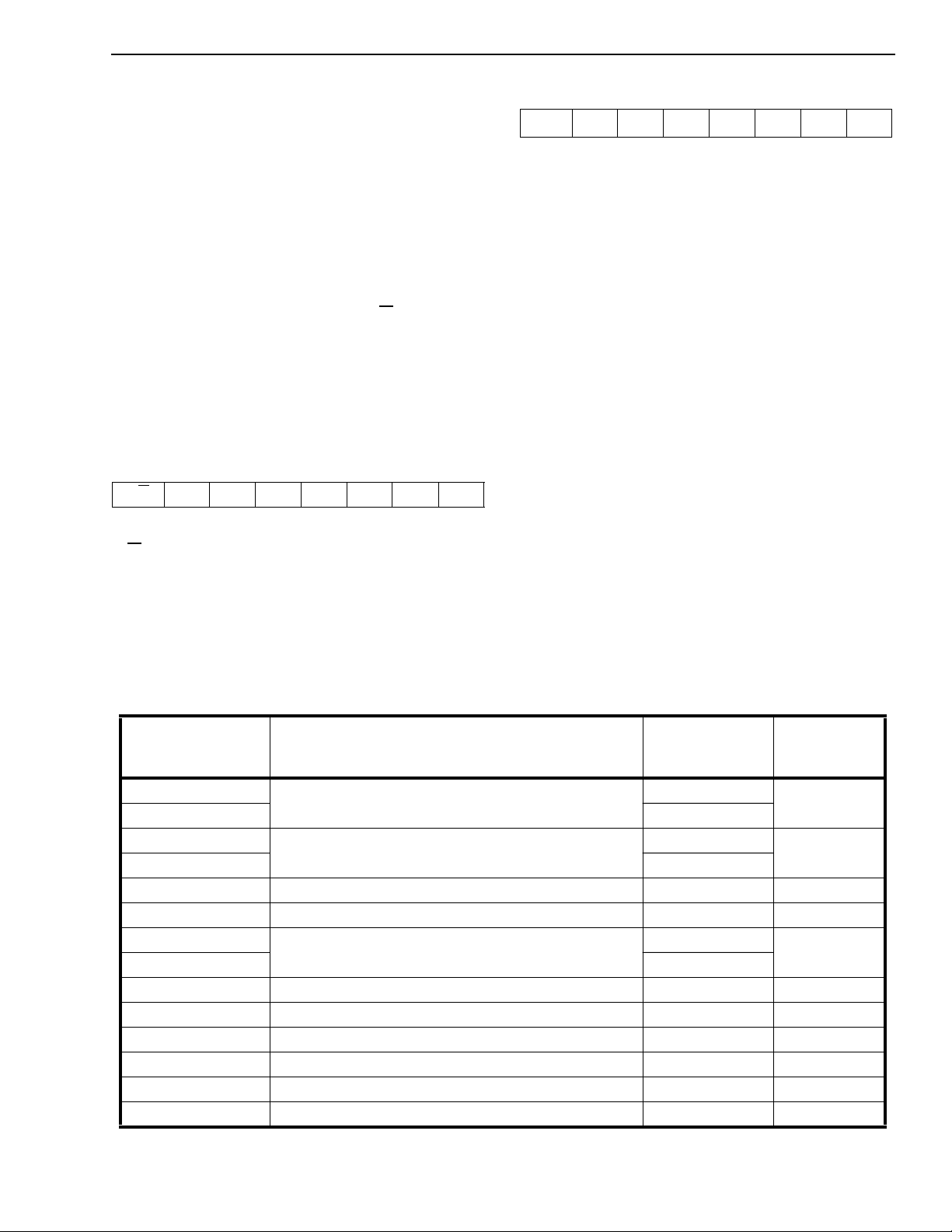

TxMF

RxMF

DSTi

DSTo

TxDL

RxDL

DLCLK

Control

Interface

(fig. 3)

C4i/C2i

F0i

Port

Data

Interface

Data

Link

Buffer

Control

Interface

National

Bit

Buffer

ABCD

Signal

Buffer

Transmit & Receive

Frame MUX/DEMUX

Test

Code

Gen.

Dual 16

Byte Tx

Dual 16

Byte Rx

Buffer

Buffer

ST-BUS Timing

2 Frame Rx

Elastic

Buffer With

Slip Control

Performance

Monitoring &

Alarm

Control

Phase

Detector

Circuit

Timin g

Figure 1 - Functional Block Diagram

PCM 30

(E1)

Link

Interface

to all registers

and counters

÷

256

Circuit

Timing

TAIS

TxA

TxB

RxA

RxB

E2i

E8Ko

V

DD

V

SS

IC

RESET

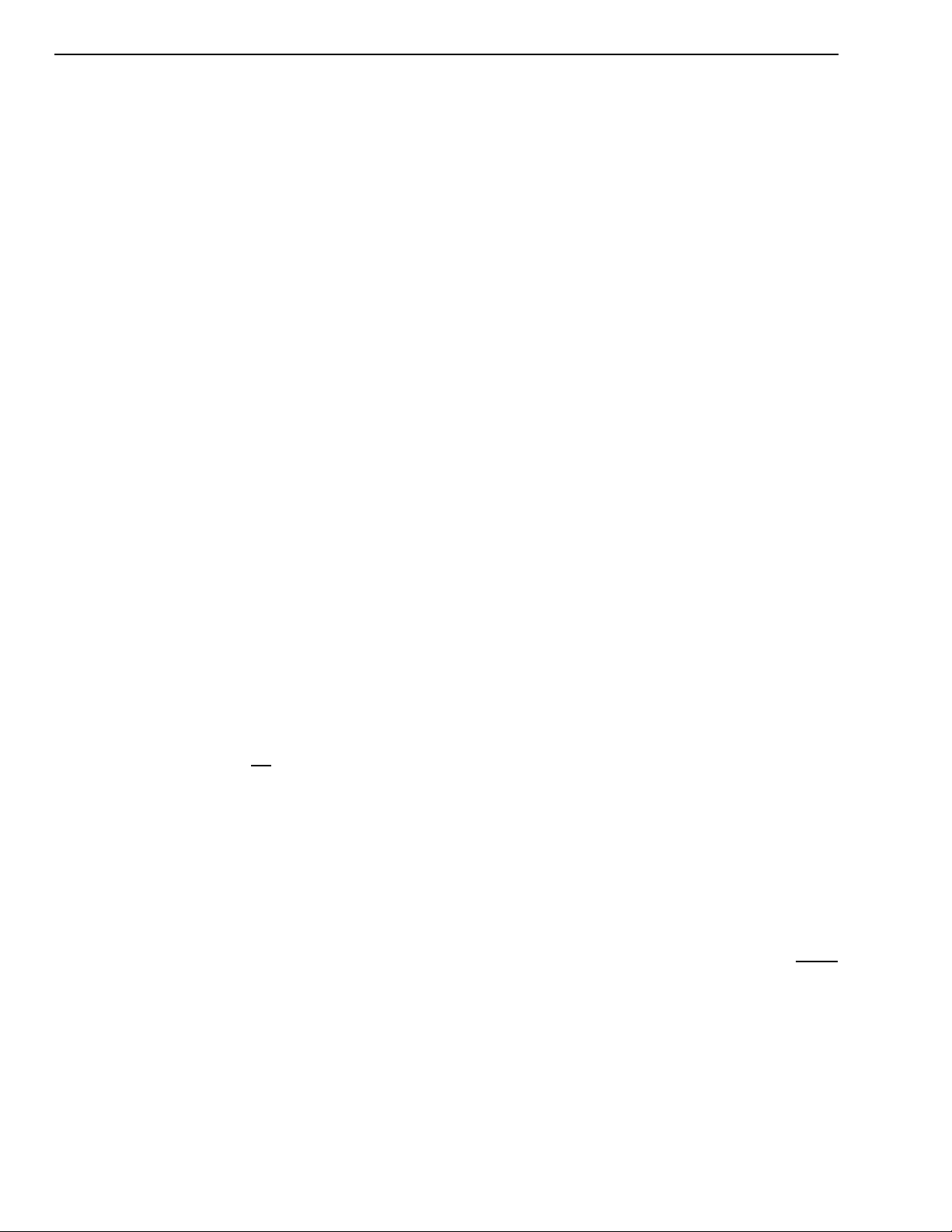

4-237

MT9079

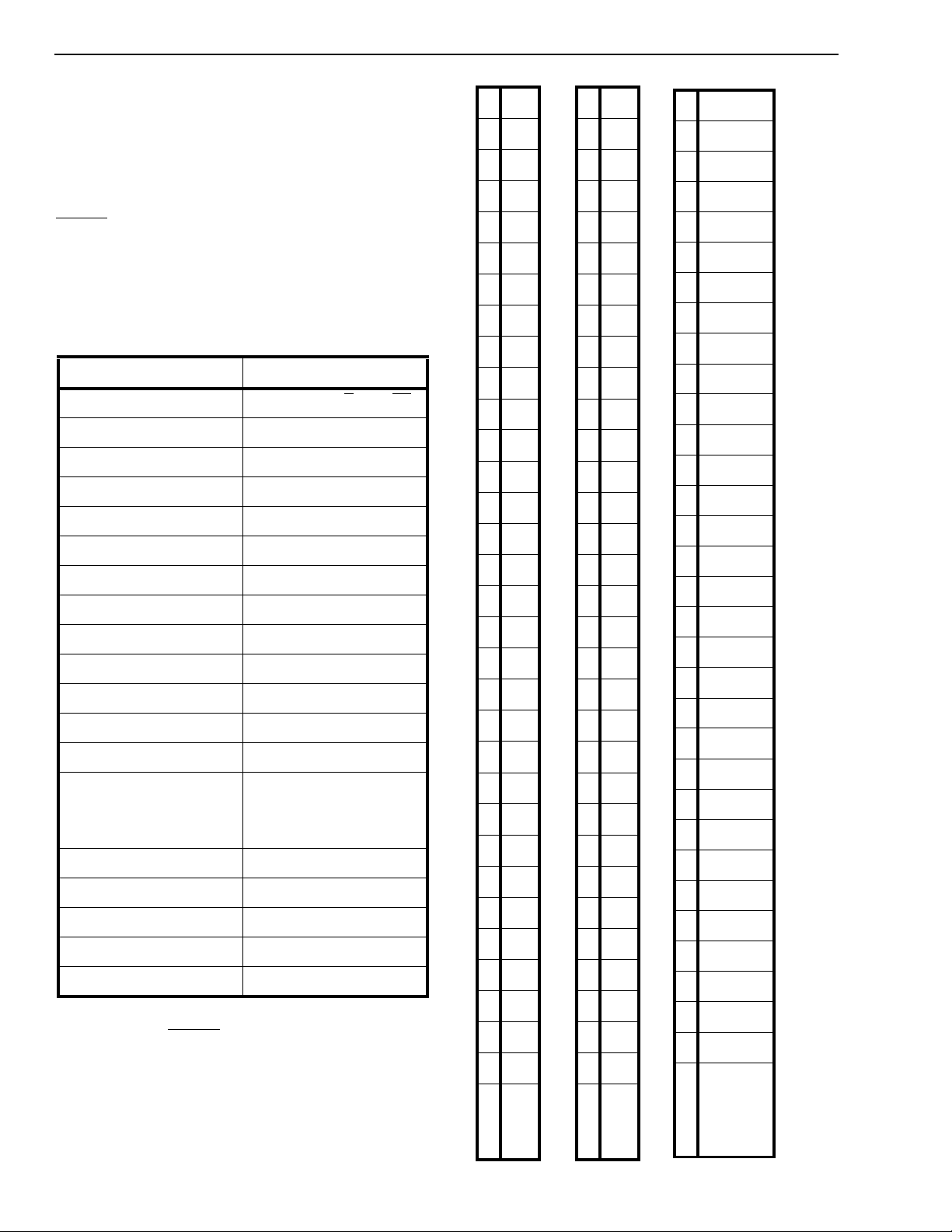

RESET

DSTo

RxDL

TxDL

DLCLK

D0\SIO\CSTo0

IRQ

D1

D2

D3

D4

D5

D6

D7

VDD

AC4\ST/SC

AC3

AC2

AC1

AC0

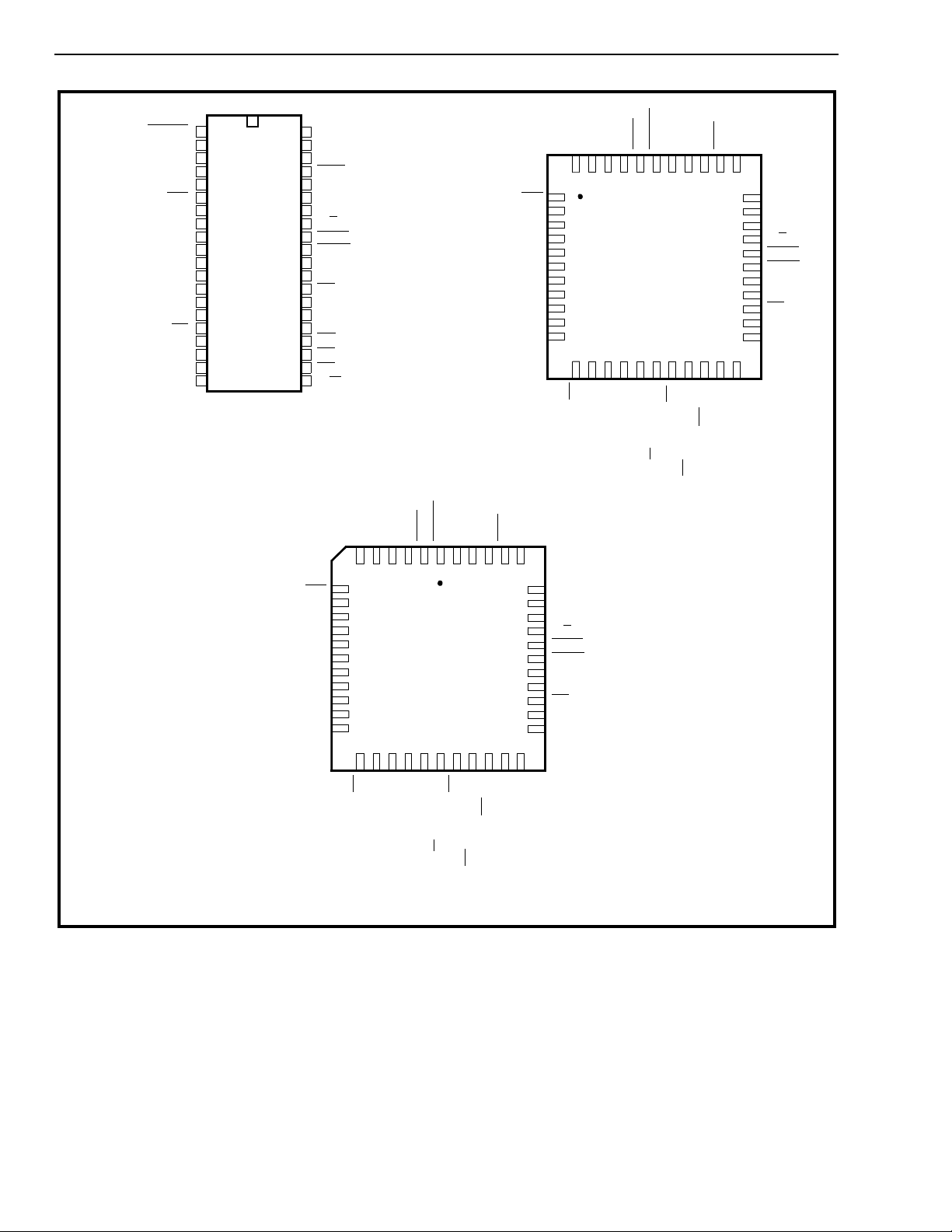

40 PIN CERDIP/PLASTIC DIP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

D0\SIO\CSTo0

40

IC

39

TxA

TxB

38

37

TAIS

CSTo1

36

CSTi2

35

VSS

34

S/P

33

32

TxMF

31

RxMF

DSTi

30

29

E8Ko

28

F0i

27

RxA

RxB

26

E2i

25

C4i

24

23

DS

22

CS

21

R/W\RxD\CSTi0

IRQ

D1

D2

D3

D4

D5

D6

D7

VDD

NC

/C2i

\SCLK\CSTi1

TxDL

DLCLK

NC

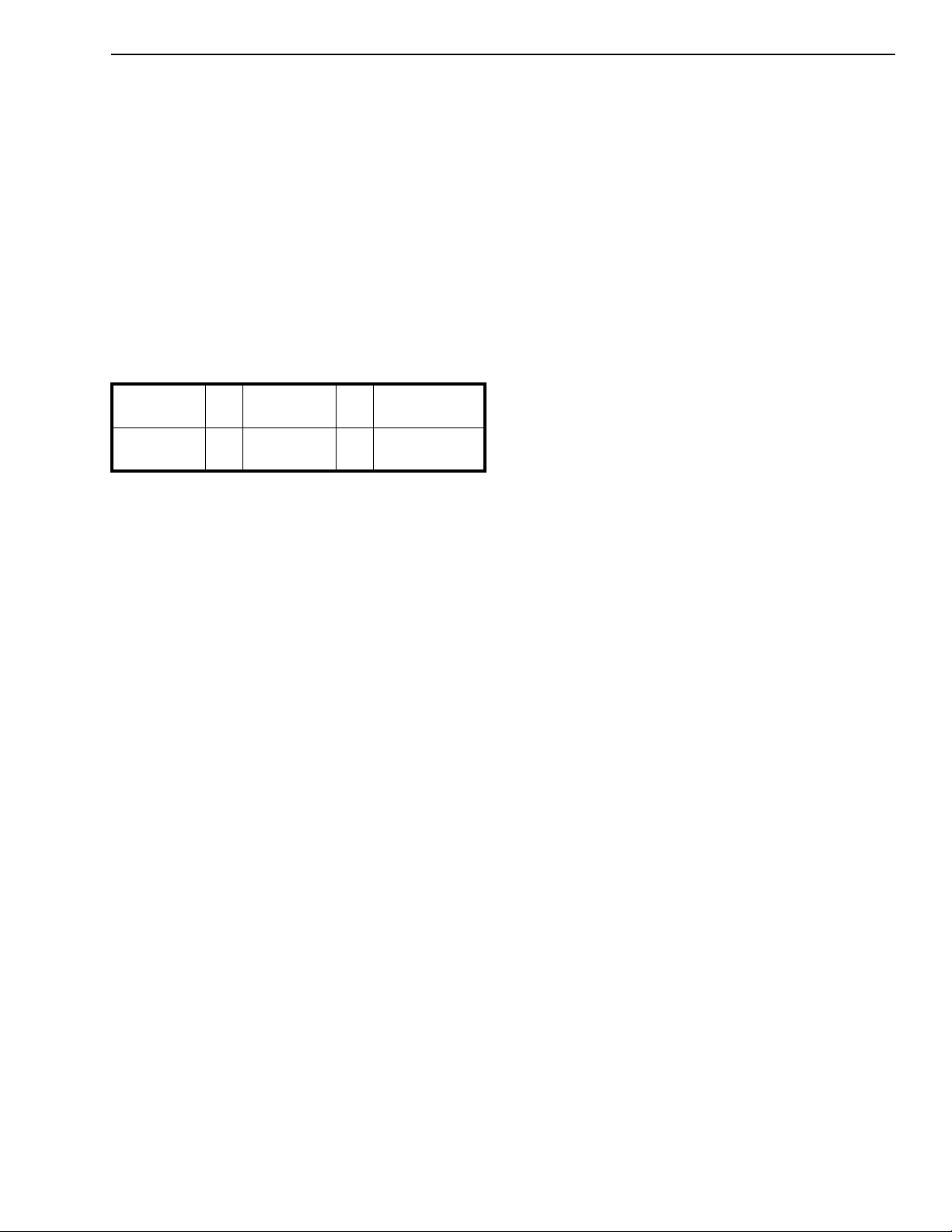

65432

7

8

9

10

11

12

13

14

15

16

17

1819202122

RxDL

D0\SIO\CSTo0

DSTo

IC

RESET

4443424140

23

2425262728

NC

4443424140

D1

D2

D3

D4

D5

D6

D7

NC

CSTo1

1

2

3

4

5

6

7

8

9

10

11

1213141516

A4\ST/SC

NC

CSTi2

VSS

S/P

TxMF

RxMF

DSTi

E8Ko

F0i

RxA

RxB

AC3

AC2

AC1

44 PIN QFP

IRQ

VDD

TxA

TxB

TAIS

39

38

37

36

35

34

33

32

31

30

29

IC

RESET

3837363534

39

17

1819202122

CS

AC0

R/W\RxD\CSTi0

TxA

\SCLK\CSTi1

DS

TxB

TAIS

CSTo1

33

NC

32

CSTi2

VSS

31

S/P

30

29

TxMF

RxMF

28

DSTi

27

E8Ko

26

F0i

25

RxA

24

23

RxB

NC

E2i

/C2i

C4i

DSTo

RxDL

TxDL

DLCLK

4-238

AC3

AC2

A4\ST/SC

44 PIN PLCC

AC1

AC0

CS

R/W\RxD\CSTi0 1

\SCLK\CSTi1

DS

E2i

NC

/C2i

C4i

Figure 2 - Pin Connection

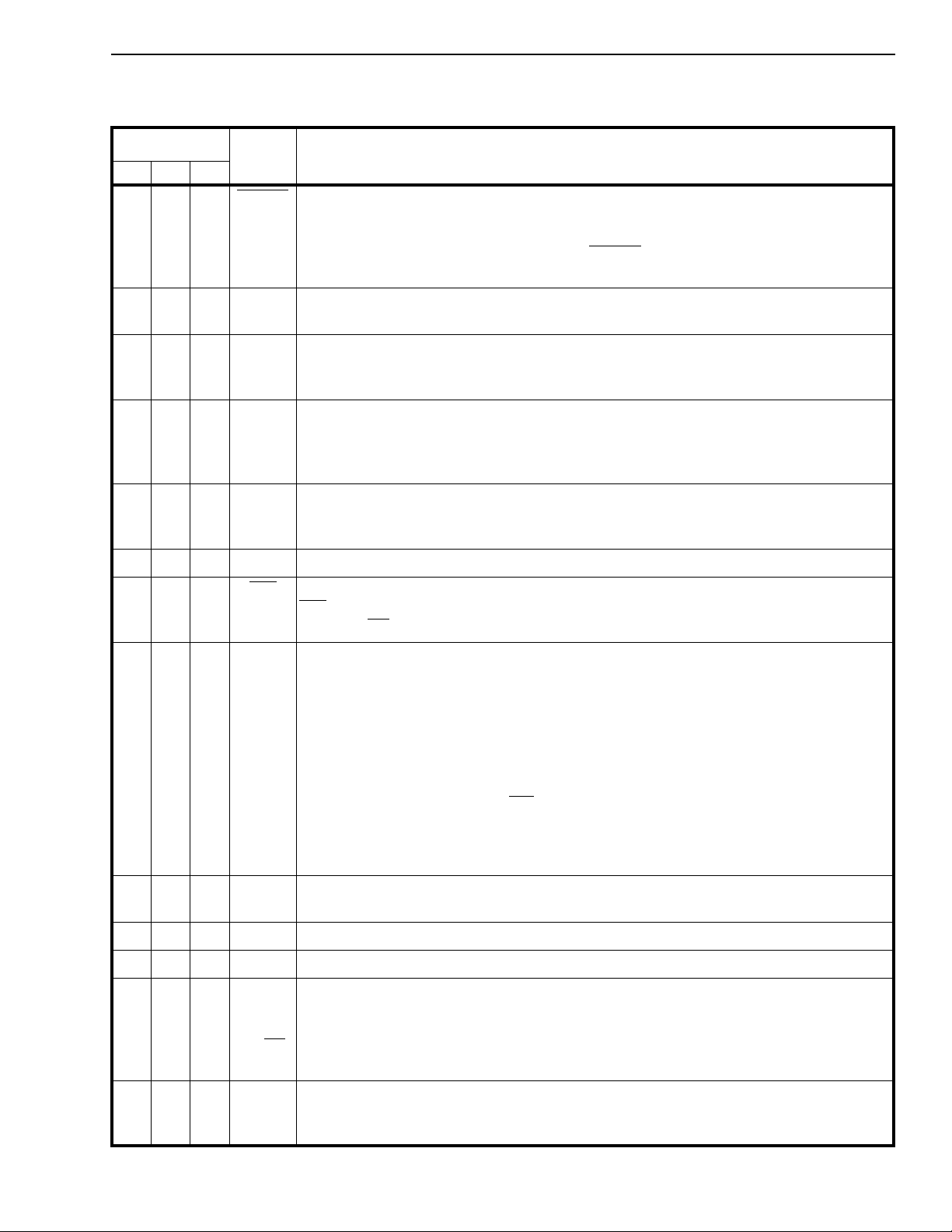

Pin Description

MT9079

Pin #

DIP PLCC QFP

1 1 39 RESET RESET (Input): Low - maintains the device in a reset condition. High - normal

2240DSToData ST-BUS (Output): A 2.048 Mbit/s serial output stream which cont ains th e 3 0

3 3 41 RxDL Receive Data Link (Output): A 4 kbit/s serial stream which is demultiplexed from a

4 4 42 TxDL Transmit Data Link (Input): A 4 kbit/s serial stream which is multiplexed into a

5 5 43 DLCLK Data Link Clock (Output): A 4 kHz clock signal used to clock out DL data (RxDL) on

-644NCNo Connection.

671 IRQ

Name Description (see notes 1, 2 and 3)

operation. The MT90 79 should be reset af ter power-up. The time const ant for a

power-up reset circuit (see Figure 11) must be a minimum of five times the rise time of

the power supply. In normal operation, the RESET

of 100 nsec. to reset the device.

PCM or data channels re ceived from the PCM 30 line. See Figure 4b.

selected national bit (non-frame ali gnm ent signa l) of the PCM 30 receive signal.

Received DL data is clocked out on the rising edge of DLCLK, see Figure 20.

selected national bit (non-frame ali gnment signa l) of the P CM 30 transmi t signal.

Transmit DL data is clocked in on the rising edge of internal clock IDCLK, see Figure

21.

its rising edge. It can also be used to clock DL data in and out of external serial

controllers (i.e., MT8952). See TxDL and RxDL pin descriptions.

Interrupt Request (Outp ut): Low - interrupt request. High - no interrup t request.

is an open drain output that should be connected to VDD through a pull-up resistor .

IRQ

An active CS

signal is not required for this pin to function.

pin must be held low for a minimum

782 D0

SIO

CSTo0

[ST]

8-14 9-15 3-9 D1-D7

15 16 10 V

-1711 NCNo Connection.

16 18 12 AC4

ST/SC

[ST S]

17-2019-2213-16AC3-AC

Data 0 (Three-state I/O): The least significant bit of the bidirecti onal dat a bus of the

[P]

parallel processor interface.

Serial Input/Output (Three state I/O): This pin function is used in serial controller

[S]

mode and can be configured as control data input/ out put for Intel operat ion

to controller pin RxD). Input data is sampled LSB first on the rising edge of SCLK; data

is output LSB first on the falling edge of SCLK. It can also be configured as the control

data output for Mot orola and Nat ional Microwire operation (dat a outp ut MSB first on

the falling edge of SCLK). See CS

Control ST-BUS Zero (Output): A 2.048 Mbit/s serial status stream which provides

device status, performance mon itoring, alarm status and phase stat us data.

Data 1 to Data 7 (Three-state I/O): These signals, combined wit h D0, f orm th e

[P]

bidirectional data bus of the parallel p rocessor interface (D7 is the most significant bit).

Positive Power Supply (Input): +5V ± 10%.

DD

Address/Co ntro l 4 (Input): The most signif icant addre ss and control input for the

[P]

non-multiplexed parallel processor interfa ce.

ST-BUS/Serial Co ntrol ler (Inp u t): High - selects ST-BUS mode of operation.

Low - selects serial controller mode of ope ratio n.

Address/Control 3 to 0 (Inputs): Address and control inputs for the

0

non-multiplexed parallel processor interface. AC0 is the least significant input.

[P]

(connect

pin description.

4-239

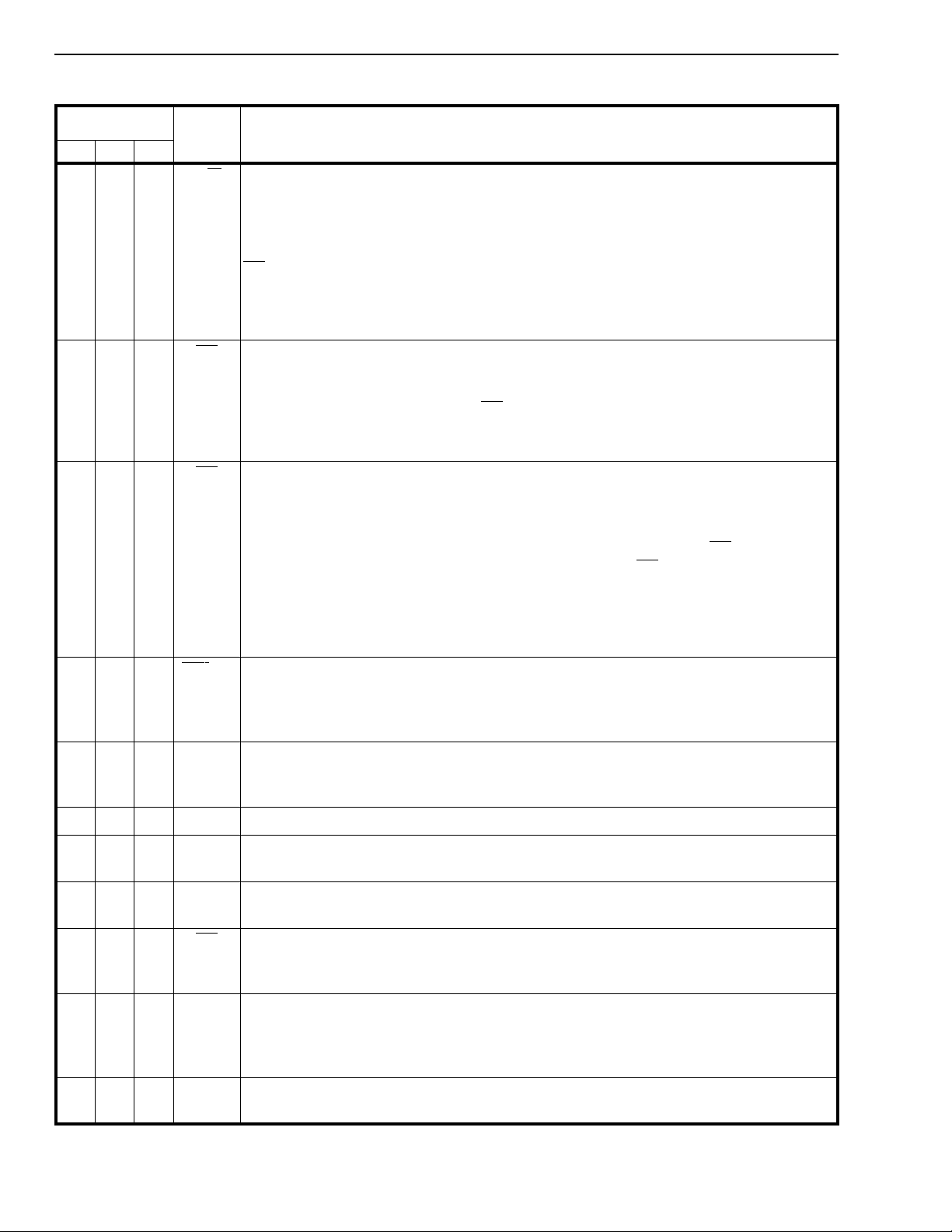

MT9079

Pin Description (Continued)

Pin #

DIP PLCC QFP

21 23 17 R/W

22 24 18 CS

23 25 19 DS

Name Description (see notes 1, 2 and 3)

[P]

RxD

[S]

CSTi0

[ST]

[SP]

[P]

SCLK

[S]

Read/Write (Input): High - the parallel processor is reading data from the MT9079.

Low - the parallel processor is writing data to the MT9079.

Receive Data (Input): This pin function is used in Motorola and National Microwire

serial controller mode. Data is sampled on the rising edge of SCLK, MSB first. See

pin description.

CS

Control ST-BUS Zero (Input): A 2.048 Mbit/s serial control stream which contains

the device control, mode selection, and performance monitoring control.

Chip Select (Input): Low - selects the MT9079 parallel processor or serial controller

interface. High - the parallel processor or serial controller interface is idle and all

bus I/O pins will be in a high impedance state. When controller mode is selected,

the SCLK input is sampled when CS

Intel mode; if SCLK is low it will be in Motorola/National Microwire mode. This pin

has no function (NC) in ST-BUS mode.

Data Strobe (Input): This input is the active low data strobe of the parallel

processor interface.

Serial Clock (Input): This is used in serial controller mode to clock serial data in

and out of the MT9079 on RxD and SIO. If SCLK is high when CS

device will be in Intel mode; if SCLK is low when CS

Motorola/National Microwire mode.

is brought low. If SCLK is high the device in is

goes low, the

goes low, it will be in

CSTi1

[ST]

24 26 20 C4i

25 27 21 E2i 2.048 MHz Extracted Clock (Input): This clock is extracted from the received

-2822 NCNo Connection.

26 29 23 RxB Receive B (Input): Received split phase unipolar signal decoded from a bipolar line

27 30 24 RxA Receive A (Input): Received split phase unipolar signal decoded from a bipolar line

28 31 25 F0i

29 32 26 E8Ko Extracted 8 kHz Clock (Output): An 8 kHz signal generated by dividing the

Control ST-BUS One (Input): A 2.048 Mbit/s serial control stream which contains

the per timeslot control programming.

/C2i 4.096 MH z and 2.048 MHz Sys tem Cloc k (Inp ut): This is master clock for the serial

PCM data and ST-BUS sections of the MT9079. The MT9079 automat ically det ects

whether a 4.096 or 2.048 MHz clock is being used. See Figure 22 for timing

information.

signal. Its rising edge is used internally to clock in data received on RxA and RxB.

See Figure 29.

receiver. Receives RZ and NRZ bipolar signals. See Figures 29 and 31.

receiver. Receives RZ and NRZ bipolar signals. See Figurs 29 and 31.

Frame Pulse (Input): This is the ST-BUS frame synchronization signal which

delimits the 32 channel frame of all ST-BUS streams, as well as DSTi and DSTo in

all modes.

extracted 2.048 MHz clock (E2i) by 256 and aligning it with the received PCM 30

frame. The 8 kHz signal can be used to synchronize the system clock with the

extracted 2.048 MHz clock. E8Ko is high when 8KSEL=0. See Figure 27.

30 33 27 DSTi Data ST-BUS (Input). A 2.048 Mbit/s serial stream which contains the 30 PCM or

data channels to be transmitted on the PCM 30 line. See Figure 4a.

4-240

Pin Description (Continued)

MT9079

Pin #

DIP PLCC QFP

31 34 28 RxMF

32 35 29 TxMF

33 36 30 S/P

34 37 31 V

35 38 32 CSTi2 Control ST-BUS Input Two (Input): A 2.048 Mbit/s ST-BUS control stream which

-3933 NCNo Connection.

36 40 34 CSTo1 Control ST-BUS Output One (Output): A 2.048 Mbit/s serial status stream which

Name Description (see notes 1, 2 and 3)

Receive Multiframe Boundary (Output): An output pulse delimiting the received

multiframe bounda ry. The next frame ou tput on the dat a st ream (DSTo) is basic frame

zero on the PCM 30 link. This receive mul tiframe signal can be relat ed to either the

receive CRC multiframe (MFSEL= 1) or the receive signalling multif rame (MFS EL=0).

See Figures 25 and 26.

Transmit Multiframe Boundary (Input): This input is used to set the channel

associated and CRC transmit multiframe boundary. The device will generate its own

multiframe if this pin is held high. This input is pulled high in most applications. See

Figures 24 to 26.

Serial/P aral lel (In pu t): High - serial controll er port or ST-BUS operation.

Low - parallel processor port operation.

Negative Power Supply (Input): Ground.

SS

contains the 30 (ABCDXXXX) transmit signalling nibbles when RPSIG=0. When

RPSIG=1 thi s pin has no function. Only the most significant nibbles of each ST-BUS

timeslot are valid. See Figure 4c.

provides the 30 (ABCDXXXX) receive signalling nibbles.

37 41 35 TAIS

38 42 36 TxB Transmit B (Output): A split phase unipolar signal suitable for use with TxA, an

39 43 37 TxA Transmit A (Output):A split phase unipolar signal suitable for use with TxB, an

40 44 38 IC Internal Connection (Input): Connect to ground for normal operation.

Notes:

1. All inputs are CMOS with TTL co mpatible logic levels.

2. All outputs are CMOS and are compatible with both TTL and CMOS logic levels.

3. See AC Electrical Characteristics - Timing Parameter Measurement Voltage Levels for input and output

voltage thresholds.

Transmit Alarm Indication Signal (Input): High - TxA and TxB will transmit data

normally. Low - TxA and TxB transmits an AIS (all ones signal).

external line driver and a transformer to construct a bipolar PCM 30 line signal. This

output can also transmit RZ and NRZ bipolar signals. See Figures 28 and 30.

external line driver and a transformer to construct a bipolar PCM 30 line signal. This

output can also transmit RZ and NRZ bipolar signals. See Figures 28 and 30.

4-241

MT9079

Functional Description

The MT9079 is an advanced PCM 30 framer that

meets or supports the layer 1 CCITT

Recommendations of G.703, G.704, G.706, G.775,

G.796 and G.732 for PCM 30; I.431 for ISDN

Primary Rate; and T1.102 f or DS1A. It also meets or

supports the layer 1 requirements of ETSI ETS 300

011 and ETS 300 233. Included are all the features

of the MT8979, except for the digital attenuation

ROM and Alternate Digit Inversion (ADI). It also

provides extensive performance monitoring data

collection features.

Control of the MT9079 is achieved through the

hardware selection of either a parallel

non-multiplexed microprocessor port, an Intel or

Motorola serial controller port, or an ST-BUS port.

The parallel port is based on the signals used by

Motorola microprocessors, but it can also be easily

mated to Intel microprocessors (see the Applications

section of this data sheet).

The serial microcontroller interface of the MT9079

will automatically adapt to either Intel or Motorola

signalling. An ST-BUS interface, consisting of two

control and one status stream, may also be selected,

however, the circular and national bit buffers cannot

be accessed in this mode.

The MT9079 supports enhanced features of the

MT8979. The receive slip buffer hysteresis has been

extended to 26 channels, which is suitable for

multiple trunk applications where large amounts of

wander tolerance is required. The phase status word

has been extended to the one sixteenth bit when the

device is clocked with C4. This provides the

resolution required for high performance phase

locked loops such as those described in MSAN-134.

A new feature is the ability to select transparent or

termination modes of operation. In termination mode

the CRC-4 calculation is performed as part of the

framing algorithm. In transparent mode the MT9079

allows the data link maintenance channel to be

modified and updates the CRC-4 remainder bits to

reflect this new data. All channel, framing and

signalling data passes through the device unaltered.

This is useful for intermediate point applications of

an PCM 30 link where the data link data is modified,

but the error information transported by the CRC-4

bits must be passed to the terminating end. See the

Application section of this data sheet.

The MT9079 has a comprehensive suite of status,

alarm, performance monitoring and reporting

features. These include counters for BPVs, CRC

errors, E-bit errors, errored frame alignment signals,

BERT, and RAI and continuous CRC errors. Also,

included are transmission error insertion for BPVs,

CRC-4 errors, frame and non-frame alignment signal

errors, and loss of signal errors.

Dual transmit and receive 16 byte circular buffers, as

well as line code insertion and detection features

have been implemented and can be associated with

any PCM 30 time slot.

A complete set of loopbacks has been implemented,

which include digital, remote, ST-BUS, payload, and

local an d rem o te time slot.

The functionality of the MT9079 has been heighten

with the addition of a comprehensive set of maskable

interrupts and an interrupt vector function. Interrupt

sources consist of synchronization status, alarm

status, counter indication and overflow, timer status,

slip indication, maintenance functions and receive

channel associated signalling bit changes.

The received CAS (Channel Associated Signalling)

bits are frozen when signalling multiframe

synchronization is lost, and the CAS debounce

duration has been extended to be compliant with

CCITT Q.422.

The MT9079 framing algorithm has been enhanced

to allow automatic interworking between CRC-4 and

non-CRC -4 interfaces. Au tomatic basic fr ame alarm

and multiframe alarms have also been added.

The national bits of the MT9079 can be accessed in

three ways. First, through single byte registers;

second, through five byte transmit and receive

national bit buffers; and third, through the data link

pins TxDL , R xD L a n d DLCLK.

4-242

The PCM 30 Interface

PCM 30 (E1) basic frames are 256 bits long and are

transmitted at a frame repetition rate of 8000 Hz,

which results in a aggregate bit rate of 256 bits x

8000/sec.= 2.048 Mbits/sec. The actual bit rate is

2.048 Mbits/sec +/- 50 ppm encoded in HDB3

format. Basic frames are divided into 32 time slots

numbered 0 to 31, see Figure 32. Each time slot is 8

bits in length and is transmitted most significant bit

first (numbered bit 1). This results in a single time

slot data r ate of 8 b i ts x 8 0 00 /s e c. = 64 kb i ts/sec.

It should be noted that the Mitel ST-BUS also has 32

channels numbered 0 to 31, but the most significant

bit of an eight bit channel is numbered bit 7 (see

Mitel Application Note MSAN-126). Therefore,

MT9079

ST-BUS bit 7 is synonymous with PCM 30 bit 1; bit 6

with bit 2: and so on. See Figure 33.

PCM 30 time slot zero is reserved for basic frame

alignment, CRC-4 multiframe alignment and the

communication of maintenance information. In most

configurations time slot 16 is reserved for either

channel associated signalling (CAS or ABCD bit

signalling) or common channel signalling (CCS). The

remaining 30 time slots are called channels and

carry either PCM encoded voice frequency signals or

digital data signals. Channel alignment and bit

numbering is consistent with time slot alignment and

bit numbering. However, channels are numbered 1 to

30 and relate to time slots as per Table 1.

PCM 30

Timeslots

Voice/Dat a

Chann els

0 1 2 3 ....15 16 17 18 19 .... 31

X 1 2 3 . ...1 5 X 16 17 18 .... 30

Table 1 - Time slot to Chan nel Relati on shi p

Basic Frame Alignment

Time slot zero of every basic frame is reserved for

basic frame alignment and contains either a Frame

Alignment Signal (FAS) or a Non-frame Alignment

Signal (NFAS). FAS and NFAS occur in time slot

zero of consecutive basic frames as can be see in

Table 4. Bit two is used to distinguish between a FAS

(bit two = 0) and a NFAS (bit two = 1).

Basic frame alignment is initiated by a search for the

bit sequence 0011011 which appears in the last

seven bit positions of the FAS, see Frame Algorithm

section. Bit position one of the FAS can be either a

CRC-4 remainder bit or an international usage bit.

Bits four to eight of the NFAS (i.e., S

- Sa8) are

a4

national bits, which telephone authorities used to

communicate maintenance, control and status

information. A single national bit can also be used as

a 4 KHz maintenance channel or data link. Bit three,

the ALM bit, is used to indicate the near end basic

frame synchronization status to the far end of a link.

Bit position one of the NFAS can be either a CRC-4

multiframe alignment signal, an E-bit or an

international usage bit. Refer to an approvals

laboratory and national standards bodies for specific

requirements.

CRC-4 Multiframing

The primary purpose for CRC-4 multiframing is to

provide a verification of the current basic frame

alignment, although it can be used for other

functions such as bit error rate estimation. The

CRC-4 multiframe consists of 16 basic frames

numbered 0 to 15, and has a repetition rate of 16

frames X 125 microseconds/frame = 2 msec. CRC-4

multiframe alignment is based on the 001011 bit

sequence, which appears in bit position one of the

first six N FASs of a CR C -4 multiframe.

The CRC-4 multiframe is divided into two

submultiframes, numbered 1 and 2, which are each

eight basic frames or 2048 bits in length.

The CRC-4 frame alignment verification functions as

follows. Initially, the CRC-4 operation must be

activated and CRC-4 multiframe alignment must be

achieved at both ends of the link. At the local end of

a link all the bits of every transmit submultiframe are

passed through a CRC-4 polynomial (multiplied by

4

then divided by X4 + X + 1), which generates a

X

four bit remainder. This remainder is inserted in bit

position one of the four FASs of the following

submultiframe before it is transmitted, see Table 4.

The submultiframe is then transmitted and at the far

end the same process occurs. That is, a CRC-4

remainder is generated for each received

submultiframe. These bits are compared with the bits

received in position one of the four FASs of the next

received submultiframe. This process takes place in

both directions of transmission.

When more than 914 CRC-4 errors (out of a possible

1000) are counted in a one second interval, the

framing algorithm will force a search for a new basic

frame alignment. See Frame Algorithm section for

more details.

The result of the comparison of the received CRC-4

remainder with the locally generated remainder will

be transported to the near end by the E-bits.

Therefore, if E1 = 0, a CRC-4 error was discovered in

a submultiframe one received at the far end; and if

E

= 0, a CRC-4 error was discovered in a

2

submultiframe two received at the far end. No

submultiframe sequence numbers or re-transmission

capabilities are supported with layer 1 PCM 30

protocol. See CCITT G.704 and G.706 for more

details on the operation of CRC-4 and E-bits.

CAS Signall ing Mu lti fram ing

The purpose of the signalling multiframing algorithm

is to provide a scheme that will allow the association

of a specific ABCD signalling nibble with the

appropriate PCM 30 channel. Time slot 16 is

reserved for the communication of Channel

Associated Signalling (CAS) information (i.e., ABCD

signalling bits for up to 30 channels). Refer to CCITT

4-243

MT9079

G.704 and G.732 for more details on CAS

mutliframing requirements.

A CAS signalling multiframe consists of 16 basic

frames (numbered 0 to 15), which results in a

multiframe repetition rate of 2 msec. It should be

noted that the boundaries of the signalling

multiframe may be completely distinct fro m those of

the CRC-4 multiframe. C AS multiframe alignment is

based on a multiframe alignment signal (a 0000 bit

sequence), which occurs in the most significant

nibble of time slot 16 of basic frame zero of the CAS

multiframe. Bit 6 of this time slot is the multiframe

alarm bit (usually designated Y). When CAS

multiframing is acquired on the receive side, the

transmit Y-bit is zero; when CAS multiframing is not

acquired, the transmit Y-bit is one. Bits 5, 7 and 8

(usually designated X) are spare bits and are

normally set to one if not used.

Time slot 16 of the remaining 15 basic frames of the

CAS multiframe (i.e., basic frames 1 to 15) are

reserved for the ABCD signalling bits for the 30

payload channels. The most significant nibbles are

the reserved for channels 1 to 15 and the least

significant nibbles are reserved for channels 16 to

30. That is, time slot 16 of basic frame 1 has ABCD

for channel 1 and 16, time slot 16 of basic frame 2

has ABCD for channel 2 and 17, through to time slot

16 of basic frame 15 has ABCD for channel 15 and

30.

MT9079 Access and Cont rol

The Control Port Interface

The control and status of the MT9079 is achieved

through one of three generic interfaces, which are

parallel microprocessor, serial microcontroller, and

ST-BUS. This control port selection is done through

pins S/P

The parallel microprocessor port (S/P

= AC4) is non-multiplexed and consists of an eight

bit bidirectional data bus (D0-D7), a five bit

address/command bus (AC0-AC4), read/write (R/W

chip select (CS

request (IRQ

most high speed parallel microprocessors.

The serial microcontroller port (S/P = 1 and ST/SC =

0) consists of a receive data input (RxD), serial clock

input (SCLK), serial data input/output (SIO), interrupt

request (IRQ

automat ically interface to Intel, Moto rola or National

microcontrollers in either synchronous or

asynchronous modes. When controller mode is

and ST/SC.

= 0 and ST/SC

), data strobe (DS) and an interrupt

). This port can be easily interfaced to

), and chip select (CS). This port will

selected, the SCLK input is sampled when CS

brought low. If SCLK is high the device is in Intel

mode; if SCLK is low it will be in Motorola/National

Microwire mode.

The ST-BUS port (S/P

= 1 and ST/SC = 1) consists

of control streams CSTi0 and CSTi1, status stream

CSTo0, and interrupt request (IRQ

). It should be

noted that in this mode access to the circular buffers

and notional bit buffers is not provided. This port

meets the requirements of the "ST-BUS Generic

Device Specification", Mitel Application Note

MSAN-126.

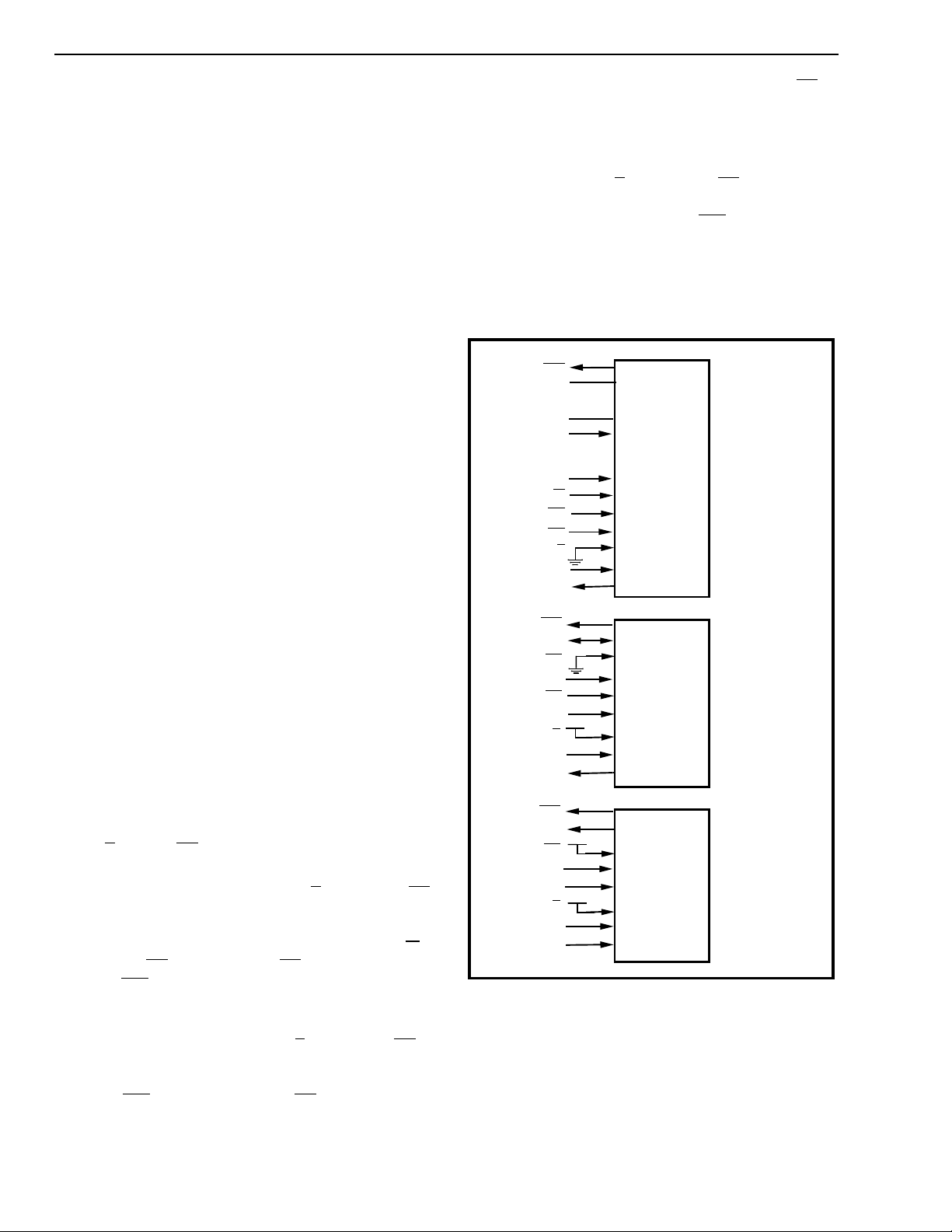

PARALLEL µP

IRQ

D0

•

•

•

D7

AC4

AC0

R/W

S/P

CSTi2

CSTo1

IRQ

RxD

ST/SC

SIO

CS

SCLK

S/P

CSTi2

CSTo1

IRQ

CSTo0

ST/SC

CSTi0

CSTi1

S/P

CSTi2

),

CSTo1

CS

DS

+5V

+5V

+5V

•

•

•

CONTROL

INTERFACE

SERIAL µP

CONTROL

INTERFACE

ST-BUS

CONTROL

INTERFACE

Figure 3 - Control Port Interface

Control and Status Register Access

The parallel microprocessor and serial

microcontroller interfaces gain access to specific

registers of the MT9079 through a two step process.

First, writing to the Command/Address Register

(CAR) selects one of the 14 pages of control and

status registers (CAR address: AC4 = 0, AC3-AC0 =

is

4-244

MT9079

don't care, CAR data D7 - D0 = page number).

Second, each page has a maximum of 16 registers

that are addressed on a read or write to a non-CAR

address (non-CAR: address AC4 = 1, AC3-AC0 =

register address, D7-D0 = data). Once a page of

memory is selected, it is only necessary to write to

the CAR when a different page is to be accessed.

See Figur e 1 7 for timing requirements.

Communications between a serial controller and

MT9079 is a two byte operations. First, a

Command/Address byte selects the address and

operation that follows. That is, the R/W

read or write function and A

determines if the next

4

byte is a new memory page address (A

data transfer within the current memory page (A

bit sel ect s a

= 0) or a

4

=

4

1). The second byte is either a new memory page

address (when A

= 0) or a data byte (when A4 = 1).

4

This is illustrated as follows:

a) Command/Address byte -

R/W XXA

4

A

3

A

2

A

1

A

0

where:

R/W - read or write operation,

X - no function,

= 0 - new memory page address to follow,

A

4

= 1 - data byte to follow, and

A

4

A

- determines the byte address.

3-A0

b) Page address or data byte -

D

D

D

D

D

D

D

7

6

5

4

3

2

D

1

0

See Figures 18 and 19 for timing requirements.

Register Access and Locations

Table 2 associates the MT9079 control and status

pages with access and page descriptions, as well as

an ST-BUS stream. When ST-BUS access mode is

used, each page contains 16 registers that are

associated consecutively with the first or second 16

channels of each ST-BUS stream. That is, page 1

regis ter lo cati ons 1 000 0 to 11111 a ppea r on CS Ti0

time slots 0 to 15, and page 2 register locations

1 0 0 0 0 t o 11111 a p pear on CSTi0 time slots 16 to 31.

It should be noted that access to the transmit and

receive circular buffers is not supported in ST-BUS

mode.

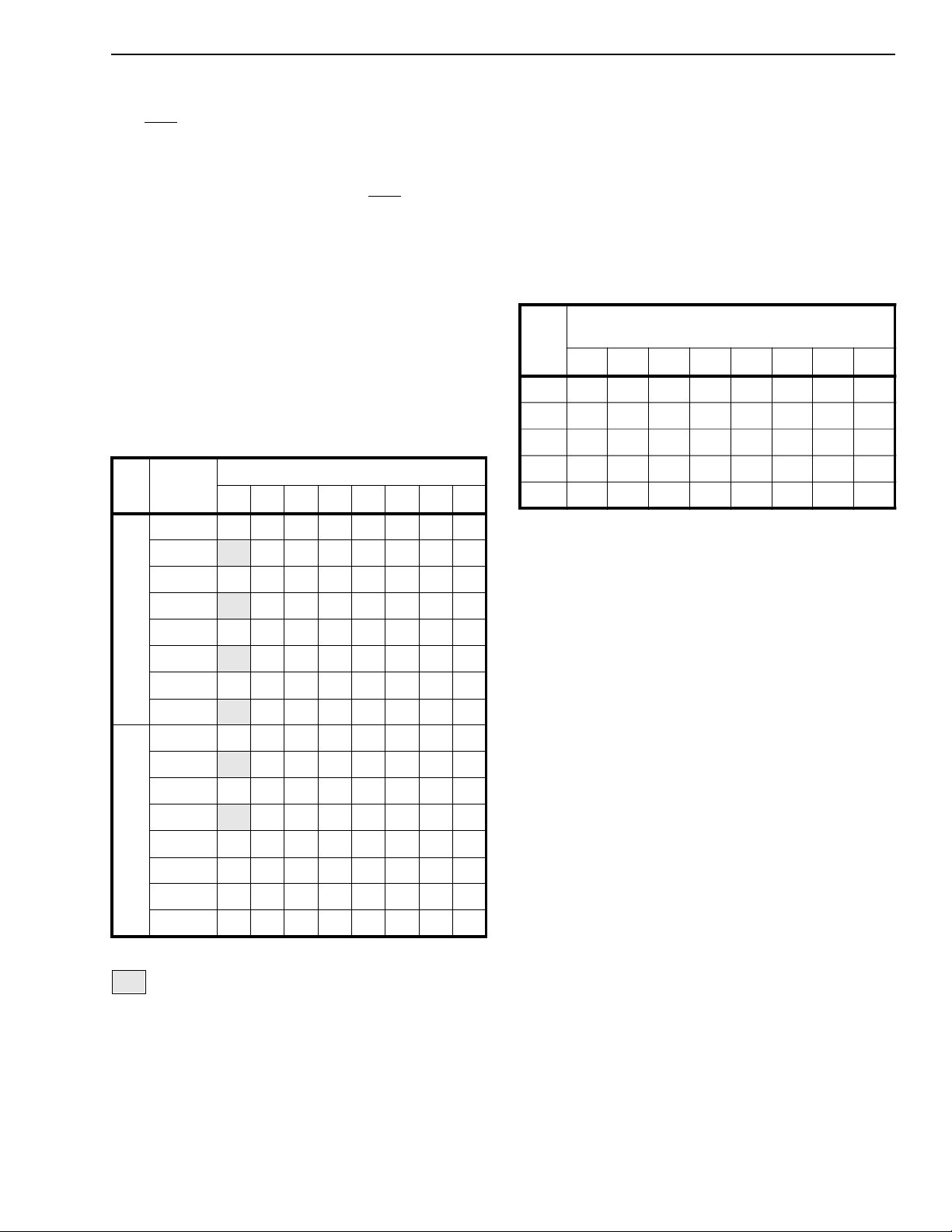

Common ST-BUS Streams

There are several control and status ST-BUS

streams that are common to all modes. CSTo1

contains the received channel associated signalling

bits (e.g., CCITT R1 and R2 signalling), and when

control bit RPSIG = 0, CSTi2 is used to control the

transmit channel associated signalling. DSTi and

DSTo contain the transmit and receive voice and

digital data. Figures 4a, b and c illustrate the relative

Page Address

D

- D

7

0

Register Description

000000 01 Master

000000 10 R/W

Control

00000011 Master

000001 00 R/W

Status

Processor/

Controller

Access

ST-BUS

Access

R/W CSTi0

RCSTo0

000001 01 Per Channel Transmit Sig nall ing R/W CSTi2

00000110 Per Cha nnel R ece ive Sign alling R CSTo1

00000111 Per Time Slot

000010 00 R/W

Control

R/W CSTi1

000010 01 Transmit Cir cular B uffer Zer o R/W --000010 10 Transmit Circular B uffer On e R /W --00001011 Receive Circular Buffer Zero R --00001100 Receive Ci rcular Buffer O ne R --00001101 Transmit National Bit Buffer R/W --00001110 Receive Nati ona l Bit Buffer R ---

Table 2 - Register Summary

4-245

MT9079

channel positions of the ST-BUS and PCM 30

interface. See Tables 13, 14, 16 and 17 for CAS bit

positions in CSTo1 and CSTi2.

15

14

30

29

Reset Operation (Initial izati on)

The MT9079 can be reset using the hardware

RESET

pin (see pin description for external reset

circuit requirements) or the software reset bit RST

(page 1, address 11H). During the reset state, TxA

and TxB are low. When the device emerges from its

reset state it will begin to function with the default

settings described in Table 3.

Function Status

Port Selection as per pins S/P & ST/SC

Mode Termination

ST-BUS Offset 00000000*

Loopbacks Deactivated

E8Ko Deactivated

Transmit FAS C

Transmit non-FAS 1/S

Transmit MFAS (CAS) 00001111

Data Link Deactivated

CRC Interworking Activated

Code Insert/Detect Deactivated

Signalling CAS (CSTi2 & CSTo1)

ABCD Bit Debounce Deactivated

Interrupt Mask Word Zero

Interrupts

unmasked, all others

masked; interru pts not

0011011

n

1111111

n

suspended

13

28

12

27

11

26

10

25

9

24

8

23

7

22

6

21

5

20

4

19

3

18

2

17

1

0

15

14

13

12

11

10

9

8

7

16

X

15

14

13

12

11

10

9

8

7

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

CSS

RxMF Output Signalling Multiframe

Error Insertion Deactivated

Coding 10*

Tx/Rx Buffers Deactivated

Counters Random

Table 3 - Reset Status

*cleared by the RESET pin, but not by the

RST control bit.

See the Applications section for the MT9079

initialization procedure.

4-246

DSTi # 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

123456789101112131415

PCM 30

Timeslot #

6

6

5

5

4

4

Figure 4c - Relationship between PCM 30 Frames, Channels and CSTo1 Channels

3

3

2

2

1

1

0

X

PCM 30

channel

Basic Fr am e

Timeslot 16 for

CCS = denotes Signalling Channel if Common Channel Signalling Mode Selected

x = Unused Channel

PCM 30

0 1 2 3 4 5 6 7 8 9 101112131415SIG171819202122232425262728293031

Timeslot #

Figure 4b - Relationship between Received PCM 30 Timeslots and Output DSTo Channels

CSTo1/CSTi2 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Figure 4a - Relationship between Input DSTi Channels and Transmitted PCM 30 Timeslots

DSTo 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

MT9079

TAIS Ope ration

The TAIS

(Transmit AIS) pin allows the PRI interface

to transmit an all ones signal form the point of

power-up without writing to any control registers.

After the interface has been initialized normal

operation can take place by making TAIS

high.

National B it Bu ff ers

Table 4 shows the contents of the transmit and

receive Frame Alignment Signals (FAS) and

Non-frame Alignment Signals (NFAS) of time slot

zero of a PCM 30 signal. Even numbered frames

(CRC Frame # 0, 2, 4, ...) are FASs and odd

numbered frames (CRC Frame # 1, 3, 5, ...) are

NFASs. The bits of each channel are numbered 1 to

8, with 1 being the most significant and 8 the least

significant.

CRC

CRC

Frame/

Type

0/FAS C10011011

1/NFAS

2/FAS C20011011

PCM 30 Channel Zero

12345678

01ALMSa4Sa5Sa6Sa7S

a8

modes, but cannot be accessed in ST-BUS mode. In

ST-BUS mode access to the national bits can be

achieved through the Transmit and Receive

Non-frame Alignment Signal (CSTi0 and CSTo).

When selected, the Data Link (DL) pin functions

override the transmit national bit buffer function.

The CALN (CRC-4 Alignment) status bit and

maskable interrupt CALNI indicate the beginning of

every received CRC-4 multiframe.

Addre

ssable

Bytes

NBB0 S

NBB1 S

NBB2 S

NBB3 S

NBB4 S

Frames 1, 3, 5, 7, 9, 11, 13 & 15 of a CRC-4

Multiframe

F1 F3 F5 F7 F9 F11 F13 F15

a4Sa4Sa4Sa4Sa4Sa4Sa4Sa4

a5Sa5Sa5Sa5Sa5Sa5Sa5Sa5

a6Sa6Sa6Sa6Sa6Sa6Sa6Sa6

a7Sa7Sa7Sa7Sa7Sa7Sa7Sa7

a8Sa8Sa8Sa8Sa8Sa8Sa8Sa8

Table 5 - MT9079 National Bit Buffers

Note: NBB0 - NBB4 are addressa ble bytes of the MT9079

transmit and receive national bit buffers.

3/NFAS

4/FAS C30011011

5/NFAS

Sub Multi Frame 1

6/FAS C40011011

7/NFAS

8/FAS C10011011

9/NFAS

10/FAS C20011011

11/NFAS

12/FAS C30011011

13/NFAS E

Sub Multi Frame 2

14/FAS C40011011

15/NFAS E

01ALMSa4Sa5Sa6Sa7S

11ALMSa4Sa5Sa6Sa7S

01ALMSa4Sa5Sa6Sa7S

11ALMSa4Sa5Sa6Sa7S

11ALMSa4Sa5Sa6Sa7S

1 ALM Sa4Sa5Sa6Sa7S

1

1 ALM Sa4Sa5Sa6Sa7S

2

a8

a8

a8

a8

a8

a8

a8

Table 4 - FAS and NFAS Structure

indicates positio n of CRC-4 multiframe alignment signal.

Table 5 illustrates the organization of the MT9079

transmit and receive national bit buffers. Each row is

an addressable byte of the MT9079 national bit

buffer, and each column contains the national bits of

an odd numbered frame of each CRC-4 Multiframe.

Data Link Ope ration

The MT9079 has a user defined 4 kbit/sec. data link

for the transport of maintenance and performance

monitoring information across the PCM 30 link. This

channel functions using one of the national bits (S

S

, Sa6, Sa7 or Sa8) of the PCM 30 channel zero

a5

non-frame alignment signal. The S

bit used for the

a

DL is selected by making one of the bits, S

- Sa8,

a4

a4

high in the Data Link Select Word. Access to the DL

is provided by pins DLCLK, TxDL and RxDL, which

allow easy interfacing to an HDLC controller.

The 4 kHz DLCLK output signal is derived from the

ST-BUS clocks and is aligned with the receive data

link output RxDL. The DLCLK will not change phase

with a received frame slip, but the RxDL data has a

50% chance of being lost or repeated when a slip

occurs.

The TxDL input signal is clocked into the MT9079 by

the rising edge of an internal 4 kHz clock (e.g., internal

data link clo ck IDCLK ). The I DCLK is 18 0 d egrees out

of phase with the DLCLK. See Figures 20 and 21 for

timing requirements.

,

The transmit and receive national bit buffers are

selectible in microprocessor or microcontroller

4-247

MT9079

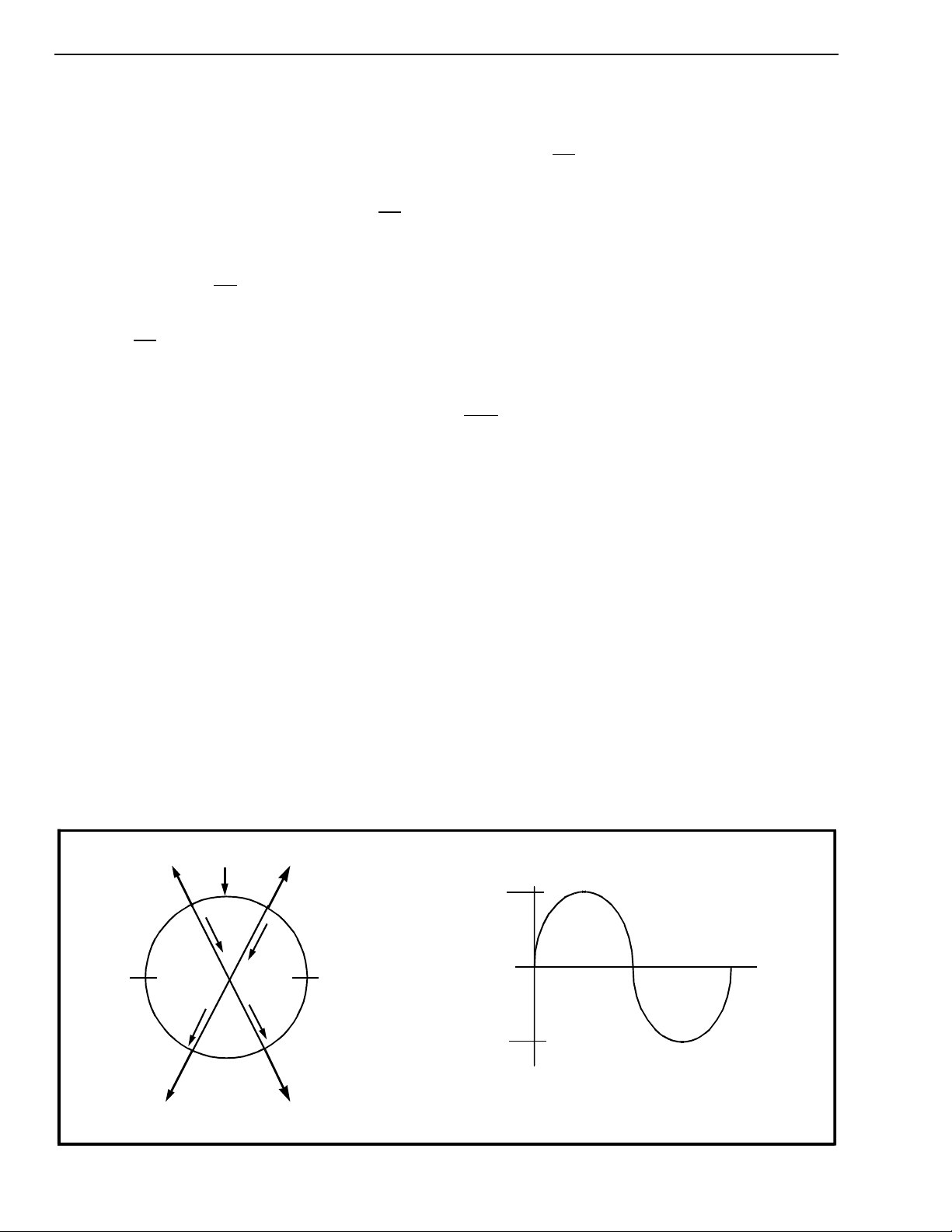

Elastic Buffer

When control bit RDLY=0, the MT9079 has a two

frame receive elastic buffer, which absorbs wander

and low frequency jitter in multi-trunk applications.

The received PCM 30 data (RxA and RxB) is clocked

into the elastic buffer with the E2i clock and is

clocked out of the elastic buffer with the C4i

/C2i

clock. The E2i extracted clock is generated from, and

is therefore phase-locked with, the receive PCM 30

data. In normal operation, the E2i clock will be

phase-locked to the C4i

/C2i clock by an external

phase locked loop (PLL). Therefore, in a single trunk

system the receive data is in phase with the E2i

clock, the C4i

/C2i clock is phase-locked to the E2i

clock, and the read and write positions of the elastic

buffer will remain fixed with respect to each other.

In a multi-trunk slave or loop-timed system (i.e., PABX

application) a single trunk will be chosen as a network

synchronizer, which will function as described in the

previous paragraph. The rem aining trunks wil l use the

system timing derived form the synchronizer to clock

data out of t heir elastic buffe rs. Even though the P CM

30 signals from the network are synchronize to each

other, due to multiplexing, transmission impairments

and route diversity, these signals may jitter or wander

with respect to the synchronizer trunk signal. Therefore, the E2i clocks of non-synchronizer trunks may

wander with respect to the E2i clock of the synchronizer and the system bus. Network standards state

that, within limits, trunk interfaces must be able to

receive error-free data in the presence of jitter and

wander (refer to network requirements for jitter and

wander tolerance). The MT9079 will allow a minimum

of 26 channels (208 UI, unit intervals) of wander and

low frequency jitter before a frame slip will occur.

The minimum delay through the receive elasti c buffer

is approximately two channels and the maximum delay

is approximately 60 channels (RDLY=0 ), see Figure 5.

When the C4i

/C2i and the E2i clocks are not

phase-locked, the rate at which data is being w ritten

into the elastic buffer from th e PCM 30 side may differ

from the rate at which it is being read out onto the

ST-BUS. If this situation persists, the delay limits

stated in the previous paragraph will be violated and

the elastic buffer will p erform a controlled frame slip.

That is, the buffer pointers will be automatically

adjusted so that a full PCM 30 frame is either repeated

or lost. All frame slips occur on PCM 30 frame boundaries.

The RSLIP and RSLPD st atus bits gi ve indication of a

slip occurrence and direction. A maskable interrupt

is also provided.

SLPI

Figure 5 illustrates the relationship between the read

and write pointers of the receive elastic buffer.

Measuring clockwise from the write pointer, if the

read pointer comes within two channels of the write

pointer a frame slip will occur, which will put the read

pointer 34 channels from the write pointer.

Conversely, if the read pointer moves more than 60

channels from the write pointer, a slip will occur,

which will put the read pointer 28 channels from the

write pointer. This provides a worst case hysteresis

of 13 channels peak (26 channels peak-to-peak) or a

wander tolerance of 208 UI.

When control bit RDLY=1, the receive elastic buffer

becomes one frame long and the controlled slip

function is disabled. This is to allow the user to

control the receive throughput delay of the MT9079

in one of th e fo l low in g wa y s:

4-248

Read Pointer

60 CH

47 CH

34 CH

Read Pointer

Write

Pointer

512 Bit

Elastic

Store

Read Point er

13 CH

2 CH

Wander Tolerance

15 CH

-13 CH

28 CH

Read Point er

Figure 5 - Elastic Buffer Functional Diagram (208 UI Wander Tolerance)

MT9079

1) by programming the SOFF7-0 bits to select the

desired throughput delay, which is indicated by

the phase status word bits RxTS4-0 and

RxBC2-0.

2) by controlling the position of the F0i

respect to the received time slot zero position.

The phase status word bits RxTS4-0 and

RxBC2-0 will also indicate the delay in this

application.

With RDLY=1, the elastic buffer may underflow or

overflow. This is indicated by the RSLIP and RSLPD

status bits. If RSLPD=0, the elastic buffer has

overflowed and a bit was lost; if RSLPD=1, a

underflow condition occurred and a bit was

repeated.

Framing Algorithm

The MT9079 contains three distinct, but

interdependent, framing algorithms. These

algorithms are for basic frame alignment, signalling

multiframe alignment and CRC-4 multiframe

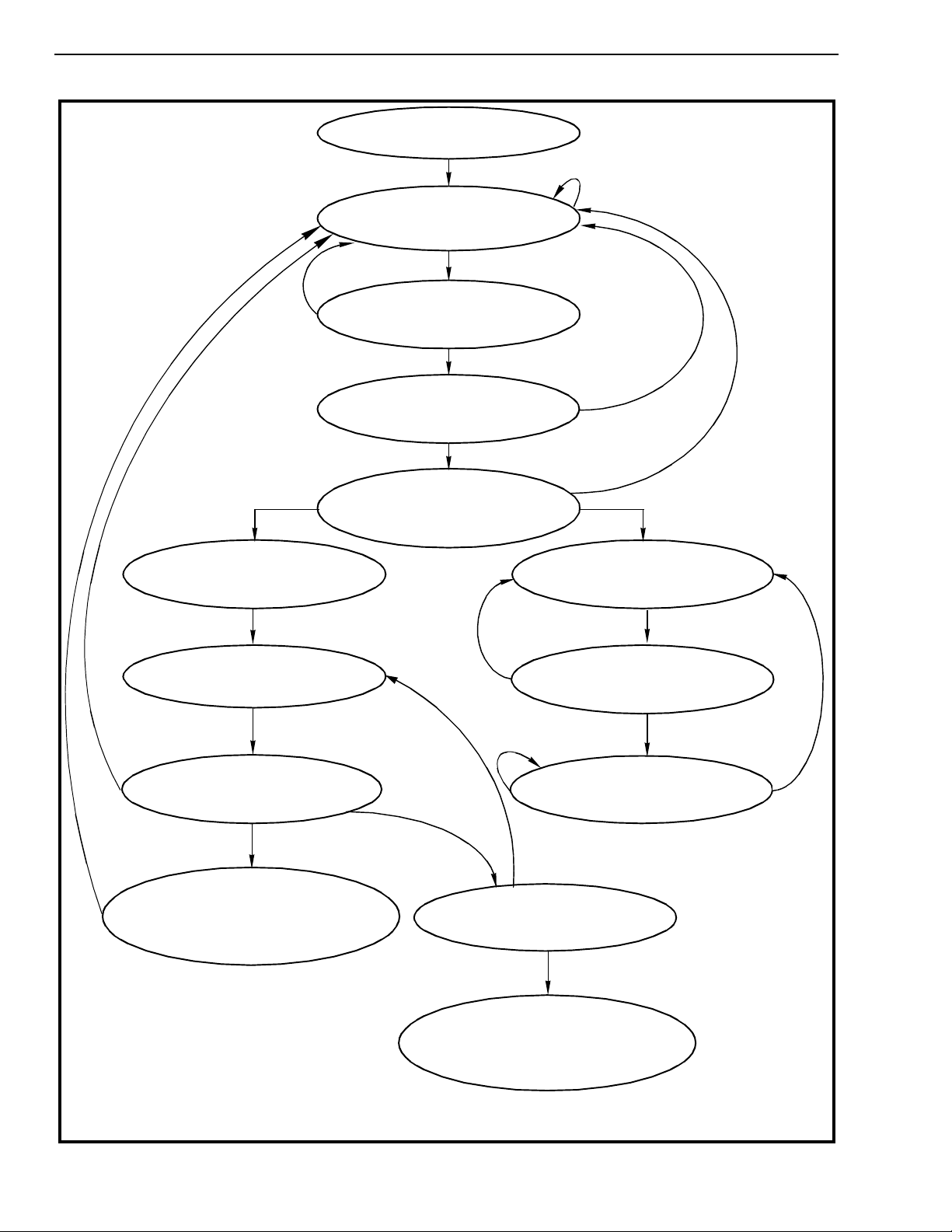

alignment. Figure 6 is a state diagram that illustrates

these functions and how they interact.

pulse with

The MT9079 framing algorithm supports automatic

interworking of interfaces with and without CRC-4

processing capabilities. That is, if an interface with

CRC-4 capability, achieves valid basic frame

alignment, but does not achieve CRC-4 multiframe

alignment by the end of a predefined period, the

distant end is considered to be a non-CRC-4

interface. When the distant end is a non-CRC-4

interface, the near end automatically suspends

receive CRC-4 functions, continues to transmit

CRC-4 data to the distant end with its E-bits set to

zero, and provides a status indication. Naturally, if

the distant end initially achieves CRC-4

synchronization, CRC-4 processing will be carried

out by both ends. This feature is selected when

control bit AUTC

Notes for Fig u re 6 :

1) The basic frame align ment, signalling multiframe

alignment, and CRC-4 multiframe alignment

functions operate in parallel and are independent.

2) The receive channel associated signalling bits

and signalling multiframe alignment bit will be frozen

when multiframe alignment is lost.

= 0. See Figure 6 for more details.

After power-up the basic frame alignment framer will

search for a frame alignment signal (FAS) in the

PCM 30 receive bit stream. Once the FAS is

detected, the corresponding bit two of the non-frame

alignment signal (NFAS) is checked. If bit two of the

NFAS is zero a new search for basic frame alignment

is initiated. If bit two of the NFAS is one and the next

FAS is correct, the algorithm declares that basic

frame synchronization has been found (i.e., SYNC

low).

Once basic frame alignment is acquired the

signalling and CRC-4 multiframe searches will be

initiated. The signalling multiframe algorithm will

align to the first multiframe alignment signal pattern

(MFAS = 0000) it receives in the most significant

nibble of channel 16 (MFSYNC = 0). Signalling

multiframing will be lost when two consecutive

multiframes are received in error.

The CRC-4 multiframe alignment signal is a 001011

bit sequence that appears in PCM 30 bit position one

of the NFAS in frames 1, 3, 5, 7, 9 and 11 (see Table

4). In order to achieved CRC-4 synchronization two

consecutive CRC-4 multiframe alignment signals

must be received without error (CRCSYN

Figure 6 for a more detailed description of the

framing functions.

= 0). See

is

3) Manual re-framing of the receive basic frame

alignment and signalling multiframe alignment

functions can be performed at any time.

4) The transmit RAI bit will be one until basic frame

alignment is established, then it will be zero.

5) E-bits can be optionally set to zero until the

equipment interworking relationship is established.

When this has been determined one of the following

will take place:

a) CRC-to-non-CRC operation - E-bits = 0,

b) CRC-to-CRC operation - E-bits as per G.704 and

I.431.

6) All manual re-frames and new basic frame

alignment searches start after the current frame

alignment signal position.

7) After basic frame alignment has been achieved,

loss of frame alignment will occur any time three

consecutive incorrect FAS or NFAS are received.

Loss of basic frame alignment will reset the complete

framing algorithm.

4-249

MT9079

Out of synchronization

>914 CRC errors

in one second

No CRC

multiframe alignment.

8 msec. timer expired*

CRC-4 multi-frame alignment

Start 400 msec timer.

Note 7.

YES

Search for primary basic

frame alignment signal

RAI=1, Es=0.

YES

NO

Verify Bit 2 of non-frame

alignment signal.

YES

Verify second occurrence

of frame alignment signal.

YES

Primary basic frame synchronization

acquired. Enable traffic RAI=0, E’s=0. Start

loss of primary basic frame alignment

checking. Notes 7 & 8.

NO

3 consecutive

incorrect frame

alignment

signals

NO

CRC-4 multi-frame alignment

Search for multiframe

alignment signal.

Note 7.

Start 8 msec timer.

Note 7.

Basic frame

alignment acquired

Find two CRC frame

alignment signals.

Note 7.

CRC multiframe

alignment

CRC-to-CRC interworking. Re-align to new

basic frame alignment. Start CRC-4 processing.

E-bits set as per G.704 and I.431. Indicate

CRC synchronization achieved.

Notes 7& 8.

timer expir ed **

Basic frame

alignment

acquired

No CRC

multiframe

alignment.

8 msec. timer expired*

No CRC

multiframe

alignment.

8 msec.

CRC-to-non-CRC interworking. Maintain

primary basic frame alignment. Continue to

send CRC-4 data, but stop CRC processing.

E-bits set to ‘0’. Indicate CRC-to-non-CRC

NO

Multiframe synchronization

acquired as per G.732.

NO

Check for two consecutive errored

multiframe alignment signals.

Parallel search for new basic frame

alignment signal.

Notes 6 & 7.

400 msec timer expired

operation. Note 7.

YES

Note 7.

YES

Notes 7 & 8.

* only if CRC-4 synchronization is selected and automatic CRC-4 interworking is de-selected.

** only if automatic CRC-4 interw orking is selected.

Figure 6 - Synchronization State Diagram

4-250

MT9079

8) When CRC-4 multiframing has been achieved,

the primary basic frame alignment and resulting

multiframe alignment will be adjusted to the basic

frame alignment determined during CRC-4

synchronization. Therefore, the primary basic frame

alignment will not be updated during the CRC-4

multiframing search, but will be updated when the

CRC-4 multiframing search is complete.

Channel Signalling

When control bit TxCAS

is low the MT9079 is in

Channel Associated Signalling mode (CAS); when

TxCAS

is high it is in Common Channel Signalling

(CCS) mode. The CAS mode ABCD signalling

nibbles can be passed either via the micro-ports

(RPSIG = 1) or through related channels of the

CSTo1 and CSTi2 serial links (RPSIG = 0), see

Figure 4. Memory page five contains the receive

ABCD nibbles and page six the transmit ABCD

nibbles for micro-port CAS access.

In CAS operation an ABCD signalling bit debounce

of 14 msec. can be selected (DBNCE = 1). This is

consistent with the signalling recognition time of

CCITT Q.422. It should be noted that there may be

as much as 2 msec. added to this duration because

signalling equipment state changes are not

synchronous with the PCM 30 multiframe.

If basic frame synchronization is lost (page 3,

address 10H, SYNC

= 1) all receive CAS signalling

nibbles are frozen. Receive CAS nibbles will become

unfrozen when basic frame synchronization is

acquired.

When the SIGI interrupt is unmasked, IRQ

will

become active when a signalling nibble state change

is detected in any of the 30 receive channels. The

SIGI interrupt mask is located on page 1, address

1CH, bit 0; and the SIGI interrupt vector (page 4,

address 12H) is 01H.

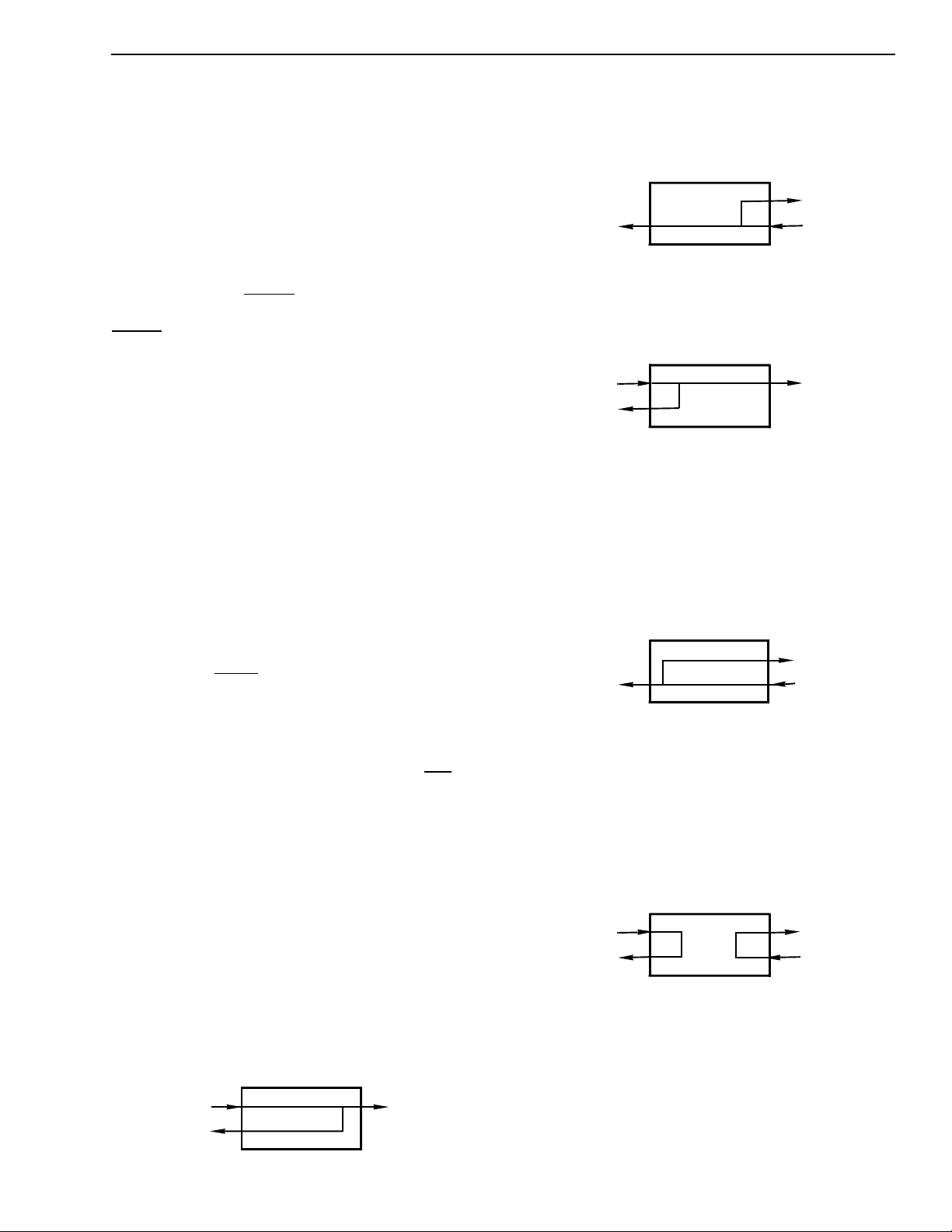

b) Remote loopback (RxA and RxB to TxA and TxB

respectively at the PCM 30 side). Bit RLBK = 0

normal; RLBK = 1 activate.

MT9079

System

DSTo

Tx

PCM30

Rx

c) ST-BUS loopback (DSTi to DSTo at the system

side). Bit SLBK = 0 normal; SLBK = 1 activate.

MT9079

System

DSTi

DSTo

Tx

PCM30

d) Payload loopback (RxA and RxB to TxA and TxB

respectively at the system side with FAS and NFAS

operating normally). Bit PLBK = 0 normal; PLBK = 1

activate. The payload loopback is effectively a

physical connection of DSTo to DSTi within the

MT9079. Channel zero and the DL originate at the

point of loopback.

MT9079

System

DSTi

DSTo

Tx

PCM30

Rx

e) Local and remote time slot loopback. Remote

time slot loopback control bit RTSL = 0 normal; RTSL

= 1 activate, will loop around transmit ST-BUS time

slots to the DSTo stream. Local time slot loopback

bits LTSL = 0 normal; LTSL = 1 activate, will loop

around receive PCM 30 time slots towards the

remote PCM 30 end.

Loopbacks

In order to meet PRI Layer 1 requirements and to

assist in circuit fault sectionalization the MT9079 has

six loopback functions. These are as follows:

a) Digital loopback (DSTi to DSTo at the PCM 30

side). Bit DLBK = 0 normal; DLBK = 1 activate.

MT9079

System

DSTi

DSTo

Tx

PCM30

MT9079

System

DSTi

DSTo

Tx

PCM30

Rx

The digital, remote, ST-BUS and payload loopbacks

are located on page 1, address 15H, control bits 3 to

0. The remote and local time slot loopbacks are

controlled through control bits 4 and 5 of the per time

slot control words, pages 7 and 8.

4-251

MT9079

PCM 30 Interfacing and Encoding

Bits 7 and 6 of page 1, address 15H (COD1-0)

determine the PCM 30 format of the PCM 30

transmit and receive signals. The RZ format

(COD1-0 = 00) can be used where the line interface

is implemented with discrete components. In this

case, the pulse width and state of TxA and TxB

directly determine the width and state of the PCM 30

pulses.

NRZ format (COD1-0 = 01) is not bipolar, and

therefore, only requires a single output line and a

single input line (i.e., TxA and RxA). This signal

along with a synchronous 4, 8 or 16 MHz clock can

interface to a manchester or similar encoder to

produce a self-clocking code for a fibre optic

transducer.

The NRZB format (default COD1-0 = 10) is used for

interfacing to monolithic Line Interface Units (LIUs).

With this format pulses are present for the full bit

cell, which allows the set-up and hold times to be

meet easily.

The HDB3

selects either HDB3 encoding or alternate mark

inversion (AMI) encoding.

control bit (page 1, address 15H, bit 5)

Bit Error Rate Counter (BR7-BR0)

An eight bit Error Rate (BERT) counter BR7 - BR0 is

located on page 4 address 18H, and is incremented

once for every bit detected in error on either the

seven frame alignment signal bits or in a selected

channel. When a selected channel is used, the data

received in this channel will be compared with the

data of the bit error rate compare word CMP7-CMP0.

See the explanation of the CDDTC control bit of the

per time slot control words (pages 7 and 8) and the

bit error rate compare word (page 2, address 11).

There are two maskable interrupts associated with

the bit error rate measurement. BERI is initiated

when the least significant bit of the BERT counter

(BR0) togg l e s, and BERO

counter value changes from FFH to 00H.

Errored Frame Alignment Signal Counter

(EFAS7-EFAS0)

An eight bit Frame Alignment Signal Error counter

EFAS7 - EFAS0 is located on page 4 address 1AH,

and is incremented once for every receive frame

alignment signal that contains one or more errors.

in initiated when the BERT

Performance Monitoring

MT9079 Error Counters

The MT9079 has six error counters, which can be

used for maintenance testing, an ongoing measure

of the quality of a PCM 30 link and to assist the

designer in meeting specifications such as CCITT

I.431 and G.821. In parallel microprocessor and

serial microcontroller modes, all counters can be

preset or cleared by writing to the appropriate

locations. When ST-BUS access is used, this is done

by writing the value to be loaded into the counter in

the appropriate counter load word (page 2, address

18H to 1FH). The counter is loaded with the new

value when the appropriate counter load bit is

toggled (page 2, address 15H).

Associated with each counter is a maskable event

occurrence interrupt and a maskable counter

overflow interrupt. Overflow interrupts are useful

when cumulative error counts are being recorded.

For example, every time the frame error counter

overflow interrupt (FERO) occurs, 256 frame errors

have been received since the last FERO interrupt.

There are two maskable interrupts associated with

the frame alignment signal error measurement. FERI

is initiated when the least significant bit of the

errored frame alignment signal counter toggles, and

FERO is initiated when the counter changes from

FFH to 00 H .

Bipolar Violation Error Counter (BPV15-BPV0)

The bipolar violation error counter will count bipolar

violations or encoding errors that are not part of

encoding. This counter BPV15-BPV0 is 16

HDB3

bits long (page 4, addresses 1DH and 1CH) and is

incremented once for every BPV error received. It

should be noted that when presetting or clearing the

BPV error counter, the least significant BPV counter

address should be written to before the most

significant location.

There are two maskable interrupts associated with

the bipolar violation error measurement. BPVI is

initiated when the least significant bit of the BPV

error counter toggles. BPVO

counter changes from FFFFH to 0000H.

is initiated when the

4-252

MT9079

CRC Error and E-bit Counters

CRC-4 errors and E-bit errors are counted by the

MT9079 in order to support compliance with CCITT

requirements. These eight bit counters are located

on page 4, addresses 1FH and 1EH respectively.

They are incremented by single error events, which

is a maximum rate of twice per CRC-4 multiframe.

There are two maskable interrupts associated with

the CRC error and E-bit error measurement. CRCI

and EBI are initiated when the least significant bit of

the appropriate counter toggles, and CRCO and

EBO are initiated when the appropriate counter

changes fro m FFH to 0 0H .

G.821 Bit Error Rate Estimation

A G.821 BERT estimation for an E1 link can be done

with either the BERT counter, when it is associated

with the FAS, or the Errored Frame Alignment Signal

counter. It should be noted that the BERT counter

will be incremented once for every bit error found in

the FAS, and not just once for every FAS in error.

The formula for the link BERT estimation is as

follows:

BERT estimation = BERT counter value/(N*F*T)

where:

N is the number of bits verified (i.e., when the FAS

is used N = 7; when a channel is selected N = 8).

F is the number of FAS or channels in one second

(i.e., when the FAS is used F= 4000, when a

channel is selected F = 8000).

T is the elapsed time in seconds.

A similar formula can be used to provide a BERT

estimation of the transmit direction by using the E-bit

error counter, EBt.

A more accurate BERT estimation can be done using

the Bipolar Violation Error counter. The BPV error

counter will count violations that are not due to HDB3

encoding. The formula for this is as follows:

BERT estimation = BPV Error counter value/(256*8000*T)

where:

256 is the number of bits per basic frame.

8000 is the number of basic frames in one second.

T is the elapsed time in seconds.

This assumes that one BPV error will be the result of

one bit error.

RAI and Continuous CRC-4 Error Counter

When the re ceive Remote Alarm Indic ation is activ e

(RAI = 1 - bit 3 of the NFAS) and a receive E-bit

indicates a remote error (En = 0), the RCRC counter

will be incremented. This counter will count the

number of submultiframes that were received in error

at the remote end of a link during a time when layer

one capabilities were lost at that end. This eight bit

RCRC counter is located on page 4, addresses 19H.

There are two maskable interrupts associated with

the RCRC counter. RCRI is initiated when the least

significant bit of the RCRC counter toggles, and

RCRO and EBO are initiated when the counter

changes from FFH to 00H.

A similar formula can be used with the FAS error

counter.

BERT estimation = FAS Error counter value/(7*4000*T).

The CRC-4 error counter can also be used for BERT

estimation. The formula for BERT estimation using

the CRC-4 e rr o r c o unt is as fo llows:

BERT estimation = CEt counter value/(2048000*T)

where:

2048000 is the number of bits that are

received in one second.

T is the elapsed time in seconds.

Maintenance and Alarms

Error Insertion

Five types of error conditions can be inserted into the

transmit PCM 30 data stream through control bits,

which are located on page 2, address 10H. These

error events include the bipolar violation errors

(BPVE), CRC-4 errors (CRCE), FAS errors (FASE),

NFAS errors (NFSE), and a loss of signal condition

(LOSE). The LOSE function overrides the HDB3

encoding function.

4-253

Loading...

Loading...