MITEL MT90737AM, MT9080AP Datasheet

2-101

Features

• Timeslot interchan ge ci rcuit fo r digita l switc h

applicati ons

• 16 bit wide data bus I/O

• 2048 x 16 bi t wide byte ca pac ity

• Dual addres sing ca pab ility; in terna l counte r

and exter nal ad dress bus

• Variable cloc k and f rame ra tes

• Microprocessor in terface

•CMOS

Applications

• Building bl ock for d igital switch ing mat rices

used in PBXs, CO equipment, data switching,

etc.

• Programmable delay lines

Description

The MT9080 is a flexible memory module suitable for

use as a basic building block in the construction of

large digital switching matrices. It can be configured

as either a Data Memory or a Connection Memory.

Interface to the device is via 16 bit wide data and

address busses. The MT9080 can operate with

variabl e cl o c k ra te s up to 16.7 MHz.

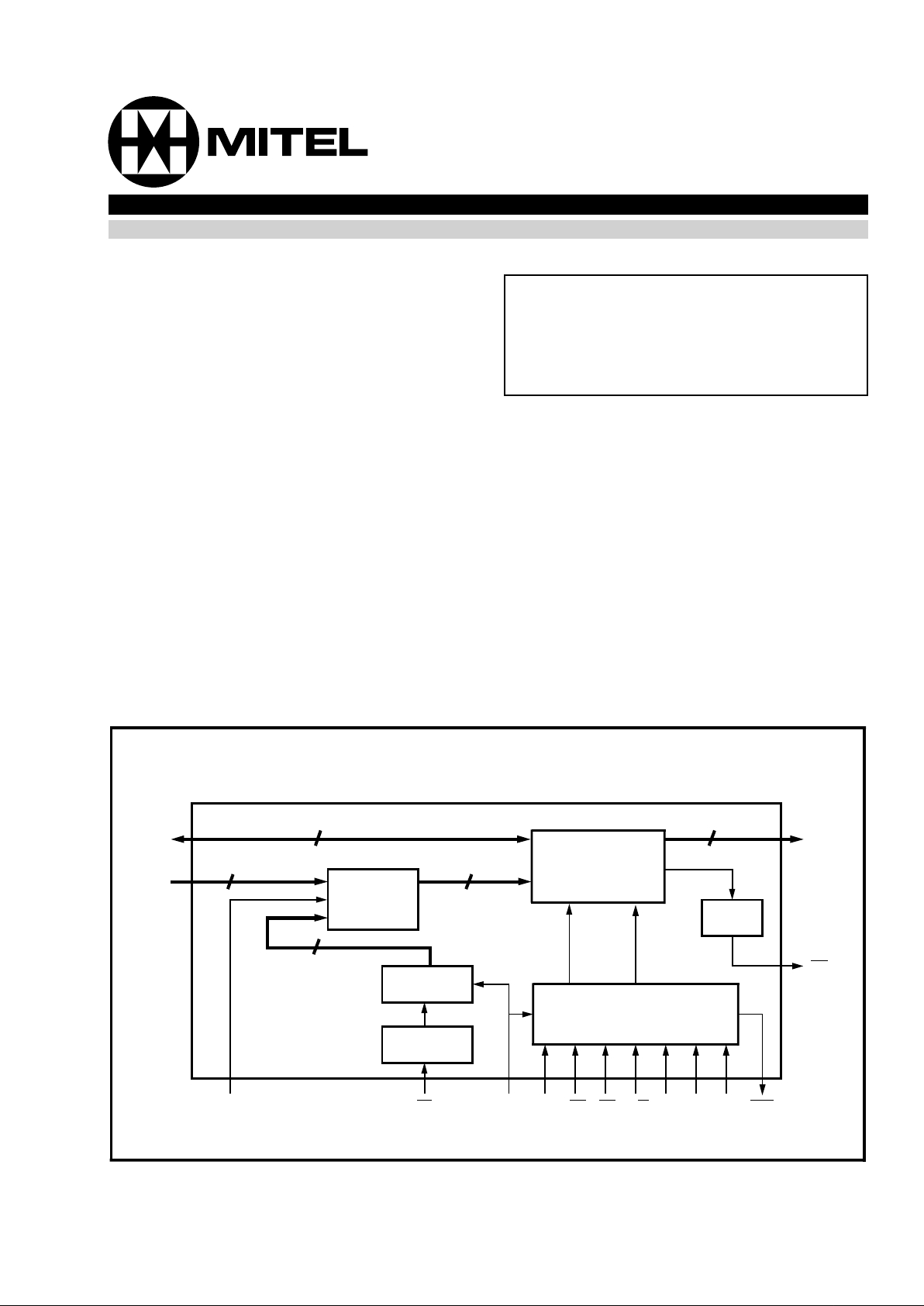

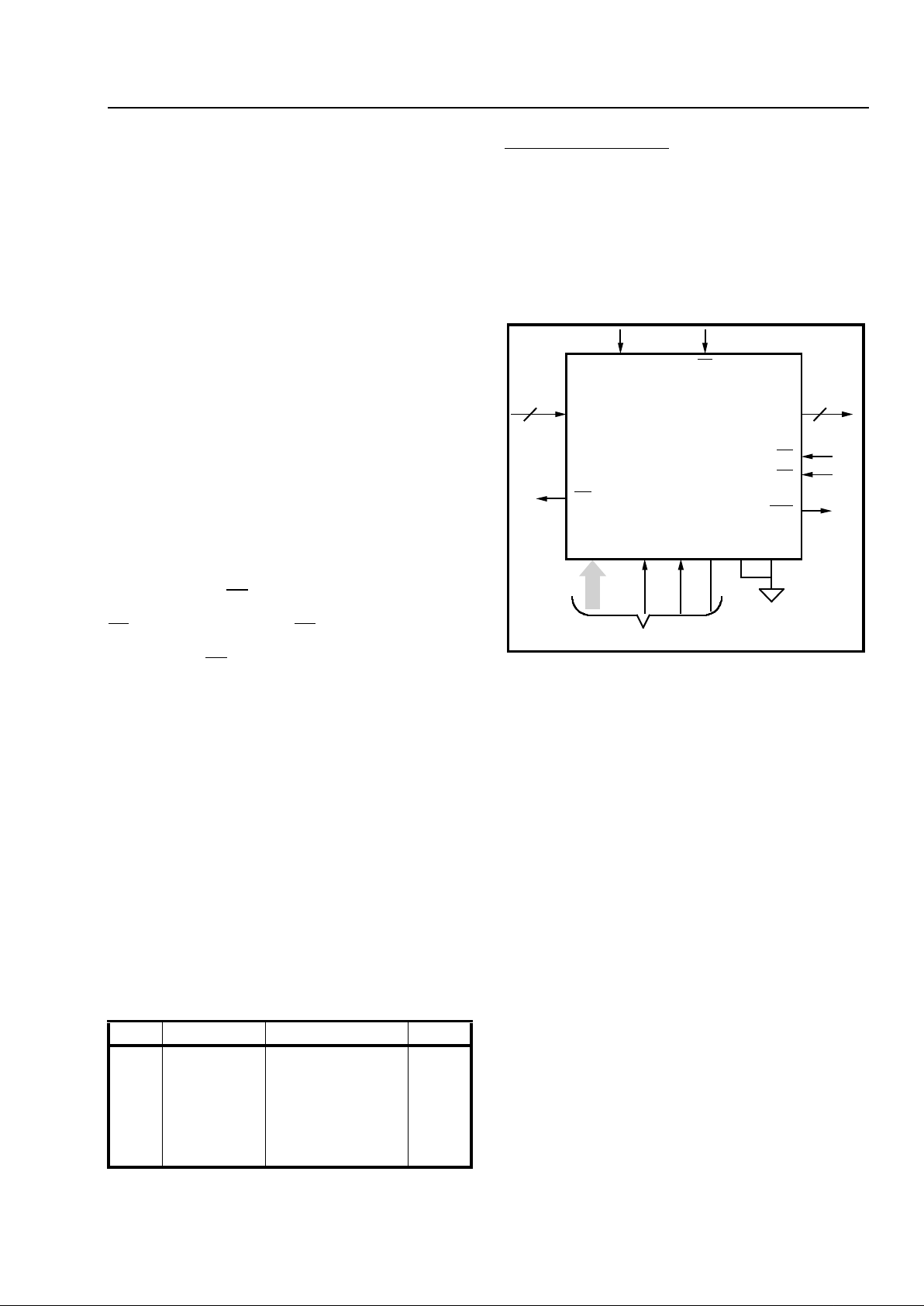

Figure 1 - Functional Block Diagram

D0i/D15i

A0-A15

ME

16

16

16

16

Address

MUX

11 Bit

Counter

Counter

Reset

2048 x 16

Static

Memory

Control Interface

WR

ENABLE

PRECHARGE

D0o/

CD

11

CRC

FP

CK ODE DS CS R/W Mx My Mz DTA

D15o

Ordering Information

MT9080AP 84 Pin PLCC

-40°C to 70°C

ISSUE 3 January 1993

MT9080

SMX - Switch Matrix Module

CMOS

MT9080 CMOS

2-102

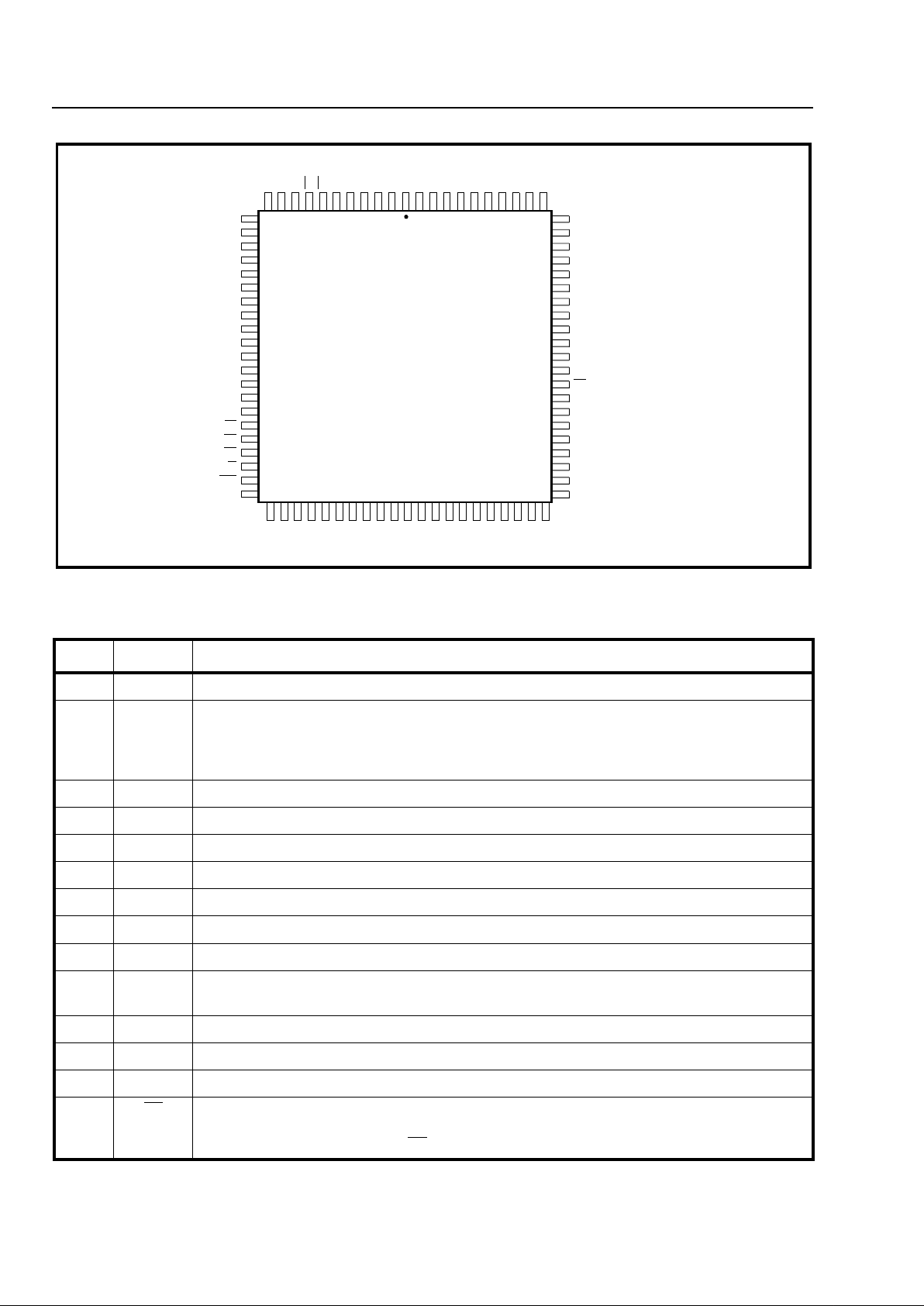

Figure 2 - Pin Connections

Pin Description

Pin # Name Description

1V

SS

Ground.

2-5 D0i-D3i Input/Micropo rt Data Bus. This is part of a 16 bit data bus. The data bus is bidirectional in

Connect Memory mode where it is typically interfaced to a microprocessor. In all other

modes the data bus is an input. Data to be switched through the device is clocked in at this

port.

6V

SS

Ground.

7-10 D4i-D7i Input/Micropo rt Data Bus. See description for pins 2-5 above.

11 V

SS

Ground.

12-15 D8i-D11i Input/Micr opo rt Data Bus. See description for pins 2-5 above.

16 V

SS

Ground.

17-20 D12i -D15i Input/Microport Data Bus. See description for pins 2-5 above.

21 V

SS

Ground.

22 CK Clock. Master cloc k input which is used to clock data into and out of the device. It also

clocks the internal 11 bit counter.

23 V

DD

+5V supply input .

24 V

SS

Ground.

25,26 IC Internal Con necti on. Should be tied to V

SS

for normal operation.

27 FP

Frame Pulse. An active low signal that serves as a synchronous clear for the int ernal 11 bit

counter in all modes except Shift Register mode. The counter is cleared on a rising edge of

CK. In the Shift Register mode, FP

serves to align channel boundaries.

74

56

58

60

62

64

68

70

72

66

12

28

26

24

22

18

16

14

20

VSS

32

30

54

10

8

6

4

2

84

82

80

78

76

34

36

38

40

42

44

46

48

50

52

NC

ODE

ME

MxMyMz

NC

IC

IC

VSS

VDD

NC

A0A1A2A3A4A5A6

A7

VSS

D7o

D6o

D5o

D4o

VSS

D3o

D2o

D1o

D0o

VSS

CD

A14

A13

A12

A11

A10

A9

A8

D8i

D9i

D10i

D11i

D13i

D14i

D15i

VSS

VSS

IC

CK

VDD

IC

FP

CS

DS

R/W

DTA

NC

VSS

D7i

D6i

D5i

D4i

VSS

D3i

D2i

D1i

VSS

VDD

D15o

D14o

D13o

D12o

VSS

D11o

D10o

D9o

D8o

D0i

84 PIN PLCC

VDD

A15

VSS

D12i

CMOS MT9080

2-103

28 CS Chip Select. Active Low input. Selects the device for microport access in connect memory,

data memory, external and shift register modes. Tying CS

high will disable output data

drivers (D0-D15o) in all modes except connect memory and shift register modes.

29 DS

Data Strobe. Active low input. Indicates to the SMX that valid data is present on th e

microport data bus durin g a write operation or that the SMX mu st outp ut data on a read

operation.

In Connect Memory modes, a low level applied to this input during a write operation indicates

to the SMX that valid data is present on the microport data bus. During a read operation the

low going signal indicates to the SMX that it must output data on the micropo rt data bus.

In Data Memory and External modes, when DS

is high, the output data bus D0o-D15o will be

disabled. The input data bus D0i-D15 i is not affected.

The DS

input has no effect on the input and output busses in Counter or Shif t Register

modes.

30 R/W

Read/Write Enable. Data is written into the device when R/W is low and read from it when it

is high. This control input is disabled in data memory and shift registe r modes. It should be

tied to V

SS

or VDD in these modes. In counter and external modes, the state of R/W pin is

clocked in with the rising edge of CK. The actual read or write operation will be implemented

on the next rising clock edge.

31 DTA

Data Transfer Acknowledge. O pen drain out put whi ch is pulled low to acknowled ge

completion of mi croport dat a transf er. On a read of the SMX, DTA

low indicates t hat t he

SMX has put valid data on the data bus. On a write, DTA

low indicates that the SMX has

completed latching the data in.

32 NC No Connection.

33 V

SS

Ground.

34 NC No Connection.

35 ODE Output Data Enable. Control input which enables the output data bus. Pulling this input low

will place the data bus in a high impedance state. The level on this pin is latched by a rising

edge of CK. The output drivers will be enabled or disabled with the rising edge in the next

timeslot (see Fig. 24 for applicable timing in diff erent modes).

36 ME Message Enable. When tied high the data latched in on the address bus is clocked out on

D0o-D15o. When ME is tied low, the contents of the addre ssed mem or y location will be

output on the bus. The level on this pin is latched in with the rising edge of the clock. The

actual mode change is implemented on the rising edge in the next timeslot. Refer to Figures

25 and 26 for more timing information .

37 Mx Mode X. One of three inputs which permit the selection of different operati ng modes for the

device. Refer to Table 1 for description of various modes.

38 My Mode Y. See description for pin 37.

39 M z Mo de Z. See description for pin 37.

40 NC No Connection.

41, 42 IC Internal Connecti on . Leave open for normal ope ratio n.

43 V

SS

Ground.

44 V

DD

Supply Voltage. +5V .

45 NC No Connection.

Pin Description

Pin # Name Description

MT9080 CMOS

2-104

46-61 A0-A15 Address Bus. These inputs have three different functions. Inputs A0-A10 are used to

address internal memory locations during read or write operat ions in all m odes except Sh ift

Register mode. In Shift Register mode, the leve ls latched in on A0-A1 0 program the delay

through the device. When the ME pin is tied high, the data latched in on A0-A15 is clocked

out on to the data bus (D0o-D15o).

62 CD

Change Detect. Open drain output which is pulled low when a change in the memory

contents from one frame to the next is detected by a Cyclic Redundancy Check (CRC).

Changes in memory contents resulting from microp rocessor access do not cause CD

to go

low. The output is reset to its normal high impedance state when the DS

input is strobed,

while the device has been selected (CS

is low).

63 V

DD

Supply Voltage. +5V .

64 V

SS

Ground.

65-68 D0o-D3o Output Data Bus. These three state outputs are part of a 16 bit data bus which is used to

clock out data from the device. Data is clocked out with the rising edge of the clock. See

Figures 24 to 26 for timing informa tion. The bus is actively driven when ODE is tied high. It

is disabled when ODE is tied low. Tyin g CS

high will also disable the output data bus in all

modes except Connect Memor y and Shift Register Mode s.

69 V

SS

Ground.

70-73 D4o-D7o Output Data Bus. See description for pins 65-68.

74 V

SS

Ground.

75-78 D8o-D11o Output Data Bus. See description for pins 65-68.

79 V

SS

Ground.

80-83 D12o-D15oOutput Data Bus. See description for pins 65-68.

84 V

DD

Supply Voltage. +5V .

Pin Description

Pin # Name Description

CMOS MT9080

2-105

Functional Description

The SMX is a flexible memory module suitable for

use in the construction of timeslot interchange

circuits used in PCM voice or data switches. The

device can be configured as a data memory or a

connection memory.

The SMX has separate 16 bit input and output data

busses. A 16 bit address bus and a full

microprocessor interface is also provided.

Data is clocked into and out of the device with the

signal applied at the CK (clock) input. Depending on

the mode of operation, the memory locations for the

read or write operation can be addressed

sequentially by the internal counter or randomly via

the external address bus. A messaging sub-mode,

which permits the data latched in on the address bus

to be multiplexed on to the output data bus, is also

available (see ME pin description).

The SMX ensures integrity of the stored data by

performing a Cyclic Redundancy Check (CRC) on a

per frame basis. When a change in the memory

contents is detected from one frame to the next, the

Change Detect (CD

) pin is pulled low. The output

will be reset to its normal high impedance state when

DS

input is strobed while CS is low (i.e., while the

device has been selected for microprocessor

access). The CD

output is not pulled low when the

memory contents have been modified by a processor

access to the device.

Modes Of Operation

The SMX can be programmed to operate in one of

eight modes as summarized in Table 1. The different

modes are used to realize specific switch

implementations. For example, to implement a 1024

channel switch, two SMXs are required. One is

operated in Data Memory mode, while the second is

operated in Connect Memory mode. A 2048 channel

switch can be realized using three SMXs. Two of the

devices are operated, alternatively, in Counter and

External modes, the third serves as the Connection

Memory. A detailed description of the

implementation is presented in the Applications

section of this data sheet. An outline of the device

functionality in each mode is presented below.

Table 1. SMX Mode s of Oper ation

Mode MXMYM

Z

Name Abbr.

1

2

3

4

5

6

7

8

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Data Memory - 1

Data Memory - 2

Connect Memory - 1

Connect Memory - 2

Counter Mode

External Mode

Shift Register Mode

Data Memory - 3

DM-1

DM-2

CM-1

CM-2

CNT

EXT

SR

DM-3

Data Memory Mode-1

Data Memory Mode-1 is designed for use in the

construction of a 1024 Channel Switch Matrix. Data

on the D0-D15 input bus is clocked into the S MX and

stored in memory locations addressed by the internal

11 bit counter. Data is clocked out according to the

addresses asserted on the address bus. The pin

configuration of the device in this mode is illustrated

in Fig .3

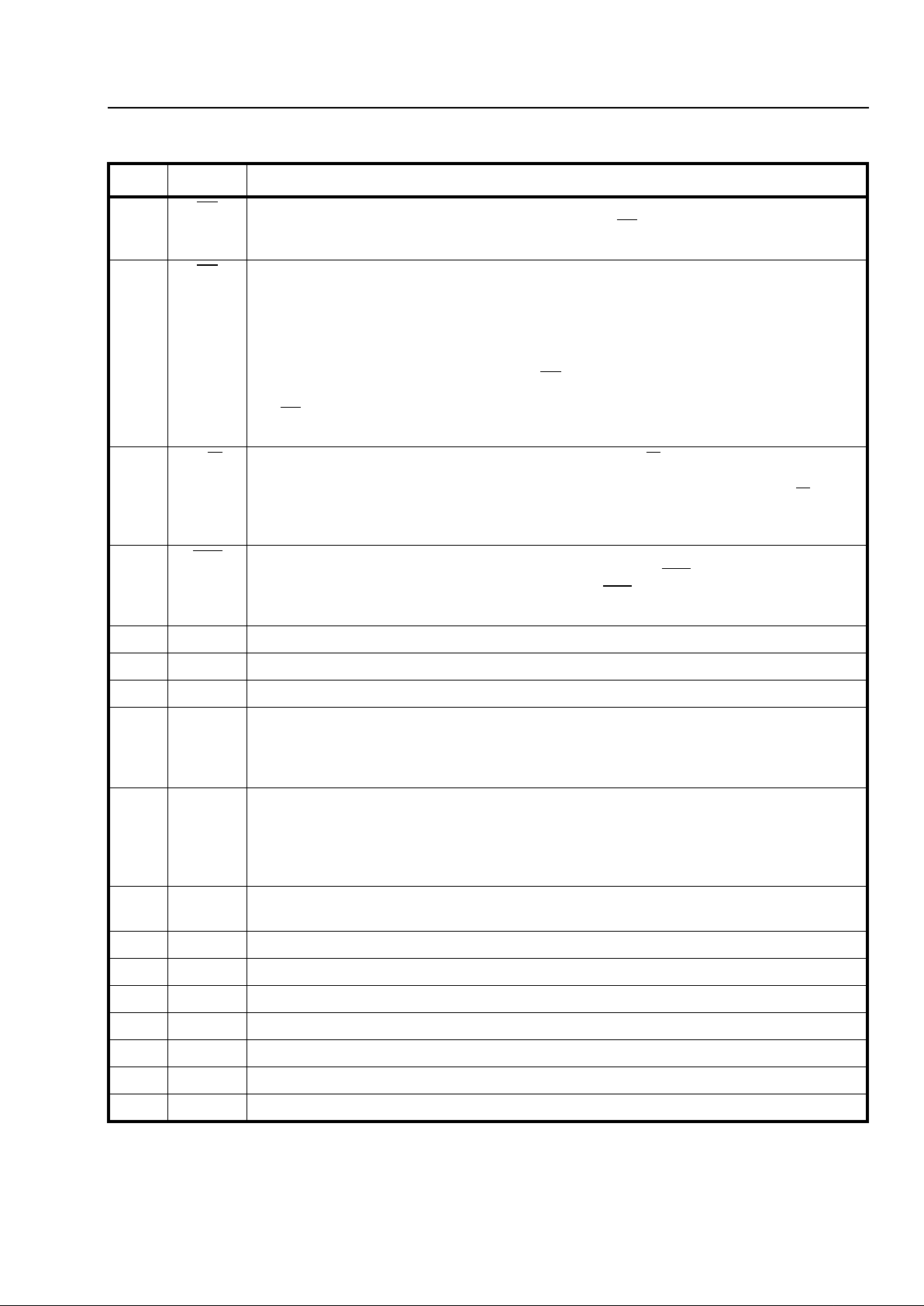

Fig. 3 - Data Memory Modes 1 and 2 Pinout

The timing for the read and write operation is

illustrated in Fig. 4. The first half of each clock period

is used for precharging the internal bus. Data is

latched in and out of the device with rising edge of

the CK clock. Correct operation of the device in this

mode requires 2048 clock cycles in a single frame

defined by the frame pulse. Consequently, for

switching of 64 kbit/s PCM voice channels, the clock

frequency must be 16.384 Mbit/s with a frame rate of

8 kHz.

The address supplied on the address bus is latched

in with the first positive clock edge in a channel

timeslot. The contents of the memory location

addressed will be clocked out on D0-D15o with the

first positive clock edge in the next timeslot (see Fig.

4).

In Data Memory Mode-1, the delay through the

switch depends on the number of channel timeslots

between the input c hannel and the output channel. If

the time difference between the input channel and

output channel is less than two channels, data

clocked into the device in the current frame will be

clocked out in the next frame. If the difference is

greater than or equal to two channels, data will be

clocked out in the same frame. This concept is

further illustrated in Fig. 5.

Data

Input

Data

Output

16

FP

D0i-D15

i

CD

A0-A15 ME ODE ZYZ

D0

o

-D15

o

CS

DS

DTA

16

MODE

CK

From Control Interface

MT9080 CMOS

2-106

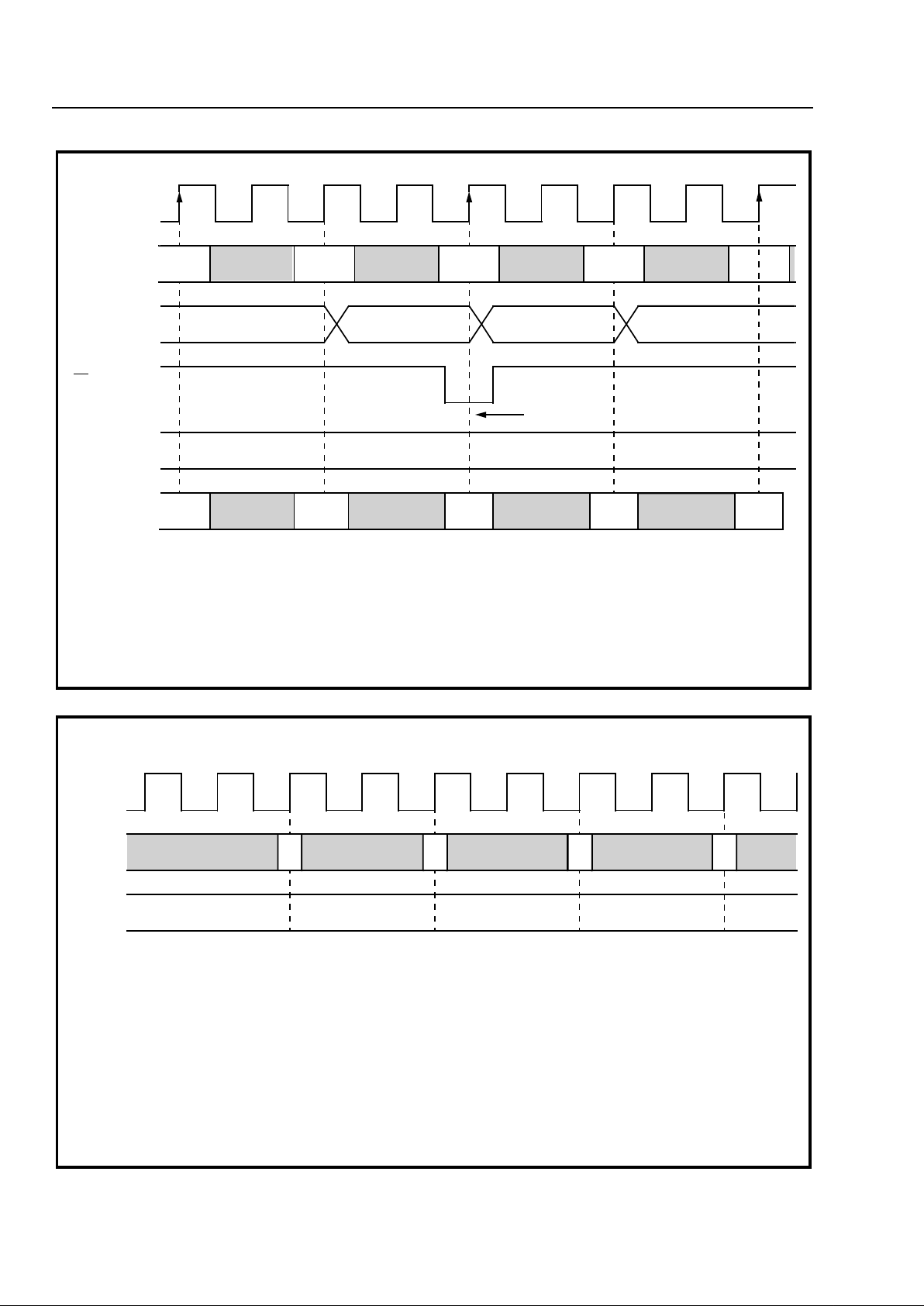

Figure 4 - Data Memory Mode Functional Timing

Figure 5 - Throughput Delay in Data Memory Mode-1

CK

External

Address

Bus A0-A15

Data Output

D0-D15o

FP

Address

generated by

Internal 11

Bit Counter

Data Input

D0-D15i

CH X CH Y CH Z

1022

1023

0

1

2101023

Counter Reset

CH X CH Y CH Z

PWP R

➀②

P = Precharge

R = Read Memory

W = Write Memory

Data is clocked out of the memory location addressed by external address bus. The address is latched in with CK edge

marked ➀. Data is clocked out with CK edge marked ②.

Data is latched into the device with the last rising edge of CK in the timeslot (e.g., edge ➂ in diagram). It is stored in the

➂➃

memory location address by the internal 11 bit counter with the next rising clock edge (edge ➃ in diagram).

CK

PW R

➀②

P

1 4

12345

23

P = Precharge

R = Read Memory

W = Write Memory

Data on the input bus of the SMX is latched into the device with last rising edge of the clock within a timeslot. It is

Data is clocked out of the memory location and latched onto the output data bus with first positive clock edge in the

Input

Data

Output

Timeslots

written into the internal memory with the following positive edge.

timeslot.

Switching channel 1 to channel 1 or channel 2 will result in one frame delay. Note that channel 2 is clocked out by CK

edge labelled ➀ while channel 1 is written into the memory with edge ②. However, if channel 1 is switched to channel

3, there will be only one channel delay.

CMOS MT9080

2-107

This mode provides minimum delay through the SMX

for any switching configuration.

Data Memory Mode-2

Data Memory Mode-2 is designed for use in

constructing a 1024 by 1024 channel double

buffered switch. This mode is similar in most

respects to Data Memory Mode-1. The double

buffering is achieved by dividing the internal 2048

memory into two equal blocks. In a single frame,

data is written into the first block and read from the

second. In the next frame, the data will be written

into the second and read from the first (see Figure

6). Frame sequence integrity of the data will be

maintained for all switching configurations if the

output frame is delayed by one channel with respect

to the input frame. In this case, data clocked into the

device during any of the channels in the current

frame will be clocked out in the next frame. However,

if the input and output frames are aligned, then data

switched from any input channel to output channels

0 or 1 will be clocked out one frame after the next consequently frame sequence integrity is not

maintained for channels 0 or 1. Frame sequence

integrity will be maintained for data switched to any

of the other output channels. (See SMX/PAC

Application Note, MSAN- 13 5 , f or mo r e info r m ati o n. )

It is possible to switch between Data Memory

Mode-1 and Mode-2 on a per timeslot basis.

Data Memory Mode-3

This mode is similar to Data Memory Mode-1.

However, there is no restriction on the minimum

acceptable clock frequency or frame rate. In this

mode, the size of the switching matrix depends on

the clock and frame rates provided as per the

following relationship:

where S is the number of channels in the switching

matrix F

FP

is the frame pulse frequency in Hz, and

F

CK

is the clock frequency in Hz. The following table

shows how the size of a switching matrix can be

varied by selecting a suitable combination of clock

and frame rates.

It is not possible to switch between Data Memory

Mode-3 and other modes on per-timeslot basis.

Connect Memory Mode -1

In Connect Memory Mode-1, the input data bus is

bidirectional. Internal memory locations can be

randomly accessed via the microprocessor bus. The

pinout of the device in this mode is illustrated in

Figure 7.

CK (kHz) FP

(kHz)

Number of channels in

the switching m atrix

16.384

16.384

16.384

12.288

12.288

8.192

8.192

4

8

16

4

8

4

8

2,048

1,024

512

1,536

768

1,024

512

S

=

F

CK

2 X F

FP

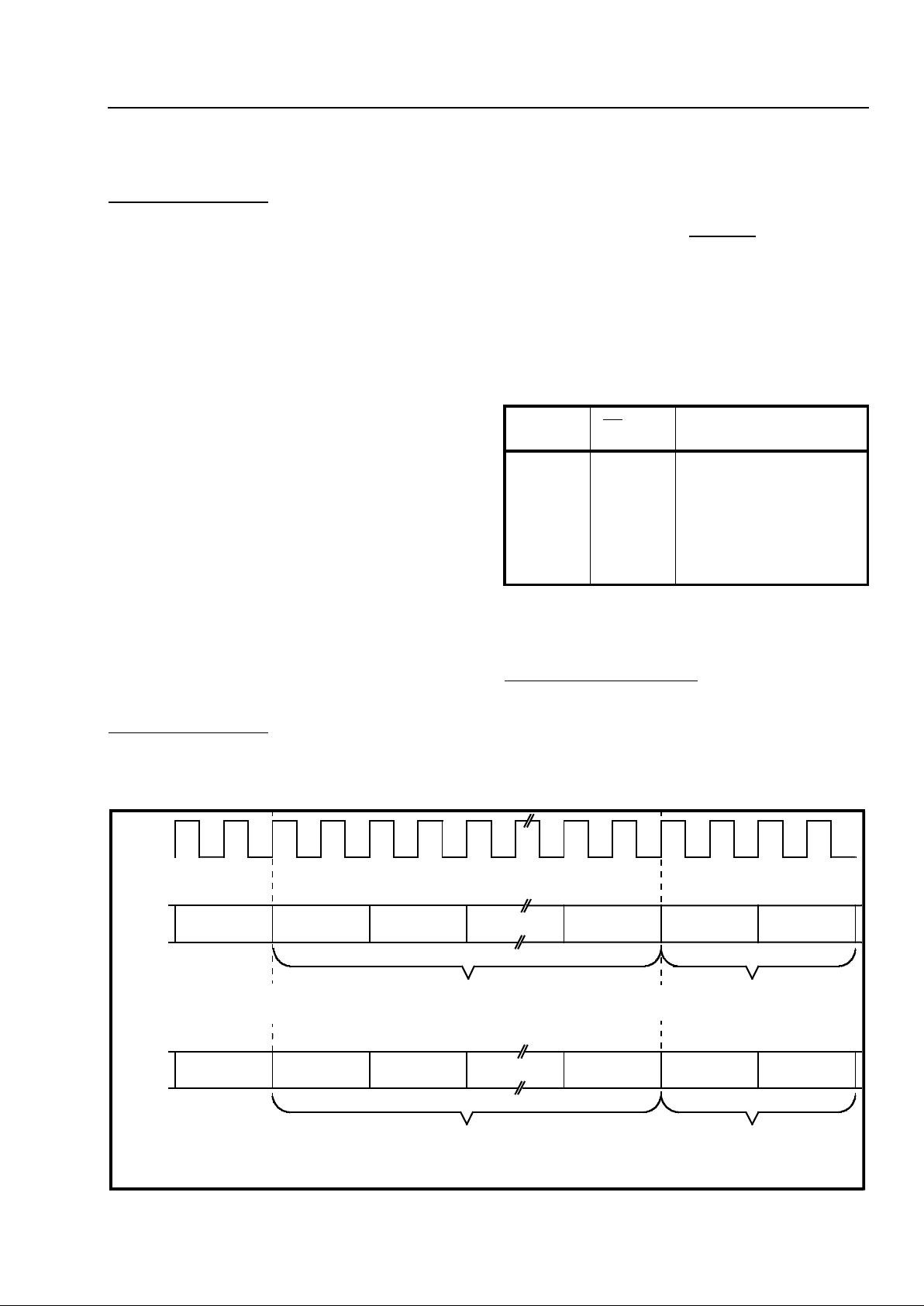

Figur e 6 - Da ta M em or y Mo de -2 F unc ti on al Tim ing

CK

Data

Input

Data

Output

FRAME 0

FRA ME 1

FRAME 2

FRA ME 1

FRAME 2

1023

0

1

102301 01

0

1

Written to Block 0 Written to Block 1

Read from Block 1 Read from Block 0

FRAME 0

Written to

Block 1

Read from

Block 0

1023

1023

Note: No input and output channel alignment is implied in the example shown above. It is assumed that the frame pulse for the

connection memory used to generate adresses for the read operation has a specific phase relationship with respect to the Data

Memory frame pulse.

MT9080 CMOS

2-108

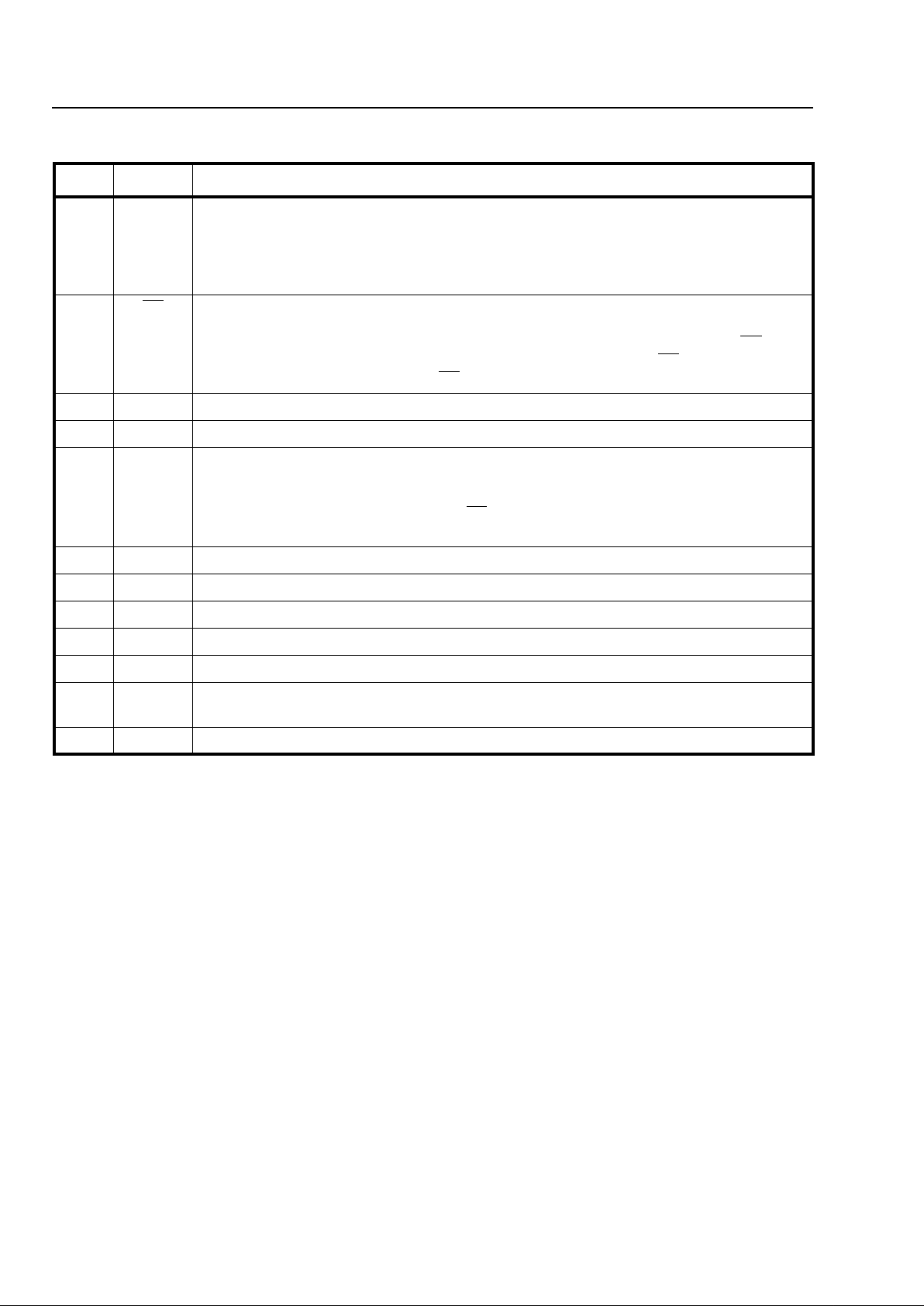

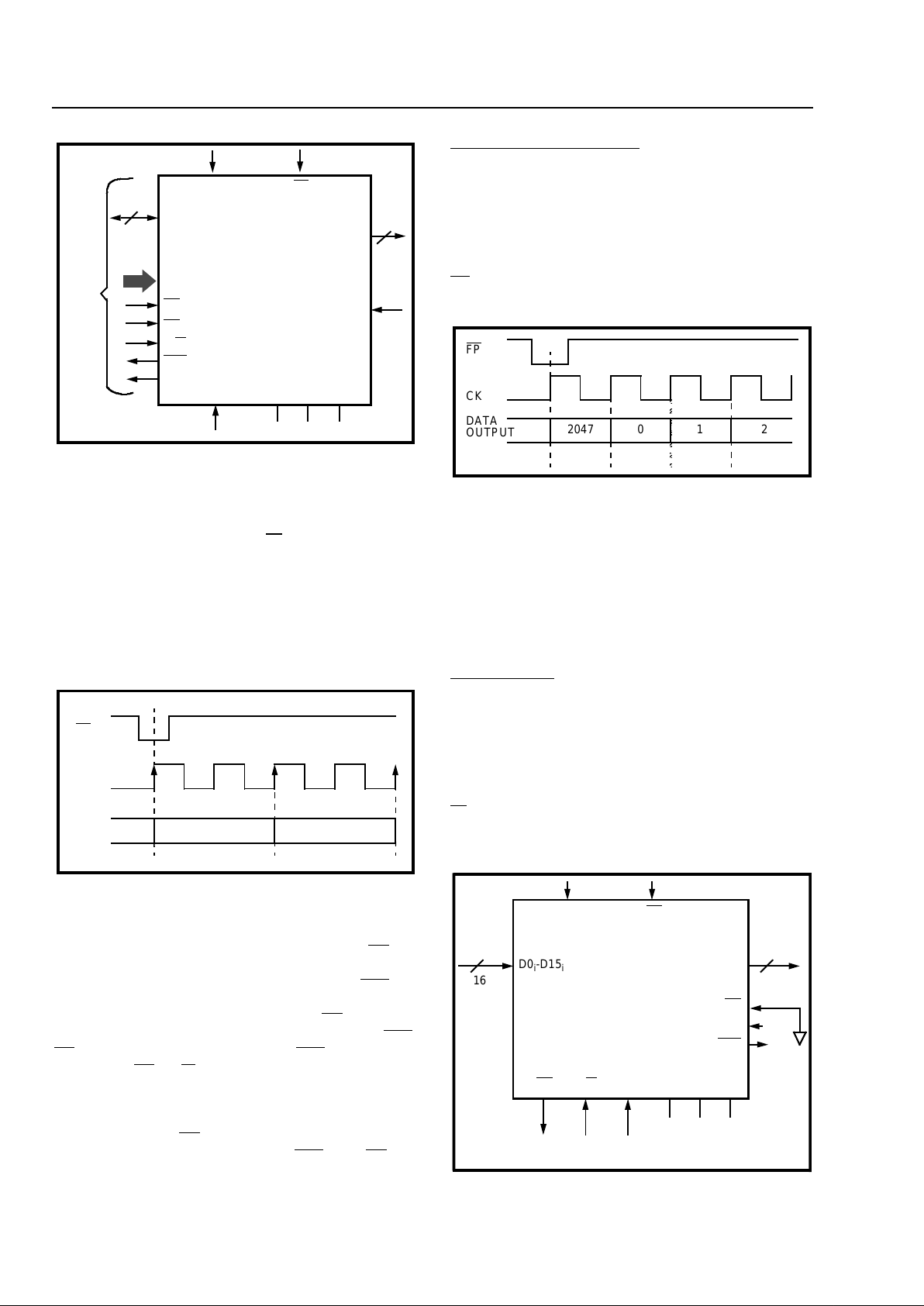

Fig. 7 - Connect Memory Modes Pinout

Data is clocked out on D0

o

-D15o from memory

locations addressed sequentially by the internal

counter. This counter is incremented every second

clock period and is reset with FP

. The frequency of

the clock signal used should be twice the data rate.

A timing diagram showing the relationship between

the data output and the clock signal is presented in

Fig. 8. With a clock rate of 16.384 MHz, the

maximum number of addresses that can be

generated in an 8 kHz frame period is 1024.

Fig. 8 - Connect Memory Mode-1 Functional

Timing

Microprocessor access timing is shown in Figures 28

and 29. During a microprocessor read cycle, DS

low

indicates to the SMX that the processor is ready to

receive data. The SMX responds by pulling DTA

low

when there is valid data present on the bus. The

processor latches the data in and sets DS

high. The

SMX completes the bus cycle by disabling the DTA

.

DS

should be kept low until after DTA is issued by

the SMX. CS

, R/W and the address lines should

also be asserted for the duration of the access. A

MPU write cycle is similar to the read cycle. Data will

be latched into the device approximately three clock

(CK) cycles after DS

goes low. When the device

has latched the data in, it will pull D TA

low. DS can

subsequently be set high.

16

CK

D0-D15

16

ODE

ME Z Y X

MODE

CD

DTA

CS

DS

R/W

A0-A15

D0

o

-D15

o

FP

0/1 1 0

Microprocessor

Interface

FP

CK

Data

Out

1023 0

Connect Memory Mode-2

Connect Memory Mode-2 is designed specifically for

2048 channel switching applications. Data is clocked

out on D0

o

-D15o with every rising clock edge from

memory locations addressed sequentially by the

internal counter (see Figure 9). This counter is

incremented with each clock period and is reset with

FP

or when a count of 2047 is reached.

Fig. 9 - Connect Memory Mode-2 Funct ional

Timing

The clock frequency should be 16.384 MHz for a

connection memory designed to support a 2048

channel switch.

Microprocessor access is similar to Connect Memory

Mode-1.

Counter Mode

This mode is designed for 2048 channel switching

applications. In the counter mode all read and write

addresses are generated sequentially by the internal

11 bit counter. The 11 bit counter is incremented

with each clock pulse. It will wrap around when it

reaches a count of binary 2047 or when it is reset by

FP

. The active input/output pins in this mode are

illustrated in Fig. 10.

Fig. 10 - Counter Mode Pinout

A

AAA

A

A

A

A

A

A

FP

CK

DATA

OUTPUT

2047 0 1 2

16

D0

i

-D15

i

CK FP

D0o-D15

o

CS

ODE

DTA

CD R/W ME XYZ

16

All other inputs should

be tied Low

100

Loading...

Loading...