MITEL MT90210AL Datasheet

MT90210

Multi-Rate Parallel Access Circuit

Preliminary Information

Features

• Parallel-to-serial and serial-to-parallel

conversion of up to 1536 full duplex channels or

3072 time-slots

• Serial port data rates selectable between 2.048,

4.096 or 8.192 Mb/s

• Provides a mechanism for a double buffer

function to be implemented in external memory

• 24 serial I/O lines programmable in different

modes: 12 in/12 out at 8.192 Mb/s (1536 full

duplex channels) or 24 bidirectional line modes

for 2.048 and 4.096 Mb/s

• Provides a bidirectional 8-bit parallel port

operating at 16.384 or 32.768 MByte/s for direct

interface to external memory (dual port)

• Provides an external 13-bit output address bus

for direct connection with an 8K-position dual

port memor y

• JTAG boundary scan

Applications

• Fast access to ST-BUS, SCSA, MVIP, and

H-MVIP serial backplanes

• Voice processing cards for Computer Telephony

Integration (CTI)

• Video and teleconferencing bridge cards

• Fast DSP access to serial TDM buses

DS5026 ISSUE 2 August 1998

Ordering Information

MT90210AL 100 Pin PQFP

-40 to +85°C

Description

The MT90210 is a 100-pin device used to interface a

parallel bidirectional 8 bit bus to 24 time division

multiplexed (TDM) serial streams. The device is

configured to perform simultaneous parallel-to-serial

and serial-to-parallel conversion with the capability

of handling up to 3072 channels, 1536 on the

transmit and 1536 on the receive direction.

Depending on the operation mode selected at the

mode pins, the individual 64 Kb/s channels on the

serial links may be configured as inputs or outputs.

The data on the parallel bus is in a format suitable for

interfacing with a dual-port RAM. Depending on the

data rate selected by the MD0-MD2 input pins, serial

data is clocked in and out on the serial streams at

either 2.048, 4.096 or 8.192 Mb/s.

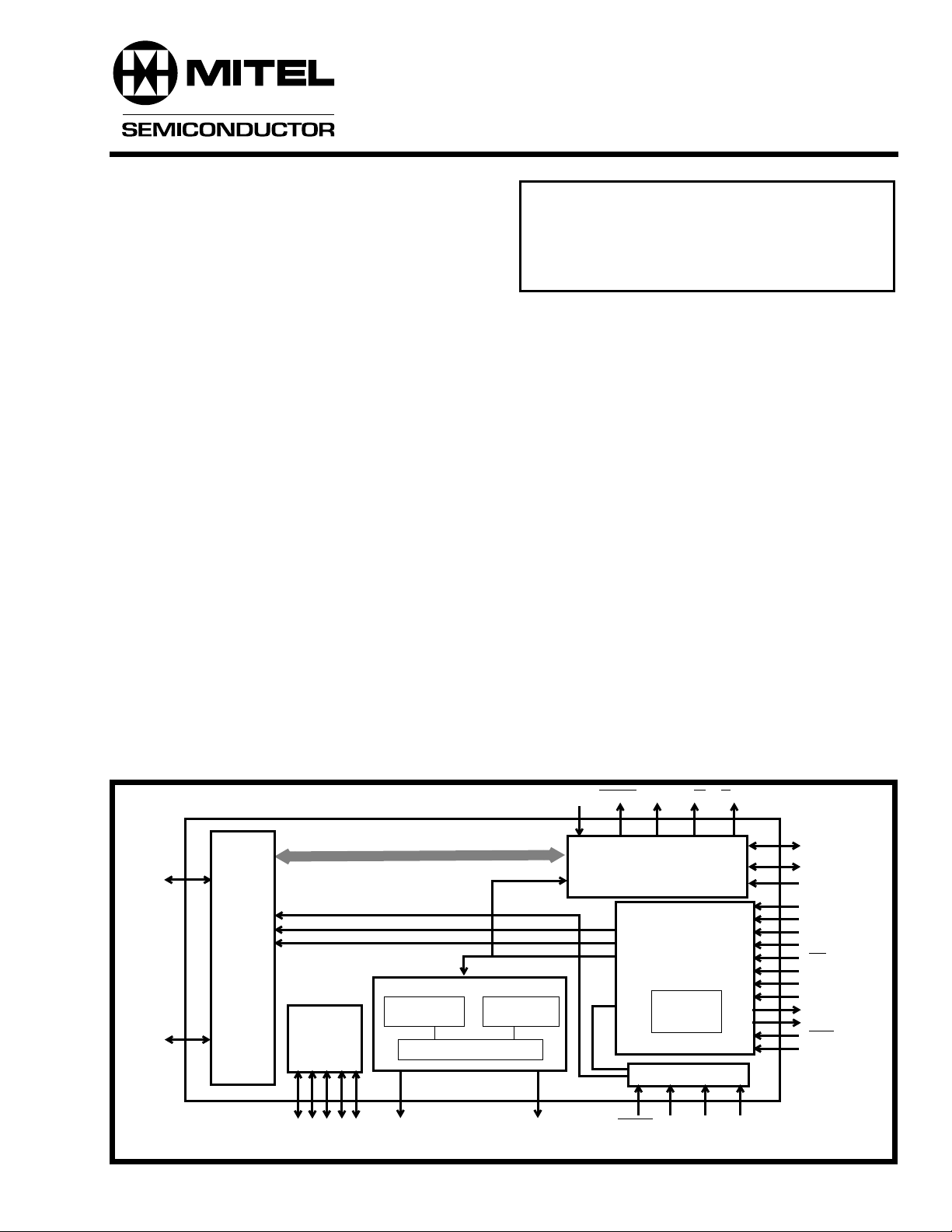

S0

•

•

•

•

•

•

•

•

S23

Shift

Registers

Boundary

Scan Test

TDI

TCK

TMS

RDin

Strobe

TDO

TRST

Address

Read

Counter

A0

•

•

•

Generator

MUX

•

•

Write

Counter

•

•

•

A12

Figure 1 - Functional Block Diagram

RBC R/W1 R/W2

External Memory

Access Control

Timing

Generation

Analog

PLL

Mode Control

OEser

MD2

P0

•

•

P7

WBC

SCLK

HC4

C16C16+

F0i

PCLK

PLLVSS

LP1,LP2

PLLAGND

CKout

RST

PLLVDD

MD0MD1

2-145

MT90210 Preliminary Information

A3

VSS

A2

S7

A1

VSS

S8S4S9

VSS

VDD

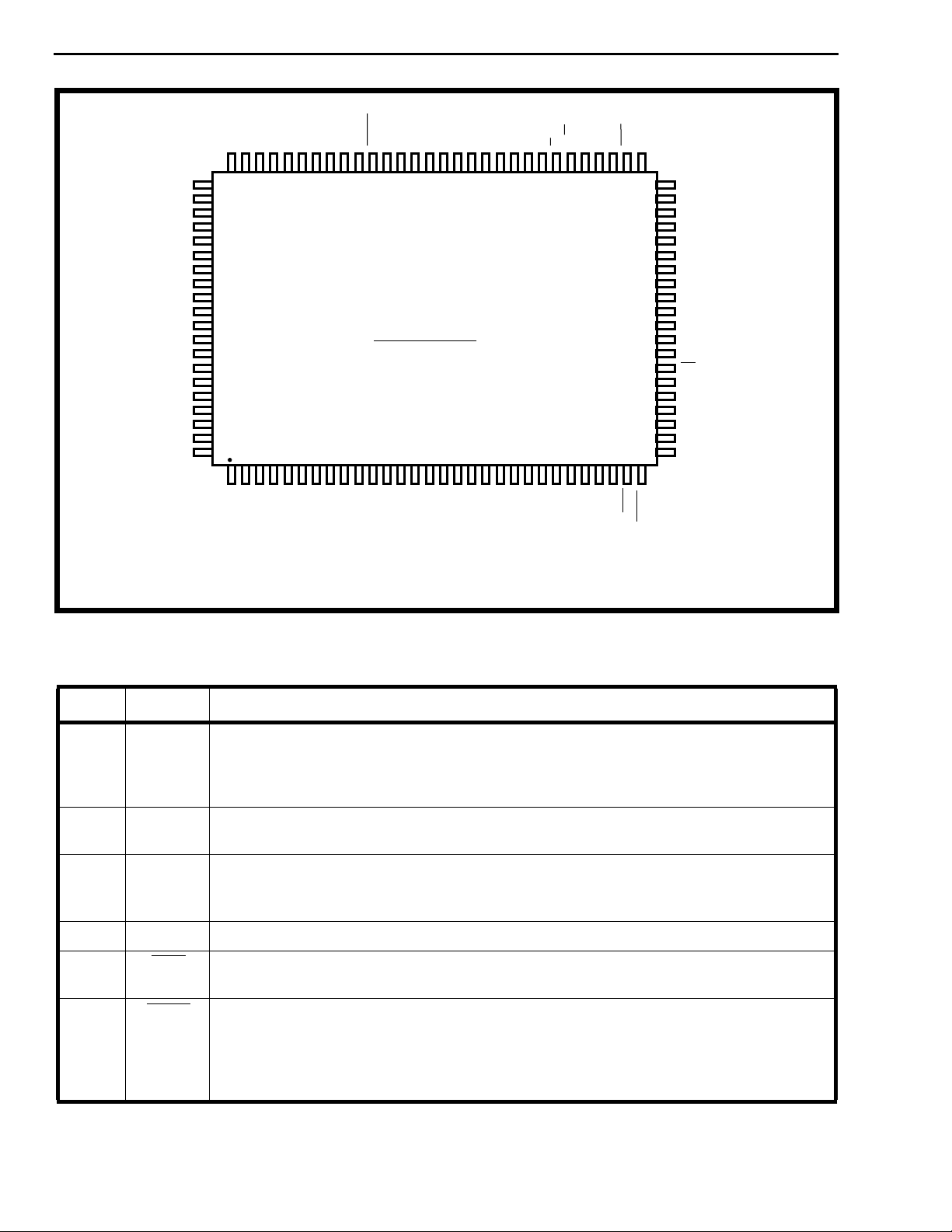

100 PIN PQFP

S11

S10

S12

S13

VSS

S14

S15

A6

A7

VSS

A8

A9

VDD

A10

VSS

A11

A12

RBC

VDD

VSS

WBC

S0

S1

S2

VSS

VDD

S3

82

84

86

88

90

92

94

96

98

100

A5

VSS

S5

VDD

S6

A4

VDD

P5

P6

P7

Strobe

A0

Note: the PQFP package meets the JEDEC standard MO-108, CC1.

Critical dimensions:

Lead pitch = 0.65mm,

Body Size = 14mm x 20mm,

Package size = 17.9mm x 23.9mm.

VSS

VDD

P4

VSS

VDD

S16

/W2

VSS

R

P0

P1

P2

P3

22 24 26 28 30

2018161412108642

S17

S18

S19

S20

S21

VSS

1

W

R/

S22

out

VDD2

CK

S23

TDO

PCLK

RST

525456586062646668707274767880

VSS2

50

48

46

44

42

40

38

36

34

32

RDin

VDD

PLL

PLLAGND

LP1

LP2

PLLVSS

IDDTN

TD

VSS2

C16C16+

VDD2

MD0

MD1

MD2

F0i

TRST

TCK

TMS

TDI

HC4

SCLK

OEser

Figure 2 - Pin Connections

Pin Description

Pin Name Description

95-97,

100,

1-3,

6

7-9,

11-15

18-22,

24-26

27 TDO Boundary Scan Test Data Output.

29 RDin Read P0-P7 input clock. This input is used by the MT90210 to sample b ytes coming in at

30 OEser Serial Port Output Enable (Input). On the parallel-to serial conv ersion direction, this input

S0-S2,

S3,

S4-S6,

S7

S8-S10,

S11-S15

S16-S20

S21-S23

Serial Lines 0-7 (TTL compatible with internal pullups in the range 25 - 125kΩ).

Bidirectional, time division multiplexed serial streams. According to mode selected by

MD0-2 inputs, distinct data rates can be selected at the serial port. In mode 3, these lines

are configured as inputs only. In modes 1, 2, 4 and 5, these lines become bidirectional.

Serial Lines 8-15. See description for S0-S7 above. In mode 3, S8-S11 are inputs and

S12-S15 are outputs. In modes 1, 2, 4 and 5 these are bidirectional lines.

Serial Lines 16-23. See descripton for S0 - S7 above . F or mode 3, these lines are outputs

and operate at 8.192 Mb/s rates. When operating in modes 1, 2, 4 and 5, these lines are

bidirectional.

the parallel port P0-P7 lines. Typically, the user should connect CKout to this input.

is used by the MT90210 to know which time-slots on the serial output streams will be

placed in high-impedance. This input is sampled synchronously along with the parallel

input data before the parallel-to-serial conversion takes place. When low, output serial

channels are actively driven. When set high, the output bus drivers are disabled.

2-146

Preliminary Information MT90210

Pin Description (continued)

Pin Name Description

31 SCLK Serial Port Clock (input). The SCLK clock is used to control the serial port operation in

modes 1,2,3 and 4. Depending on the operation mode selected at the MD0-MD2 inputs,

this input can accept 4.096 (MD2-0=000), 8.192 (MD2-0=001) or 16.384 (MD2-0 =010 and

011) MHz clock. In mode 5, this input is ignored.

32 HC4 H-MVIP C4. This is a 4.096 MHz clock utilized in modes 4 and 5 to maintain compatibility

with existing MVIP-90 systems. It is utilized to sample the fr ame pulse input (F0i). Not used

in Modes 1 - 3.

33 TDI Boundary Scan Test Data Input.

34 TMS Boundary Scan Test Mode Select.

35 TCK Boundary Scan Test Clock.

36 TRST Boundary Scan Test Reset.

37 F0i Frame Synchronization Signal (TTL compatible input). This input signal establishes

the frame boundary for the serial input/output streams.

38-40 MD2-MD0 Operation Mode Bits 0-2 (Input). Selects the data rate for the time division, multiplexed

serial streams. 2.048 (mode 1, MD2-0=000), 4.096 (mode 2, MD2-0=001) or 8.192 (mode

3, MD2-0=010) Mb/s data rates are available. When MD2-0 are set to 011 (mode 4), the

MT90210 operates in mixed data rates mode where S16-23 operate at 8.192 Mb/s and the

remaining serial streams run at 2.048 Mb/s. In mode 5 (MD2-0=100), the MT90210

operates as per mode 4 but the device will accept a differential clock reference at 16.384

MHz at pins C16+ and C16-.

42 C16+ Serial P ort Clock Input.In mode 5 (MD2-0= 100), this is a 16.384 MHz diff erential signal.

Note used in Modes 1 - 3.

43 C16- Serial Port Clock Input. The complement to C16+.

45 TD Reserved - Do not connect.

46 IDDTN Connect to Ground.

47 PLLVSS PLL Ground Input.

48 LP2 Loop Filter Input. An external RC circuit is required at this input, refer to Figure 10.

49 LP1 Loop Filter Input. An external RC circuit is required at this input, refer to Figure 10.

50 PLLAGND PLL Analog Ground output. Provides ground to PLL loop filter, refer to Figure 10.

51 PLLVDD PLL Power Input. +5V

52 RST RESET. A low on this pin resets the device.

53 PCLK Parallel Port Clock Input. CKout must be connected to this input.

54 CKout Internal VCO Output Signal. Output of internal PLL frequency multiplier. In mode 1 the

frequency is 16.384 MHz, for the other modes the frequency is 32.768 MHz. Must be

connected to PCLK only.

56 R/W1 Read/Write Output 1. This output signal toggles low for the last half of a memory write

cycle indicating valid data.

57 R/W2 Read/Write Output 2. This output is low f or memory read operations and high for memory

write operations.

2-147

MT90210 Preliminary Information

Pin Description (continued)

Pin Name Description

58-59,

61-62,

64,

66-68

70 Strobe Strobe Output. This output is typically connected to the Chip-enable input of the external

72-73,

75- 77,

80-82,

84-85,

87,

89-90

91 RBC Read Data Block Complete (output). A transition on this output is used to notify the

94 WBC Write Data Block Complete (Output). A transition on this output is used to notify the

P0-P1,

P2-P3,

P4,

P5-P7

A0-A1,

A2-A4,

A5-A7,

A8-A9,

A10,

A11-A12

Parallel Input/Output Data Bus. This 8 bit data bus is a bidirectional parallel port used to

perform 8-bit transactions between the MT90210 and the external dual port RAM. Data is

clocked in and out of the P0-P7 parallel port according to Figures 22 and 23.

dual port RAM. It is kept low during all read cycles, stays high during inactive periods and

goes low for the last half of a memory write cycle.

External Memory Address Outputs A0-A12. These 13 address output lines are provided

by the MT90210 to allow a direct connection to an external dual port RAM.

external CPU that the MT90210 has finished reading the contents of one entire 125µs

frame from the external dual port memory (e.g.; from addresses 0000h to 0FFFh in modes

3, 4 or 5). Whenever RBC toggles , the MT90210 starts reading the next half of the memory

(addresses 1000h to 1FFFh) while the local CPU updates the first half with more data to

be sent. RBC toggles every 125µs. When this signal is low, the MT90210 is reading the

lower memory block.

external CPU that the MT90210 has finished writing the contents of one entire 125µs

frame into the external dual port memory (e.g; from addresses 0000h to 0FFFh in modes

3,4 or 5). Once WBC toggles, the local CPU can access the Dual port memory to get the

data while the MT90210 writes the contents of the next 125µs frame into the other half

(addresses 1000h to 1FFFh) of the dual port memory. WBC toggles every 125µs. When

this signal is low, the MT90210 is writing to the lower memory block.

4,16,

63, 71,

78, 86,

92, 99

41, 55 V

5,10,

17, 23,

60, 65,

69, 74,

79,83,

88, 93,

98

28 V

V

V

DD

DD2

SS

SS2

Supply Input. +5V.

Supply Input. +5V.

Ground.

Ground.

2-148

Preliminary Information MT90210

Functional Description

The MT90210 is a 100-pin device that converts

incoming serial telecom streams of 2.048, 4.096 or

8.192 Mb/s on to an 8-bit parallel bus, and converts

input data on this parallel bus to the outgoing serial

telecom links. The device is configured to perform

simultaneous parallel-to-serial and serial-to-parallel

conversion.

MT90210 interfaces up to 24 bidirectional serial data

streams to a byte oriented parallel port for access by

a dual-port RAM. It contains an address generator

for parallel port read and write operations directly to

an external dual port memory. A single MT90210

device can handle up to 3072 channels, 1536 on the

transmit and 1536 on the receive direction.

Depending on the operation mode selected at the

mode pins (MD0-MD2), the 64 kb/s serial telecom

channels may be configured as inputs or outputs.

The data on the parallel bus is in a format suitable for

interfacing with popular dual port memories.

Depending on the data rate selected by the MD0MD2 input pins, serial data is clocked in and out on

the serial streams at either 2.048, 4.096 or 8.192

Mb/s, as shown in Figure 6. A mechanism for

implementing external double buffering is provided

by the Write Block Complete (WBC) and Read Block

Complete (RBC) output pins. Double buffering the

data allows the processor to independently access

an entire frame of data in the external memory while

the MT90210 reads or writes the complementary

frame in the memory. For e xample , in mode 3 (Figure

4), during the first frame the MT90210 will read and

write in to the first half of the memory space (Block

0) and during the second frame the MT90210 will

read and write in to the second half of the memory

space (Block 1). Within each block the transmit data

and receive data are separated and located at fixed

address locations. The operation of WBC and RBC is

shown in Figures 7a and 7b.

On the external memory port side, the device

performs 8-bit wide operations with a cycle time of

30 or 61 ns. The parallel port operates at 16.384

MByte/s (for mode 1) or 32.768 MByte/s (for modes

2,3,4 and 5). To create the high speed clock required

to manage the byte operations at the parallel port, a

built in PLL multiplies the serial port input clock

(SCLK) by a factor of two or four depending on the

mode. In all operation modes, the user should

connect the PLL CKout to PCLK input.

A separate input pin, Output Enable serial (OEser

pin 30), may be used to selectively tristate individual

64Kb/s serial links. By using a 9-bit external dual

port RAM and connecting the ninth bit to OEser as

shown in Figure 9, the processor may disable an

individual channel by setting the ninth bit for that

channel in the transmit (TX) portion of the current

block. The remaining 8 bits for this channel may be

any value since they are ignored by the MT90210

when the ninth bit is 1. To avoid contention on the

serial bus, it is recommend that the user configure all

serial streams as inputs at start-up. This may be

done by setting all OEser bits to 1 in the TX por tions

of both memory blocks. In mode 3, the serial streams

are permanently configured as 12 inputs and 12

outputs, and the state of OEser is ignored.

An Overview of CTI bus protocols

Multi-Vendor Integration Protocol (MVIP) provides a

coherent approach to building solutions for

worldwide markets by merging computing and

communications technologies under one open

architecture. MVIP ensures inter-operability among

telephone-based resources (such as trunk

interfaces, voice, video, fax, text-to-speech, speech

recognition) for use within a computer chassis in an

individual or networked configuration. H-MVIP

addresses the need for higher telephony traffic

capacity in individual computer chassis. H-MVIP

defines three major items that together make a

useful digital telephony transport and switching

environment: the H-MVIP digital telephony bus with

up to 3072 "time-slots" of 64 Kb/s each; a bus

interface with digital switching that allows a group of

H-MVIP interfaced circuit boards to provide

complete, flexible, distributed telephony switching;

and a logical device driver model and standard

software interface to a logical model.

Operating Modes

The MT90210 device can operate in one of five

modes appropriate for different application needs.

Mode selection must be done while the device is in

reset (RST low and a valid clock applied to the PCLK

input). These modes are explained in the following

paragraphs.

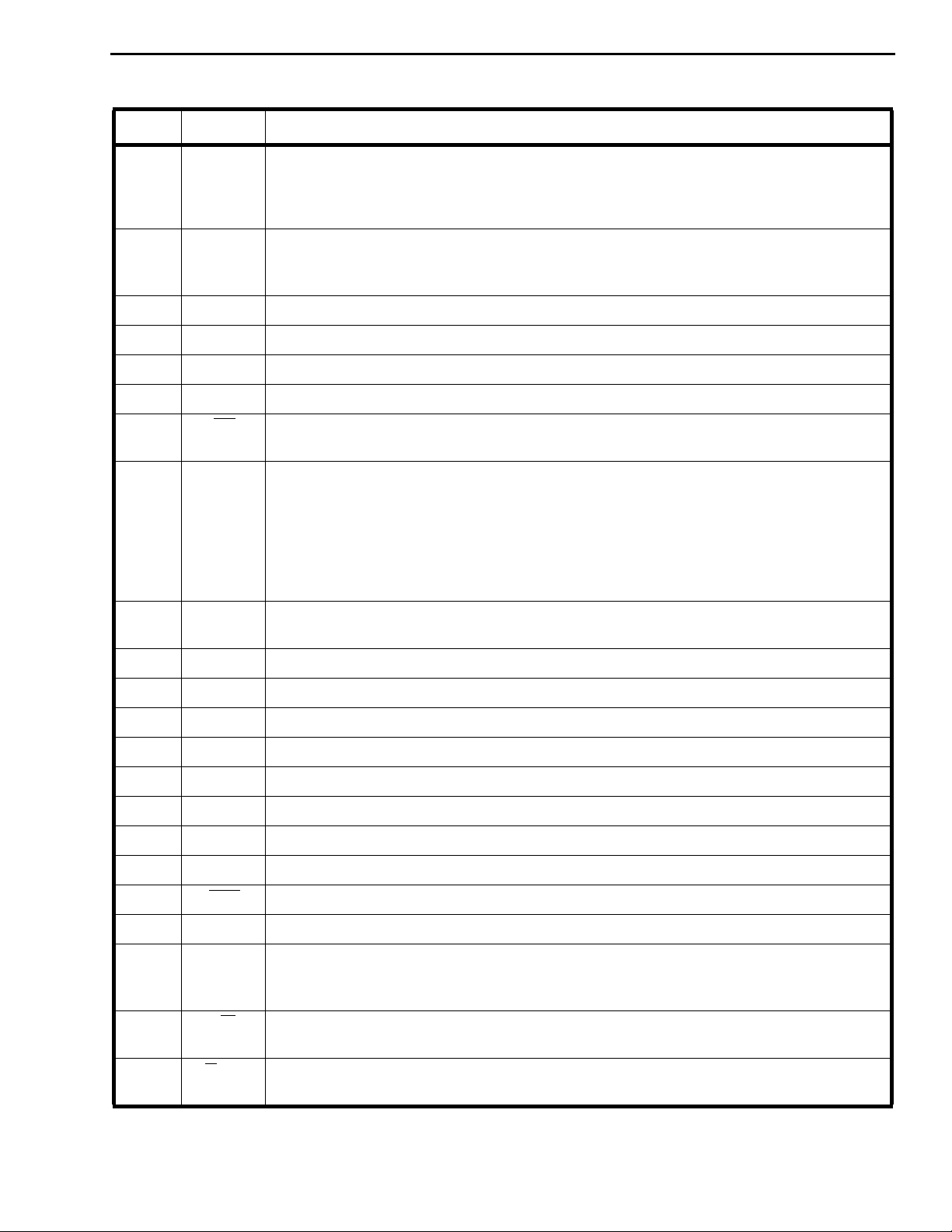

Mode 1: The serial input/output format conforms to

the ST-BUS requirements when the data rate is

2.048 Mb/s (see Figure 6). Serial port clock (SCLK)

is 4.096 MHz. The on-chip PLL produces a phase

locked 16.384 MHz clock (CKout) from the SCLK

input. In this data rate operation, the 24 serial lines

(S0-23) become bidirectional links at 2.048 Mb/s.

The ST-BUS is a time-division multiplexed serial bus

with 32, 8-bit channels per frame. Frame boundaries

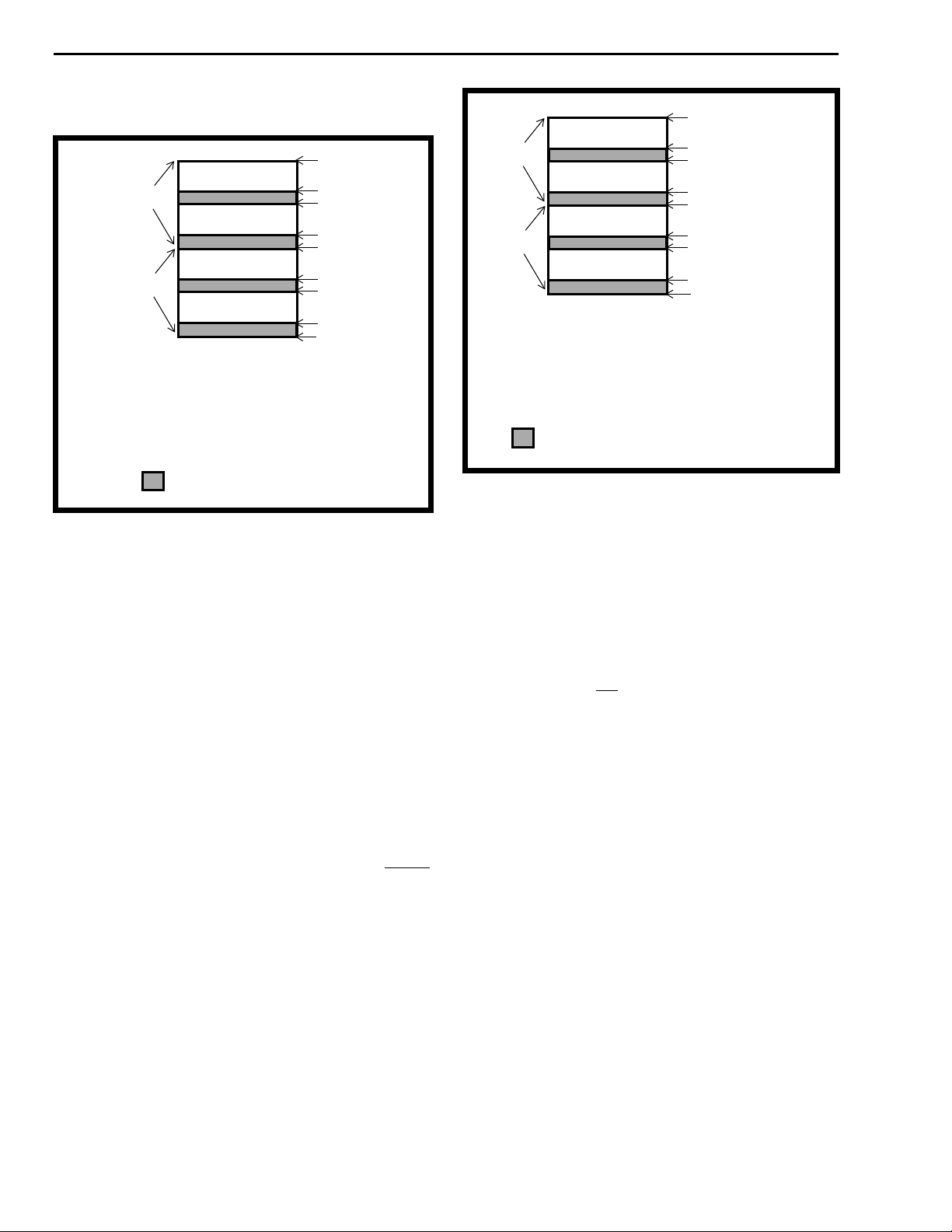

are delineated by the frame pulse. Figure 3 depicts

2-149

MT90210 Preliminary Information

how the data from the serial port is mapped into the

external dual port memory.

768 bytes

for TX

BLOCK 0

BLOCK 1

24 bidirectional streams at 2.048Mb/s

768 bytes

for RX

768 bytes

for TX

768 bytes

for RX

MODE 1

0000

02FF

0400

06FF

0800

0AFF

0C00

0EFF

0FFF

1536 bytes

for TX

BLOCK 0

BLOCK 1

24 bidirectional streams at 4.096Mb/s,

or 12 in / 12 out at 8.192Mb/s

Address outputs used: A0-A12

1536 bytes

for RX

1536 bytes

for TX

1536 bytes

for RX

MODES 2 & 3

0000

05FF

0800

0DFF

1000

15FF

1800

1DFF

1FFF

Address outputs used: A0-A11;

A12 always zero.

Legend:

unused memory space

Figure 3 - Dual Port RAM Memory Map for

Mode 1

Mode 2: When the device is configured for

4.096 Mb/s data rate operation, each of the 24 timedivision multiplexed serial streams is made up of 64

channels. In this data rate operation, the 24 serial

lines (S0-23) become bidirectional links at

4.096 Mb/s. Serial por t clock (SCLK) is 8.192 MHz.

The on-chip PLL produces a phase locked 32.768

MHz clock (CKout) from the SCLK input. Figure 4

depicts how the data from the serial port is mapped

into the external dual port memory.

Mode 3: When the device is configured for 8.192

Mb/s data rate operation, each of the 24 timedivision multiplexed serial streams is made up of 128

channels. In this mode, bidirectional operation on the

serial port streams is not provided and the MT90210

is set in a 12 in / 12 out configuration and the OEser

input is ignored. Streams S0-S11 are configured as

inputs, and S12-S23 are configured as outputs.

Serial port clock is 16.384 MHz. The on-chip PLL

doubles this clock to produce a CKout clock of

32.768 MHz. Figure 4 depicts how the data from the

serial port is mapped into the external dual port

memory. Figure 12 and Table 3 show the write and

read operations on the parallel port at the frame

boundary.

Legend:

unused memory space

Figure 4 - Dual Port RAM Memory Map for

Modes 2 and 3

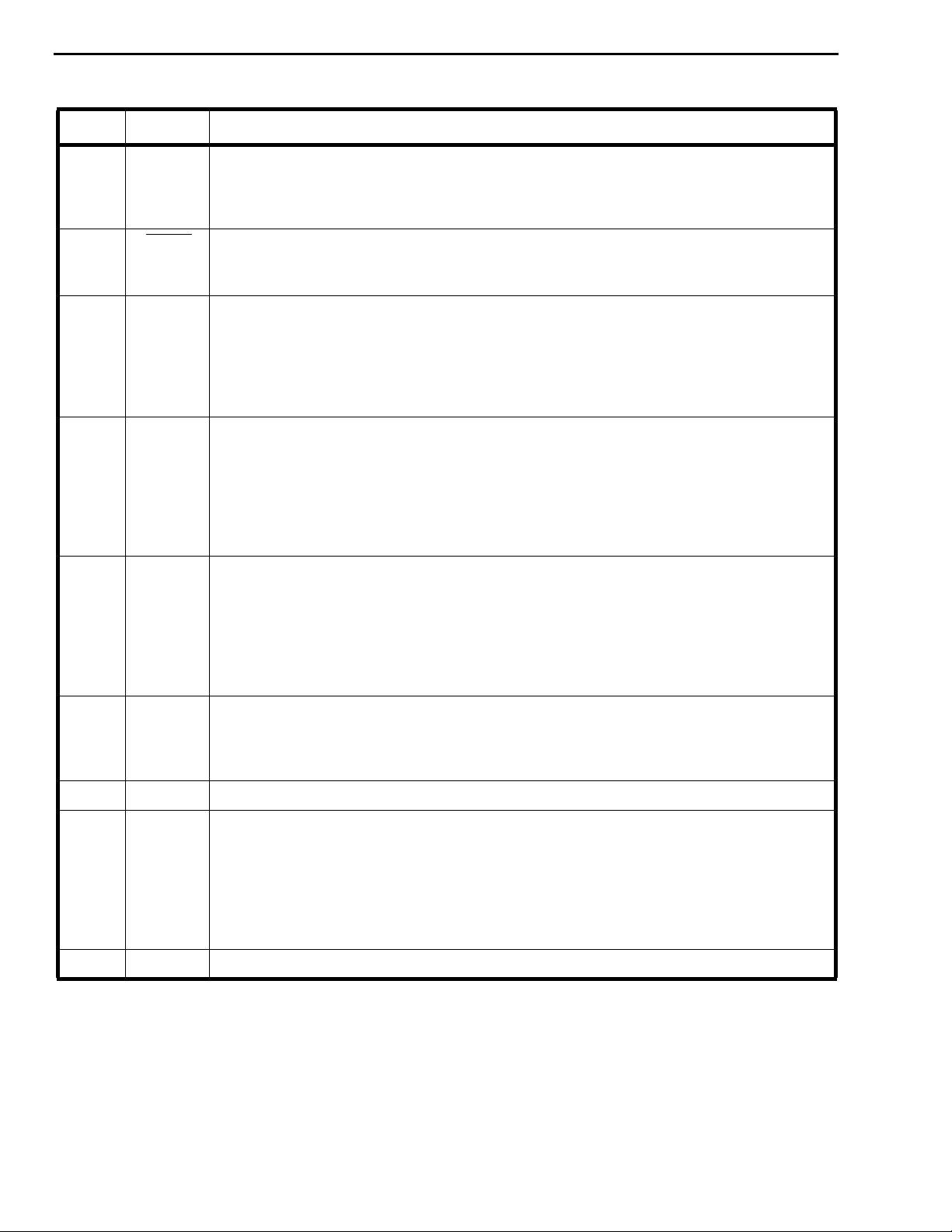

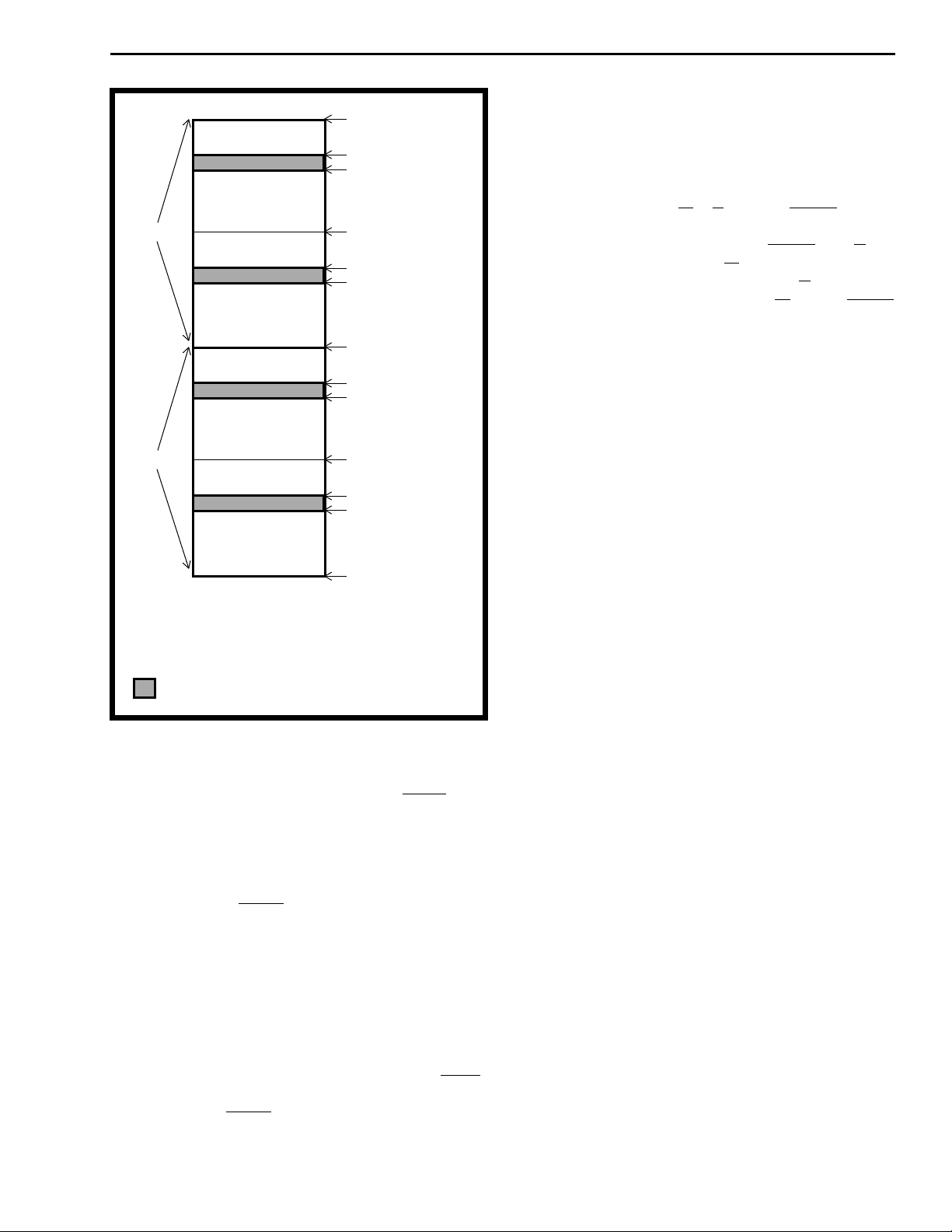

Mode 4: The MT90210 is configured such that the

24 serial streams are bidirectional and split into two

different functional groups: (i) streams S0-S15

operate at 2 Mb/s rate (512 timeslots), (ii) S16-S23

operate at 8.192 Mb/s rate (1024 timeslots). Memory

mapping for mode 4 is described in Figure 5. For

compatibility with legacy MVIP timing, mode 4

provides an additional clock input at 4.096 MHz

(HC4 input pin) which allows the device to detect

frame sync pulse (F0i) with a typical width of 244 ns.

In mode 4, the 16.384 (SCLK) and 4.096 (HC4) MHz

clocks should be in sync according to H-MVIP

specifications. The on-chip PLL doubles SCLK to

produce a CKout signal of 32.768 MHz. Figure 13

and Table 4 show the write and read operations on

the parallel port at the frame boundary.

Mode 5: Identical operation as per mode 4 with the

difference that the 16.384 MHz clock is a differential

signal received at the two input pins, C16+ and C16of the MT90210 device. The differential clock is

needed to eliminate distortion in the clock signal

passing through a ribbon cable as per H-MVIP

specification. The SCLK input is not used in this

mode. Memory mapping for mode 5 is depicted in

Figure 5.

2-150

Preliminary Information MT90210

Functional operation of the MT90210

512 bytes for

S0-S15 TX

1024 bytes for

S16-S23 TX

BLOCK 0

BLOCK 1

S0-S15 bidirectional 2.048Mb/s streams

S16-S23 bidirectional 8.192Mb/s streams

Address outputs used: A0-A12

Legend:

unused memory space

512 bytes for

S0-S15 RX

1024 bytes for

S16-S23 RX

512 bytes for

S0-S15 TX

1024 bytes for

S16-S23 TX

512 bytes for

S0-S15 RX

1024 bytes for

S16-S23 RX

0000

01FF

0400

0800

09FF

0C00

1000

11FF

1400

1800

19FF

1C00

1FFF

Figure 5- External Double Buffer Operation and

Memory Arrangement in Modes 4 and 5.

Bidirectional Operation: Serial output channel

timeslots can be tri-stated by setting the OEser input

pin high during a specific parallel channel timeslot.

Note that when operating in bidirectional mode, the

MT90210’s I/O buffers on the serial port are

permanently at high impedance and the control of

contention on the serial bus has to be done by the

user through the OEser input pin. In modes 1, 2, 4

and 5 all of the transmit channels on the serial port

side are copied back to the memory interface. This is

true only in bidirectional modes (i.e., modes 1, 2, 4

and 5). Note that only the transmit (output) channels

are copied back to the memory and that the input

channels remain unaffected.

For a specific time-slot sampled at the external

memory parallel interface, the respective OEser

input pin must be in the desired state; i.e., the

sampling of the OEser input is synchronized with the

parallel byte read at the P0-P7 lines.

device at the parallel interface for

modes 1, 2, and 3

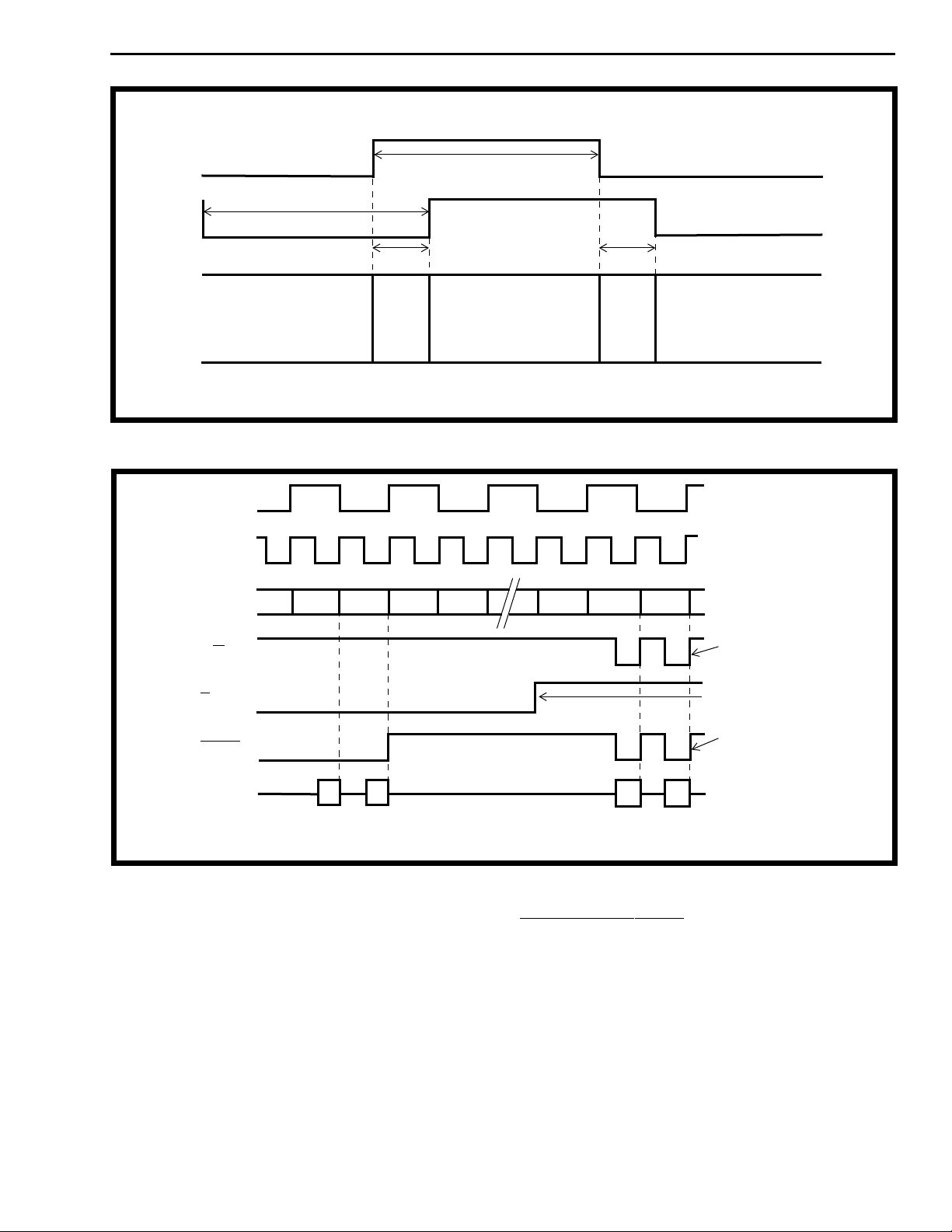

Figures 8, 12, and 13 depict the parallel port READ

and WRITE operation of the MT90210 device. The

state of the signals R/W1, R/W2 and Strobe defines

a valid Read or a valid Write operation. During a

valid READ operation the signals Strobe and R/W2

stay LOW while the signal R/W1 is always HIGH. For

the valid WRITE operation the signal R/W2 always

stays HIGH while the signals R/W1 and Strobe

toggle. Table 3 represents the sequence of events as

depicted in Figure 12 during the last channel at the

end of an ST-BUS frame. The MT90210 device

repeats the same sequence of operation during the

entire frame. For example, during channel 127 at the

end of an ST-BUS frame the MT90210 will write

channel 126 (streams 0 to 11) and read from channel

1 (streams 12 to 23) of the next frame as shown in

Table 3. Note that there is a two channel difference

between a write and a read sequence. In mode 1

and mode 2, the MT90210 device performs a group

of writes and a group of reads separated by 8 PCLK

periods, while for modes 3, 4 and 5 they are

separated by 4 PCLK periods.

Functional operation of the MT90210

device at the parallel interface for mode

4 and mode 5

Table 4 represents the sequence of events when the

MT90210 device is operating at a mixed rate of

operation (mode 4 and mode 5) as depicted in Figure

13. The MT90210 device repeats the same sequence

of operation as shown in Table 4 throughout the entire

frame. In mode 4 and mode 5 the MT90210 device is

configured with 24 bidirectional serial streams and split

into two different rates: S0 to S15 operate at 2.048

Mb/s data rates (512 time-slots) and streams S16 to

S23 run at 8 Mb/s data rates (1024 time-slots). In this

mode, 12 writes are carried out during a parallel port

write cycle and 12 reads during a read cycle. Of each

group of 12, 8 are dedicated to the high-speed 8.192

Mb/s links, therefore four slots are available for the

2.048 Mb/s links. To process all the 16 streams

devoted for 2.048 Mb/s, four separate write or read

cycles are required (these slots are denoted with the

suffix "a", "b", "c", "d" in Figure 13). Each write or

read cycle will use four time-slots. For example, read

or write cycle "a" uses streams S0 to S3, read or

write cycle "b" uses streams S4 to S7, read or write

cycle "c" uses streams S8 to S11 and read or write

cycle "d" uses streams S12 to S15 (see Table 4).

There is a two channel difference between a read

and write sequence for 2 Mb/s data and an eight

channel difference for 8 Mb/s data.

2-151

MT90210 Preliminary Information

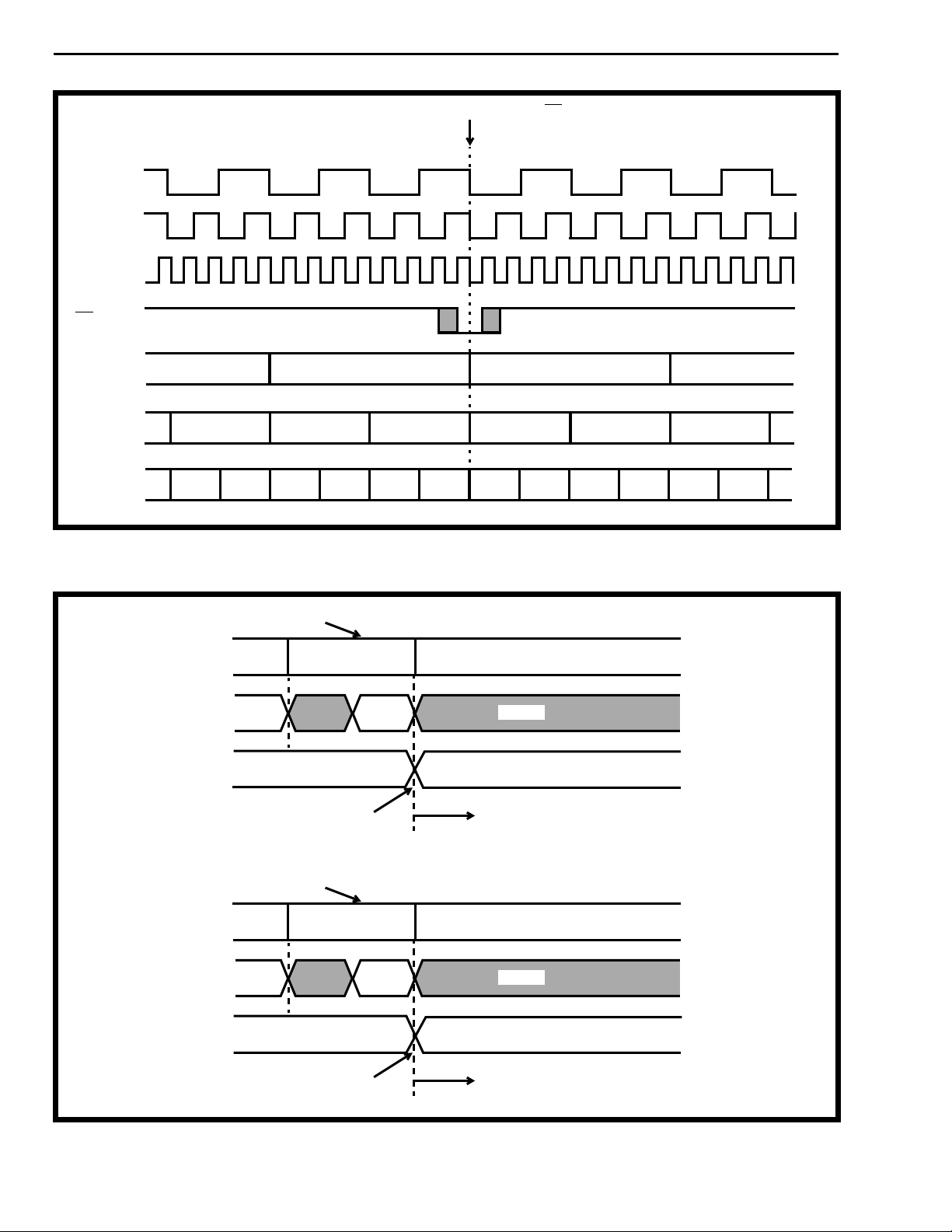

Frame Boundary Established by F0i

SCLK

(4 MHz)

SCLK

(8 MHz)

SCLK, C16

(16 MHz)

F0i

Serial I/O

2 Mb/s

Serial I/O

4 Mb/s

Serial I/O

8 Mb/s

W

R

I

T

E

Ch. 31, Bit 1

Ch. 63, Bit 2 Ch. 63, Bit 1 Ch. 63, Bit 0 Ch. 0, Bit 7 Ch. 0, Bit 6 Ch. 0, Bit 5

Ch. 127,

Bit 5

Ch. 127,

Bit 4

Ch. 127,

Bit 3

Ch. 31, Bit 0 Ch. 0, Bit 7 Ch. 0, Bit 6

Ch. 127,

Bit 2

Ch. 127,

Bit 1

Ch. 127,

Bit 0

Ch. 0,

Bit 7

Ch. 0,

Bit 6

Ch. 0,

Bit 5

Ch. 0,

Bit 4

Figure 6 - Serial Port Functional Timing

last write address

of frame n

A0-A12

P0-P7

WBC

Data

Out

address x

Data

Out

inactive

inactive

Ch. 0,

Bit 3

Ch. 0,

Bit 2

2-152

MT90210 finishes writing

data from frame n.

last read address

of frame n

R

E

A

A0-A12

P0-P7

Data

In

address y

Data

In

MT90210 will handle parallel port

transactions related to frame n +1.

inactive

inactive

D

WBC

MT90210 finishes reading

data from frame n.

MT90210 will handle parallel port

transactions related to frame n +1.

Figure 7a - WBC and RBC Output Transition

Preliminary Information MT90210

RBC

125 us

WBC

Exclusive access of

Block 0

125 us

t

NA

Access

of both

Block 0

&

Block 1

Exclusive access of

Block 1

t

NA

Access

of both

Block 0

&

Block 1

tNA ~ 1 timeslot for modes 1, 2 & 3

tNA ~ 3 timeslots for modes 4 & 5

Exclusive access of

Block 0

Figure 7b - WBC and RBC operation in relation to accessing data from Block 0 and Block 1

SCLK

PCLK

A0-A12

R/

W1

R/W2

Strobe

A

RD

A

RD

A

WR

A

WR

Toggles only during

write data cycle

Changes state (high to low)

on every change of a block

of reads or block of writes

Low during read cycle,

high during inactive

periods and toggles

during write cycles

P0-P7

Note: The MT90210 device performs groups of writes and groups of reads separated by 4 inactive PCLK periods

for modes 3, 4 and 5. In mode 1 and mode 2, the write and read groups are separated by 8 PCLK periods.

RD RD

WR

WR

Figure 8 - Parallel Port Functional Read/Write Operation

JTAG Support

Test Access Port (TAP)

The Test Access Port (TAP) provides access to many

The MT90210 JTAG interface is designed according

to the Boundary-Scan standard IEEE1149.1. The

standard specifies a design-for-testability technique

called Boundary-Scan Test (BST). A boundary-scan

IC has a shift-register stage or ‘Boundary-Scan Cell’

(BSC) in between the core logic and the I/O buffers

adjacent to each I/O pin. The BSCs can control and

observe what happens at each I/O pin of the IC. The

operation of the boundary-scan circuitry is controlled

test support functions built into the MT90210. It

consists of three input connections and one output

connection. The following connections form the TAP:

• Test Clock Input (TCK)

• Test Mode Select Input (TMS)

• Test Data Input (TDI)

• Test port Reset (TRST)

• Test Data Output (TDO)

by a Test Access Port (TAP) Controller.

2-153

Loading...

Loading...