MITEL MT89790BN, MT89790BS, MT89790B Datasheet

4-187

Features

• Complete pri mary ra te 20 48 kbit/s CEPT

transceiver with CRC-4 option

• Selectable HDB3 or AMI line code

• Two frame elastic buffer with 32µs j itter buffer

• Tx and Rx fr ame an d mult ifram e

synchroniza-tion signals

• Frame alignm ent and CRC error coun ters

• Insertion and dete ction of A, B, C, D sign alling

bits with opt iona l debo unce

• Line drive r and rec eive r

• Per channel , overa ll, and re mote l oop aro und

• Digital ph ase det ecto r betw een E 1 line and

ST-BUS

• ST-BUS compatible

• Pin compatible with the MH89790

• Inductorless clock recovery

• Loss of Sign al (LO S) indi cation

• Available in standard, narrow and surface

mount form ats

• Supports si ngle su pply ra il ope ratio n

Applications

• Primary rate ISDN netw ork node s

• Multiplexing equipment

• Private network: PBX to PBX links

Description

The MH89790B is Mitel’s CEPT PCM 30 interface

solution, designed to meet the latest CCITT

standards PCM 30 format with CRC-4. The

MH89790B provides a complete interface between a

2.048 Mbit/sec digital trunk and Mitel’s Serial

Telecom Bus, the ST-BUS.

The MH89790B is a pin-compatible enhancement of

the MH89790, permitting the removal of the tuneable

inductor and inclusion of the external NAND gate

used for generating RxD.

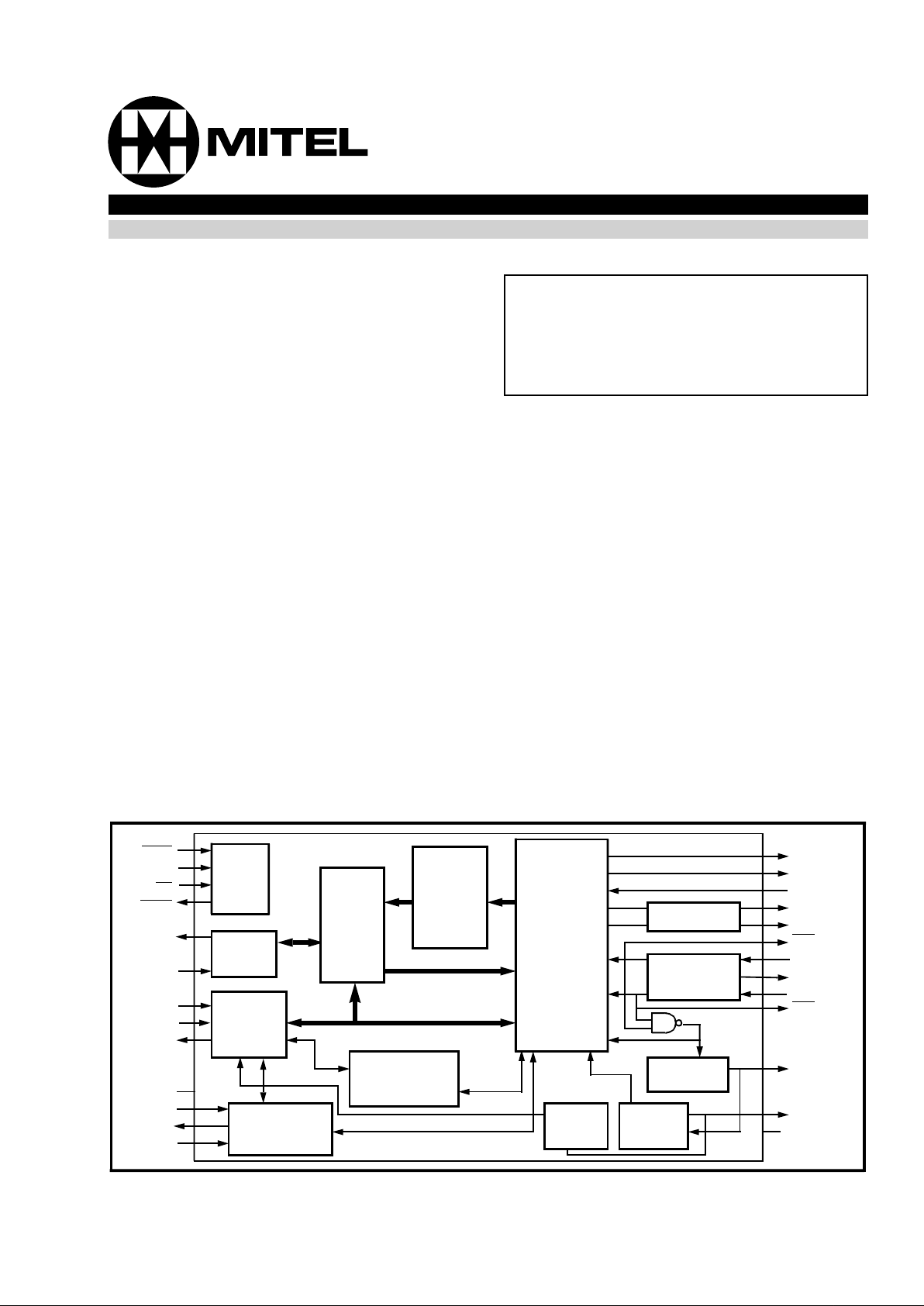

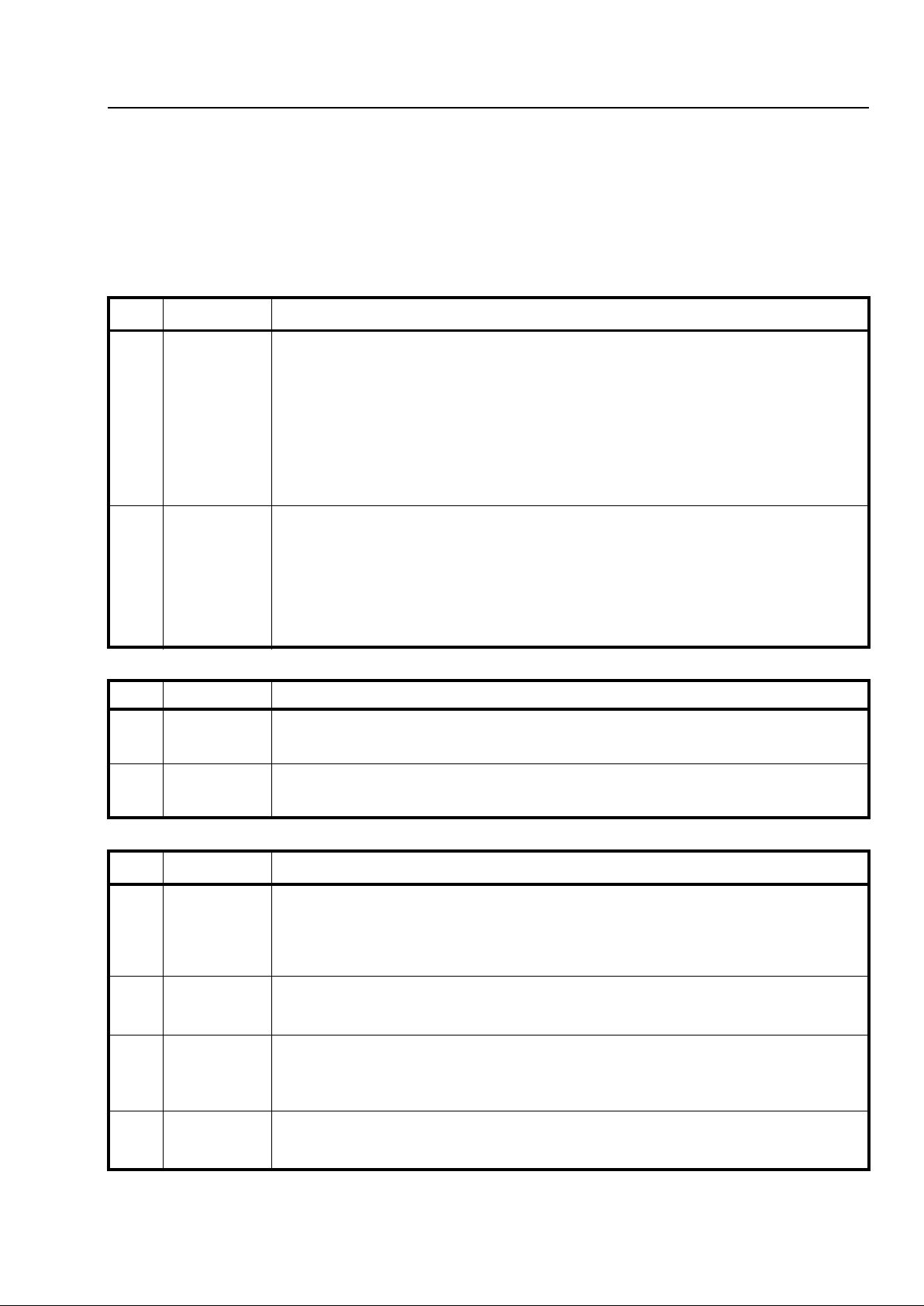

Figure 1 - Functional Block Diagram

TxMF

C2i

F0i

RxMF

DSTo

DSTi

CSTi0

CSTi1

CSTo

VDD

ADl

XCtl

XSt

PADi

TxG

PADo

OUTA

OUTB

RxA

RxT

LOS

RxR

RxB

E2o

E8Ko

VSS

ST-BUS

Timing

Cicuitry

Data

Interface

Control

Logic

Digital

Attenu-

ator

ROM

2 Frame

Elastic

Buffer

with Slip

Control

ABCD

Signalling RAM

CEPT

Link

Interfac e

Phase

Detector

CEPT

Counter

Clock

Extractor

Receiver

Tran smitter

Serial

Interface

Control

•

•

•

•

•

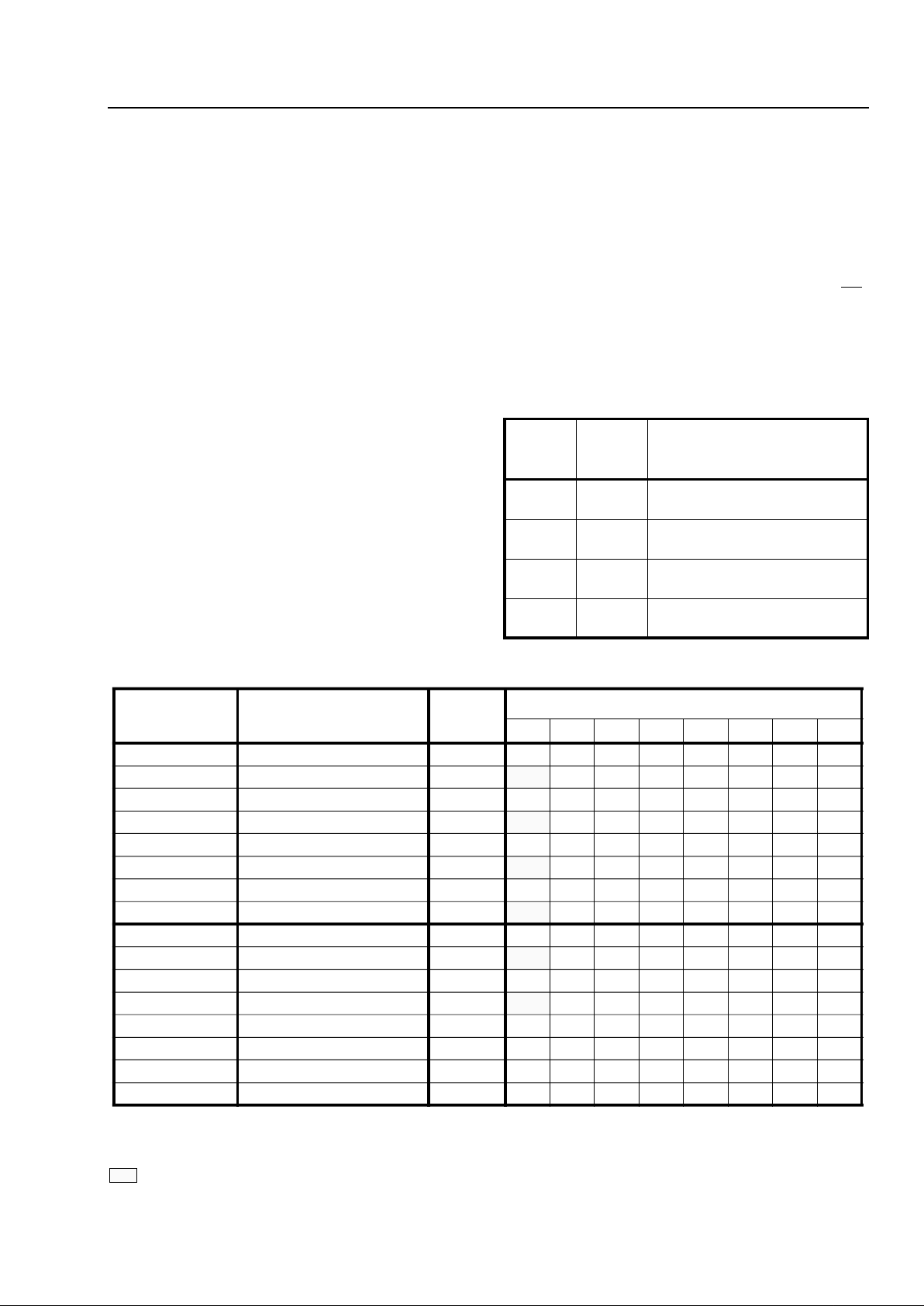

Ordering Information

MH89790B 40 Pin DIL Hybrid 1.3” row pitch

MH89790BN 40 Pin DIL Hybrid 0.8“ row pitch

MH89790BS 40 Pin Surface Mount Hybrid

0°C to 70°C

ISSUE 5 May 1995

MH89790B

CEPT PCM 30/CRC-4 Framer & Interface

ST-BUS FAMILY

Preliminary Info rmat ion

4-188

MH89790B Preliminary Information

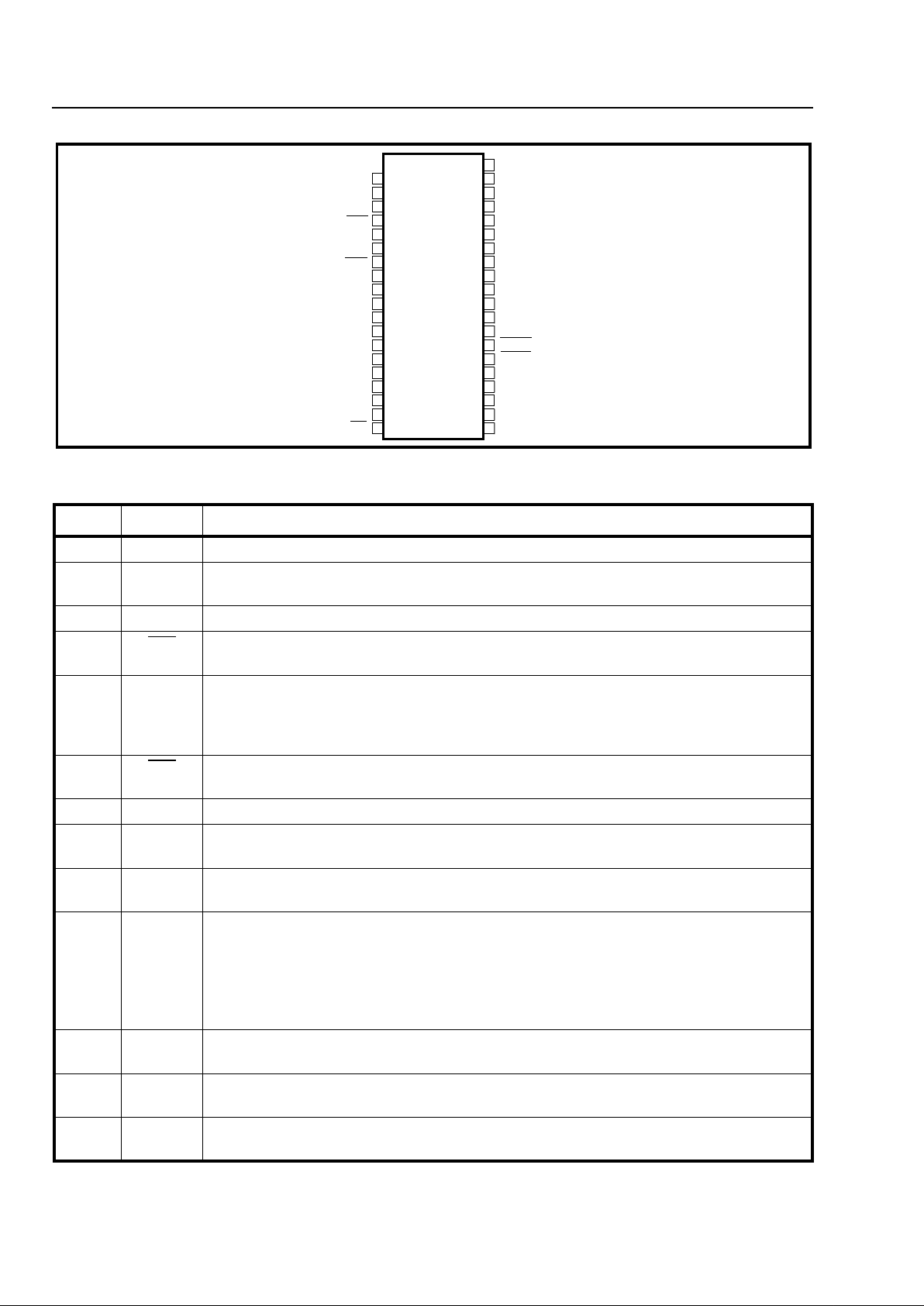

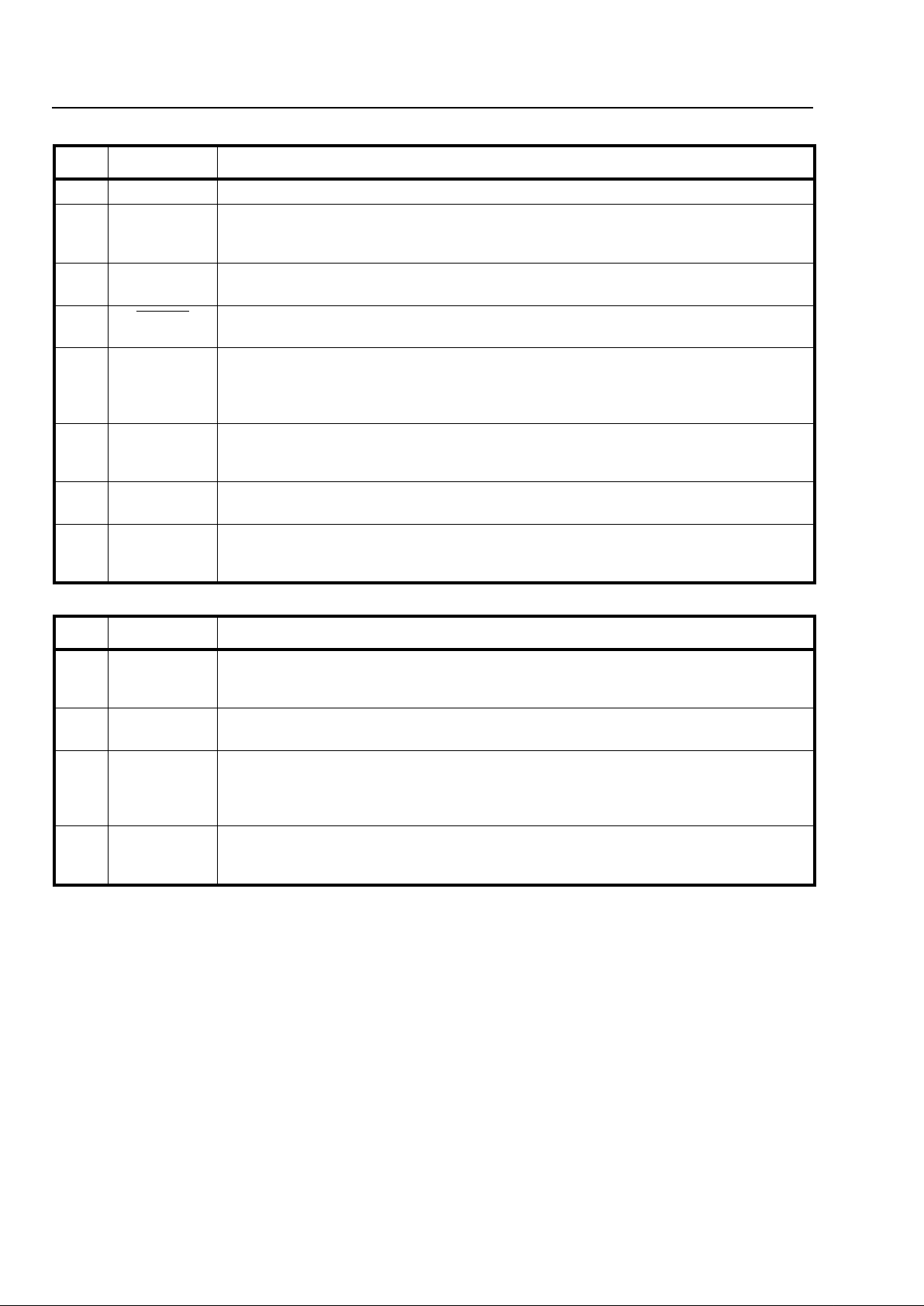

Figure 2 - Pin Connections

Pin Description

Pin # Name Description

2ICInternal Connection . Leave open circuit.

3E2o2048 kHz Extracted Clock (Output): T his clock is extracted by the device from the

received signal. It is used internally to clock in data received at RxT and RxR.

4V

DD

D.C. Power Inp ut. (+5V ).

5RxA

Receive A (Output): The bipolar CEPT signal received by the device at the RxR and

RxT inputs is converted to a unipolar format and output at this pin.

6

7

RxT

RxR

Receive Tip and Receive Ring Inpu ts. The AMI receive signal is input to these pins.

Both inputs should be connected to a center-tapped , center-grounded tran sform er.If the

receive side of the device is not used, these pins must be tied to ground through 1kΩ

resistors.

8RxB

Receive B (Output): The bipolar CEPT signal received by the device at the RxR and

RxT inputs is converted to a unipolar format and output at this pin.

9NCNo Connection.

10 CSTi1 Control ST-BUS Input #1: A 2048 kbit/s stream that contains channel associated

signalling, frame alignment and diagno stic fun ction s.

11 CSTi0 Control ST-BUS Input #0: A 2048 kbit/s stream that contains 30 per channel control

words and two Master Control Words.

12 E8Ko 8 kHz Ex tracted Clock (Output): An 8 kHz output generat ed by dividing the extracted

2048 kHz clock by 256 and aligning it with the received CEPT frame. The 8 kHz signal

can be used for synchronizing the system clock to the extracted 2048 kHz clock. Only

valid when device achieves synchronization (g oes low d uri ng a los s of s ignal or a loss

of basic frame synchronization condition).

E8Ko goes to high impedance when 8kHzSEL = 0 in MCW2.

13 XCtl External Control (Output): An uncommitted external output pin which is set or reset via

bit 1 in Master Control Word 2 on CSTi0. The state of XCtl is updated once per frame.

14 XSt External Statu s: The state of this pin is sampl ed once per frame and the status is

reported in bit 1 of the Master Status Word 1 on CSTo.

15 CS To Control ST -BUS Output: A 2048 kbit/s serial control stream which provides the 16

signalling words, two Master Status Words, Pha se Status Word and CRC Error Count.

IC

E2o

VDD

RxA

RxT

RxR

RxB

NC

CSTi1

CSTi0

E8Ko

XCtl

XSt

CSTo

NC

LOS

NC

NC

NC

NC

VSS

NC

DSTo

NC

OUTB

NC

RxMF

ADl

DSTi

C2i

E2o

F0i

NC

TxMF

OUTA

PADo

TxG

PADi

VSS

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

4-189

Preliminary Information MH89790B

16 ADI Alternate Digit Inversion (Input): If this input is high, the CEPT timeslots which are

specified on CSTi0 as voice channels are ADI coded and decoded. When this bit is low

it disables ADI coding for all channels. This feature allows either ADI or non-ADI codecs

to be used on DSTi and DSTo. Internally pulled with a 4.7kΩ resistor to +V

DD

.

17 DSTi Data ST-BUS Input: This pin accepts a 2048 kbit/s serial stream which contain s the 30

PCM or data channels to be transmitted on t he CEPT trunk.

18 C2i 2048 kbit/s System Clock (In pu t): The master clock for the S T-BUS section of the

chip. All data on the ST-BUS is clocked in on the falling edge of the C2i and output on the

rising edge. The falling edge of C2i is also used to clock out data on the CEPT PCM 30

transmit link.

19 E2o 2048 kHz Extracted Clock (Output): Internally connected to pin 3.

20 F0i

Frame Pulse Input: The ST-BUS frame synchronization signal which defines the

beginning of the 32 channel frame.

21 V

SS

Ground. D.C. Power Return.

22 PA Di PAD Input: Input to the symmetrical resistive 75 ohm T-type line matching circuit. In a

typical application connect this input to the output of the line driving transforme r.

23 TxG Transmit Ground: Common point of the T-type PAD circuit. Connect to GND in a typical

application.

24 PADo PAD Output: Output from the T-type PAD circuit. Output impedance of the PAD is pure

resistive 75Ω.

25 OUTA Output A (Open Collector Output): This is the output of the CEPT transmitter. It is

suitable for use with an external pulse transform er to generate the transmit bipolar line

signal.

26 TxMF

Transmit Multiframe Bou nda ry (Inp ut): This input can be used to set the channel

associated and CRC transmitted multifram e boundary (clear the frame count ers). If a

transmit multiframe signal is not being generated externally to the device, the MH89790B

will internally generate its own mul tifram e when this pin is tie d high.

27 RxMF

Received Multiframe Boundary (Output): An output pulse delim iting the received

multiframe boundary. (This multiframe is not related to the received CRC multiframe. )

28 NC No Connection.

29 OUTB Output B (Open Collector Output): Output of the CEPT transmi tte r. I t is suitable fo r

use with an external pulse tran sfor m er to generate the tra nsmit bipolar line si gnal.

30 NC No Connection.

31 DS To Data ST-BUS Output: A 2048 kbit/s serial output stream which contains the 30 PCM or

data channels received from the CEPT line.

32 NC No Connection.

33 V

SS

Ground. D.C. Power Return.

34 - 37 NC No Connection.

38 LOS Loss of Signal (Output): This pin goes High when 128 contiguous ZEROs are received

on the RxT and RxR inputs. When LOS is High, RxA

and RxB are forced High. LOS is

reset when 64 ONEs are received in a two E1-frame period.

39 - 40 NC No Connection.

Pin Description (Continued)

Pin # Name Description

4-190

MH89790B Preliminary Information

Functional Description

The MH89790B is a digital trunk interface

conforming to CCITT Recommendation G.704 for

PCM 30 and I.431 for ISDN. It includes features

such as insertion and detection of synchronization

patterns, optional cyclical redundancy check

(CRC-4) and far end error performance reporting,

HDB3 decoding and optional coding, channel

associated or common channel signalling,

programmable digital attenuation, and a two frame

received elastic buffer. The MH89790B can also

monitor several conditions on the CEPT digital trunk

which include the following: Loss of Signal (LOS)

indication, frame and multiframe synchronization,

received all 1’s alarms, data slips, as well as near

and far end framing and CRC errors.

The system interface to the MH89790B is a serial

bus that operates at 2048 kbit/s known as the

ST-BUS. This serial stream is divided into 125 µs

frames that are made up of 32 x 8 bit channels.

The line interface to the MH89790B consists of split

phase unipolar inputs and outputs which are

supplied from/to a bipolar line receiver/driver,

respectively.

CEPT Interface

The CEPT frame format consists of 32, 8 bit

timeslots. Of the 32 timeslots in a frame, 30 are

defined as information channels, timeslots 1-15 and

17-31 which correspond to telephone channels 1-30.

An additional data channel may be obtained by

placing the device in common channel signalling

mode. This allows use of timeslot 16 for 64 kbit/s

common channel signalling. Synchronization is

included within the CEPT bit stream in the form of a

bit pattern inserted i n to tim e s lot 0. The c o nt ents of

timeslot 0 alternate between the frame alignment

pattern and the non-frame alignment pattern as

described in Figure 3 below. Bit 1 of the frame

alignment and non-frame alignment bytes have

provisions for additional protection against false

synchronization or enhanced error monitoring. This

is described in more detail in the following section.

In order to accomplish multiframe synchronization, a

16 frame multiframe is defined by sending four zeros

in the high order quartet of timeslot 16 frame 0, i.e.,

once every 16 frames (see Figure 4). The CEPT

format has four signalling bits, A, B, C and D.

Signalling bits for all 30 information channels are

transmitted in timeslot 16 of frames 1 to 15. These

timeslots are subdivided into two quartets (see Table

6).

Cyclic Redundancy Check (CRC)

An optional cyclic redundancy check (CRC) has

been incorporated within CEPT bit stream to provide

additional protection against simulation of the frame

alignment signal, and/or where there is a need for an

enhanced error monitoring capability. The CRC

process treats the binary string of ones and zeros

contained in a submultiframe (with CRC bits set to

binary zero) as a single long binary number. This

string of data is first multiplied by x

4

then divided by

the polynomial x

4

+x+1. This process takes place at

both the transmitter and receiver end of the link. The

remainder calculated at the receiver is compared to

the one received with the data over the link. If they

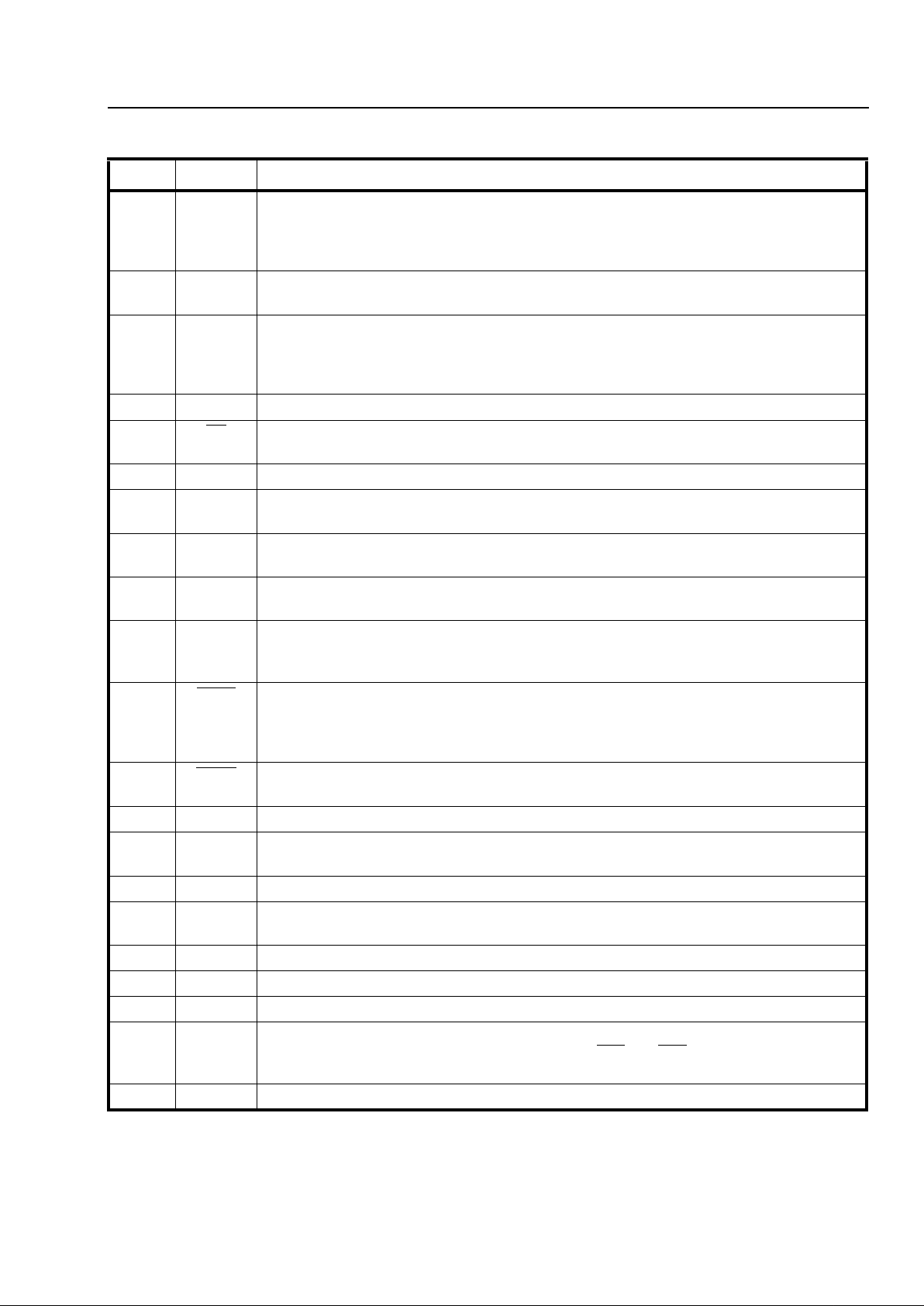

Figure 3 - Allocation of Bits in Timeslot 0 of the CEPT Link

Note 1 : With CRC active, this bit is ignored.

Note 2 : With SiMUX active, this bit transmits SMF CRC re sults in frames 13 and 15.

Note 3 : Reserved for National use.

.

Figure 4 - Allocation of Bits in Timeslot 16 of the CEPT Link

Bit Number

1 2 3 45678

Timeslot 0 containing the

frame alignment signal

Reserved for

International

use

(1)

0 0 11011

Timeslot 0 containing the

non-frame alignment signal

Reserved for

International

use

(2)

1 Alarm indication to the

remote PCM multiplex

equipment

See

Note

#3

See

Note

#3

See

Note

#3

See

Note

#3

See

Note

#3

Timeslot 16 of frame 0 Timeslot 16 of frame 1

• • •

Timeslot 16 of frame 15

0000 XYXX

ABCD bits for

telephone

channel 1

(timeslot 1)

ABCD bits for

telephone

channel 16

(timeslot 17)

ABCD bits for

telephone

channel 15

(timeslot 15)

ABCD bits for

telephone

channel 30

(timeslot 31)

4-191

Preliminary Information MH89790B

are the same, it is of high probability that the

previous submultiframe was received error free.

The CRC procedure is based on a 16 frame

multiframe which is divided into two 8 frame

submultiframes (SMF). The frames which contain

the frame alignment pattern contain the CRC bits, C

1

to C4, respectively, in the bit 1 position. The frame

which contains the non-frame alignment pattern

contains within the bit 1 position, a 6 bit CRC

multiframe alignment signal and two spare bits (in

frames 13 and 15) which are used for CRC error

performance reporting (refer to Figure 5). During the

CRC encoding procedure the CRC bit positions are

initially set at zero. The rem ainder of the calculation

is stored and inserted into the respective CRC bits of

the next SMF. The decoding process repeats the

multiplication/division process and compares the

remainder with the CRC bits received in the next

SMF.

The two spare bits (denoted Si1 and Si2 in Figure 5)

following the 6-bit CRC mu ltiframe alignment signal

can be used to monitor far-end error performance.

The results of the CRC-4 comparisons for the

previously received SMFII and SMFI are encoded

and transmitted back to the far end in the Si bits

(refer to Table 1).

ST-BUS Interface

The ST-BUS is a synchronous time division

multiplexed serial bus with data streams operating at

2048 kbit/s and configured as 32, 64 k bit/s channels

(refer Figure 6). Synchronization of the data transfer

is provided from a frame pulse which identifies the

frame boundaries and repeats at an 8 kHz rate.

Figure 2 shows how the frame pulse (F0i

)

defines the ST-BUS frame boundaries. All data is

clocked into the device on the falling edge of the

2048 kbit/s clock (C2i), while data is clocked out on

the rising edge of the 2048 kbit/s clock at the start of

the bit cell.

Table 1. Coding of Spar e Bits Si1 and Si 2

Si1 bit

(frame

13)

Si2 bit

(frame

15)

Meaning

11

CRC results for both SMFI, II a re

error free.

10

CRC result for SMFII is in error.

CRC result for SMFI is error free.

01

CRC result for S MFII is erro r fre e.

CRC result for SMFI is in error.

00

CRC results for both SMFI, II a re

in error.

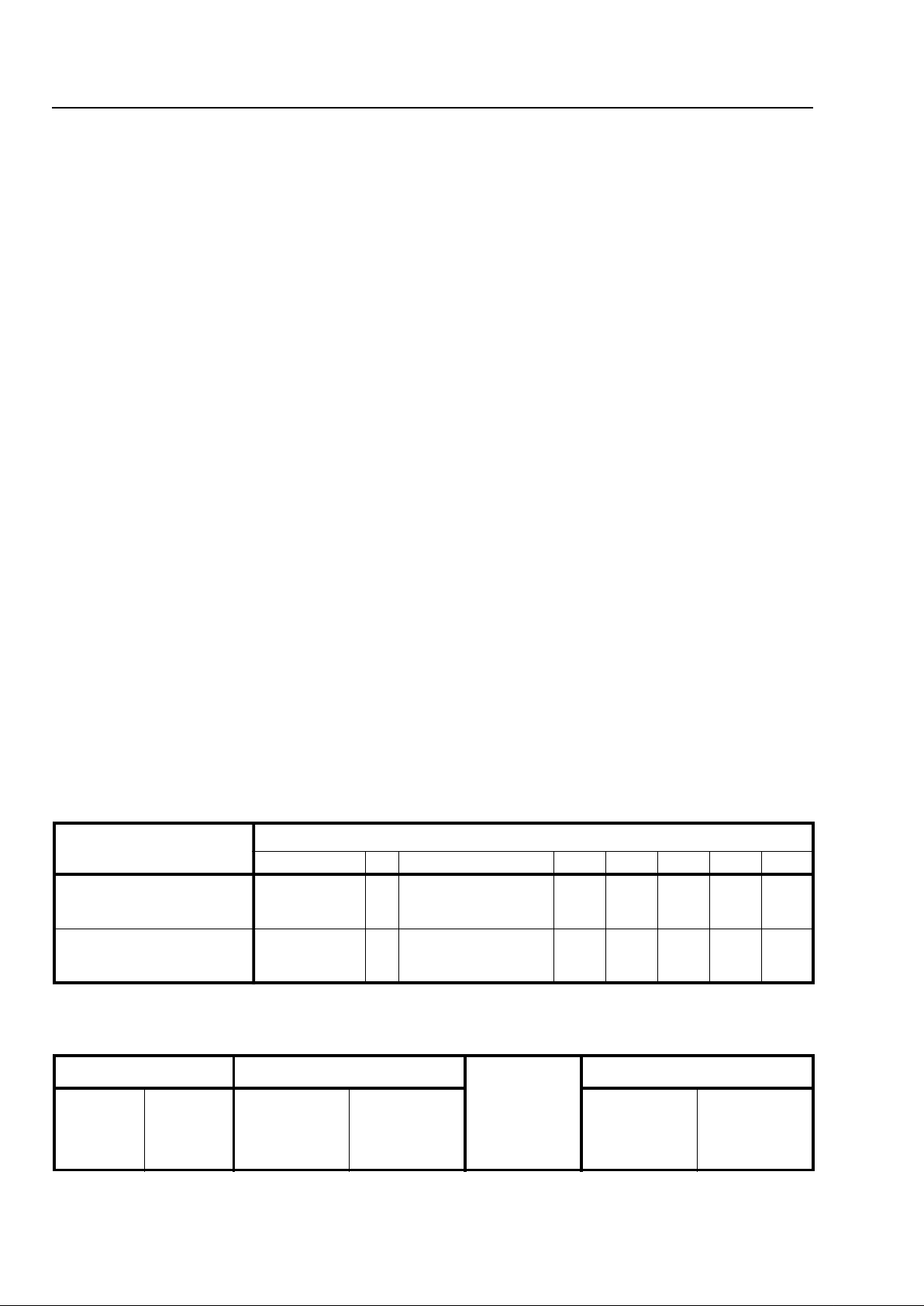

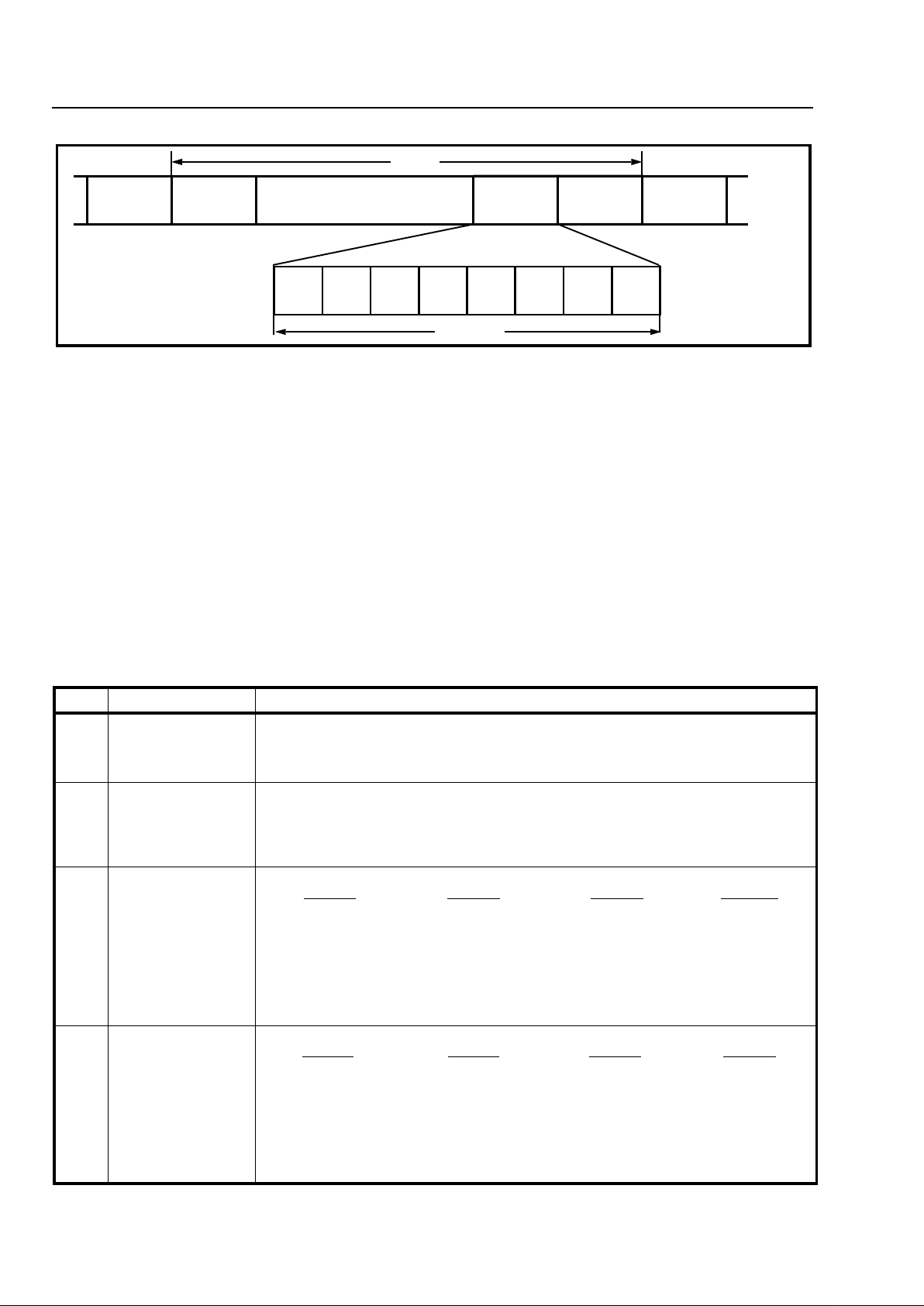

Figure 5 - CRC Bit Allocation and Submultiframing

Note 1 : Remote Alarm. Keep at 0 for normal operation.

Note 2 : Reser ved for Nati onal use. Keep at 1 for norma l opera tion .

Note 3 : Used to monitor far-e nd CRC e rro r performan ce.

Multiple Fr am e

Componen t

Frame Type

CRC

Frame #

Timeslot Ze ro

12345678

Frame Alignment Signal 0 C

1

0011011

Non-Frame Alignment Signal 1

01A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

S Frame Alignment Signal 2 C

2

0011011

M Non-Frame Alignment Signal 3

01A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

F Frame Alignment Signal 4 C

3

0011011

Non-Frame Alignment Signal 5

11A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

I Frame Alignment Signal 6 C

4

0011011

Non-Frame Alignment Signal 7

01A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Frame Alignment Signal 8 C

1

0011011

S Non-Fr ame Alignment Signal 9

11A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

M Frame Alignment Signal 10 C

2

0011011

F Non-Frame Alignment Signal 11

11A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Frame Alignment Signal 12 C

3

0011011

I Non-Frame Alignment Signal 13 Si1

(3)

1A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

I Frame Alignment Signal 14 C

4

0011011

Non-Frame Alignment Signal 15 Si2

(3)

1A

(1)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

Sn

(2)

indicates position of CRC-4 multiframe alignment signal

4-192

MH89790B Preliminary Information

Figure 6 - ST-BUS Stream Form at

CHANNEL

31

030

BIT

CHANNEL

CHANNEL

CHANNEL

CHANNEL

31 0

BIT BIT

BIT

BIT BIT BIT

BIT

• • •

Least

Significant

Bit (Last)

Most

Significant

Bit (First)

(8/2.048 )µ s

125µs

7654321

0

Data Input (DSTi)

The MH89790B receives information channels on

the DSTi pin. Of the 32 available channels on this

serial input, 30 are defined as information channels.

They are channels 1-15 and 17-31. These 30

timeslots are the 30 telephone channels of the CEPT

format numbered 1-15 and 16-30.

Timeslot 0 and 16 are unused to allow the

synchronization and signalling information to be

inserted, from the Control Streams (CSTi0 and

CSTi1). The relationship between the input and

output ST-BUS stream and the CEPT line is

illustrated in Figures 7 to 11. In common channel

signalling mode timeslot 16 becomes an active

channel. In this mode channel 16 on DSTi is

transmitted on timeslot 16 of the CEPT link

unaltered. This mode is activated by bit 5 of channel

31 of CSTi0.

Control Input 0 (CSTi0)

All the necessary control and signalling information

is input through the two control streams. Control

ST-B US input number 0 (CSTi0) contains the control

informat ion th at is asso ciated wit h each inform ation

channel. Each control channel contains the per

channel digital attenuation information, the individual

Table 2. Per Chan nel Co ntro l Word: Data Form at for CSTi0 Cha nnels 0-14, an d 16-3 0

BIT NAME DESCRIPTION

7 DATA Data Channel: If ‘1‘, then the controlled timeslot on the CEPT 2048 kbit/s link is treated as a

data channel; i .e., no ADI encoding or decoding is performed on transmission or r e ception,

and digital attenuation is disabled. If ‘0‘, then the state of the ADI pin determines whether or

not ADI encoding and decoding is performed.

6 LOOP Per-Channel Loopback: If ‘1‘, then the controlled timeslot on the transmitted CEPT 2048

kbit/s link is looped internally to replace the data on the corresponding received ti me slot. If

‘0‘, then this function is disabled. This function only operates if frame synchronization is

received from the CEPT link. If more than one channel is looped per frame only the first one

will be ac t i v e.

5,4,3 RX PAD4,2,1 Receive Attenuation Pad: Per timeslot receive attenuation control bits.

RXPAD4

0

0

0

0

1

1

1

1

RXPAD2

0

0

1

1

0

0

1

1

RXPAD1

0

1

0

1

0

1

0

1

Gain (dB)

0

-1

-2

-3

-4

-5

-6

1

2,1,0 TXPAD4,2,1 Transmit Attenuation Pad: Per timeslot transmit attenuation control bits.

TXPAD4

0

0

0

0

1

1

1

1

TXPAD2

0

0

1

1

0

0

1

1

TXPAD1

0

0

1

0

1

0

1

0

Gain (dB

)

0

-1

-2

-3

-4

-5

-6

1

4-193

Preliminary Information MH89790B

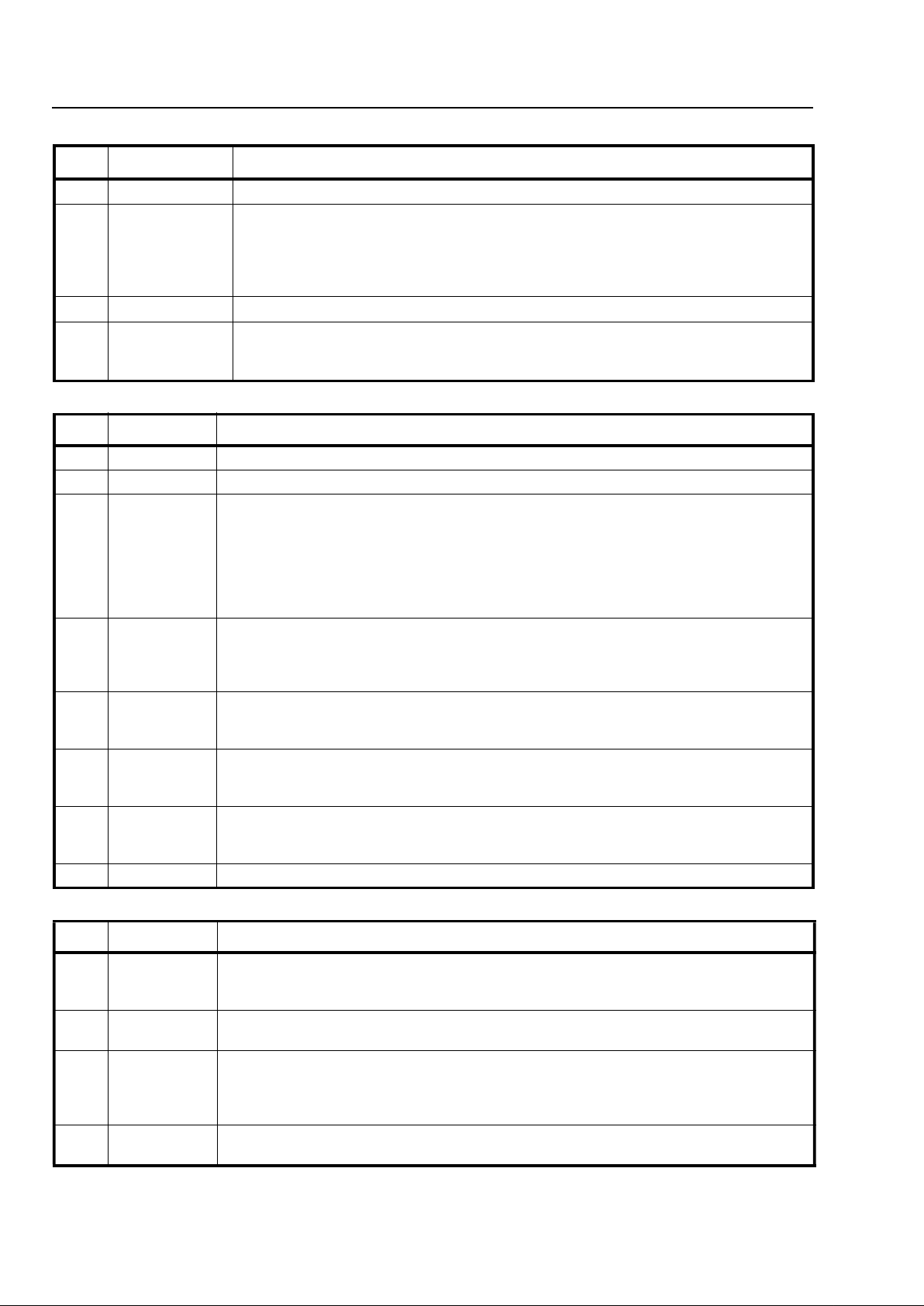

Figure 7 - Relationship between Input DSTi Channels and Transmitted CEPT Timeslots

Figure 8 - Relationship between Received CEPT Timeslots and Output DSTo Channels

Figure 9 - Relationship between Input CSTi0 Channels and Controlled CEPT Timeslots

Figure 10 - Relationship between Input CSTi1 Channels and Transmitted CEPT Frames

Figure 11- Relationship between Received CEPT Frames and Output CSTo Channels

- *Denotes Unused Channel (CSTo output is not put in high impedance state) -CCS Denotes Signa lling Chan ne l i f C o m mo n C ha nn el S i gn al lin g Mode Sele c ted

- A Denotes Frame-Alignment Frame -S1 Denotes Master Status Word 1 (MSW1)

- N Denotes Non Frame-Alignment Frame -S2 Denotes Ph as e Sta tus W o rd (PSW)

- C1, C2, C3 Deno te s Ma s ter C on trol Words 1 ,2 ,3 -S3 Denotes CRC Error Count

- SIG Denotes Signalling C h an ne l -S4 Denotes Master Status Word 2 (MSW2)

DSTi

Channel #

0 1 2 3 4 5 6 7 8 9 10111213141516171819202122232425262728293031

CEPT

Timeslot #

1 2 3 4 5 6 7 8 9 101112131415

CCS

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

DSTi

Channel #

0 1 2 3 4 5 6 7 8 9 10111213141516171819202122232425262728293031

CEPT

Timeslot #

0123456789101112131415

SIG

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

CSTi0

Channel #

012345678910111213141516171819202122232425262728293031

Device Control C1 C2

CEPT Channel #

Control Word

123456789101112131415 171819202122232425262728293031

CSTi1

Channel #

0 1 2 3 4 5 6 7 8 9 10111213141516171819202122232425262728293031

Device Control C3*************

CEPT

FRAME #

CHANNEL #

0

16

1

16

2

16

3

16

4

16

5

16

6

16

7

16

8

16

9

16

10

16

11

16

12

16

13

16

14

16

15

16

A

0

N

0

CSTo

Channel #

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Device Status S1S2S3S4**********

CEPT

FRAME #

TIMESLOT #

0

16

1

16

2

16

3

16

4

16

5

16

6

16

7

16

8

16

9

16

10

16

11

16

12

16

13

16

14

16

15

16

A

0

N

0

4-194

MH89790B Preliminary Information

Table 3. Mast er C ontrol Wor d 1 (M CW1): Dat a Form at for C STi0 Chan nel 15

Table 4. Master Contr ol Word 2 (M CW2): D ata Forma t for CSTi0 Ch ann el 31

Table 5. Multifra me Alignm ent Sign al:D ata Forma t for CSTi1Ch annel 0 on the Transmitted CEPT Link

BIT NAME DESCRIPTION

7 (N/A) Keep at ‘1‘ for normal operation.

6 LOOP16 Channel 16 Loopback: If ‘1‘, then timeslot 16 on the transmitted CEPT 2048 kbit/s link is

looped internally to replace the data received on timeslot 16. If ‘0,‘ then this function is

disabled.

This function only operates if frame synchronization is received from the CEPT link and only a

single timeslot can be looped within the frame.

5,4 (N/A) Keep at ‘1‘ for normal operation.

3,2,

1

& 0

NDBD, NDBC,

NDBB

& NDBA

Signalling Bit Debounce: If ‘1‘, then no debouncing is applied to the received A, B, C or D

signalling bits. If ‘0‘, then the received A, B, C or D signalling bits are debounced for between

6 and 8 ms.

BIT NAME DESCRIPTION

7 (N/A) Keep at ‘1‘ for normal operation.

6 (N/A) Keep at ‘0‘ for normal operation.

5 CCS Common Channel Signalling: If 1, then the MH89790B operates in its common channel

signalling mode. Channel 16 on the DSTi pin is transmitted on timeslot 16 of the CEPT link, and

timeslot 16 from the received CEPT link is output on channel 16 on the DSTo pin. Channel 15 on

the CSTi0 pin contains the information for the control of timeslot 16. Channels 0 to 15 on CSTi 1

and CSTo are unused.

If ‘0‘, the device is in channel associated signalling mode where channel 16 is used to transmit

the ABCD signalling bits.

4 8kHzSEL 8kHz Select: If ‘1‘, then an 8 kHz signal synchronized to the received CEPT 2048 kbit/s link is

output on the E8Ko pin. This feature is only valid when frame synchronization is received from

the CEPT link.

If ‘0‘, then the E8Ko pin goes into its high impedance state.

3 TXAIS Transmit Alarm Indication Signal:

If ‘1‘, then an all 1’ s alarm signal is transmitted on all timeslots.

If ‘0‘, then the timeslots functions normally.

2 TXTS16AIS Transmit Timeslot 16 Alarm Indication Signal:

If ‘1‘, then an all 1’s alarm signal is transmitted on timeslot 16.

If ‘0‘, then timeslot 16 functions normally.

1 XCtl External Control:

If ‘1‘, then the XCtl pin is driven high.

If ‘0‘, then the XCtl pin is driven low.

0 (N/A) (unused)

BIT NAME DESCRIPTION

7-4 MA1-4 Transmit Multiframe Alignment Bits 1 to 4: These bits are transmitted on the CEPT 2 048

kbit/s link in bit positions 1 to 4 of timeslot 16 of frame 0 of the multiframe. They should be kept at

‘0‘ to allow multiframe alignment to be detected.

3X1This bit is transmitted on the CEPT 2048 kbit/s link in bit position 5 of timeslot 16 of frame 0 of the

multiframe. It is a spare bit which should be kept at ‘1‘ if unused.

2YThis bit is transmitted on the CEPT 2048 kbit/s link in bit position 6 of timeslot 16 of frame 0 of the

multiframe. It is used to indicate the loss of multiframe alignment to the remote end of the link. A

‘1‘ on this bit is the signal that multiframe alignment on the received link has been lost. A ‘0’

indicates that multiframe alignment is detected.

1,0 X2,X3 These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 7 and 8 respectively, of

timeslot 16 of frame 0 of the multiframe. They are spare bits which should be kept at ‘1‘ if unused.

4-195

Preliminary Information MH89790B

loopback control bit, and the voice or data channel

identifier, see Table 2. When a channel is in data

mode (B7 is high) the digital attenuation and

Alternate Digit Inversion are disabled. It should be

noted that the control word for a given information

channel is input one timeslot early, i.e., channel 0 of

CSTi0 controls channel 1 of DSTi. Channels 15 and

31 of CSTi0 contain Master Control Words 1 and 2

(MCW1, MCW2) which are used to set up the

interface feature as seen by the respective bit

functions of Tables 3 and 4.

Table 6. Channel Associated Signalling: Data Format for CSTi1 Channels 1 to 15

Table 7. Frame-Alignment Signal: Data Format for CSTi1 Channel 16

Table 8. Non-Frame-Alignment Signal: Data Format for CSTi1 Channel 17

BIT NAME DESCRIPTION

7,

6,

5

& 4

A(N),

B(N),

C(N)

& D(N)

Transmit Signalling Bits for Channel N: These bits are transmitted on the CEPT 2048 kbit/s

link in bit positions 1 to 4 of timeslot 16 in frame N, and are the A, B, C and D signalling bits

associated with telephone channel N. The value of N lies in the range 1 to 15 and refers to the

channel on the CSTi1 channel from which the bits are sourced, the telephone channel with which

the bits are associated and the frame on the CEPT link on which the bits are transmitted. For

example, the bits input on the CSTi1 pin on channel 3 are associated with telephone channel 3,

which is timeslot 3 of the CEPT link, and are transmitted on bits positions 1 to 4 of timeslot 16 in

frame 3 of each multiframe on the CEPT link . If bits B, C or D are not used they should be given

the values ‘1, 0‘ and ‘1‘ respectively. The combination ‘0000‘ for ABCD bits should not be used f or

telephone channels 1 to 15 as this would interfere with multiframe alignment.

3,

2,

1

& 0

A(N+15),

B(N+15),

C(N+15)

& D(N+15)

Transmit Signalling Bits for Channel N+15: These bits are transmitted on the CEPT 2048

kbit/s link in bit positions 5 to 8 of timeslot 16 in frame N, and are the A, B, C and D signalling bits

associated with telephone channel N+15. The value of N lies in the range 1 to 15 and refers to

both the channel on the CSTi1 stream where the bits are supplied and the frame on the CEPT

link on which the bits are transmitte d, and indirectly indicates the telephone channel with which

the bits are are associated. For example, the bits input on the CSTi1 pin on channel 3 are

associated with telephone channel 18, which is timeslot 19 of the CEPT link, and are transmitted

in bits positions 5 to 8 of timeslot 16 in frame 3 of each multiframe on the CEPT link .

BIT NAME DESCRIPTION

7 IU0 International U se 0: When CRC is disabled, this bit is transmitted on the CEPT 2048 kbit/s link

in bit position 1 of timeslot 0 of frame-alignment frames . It is reserved for international use and

should be kept at ‘1’ when not used. If CRC is enabled, this bit is not used.

6-0 FAF2-8 Transmit Frame Alignment Signal Bits 2 to 8: These bits are transmitted on the CEPT 2048

kbit/s link in bit positions 2 to 8 of timeslot 0 of frame-alignment frames. These bits form the

frame alignment signal and should be set to ‘00110 11‘.

BIT NAME DESCRIPTION

7 IU1 International U se 1: When the CRC is disabled and SiMUX bit in MCW3 is disabled, this bit is

transmitted on the CEPT 2048 kbit/s link in bit position 1 of timeslot 0 of non-frame-alignment

frames . It is reserved for international use and should be kept at ‘1‘ when not used. If CRC is

enabled and SiMUX is disabled, this bit is transmitted in bit 1 of timeslot 0 for frame 13 and 15. If

both CRC and SiMUX are enabled, then this bit is not used.

6 NFAF Transmit Non-Frame Alignment Bit: This bit is transmitted on the CEPT 2 048 kbit/s link in bit

position 2 of timeslot 0 of non-frame-alignment frames . In order to differentiate between

frame-alignment frames and non-frame-alignment frames, this bit should be kept at ‘1‘.

5 ALM Non-Frame Alignment Alarm: This bit is transmitted on the CEPT 2048 kbit/s link in bit position

3 of timeslot 0 of non-frame-alignment frames . It is used to signal an alarm to the remote end of

the CEPT link. The bit should be set to ‘1‘ to signal an alarm and should be kept at ‘0‘ under

normal operation.

4-0 NU1-5 National Use: These bits are transmitted on the CEPT 2048 kbit/s link in bit positions 4 to 8 of

timeslot 0 of non-frame-alignment frames . These bits are reserved for national use, and on

crossing international borders they should be set to ‘1‘.

4-196

MH89790B Preliminary Information

Table 9. Master Contr ol Word 3 (M CW3): D ata Forma t for CSTi1 Ch ann el 18

Table 10. Received Multiframe Alignment Signal: Data Format for CSTo Channel 0

BIT NAME DESCRIPTION

7N/AKeep at zero for normal operation.

6SiMUXWhen set to ‘1’, this bit will cause the SMFI CRC result to be transmit ted in the next outgoing Si1

bit in frame 13 and the SMFII CRC result to be transmitted in the next outgoing Si2 bit in frame

15.

5 RMLOOP Remote Loopback: If set the RxT and RxR signals are looped to OUTA and OUTB,

respectively.

4 HDB3en

Enable HDB3 Encoding: A ’1’ will disable the HDB3 line coding and transmit the information

transparently.

3 Maint Maintenance: A ’1’ will force a complete reframe if the CRC multiframe synchro- ni zat ion is not

achieved within 8 ms of frame synchronization. Reframe will also be generated if more than 914

CRC errors occur within a one second interval (CRC error counter is reset with every one second

interval). A ’0’ will disable this option.

2 CRCen Enable Cyclical Redundancy Check: A ’1’ will enable the CRC gener ation on the transmit

data. A ’0’ will disable the CRC generator. The CRC receiver is always active regardless of the

state of CRCen.

1 DGLOOP Digit al Loopack: When set, the transmitted signal is looped around from DSTi to DSTo. The

normal received data is interrupted.

0 ReFR Force Reframe: If set, for at least one frame, and then cleared the chip will begin to search for a

new frame position when the chip detects the change in state fr om high to low. Only the change

from high to low will cause a reframe, not a continuous low level.

BIT NAME DESCRIPTION

7-4 MA1-4 Receive Multiframe Alignment Bits 1 to 4: These are the bits which are received from the

CEPT 2048 kbit/s link in bit positions 1 to 4 of timeslot 16 of frame 0 of the multiframe. They

should all be ‘0‘.

3X1This is the bit which is received on the CEPT 2048 kbit/s link in bit position 5 of timeslot 16 of

frame 0 of the multiframe. It is a spare bit which should be ‘1‘ if unused . It is not debounced.

2YThis is the bit which is received on the CEPT 2048 kbit/s link in bit position 6 of timeslot 16 of

frame 0 of the multiframe. It is used to indicate the loss of multiframe alignment at the remote end

of the link. A ‘1‘ on this bit is the signal that multiframe alignment at the remote end of the link has

been lost. A ‘0‘ indicates that multiframe alignment is detected. It is not debounced.

1,0 X2,X3 These are the bits which are received on the CEPT 2048 kbit/s link in bit positions 7 and 8

respectively, of timeslot 16 of frame 0 of the multiframe. They are spare bits which should be ‘1‘ if

unused. They are not debounced.

Control Input 1 (CSTi1)

Control ST-BUS input stream number 1 (CSTi1)

contains the synchronization information and the A,

B, C & D signalling bits for insertion into timeslot 16

of the CEPT stre am (re fer to Tables 5 to 8 ). Timesl ot

0 contains the four zeros of the multiframe alignment

signal plus the XYXX bits (see Figure 4). Channels 1

to 15 of CSTi1 contain the A, B, C & D signalling bits

as defined by the CEPT format (see Figure 4), i.e.,

channel 1 of CSTi1 contains the A, B, C & D bits for

DSTi timeslots 1 and 17. Channel 16 contains the

frame alignment signal, and channel 17 contains the

non-frame alignment signal (see Figure 3). Channel

18 contains the Master Control Word 3 (see Table 9).

Figure 10 shows the relationship between the control

stream (CSTi1) and the CEPT stream.

Control Output (CSTo)

Control ST-BUS output (CSTo) contains the

multiframe signal from timeslot 16 of frame 0 (see

Table 10). Signalling bits, A, B, C & D for each CEPT

channel are sourced from timeslot 16 of frames 1-15

and are output in channels 1-15 on CSTo , as shown

in Table 11. The frame alignment signal and

non-frame alignment signal, received from timeslot

0 of alternate frames are output in timeslots 16 and

17, as shown in Tables 12 and 13.

Loading...

Loading...