MITEL MT8920BE, MT8920BC, MT8920BP, MT8920BS Datasheet

ISO-CMOS ST-BUS FAMILY

MT8920B

ST-BUS Parallel Access Circuit

Features

• High speed par allel acc ess to the se ria l

ST-BUS

• Parallel bus o ptimi zed for 68000 µP (m ode 1)

• Fast dual-port RAM ac cess (m ode 2)

Access time: 120 nsec

• Parallel bus c ontrol ler (m ode 3) - no exter nal

controller requ ired

• Flexible interru pt cap abilitie s - two

independen t/prog ram ma ble int errupt s ources

with auto-vectoring

• Selectab le 24 a nd 32 c hanne l oper atio n

• Programmable loop-a r ou nd modes

• Low power CM OS t echnol ogy

Applications

• Parallel cont rol/da ta acce ss t o T1/CE PT digi tal

trunk interfaces

• Digital signa l proces sor int erfac e to ST-BUS

• Computer to Digital PABX link

• Voice store and forward sys tems

• Interproce ssor co mm unicati ons

ISSUE 5 May 1995

Ordering Information

MT8920BE 28 Pin Plastic D IP

MT8920BC 28 Pin Ceram i c D IP

MT8920BP 28 Pin Plastic J-Lead

MT8920B S 28 Pin SOIC

-40°C to 85° C

Description

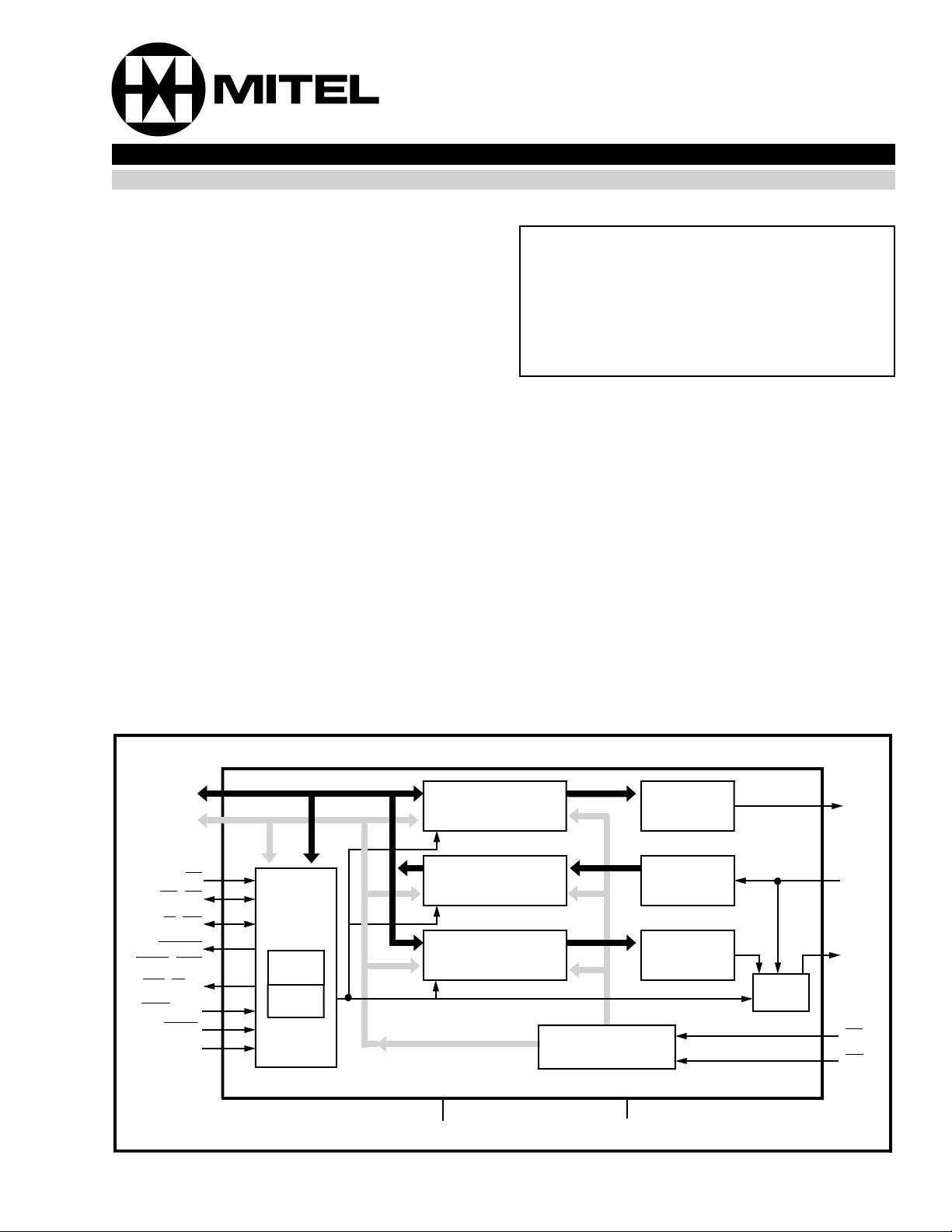

The ST-BUS Parallel Access Circuit (STPA) provides

a simple interface between Mitel’s ST-BUS and

parallel syst em environments.

D7-D0

A4-A0

CS

DS, OE

R/W, WE

DTACK,

BUSY, DCS

IRQ, 24/32

, MS1

IACK

A5, STCH

MMS

Parallel

Port

Interface

Interrupt

Registers

Control

Registers

Tx0

Dual Port Ram

32 X 8

Rx0

Dual Port Ram

32 X 8

Tx1

Dual Port Ram

32 X 8

Address

Generator

V

SS

V

DD

Figure 1 - Functional Block Diagram

Parallelto-serial

Converter

Serial-to-

Parallel

Converter

Parallelto-Serial

Converter

Comp/

MUX

STo0

STi0

STo1

F0i

C4i

3-3

3

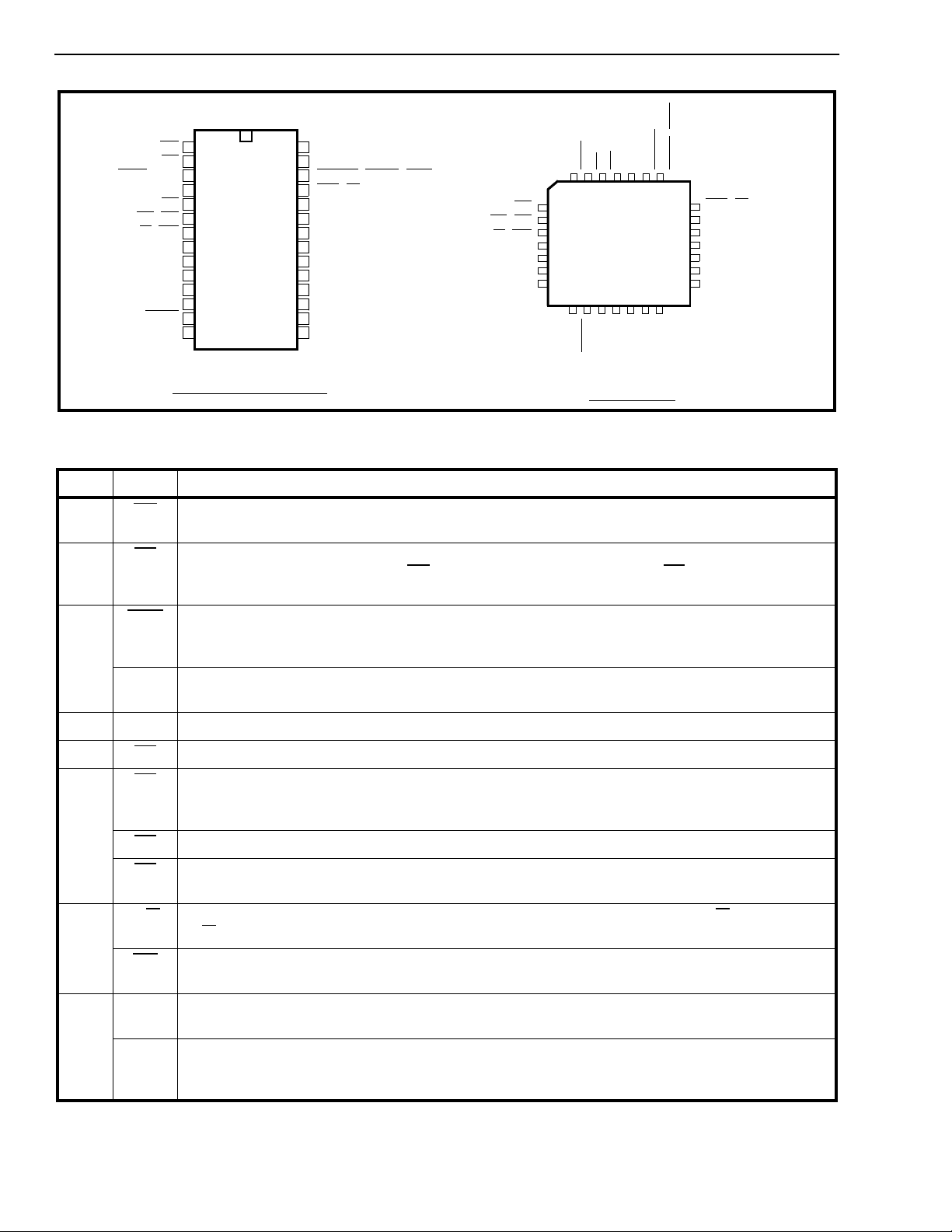

MT8920B CMOS

1

C4i

2

F0i

IACK, MS1

STi0

DS, OE

R/W, WE

A5, STCH

VSS

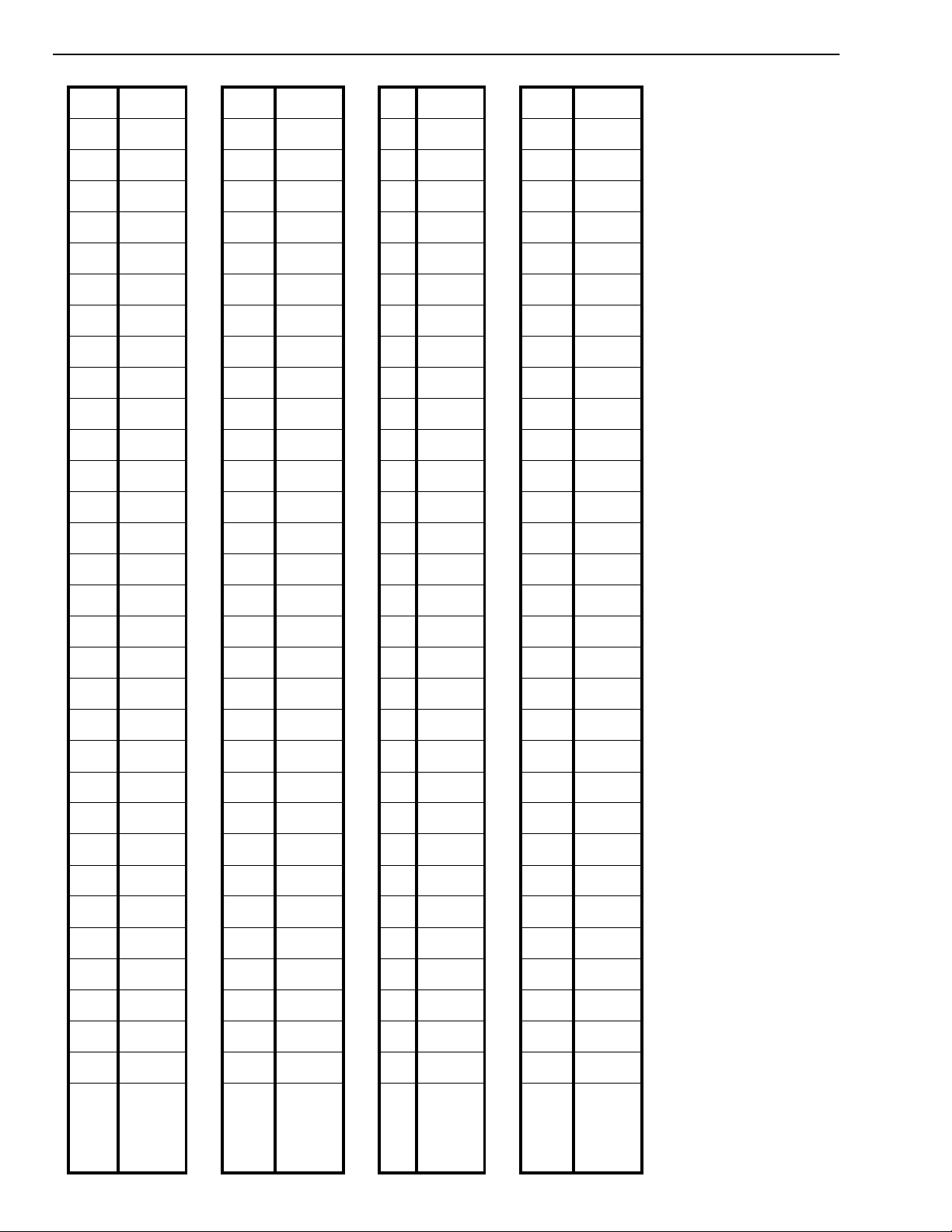

Pin Description

3

4

5

CS

6

7

A0

8

A1

9

A2

10

A3

11

A4

12

13

14

28 PIN PDIP/CERDIP/SOIC

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDD

MMS

, BUSY, DCS

DTACK

IRQ, 24/32

STo1

STo0

D7

D6

D5

D4

D3

D2

D1

D0

Figure 2 - Pin Connections

CS

DS, OE

R/W, WE

A0

A1

A2

A3

STi0

432

5

6

7

8

9

10

11

1213141516

A4

28 PIN J-LEAD

IACK, MS1

A5, STCH

F0i

C4i

1

•

D0D3D2

VSS

VDD

28

17

D1

MMS

27

,

DTACK

26

18

, DCS

BUSY

25

24

23

22

21

20

19

IRQ, 24/32

STo1

STo0

D7

D6

D5

D4

Pin # Name Description

‡

1C4i4.096 MHz Clock. The ST-BUS timing clock used to establish bit cell boundaries for the serial

bus.

2F0i

Framing P ul se. A low going pulse used to synchronize the STPA t o the 2048 kbit/s ST-BUS

stream. The first falling edge of C4i

subsequent to the falling edge of F0i identifies the start of

a frame.

3IACK

Interrupt Acknowledge (Mode 1). This active low input signals that the current bus cycle is

an interrupt vector fetch cycle. Upon receiving this acknowledgement, the STPA wi ll

output a user-programmed vector num ber on D

- D7 indicating the source of the interrupt.

0

MS1 Mode Select 1 (Mode 2,3). This input is used to select the device operating modes. A low

applied to this pin will select mode 3 while a high will select mode 2. (Refer to Table 1.)

4STi0ST -BUS Input 0. This is the input for the 2048 kbit/s ST-BUS serial data stream.

5CS

6DS

Chip Select. This active low input is used to select the STPA for a parallel access .

Data Strobe (Mode 1). This active low input indicates to the STPA that valid data is on the data

bus during a write operation or that the STPA must output valid data on the data bus during a

read operation.

OE

OE

Output Enable (Mode 2). This active low input enables the data bus driver outputs.

Output Enable (Mode 3). This active low output indicates that the selected device is to be

read and that the data bus is available for data transfer.

7 R/W

Read/Write (Mode 1,2). This input defines the data bus transfer as a read (R/W = 1) or a write

= 0) cycle.

(R/W

WE

Write Enable (Mod e 3). This active low output ind icate s the data on t he data bus is to be

written into the selected location of an external device.

8-12 A0-A4 Address Bus (Mode 1, 2). These inputs are used to select the internal registers and two-port

memories of the STPA.

A0-A4 Address Bus (Mode 3). These address outputs are generat ed by the ST PA and reflect the

position in internal RAM where the information will be fetched f rom or stored in. Addresses

generated in this mode are used to access external devices for direct memory t ransfer.

3-4

Pin Description (continued)

CMOS MT8920B

Pin # Name Description

‡

13 A5 Address Bit A5 (Mode 1). This input is used to extend the address range of the STPA. A5

selects internal registers when high and Tx/Rx RAM’s when low.

A5 Address Bit A5 (Mode 2). This input is used to extend the address range of the STPA. A5

selects Tx0/Rx0 RAM’s when low and Tx1/Rx0 RAM’s when high.

STCH

Start of Channel (Mod e 3). This signal is a low going pulse which indicates the start of an

ST-BUS channel. The pulse is four bits wide and begins at the start of each valid channel.

14 V

SS

Ground .

15-22 D0-D7 Bidi recti onal Data Bus. This bus is used to transfer data to or from the STPA during a write

or read operation.

23 STo0 ST -BUS Output 0. This output supplies the output ST-BUS 2048 kbit/s serial data stream from

Tx0 two-port RAM.

24 STo1 ST-BUS Output 1. In modes 1 and 2 this output supplies the output ST-B US 2048 kbit/s serial

data stream from Tx1 two-port RAM. In mode 3, information arriving at STi0 is output here with

one frame delay.

25 IRQ

Interrupt Request (Mo de 1). This open drain output, when low, indicates when an interrupt

condition has been raised within the STPA.

24

/32 24 Channel/32 Chan ne l Select (Mode 2,3). This input is used to select the channel

configuration in modes 2 and 3. A low applied to this pin will select a 24 (T1) channel mode

while a high will select a 32 (CEPT) cha nnel m ode.

26 DTACK

Data Transfer Acknowledge (Mode 1). This open drain output is supplied by the STPA to

acknowledge the completion of data transfers back to the µP. On a read of the STPA, DTACK

low indicates that the STPA has put valid data on the data bus. On a write, DTACK

low

indicates that the STPA has completed latching the µP’s data from the data b us.

BUSY

BUSY (Mode 2). This open drain output signals that the controller and th e ST-BUS are

accessing the same location in the dual-port RAM’s. It is intended to delay the controller

access until after the ST-BUS completes its access.

DCS

Delayed Chip Se lect (Mo de 3). This low going pulse, which is four bit cells long, is active

during the last half of a valid channel. This signal is used to daisy-chain together two STPA’s in

mode 3 that are accessing devices on the same parallel data bus.

27 MMS Master M ode Select (Re set). This Schmitt trigger input selects bet ween either mode 1 (MMS

= 1), or modes 2and 3 (MMS = 0). I f MMS is pulsed low in Mode 1 operation the control and

interrupt registers will be reset. (Refer to Table 1.) During power-up, the time constant of the

reset circuit (see Fig. 8) must be a minimum of five times the rise time of the power supply.

28 V

‡ Pin Descriptions pertain to all modes unless otherwise stated.

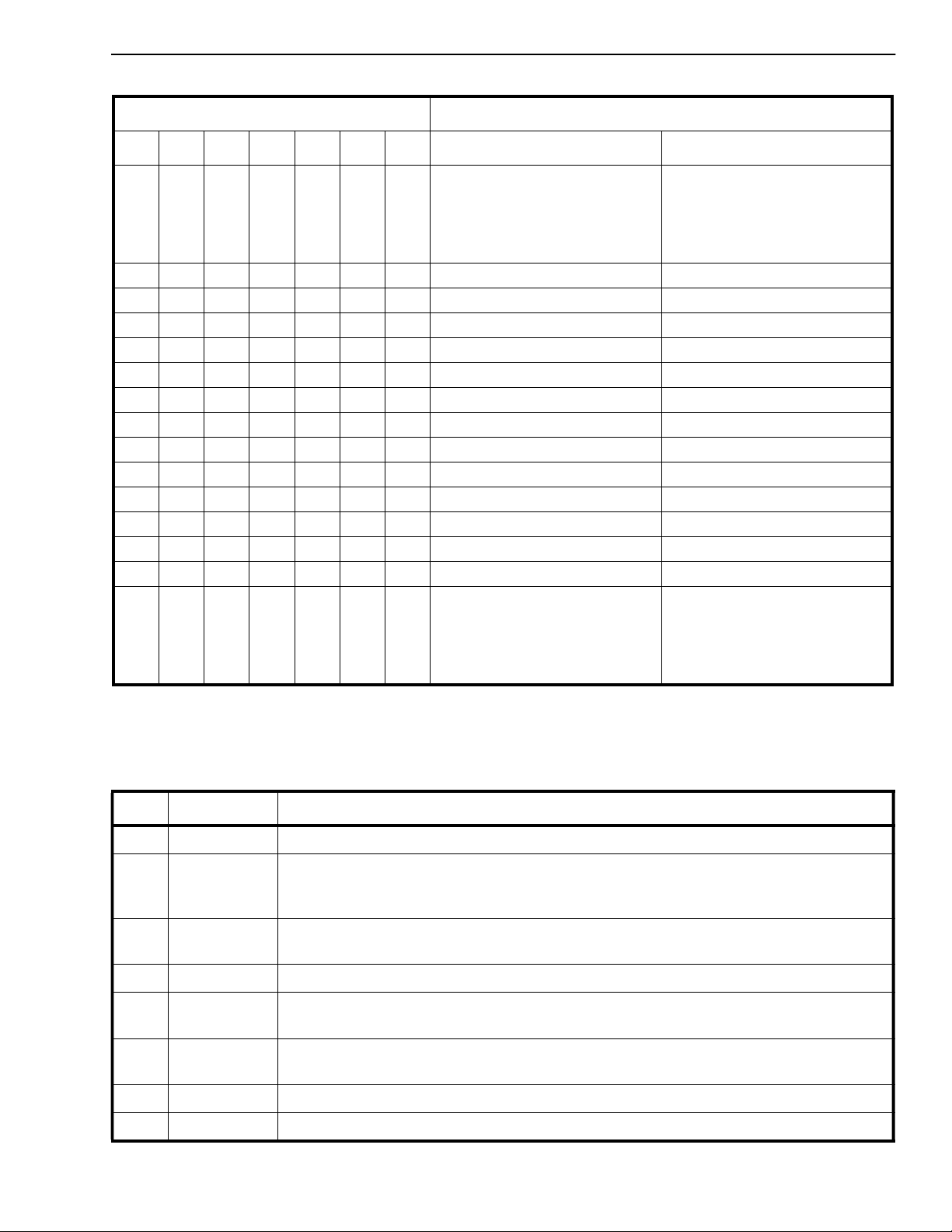

Mode MMS MS1

1 1 N/A µP

2 0 1 Fast RAM

300 Bus

Power Supp ly Input. (+5V).

DD

Mode of

Operation

The STPA provides parallel-to-serial and serial-to-parallel conversions through a

Peripheral

Mode

Mode

Controller

Mode

68000-type interface. Two Tx RAMs and one Rx RAM are available along with full

interrupt capability . 32 channel or 24 channe l support is ava ilable. Control Register 1, bit

D

5

operation.

The STPA provides a fast access interface to Tx0, Tx1 and Rx0 RAMs. This mode is

intended for full parallel support of 24 channel T1/ESF trunks and 32 channel CEPT

trunks. Input 24

channel operation.

The STPA will synchronously drive the parallel bus using the address generator and

provide all data transfer signals. This mode is intended to support 24 or 32 channel

devices in the absence of a parallel bus controller. Input 24

operation, input 24

Function

(RAMCON) = 0 for 32 channel operation and D5 (RAMCON)= 1 for 24 channel

/32 (pin 25) = 0 for 24 channel operation, input 24/32 (pin 25) = 1 for 32

/32 (pin 25) = 0 for 24 channel

/32 (pin 25) = 1 for 32 channel operation.

Ta ble 1. STPA Modes of Op eratio n

3-5

MT8920B CMOS

Functional Description

The STPA (ST-BUS Parallel Access) device provides

a simple interface between Mitel’s ST-BUS and

parallel system environments. The ST-BUS is a

synchronous, time division, multiplexed serial

bussing scheme with data streams operating at 2048

kbit/s. The ST-BUS is the primary means of access

for voice, data and control information to Mitel’s

family of digital telecommunications components,

including North American and European digital trunk

interfaces, ISDN U and S digital line interfaces, filter

codecs, rate adapters, etc. The STPA provides

several modes of operation optimized according to

the type of inform ation being handled.

For interfacing parallel data and control information

to the ST-BUS, such as signalling and link control for

digital trunks, the STPA provides a µP access mode

(Mode 1), and looks like a 68000 type peripheral. In

this mode, the device provides powerful interrupt

features, useful in monitoring digital trunk or line

status (i.e., synchronization, alarms, etc.) or for

setting up message communication links between

microprocessors.

To interface high speed data or multi-channel v oice/

data to the S T-BUS for switching or transmission, the

STPA has a high speed synchronous access mode

(Mode 2) and acts like a fast RAM. For voice

storage and forward, bulk data transfer, data

buffering and other similar applications, the STPA

has a controllerless mode (Mode 3) in which it

provides address and control signals to the parallel

bus This is useful for performing direct transfers to

the ST-BUS from external devices such as a RAM

buffer.

The STPA is a two port device as shown in the

functional block diagram in Figure 1. The parallel

port provid es direc t acces s to thr ee dual port RA M’s,

two transmit and one receive. The address, data

and control busses are used to communicate

between the RAM‘s and a parallel environment.

Two parallel-to-serial converters, and one

serial-to-parallel converter interface the dual port

RAM’s to the ST-BUS port of the STPA. This port

consists of two serial output streams and one serial

input stream operating at 2048 kbit/s. This

configuration of two outputs and one input was

designed to allow a single STPA to form a complete

control interface to Mitel’s digital trunk interfaces

(MT8976, MT8978 and MT8979) which have two

serial input and one s erial output control streams.

ST-BUS clocking circuitry, address generator and

various control and interrupt registers complete the

STPA’s functionality.

Modes o f Ope ratio n

The three basic modes of operat ion, µP Peripheral

Mode (Mode 1), Fast RAM Mode (Mode 2) and Bus

Controller Mode (Mode 3) are selected using two

external input pins. These inputs are M MS and MS1

and are decoded as shown in Table 1. Whenever

MMS=1 the device resides in Mode 1. In this mode,

MS1 pin is unavailable and is used for a different

function.

When MMS=0, Modes 2 or 3 are selected as

determined by input MS1. If MS1=1, Mode 2 is

selected and if MS1 =0, Mode 3 is selected.

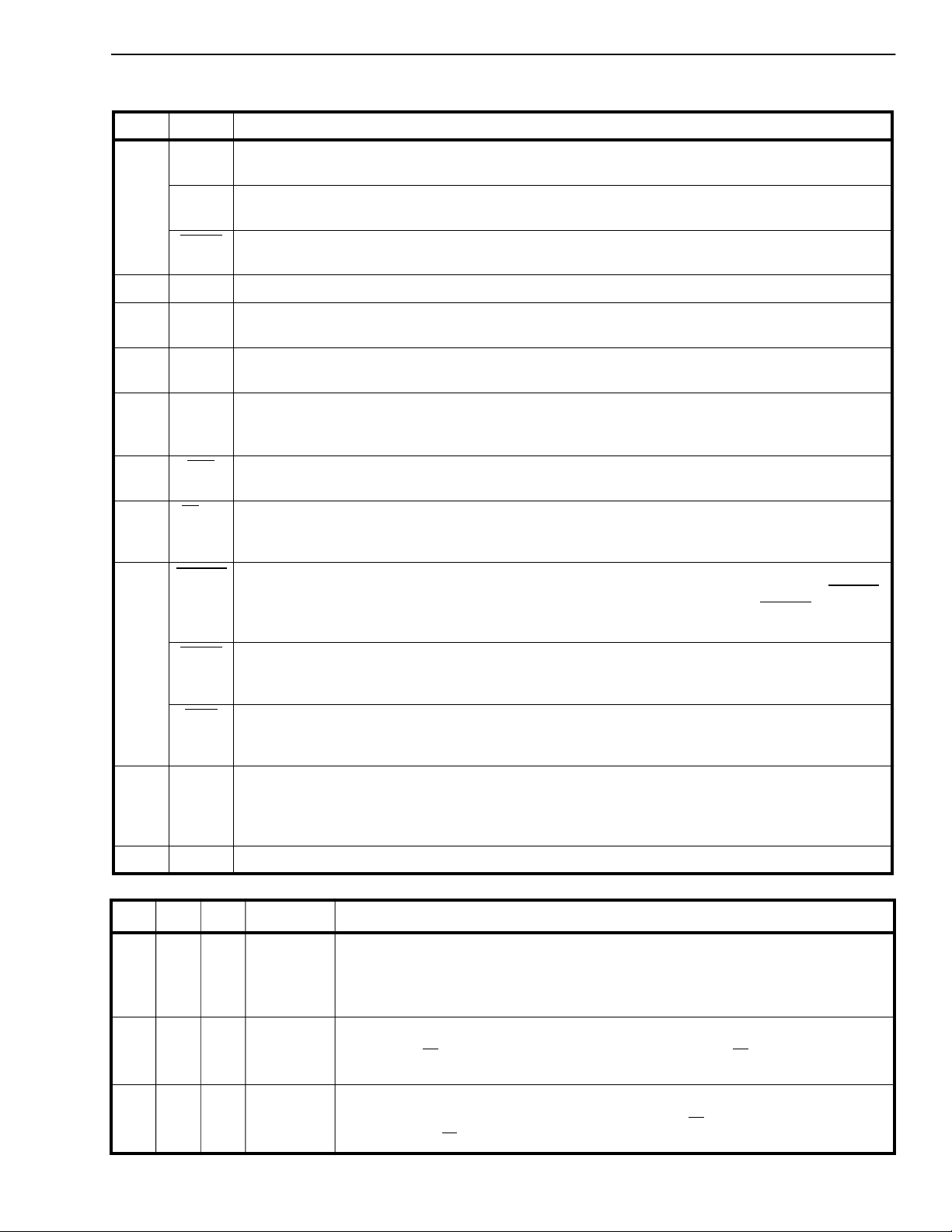

Each of the modes of the STPA provides a different

pinout to ease interfacing requirements of different

parallel environments. These are shown in Figure 3

below. In µP Peripheral Mode the device uses

interface signals consistent with a 68000-type µP

bus. Mode 2, Fast RAM Mode, uses signals typical

of standard RAM type interfaces. Mode 3 interface

signals are very similiar to Mode 2 signals except

that the address and control signals are supplied as

outputs by the STPA.

3-6

µP Peripheral Mode #1

1

C4i

2

F0i

CS

DS

A0

A1

A2

A3

A4

A5

10

11

12

13

14

3

4

5

6

7

8

9

IACK

STi0

R/W

VSS

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Mode #2 Bus Controller Mode #3

1

2

3

4

5

6

7

8

9

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDD

MMS

BUSY

24/32

STo1

STo0

D7

D6

D5

D4

D3

D2

D1

D0

VDD

MMS

DTACK

IRQ

STo1

STo0

D7

D6

D5

D4

D3

D2

D1

D0

C4i

F0i

MS1

STi0

CS

OE

R/W

A0

A1

A2

A3

A4

A5

VSS

Fast RAM

10

11

12

13

14

Figure 3 - Modes 1, 2, 3 Pin Connections

C4i

F0i

MS1

STi0

CS

OE

WE

A0

A1

A2

A3

A4

STCH

VSS

10

11

12

13

14

1

2

3

4

5

6

7

8

9

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDD

MMS

DCS

24/32

STo1

STo0

D7

D6

D5

D4

D3

D2

D1

D0

CMOS MT8920B

24/32 Chan nel O perat ion

The STPA may be configured to operate as a 32

channel or 24 channel device. This feature, which is

available in all three modes of operation, is

particularly useful in applications involving data

access to CEPT and T1 digital trunk interfaces.

When used as a data interface to Mitel‘s CEPT

digital trunks, the STPA maps the 32 consecutive

bytes of each dual port memory directly to ST-BUS

channels 0-31. This is performed by the address

generator shown in the functional block diagram (see

Figure 1). Figures 4 c & d show the relationship

between relative dual port RAM locations and

corresponding ST-BUS channels, for both input and

output serial streams, when the STPA is configured

as a 32 channel device.

When used as a data interface to Mitel’s T1 trunk

devices, however, only the first 24 consecutive RAM

locations are mapped to 24 of the 32 ST-BUS

channels. This mapping follows a specific pattern

which corresponds with the data streams used by

Mitel‘s T1 products. Instead of a direct correlation

(as in 32 channel operation), the 24 consecutive

RAM locations are mapped to the ST-BUS with every

fourth channel, beginning at channel 0, set to FF

16

(ie. channel 0, 4, 8, 12, 16, 20, 24 and 28). F igures

4 a & b show the relationship between RAM

locations and ST-BUS channel configuration. This

feature allows the STPA to be interfaced directly to

Mitel’s T1 trunk family.

When the STPA is operated in Mode 1, 24 and 32

channel configurations are selected using bit D

(RAMCON) in Control Register 1. D5 = 0 selects 32

channel operation and D

= 1 selects 24 channel

5

operation. When the STPA is operated in Modes 2

or 3, however, the channel configuration is done

using input 24

device uses all 32 channels and when 24

/32 (pin 25). When 24/32 = 1 th e

/32 = 0 it

uses 24.

lessened since ST-BUS accesses require only the

last half cycle of C4i

of every channel. When

contention do e s occur, priority is always given to th e

ST- BUS access.

The STPA indicates this contention situation in a

diff erent manner for Modes 1 and 2. In Mode 1, the

contention is masked by virtue of the

"handshaking" method used to transfer data on

this 68000-type interface. Data Strobe (DS

and Data Transfer Acknowledge (DTACK

the exchange. If contention should occur the

device will delay returning DTACK

and thus stretch

the bus cycle until the µP access can be completed.

In Mode 2, if access is attempted during a

"contention window" the STPA will supply the

BUSY

signal to delay the start of the bus cycle. This

“contention window” is defined as shown in Figure

16. The window exists during the last cycle of C4i

clock in each channel timeslot. Although ST-BUS

access is only required during the last half of this

clock period, the “contention window“ exists for the

entire clock period since a parallel access occurring

just prior to an ST-BUS access will not complete

before the ST-B US access begins. Figure 16 further

shows four possible situations that may occur when

parallel accesses are attempted in and around the

“contention window”. Condition 1 indicates that an

access occurring prior to the contention window but

lasting into the first half of it will complete normally

with no contention arbitration. If the access should

extend past the first half of the contention window

and into the ST-BUS access period, the BUSY

will be generated. Conditions 3 and 4 show accesses

occurring inside the contention window. These

5

accesses will result in BUSY

becoming active

immediately after the access is initiated and

remaining active as shown in Figure 16.

Access contention is non-existent in Mode 3 since

the parallel bus signals, driven by the STPA, are

synchron ize d to th e ST-BUS cl o c ks.

)

) control

signal

Dual Port RAMS

Each of the three serial ST-BUS streams is

interfaced to the parallel bus through a 32 byte dual

port RAM. This allows parallel bus accesses to be

performed asynchronously while accesses at the

ST-BUS port are synchronous with ST-BUS clock.

As with any dual port RAM interface between two

asynchronous systems, the possibility of access

contention exists. The STPA minimizes this

occurrence by recognizing contention only when

accesses are performed at the same time for the

same 8-bit cell within the dual port RAM’s.

Furthermore, the probability of contention is

Mode 1 - µP Peripheral Mode

In Mode 1, the STPA operates as an asynchronous

68000-type microprocessor peripheral. All three

dual-port RAMS (Tx0, Tx1, Rx0) are made available

and may be configured as 32 or 24 byte RA M’s. Also

available are the full complement of control and

inter rupt r egist ers. Th e addr ess ma p for M ode 1 is

shown in Table 2.

The STPA, in Mode 1, uses signals CS

, R/W, DS

(Data Strobe), DTACK (Data Acknowledge) IRQ, and

IACK

(Interrupt Acknowledge) at the parallel interface.

The pin out of the device is s h o w n in Figure 3.

3-7

MT8920B CMOS

29 30 31

25 26 27 28

21 22 23 24

17 18 19 20

29 30 31

X

X

X

X

X

25 26 27 28

X

21 22 23 24

X

16

17 18 19 20

X

13 14 15 16

X

9 101112

X

5678

X

1234

0

X

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

Figure 4 a) RELATIVE Rx RA M ADDRESS vs. ST-BUS CHANNEL - 24 CHAN NEL MODE

13 14 15 16

X

9 101112

X

5678

X

1234

0

X

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

Figure 4 b) RELATIVE Tx RAM ADDRESS vs. ST-BUS CHANNEL - 24 CHANN EL MODE

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 2 3 24 25 26 27 28 29 3 0 31

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 2 3 24 25 26 27 28 29 3 0 31

X- unused channe ls m arked X tran smit F F

Figure 4 c) RELATIVE Rx RAM ADDRESS vs. ST-BUS CHANNEL - 32 CHANNEL MODE

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 2 3 24 25 26 27 28 29 3 0 31

Figure 4 d) RELATIVE Tx RAM ADDRESS vs. ST-BUS CHANNEL - 32 CHANN EL MODE

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 2 3 24 25 26 27 28 29 3 0 31

3-8

STi0

RAM

RELATIVE

LOCATION

STo0

STo1

RAM

RELATIVE

LOCATION

STi0

RAM

RELATIVE

LOCATION

STo0

STo1

RAM

RELATIVE

LOCATION

CMOS MT8920B

ADDRESS BITS REGISTERS

A

A

A

A

A

A

6

5

4

3

2

0

0

0

0

0

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

0

0

1

1

1

A

1

0

0

0

•

•

•

•

•

•

1

1

X 1 0 0 0 0 0 Control Register 1 Control Register 1

X 1 0 0 0 0 1 Control Register 2 Control Register 2

X 1 0 0 0 1 0 Interrupt Vector Register Interrupt Vector Register

X 1 0 0 1 0 0 Interrupt Flag Register 1 X 1 0 0 1 0 1 Interrupt Flag Register 2 X 1 0 0 1 1 0 Image Register 1 X 1 0 0 1 1 1 Image Register 2 X 1 0 1 0 0 0 Interrupt Mask Register 1 Interrupt Mask Register 1

X 1 0 1 0 0 1 Interrupt Mask Register 2 Interrupt Mask Register 2

X 1 0 1 0 1 0 Match Byte Register 1 Match Byte Register 1

X 1 0 1 0 1 1 Match Byte Register 2 Match Byte Register 2

X 1 0 1 1 0 0 Interrupt Channel Address 1 In terrupt Channel Address 1

X 1 0 1 1 0 1 Interrupt Channel Address 2 In terrupt Channel Address 2

1

0

0

0

0

0

0

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

1

0

1

1

1

1

1

Table 2. Mode 1 Address Map

NOTES:

X is don’t care

A

is bit D4 of Control Register 1

6

READ WRITE

Rx0 - Channel 0

•

•

•

Rx0 - Channel 31

Rx0 - Channel 0

•

•

•

Rx0 - Channel 31

Tx0 - Channel 0

Tx0 - Channel 31

Tx1 - Channel 0

Tx1 - Channel 31

•

•

•

•

•

•

Bit Nam e Descri ptio n

7 (Unused)

6 IRQRST Interrupt Reset. This bit, when set high, automatically clears the Interrupt Flag Register

and the Interrupt Image Register without these registers being serviced. This bit

automatically resets to zero after the register clear is complete d.

5RAMCONRA M Configuration. This bit configures Tx0, Tx1 and Rx0 RAMS for 32 or 24 byte

operation. D

4A

6

Address Bit A6. This bit extends the addressing range for access to Tx1 memory.

= 0 for 32 channel; D5 = 1 for 24 channel.

5

3 IRQ2MODE Interrupt Source 2 Mode Se lec t. This bit configure s the source 2 interrupt generator.

D

= 0 selects “static” interrupt mode; D3 = 1 selects “dynamic” interrupt mode.

3

2 IRQ 1M O DE Interrupt Source 1 Mo de Se lec t. This bit configure s the source 1 interrupt generator.

D

= 0 selects “static” interrupt mode; D2 = 1 selects “dynamic” interrupt mode.

2

1 IRQ2EN Interrupt Sou rce 2 Enabl e. IRQ2EN = 1 enables interrupts to occur from source 2.

0 IRQ1EN Interrupt Sou rce 1 Enabl e. IRQ1EN = 1 enables interrupts to occur from source 1.

Table 3. Control Register 1 Bit Definitions

3-9

MT8920B CMOS

Timing information for data transfers on this interface

is shown in Figure 14. The Mode 1 interface is

designed to operate directly with a 68000-type

asynchronous bus but can easily accommodate most

other popular microprocessors as well.

Control Registe rs

Two control registers allow control of Mode 1

features. Control Register 1 provides bits to select

the type of interrupt, to enable interrupts from two

different and independent sources and to reset the

interrupt registers. Also contained in Control

Register 1 are bits to configure the device for 24 or

32 channel operation and to expand the address

range for convenient access to the second transmit

RAM Tx1. A description of the bit functions in

Control Register 1 is shown in Table 3.

Mode 1 provides various loopback paths and output

configuration options which are controlled by bits in

Control Register 2. Bits D

, D1 of Control Register 2

0

configure loopbacks using input and output streams

STi0, STo0 as described in Table 4. The input

stream S Ti0 can be looped back to source the output

stream STo0 as well as receive RAM Rx0. The

transmit RAM Tx0 can be looped to source the

receive RAM Rx0, as well as STo0 and, the transm it

RAM Tx0 can be looped to the receive RAM Rx0

while STi0 sources STo0. The function of these

loopback configurat ions is shown in Figure 5.

In a similar way, the output STo1 can be reconfigured

for different functionality. Bits D

and D3 of Control

2

Register 2 allow STo1 to be sourced, with a one

frame delay via Tx1 from receive stream STi0. STo1

can also output the result of a comparison of the

contents of Tx1 ram wit h input stream STi0. These

output configurations of STo1 are shown in Figure 6

a and b. Figure 6 c shows the effect of combining

these two features.

Interrupt Registers

Interrupts can be generated in Mode 1 only. Two

channels of the ST-BUS input stream, S Ti0, can be

selected to provide an interrupt to the system.

Interrupts can be of two types: Static or Dynamic.

Static interrupts are caused when data within a

selected channel matches a given patte rn. Dynamic

interrupts occur when bits in a selected channel

change state (1 to 0, 0 to 1 or toggle). Interrupts are

controlled through two identical paths (1 and 2)

consisting of the following registers:

Interrupt Channel Address (1/2): The address

(0-31) of the channel which will generate the

interrupt is stored in this register.

Image Register (1/2): The contents of the

channel causing the interrupt is stored in this

register. R eading this register will clear its contents.

Match Byte Register (1/2): In static mode this

register is used to store the byte which will be

compared with the contents of the selected channel

causing the interrupt.

In dynamic mode, the bits in this register and the

corresponding bit in the Interrupt Mask Register

define the type of dynamic interrupt (i.e., 0 to 1, 1 to

0, toggle ). ( R ef er to Table 5.)

Bit Name Description

7-4 (Unused)

3-2 CONFIG STo1 Output Configuration Bits:

D

= 00- Normal operation. ST-BUS stream from Tx1 is output on STo1 pin.

3D2

01- S Ti0 stream is output on STo1 pin delayed one fram e (Figure 6 a).

10- S Ti0 is compared through XOR (exclusive OR) with ST-BUS stream

from Tx1 and output at STo1 (Figure 6 b).

11- STi0 stream, delayed one frame (via Tx1), is compared (XOR) w ith the

next frame arriving at STi0 and the result output at STo1 (Figure 6 c).

1-0 LOOPBACK Internal Loopback Con figuration Bits:

= 00- Normal operation. No internal loo ps.

D

1D0

01- L oo p STi0 to STo0 while still receiving STi0 in Rx0 (Figure 5 a).

10- L oo p Tx0 output ST-BUS stream to Rx0 input ST-BUS stream while

outputting Tx0 outpu t to STo0. STi0 is not received (Figure 5 b).

11- Loop Tx0 output ST-BUS stream to Rx0 input ST-B US stream. Loop

STi0 to STo0 (Figure 5 c).

Table 4. Control Register 2 Bit Definitions

3-10

Loading...

Loading...