MITEL MT8815AC, MT8815AP, MT8815AE Datasheet

ISO-CMOS

MT8815

8 x 12 Analog Switch Array

Features

• Internal cont rol lat ches and add ress d eco der

• Short set-up and hold times

• Wide ope rating v oltag e: 4. 5V to 13.2V

• 12Vpp anal og s ignal capabi lity

•R

• ∆R

65Ω max. @ VDD=12V, 25°C

ON

≤ 10Ω @ VDD=12V, 25°C

ON

• Full CMOS switch for low distortion

• Minimum f eedthr oug h and c ros stal k

• Separate ana lo g and di gital re ferenc e supp lies

• Low power consumption ISO-CMOS technology

Applications

• Key systems

• PBX systems

• Mobile rad io

• Test equipment /instru men tatio n

• Analo g/ di gita l m ult ip le xers

• Audio/Video switching

ISSUE 1 November 1988

Ordering Information

MT8815AC 40 Pin Ce r am i c D IP

MT8815AE 40 Pin Pla stic D IP

MT8815AP 44 Pin PL C C

-40° to 85°C

Description

The Mitel MT8815 is fabricated in MITEL’s ISOCMOS technology providing low power dissipation

and high reliability. The device contains a 8 x 12

array of crosspoint switches along with a 7 to 96 line

decoder and latch circuits. Any one of the 96

switches can be addressed by selecting the

appropriate seven address bits. The selected switch

can be turned on or off by applying a logical one or

zero to the DATA input. V

of the digital inputs. The range of the analog signal

is from V

to VEE.

DD

is the ground reference

SS

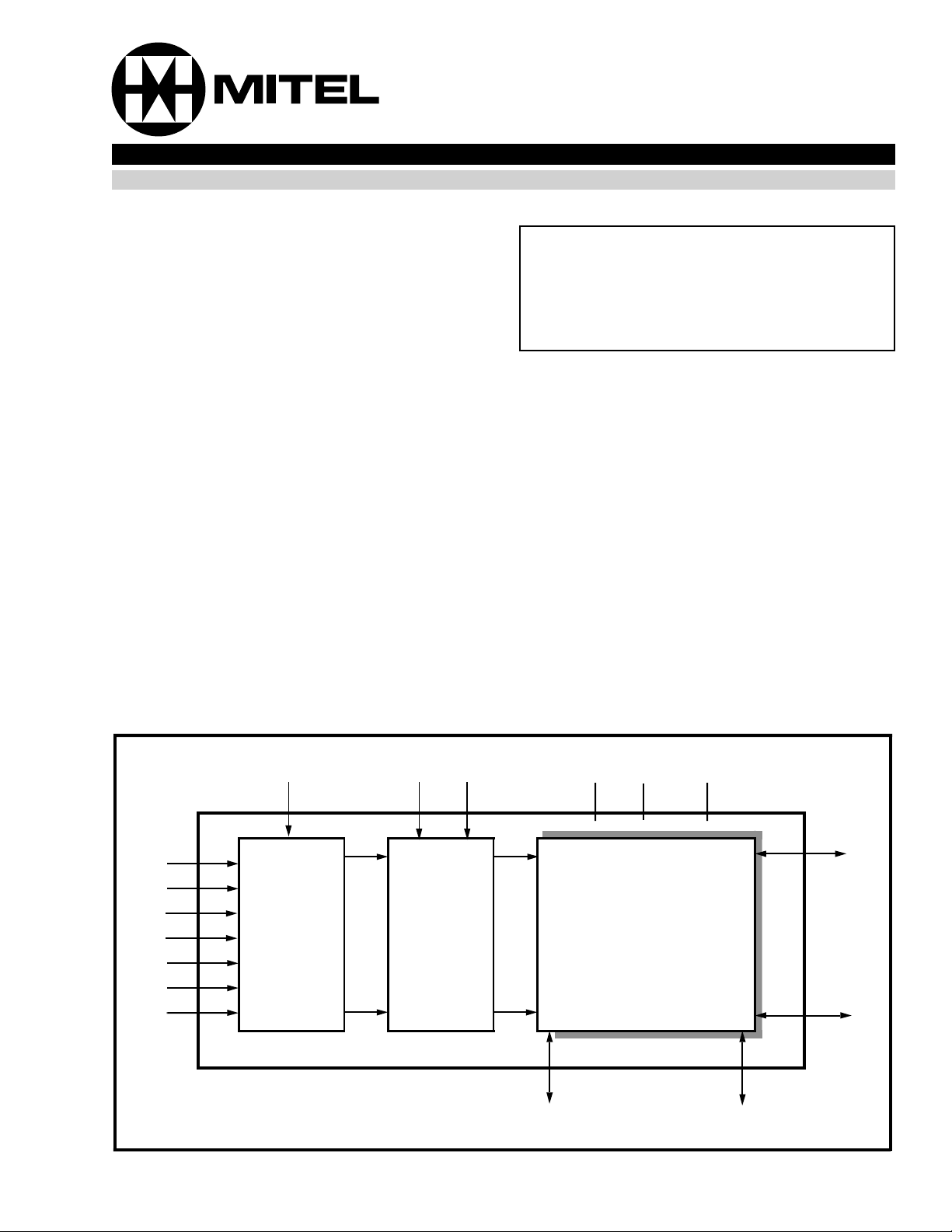

AX0

AX1

AX2

AX3

AY0

AY1

AY2

STROBE DATA RESET VDD VEE VSS

11

8 x 12

7 to 96

Decoder

Latches

Switch

Array

9696

• • • • • • • • • • • • • • • • • • •

Yi I/O (i=0-7)

Figure 1 - Functional Block Diagram

• • • • • • • • • • • • • • • •

Xi I/O

(i=0-11)

3-39

3-39

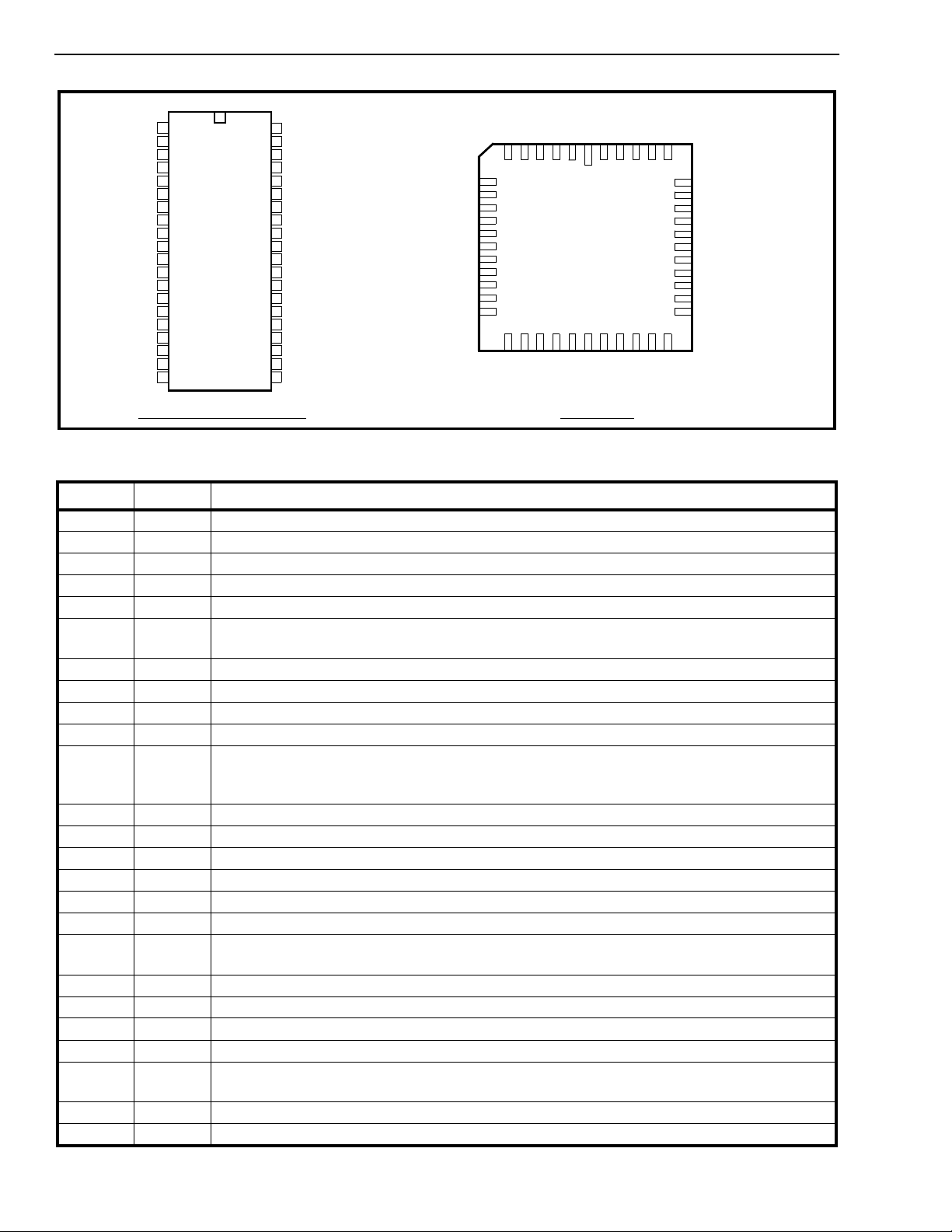

MT8815 ISO-CMOS

1

Y3

AY2

RESET

AX3

AX0

VSS

STROBE

VEE

2

3

4

5

6

NC

7

NC

8

X6

9

X7

10

X8

11

X9

12

X10

13

X11

14

NC

15

Y7

16

17

Y6

18

19

Y5

20

40 PIN CERDIP/PLASTIC DIP 44 PIN PLCC

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

NC

Y2

DATA

Y1

VDD

Y0

NC

X0

X1

X2

X3

X4

X5

NC

NC

AY1

AY0

AX2

AX1

Y4

NC

NC

X6

X7

X8

X9

X10

X11

NC

NC

Y7

DATA

Y2

NC

Y3

AY2

RESET

AX3

AX0

NC

65432 44434241

7

8

9

10

11

12

13

14

15

16

17

Y6

VSS

1

231819202122 242526 2728

Y5

VEE

STROBE

Y4

AX1

AX2

AY0

Y1

40

39

38

37

36

35

34

33

32

31

30

29

AY1

VDD

Y0

NC

X0

X1

X2

X3

X4

X5

NC

NC

NC

NC

Figure 2 - Pin Connections

Pin Description

Pin #* Name Description

1Y3Y3 Analog (Input/Output): this is connected to the Y3 column of the switch array.

2AY2Y2 Add ress Lin e (Inp ut).

3 RESET Master RESET (Input): this is used to turn off all switches. Active High.

4,5 AX3,AX0 X3 and X0 Address Lines (Inputs): these are used to select X3 and X0 rows of switches.

6,7 NC No Connection.

8-13 X6-X11 X6-X11 Analog (Inputs/Outputs): these are connected to the X6-X11 rows of the switch

array.

14 NC No Connection

15 Y7 Y7 Analog (Input/Output): this is connected to the Y7 column of the switch array.

16 V

17 Y6 Y6 Analog (Input/Output): this is connected to the Y6 column of the switch array.

18 STROB E STROBE (Input): enables function selected by address and data. Address must be stable

19 Y5 Y5 Analog (Input/Output): this is connected to the Y5 column of the switch array.

20 V

21 Y4 Y4 Analog (Input/Output): this is connected to the Y4 column of the switch array.

22, 23 AX1,AX2 X1 and X2 Address Lines (Inputs).

24, 25 AY0,AY1 Y0 and Y1 Address Lines (Inputs).

26, 27 NC No Connection.

28 - 33 X5-X0 X5-X 0 Analog (Inp uts/Ou tp uts): these are connected to the X5-X0 rows of the switch

34 NC No Connection.

35 Y0 Y0 Anal og (Input/Ou tpu t): this is connected to the Y0 column of the switch array.

36 V

37 Y1 Y1 Anal og (Input/Ou tpu t): this is connected to the Y1 column of the switch array.

38 DATA DATA (Input): a logic high input will turn on the selected switch and a logic low will turn off

39 Y2 Y2 Anal og (Input/Ou tpu t): this is connected to the Y2 column of the switch array.

40 NC No Connection.

* Plastic DIP and CERDIP only.

Digital Ground Reference (Input).

SS

before STRO BE goes high and DATA must be stable on the falling edge of the STROBE .

Active High.

Negative Power Supply.

EE

array.

Positive Po wer Supply.

DD

the selected switch. Active High.

3-40

Loading...

Loading...