MITEL MT3370BN, MT3370BS, MT3271BE, MT3270BE, MT3170BE Datasheet

...

MT3170B/71B, MT3270B/71B, MT3370B/71B

Wide Dynamic Range DTMF Receiver

Features

• Wide dynamic range (50dB) DTMF Receiver

• Call progress (CP) detection via cadence

indication

• 4-bit synchronous serial data output

• Softwa re con trolle d guard t ime f or MT3x 70B

• Internal guard time circuitry for MT3x71B

• Powerdown option (MT317xB & MT337xB)

• 4.194304MHz crystal or ceramic re sonator

(MT337xB and M T327 xB)

• External clock input (MT317xB)

• Guara ntees non-de tectio n of sp urious t ones

Applications

• Integrat ed te leph one answ ering mac hine

• End-to -end si gnall ing

• Fax Machines

Description

The MT3x7xB is a family of high performance DTMF

receivers which decode all 16 tone pairs into a 4-bit

binary code. These devices incorporate an AGC for

wide dynamic range and are suitable for end-to-end

ISSUE 2 May 1995

Ordering Information

MT3170/71BE 8 Pin Plastic DIP

MT3270/71BE 8 Pin Plastic DIP

MT3370/71BS 18 Pin SOIC

MT3370/ 71BN 20 Pin SS OP

-40 °C to +85 °C

signalling. The MT3x70B provides an early steering

(ESt) logic output to indicate the detection of a DTMF

signal and requires external software guard time to

validate the DTMF digit. The MT3x71B, with preset

internal guard times, uses a delay steering (DStD)

logic output to indicate the detection of a valid DTMF

digit. The 4-bit DTMF binary digit can be clocked out

synchronously at the serial data (SD) output. The

SD pin is multiplexed with call progress detector

output. In the presence of supervisory tones, the

call progress detector circuit indicates the cadence

(i.e., envelope) of the tone burst. The cadence

information can then be processed by an external

microcontroller to identify specific call progress

signals. The MT327xB and MT337xB can be used

with a crystal or a ceramic resonator without

additional components. A power-down option is

provided for the MT317xB and MT337xB.

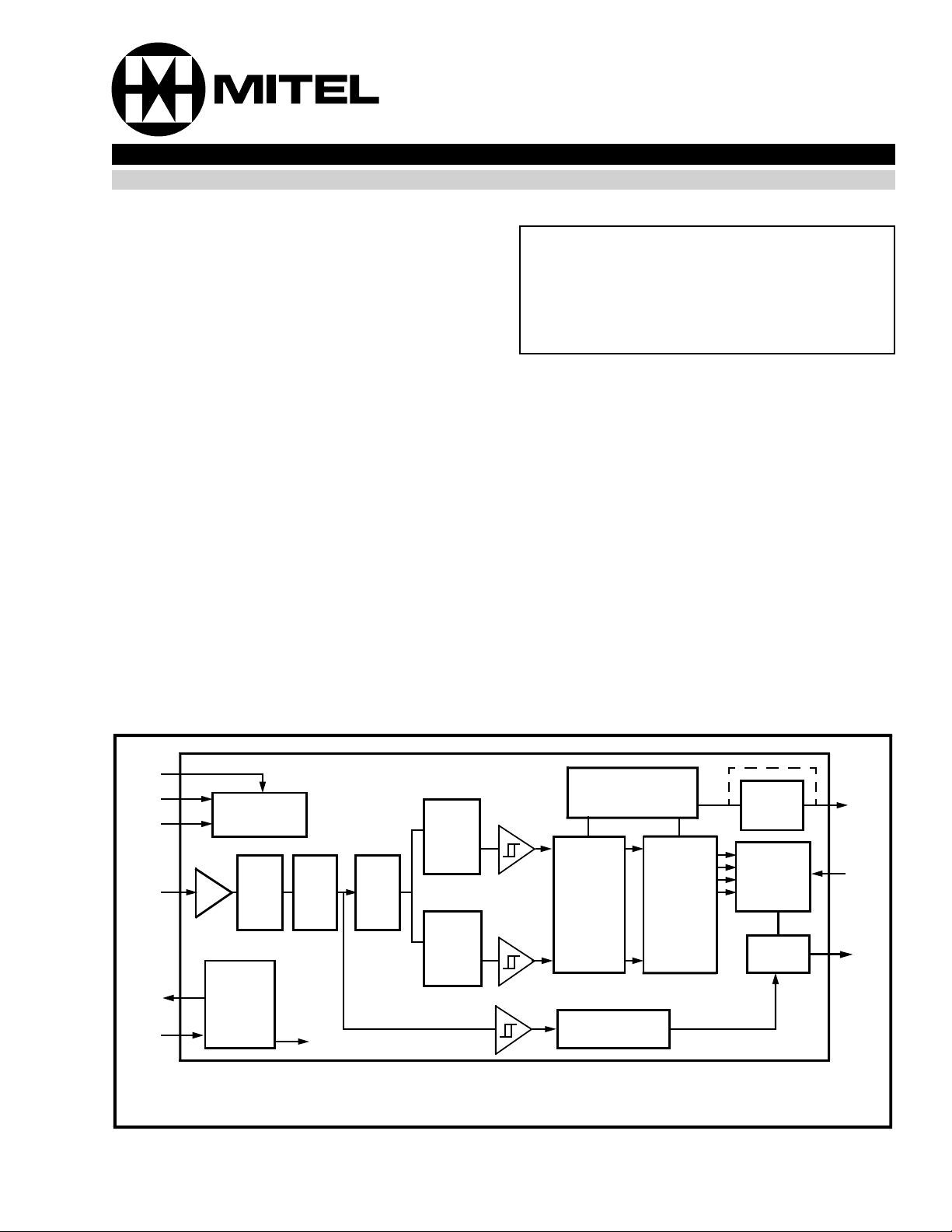

➀

PWDN

VDD

VSS

INPUT

➁

OSC2

OSC1

(CLK)

➀ MT3170B/71B and MT337xB only.

➁ MT3270B/71B and MT337xB only.

➂ MT3x71B only.

Voltage

Bias Circuit

AGC

Filter

Oscillator

and

Clock

Circuit

Antialias

To All Chip Clocks

Dial

Tone

Filter

Figure 1 - Functional Block Diagram

High

Group

Filter

Low

Group

Filter

Digital

Detector

Algorithm

Energy

Detection

Steering

Circuit

Code

Converter

and

Latch

Digital

Guard

➂

Time

Parallel to

Serial

Converter

& Latch

Mux

ESt

or

DStD

ACK

SD

4-3

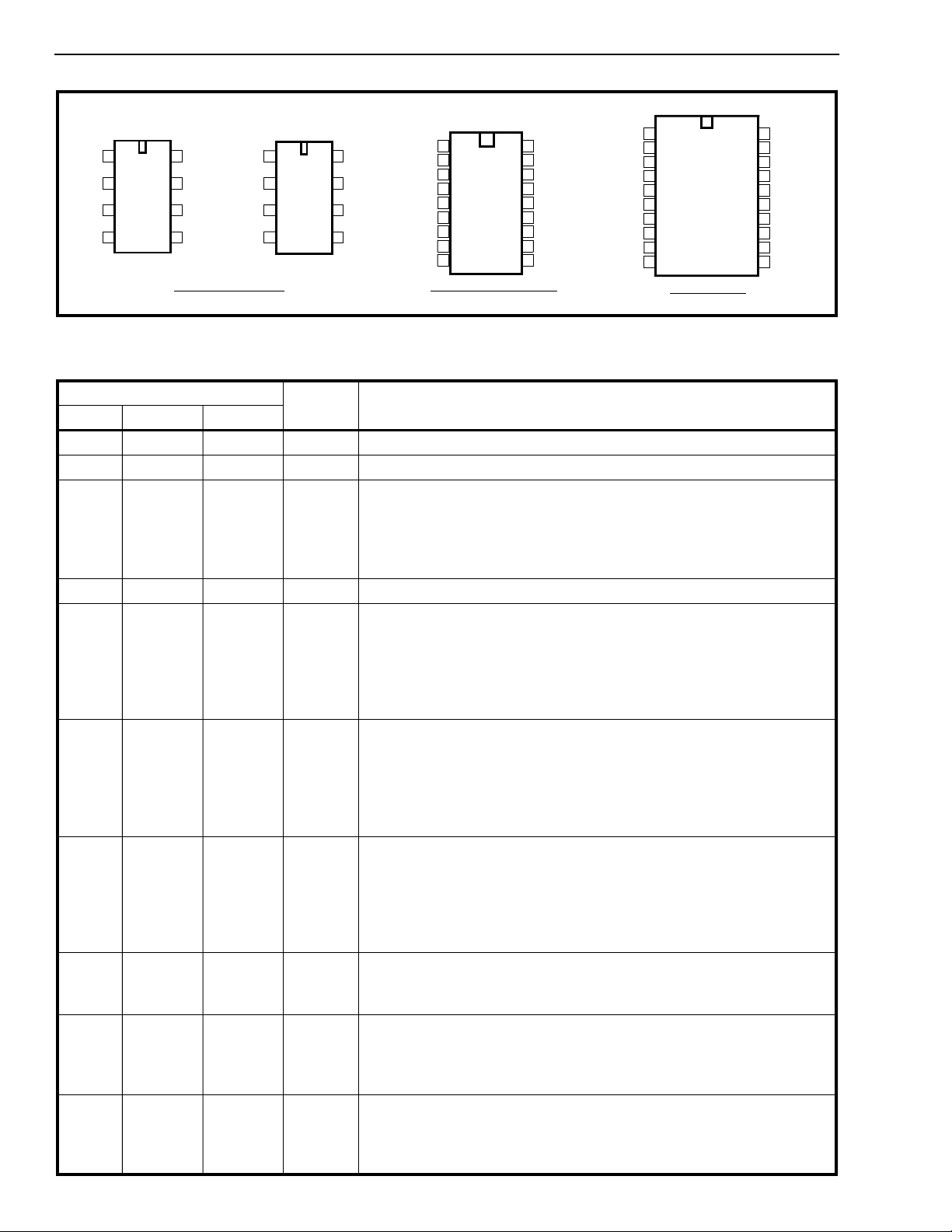

MT3170B/71B, MT3270B/71B, MT3370B/71B

NC

NC

NC

NC

NC

MT3370B/71B

1

2

3

4

5

6

7

8

9

10

20 PIN SSOP

20

19

18

17

16

15

14

13

12

11

MT3170B/71B MT3270B/ 71 B MT3370B/ 71 B

INPUT

PWDN

CLK

VSS

VDD

ESt/

DStD

ACK

SD

INPUT

OSC2

OSC1

VSS

1

2

3

4

1

8

2

7

3

6

4

5

8 PIN PLASTIC DIP

VDD

8

ESt/

7

DStD

ACK

6

SD

5

NC

INPUT

PWDN

OSC2

NC

OSC1

NC

NC

VSS

18 PIN PLASTIC SOIC

1

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

VDD

NC

NC

ESt/DStD

NC

ACK

NC

SD

NC

INPUT

PWDN

OSC2

OSC1

VSS

Figure 2 - Pin Connections

Pin Description

Pin #

337xB 327xB 317xB

2 1 1 INPUT DTMF/CP Input. Input signal must be AC coupled via capacitor.

42 -OSC2Oscillator Ou tpu t.

63 3OSC1

94 4V

11 5 5 SD Serial Data/Call Progress Output. This pin serves the dual function

13 6 6 ACK Acknow le dg e Pulse Inpu t . After ESt or DStD is high, applying a

15 7 7 ESt

Name Description

Oscillator/ Cl ock In pu t. This pin can either be driven by:

(CLK )

1) a n external dig ital clock with defi ned input logic levels. OSC2

should be left open.

2) connecting a crystal or ceramic resonator between OSC1 and

OSC2 pins.

Ground. (0V)

SS

of being the serial data output when clo ck pulse s are applied after

validation of DTMF signal, and also indicate s the cadence of call

progress input. As DTMF signal lies in the same frequency band a s

call progress signal, this pin may togg le for DTM F input. The SD pin

is at logic low in powerdown state.

sequence of four pulses on this pin will then shift out four bits on the

SD pin, representing the decoded DTMF digit. The rising edge of the

first clock is used to latch the 4-bit data prior to shifting. This pin is

pulled down internall y. The idle state of the ACK signal should be

low.

Early Steerin g Output. A logic high on ESt indicates that a DTMF

(MT3x70B)

signal is present. ESt is at logic low in powerdown state.

NC

NC

VDD

NC

ESt/DStD

NC

ACK

SD

NC

NC

DStD

(MT3x7 1B)

Delayed Steering Output. A logic high on DStD indicate s that a

valid DTMF digit has been dete cted. DStD is at logic low in

powerdown state.

18 8 8 V

Positive Power Supply (5V Typ.) Performance of the device can be

DD

optimized by minim izing noise on the supply rails. Decoupli ng

1,5,7,8,

capacitors across V

--NCNo Connection. Pin is unconnected internally.

and VSS are therefore recommend ed.

DD

10, 12,

14,16,

17

3- 2PWDNPower Dow n Inpu t. A logic high on this pin will power down the

device to reduce power consumption. This pin is pulled down

internally and can be left open if not used. ACK pin should be at logic

’0’ to power down device.

4-4

MT3170B/71B, MT3270B/71B, MT3370B/71B

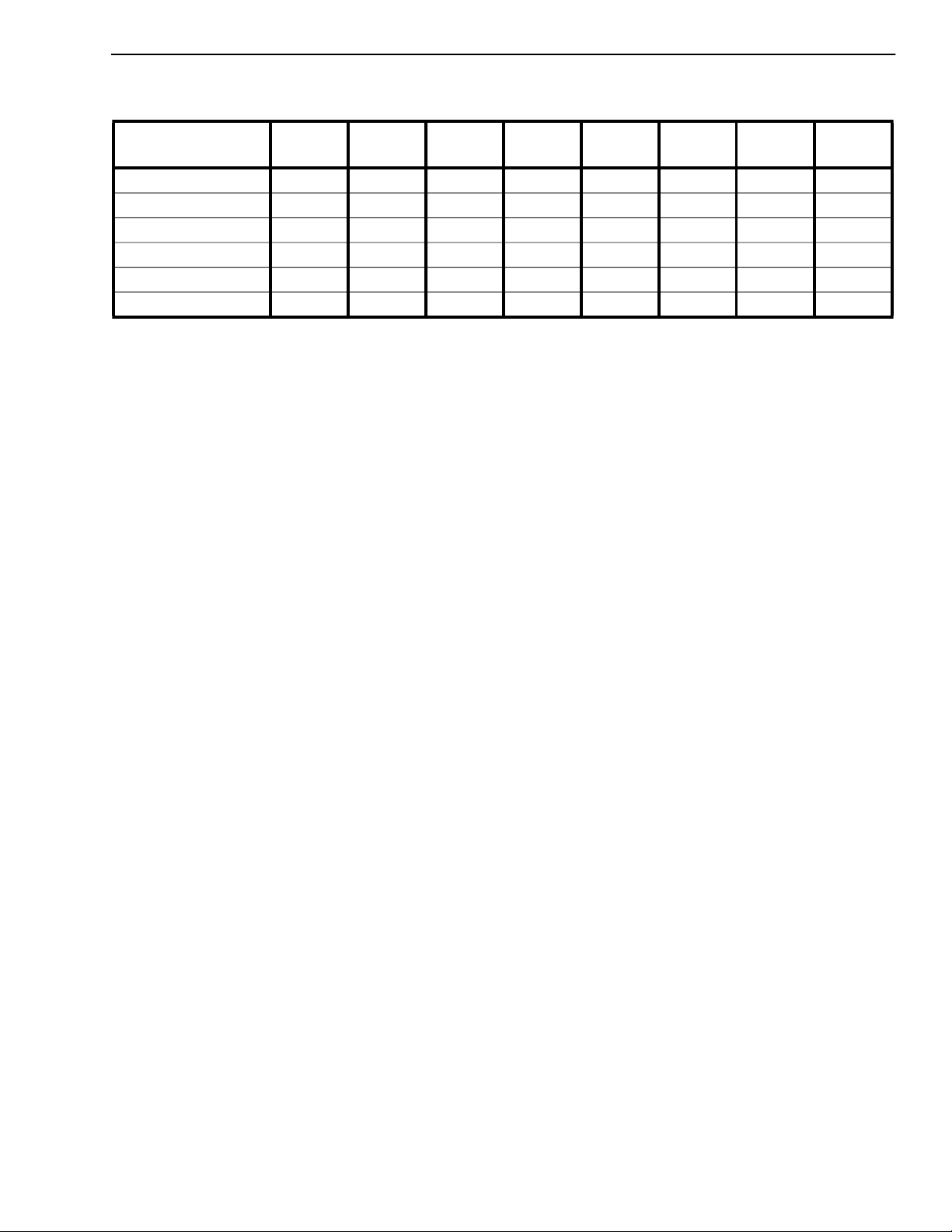

Summary of MT3x70/71B Product Family

Device

Type

MT3170B ✔✔✔✔

MT3171B ✔✔✔✔

MT3270B ✔✔✔✔

MT3271B ✔✔✔✔

MT3370B ✔✔✔✔✔✔

MT3371B ✔✔✔✔✔ ✔

Functional Description

The MT3x7xBs are high performance and low power

consumption DTMF receivers. These devices

provide wide dynamic range DTMF detection and a

serial decoded data output. These devices also

incorporate an energy detection circuit. An input

voiceband signal is applied to the devices via a

series decoupling capacitor. Following the unity gain

buffering, the signal enters the AGC circuit followed

by an anti-aliasing filter. The bandlimited output is

routed to a dial tone filter stage and to the input of

the energy detection circuit. A bandsplit filter is then

used to separate the input DTMF signal into high

and low group tones. The high group and low group

tones are then verified and decoded by the internal

frequency counting and DTMF detection circuitry.

Following the detection stage, the valid DTMF digit is

translated to a 4-bit binary code (via an internal lookup ROM). Data bits can then be shifted out serially

by applying external clock pulses.

Automatic Gain Control (A GC) Circ uit

As the device operates on a single power supply, the

input signal is biased internally at approximately

VDD/2. With large input signal amplitude (between 0

and approximately -30dBm for each tone of the

composite signal), the AGC is activated to prevent

the input signal from being clipped. At low input

level, the AGC remains inactive and the input signal

is passed directly to the hardware DTMF detection

algorithm and to the energy detection circuit.

Filter and Decoder Section

The signal entering the DTMF detection circuitry is

filtered by a notch filter at 350 and 440 Hz for dial

tone rejection. The composite dual-tone signal is

further split into its individual high and low frequency

components by two 6

bandpass filters. The high group and low group

tones are then smoothed by separate output filters

and squared by high gain limiting comparators. The

8 Pin 18 Pin 20 Pin PWDN

resulting squarewave signals are applied to a digital

detection circuit where an averaging algorithm is

employed to determine the valid DTMF signal. For

MT3x70B, upon recognition of a valid frequency from

each tone group, the early steering (ESt) output will

go high, indicating that a DTMF tone has been

detected. Any subsequent loss of DTMF signal

condition will cause the ESt pin to go low. For

MT3x71B, an internal delayed steering counter

validates the early steering signal after a

predetermined guard time which requires no external

components. The delayed steering (DStD) will go

high only when the validation period has elapsed.

Once the DStD output is high, the subsequen t loss of

early steering signal due to DTMF signal dropout will

activate the internal counter for a validation of tone

absent guard time. The DStD output will go low only

after this validation period.

Energy Detection

The output signal from the AGC circuit is also

applied to the energy detection circuit. The detection

circuit consists of a threshold comparator and an

active integrator. When the signal level is above the

threshold of the internal comparator (-35dBm), the

energy detector produces an energy present

indication on the SD output. The integrator ensures

the SD output will remain at high even though the

input signal is changing. When the input signal is

removed, the SD output will go low following the

integrator decay time. Short decay time enables the

signal envelope (or cadence) to be generated at the

SD output. A n external mic rocontroller c an monitor

this output for specific call progress signals. Since

presence of speech and DTMF signals (above the

threshold limit) can cause the SD output to toggle,

both ESt (DStD) and SD outputs should be

monitored to ensure correct signal identification. As

the energy detector is multiplexed with the digital

serial data out put at the SD pin, the detector output

th

order switched capacitor

is selected at all times except during the time

between the rising edge of the first pulse and the

falling edge of the fourth pulse applied at the ACK

pin.

2 Pin

OSC

Ext

CLK

ESt DStD

4-5

Loading...

Loading...