MITEL MH89792-3, MH89792-2, MH89792-1 Datasheet

MH89792

E1Transceiver

Preliminary Information

Features

• Complet e primary ra te 20 48kb /s CEPT line

driver and re ceiver

• Onboard pul se tran sform ers for transm it and

receive

• Meets lates t E TSI requirement s (ET S I ETS 30 0

011 (NET 5))

• Inductorless clock recovery

• Loss of signal indication/ polarity selection

• Programmab le pol arit y of extra cted c lock &

receive data

• Single +5 V ope ration

• Compatible with all E1 framers

2

• Small footprint area (<330mm

)

Applications

• Primary rate ISDN network Interface

• Multiplexe r equ ipm ent

• Private Network links

• Isochrono us LA NS/WANS

ISSUE 3 April 1995

Ordering Information

MH89792-1 20 Pin SIL Package

MH89792-2 20 Pin SIL Package

MH89792-3 20 Pin SIL Package

0°C to 70°C

Description

The Mitel MH89792 is a low cost E1 line driver/

receiver with clock extraction requiring no external

components. There are three versions available:

MH8979 2- 1 fo r 120

MH89792-2 for 75

MH8979 2- 3 fo r 100

Ω twisted pair cable;

Ω co-axial links;

Ω digital twisted pair.

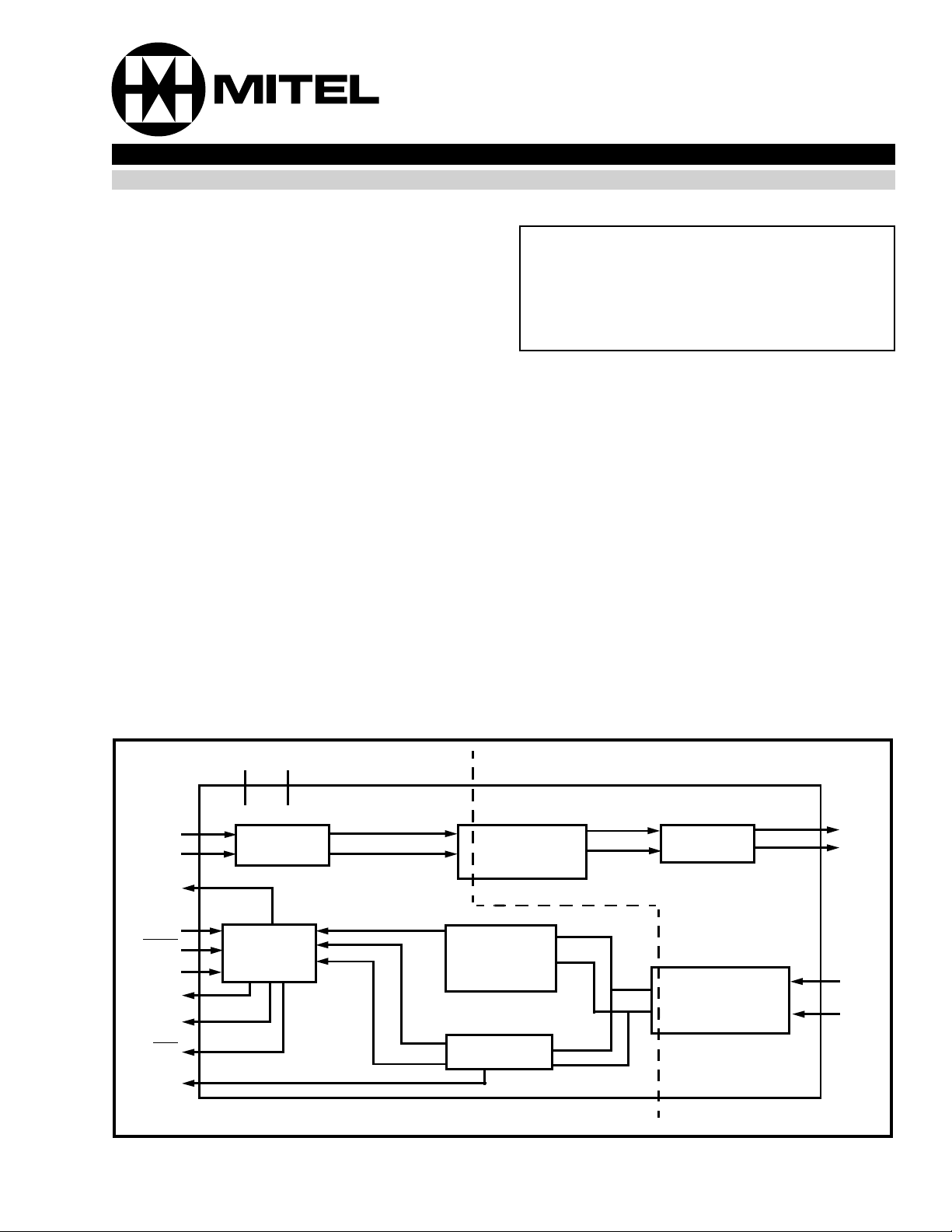

TxA

TxB

E2o

LOSP

CLKF/

CLKR

RxINV

RxA

RxB

LOS

RxD

VDD VSS

Line

Driver

Polarity

Selection

Clock/Data

Transmit

Isolation

Transform er

Clock

Recovery

Line

Receiver

EQUIPMENT SIDE

Figure 1 - Functional Blo ck Diag ram

6dB

Pad

Receive

Isolation

Transformer

LINE SIDE

TLA

TLB

RLA

RLB

4-223

MH89792 Preliminary Information

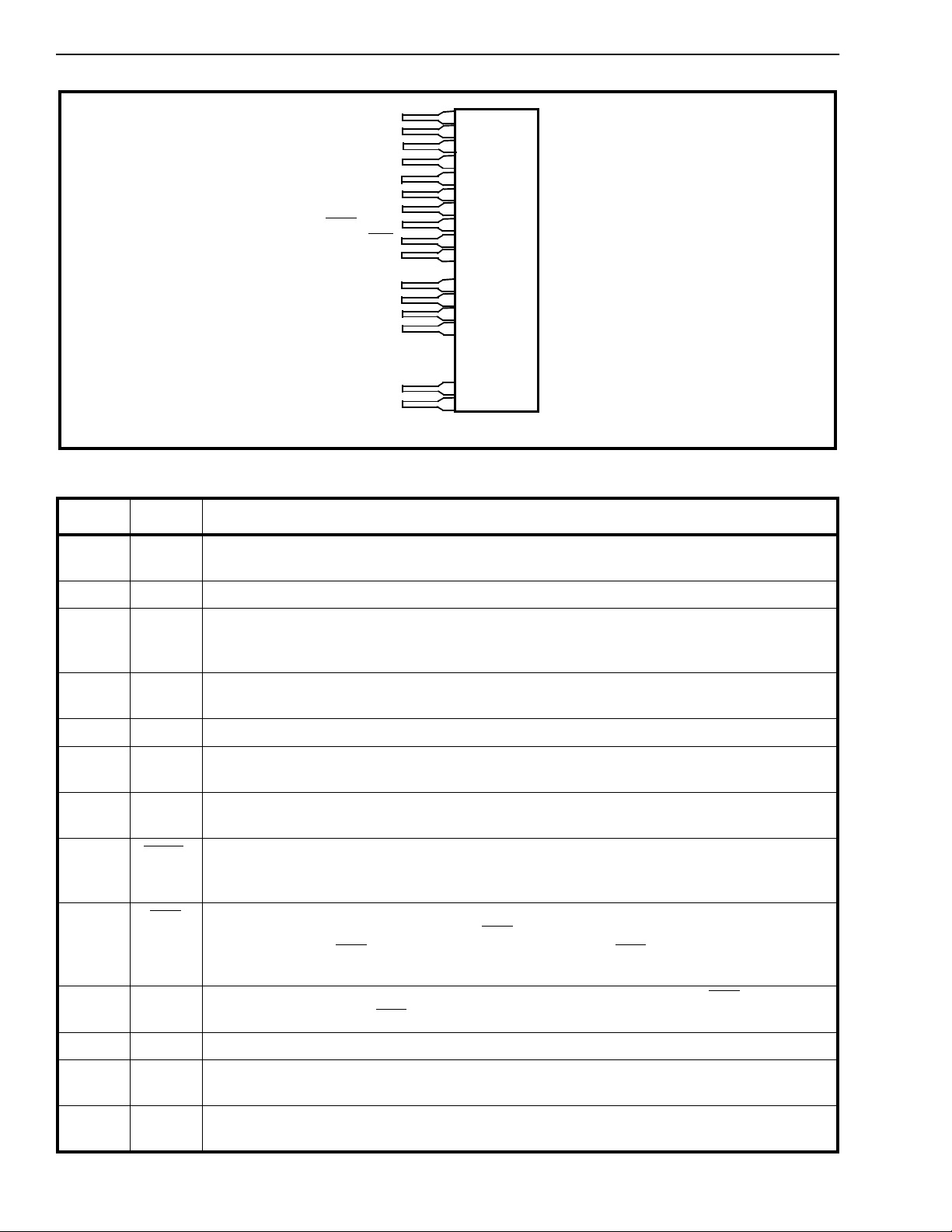

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

CLKF

E2o

VDD

RxA

RxB

VSS

RxD

RxINV

/CLKR

LOS

LOSP

NC

RLA

RLB

TLA

TLB

NC

NC

NC

TxA

TxB

Figure 2 - Pin Connections

Pin Description

Pin # Name Description

1E2o2048kHz Extracted clock (Output). This clock is extracted by the device from the received

signal. It is used internally to clock in data received from RLA and RLB.

2V

D.C. Power (In pu t) +5V supply

DD

3RxAReceiver A (Output ). The bipolar CEPT signal received by the device at RLA and RLB

inputs is converted to a unipolar format and output at this pin. This pin should be connected

to the positive receive pin of the framer.

4RxBReceiver A (Output). This pin should be connect ed to the negati ve receive gain pin of the

framer and provides a signal of the same format as RxA.

5V

Ground (Input). D.C. power return path.

SS

6RxDReceiv ed Data (Outp ut) This unipolar return to zero format signal is the product of RxA

and RxB logically “OR” ed and is required by some framers.

7RxINVRxA/RxB inversion (Input). A logic low applied to this pin will invert the outputs RxA and

RxB. A logic high should be applied if no inversion is required.

8

CLKF/

CLKR

E2o phase selecti on is achieved by use of this pin. A logic low provides E2o with a

falling edge coinciding with the centre of the data bit. A logic high provides E2o with a rising

edge.

9

LOS

Loss of signal (Output). This pin goes low when 128 continuous zeros are received on the

RLA and RLB inputs. When RxINV and LOS

RxINV is high and LOS

is low RxA and RxB are forced low. LOS is reset when 64 ones are

are low RxA and RxB are forced high. When

received in two dual E1 framer periods.

10 LOSP Loss of signal Polarity (Input). A logic low applied to this pin will invert LOS. A logic high

should be applied when LOS

is required.

11 NC No connection. This pin is not fitted.

12 RLA Received Li ne A (In put). The A wire or Tip Connection of the E1 receive line should be

connected to this pin.

13 RLB Receive Line B (Input). The B wire or Ring connection of the E1 receive line should be

connected to this pin.

4-224

Loading...

Loading...