miscellaneous ct8 0413 d3b Service Manual

1

2

3

4

5

6

7

8

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

A A

LAYER 4 : IN2

LAYER 5 : VCC

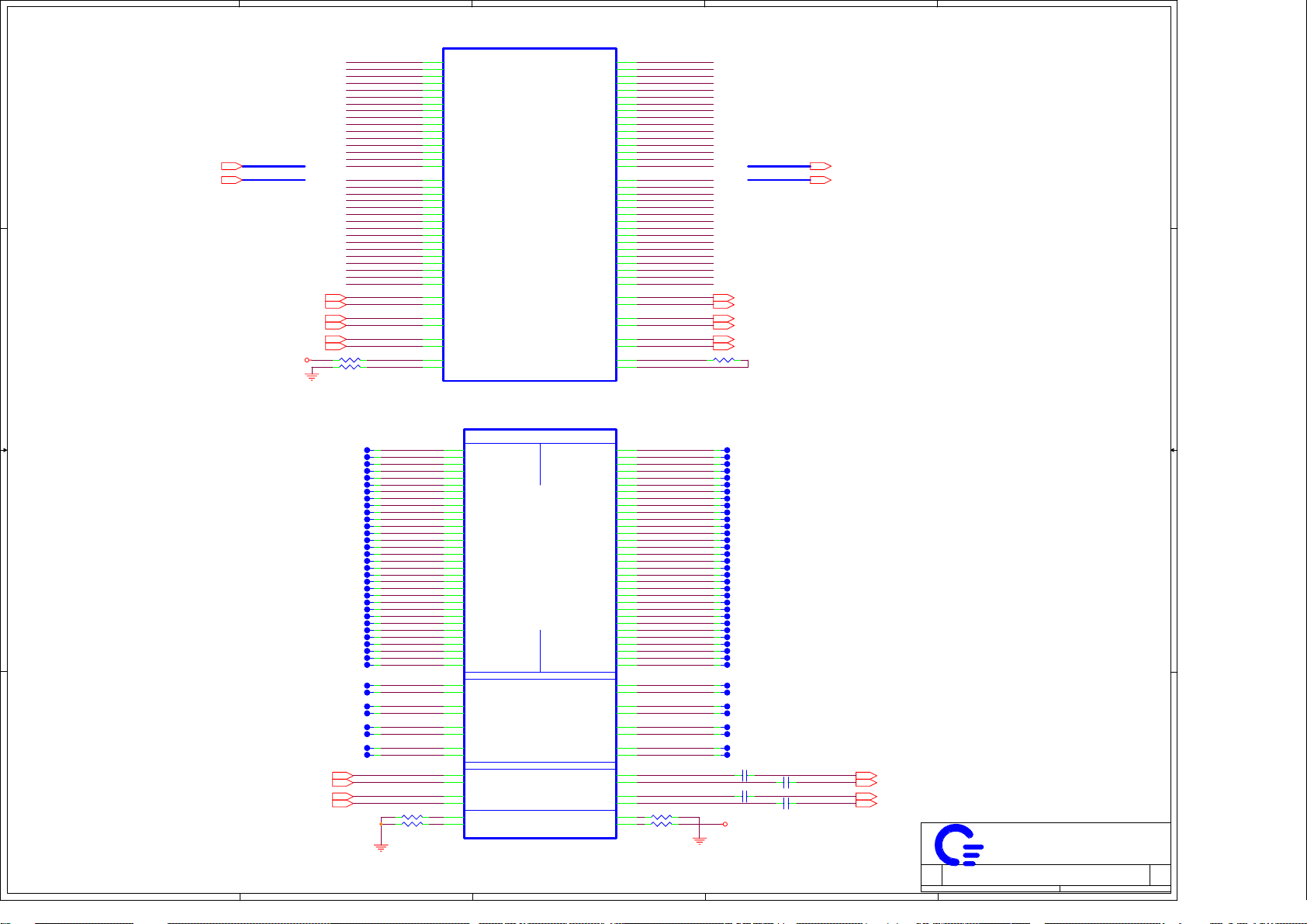

DDR-SODIMM1

DDR-SODIMM2

DDR

266,333,400MHz

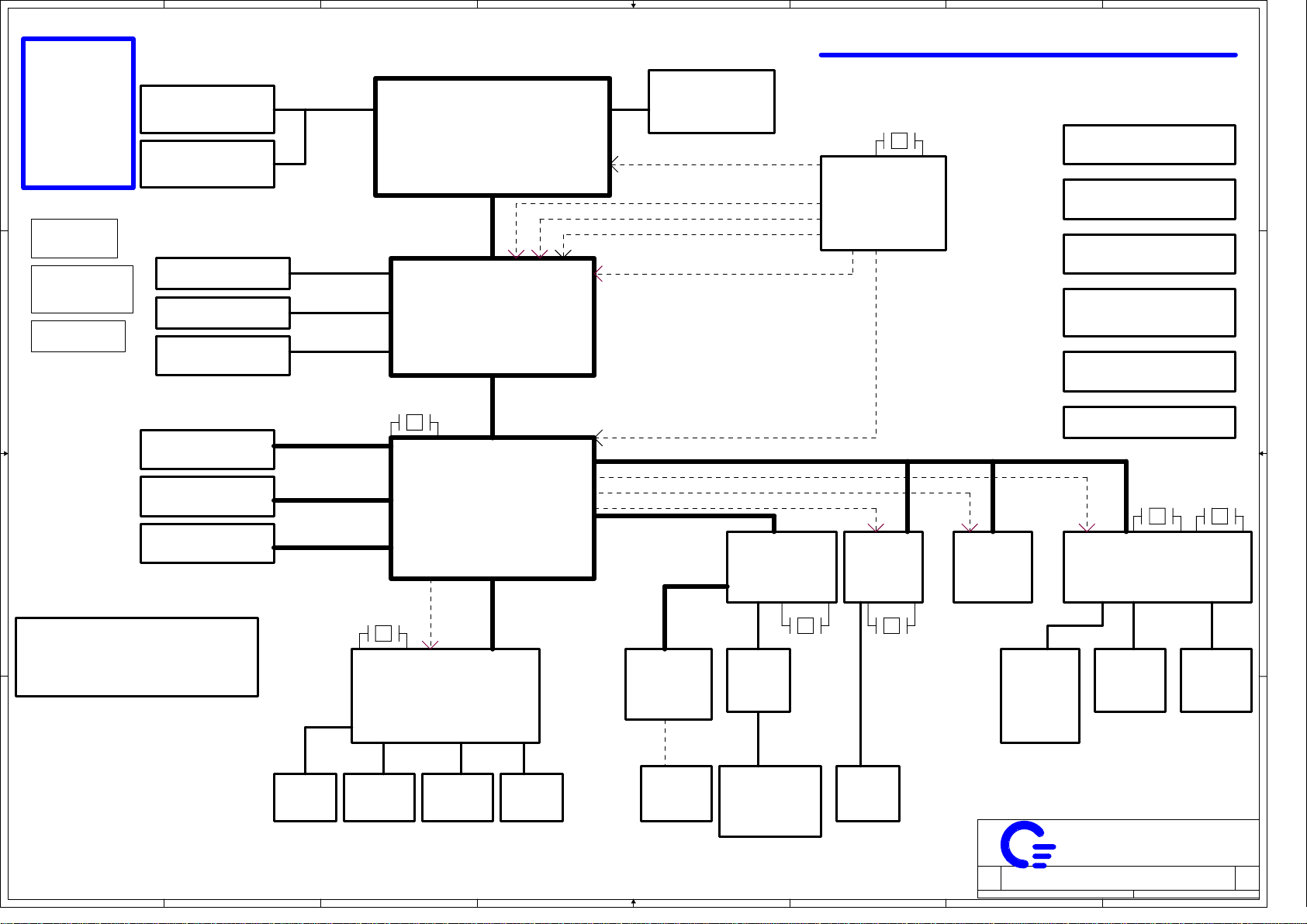

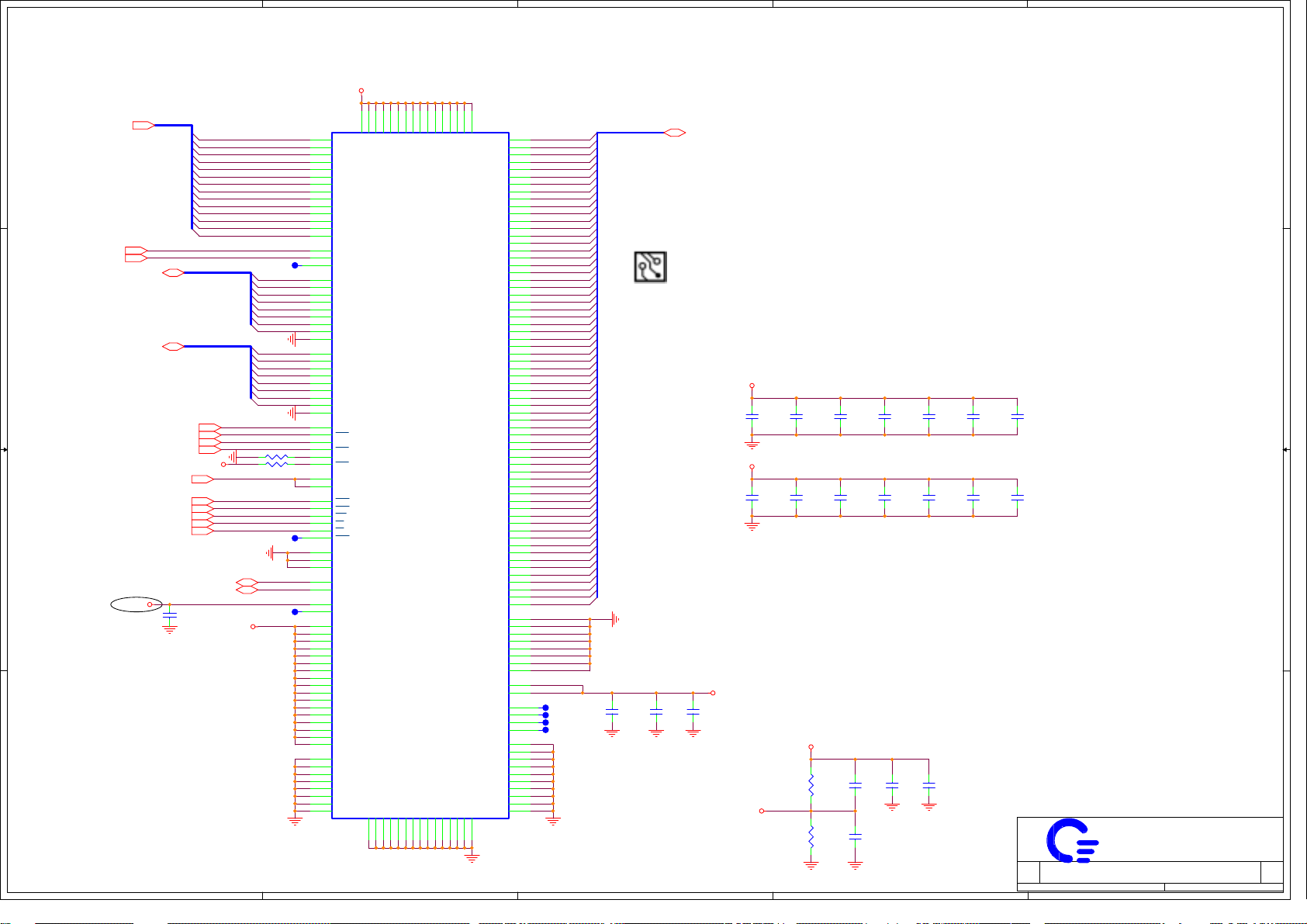

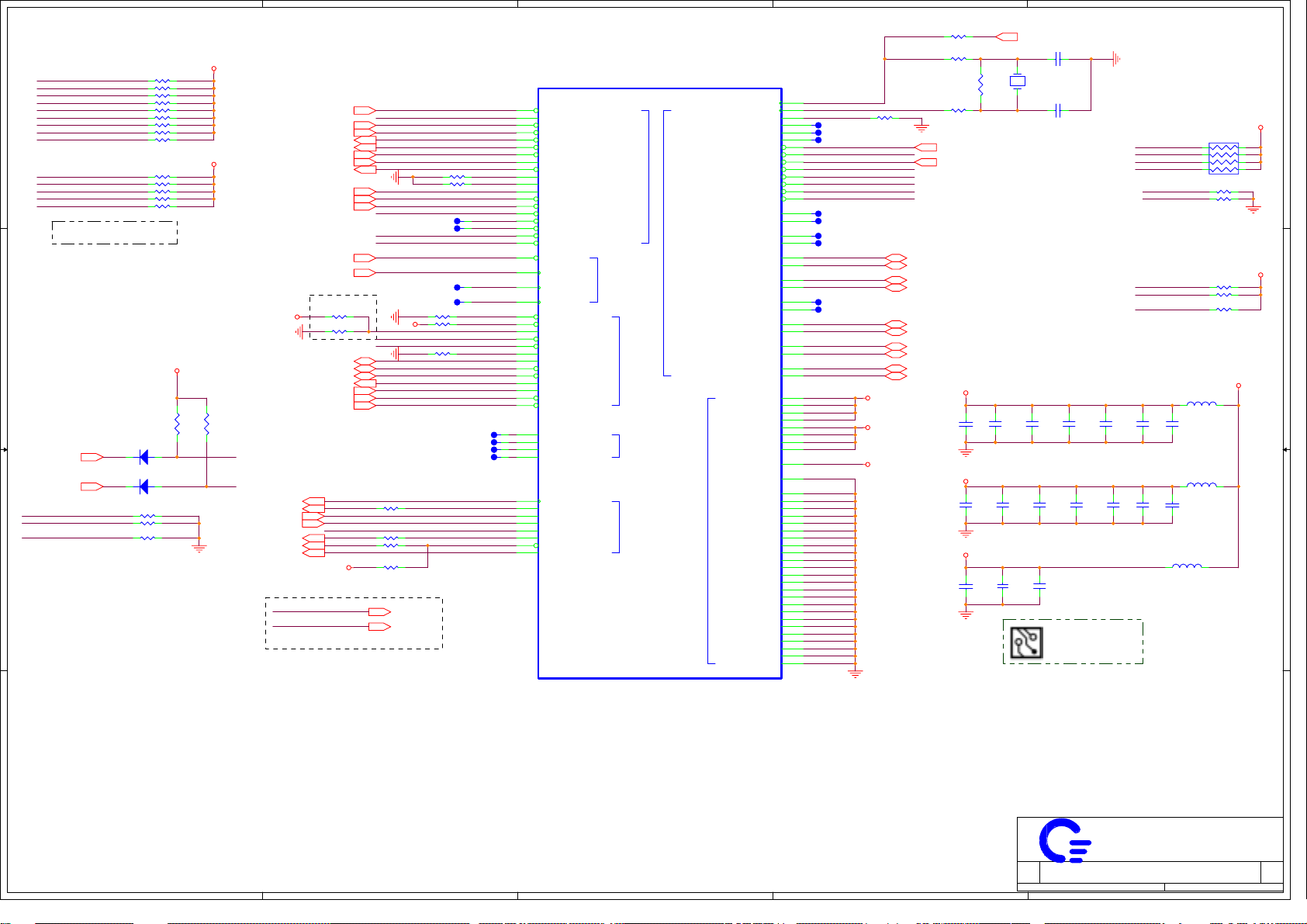

CPU CLAW HAMMER

754 Pins (uPGA)

CPU THERMAL

SENSOR

GMT-781

CPUCLK,

CPUCLK#

LAYER 6 : BOT

SBLINKCLK, SBLINKCLK#

HyperThansport I/O BUS

CABLE DOCK

Daughter Board

TV, USB, BLUE TOOTH

CRT port

LCD Panel

Power Board

B B

S-VIDEO

R.G,B

LVDS X1

TV-OUT

Link 16x16

NORTH BRIDGE

RS480M

705 BGA

INTEGRADED VGA FUNCTION

Based on Redeon 9600

NBSRCCLK, NBSRCCLK#

HTREFCLK

OSC14M

A-LINK

32.768KHz

USB PORT 0, 1, 2

1st IDE - HDD

2nd IDE - CDROM

C C

USB 2.0

ATA 66/100/133

ATA 66/100/133

2X

PCI-E

SB400

564 BGA

NBSRCCLK, NBSRCCLK#

33MHZ, 3.3V PC I

PCLK_7411

PCLK_MINI

PCLK_LAN

AC97

PWRCLKP

PWRCLKN

DIB_DATAN

DIB_DATAP

AC97

CX20468-31

MBAMC20493-010

CT8 BLOCK DIAGRAM

CLAW HAMMER / RS480 / SB400

14.318MHz

CLOCK GEN

CY28RS480/ ICS951412

LAN

Realtek

8100CL

MINI-PCI

SYSTEM POWER MAX1845

(1.2V/NB_CORE/1.25V)

CPU CORE MAX1544

POWER 1.2V

SYSTEM MAX1999

POWER(3/5V)

SYSTEM POWER MAX1845

(2.5VSUS/1.8VSUS)

BATT CHARGER

MAX1722

DISCHARGE

24.576MHz

CARDBUS / IEEE 1394

CONTROLLER/CF

48MHz

TI 7411

PCI DEVICES IRQ ROUTING

DEVICE

GBIT ETHERNET

MINIPCI SLOT

CardBus/1394

IDSEL #

AD16

AD18

AD25

REQ/GNT #

32.768KHz

PCLK_591

3.3V LPC, 33MHz

24.576MHz

PCI_INT

2

1

4

C

E,F

B,D,G

PC97551

SMARTDAA

MODEM,

AMP

TPA0312

TQFP 176

25MHz

5 IN 1

CARD

READER

SD/MMC,

SM, MS,

XD

CARDBUS

SLOT X1

1394

CONN

WIRE

D D

FAN

Touchpad

Keyboard

FLASH

RJ11

JACK

JACK

HEADPHONE,

2ND HEADPHONE,

MIC

RJ45

JACK

PROJECT : CT8

Quanta Computer Inc.

Size Document Number Rev

1

2

3

4

5

6

Date: Sheet

7

BLOCK DIAGRAM

of

142Thursday, April 14, 2005

8

1ACustom

5

4

3

2

1

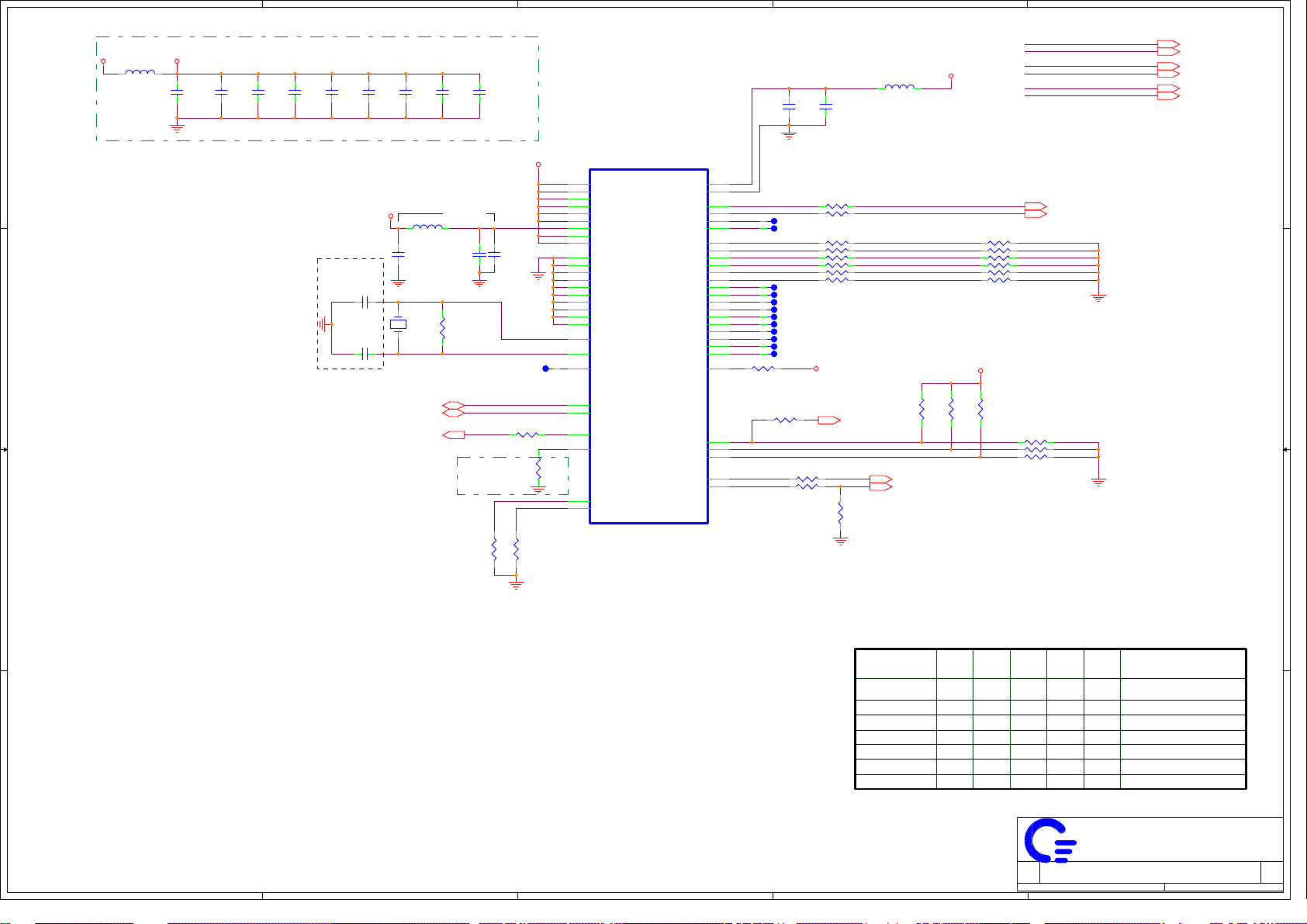

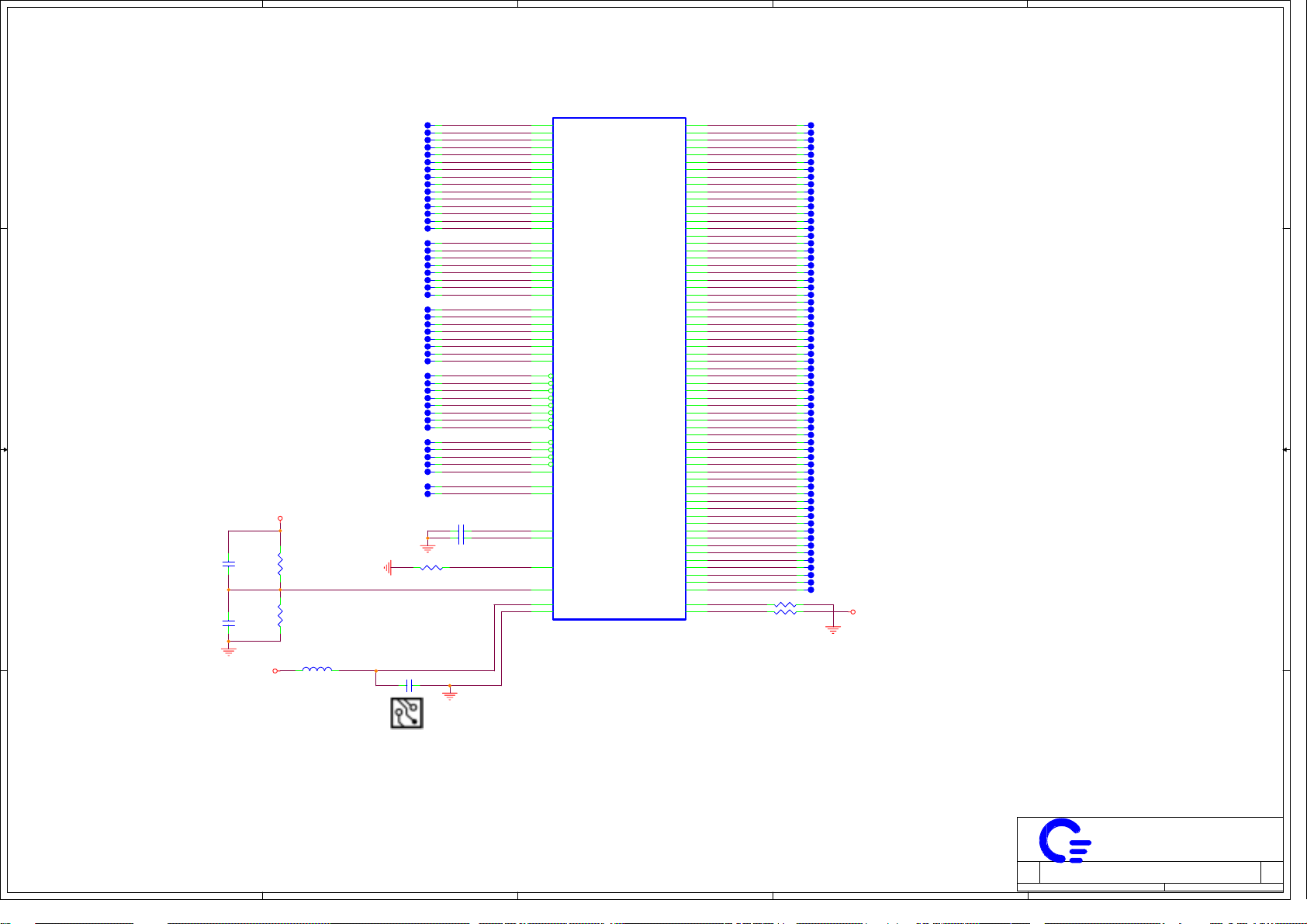

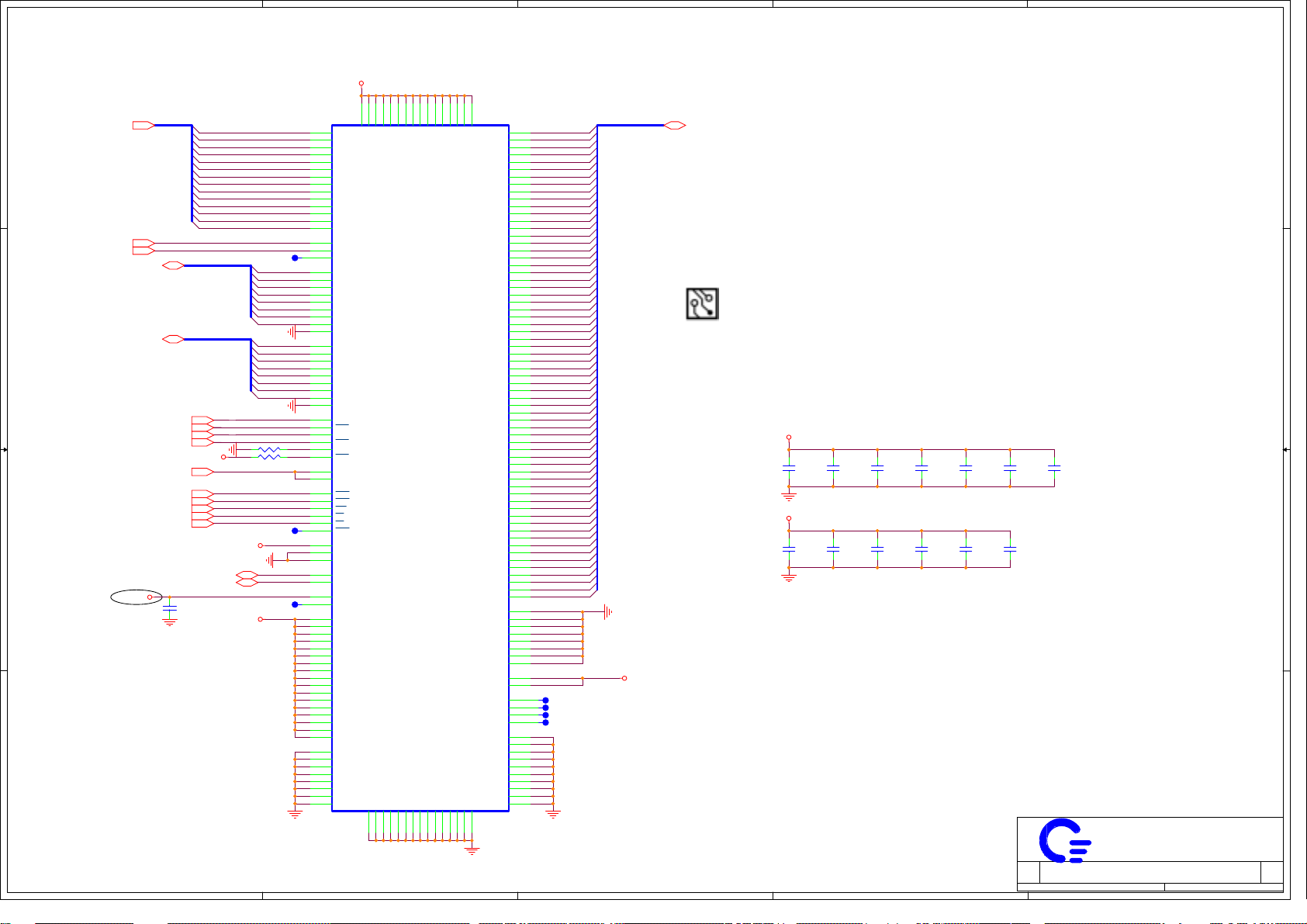

CLK FREQ

SELECT

NBSRCCLK

NBSRCCLK#

SBSRCCLK

SBSRCCLK#

SBLINKCLK

SBLINKCLK#

CPUCLK 3

CPUCLK# 3

CLK

D D

C C

B B

+3V

L39

CLK_VDD

TI201209G121

C478

22U

20 Mils

C485

0.1U

Parallel Resonance Crystal

Tolerance: 35ppm (max)

Load: 20pf

C497

0.1U

C496

0.1U

C488

0.1U

REV.B

C320 27P

C479 27P

C483

C480

0.1U

0.1U

EMI

+3V

SBK160808T-301Y-S

L40

C749

0.1U

Y2

2 1

14.318MHZ

1.Remove R84.

SCLK9,10,13

SDATA9,10,13

OSC14M7

C498

C491

0.1U

0.1U

REV.C

C482

2.2U

R83

*1M

REV.B

R281 33

Ioh = 5 * Iref

(2.32mA)

Voh = 0.71V @ 60 ohm

R292

*10K

C750

0.1U

CLK_VDD

T296

R282

*10K

U23

43

VDDCPU

14

VDDSRC3

21

VDDSRC2

32

VDDSRC1

35 44

VDD_SRC0 CPUCLK8C0

51

VDD_PCI

3

VDD48

48

VDDHTT

56

VDDREF

5

GND1

55

GND2

36

GNDSRC0

31

GNDSRC1

26

GNDSRC2

20

GNDSRC3

15

GNDSRC4

49

GNDPCI

46

GNDHTT

42

GNDCPU

1

X1

2

X2

R304

475/F

6

7

8

52

37

11

10

ICS951412

NC

SCLK

SDATA

REF2

IREF

CLKREQB#

CLKREQA#

SEL75#/100/PCICLK0

Operating Current: 400mA

VDDA

GNDA

CPUCLK8T0

CPUCLK8T1

CPUCLK8C1

SRCCLKT7

SRCCLKC7

SRCCLKT6

SRCCLKC6

SRCCLKT5

SRCCLKC5

SRCCLKT4

SRCCLKC4

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT1

SRCCLKC1

SRCCLKT0

SRCCLKC0

FS0/REF0

FS1/REF1

USB_48MHz

HTTCLK0

R274

10K

+3V

R277

10K

R285 49.9/F

R289 49.9/F

R295 49.9/F

R297 49.9/F

R300 49.9/F

R302 49.9/F

CLK_VDD

R276

10K

R275 *10K

R280 *10K

R279 *10K

T128

T297

T131

T299

T301

T306

T305

T302

T304

T303

T298

T300

R273 *22

R278 33

R284 33

40 Mils

C492

0.1U

R288 15/F

R291 15/F

R286 33

R290 33

R296 33

R298 33

R301 33

R303 33

C494

22U

CLK_VDD

SB_OSC_INT 7,13

R287

51.1

L42

TI201209G121

SBSRCCLK

SBSRCCLK#

NBSRCCLK

NBSRCCLK#

SBLINKCLK

SBLINKCLK#

USBCLK_EXT 13

HTREFCLK 7

CLK_VDDA

39

38

CPUCLK8T0

45

CPUCLK8C0

41

40

SRCCLKT7

12

SRCCLKC7

13

SRCCLKT6

16

SRCCLKC6

17

SRCCLKT5

18

SRCCLKC5

19

22

23

24

25

27

28

30

29

34

33

R283 *4.7K

50

54

53

9

FS2

4

47

NBSRCCLK 7

NBSRCCLK# 7

SBSRCCLK 12

SBSRCCLK# 12

SBLINKCLK 7

SBLINKCLK# 7

Layout Note:

1- PLACE ALL THE SERIES TERMINATION RESISTORS AS CLOSE AS

CKG. AS POSSIBLE

2- ROUTE ALL CPUCLK/#, NBSRCCLK/#, SBSRCCLK/#, SBLINKCLK/# AS

DIFFERENT PAIR RULE

3- PUT DECOUPLING CAPS CLOSE TO CKG. POWER PIN

A A

EXT CLK FREQUENCY SELECT TABLE(MHZ)

FS2

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 1

CPUFS1

Hi-Z

X

180.00

220.00

100.00

133.33

200.00

SRCCLK

[2:1]

100.00

100.00

100.00

100.00

100.00

100.00

100.00

HTTFS0 PCI

Hi-Z Hi-Z

X/6X/3

30.0060.00

36.56 73.12

66.66 33.33

66.66 33.33

66.66 33.33

USB

COMMENT

48.00

Reserved

48.00

Reserved

48.00

Reserved

48.00

Reserved

48.00

Reserved

48.00

Reserved

48.00

Normal HAMMER operation

PROJECT : CT8

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

EXT CLOCK GENERATOR

1

242Thursday, April 14, 2005

3ACustom

of

5

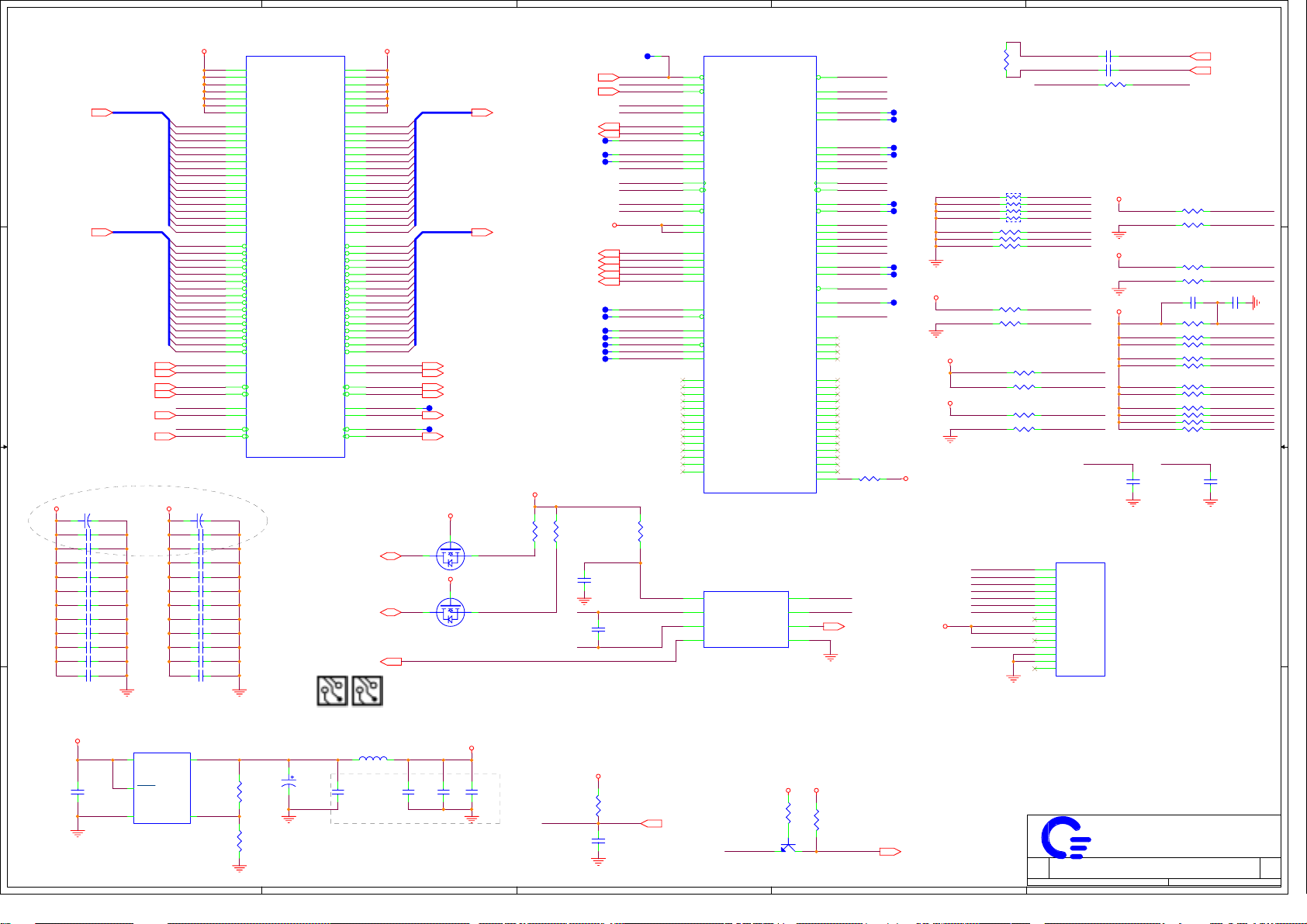

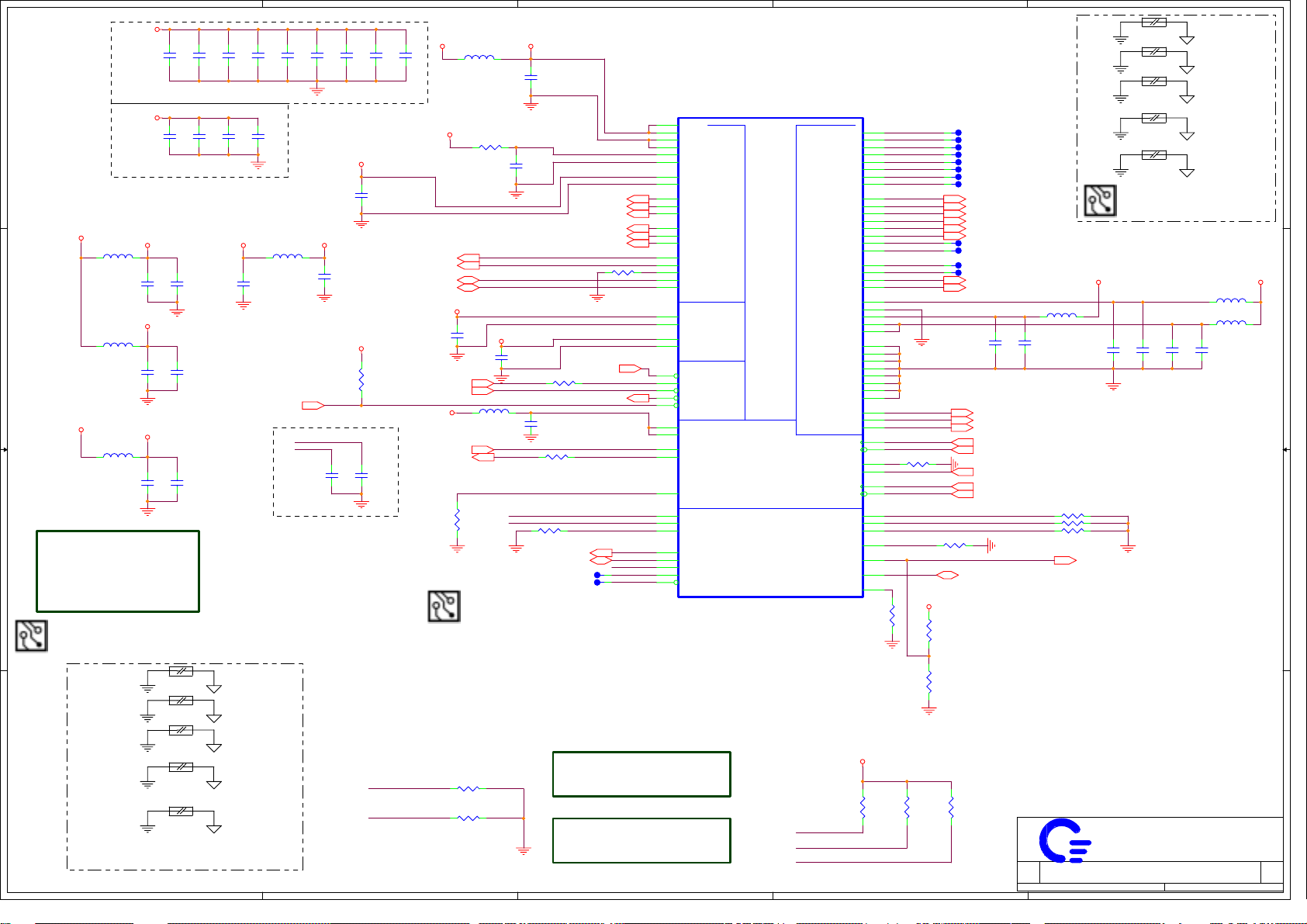

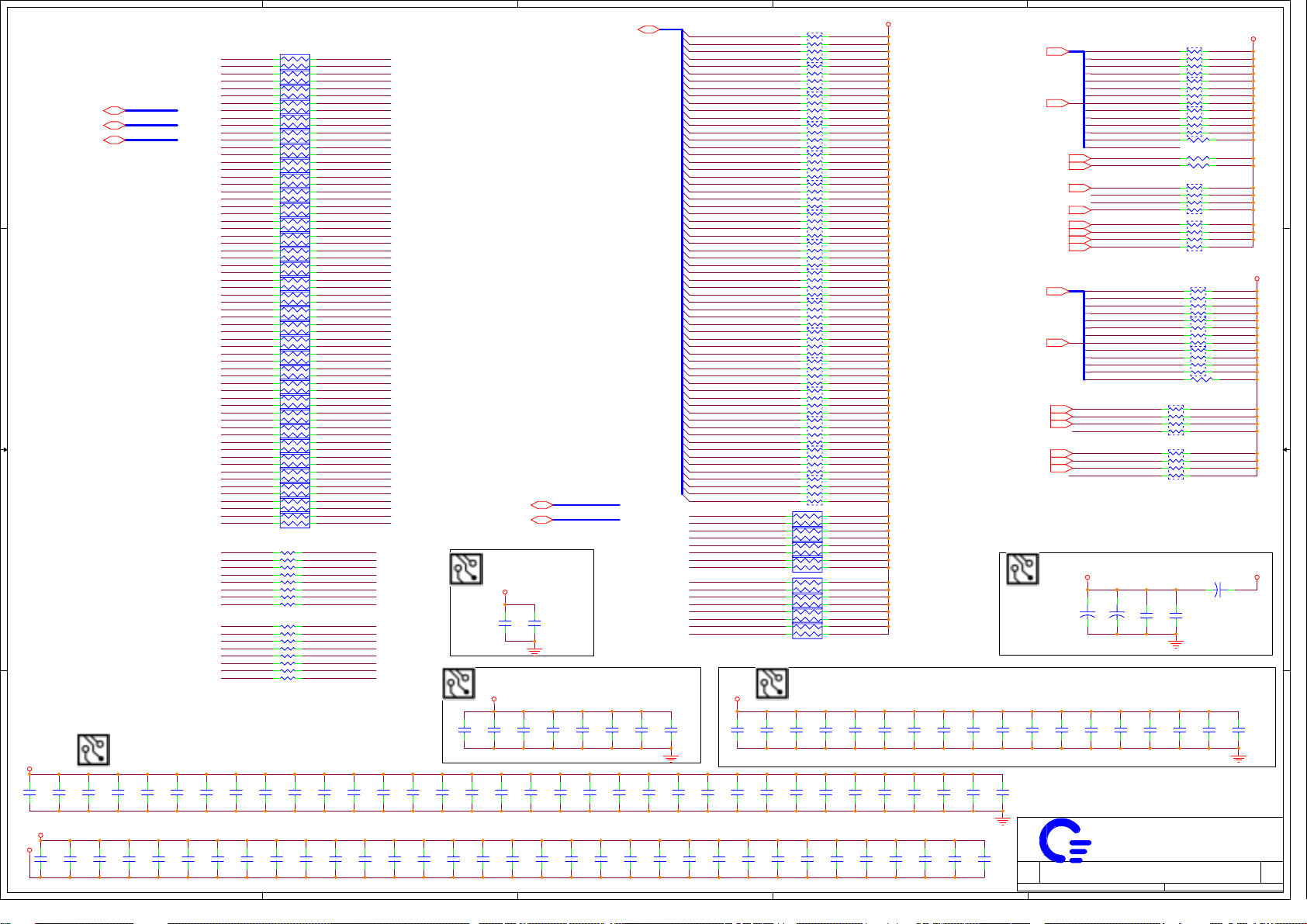

CPU

D D

C C

B B

A A

CADIP[0..15]5

CADIN[0..15]5

add c154,c283,c284,c285 4.7u

c9,c277 100u change to 220u

VDDA_1V2 VDDA_1V2

C277 220U/6.3V

50 Mils, routing as 15 mils width if the

distance from bead to cpu pin less than 1000

mils.

C308

10U/10V

CADIP[0..15]

CADIN[0..15]

CLKIP15

CLKIP05

CLKIN15

CLKIN05

CTLIP05

CTLIN05

+

C154 4.7U

C285 4.7U

C161 4.7U

C146 4.7U

C141 0.22U

C465 0.22U

C473 0.22U

C466 0.22U

C469 0.22U

C117 0.22U

C119 0.22U

+3V VDDA_2.5V

1 2

U6

3 4

VIN VOUT

1

SHDN

2

GND

G923

5

VDDA_1V2

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP2

CADIP1

CADIP0

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

CLKIP1

CLKIP0

CLKIN1

CLKIN0

CTLIP1

CTLIP0

CTLIN1

CTLIN0

C9 220U

C284 4.7U

C283 4.7U

C168 4.7U

C286 4.7U

C126 0.22U

C470 0.22U

C175 0.22U

C171 0.22U

C184 0.22U

C187 0.22U

C472 0.22U

SET

U22A

AMD K8

V_HT0_A0

V_HT0_A1

V_HT0_A2

V_HT0_A3

V_HT0_A4

V_HT0_A5

V_HT0_A6

HT_RXD15

HT_RXD14

HT_RXD13

HT_RXD12

HT_RXD11

HT_RXD10

HT_RXD9

HT_RXD8

HT_RXD7

HT_RXD6

HT_RXD5

HT_RXD4

HT_RXD3

HT_RXD2

HT_RXD1

HT_RXD0

HT_RXD#15

HT_RXD#14

HT_RXD#13

HT_RXD#12

HT_RXD#11

HT_RXD#10

HT_RXD#9

HT_RXD#8

HT_RXD#7

HT_RXD#6

HT_RXD#5

HT_RXD#4

HT_RXD#3

HT_RXD#2

HT_RXD#1

HT_RXD#0

HT_RXCLK1

HT_RXCLK0

HT_RXCLK#1

HT_RXCLK#0

HT_RXCTL1

HT_RXCTL0

HT_RXCTL#1

HT_RXCTL#0

LDT

HT_TXCLK#1

HT_TXCLK#0

HT_TXCTL#1

HT_TXCTL#0

V_HT0_B0

V_HT0_B1

V_HT0_B2

V_HT0_B3

V_HT0_B4

V_HT0_B5

V_HT0_B6

HT_TXD15

HT_TXD14

HT_TXD13

HT_TXD12

HT_TXD11

HT_TXD10

HT_TXD9

HT_TXD8

HT_TXD7

HT_TXD6

HT_TXD5

HT_TXD4

HT_TXD3

HT_TXD2

HT_TXD1

HT_TXD0

HT_TXD#15

HT_TXD#14

HT_TXD#13

HT_TXD#12

HT_TXD#11

HT_TXD#10

HT_TXD#9

HT_TXD#8

HT_TXD#7

HT_TXD#6

HT_TXD#5

HT_TXD#4

HT_TXD#3

HT_TXD#2

HT_TXD#1

HT_TXD#0

HT_TXCLK1

HT_TXCLK0

HT_TXCTL1

HT_TXCTL0

W27

AA27

AB25

AC27

AD25

AB29

AB27

AD29

AD27

W26

AA26

AA25

AC26

AC25

W29

AA29

AB28

AC29

AD28

W25

B27

B29

C26

C28

D25

D27

D29

T25

U27

V25

T27

V29

V27

Y29

R25

U26

U25

T28

U29

V28

Y25

Y27

Y28

R27

T29

R26

R29

REV.B

+

1999_RST#37

Output current(Max):

300mA

REV.C

12

Ra

C311

R80

5

100K/F

R79

2. Change C311 from 10u to 100u,

remove C304.

100K/F

Rb

C721

100U/6.3V

REV.B

Vout=1.25(1+Ra/Rb)

Ra=Rb(Vout/1.25-1)

100P

AF25

AE28

AF29

AG26

AG28

AH27

AH29

N26

L25

L26

J25

G25

G26

E25

E26

N29

M28

L29

K28

H28

G29

F28

E29

N27

M25

L27

K25

H25

G27

F25

E27

P29

M27

M29

K27

H27

H29

F27

F29

J26

J29

J27

K29

N25

P28

P25

P27

MBDATA30,36

MBCLK30,36

VDDA_1V2

CADOP15

CADOP14

CADOP13

CADOP12

CADOP11

CADOP10

CADOP9

CADOP8

CADOP7

CADOP6

CADOP5

CADOP4

CADOP3

CADOP2

CADOP1

CADOP0

CADON15

CADON14

CADON13

CADON12

CADON11

CADON10

CADON9

CADON8

CADON7

CADON6

CADON5

CADON4

CADON3

CADON2

CADON1

CADON0

CLKOP1

CLKOP0

CLKON1

CLKON0

CTLOP1

CTLOP0

CTLON1

CTLON0

L21

TI201209G121

REV.B

4

20 Mils width to pin

100 Mils width to capacitor

250 Mils width to PWM

CADOP[0..15]

CADON[0..15]

CLKOP1 5

CLKOP0 5

CLKON1 5

CLKON0 5

T101

CTLOP0 5

T102

CTLON0 5

+3V

2

Q28 2N7002E

3

Q8 2N7002E

3

C722

4.7U

4

3300P

+3V

C723

1

2

1

C724

0.22U

CADOP[0..15] 5

CADON[0..15] 5

R32

10K

THDAT_SMB

+3V

LDT_RST#12

LDTSTOP#7,12

COREFB40

COREFB#40

R35

10K

CPUPWRGD

ESD

REV.D

T96

T120

VDDA_2.5V

VID040

VID140

VID240

VID340

VID440

JTAG6

JTAG7

JTAG5

JTAG1

JTAG2

JTAG4

JTAG3

6657VCC

C111

.1U/16V/0402

+2.5V

3

T124

LDT_RST#

CPUPWRGD

LDTSTOP#

L0_REF1

L0_REF0

COREFB

COREFB#

VDDIO_SENSE

CPU_CLK

CPU_CLK#

FBCLKOUT

FBCLKOUT#

VID0

VID1

VID2

VID3

VID4

DBRDY

DBREQ#

TMS

TCK

TRST#

TDI

TDO

R38

100/F

AF20

AE18

AJ27

AF27

AE26

AE12

AF12

AE11

AJ21

AH21

AH19

AJ19

AH25

AJ25

AE15

AF15

AG14

AF14

AG13

AH17

AE19

A23

A24

B23

E20

E17

B21

A21

A22

A25

B13

B18

C20

C23

C24

U22C

AMD K8

RESET#

PWROK

HT_STOP#

L0_REF1

L0_REF0

COREFB

COREFB#

CORE_SENSE

VDDIOFB

VDDIOFB#

VDDIO_SENSE

CLKIN

CLKIN#

FBCLKOUT

FBCLKOUT#

VDDA1

VDDA2

VID0

VID1

VID2

VID3

VID4

DBRDY

DBREQ#

TMS

TCK

TRST#

TDI

TDO

NC_A25

B7

NC_B7

NC_B13

NC_B18

C1

NC_C1

C3

NC_C3

C6

NC_C6

C9

NC_C9

NC_C20

NC_C23

NC_C24

D3

NC_D3

F3

NC_F3

J3

NC_J3

CTL & DBG

NC_SCANCLK1

NC_SCANCLK2

NC_SCANSHENB

NC_SCANSHENA

NC_RSVD_SCL

NC_RSVD_SDA

NC_DCLKTWO

NC_ANALOG0

NC_ANALOG1

NC_ANALOG2

NC_ANALOG3

THERMTRIP#

THERMDA

THERMDC

NC_BP3

NC_BP2

NC_BP1

NC_BP0

NC_BPSCLK

NC_BPSCLK#

NC_PLLCHZ

NC_PLLCHZ#

NC_SCANEN

NC_BRN#

NC_SINCHN

NC_K1

NC_R2

NC_R3

NC_AA2

NC_AA3

NC_AE9

NC_AE21

NC_AE22

NC_AG2

NC_AG4

NC_AG6

NC_AG7

NC_AG9

NC_AH1

NC_AF18

H/W MONITOR

U18

1

THERMDATHCLK_SMB THDAT_SMB

C431

2200P/50V

THERMDC

R257

680

C766

*.1U

3

VCC

2

DXP

3

DXN

4 5

-OVT GND

MAX6657/GMT-781

CPUPWRGD 12

SMCLK

SMDATA

-ALT

1.Remove R386,Q33, connect

U18 pin 6 to TEMP_ALARM#.

+2.5V

2

THERMTRIP#

1 3

Q14

MMBT3904

8

7

6

KEY0

KEY1

R89

1K

A20

A26

A27

AJ28

A28

AG18

AH18

AG17

AJ18

AJ23

AH23

AE24

AF24

D20

C21

D18

C19

B19

D22

C22

A19

C15

C18

AF21

AF22

AF23

AE23

K1

R2

R3

AA2

AA3

AE9

AE21

AE22

AG2

AG4

AG6

AG7

AG9

AH1

AF18

THCLK_SMB

3V_S5

R86

10K

THERM_CPUDIE#

THERMTRIP#

THERMDA

THERMDC

NC_AG17

NC_AJ18

NC_AJ23

NC_AH23

NC_D20

NC_C21

NC_C19

NC_B19

NC_A19

NC_C18

R77 0

TEMP_ALARM# 13

REV.B

2

R76

169/F

T294

T97

T118

T295T121

680-8P4R

RN1

1

2

3

T122

T123

T93

T82

STUFF WHEN CONFIGURED AS 16-BIT LINK

VDDA_1V2

T68

2.5VSUS

+2.5V

THERM_CPUDIE# 13,30

2

2.5VSUS

2.5VSUS

R56 49.9/F

R57 49.9/F

DBREQ#

DBRDY

TCK

TMS

TDI

TRST#

TDO

LDT_RST#

4

5

6

7

8

R34 680

R265 680

R256 680

R40 *680

R66 51.1

R259 820

R267 820

Size Document Number Rev

Date: Sheet

Near Socket754

CTLIP1

CTLIN1

TDO

VDDIO_SENSE

CON1

1

DBREQ_L

2

DBRDY

3

TCK

4

TMS

5

TDI

6

TRST_L

7

TDO

8

+2.5V

9

+2.5V

KEY-NC

RES

RES

RES

RES

RES

*HDT

C295 3900P

C296 3900P

R78 80.6/F

NC_AJ23

NC_AH23

REV.B

CPU_CLK

CPU_CLK#

FBCLKOUT#

NC_D20

NC_C19

NC_B19

NC_C21

NC_D18

NC_AG17NC_D18

NC_AJ18

10

10

11

12

13

14

1

CPUCLK 2

R42 51

R41 51

R262 44.2/F

R261 44.2/F

C762

*330p

R268 680

R260 680

R90 680

R48 680

R49 680

R258 *680

R266 *680

R33 *680

R54 *680

R50 *680

R46 *680

DBREQ#

ESD

REV.D

CPUCLK# 2

C765

*.1U

VCC_CORE

VDDA_1V2

+2.5V

NC_A19

ESD

REV.D

FBCLKOUT

REV.D

ESD

C764

*.1U

PROJECT : CT8

Quanta Computer Inc.

CPU H.T/CTL I/F

1

342Thursday, April 14, 2005

COREFB

COREFB#

L0_REF1

L0_REF0

C763

*330p

LDT_RST#

LDTSTOP#

THERMTRIP#

NC_A19

NC_C18

DBREQ#

DBRDY

TCK

TMS

TDI

TRST#

of

3ACustom

5

4

3

2

1

2.5VSUSVCC_CORE

VDD93

VDD94

VDD95

VDD96

VDD97

VDD98

VDD99

D5

D7

D9

D11

D13

D15

E4

F6

F8

F10

F12

F14

F16

G4

G7

G9

H6

H8

J4

J7

K6

L4

M6

N4

P6

R4

T6

U4

V6

W4

Y6

AA4

AA7

AB6

AB8

AC4

AC7

AC9

AD6

AD8

AD10

AD12

AD14

AD16

AE4

AF5

AF7

AF9

AF11

AF13

Y12

Y14

Y16

Y18

Y20

Y22

Y24

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AA28

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AB24

AB26

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD18

AD20

AD22

AD24

AE17

AE25

AE27

AG19

2.5VSUS

+

C148 220U

+

C163 220U

REV.B

C178 *4.7U

C177 *4.7U

C182 4.7U

C180 4.7U

C179 4.7U

C314 4.7U

C181 4.7U

C313 4.7U

C258 1U

C262 1U

C268 1U

C324 0.22U

C226 0.22U

C336 0.22U

C299 0.22U

C166 0.22U

C176 0.22U

C288 0.1U

C307 0.1U

C247 1U

C272 1U

VCC_CORE

VCC_CORE

PROJECT : CT8

Quanta Computer Inc.

Size Document Number Rev

Date: Sheet

CPU DDR/POWER I/F

1

+

C267 330U

+

C225 330U

+

C243 330U

REV.B

C451 4.7U

C207 4.7U

C456 4.7U

C237 4.7U

C444 4.7U

C238 4.7U

C457 4.7U

C223 4.7U

C224 4.7U

C208 4.7U

C450 4.7U

C445 4.7U

C248 0.22U

C240 0.22U

C192 0.22U

C229 0.22U

C190 0.22U

C256 0.22U

C253 0.22U

C448 0.22U

C454 0.22U

C194 0.1U

C254 0.1U

C193 0.1U

C216 0.1U

C205 0.1U

C244 0.1U

C231 0.1U

C206 0.1U

C245 0.1U

C222 0.1U

C257 0.1U

C199 0.1U

C455 0.1U

C215 0.1U

C198 0.1U

C232 0.1U

C255 0.1U

C200 0.1U

C234 0.1U

C214 0.1U

C447 0.1U

C246 0.1U

C191 0.1U

C213 0.1U

of

442Thursday, April 14, 2005

2ACustom

AF16

AG15

AG16

AH16

AJ17

AG10

AG12

N3

N1

U3

V1

N2

P1

U1

U2

D8

C8

E8

E7

D6

E6

C4

E5

AE7

AE8

C10

D10

E11

E12

AG8

AF8

AE10

AF10

V4

V3

K4

K5

P5

R5

P4

P3

K3

H3

H5

D4

G5

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

L5

J5

H4

F5

F4

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

2.5VSUS

2.5VSUS

VTT_DDR

MEMRST#

1.25VREF

CS#7

CS#6

CS#5

CS#4

CS#3

CS#2

CS#1

CS#0

CKE1

CKE0

DCLK#7

DCLK7

DCLK#6

DCLK6

DCLK#5

DCLK5

DCLK#4

DCLK4

DCLK#3

DCLK3

DCLK#2

DCLK2

DCLK#1

DCLK1

DCLK#0

DCLK0

MEMBAA1

MEMBAA0

RAS#A

CAS#A

WE#A

MAA15

MAA14

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MEMBAB1

MEMBAB0

RAS#B

CAS#B

WE#B

MAB15

MAB14

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

20 mils width to CPU pins.

T119

T289

T288

T109

T107

T287

T290

T106

T108

T87

T79

T94

T89

CS#3 10,11

CS#2 10,11

CS#1 9,11

CS#0 9,11

DCLK#7 9

DCLK7 9

DCLK#6 10

DCLK6 10

DCLK#5 9

DCLK5 9

DCLK#4 10

DCLK4 10

T111

T110

T99

T100

MEMBAA1 9,11

MEMBAA0 9,11

RAS#A 9,11

CAS#A 9,11

WE#A 9,11

T86

T95

MEMBAB1 10,11

MEMBAB0 10,11

RAS#B 10,11

CAS#B 10,11

WE#B 10,11

T98

T75

DCLK#7

DCLK#6

DCLK#5

DCLK#4

CKE0

CKE1

MD[63..0]

DQS[7..0]

DM[7..0]

MAA[13..0]

MAB[13..0]

3

R53 120/F

R52 120/F

R69 120/F

R75 120/F

DCLK7

DCLK6

DCLK5

DCLK4

LAYOUT: Place close to CPU.

CKE0 9,11

CKE1 10,11

MD[63..0] 11

DQS[7..0] 11

DM[7..0] 11

MAA[13..0] 9,11

MAB[13..0] 10,11

2.5VSUS

R254

100/F

R255

100/F

C468

0.1U

C475

0.1U

C471

1000P

W/S 15/20 mils

C467

0.01U

1.25VREF

C474

*100P

U22D

AMD K8

POWER

B20

VDD1

B24

VDD2

D24

VDD3

E19

VDD4

E21

VDD5

E23

VDD6

E28

VDD7

F18

VDD8

F20

VDD9

F22

VDD10

F24

VDD11

F26

VDD12

G11

VDD13

G13

VDD14

G15

VDD15

G17

VDD16

G19

VDD17

G21

VDD18

G23

VDD19

H10

VDD20

H12

VDD21

H14

VDD22

H16

VDD23

H18

VDD24

H20

VDD25

H22

VDD26

H24

VDD27

J9

VDD28

J11

VDD29

J13

VDD30

J15

VDD31

J17

VDD32

J19

VDD33

J21

VDD34

J23

VDD35

J28

VDD36

K8

VDD37

K10

VDD38

K12

VDD39

K14

VDD40

K16

VDD41

K18

VDD42

K20

VDD43

K22

VDD44

K24

VDD45

K26

VDD46

L7

VDD47

L9

VDD48

L21

VDD49

L23

VDD50

M8

VDD51

M10

VDD52

M20

VDD53

M22

VDD54

M24

VDD55

N7

VDD56

N9

VDD57

N21

VDD58

N23

VDD59

N28

VDD60

P8

VDD61

P10

VDD62

P20

VDD63

P22

VDD64

P24

VDD65

P26

VDD66

R7

VDD67

R9

VDD68

R21

VDD69

R23

VDD70

T8

VDD71

T10

VDD72

T20

VDD73

T22

VDD74

T24

VDD75

U7

VDD76

U9

VDD77

U21

VDD78

U23

VDD79

U28

VDD80

V8

VDD81

V10

VDD82

V20

VDD83

V22

VDD84

V24

VDD85

V26

VDD86

W7

VDD87

W9

VDD88

W21

VDD89

W23

VDD90

Y8

VDD91

Y10 AH24

VDD92 VDD133

2

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

C292

0.22U

VTT_DDR

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

60 mils

C293

4.7U

CPU

U22E

AMD K8

GROUND

B2

VSS1

B4

VSS2

B6

VSS3

B8

VSS4

B10

VSS5

D D

C C

B B

A A

B12

VSS6

B14

VSS7

B16

VSS8

B22

VSS9

B25

VSS10

B26

VSS11

B28

VSS12

C25

VSS13

C27

VSS14

C29

VSS15

D2

VSS16

D16

VSS17

D19

VSS18

D21

VSS19

D23

VSS20

D26

VSS21

D28

VSS22

E15

VSS23

E16

VSS24

E18

VSS25

E22

VSS26

E24

VSS27

F2

VSS28

F7

VSS29

F9

VSS30

F11

VSS31

F13

VSS32

F15

VSS33

F17

VSS34

F19

VSS35

F21

VSS36

F23

VSS37

G6

VSS38

G8

VSS39

G10

VSS40

G12

VSS41

G14

VSS42

G16

VSS43

G18

VSS44

G20

VSS45

G22

VSS46

G24

VSS47

G28

VSS48

H2

VSS49

H7

VSS50

H9

VSS51

H11

VSS52

H13

VSS53

H15

VSS54

H17

VSS55

H19

VSS56

H21

VSS57

H23

VSS58

H26

VSS59

J6

VSS60

J8

VSS61

J10

VSS62

J12

VSS63

J14

VSS64

J16

VSS65

J18

VSS66

J20

VSS67

J22

VSS68

J24

VSS69

K2

VSS70

K7

VSS71

K9

VSS72

K11

VSS73

K13

VSS74

K15

VSS75

K17

VSS76

K19

VSS77

K21

VSS78

K23

VSS79

L6

VSS80

L8

VSS81

L10

VSS82

L20

VSS83

L22

VSS84

L24

VSS85

L28

VSS86

M2

VSS87

M7

VSS88

M9

VSS89

M21

VSS90

M23

VSS91

M26

VSS92

N6

VSS93

N8

VSS94

N10

VSS95

N20

VSS96

N22

VSS97

N24

VSS98

P2

VSS99

P7

VSS100

P9

VSS101

P21

VSS102

P23

VSS103

R6

VSS104

R8

VSS105

R10

VSS106

R20

VSS107

R22

VSS108

R24

VSS109

5

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

R28

T2

T7

T9

T21

T23

T26

U6

U8

U10

U20

U22

U24

V2

V7

V9

V21

V23

W6

W8

W10

W20

W22

W24

W28

Y2

Y7

Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

Y26

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA24

AB2

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC6

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AC28

AD2

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD21

AD23

AD26

AE14

AE16

AE20

AE29

AF2

AF17

AF19

AF26

AF28

AG20

AG21

AG22

AG23

AG24

AG25

AG27

AG29

AH2

AH4

AH6

AH8

AH10

AH12

AH14

AH20

AH22

AH26

AH28

AJ20

AJ22

AJ24

AJ26

VTT_SENSE41

T104

T103

VTT_DDR

C142

0.22U

U22B

AMD K8

A18

B17

C16

C17

D17

AE13

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

B9

C7

A6

C11

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

AC1

AC3

W2

Y1

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

R1

A13

A7

C2

H1

AA1

AG1

AH7

AH13

T1

A14

A8

D1

J1

AB1

AJ2

AJ8

AJ13 M3

C139

4.7U

MEMORY

VTT_A1

VTT_A2

VTT_A3

VTT_A4

VTT_A5

VTT_SENSE

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0 MEMADDB0

DCLK#1

DCLK#0

DCLK0

DCLK1

MEMZN

MEMZP

4

VTT_B1

VTT_B2

VTT_B3

VTT_B4

VTT_B5

MEMRESET#

MEMVREF1

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

MEMCS#7

MEMCS#6

MEMCS#5

MEMCS#4

MEMCS#3

MEMCS#2

MEMCS#1

MEMCS#0

MEMCKEB

MEMCKEA

MEMCLK#7

MEMCLK7

MEMCLK#6

MEMCLK6

MEMCLK#5

MEMCLK5

MEMCLK#4

MEMCLK4

MEMCLK#3

MEMCLK3

MEMCLK#2

MEMCLK2

MEMCLK#1

MEMCLK1

MEMCLK#0

MEMCLK0

MEMBANKA1

MEMBANKA0

MEMRASA#

MEMCASA#

MEMWEA#

NC_MEMADDA15

NC_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMBANKB1

MEMBANKB0

MEMRASB#

MEMCASB#

MEMWEB#

NC_MEMADDB15

NC_MEMADDB14

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

R58 10K

R59 10K

R60 10K

R62 10K

R45 34.8/F

R47 34.8/F

5

4

3

2

1

Link 0 Is Clawhammer <--> RS4 80

CLG

CADOP15

CADON15

CADOP14

CADON14

CADOP13

CADON13

CADOP12

CADON12

D D

CADOP[0..15]3

CADON[0..15]3

C C

CADOP[0..15]

CADON[0..15]

VDDA_1V2

CLKOP13

CLKON13

CLKOP03

CLKON03

CTLOP03

CTLON03

R233 49.9/F

R234 49.9/F

CADOP11

CADON11

CADOP10

CADON10

CADOP9

CADON9

CADOP8

CADON8

CADOP7

CADON7

CADOP6

CADON6

CADOP5

CADON5

CADOP4

CADON4

CADOP3

CADON3

CADOP2

CADON2

CADOP1

CADON1

CADOP0

CADON0

HT_RXCALP

HT_RXCALN

W25

W24

AA25

AA24

AB26

AA26

AC25

AC24

AD26

AC26

W30

AB29

AA29

AC29

AC28

W26

W29

W28

T26

R26

U25

U24

V26

U26

R29

R28

T30

R30

T28

T29

V29

U29

Y30

Y28

Y29

Y26

P29

N29

D27

E27

U17A

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALN

HT_RXCALP

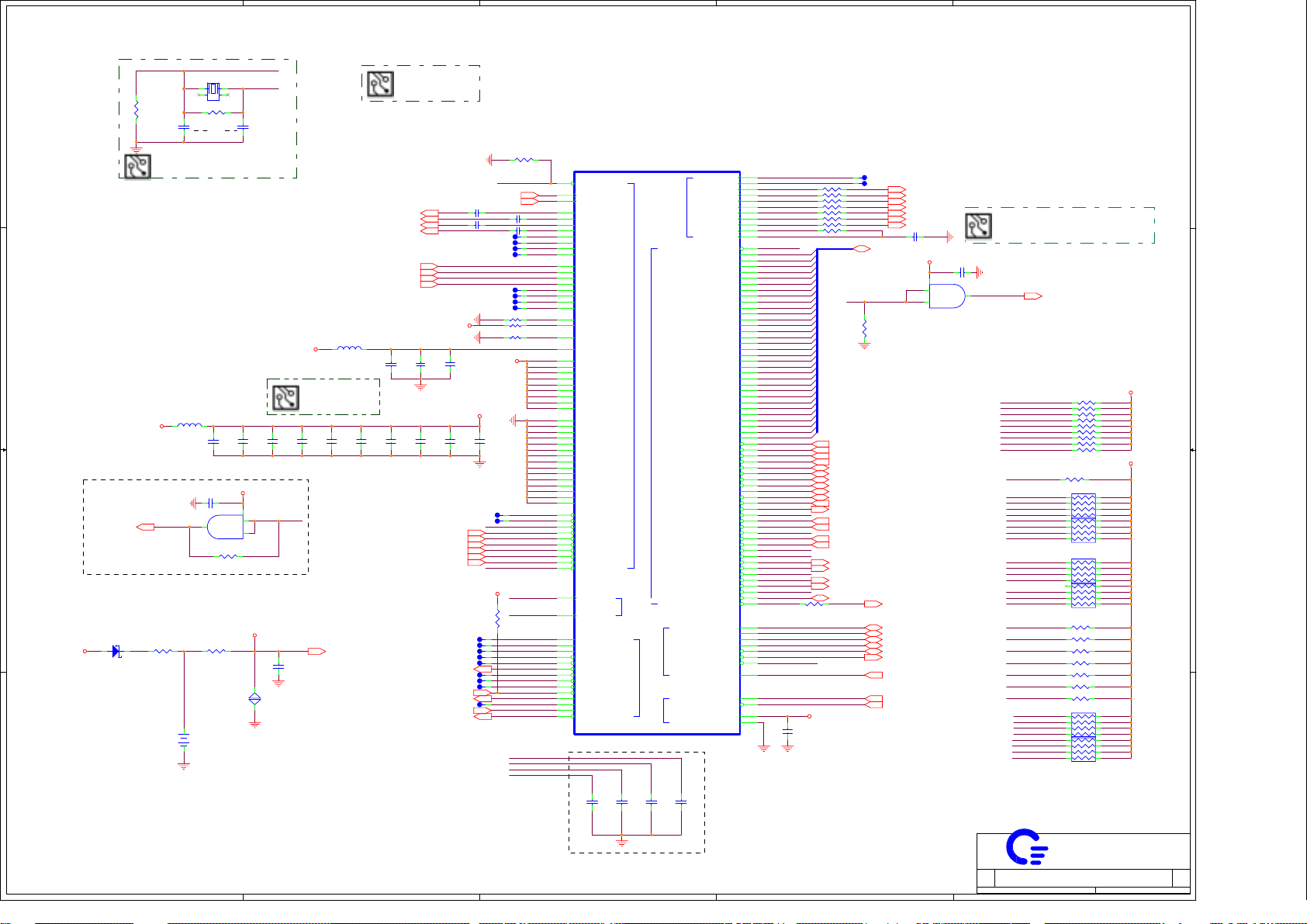

RS480M

PART 1OF6

HYPER TRANSPORT CPU

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

I/F

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

CADIP15

R24

CADIN15

R25

CADIP14

N26

CADIN14

P26

CADIP13

N24

CADIN13

N25

CADIP12

L26

CADIN12

M26

CADIP11

J26

CADIN11

K26

CADIP10

J24

CADIN10

J25

CADIP9

G26

CADIN9

H26

CADIP8

G24

CADIN8

G25

CADIP7

L30

CADIN7

M30

CADIP6

L28

CADIN6

L29

CADIP5

J29

CADIN5

K29

CADIP4

H30

CADIN4

H29

CADIP3

E29

CADIN3

E28

CADIP2

D30

CADIN2

E30

CADIP1

D28

CADIN1

D29

CADIP0

B29

CADIN0

C29

L24

L25

F29

G29

M29

M28

B28

A28

HT_TXCALP

HT_TXCALN

R235 100/F

CLKIP1 3

CLKIN1 3

CLKIP0 3

CLKIN0 3

CTLIP0 3

CTLIN0 3

CADIP[0..15]

CADIN[0..15]

CADIP[0..15] 3

CADIN[0..15] 3

U17B

T32

T226

T219

T211

T206

T185

T15

T183

T170

T18

T7

T16

T197

T184

T29

T196

B B

A A

T177

T201

T22

T166

T168

T10

T38

T37

T178

T194

T23

T13

T19

T11

T341

T337

T193

T190

T173

T172

T339

T165

T9

T204

A_RX0P12

A_RX0N12 A_TX0N 12

A_RX1P12

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

A_RX0P

A_RX0N

A_RX1P

A_RX1N

R14 10K/F

R16 8.25K/F

D8

D7

D5

D4

E4

F4

G5

G4

H4

J4

H5

H6

G1

G2

K5

K4

L4

M4

N5

N4

P4

R4

P5

P6

P2

R2

T5

T4

U4

V4

W1

W2

AE1

AE2

AB2

AC2

AB5

AB4

Y4

AA4

AG1

AH1

AC5

AC6

AH3

AJ3

REV.B

REV.C REV.C

RS480M

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

PCE_ISET

PCE_TXISET

PART 2 OF 6

PCIE I/F TO

VIDEO

PCIE I/F TO SLOT

PCIE I/F TO SB

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

PCE_PCAL

PCE_NCAL

A7

B7

B6

B5

A5

A4

B3

B2

C1

D1

D2

E2

F2

F1

H2

J2

J1

K1

K2

L2

M2

M1

N1

N2

R1

T1

T2

U2

V2

V1

Y2

AA2

AD2

AD1

AA1

AB1

Y5

Y6

W5

W4

AF2

AG2

AC4

AD4

R9 150/F

AH2

R12 82.5/F

AJ2

GFX_TX0P_C

GFX_TX0N_C

GFX_TX1P_C

GFX_TX1N_C

GFX_TX2P_C

GFX_TX2N_C

GFX_TX3P_C

GFX_TX3N_C

GFX_TX4P_C

GFX_TX4N_C

GFX_TX5P_C

GFX_TX5N_C

GFX_TX6P_C

GFX_TX6N_C

GFX_TX7P_C

GFX_TX7N_C

GFX_TX8P_C

GFX_TX8N_C

GFX_TX9P_C

GFX_TX9N_C

GFX_TX10P_C

GFX_TX10N_C

GFX_TX11P_C

GFX_TX11N_C

GFX_TX12P_C

GFX_TX12N_C

GFX_TX13P_C

GFX_TX13N_C

GFX_TX14P_C

GFX_TX14N_C

GFX_TX15P_C

GFX_TX15N_C

GPP_TX0P_C

GPP_TX0N_C

GPP_TX1P_C

GPP_TX1N_C

GPP_TX2P_C

GPP_TX2N_C

GPP_TX3P_C

GPP_TX3N_C

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

T228

T227

T225

T221

T220

T218

T214

T213

T210

T208

T207

T202

T200

T198

T181

T199

T180

T179

T195

T167

T169

T182

T176

T192

T164

T191

T175

T5

T203

T187

T189

T186

T163

T171

T188

T174

T17

T25

T31

T12

VDDA_1V2

C16

0.1U

C14

0.1U

C17

0.1U

C15

0.1U

A_TX0P 12

A_TX1P 12

A_TX1N 12A_RX1N12

PROJECT : CT8

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RS480M-HT A-LINK0

1

542Thursday, April 14, 2005

3ACustom

of

CLG

5

4

3

2

1

D D

C C

+2.5V

B B

C62

0.1U

C72

0.1U

R29

1K

R30

1K

T57

T246

T241

T51

T262

T260

T62

T256

T255

T253

T248

T52

T56

T245

T249

T88

T278

T80

T266

T235

T44

T231

T30

T83

T284

T65

T270

T238

T46

T216

T28

T265

T283

T71

T268

T236

T42

T215

T27

T50

T250

T53

T254

T58

T244

T243

R31 1K

MEM_VREF

Side-Port not used

MEM_VREF to 2.5VSUS

C130 0.47U

C23 0.47U

Stuff

MEMAA0

MEMAA1

MEMAA2

MEMAA3

MEMAA4

MEMAA5

MEMAA6

MEMAA7

MEMAA8

MEMAA9

MEMAA10

MEMAA11

MEMAA12

MEMAA13

MEMAA14

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

QSP0

QSP1

QSP2

QSP3

QSP4

QSP5

QSP6

QSP7

M_QSN0

M_QSN1

M_QSN2

M_QSN3

M_QSN4

M_QSN5

M_QSN6

M_QSN7

RASA#

CASA#

WEA#

CSA#0

M_CKEA

M_CLKA0

M_CLKA#0

MEM_CAP1

MEM_CAP2

MEM_VMODE

AF17

AK17

AH16

AF16

AJ22

AJ21

AH20

AH21

AK19

AH19

AJ17

AG16

AG17

AH17

AJ18

AG26

AJ29

AE21

AH24

AH12

AG13

AH8

AE8

AF25

AH30

AG20

AJ25

AH13

AF14

AG8

AG25

AH29

AF21

AK25

AJ12

AF13

AK7

AF9

AE17

AH18

AE18

AJ19

AF18

AK16

AJ16

AE28

AJ20

AK20

AJ15

AJ14

AJ7

AJ4

U17C

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_DQS0P

MEM_DQS1P

MEM_DQS2P

MEM_DQS3P

MEM_DQS4P

MEM_DQS5P

MEM_DQS6P

MEM_DQS7P

MEM_DQS0N

MEM_DQS1N

MEM_DQS2N

MEM_DQS3N

MEM_DQS4N

MEM_DQS5N

MEM_DQS6N

MEM_DQS7N

MEM_RAS#

MEM_CAS#

MEM_WE#

MEM_CS#

MEM_CKE

MEM_CKP

MEM_CKN

MEM_CAP1

MEM_CAP2

MEM_VMODE

MEM_VREF

MPVDD

MPVSS

RS480M

PART 3 OF 6

MEM_A I/F

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_COMPP

MEM_COMPN

AF28

AF27

AG28

AF26

AE25

AE24

AF24

AG23

AE29

AF29

AG30

AG29

AH28

AJ28

AH27

AJ27

AE23

AG22

AF23

AF22

AE20

AG19

AF20

AF19

AH26

AJ26

AK26

AH25

AJ24

AH23

AJ23

AH22

AK14

AH14

AK13

AJ13

AJ11

AH11

AJ10

AH10

AE15

AF15

AG14

AE14

AE12

AF12

AG11

AE11

AJ9

AH9

AJ8

AK8

AH7

AJ6

AH6

AJ5

AG10

AF11

AF10

AE9

AG7

AF8

AF7

AE7

AH5

AD30

MEM_COMPP

MEM_COMPN

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

R22 *61.9/F

R43 *61.9/F

T279

T81

T85

T84

T78

T77

T73

T76

T281

T286

T280

T277

T282

T276

T275

T274

T69

T70

T72

T67

T74

T64

T66

T61

T273

T272

T271

T269

T267

T263

T264

T261

T242

T36

T239

T240

T232

T237

T234

T233

T48

T47

T49

T45

T41

T40

T35

T39

T230

T229

T222

T223

T224

T212

T209

T205

T26

T20

T33

T34

T217

T21

T14

T24

+2.5V

L5

+1.8V

TI201209G121

Side-Port not used

MPVDD to 1.8V

MPVDD_PLL

C45

1U

Decouple to MPVSS near the ball

A A

PROJECT : CT8

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RS480M-SIDE PORT MEM I/F

1

642Thursday, April 14, 2005

1ACustom

of

5

EMI

REV.B

EMI

REV.B

TI201209G121

TI201209G121

150/F

REV.C

+3V

+1.8V

AVDDQ

PLLVDD

HTPVDD

C137

10U

C56

10U

PLLVSS

C138

10U

JOINT

JOINT

JOINT

JOINT

JOINT

C711

0.1U

C717

0.1U

C120

1U

AVSSQ

C37

1U

C121

1U

HTPVSS

C712

0.1U

C718

0.1U

AVSSN

AVSSQ

AVSSDI

PLLVSS

HTPVSS

C713

0.1U

C719

0.1U

L18

C143

10U

AVSSN

C714

0.1U

C720

0.1U

TI201209G121

SUS_STAT#13

C715

0.1U

C158

1U

NB_PWRGD_R

LDTSTOP#

REV.B

REV.C

EMI

C716

0.1U

AVSSQ

+2.5VAVDD

REV.B

ESD

REV.D

C740

*330p

CLG

D D

+1.8V

L16

C C

B B

A A

L6

+1.8V

L17

DAC VDD (2.5V)

AVDD

DIGITAL VDD (1.8V)

AVDDDI

DAC2 BANDGAP REF (1.8V)

AVDDQ

PLL VDD (1.8V)

PLLVDD

HT PLL VDD (1.8V)

HTPVDD

PUT AVDD, AVDDDI, AVDDQ,PLVDD,HTPVDD

DECOUPLING CAPS ON THEBOTTOM, CLOSE

TO BALLS

DO NOT SHARE GND VIA ON JOINT

5

AVDDQ

+1.8V

C745

0.1U

C746

0.1U

(1.8V)

C102

1U

R17

4.7K

C741

1000P

LOAD_ROM#

SPMEM_EN#

4

C747

0.1U

+3V

L14

*BK2125HS220

AVDD

40 mils

(2.5V)

C118

1U

AVSSN

+1.8V

R36 0

20 mils20 mils

AVDDDI

C98

1U

AVSSDI

VSYNC31

HSYNC31

DDCCLK31

DDCDAT31

PLLVSS

SB_OSC_INT2,13

+3V

PWROK18,30

LDTSTOP#3,12

PLLVDD

OSC14M2

20 mils

(1.8V)

C51

HTPVDD

1U

(1.2V)

C90

TI201209G121

R221

10K

1U

R404 0

C44

R26 22

SPMEM_EN#

LOAD_ROM#

R227 *3K

1U

HTPVSS

L3

ROUTING H_THRMDA AND HW_AGND AS DIFFERENTIAL PAIR

R37 715/F

20 mils

NB_RST#12,34

NB_PWRGD_R

ALLOW_LDTSTOP12

VDDR3

RS480_TVCLKIN

BMREQ#12

EDIDCLK18 POWER_PLAY

T6

T8

REV.B DEL Y1 AND U3 CIRCUIT.

LOAD_ROM#:LOAD ROM STRAP ENABLE strap

High, LOAD ROM STRAP DISABLE

R27 *3K

R28 *3K

Low, LOAD ROM STRAP ENABLE

SPMEM_EN#:SIDE PORT MEMORY ENABLE strap

NC, SIDE PORT MEMORY DISABLE

Low, SIDE PORT MEMORY ENABLE

4

S-CD132

S-YD132

S-CVBS132

CRT_R31

CRT_G31

CRT_B31

SB_OSC_INT_R

DFT_GPIO2

EDIDCLK

I2C_DATA

3

3

U17D

B27

AVDD1

C27

AVDD2

D26

AVSSN1

D25

AVSSN2

C24

AVDDDI

B24

AVSSDI

E24

AVDDQ

D24

AVSSQ

B25

C

A25

Y

A24

COMP

C25

RED

A26

GREEN

B26

BLUE

A11

DAC_VSYNC

B11

DAC_HSYNC

C26

RSET

E11

DAC_SCL

F11

DAC_SDA

A14

PLLVDD

B14

PLLVSS

M23

HTPVDD

L23

HTPVSS

D14

SYSRESET#

B15

POWERGOOD

B12

LDTSTOP#

C12

ALLOW_LDTSTOP

AH4

SUS_STAT#

H13

VDDR3_1

H12

VDDR3_2

A13

OSCIN

B13

OSCOUT

B9

TVCLKIN

F12

DFT_GPIO0/RSV

E13

DFT_GPIO1/RSV

D13

DFT_GPIO2/RSV

F10

BMREQb

C10

I2C_CLK

C11

I2C_DATA

AF4

THERMALDIODE_P

AE4

THERMALDIODE_N

RS480M

PART 4 OF 6

CRT/TVOUT

PLL PWR

PM

CLOCKs

DFT_GPIO3/RSV

DFT_GPIO4/RSV

DFT_GPIO5/RSV

MIS.

EDIDCLK

I2C_DATA

EDIDDATA

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

TXCLK_UP

TXCLK_UN

TXCLK_LP

LVDS

TXCLK_LN

LPVDD

LPVSS

LVDDR18D

LVDDR18A_1

LVDDR18A_2

LVSSR1

LVSSR2

LVSSR3

LVSSR4

LVSSR5

LVSSR6

LVSSR7

LVSSR8

LVDS_DIGON

LVDS_BLON

LVDS_BLEN

GFX_CLKP

GFX_CLKN

HTTSTCLK

HTREFCLK

SB_CLKP

SB_CLKN

TMDS_HPD

STRP_DATA

DDC_DATA

TESTMODE

+3V

D18

C18

B19

A19

D19

C19

D20

C20

B16

A16

D16

C16

B17

A17

E17

D17

B20

A20

B18

C17

E18

F17

E19

G20

H20

G19

E20

F20

H18

G18

F19

H19

F18

E14

F14

F13

B8

A8

P23

N23

E8

E7

C13

C14

C15

A10

E10

B10

E12

R225

4.7K

R20

4.7K

2

25 mils

LPVSS

R44 10K/F

R222 1K

+3V

R228

4.7K

2

LVDDR18D

EDIDDATA 18

R23

2K

R21

*2K

T63

T59

T247

T251

T54

T252

T60

T257

TXLOUT0+ 18

TXLOUT0- 18

TXLOUT1+ 18

TXLOUT1- 18

TXLOUT2+ 18

TXLOUT2- 18

T43

T55

T259

T258

TXLCLKOUT+ 18

TXLCLKOUT- 18

DISP_ON 18

LCD_BLON 18

CPIS_BLEN 18

NBSRCCLK 2

NBSRCCLK# 2

HTREFCLK 2

SBLINKCLK 2

SBLINKCLK# 2

DFT_GPIO3

DFT_GPIO4

DFT_GPIO5

R223

4.7K

1

JOINT

JOINT

JOINT

JOINT

JOINT

AVSSN

AVSSQ

AVSSDI

PLLVSS

LPVSS

DO NOT SHARE GND VIA ON JOINT

+1.8V

25 mils

LPVDD

L8

C80

0.1U

L11

TI201209G121

C91

1U

R226 *3K

R224 *3K

R229 *3K

25 mils

C65

0.1U

LVDDR18A

C64

1U

C81

0.1U

TI201209G121

L10

TI201209G121

C75

4.7U

PROJECT : CT8

Quanta Computer Inc.

Size Document Number Rev

Date: Sheet

RS480M-VIDEO & CLKGEN

1

of

742Thursday, April 14, 2005

+1.8V

3ACustom

5

4

3

2

1

VSSA16

VSSA17

VSSA18

VSSA22

AA3A2AB3P8J6C8AD3V8F3

VSSA19

VSSA20

VSSA21

VSSA22

VSSA23

VSSA24

AE3

AF3M5AB7G3B4P7AA5C9C7J5R6J3AD5D6C4K3AB8T7Y7

VSSA25

VSSA26

VSSA27

VSSA28

VSSA29

VSSA30

VSSA31

VSSA32

VSSA33

VSSA34

VSSA35

VSSA36

VSSA37

VSSA38

VSSA39

VSSA40

VSSA41

VSSA42

VSSA43

VSSA44

VSSA45

VSSA46

AD6K7H7M3V6H8C2

VSSA47

VSSA48

VSSA49

VSSA50

VSSA51

VSSA52

CLG

R5

AE5V5N3F7F5R3AA6T3M6C5F8M8Y8V3C3W3K8D3C6

VSSA1

VSSA2

VSSA3

VSSA4

VSSA5

VSSA6

VSSA7

VSSA8

D D

VSSA9

VSSA10

VSSA11

VSSA12

VSSA13

VSSA14

VSSA15

PAR 6 OF 6

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

G10

G12

AD29

AD27

AC27

G15

G14

Y24

G13E9D15D9AD9

G11

F16

G30

AB28

AB25

D12

AD24

AA28

G17

Y23

AC9

R19

Y27

C28

G16

F25

B30

T24

F26

W27

D11

H11

AD25

H17

H10

H16

H14

E16

D10

E15

F15

U15

V14

R15

T14

N15

V12

C152

22U

C99

0.1U

C96

0.1U

C52

0.1U

C55

0.1U

C42

0.1U

VSS30

C105

0.1U

C94

0.1U

C88

0.1U

C74

0.1U

C116

0.1U

C43

0.1U

C54

0.1U

C84

0.1U

C104

0.1U

C87

0.1U

C50

0.1U

C113

0.1U

C73

0.1U

C63

0.1U

VDD18

C101

0.1U

C110

0.1U

C83

0.1U

C70

0.1U

C93

0.1U

C89

0.1U

C57

0.1U

C107

0.1U

C95

0.1U

C31

0.1U

C35

0.1U

C36

0.1U

20 mils

C76

0.1U

VDDHT30

VDDHT31

C21

0.1U

C71

1U

VDDA_1V2

L15

C C

L15,L55 TI201209G121

CHANGE TO

FBMJ2125HM330-T

B B

A A

+3V

REV.B

2

FBMJ2125HM330-T

+2.5V

D2

BAV99

3

1

+1.8V

3.3V_2.7

2

L7

TI201209G121

D1

3

BAV99

C115

22U

C85

0.1U

C77

0.1U

1

Notice the trace width.

AG3L6AJ1M7V7F6E6U5U6E5L5

VSSA53

VSSA54

VSSA55

VSSA56

VSSA57

VSS51

VSS52

VSS53

VSS54

VSS55

N13

P14

U17

T16

R17

P12

VDDHT

AB24

AA27

AB27

AB23

AA23

AC30

AK23

AK28

AK11

AE30

AC14

AD12

AC18

AC20

AD10

AD14

AD15

AD20

AC10

AD18

AC12

AD22

AC22

AH15

AC17

AC15

VSSA59

VSSA58

VSSA59

VSS56

VSS57

T12

R13

N27

U27

V27

G27

V24

H27

K24

P27

J27

K27

P24

V23

G23

E23

W23

K23

J23

H23

U23

D23

F23

C23

B23

A23

A29

AK4

H15

B21

C21

A22

B22

C22

F21

F22

E21

G21

VSSA60

VSSA61

VSSA62

VSSA63

VSS58

VSS59

VSS60

VSS61

W13

W17

P18

U17E

VDD_HT1

VDD_HT2

VDD_HT3

VDD_HT4

VDD_HT5

VDD_HT6

VDD_HT7

VDD_HT8

VDD_HT9

VDD_HT10

VDD_HT11

VDD_HT12

VDD_HT13

VDD_HT14

VDD_HT15

VDD_HT16

VDD_HT17

VDD_HT18

VDD_HT19

VDD_HT20

VDD_HT21

VDD_HT22

VDD_HT23

VDD_HT24

VDD_HT25

VDD_HT26

VDD_HT27

VDD_HT28

VDD_HT29

VDD_HT30

VDD_HT31

VDD_MEM1

VDD_MEM2

VDD_MEM3

VDD_MEM4

VDD_MEM5

VDD_MEM6

VDD_MEM7

VDD_MEM8

VDD_MEM9

VDD_MEM10

VDD_MEM11

VDD_MEM12

VDD_MEM13

VDD_MEM14

VDD_MEM15

VDD_MEM16

VDD_MEM17

VDD_MEM18

VDD_MEMCK

VDD18_1

VDD18_2

VDD18_3

VDD_CORE47

VDD_CORE46

VDD_CORE45

VDD_CORE44

VDD_CORE43

VDD_CORE42

VDD_CORE41

VDD_CORE40

VDD_CORE39

RS480M

VSSA64

VSSA65

VSSA66

VSS62

VSS63

VSS64

V18

M18

U13

PART 5 OF 6

T8

VSSA67

VSSA68

GROUND

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

N17

W15

V16

T18

M14

M12

VDD_CORE10

VDD_CORE11

VDD_CORE12

VDD_CORE13

VDD_CORE14

VDD_CORE15

VDD_CORE16

VDD_CORE17

VDD_CORE18

VDD_CORE19

VDD_CORE20

VDD_CORE21

VDD_CORE22

VDD_CORE23

VDD_CORE24

VDD_CORE25

VDD_CORE26

VDD_CORE27

VDD_CORE28

VDD_CORE29

VDD_CORE30

VDD_CORE31

VDD_CORE32

VDD_CORE33

VDD_CORE34

POWER

VDD_CORE35

VDD_CORE36

VDD_CORE37

VDD_CORE38

F28

H28

M24

J28

VSS113

VSS114

VSS115

VSS116

VSS71

VSS72

M16

P16

VDDA12_14

VDDA12_1

VDDA12_2

VDDA12_3

VDDA12_4

VDDA12_5

VDDA12_6

VDDA12_7

VDDA12_8

VDDA12_9

VDDA12_10

VDDA12_11

VDDA12_12

VDDA12_13

VDDA18_1

VDDA18_2

VDDA18_3

VDDA18_4

VDDA18_5

VDDA18_6

VDDA18_7

VDDA18_8

VDDA18_9

VDDA18_10

VDDA18_11

VDDA18_12

VDDA18_13

VDD_CORE1

VDD_CORE2

VDD_CORE3

VDD_CORE4

VDD_CORE5

VDD_CORE6

VDD_CORE7

VDD_CORE8

VDD_CORE9

N19

K28

VSS117

VSS73

U19

AC16

T23

L27

VSS118

VSS119

VSS74

VSS75

AG18

AC23

H9

AA7

G9

U8

N7

N8

U7

F9

AA8

G8

G7

J8

J7

B1

AG4

R8

AC8

AC7

AF6

AE6

L8

W8

W7

L7

R7

AF5

AK2

N16

M13

M15

W16

N18

P19

N12

P15

N14

M17

T19

G22

R12

P13

R14

V19

R18

U16

U12

T13

U14

T17

U18

E22

R16

V13

T15

P17

W18

D22

W12

V15

W14

V17

M19

H22

H21

D21

M27

VSS120

VSS76

VSS77

AD8

AD11

H24

N28

VSS122

VSS123

VSS78

VSS79

AD13

AD16

P25

P28

E26

VSS124

VSS125

VSS126

VSS127

VSS80

VSS81

VSS82

VSS83

AD19

AD23

AG5

VDDA12_13

VDDA18_13

K25

U28

VSS128

VSS84

AG6

AG21

V25

V28

VSS129

VSS130

VSS85

VSS86

AD17

AG15

R23

VSS131

VSS132

VSS87

VSS88

AG12

AF30

VSS89

C34

1U

VDDA18

C29

22U

VSS89

VSS90

AG24

VDDA_1V2

VSS91

AG9

VSS92

AC19

VSS93

AG27

C27

0.1U

C24

0.1U

VSS94

VSS95

AC11

AD7

VDDA12

C114

22U

C67

0.1U

C103

22U

C38

0.1U

C100

0.1U

VSS96

VSS97

VSS98

VSS99

AJ30

AC21

AK5

AK10

120 mils120 mils

C28

0.1U

20 mils

C25

0.1U

VSS100

AC13

AD21

C59

0.1U

C41

0.1U

C61

0.1U

C66

0.1U

C97

0.1U

VSS101

VSS102

AK22

AK29

C32

0.1U

C33

0.1U

VSS103

VSS104

W19

AE26

C58

0.1U

C48

0.1U

C39

0.1U

C60

0.1U

C78

0.1U

VSS105

VSS106

AE27

REV.B

VSS107

VSS108

T27

R27

AD28

C26

0.1U

L4

TI201209G121

C22

0.1U

C46

0.1U

C49

0.1U

C40

0.1U

C68

0.1U

C79

0.1U

VSS109

VSS110

F24

F27

L55

C10

22U

VSS111

VSS112

G28

+1.8V

C47

0.1U

C69

0.1U

+

*220U

C18

U17F

RS480M

VDDA_1V2

FBMJ2125HM330-T

NB RS480 POWER STATES

Power Signal

VDDHT

VDDR,VDDRCK

VDD18

VDDC

VDDA18

VDDA12

AVDD

AVDDDI

PLLVDD

HTPVDD

VDDR3

LPVDD

LVDDR18D

LVDDR18A

VDDA12_13

VSSA22

VDDA18_13

VSSA59

VDDHT30

VSS30

VDDHT31

VSS89

PUT DECOUPLING CAPS ON THE TOP, CLOSE

TO BALLS

CONNECT VSSA22,VSSA59,VSS30,VSS89

to the ground.

S0

S3

S1

OFF

ON

ON

ON

ON

ON

ON

ON

OFF

ON

ON

OFF

ON

ON

OFF

ON OFF

ON

ON

ON

OFF

OFF

ON

ON

ON

OFF

ON

OFF

ON

ON

ON

ON

OFF

OFF

ON

ON

ON

OFF

ON

ON

ON

OFF

C13

4.7U

C12

4.7U

C144

4.7U

C122

4.7U

S4/S5

OFF

ON

OFF OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

PROJECT : CT8

G3

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RS480M-POWER

842Thursday, April 14, 2005

1

2ACustom

of

5

4

3

2

1

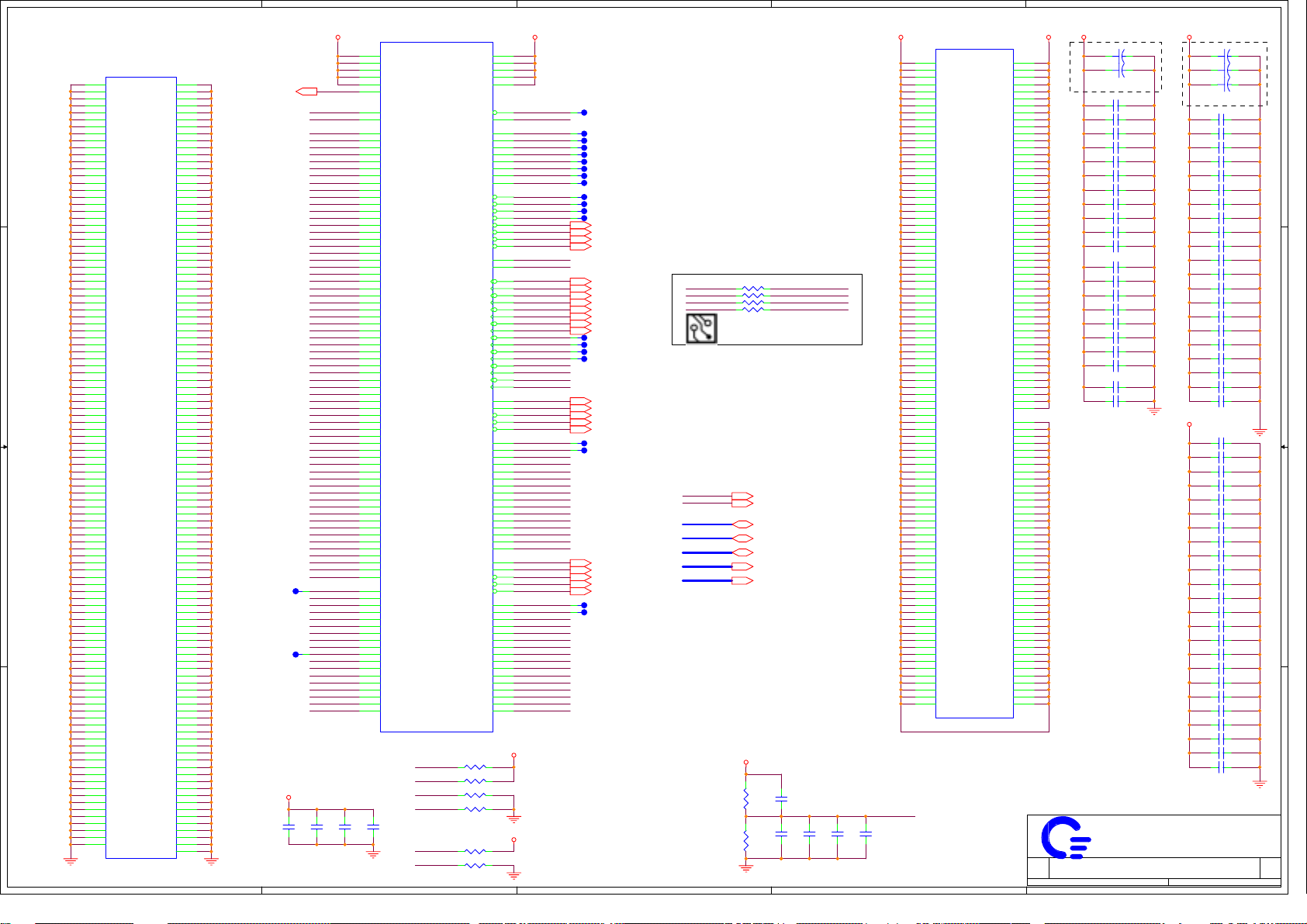

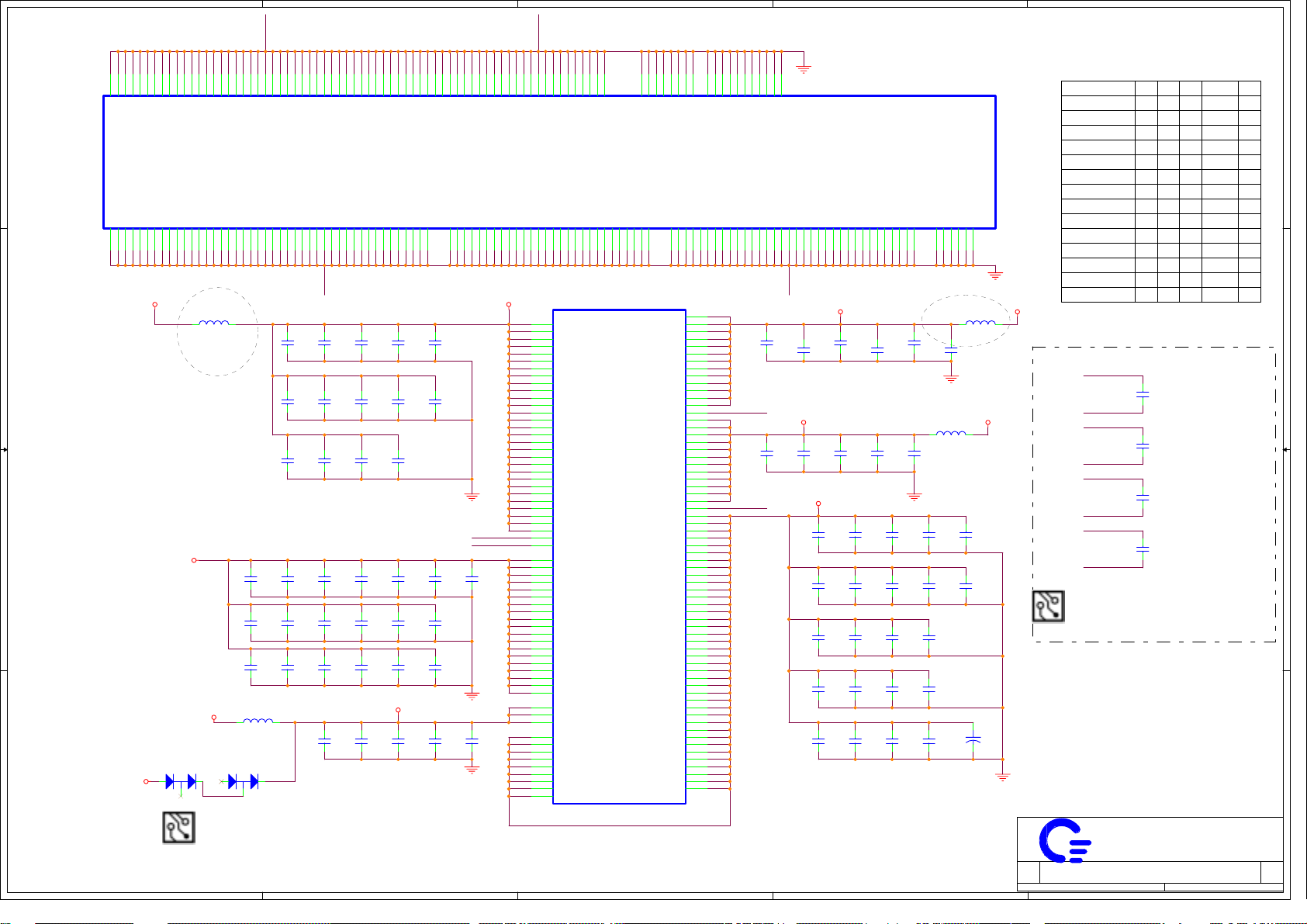

DDR

D D

NOTE: BA2 is not used and it is left open.

C C

B B

NOTE: VDDid is a no connect for 2.5V DDR SDRAM.

NOTE: Pin 10 (RESET_L) is not

A A

MAA[13..0]4,11

MEMBAA04,11

MEMBAA14,11

DM_[7..0]10,11

DQS_[7..0]10,11

DCLK#54

DCLK#74

CKE04,11

RAS#A4,11

CAS#A4,11

WE#A4,11

CS#04,11

CS#14,11

+3V

It is only used for 3.3V SDRAM.

used by unbuffered DIMM's.

5

Unbuffered DDR Near SODIMM Socket

2.5VSUS

DCLK54

DCLK74

C150

0.1U

DM_[7..0]

DQS_[7..0]

2.5VSUS

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

SDATA2,10,13

SCLK2,10,13

20 mils

2.5VSUS

CS#0

CS#1

DM_0

DM_1

DM_2

DM_3

DM_4

DM_5

DM_6

DM_7

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

DCLK5

DCLK#5

DCLK7

DCLK#7

R71 10K

R72 10K

T112

T116

T92

91021223334364645575869708182

112

A0

111

A1

110

109

108

107

106

105

102

101

115

100

123

117

116

134

148

170

184

133

147

169

183

160

158

118

120

119

121

122

194

196

198

193

195

197

199

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

VDD

A2

VDD#10

VDD#21

VDD#22

VSS#186

185

186

VDD#33

VSS#173

VSS#174

VSS#185

173

174

4

A3

A4

A5

A6

A7

A8

A9

A10

A11

99

A12

A13

BA0

BA1

98

BA2

12

DM0

26

DM1

48

DM2

62

DM3

DM4

DM5

DM6

DM7

78

DM8

11

DQS0

25

DQS1

47

DQS2

61

DQS3

DQS4

DQS5

DQS6

DQS7

77

DQS8

35

CK0

37

CK0

CK1

CK1

89

CK2

91

CK2

96

CKE0

95

CKE1

RAS

CAS

WE

S0

S1

86

RSET

SA0

SA1

SA2

SDA

SCL

VDDspd

VDDid

93

VDD#93

94

VDD#94

VDD#113

VDD#114

VDD#131

VDD#132

VDD#143

VDD#144

VDD#155

VDD#156

VDD#157

VDD#167

VDD#168

VDD#179

VDD#180

VDD#191

VDD#192

3

VSS

4

VSS#4

15

VSS#15

16

VSS#16

27

VSS#27

28

VSS#28

38

VSS#38

39

VSS#39

Socket_SO_DIMM_200_pin,_RVS H5.2

VDD#34

VDD#36

VSS#161

VSS#162

161

162

VDD#46

VDD#45

VSS#150

VSS#159

150

159

92

CN13

DQ0

DQ1

DQ2

VDD#92

VDD#57

VDD#58

VDD#69

VDD#70

VDD#81

VDD#82

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

CB0

CB1

CB2

CB3

CB4

CB5

SO-DIMM

VSS#138

VSS#149

137

138

149

CB6

(REVERSE)

CB7

VREF

VREF#2

DU

DU#97

DU#124

DU#200

VSS#40

VSS#51

VSS#52

VSS#63

VSS#64

VSS#75

VSS#76

VSS#87

VSS#88

VSS#90

VSS#103

VSS#104

VSS#125

VSS#126

VSS#137

103

104

125

126

5

7

13

17

6

8

14

18

19

23

29

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

71

73

79

83

72

74

80

84

1

2

85