Page 1

MIPS® Malta™ User’s Manual

Document Number: MD00048

Revision 01.07

August 28, 2009

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

MIPS Technologies, Inc.

955 East Arques Avenue

Sunnyvale, CA 94085-4521

Page 2

Copyright © 2000-2007 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of

this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a

minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution

restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT

PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN

PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologiesreserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does

not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether

express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded.

Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not

give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any

country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export,

reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software

documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals,

is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure,

or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian

agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further

restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS

Technologies or an authorized third party.

MIPS, MIPS I, MIPS II, MIPS III, MIPS IV,MIPSV, MIPS-3D, MIPS16, MIPS16e, MIPS32, MIPS64, MIPS-Based, MIPSsim, MIPSpro, MIPS Technologies

logo, MIPS-VERIFIED, MIPS-VERIFIED logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24Kf,

24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, R3000, R4000, R5000, ASMACRO, Atlas, "At the core of the user

experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2

NAVIGATOR, HyperDebug, HyperJTAG, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, OCI, PDtrace, the Pipeline, Pro Series, SEAD, SEAD-2,

SmartMIPS, SOC-it, System Navigator, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other

countries.

All other trademarks referred to herein are the property of their respective owners.

Template: nB1.02, Built with tags: 2B

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

MIPS® Malta™ User’s Manual, Revision 01.07

Page 3

Table of Contents

Chapter 1: Introduction..........................................................................................................................7

1.1: Overview...................................................................................................................................................... 7

Chapter 2: Getting Started...................................................................................................................11

2.1: Required Hardware ................................................................................................................................... 11

2.2: Optional Hardware..................................................................................................................................... 11

2.3: Wiring It Up................................................................................................................................................12

2.4: Power-up Sequence.................................................................................................................................. 12

Chapter 3: Memory Map.......................................................................................................................13

3.1: Revision Information..................................................................................................................................14

3.2: NMI Interrupts............................................................................................................................................15

3.3: NMI Acknowledge...................................................................................................................................... 15

3.4: Switches / Status....................................................................................................................................... 16

3.5: Displays..................................................................................................................................................... 17

3.6: Reset Control............................................................................................................................................. 19

3.7: CBUS UART, tty2...................................................................................................................................... 20

3.8: General Purpose I/O.................................................................................................................................. 20

3.9: I2C............................................................................................................................................................. 21

Chapter 4: Board Layout......................................................................................................................25

4.1: Connectors & Jumpers.............................................................................................................................. 26

4.2: Switches.................................................................................................................................................... 28

4.3: Displays / LEDs......................................................................................................................................... 29

Chapter 5: Hardware Description........................................................................................................31

5.1: PCI Bus ..................................................................................................................................................... 31

5.1.1: PCI Arbiter........................................................................................................................................32

5.2: I2C Bus......................................................................................................................................................32

5.3: Power ........................................................................................................................................................ 32

5.4: Reset......................................................................................................................................................... 33

5.5: Clocks........................................................................................................................................................33

5.6: Interrupt Controller..................................................................................................................................... 33

5.7: Serial Ports................................................................................................................................................ 37

5.7.1: File Download ..................................................................................................................................37

5.7.2: Serial Port Reset.............................................................................................................................. 38

5.8: Ethernet..................................................................................................................................................... 38

5.9: USB........................................................................................................................................................... 38

5.10: Keyboard / Mouse / IEEE1284 Parallel Port / Floppy Disk......................................................................38

5.11: Real Time Clock (RTC) ........................................................................................................................... 39

5.12: IDE/CompactFlash (True IDE Mode)....................................................................................................... 39

5.13: Flash Memory..........................................................................................................................................39

5.14: EEPROM................................................................................................................................................. 39

5.15: AMR (Audio Modem Riser)...................................................................................................................... 40

5.16: Front Panel Connector ............................................................................................................................ 40

5.17: Debug Access ......................................................................................................................................... 40

MIPS® Malta™ User’s Manual, Revision 01.07 3

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 4

5.17.1: Software Debug .............................................................................................................................40

5.17.2: Hardware Debug............................................................................................................................ 40

Chapter 6: 1284 Flash Download Format ...........................................................................................45

Chapter 7: Core Card Design...............................................................................................................49

7.1: Required Interfaces................................................................................................................................... 49

7.1.1: Power............................................................................................................................................... 49

7.1.2: PCI Bus............................................................................................................................................ 49

7.1.3: Clock................................................................................................................................................ 49

7.1.4: Revision Number.............................................................................................................................. 49

7.1.5: I2C bus............................................................................................................................................. 49

7.1.6: Interrupts.......................................................................................................................................... 49

7.1.7: Endian.............................................................................................................................................. 50

7.1.8: CBUS............................................................................................................................................... 50

7.1.9: EJTAG..............................................................................................................................................51

7.1.10: Misc................................................................................................................................................ 51

7.2: Signals.......................................................................................................................................................52

7.2.1: J3 Connector.................................................................................................................................... 53

7.2.2: J4 Connector.................................................................................................................................... 55

7.3: Physical Design......................................................................................................................................... 56

4 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 5

List of Figures

Figure 1.1: MaltaTM Development Platform Block Diagram...................................................................................... 8

Figure 4.1: Malta Board Layout............................................................................................................................... 25

Figure 4.2: Rear Panel Connector Layout .............................................................................................................. 26

Figure 5.1: PCI Arbiter Connections ....................................................................................................................... 32

Figure 5.2: Interrupt Wiring ..................................................................................................................................... 35

Figure 5.3: Front Panel Connector.......................................................................................................................... 40

Figure 7.1: CBUS Read Cycle ................................................................................................................................ 50

Figure 7.2: CBUS Write Cycle.................................................................................................................................51

Figure 7.3: J3 and J4 Alignment ............................................................................................................................. 57

Figure 7.4: Core Card Template Layout..................................................................................................................58

MIPS® Malta™ User’s Manual, Revision 01.07 5

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 6

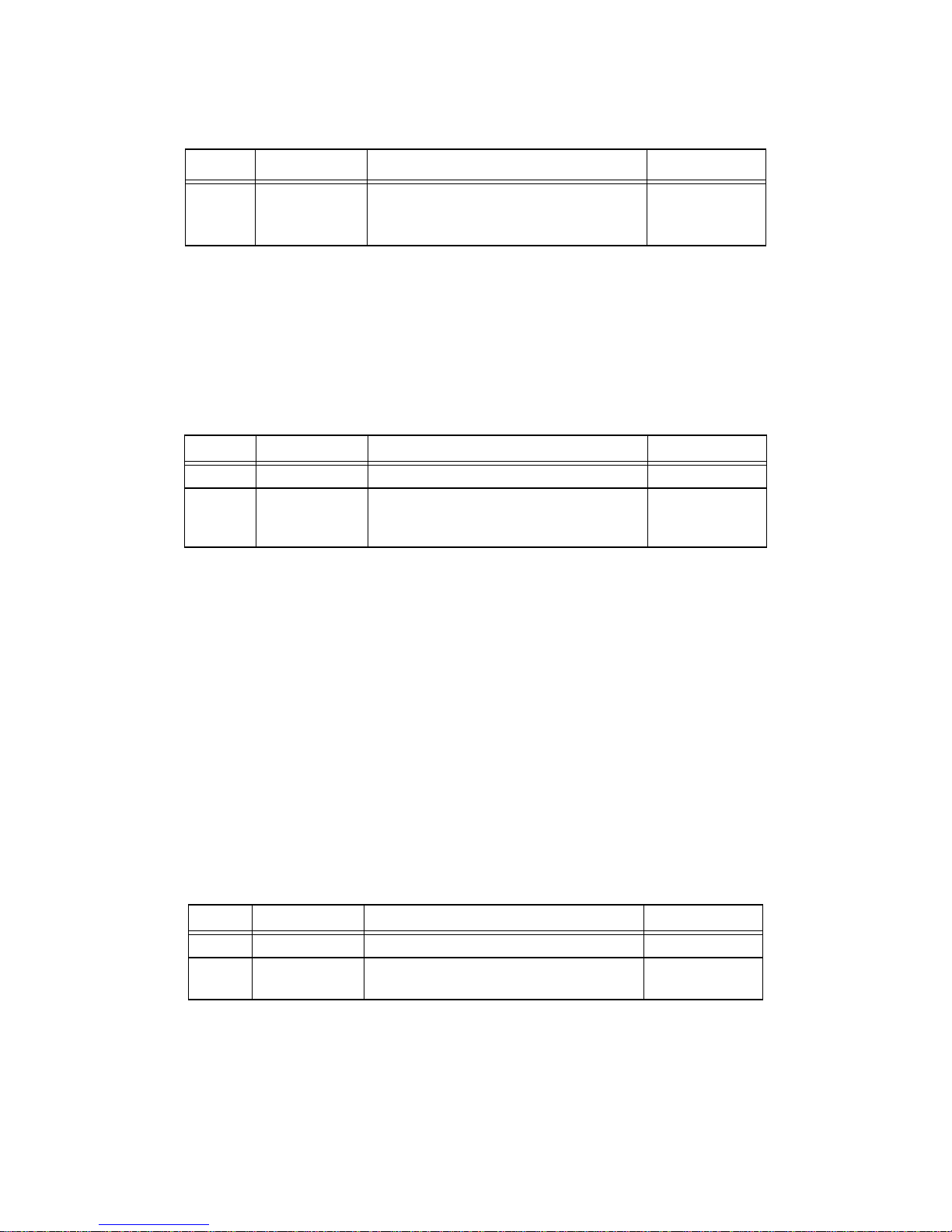

List of Tables

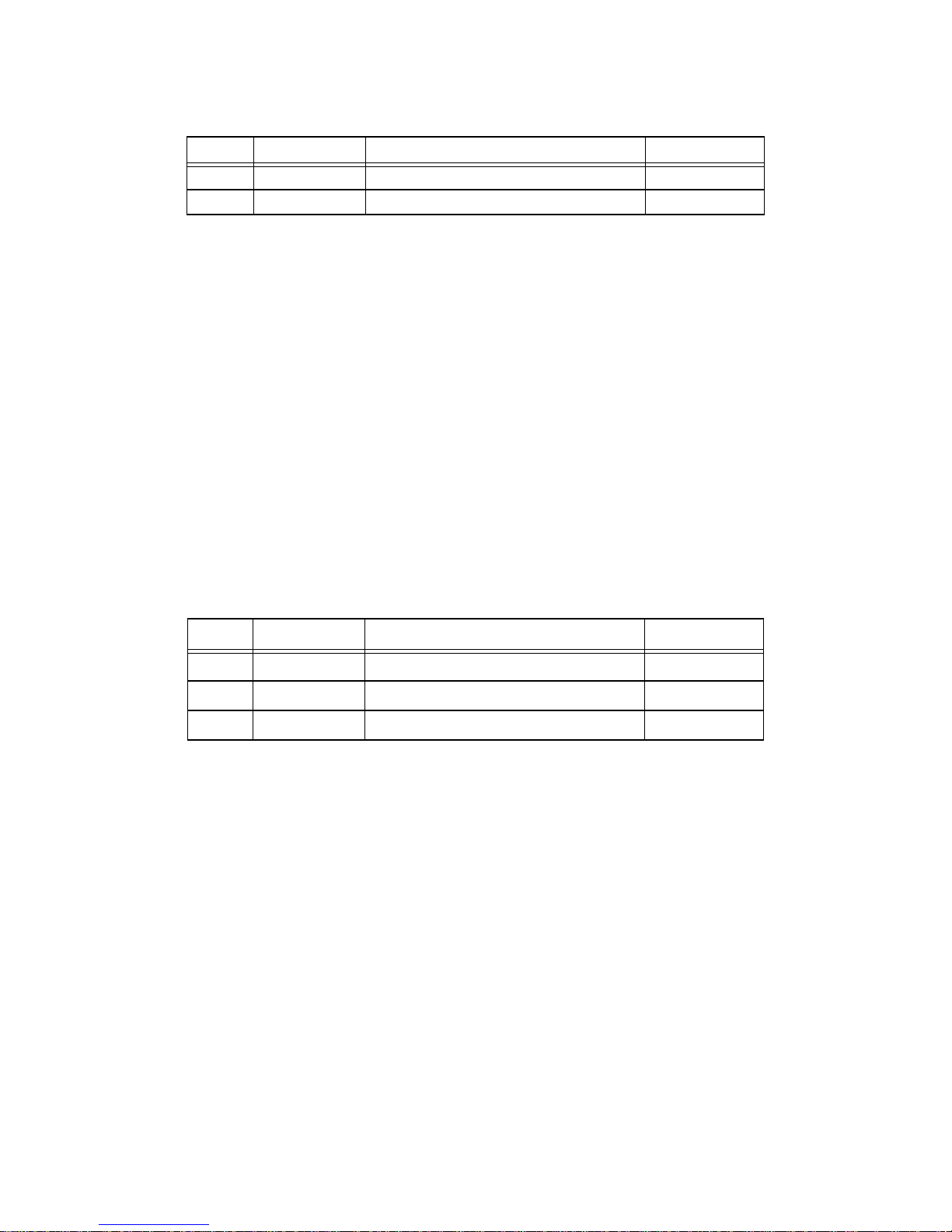

Table 3.1: Malta Physical Memory Map.................................................................................................................. 13

Table 3.2: I2C Slave Address Map ......................................................................................................................... 14

Table 3.3: REVISION Register ............................................................................................................................... 14

Table 3.4: NMISTATUS Register............................................................................................................................ 15

Table 3.5: NMIACK Register................................................................................................................................... 16

Table 3.6: SWITCH Register...................................................................................................................................16

Table 3.7: STATUS Register .................................................................................................................................. 16

Table 3.8: JMPRS Register .................................................................................................................................... 17

Table 3.9: Display Registers. BASE = 0x1F00.0400 .............................................................................................. 17

Table 3.10: LEDBAR Register ................................................................................................................................ 18

Table 3.11: ASCIIWORD Register.......................................................................................................................... 19

Table 3.12: ASCIIPOS0-7 Registers....................................................................................................................... 19

Table 3.13: SOFTRES Register.............................................................................................................................. 19

Table 3.14: BRKRES Register................................................................................................................................ 20

Table 3.15: UART Registers. BASE = 0x1F00.0900 .............................................................................................. 20

Table 3.16: GPOUT Register.................................................................................................................................. 21

Table 3.17: GPINP Register ................................................................................................................................... 21

Table 3.18: I2CINP Register...................................................................................................................................22

Table 3.19: I2COE Register.................................................................................................................................... 22

Table 3.20: I2COUT Register ................................................................................................................................. 22

Table 3.21: I2CSEL Register .................................................................................................................................. 23

Table 4.1: Interface Connectors.............................................................................................................................. 26

Table 4.2: Jumpers ................................................................................................................................................. 27

Table 4.3: Switches................................................................................................................................................. 28

Table 4.4: LEDs ...................................................................................................................................................... 29

Table 4.5: Ethernet Connector LED Functionality................................................................................................... 30

Table 5.1: IDSEL and INT# for PCI Devices........................................................................................................... 31

Table 5.2: IRQ 0..15 Mapping................................................................................................................................. 36

Table 5.3: CPU INT0..5 and CPU NMI Mapping..................................................................................................... 36

Table 5.4: Serial Port Pinouts ................................................................................................................................. 37

Table 5.5: Testpoints .............................................................................................................................................. 40

Table 5.6: Logic Analyser Connectors....................................................................................................................41

Table 6.1: Download Codes.................................................................................................................................... 46

Table 6.2: Flash Download Error Messages........................................................................................................... 46

Table 7.1: CBUS AC Timing Parameters................................................................................................................ 51

Table 7.2: Core Card Interface Signals................................................................................................................... 52

Table 7.3: J3 Pin List .............................................................................................................................................. 53

Table 7.4: J4 Pin List .............................................................................................................................................. 55

Table 7.5: Core Card Component Height Restrictions............................................................................................ 57

6 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 7

Chapter 1

Introduction

This document is the primary reference document for the Malta™ Development Board.

1.1 Overview

The Malta Board provides a standard platform for software development with MIPS32® and MIPS64® processors.

The platform is composed of two parts: the Malta Motherboard, which holds the CPU-independent parts of the circuitry, and one or more CoreLV or CoreFPGA Core boards, which hold the MIPS CPU plus its System Controller

and fast SDRAM memory.

The Malta Board is designed around a standard PC chipset, which provides all the advantages of easy-to-obtain software drivers. It is supplied with the YAMON ROM monitor in the on-board Flash memory, which can be reprogrammed from a PC or workstation via the IEEE1284 port. The feature set extends from low-level debugging aids,

such as DIP switches, LED displays, and logic analyzer connectors, to sophisticated EJTAG debugger connectivity,

audio support, IDE. flash disks and Ethernet. Four PCI slots on the board give the user a high degree of flexibility in

extending the functionality of the system. The board is an ATX form factor and is intended to be used in an ATXcabinet.

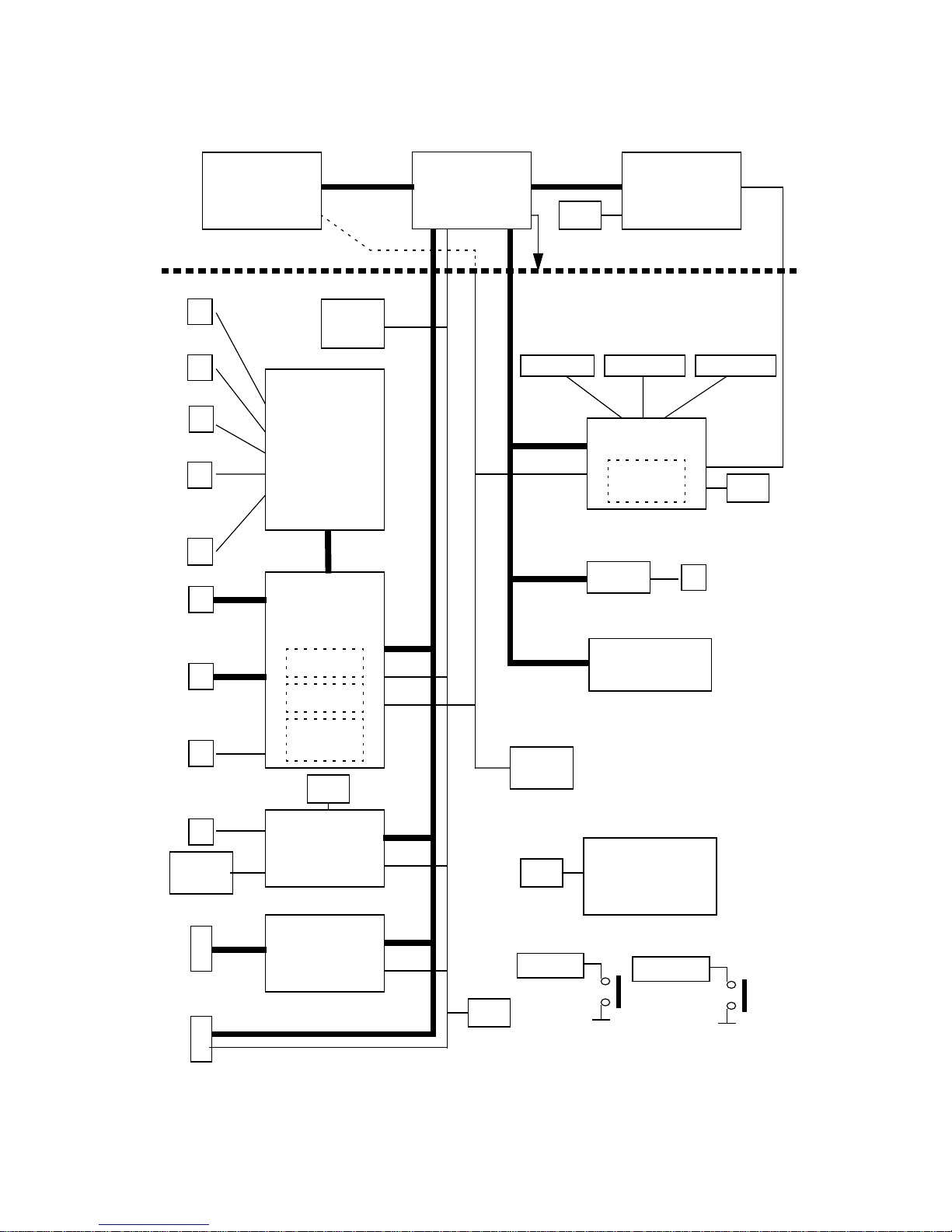

The major components of the Malta Board are shown in Figure 1.1 and listed below:

• ATX form factor

• Daughter card hosting either an FPGA implementation of a synthesizable core or a Lead Vehicle

• 100 Mbps Ethernet

• 4 PCI slots

• Audio modem riser connector

• Serial, parallel, USB, keyboard, mouse ports

• IDE and compact flash slots

• 4 Mbytes boot Flash

• 64 Mbytes SDRAM

• EJTAG v2.5 debugger connector

• YAMON™ ROM Monitor

MIPS® Malta™ User’s Manual, Revision 01.07 7

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 8

Introduction

Figure 1.1 MaltaTM Development Platform Block Diagram

System RAM

Malta/Core interface

tty0

tty1

1284

Floppy

KBD/

Mouse

Primary IDE

Secondary IDE/

CompactFlash

PCI

Arbiter

SMsC

FDC37M817

Super I/O

Controller

ISA

Intel

82371EB

(PIIX4E)

South Bridge

Timer

RTC

PCI

PCI Bridge

& SDRAM

Controller

2

C

I

CBUS

LED(x8)

SYSAD

CLK

INT

ASCII LED

CBUS FPGA

2

I

C

Controller

UART

Monitor Flash

4 Mbyte (x32)

CPU

DIL switch

(interrupts, etc.)

CLK

tty2

USB

Interrupt

Controller

EE

PROM

CLK

Ethernet

AMD

Am79C973

EE

PROM

Ethernet

Controller

CLK

Cypress

CY2278A

Clock/Synthesizer

Driver

AMR slot

Crystal

CS4281

PCI slot 1-4

Audio

Controller

CLK

Reset

On/NMI

8 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 9

1.1 Overview

The Core board shown in Figure 1.1 is a typical implementation. Though the Core Board is not strictly within the

scope of this document, it is worth noting that all Core Boards conform to the same interface specification, which is

described in Chapter 7, “Core Card Design” on page 49. Also worth noting is that most Core Boards generate their

own clock, independently of the PCI clock. Nothing on Malta is synchronized to the Core Board clock—the CBUS

protocol is asynchronous by nature. The CBUS allows the CPU to access peripherals, which either have to be available before the PCI bus has been configured (for example, the Flash memory from which it boots) or those that

require simple, low-latency access (for example, the debug LEDs and ASCII display, the tty2 port. and so on).

The PCI bus is 32-bit, 33 MHz PCI standard version 2.2 compliant (Reference [1]), and allows devices on the bus

DMA access to the DRAM on the Core Board. Four 5V PCI slots are provided on Malta to allow insertion of optional

peripherals (for example, a video controller), and also to provide a way of monitoring traffic on this bus. The PCI bus

contains the following components:

• Core Board connector for connection to the system controller on the Core Board.

• Intel PIIX4E South Bridge, 82371E (U9).

• AMD Ethernet controller, Am79C973 (U41).

• Crystal Audio controller, CS4281 (U23).

• Four 5V, 32 bit PCI connectors (J12-J15) that can be used for debug / trace purposes or for installation of a

PCI board.

The Malta Board has a PC-like structure with a South Bridge. An ISA bus is attached to the South Bridge for connection with the Super I/O (U11). The Super I/O contains the following components:

• PS/2 Keyboard and Mouse (J7).

• 1284 parallel port (J6).

• Two serial ports tty0 and tty1 (J6).

• Floppy drive, only drive A supported (J21).

The Monitor Flash is used to boot the system.

In addition to the YAMON monitor, the Malta Board includes a sample Linux port. BSPs for Microsoft® Windows®

CE, Nucleus Plus, and Windriver Systems VxWorks are also available.

MIPS® Malta™ User’s Manual, Revision 01.07 9

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 10

Introduction

10 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 11

Chapter 2

Getting Started

2.1 Required Hardware

In addition to the basic Malta motherboard, you will typically need:

• a suitable standard ATX cabinet with power supply. For a power supply with stand-by capabilities, a minimum

current of 720 mA is required (1A/1.5A peak recommended) for the 5V stand-by voltage.

• the Core Board that contains the MIPS CPU

• a serial cable for RS232 serial connection. The cable must be a Null Modem cable with 9 way ‘D’ female connector in both ends.

2.2 Optional Hardware

The following may also be useful, depending on your application:

• Ethernet cable

• USB cable

• PS2 Keyboard / mouse

• IDE disk drive and cabling

• Type I or II CompactFlash module (supporting True IDE mode)

• Floppy disk drive and cabling

The following are useful for debugging:

• LA probe connectors (that match the AMP Mictor headers) if you have an HP Logic Analyser

• PCI probe board, if you want to be able to monitor activity on the internal PCI bus (for example, FuturePlus

FS2000)

• Standard parallel-port download cable for extending the parallel male-male conversion cable

• Standard 10-pin header to DB9 converter cable for tty2

MIPS® Malta™ User’s Manual, Revision 01.07 11

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 12

Getting Started

2.3 Wiring It Up

Begin by connecting the Core Board to the Malta motherboard. Notice that the connectors J3 and J4 have the same

numbers on both boards, and one of the corner mounting pillars is offset to prevent incorrect insertion. When removing the Core Board at some later date, be careful not to bend it. Under each corner of the Core Board is a mounting

pillar, with a gap where a screwdriver can be inserted to gently lever it up. Only apply the screwdriver to the PCB

area around the mounting holes to avoid accidently cutting any tracks.

Before turning on the power, you will probably want to have set up the following:

• tty0. The supplied PROM monitor (YAMON) by default prints its welcome message via the tty0 port (J6), using

38.4 kbaud, 8 bits/char, RTS/CTS hardware handshaking, without parity. A 5-wire cable is sufficient. The implemented signals must be RXD, TXD, RTS, CTS, and GND. See Section 5.7, "Serial Ports" for the serial connector

pinout.

• Ethernet. Twisted-pair ethernet cable will plug into the socket on the rear edge of the board. This will auto configure at 10 or 100Mbit/s, half/full-duplex.

• Check that the settings of S5 switches are correct, as specified in Section 4.2, "Switches".

2.4 Power-up Sequence

When you connect the power supply and switch it on, the board is powered up. Check that the green “ATX ON”,

“3V3”, “5V”, and “STBY” LEDs are on, indicating good power.

NOTE: With some ATX supplies, Malta draws so little current that the supply is not stable. This is technically a

deviation from the ATX spec.

NOTE: The board is brought into “stand-by” mode by pressing the switch marked “ON/NMI” (S4) for more than

four seconds. The “ATX ON” LED is lit when in “stand-by” mode. Press “ON/NMI” to bring up the board again.

The green “FPGA” LED should be on, indicating that the board’s FPGA has booted.

The red “RST” LED should be off. If it is lit, it indicates that something is holding the board in reset.

When the CPU initially boots, YAMON signs-on using the tty0 serial port (the left one) with information about the

board’s configuration, for example, board revision, SDRAM size, etc.

You should now arrive at YAMON’s prompt line. Simultaneously, you should see the word “YAMON”on the ASCII

LED display. If you do not see this, check the YAMON User’s Manual for the meaning of the displayed messages.

Yamon’s help command lists the available commands, and help <command name> gives more detailed information about a specific command.

The board’s default mode is little endian. You can change to big-endian using S5-2, as described in Table 4.3.

12 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 13

Chapter 3

Memory Map

This chapter describes the Malta Board’s memory map and its control/status registers as seen by the CPU. The memory map showing the starting addresses of the major devices on the board is shown in Table 3.1.

Base Address Size Function

Table 3.1 Malta Physical Memory Map

0000.0000

0800.0000 256 Mbytes Typically PCI

1800.0000 62 Mbytes Typically PCI

1BE0.0000 2 Mbyte Typically System controller’s internal registers

1C00.0000 32 Mbytes Typically not used

1E00.0000 4 Mbytes Monitor Flash

1E40.0000 12 Mbytes Reserved

1F00.0000 12 Mbytes Switches

(*)

128Mbytes Typically SDRAM (on Core Board)

LEDs

ASCII display

Soft reset

FPGA revision number

CBUS UART (tty2)

General purpose I/O

2

I

C controller

1F10.0000 11 Mbytes Typically System Controller specific.

1FC0.0000 4Mbyte Maps to Monitor Flash

1FD0.0000 3 Mbytes Typically System Controller specific.

The shaded area of the table indicate memory areas whose mapping depends on the implementation of the

Core Board and on software.

The memory area 000F.0000-000F.FFFF (PC BIOS area) is only accessible from the CPU and not from the

PCI bus (the South Bridge decodes this memory area).

Note: Address 1FC0.0010 in Flash memory is “special”—a read from this address reads the contents of the Revision

register, allowing software to identify the hardware environment and configure itself accordingly. The next address,

1E00.0010, decodes to an address in Flash memory.

MIPS® Malta™ User’s Manual, Revision 01.07 13

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 14

Memory Map

RAM is typically mapped at the bottom of memory, so that exception vectors are located in fast memory.

Malta does not specify a mapping for addresses above 0x2000.0000. These addresses are accessed via kuseg, using

mapping defined by TLB entries.

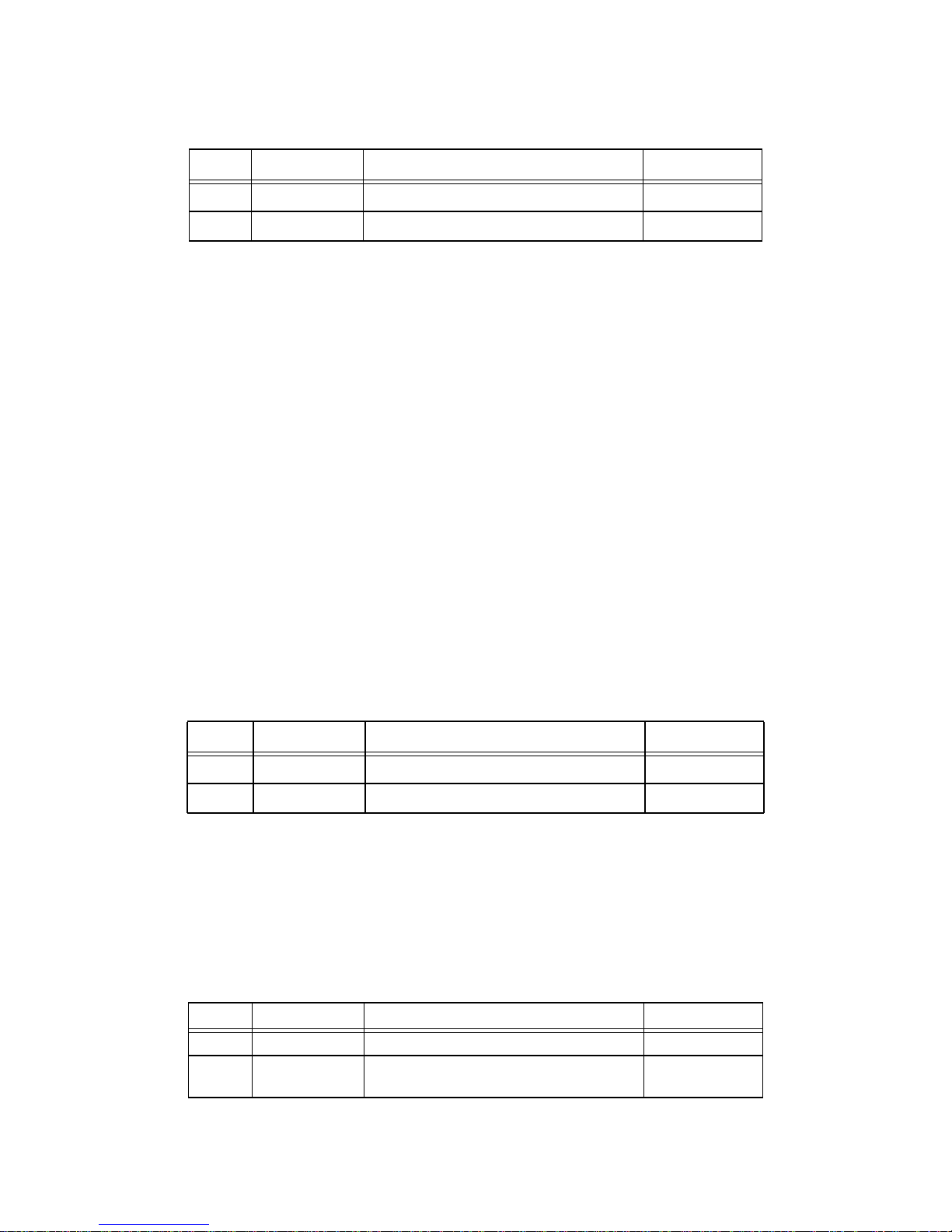

The I2C bus (called the SMB bus in the Intel documentation) is controlled by the CBUS FPGA (it can also be controlled by the controller in the South Bridge). The I2C bus address map is shown in Table 3.2.

2

Table 3.2 I

I2C Slave Address Size Function

0x50 256 bytes Core Board, PC-100 SDRAM

0x51 256 bytes Core Board, optional PC-100

0x52 256 bytes Core Board, optional PC-100

0x53 256 bytes Core Board, optional PC-100

C Slave Address Map

SDRAM

SDRAM

SDRAM

0x54-0x57 1024 bytes Malta EEPROM - read-only

Note that all addresses shown are physical addresses. You should use the macros in the header files to access all registers and fields [3].

All registers are addressed as 32-bit words, on 64-bit word boundaries. This convention allows software to access all

registers using the same word address in both big- and little-endian modes. Those registers that contain a single value

are not described in bit-field detail; these values occupy the least-significant bit of the register.

3.1 Revision Information

The Revision register contains information about the revision of the Malta and Core Boards.

Name: REVISION

Address: 0x1FC0.0010

Access: RO

Reset Value: n/a

Bits Field Name Function Initial Value

Contains serial number

Table 3.3 REVISION Register

31:24 Reserved Reserved 0

23:16 FPGRV 8-bit binary number gives revision of CBUS

15:10 CORID 6-bit Core Board ID n/a

9:8 CORRV 2-bit Core Board revision n/a

14 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

n/a

FPGA.

Page 15

Bits Field Name Function Initial Value

7:4 PROID 4-bit binary number gives product ID 0x2

3:0 PRORV 4-bit binary number gives product revision. n/a

3.2 NMI Interrupts

There are two sources of NMI:

• ON/NMI push button

• South Bridge due to assertion of PCI SERR (from PCI slot or Core card) or assertion of ISA IOCHK.

When the ON/NMI push button is activated, the signal is debounced and latched in the NMI interrupt controller. The

South Bridge NMI is routed through the NMI controller as it is. These signals then generate an active state on the

NMIN pin of the MIPS Core Board. The NMISTATUS register can be read to determine the cause of the NMI.

3.2 NMI Interrupts

Table 3.3 REVISION Register (Continued)

Name: NMISTATUS

Address: 0x1F00.0024

Access: RO

Reset Value: n/a

Bits Field Name Function Initial Value

31:1 Reserved Reserved n/a

1 SB Pending NMI from the South Bridge n/a

0 ONNMI Pending NMI from the ON/NMI push button n/a

3.3 NMI Acknowledge

The ON/NMI interrupt is by nature transient. Therefore it is debounced and latched and thereafter treated as an ordinary level-based interrupt in the NMI interrupt controller. The NMI interrupt can be cleared by writing a “1” to the

NMIACK register. Note that South Bridge NMI is acknowledged in the South Bridge.

Name: NMIACK

Address: 0x1F00.0104

Table 3.4 NMISTATUS Register

Access: WO

Reset Value: n/a

MIPS® Malta™ User’s Manual, Revision 01.07 15

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 16

Memory Map

Bits Field Name Function Initial Value

31:1 Reserved Reserved n/a

0 ONNMI Write 1 to acknowledge ON/NMI NMI n/a

3.4 Switches / Status

The SWITCH, STATUS, and JPMRS registers allow software to monitor the state of various switches and jumpers

on the Malta Board. All DIP switches have a value of “1” for a switch in the “ON” position.

A switch is considered ON if any of the following are true:

• It is in the position marked “ON” on the switch body.

• It is in the position marked “CLOSED” or not in the “OPEN” position as marked on the switch body.

There is no debouncing on these registers, so if software wants to monitor a value while it changes, allowance for this

must be made by waiting for the new value to become stable.

Table 3.5 NMIACK Register

For the DIP switches S2 & S5, bit 0 is marked by a dot or by a “0” in the silkscreen, or the switch is marked by a “1”.

Name: SWITCH

Address: 0x1F00.0200

Access: RO

Reset Value: n/a

Table 3.6 SWITCH Register

Bits Field Name Function Initial Value

31:8 Reserved Reserved 0

7:0 S2 8-bit value of the setting of DIP switch S2. n/a

Name: STATUS

Address: 0x1F00.0208

Access: RO

Reset Value: n/a

Table 3.7 STATUS Register

Bits Field Name Function Initial Value

31:5 Reserved Reserved 0

4 MFWR “1” indicates Monitor Flash lock bits are write

16 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

n/a

protected (JP1 fitted).

Page 17

Table 3.7 STATUS Register (Continued)

Bits Field Name Function Initial Value

3.5 Displays

3 S54 DIP switch S5-4.

YAMON use this switch.

“1” will set YAMON in factory default mode

(communication on tty0, etc.).

2 S53 DIP switch S5-3 n/a

1 BIGEND “1” indicates big endian mode, as controlled by

switch S5-2.

0 Reserved Reserved 0

Name: JMPRS

Address: 0x1F00.0210

Access: RO

Reset Value: n/a

n/a

n/a

Table 3.8 JMPRS Register

Bits Field Name Function Initial Value

31:5 Reserved Reserved 0

4:2 PCICLK PCI clock frequency 10-37.5MHZ

See Table 4.2

Bit 4 is Pins 5-6

Bit 3 is Pins 3-4

Bit 2 is Pins 1-2

“1” = jumper fitted

1 EELOCK

0 Reserved Reserved 0

State of JP2: Not fitted ~ “1” =

write protected.

I2C EEPROM

n/a

n/a

3.5 Displays

There are 2 display devices on the board: an 8-LED array (D28 is a 10-LED, but only 8 are used), and an 8-character

ASCII display (U42). These are controlled using the registers shown in Table 3.9 through Table 3.12.

Table 3.9 Display Registers. BASE = 0x1F00.0400

Register Name Offset Address Access Function

LEDBAR 0x0000.0008 R/W 8 bits each corresponding to 1 LED.

ASCIIWORD 0x0000.0010 WO Writing a 32-bit word to this register

MIPS® Malta™ User’s Manual, Revision 01.07 17

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

1 = ON

will cause it to be displayed in hex

on the ASCII character display.

Page 18

Memory Map

Table 3.9 Display Registers. BASE = 0x1F00.0400 (Continued)

Register Name Offset Address Access Function

ASCIIPOS0 0x0000.0018 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘0’, which is the left-most positioned

character.

ASCIIPOS1 0x0000.0020 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘1’.

ASCIIPOS2 0x0000.0028 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘2’.

ASCIIPOS3 0x0000.0030 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘3’.

ASCIIPOS4 0x0000.0038 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘4’.

ASCIIPOS5 0x0000.0040 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘5’.

ASCIIPOS6 0x0000.0048 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘6’.

ASCIIPOS7 0x0000.0050 WO Writing an ASCII value to this regis-

ter updates ASCII display position

‘7’, which is the right-most positioned character.

Name: LEDBAR

Address: 0x1F00.0408

Access: R/W

Reset Value: 0x00

Table 3.10 LEDBAR Register

Bits Field Name Function Initial Value

31:8 Reserved Reserved 0

7:0 BAR 8 bits each corresponding to 1 LED (1 = ON) 0x00

Name: ASCIIWORD

Address: 0x1F00.0410

Access: WO

Reset Value: n/a

18 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 19

Table 3.11 ASCIIWORD Register

Bits Field Name Function Initial Value

3.6 Reset Control

31:0 HEX Writing a 32-bit word to this register will

Bits Field Name Function Initial Value

31:8 Reserved Reserved n/a

7:0 ASCII Writing an ASCII value to this register updates

3.6 Reset Control

n/a

cause it to be displayed in hex on the ASCII

character display.

Name: ASCIIPOS0

Address: 0x1F00.0418

Access: WO

Reset Value: n/a

Table 3.12 ASCIIPOS0-7 Registers

n/a

ASCII display position ‘0’. Position ‘0’ is the

left-most positioned character.

There are two reset functionalities that are controlled by software: writing a “magic” value to the SOFTRES register

immediately triggers a reset of the whole board, and the BRKRES register controls how the “break” condition on the

tty0 port is monitored. Both reset functions generate a board reset with the exact same effect as if you had pressed the

reset button.

Name: SOFTRES

Address: 0x1F00.0500

Access: WO

Reset Value: 0x00

Table 3.13 SOFTRES Register

Bits Field Name Function Initial Value

31:8 Reserved Reserved n/a

7:0 RESET Writing the magic value GORESET (==0x42)

to this field will initiate a board reset

Name: BRKRES

Address: 0x1F00.0508

Access: R/W

0x00

MIPS® Malta™ User’s Manual, Revision 01.07 19

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 20

Memory Map

Reset Value: 0x0A

Table 3.14 BRKRES Register

Bits Field Name Function Initial Value

31:8 Reserved Reserved 0

7:0 WIDTH Writing a value to this address indicates the

NOTE: The initial value for WIDTH of 10 ms will cause problems, if the baud rate of the tty0 port is less than 2400

Baud. If baud rates below 2400 Baud are used, this register must be programmed with a larger value.

3.7 CBUS UART, tty2

For details on programming the CBUS UART (TI 16C550C), see the data sheet from Texas Instruments [10]. The

clock frequency for baud rate calculations is 3.6864 MHz.

The UART registers of the UART are 8 bits wide and mapped on 64-bit aligned boundaries. These registers are

described in Table 3.15.

Name Offset Address Access Function

RXTX 0x0000.0000 R/W Receive / Transmit char register

INTEN 0x0000.0008 R/W Interrupt enable register

number of milliseconds in length a “Break”

must be on the tty0 port in order to trigger a

reset. Valid values are from 0 to 255.

A value of zero prevents this reset ever occurring.

Table 3.15 UART Registers. BASE = 0x1F00.0900

0x0A

(i.e., 10ms)

IIFIFO 0x0000.0010 R/W Read: Interrupt identification

Write: FIFO control

LCTRL 0x0000.0018 R/W

MCTRL 0x0000.0020 R/W Modem control register

LSTAT 0x0000.0028 R/W Line status register

MSTAT 0x0000.0030 R/W Modem status register

SCRATCH 0x0000.0038 R/W Scratch register

1. The Divisor Latch Registers are accessible through RXTX and INTEN registers when bit 7

(Divisor Latch Access Bit) of the Line Control Register is set.

Line control register

1

3.8 General Purpose I/O

The Malta Board has eight GP inputs and eight GP outputs connected to the Core Board. For usage details, refer to

the documentation on the specific Core Board.

20 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 21

Name: GPOUT

Address: 0x1F00.0A00

Access: R/W

Reset Value: n/a

Table 3.16 GPOUT Register

Bits Field Name Function Initial Value

31:8 Reserved Reserved n/a

3.9 I2C

3.9 I2C

7:0 OUTVAL Writing to this address sets the 8 GP output

pins.

Reading gives the actual setting of the GP output pins.

Functionality is Core Board dependent.

Name: GPINP

Address: 0x1F00.0A08

Access: RO

Reset Value: n/a

0

Table 3.17 GPINP Register

Bits Field Name Function Initial Value

31:8 Reserved Reserved 0

7:0 INPVAL Reading gives the actual state of the GP input

pins. Functionality is Core Board dependent.

n/a

I2C bus access registers. As both lines have an open-drain output, no conflicts can occur during direction shift on the

bi-directional lines.

There are three registers for I2C control:

• I2CINP: Reads input values.

• I2COE: Controls output enables

• I2COUT: Controls output values.

and one register for selecting the I2C controller:

• I2CSEL: Selects between the FPGA I2C controller and the South Bridge I2C controller (the two I2C controllers

cannot co-exist).

MIPS® Malta™ User’s Manual, Revision 01.07 21

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 22

Memory Map

Name: I2CINP

Address: 0x1F00.0B00

Access: RO

Reset Value: n/a

Table 3.18 I2CINP Register

Bits Field Name Function Initial Value

31:2 Reserved Reserved n/a

1 I2CSCL Reading gives the actual value of the I2C SCL pin. 1

0 I2CSDA Reading gives the actual value of the I2C SDA

pin.

Name: I2COE

Address: 0x1F00.0B08

Access: R/W

Reset Value: n/a

Table 3.19 I2COE Register

Bits Field Name Function Initial Value

31:2 Reserved Reserved n/a

1 I2CSCL “1” means that the I2CSCL bit of the I2COUT

register will be driven to the I2C SCL pin.

“0” means that the I2C SCL pin is tri-stated.

0 I2CSDA “1” means that the I2CSDA bit of the I2COUT

register will be driven to the I2C SDA pin.

“0” means that the I2C SDA pin is tri-stated.

Name: I2COUT

1

0

0

Address: 0x1F00.0B10

Access: R/W

Reset Value: n/a

Bits Field Name Function Initial Value

31:2 Reserved Reserved n/a

1 I2CSCL The value of this bit will be driven to the I2C

22 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Table 3.20 I2COUT Register

1

SCL pin when the I2CSCL bit of the I2COE

register is “1”.

Page 23

Table 3.20 I2COUT Register

Bits Field Name Function Initial Value

3.9 I2C

0 I2CSDA The value of this bit will be driven to the I2C

SDA pin when the I2CSDA bit of the I2COE

register is “1”.

Name: I2CSEL

Address: 0x1F00.0B18

Access: R/W

Reset Value: 0x01

1

Table 3.21 I2CSEL Register

Bits Field Name Function Initial Value

31:1 Reserved Reserved n/a

0 I2CFPGA “1” means that the I2C controller in the FPGA

is enabled and the I2C controller in the South

Bridge is disconnected from the I2C bus.

“0” means that the I2C controller in the FPGA

is disabled and the I2C controller in the South

Bridge is connected to the I2C bus.

1

MIPS® Malta™ User’s Manual, Revision 01.07 23

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 24

Memory Map

24 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 25

Chapter 4

Board Layout

The basic layout of the Malta Board is shown in Figure 4.1.

Figure 4.1 Malta Board Layout

JP4

J17

J7

J3

J5

J6

J2

TX

SPD100

J4

J12

J13

J8

JP1

J9

J1

JP3

3V

J19 J18

J20

ON/NMI

J22

RESET

J10

RST

STBY

5V

3V3

ATX ON

FPGA

U42

J21

J31

D28

S2

S5

1 2 43

1 2 4 5 6 7 83

12345678910

J14

J15

JP2

J16

MIPS® Malta™ User’s Manual, Revision 01.07 25

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

1 2 3 4 5 6 7 8

Page 26

Board Layout

The board has an ATX (305 mm x 244mm) form factor and is in accordance with the ATX specification [12] with

regards to board size, mounting hole placement, connector placement, and height constraints.

The connector layout on the rear panel (namely, the shield design as described in Design Guide for Intel ATX Motherboard I/O Implementations Version 1.1 [13] is a subset of Intel Core design #1. This enables the Malta Board to be

installed in an ordinary ATX chassis. Figure 4.2 shows the rear panel connector layout.

Figure 4.2 Rear Panel Connector Layout

Mouse

Keyboard

Ethernet

Dual USB

4.1 Connectors & Jumpers

All jumpers are standard 0.1” pitch. A dot by a pin indicates pin 1. On all jumpers, pins are numbered crosswise, that

is, the end pins are 1 & 2 (this is not always the case on other connectors).

Ref Type Description

J1 10 pin 0.1” header Download connector for CBUS FPGA EEPROM.

J2 10 pin 0.1” header Download connector for Arbiter EPLD.

J3 200way header Connects the Core Board. Carries amongst other things the CBUS.

J4 200way header Connects the Core Board. Carries amongst other things the primary

J5 RJ45 Ethernet.

Serial Port (tty0) Serial Port (tty1)

Parallel Port (1284)

Table 4.1 Interface Connectors

PCI bus.

Dual USB A Two USB host ports.

J6 25 pin DSUB IEEE1284 / Flash programming port. This can either be used as a par-

Dual 9 pin DSUB tty0 (left) and tty1 (right).

J7 Dual 6 pin miniDIN Connection to a PC keyboard (lower) and mouse (upper).

J8 ATX PSU This connects the power.

26 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

allel port for communications, and is also used to program Flash

devices during production.

Page 27

4.1 Connectors & Jumpers

Table 4.1 Interface Connectors (Continued)

Ref Type Description

J9 18 pin 0.1” header Front Panel connector. Power LED, HD LED, Power Switch, Reset

Switch. Pin 14 is removed from the connector.

J10 Battery Connector CR2032 Battery Connector used by the RTC (South Bridge).

J12-15 PCI slot Allows insertion of probe board, or PCI board with additional func-

tionality.

J16 AMR slot Allows insertion of audio modem riser (AMR) board.

J17 14 pin 0.1” header

J18 40 pin 0.1” header Primary IDE interface. Pin 20 is removed from the connector.

J19 40 pin 0.1” header Secondary IDE interface. Pin 20 is removed from the connector.

J20 Compact Flash con-

nector

J21 34 pin 0.1” header

EJTAG connector. As per EJTAG specification, see Ref

removed from the connector.

Compact Flash interface at Secondary IDE interface.

Type I or II module.

Floppy Disk interface. Connects to FD via IDC ribbon cable (

[4]. Pin 12 is

7 wires

twisted, PC-style). Drive A support only.

J22 10 pin 0.1” header tty2 (CBUS UART).

J23 AMP 38 pin Mictor HP Logic Analyzer connector (CBUS data).

J24 AMP 38 pin Mictor HP Logic Analyzer connector (CBUS control + address).

J25 AMP 38 pin Mictor HP Logic Analyzer connector (CBUS FPGA).

J26 AMP 38 pin Mictor HP Logic Analyzer connector (Reset + Interrupts).

J27 AMP 38 pin Mictor HP Logic Analyzer connector (JTAG + PCI Arbiter).

J30 3 pin 0.1” header Power LED connector

J31 Compact Flash con-

nector

Compact Flash interface at Secondary IDE interface.

Type I or II module. Alternative fit for J20

Ref Silkscreen Pins Options Default Description

JP1 MFWR 2 fit-notfit notfit When fitted Enables writing to the Monitor Flash lock

MIPS® Malta™ User’s Manual, Revision 01.07 27

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Table 4.2 Jumpers

When not

fitted

bits from software. It also allows writing

to the Monitor Flash itself, regardless of

the state of the Lock bits.

Disables writing to the Monitor Flash lock

bits from software.

Page 28

Board Layout

Ref Silkscreen Pins Options Default Description

Table 4.2 Jumpers (Continued)

JP2 EEWR 2 fit - notfit notfit When fitted

Enables writing to the I

2

C EEPROM

(U14).

Do NOT fit this - it is reserved for production use.

When not

fitted

Disables writing to the

(U14).

I2C EEPROM

JP3 CF MASTER 2 fit - notfit notfit When fitted Sets Compact Flash module as Master

IDE drive on the secondary IDE bus.

JP4 PCI CLK 6 10 - 37.5

33.33

When not

fitted

(2)

Sets PCI clock- frequency between 10MHz - 37.5MHz.

Sets Compact Flash module as Slave IDE

drive on the secondary IDE bus.

“X” = fitted.

MHz/Pins 1-2 3-4 5-6

10

12.5

16.67

20

25

(1)

(1)

(1)

(1)

(1)

XXX

X

XX

X

X

Note 1: Only 10BASE-T is supported (100BASE-TX is not supported).

Note 2: Some Core Boards cannot run with a PCI clock frequency of 33.33 MHz. See the respective Core Board

User’s Manuals for maximum clock frequency.

4.2 Switches

Malta’s switches are described in Table 4.3. For those switches that are software-readable, a switch in position “ON”

or “CLOSED” (not in the “OPEN” position) will give a “1” in the appropriate register.

Ref Type Default Description

S2 8-way

DIP

30

(1)

XX

33.33

37.5 X X

Table 4.3 Switches

All OFF This switch provides a value which can be read from the SWITCH register.

28 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 29

Table 4.3 Switches (Continued)

Ref Type Default Description

4.3 Displays / LEDs

S3 Push-

button

S4 Push-

button

S5 4-way

DIP

S5-1 OFF When ON, enables Flash programming via 1284 parallel port.

S5-2 OFF When ON, set operation mode to big endian.

S5-3 OFF If S5-3 is enabled and an SMP/CMP processor is detected (34K/1004K),

S5-4 OFF When ON at power-on or at reset, sets YAMON in factory default mode e.g.,

n/a Reset button.

n/a NMI/Power ON button. This button will bring the ATX power supply out of

stand-by. It also generates an NMI to the CPU, for example, to shut down the

PSU again.

This button causes a hardware shutdown if pressed for more than four seconds

at a PCI clock at 33MHz. For PCI clocks below 33.33 MHz, the button has to

be pressed for a longer period of time (up to 12 seconds).

This swithch enables writing to the Monitor Flash lock bits. It overrides

Jumper JP1.

If the endianess is changed, Malta must be reset again in order for the new

endian mode to take effect.

If the board is not reset unpredictable operation can occur.

YAMON will initialise all CPUs and place them in an idle loop early on in the

initialisation.

communication on tty0 port is forced to 38.4 kbaud, 8 bits/char, RTS/CTS

hardware handshaking and no parity.

DIP switches S2, S5-2, S5-3, and S5-4 are readable by software.

For the DIP switches S2 & S5, a switch referred to as “1” is marked by a dot or by a “0” in the silkscreen, or the

switch is marked by a “1”.

4.3 Displays / LEDs

The Malta Board has two displays and various individual status LEDs., described in Table 4.4. See also Section 3.5,

"Displays".

Ref Silkscreen Type Description

D28 n/a 8-way bar Controlled by software.

U42 n/a 8 char ASCII

D7 ATX ON Green SMD Indicates that power is applied to the ATX power-supply.

D2 STBY Green SMD Indicates that power is applied to 3V3STBY (+/-5%) and

D6 5V Green SMD Indicates that power is applied to 5V (+/-5%).

Table 4.4 LEDs

display

Used by YAMON to display status.

Can be used for any user purpose.

Also lit when board is in stand-by mode.

5VSTBY (+/-5%). Not led when board is in stand-by

mode.

MIPS® Malta™ User’s Manual, Revision 01.07 29

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 30

Board Layout

The two LEDs, described in Table 4.5, are built-in to the RJ45 connector J5 and display status.

Table 4.4 LEDs (Continued)

Ref Silkscreen Type Description

D4 3.3V Green SMD Indicates that power is applied to 3.3V (+/-5%).

D5 FPGA Green SMD Indicates that CBUS FPGA programming completed OK.

D9 RST Red SMD Indicates that RSTN is active.

D1 TX Yellow SMD Ethernet LED3: Blinks on TX Ethernet packets (Program-

mable).

D3 SPD100 Green SMD Ethernet LED2: ndicates that 100 Mbit speed is selected

(Programmable).

Table 4.5 Ethernet Connector LED Functionality

LED Function

Green Ethernet LED0: Link up (Programmable)

Yellow Ethernet LED1: Activity (Programmable)

All four ethernet LEDs are programmed/controlled by the ethernet controller. LED0-LED3 are linked to the four

LEDs.

30 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 31

Chapter 5

Hardware Description

This chapter describes the Malta Board’s hardware components. For more detailed information on these components,

refer to the Malta Schematics [16].

5.1 PCI Bus

The PCI bus is implemented as a 5V, 32-bit and 33 MHz PCI standard version 2.2 compliant bus [1] that connects the

main components on the Malta Board.

The devices on the PCI bus are:

• Core Board connector for connection to the system controller on the Core Board

• Intel PIIX4E South Bridge, 82371E (U9)

• AMD Ethernet controller, Am79C973 (U41)

• Crystal Audio controller, CS4281 (U23)

• Four 5V, 32-bit PCI connectors (J12-J15) that can be used for debug and trace and/or for installation of PCI

boards

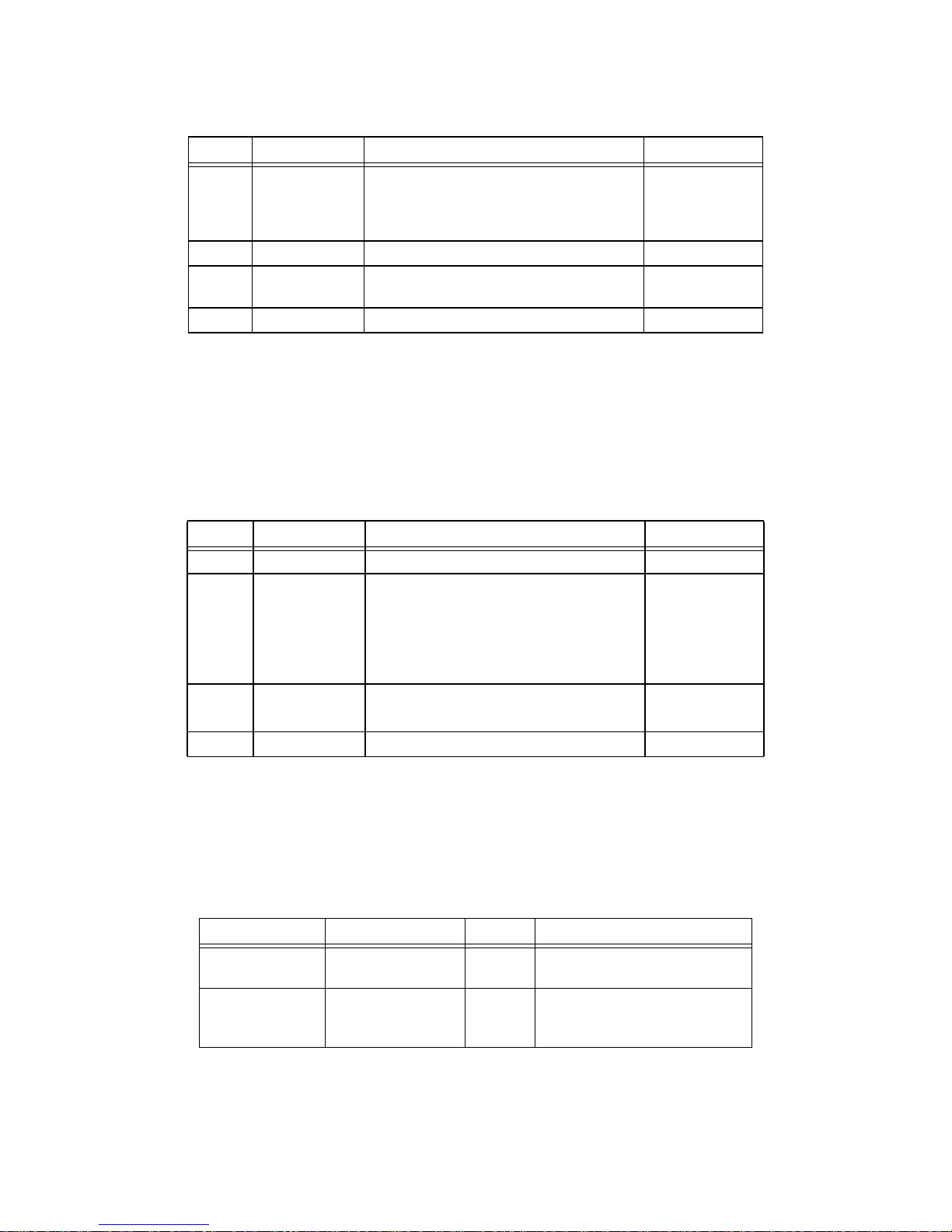

For configuration purposes, the IDSEL and INT# signals to the PCI devices are connected as shown in Table 5.1.

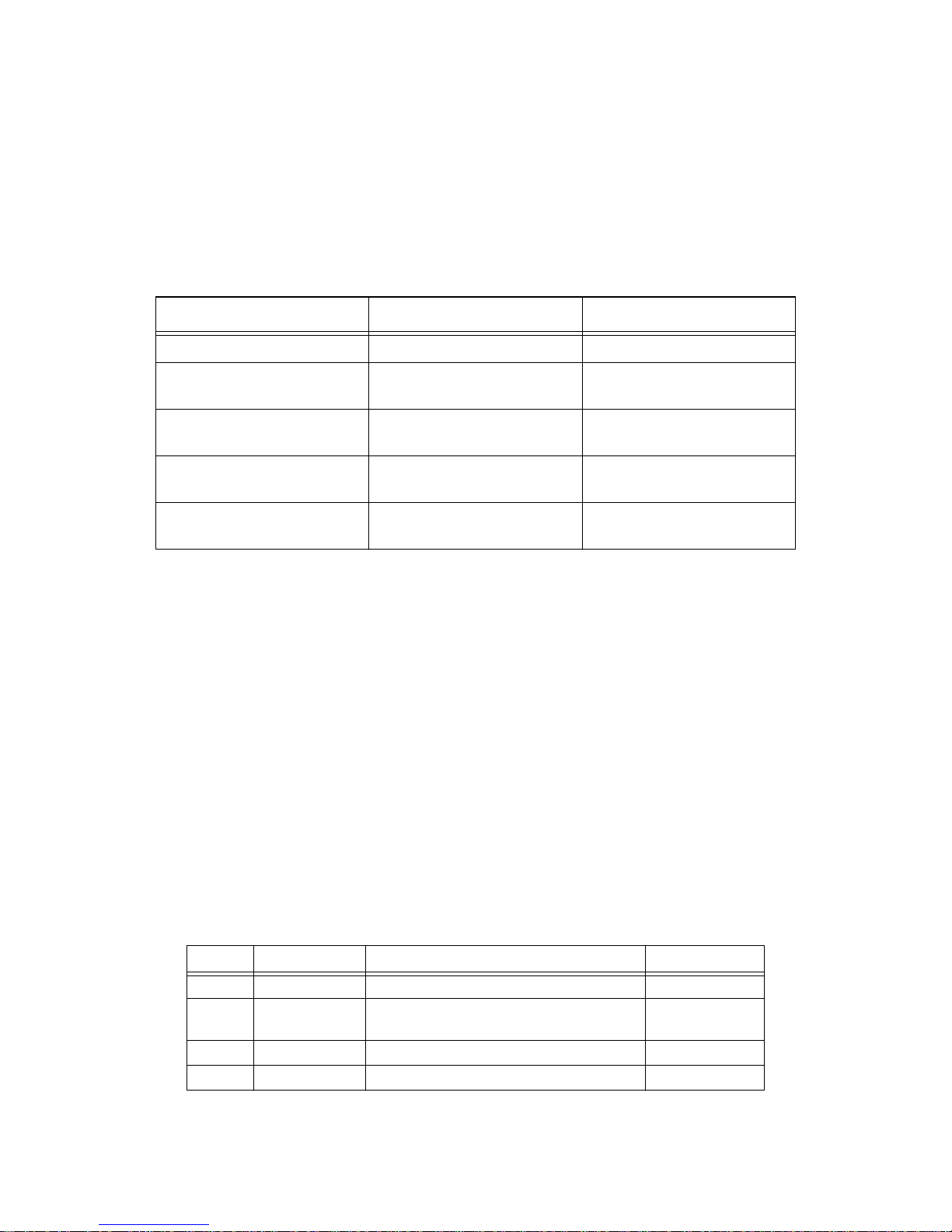

Table 5.1 IDSEL and INT# for PCI Devices

IDSEL PCI

Device

South Bridge PCI_ADP20 USB_IRQ#

Ethernet controller PCI_ADP21 ETHER_IRQ#

Audio controller PCI_ADP22 AUDIO_IRQ#

Core Card PCI_ADP27

PCI Connector 1 PCI_ADP28 INTA# INTB# INTC# INTD#

PCI Connector 2 PCI_ADP29 INTD# INTA# INTB# INTC#

PCI Connector 3 PCI_ADP30 INTC# INTD# INTA# INTB#

PCI Connector 4 PCI_ADP31 INTB# INTC# INTD# INTA#

Address

PCI_INTAN PCI_INTBN PCI_INTCN PCI_INTDN

PCI Interrupts Mapping

MIPS® Malta™ User’s Manual, Revision 01.07 31

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 32

Hardware Description

5.1.1 PCI Arbiter

The PCI arbiter controls the request and grant scheduling to the eight PCI components and is implemented in an

Altera MAX3064 EPLD.

The PCI arbiter implements a round-robin scheme, where each of the eight components have equal priority.

Figure 5.1 shows the signals used during PCI arbitration.

Figure 5.1 PCI Arbiter Connections

pci_gnt#_corepci_req#_core

pci_gnt#_southbridgepci_req#_southbridge

5.2 I2C Bus

The Malta Board has two I2C controllers:

• a simple one in the FPGA, used for accessing SDRAM information for debug purposes and similar operations

when the PCI bus is unconfigured

• a more advanced controller in the South Bridge used for normal operation

The active I2C controller is set in the I2CSEL register in FPGA.

PCI

Arbiter

pci_gnt#_ethernetpci_req#_ethernet

pci_gnt#_audiopci_req#_audio

pci_gnt#_con1pci_req#_con1

pci_gnt#_con2pci_req#_con2

pci_gnt#_con3pci_req#_con3

pci_gnt#_con4pci_req#_con4

5.3 Power

The board operates with 3.3V and 5V, supplied from a standard PC ATX power supply connected to J8. This should

be able to supply enough current for the board and all conceivable Core Board options. The 12V and -12V is only

connected to the Core Board (only 12V) and the AMR and PCI connectors. See [11] for details of a suitable supply.

Power On/Off is controlled by the South Bridge and its function is similar to a PC.

The board also supports Power Management Events, for eample, Wake On LAN events, used for powering up in

stand-by mode.

32 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 33

5.4 Reset

A push-button switch (S3) is provided to reset the board. Alternative sources of reset are:

• the CBUS FPGA, when a “magic” value is written to the SOFTRES register

• the EJTAG probe system reset signal (EJRSTN)

• an incoming break on the tty0 port (J6). This break may be disabled by software.

All resets are the same - there is no difference between a “warm” and a “cold” reset. All hardware, including hardware driven by stand-by voltages, are reset at reset.

5.5 Clocks

The PCI clock normally runs at 33 MHz, generated from a 14.31818 MHz crystal using a clock synthesizer/driver

(U13). The PCI clock can be configured via JP4 (see Table 4.1).

This will not affect the clock frequency of a CPU mounted on its Core Board; the Core Board generates its own clock.

5.4 Reset

The Malta Board contains the following clocks:

• RTC (32.768 KHz)

• CBUS UART (tty2) (3.6864 MHz)

• ISA Environment (14.31818 MHz)

• Ethernet (25 MHz)

• PCI clock (33 MHz - configurable to 10, 12.5, 16.67, 20, 25, 30, 33.33 and 37.5 MHz)

• CBUS FPGA (40 MHz)

• USB (48 MHz)

5.6 Interrupt Controller

The interrupt controller is located in the South Bridge device. An NMI interrupt controller (for South bridge NMI and

ON/NMI button) is located in the FPGA (see Section 3.2, "NMI Interrupts").

Interrupts routed to the South Bridge are triggered by the following devices:

• South Bridge internal devices (timer, real time clock, USB)

• Super I/O devices (keyboard, 2 UARTs, floppy disk, parallel port, mouse)

• Ethernet controller

• Audio controller

MIPS® Malta™ User’s Manual, Revision 01.07 33

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 34

Hardware Description

• Primary and Secondary IDE devices

• PCI slots 1..4

• SERR (PCI bus) and IOCHK (ISA bus) signals may trigger the South Bridge NMI interrupt

• Various power management related events in the South Bridge may trigger the South Bridge SMI interrupt

•I2C bus controller in the South Bridge may trigger either the South bridge SMI or IRQ9 interrupt

Interrupts routed directly to the Core Card are triggered by the following devices :

• Core card (COREHI, CORELO signals)

• Discrete 16550 UART device (CBUS UART (tty2))

Figure 5.2 shows the interrupt wiring. The figure does not include the connections of SERR from the PCI slots and

the Core Card to the South Bridge.

IRQ 0..15 from devices located in the Super I/O device are routed to the South Bridge using a serial connection.

PCI A..D interrupts including the South Bridge USB controller (using PCI D) are mapped on IRQ 0..15, which are

further multiplexed to South Bridge INTR.

Based on the interrupt sources, the South Bridge generates 3 interrupts : INTR, SMI, and NMI.

34 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 35

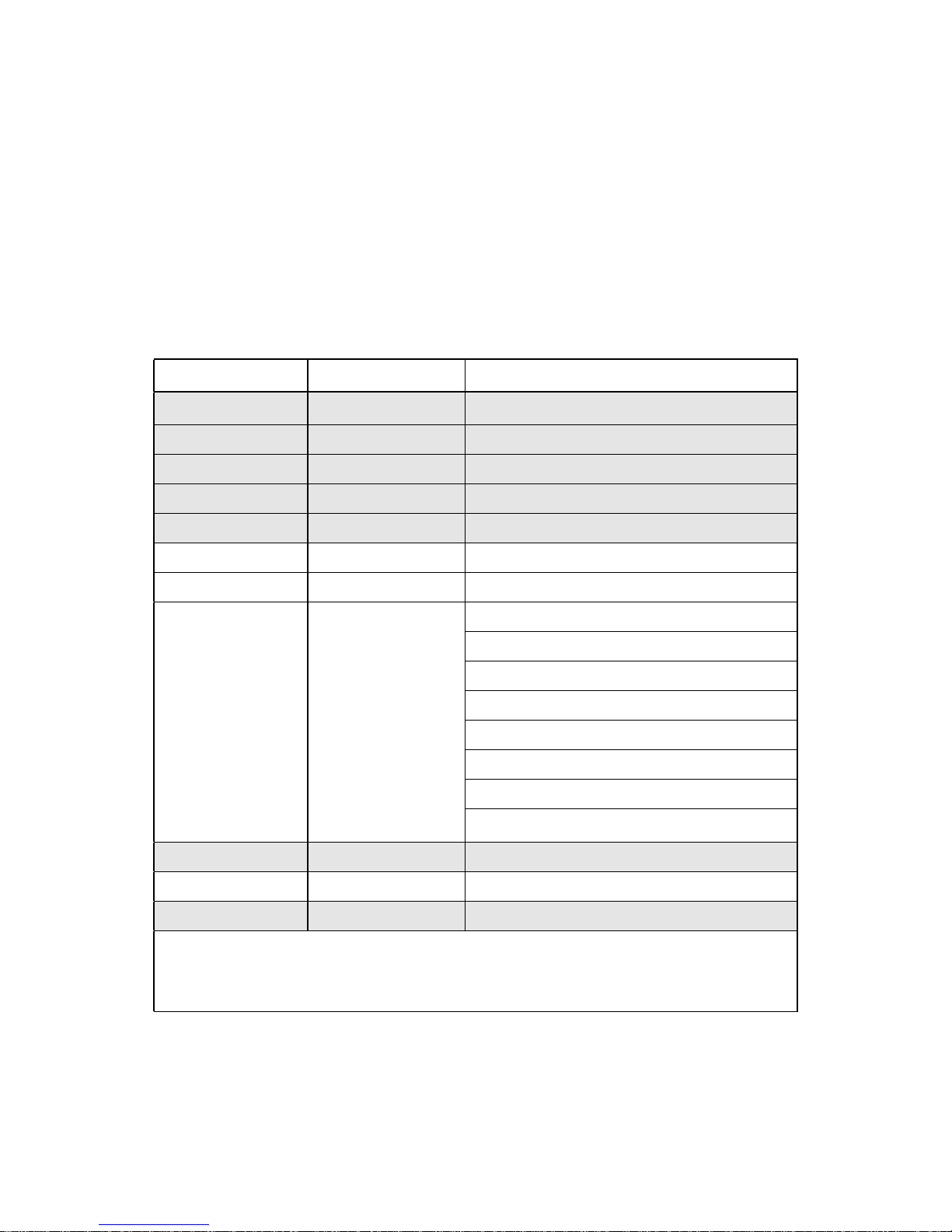

Figure 5.2 Interrupt Wiring

CORE Card

5.6 Interrupt Controller

PCI slots 4..1

A

B

C

D

A

B

C

D

Ethernet

Audio

Prim. IDE

connector

Sec. IDE/

Compact

Flash

connector

INT 0..5

A

B

C

D

A

B

C

D

PCI A

PCI B

PCI C

PCI D

INTR

SMI

South

Bridge

NMI

IRQ 14

IRQ 15

COREHI

CORELO

deasserted

INT 3

INT 4

INT 5

INT 0

INT 1

NMI

SuperI/O

tty2

ON/NMI

Serial IRQ

PwrBtn

INT 2

NMI Controller

Most sources of interrupt are handled in an interrupt controller located in the South Bridge. A few are handled in the

CBUS FPGA (COREHI, CORELO and CBUS UART (tty2) interrupt), this means that CPU and CBUS interrupt

sources can be handled before the PCI bus has been configured. Please use the macros in the header file to access all

registers and fields of the interrupt controller, as described in [3].

MIPS® Malta™ User’s Manual, Revision 01.07 35

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 36

Hardware Description

IRQ 0..15 are prioritized in the sequence : 0, 1, 8..15, 3..7. IRQ 2 is reserved for cascading the two 82C59 devices that

together constitute the South Bridge Interrupt Controller.

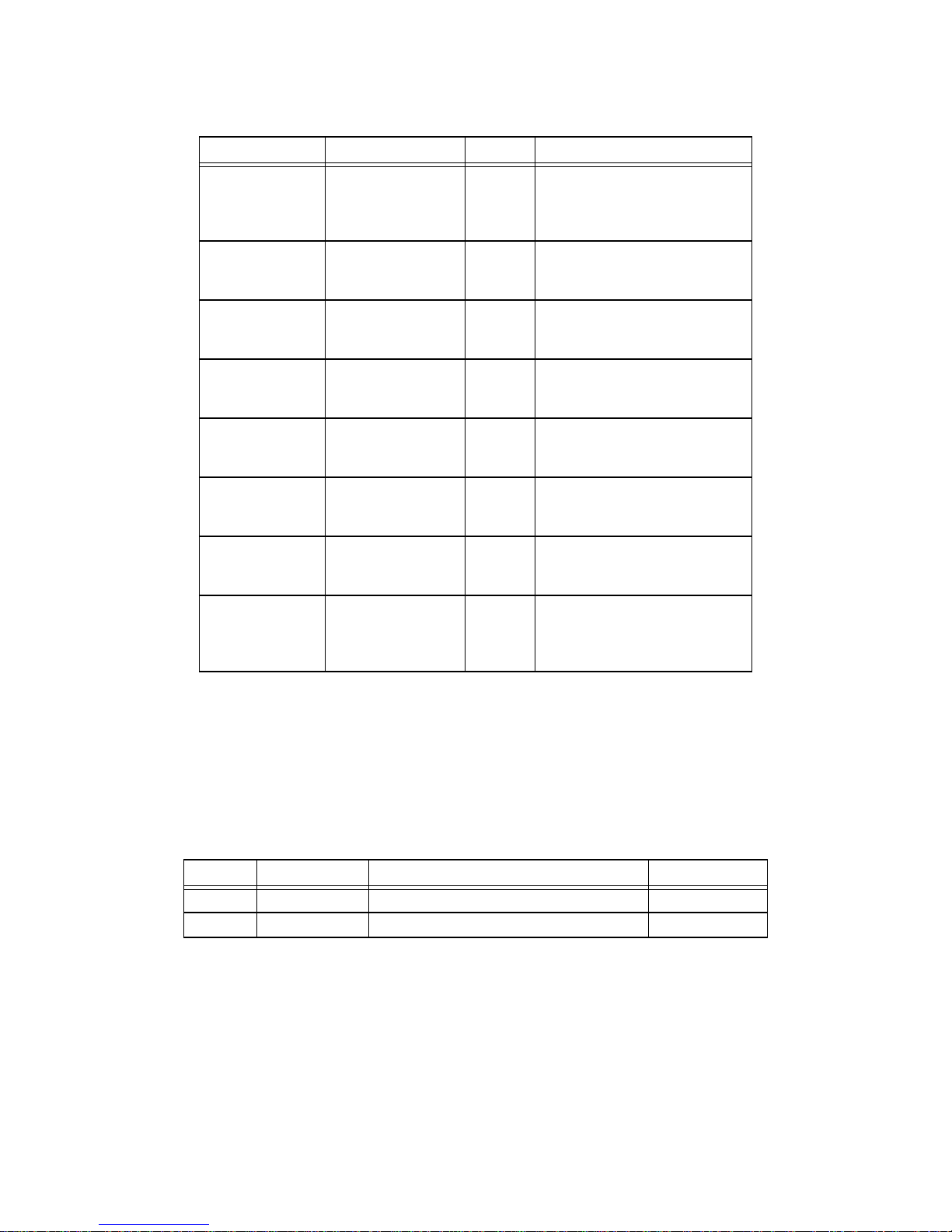

The mapping of IRQ 0..15, as used by YAMON, is shown in Table 5.2.

IRQ # Source(s) Device(s)

0 Timer South Bridge

1 Keyboard SuperI/O

2 Reserved by South Bridge (for cascading)

3 UART (tty1) SuperI/O

4 UART (tty0) SuperI/O

5 Not used

6 Floppy Disk SuperI/O

7 Parallel port (1284) SuperI/O

8 Real Time Clock South Bridge

Table 5.2 IRQ 0..15 Mapping

9

I2C bus

10 PCI A, PCI B (including Ethernet) PCI slot 1..4, Ethernet

11 PCI C (including audio),

PCI D (including USB)

12 Mouse SuperI/O

13 Reserved by South Bridge

14 Primary IDE Primary IDE slot

15 Secondary IDE Secondary IDE slot/Compact flash connector

South Bridge

PCI slot 1..4, Audio, USB (South Bridge)

The mapping of CPU INT0..5 and CPU NMI is shown in Table 5.3.

Table 5.3 CPU INT0..5 and CPU NMI Mapping

CPU INT/NMI Source(s) Device(s)

NMI South Bridge NMI or NMI button South Bridge or On/NMI Buttom

0 South Bridge INTR South Bridge

1 South Bridge SMI South Bridge

2 CBUS UART (tty2) Discrete 16550

3 COREHI Core Card

4 CORELO Core Card

5 Not used, driven inactive Typically used for CPU internal timer interrupt

36 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 37

5.7 Serial Ports

There are 2 serial ports (tty0 and tty1) on Malta which are available on the rear edge via standard, male DB9 connectors (J6). These ports are provided by the Super I/O. A third serial port (tty2) is available via a 10-pin header (J22).

This port is provided by the discrete 16550. The pinout of these connectors is shown below:

Each port is electrically identical, with the pinout shown in the table below allowing full hardware handshaking.

PIN NO (DB9) PIN NO (10-pin) Name Direction

5.7 Serial Ports

Table 5.4 Serial Port Pinouts

1 1 CD Input

2 3 RXD Input

3 5 TXD Output

4 7 DTR Output

5 9 GND

6 2 DSR Input

7 4 RTS Output

8 6 CTS Input

9 8 RI Input

10 No Connect

The following 5-wire symmetric wired cable must be used to guarantee correct operation of the hardware flow control, which is used by YAMON. Pin connections between the two, 9-pole male connectors (for a standard PC serial

port):

• 2 to 3 (RXD to TXD)

• 3 to 2 (TXD to RXD)

• 5 to 5 (GND to GND)

• 7 to 8 (RTS to CTS)

• 8 to 7 (CTS to RTS)

5.7.1 File Download

The recommended data terminal program for PCs running Windows OS is Procomm Plus32 from DATASTORM

TECHNOLOGIES. Here is the setup sequence for simple Motorola S-record file downloads:

Communication settings in the menu area:

• Options->SystemOptions->ModemConnection->System

MIPS® Malta™ User’s Manual, Revision 01.07 37

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 38

Hardware Description

Now select the ‘com’ port and click on the ‘Modem/ConnectionProperties’ to set the ‘baudrate’(=38400), ‘parity’(=none), data bits(=8), stop bits(=1) and important select ‘use hardware flow control’.

Download protocol setting in the menu area:

• Options->SystemOptions->ModemConnection->Data

Now set ‘current transfer protocol’ to ‘ASCII’, set all delays to ‘0’ and set the CR/LF options to ‘don’t translate

CR/LF’. The file to be downloaded (to Malta) is selected via the path:

• Data->SendFile

5.7.2 Serial Port Reset

The tty0 port (J6) can be used to reset the Malta Board. By default, a “Break” condition on the tty0 port for more than

10 ms will reset the board, exactly as if the reset button had been pressed. This functionality can be disabled, or the

time can be changed to a different value by programming the BRKRES register in the CBUS FPGA (see Section 3.6,

"Reset Control").

5.8 Ethernet

The Ethernet controller (U41 [8]) supports both 10base-T and 100base-TX standard on a twisted pair connection via

the rear panel connector J5. The device has an integrated PHY section and is capable of auto-negotiating the line

speed/duplex with the far end. Its MAC address is stored in the locally-connected EEPROM (U39) and must not be

altered.

Note: Only 10BASE-T is supported (100BASE-TXis not) for PCI clocking frequencies below 33.33 MHz (see Table

4.1).

See Section 4.3, "Displays / LEDs" for a description of the Ethernet LEDs, which are built into the RJ45 connector

and the on-board LEDs.

The ethernet controller supports Wake On LAN for remote wake-up. For additional information, see [8].

5.9 USB

Two host USB ports are available on a double connector (J5) on the rear edge of the board. These are controlled

through the South Bridge[6].

5.10 Keyboard / Mouse / IEEE1284 Parallel Port / Floppy Disk

These functions are provided by the Super I/O chip (U11)[9]. The PC keyboard and mouse are on a double mini-DIN

connector (J7), and the parallel (1284) port is on a 25-pin DSUB connector (J6), both on the rear board edge. The

floppy disk connector is header J21.

The parallel port also allows the user to reprogram the Flash memory, which is usually only done for production or

software upgrades. See Section 5.13, "Flash Memory".

The Super I/O supports one floppy disk, connected via a 34 wires ribbon cable (7 wires twisted, PC-style).

38 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 39

5.11 Real Time Clock (RTC)

The South Bridge (U9) contains the Real Time Clock for the board [6]. The clock has an external battery backup

(CR2032 coin cell) (J10), which has an expected life time of 5-10 years.

5.12 IDE/CompactFlash (True IDE Mode)

The South Bridge (U9) provides both primary and secondary IDE busses [6]. The primary bus is brought out on connector J18, and may have both master and slave devices attached. The secondary bus connects both to the Compact

Flash connector J20 (Type I or II connector) and to the secondary IDE connector J19. Jumper JP3 selects whether the

Compact Flash module behaves as (if fitted) a master or (if not fitted) as a slave device. If a Compact Flash module is

used, any device plugged into the secondary IDE connector must have the opposite setting.

For additional information about Compact Flash modules, see [15].

5.13 Flash Memory

Malta is fitted with 4 Mbytes of Flash memory (refered to as Monitor Flash), which is used to boot the system. See

Chapter 3, “Memory Map” on page 13 for details of the Malta memory map.

5.11 Real Time Clock (RTC)

The Monitor Flash can be programmed via a download cable, as described in Chapter 6, “1284 Flash Download

Format” on page 45.

The Monitor Flash can also be reprogrammed by software. There is one protection mechanism:

• Jumper JP1 (See Section 4.1, "Connectors & Jumpers") must be installed for any writing to the Monitor Flash

Lock Bits from software.

Note that while the Monitor Flash is being reprogrammed by software, the code that performs the reprogramming

will have to be copied into RAM and executed there, because the Flash is inaccessible during this process.

All the Flash fitted are Intel 16 Mbit FlashFile devices. See Intel’s web site for the documentation, or see YAMON

documentation [3] for an easy-to-use software interface.

From a hardware viewpoint, the Flash appears as a 32-bit wide block, with no individual write control capability to

allow writing to just one, 16-bit halfword. However, this function can be achieved by software by running a

Read-Modify-Write cycle.

5.14 EEPROM

The I2C-connected EEPROM (U14) contains, on manufacture, the board serial number. The remaining locations in

the EEPROM are not available for application use.

A second EEPROM (U39) is directly connected to the Ethernet controller and is used to store the board’s MAC

address.

MIPS® Malta™ User’s Manual, Revision 01.07 39

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Page 40

Hardware Description

5.15 AMR (Audio Modem Riser)

Connector J16 is an AMR connector [14] that allows an audio/modem interface card to be plugged into the motherboard. This is controlled via U23, a PCI Audio controller [7]. The AMR connector is a dual AC’97 audio codec interface.

5.16 Front Panel Connector

The Front Panel connector (J9), shown in Figure 5.3, contains all signals to/from the front panel of a normal PC-chassis. An additional connector (J30) is available for a three-pin Power LED connector.

Figure 5.3 Front Panel Connector

J9

HD LED

Reset Button

Reserved

5.17 Debug Access

5.17.1 Software Debug

The EJTAG connector (J17) allows connection of a suitable EJTAG debugger probe directly to the CPU. This allows

access to the internal hardware debug functionality of the CPU core. See [4] for details.

12

++

Power LED

On/NMI Button

Reserved

+5V

J30

1

+

Power LED

-

5.17.2 Hardware Debug

You have access to most, if not all, interesting signals on the Malta Board via testpoints (Table 5.5) and HP Logic

Analyser high-density connectors (Table 5.6). Refer to the tables below and the schematics for details of these.

Ref Silkscreen Color Function

TP1 D3V3SB Red Digital 3.3V Stand-by

TP2 D5VSB Red Digital 5V Stand-by rail

TP3 D3V3 Red Digital 3.3V rail

40 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

Table 5.5 Testpoints

Page 41