Page 1

SmartFusion Development Kit

User’s Guide

Page 2

SmartFusion Development Kit

Table of Contents

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Kit Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

SmartFusion Development Kit Web Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Board Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1 Installation and Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Software Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Hardware Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2 Hardware Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

SmartFusion cSoC Description and Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

I/O Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

SmartFusion cSoC Hard ARM Cortex-M3 Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Power Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3 Components Description and Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

VAREF Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Current Sensing Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

PWM Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Push-Button System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Push-Button, DIP Switches, and User LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

One-Bit DAC (OBD) Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

OLED Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

SPI Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

SPI DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2

C EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

I

Clock Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

USB-to-UART Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

RS485 Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Ethernet Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Memory Section Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Using EMC I/Os as User I/Os . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Controller Area Network (CAN) Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Ethernet for Control Automation Technology (EtherCAT) Interfa ce . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Low Cost Programming Stick (LCPS) Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

RealView Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Direct-C Programming Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

FlashPro4 Programming Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

A2F500 Digital I/O Expansion Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Mixed Signal Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4 Pin List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Pin List for A2F500M3G-FGG484ES Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5 Board Stackup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Revision 7 2

Page 3

Table of Contents

A2F500-DEV-KIT-2 Board Stack-Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

6 Manufacturing Test. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

A2F500-DEV-KIT-2 Board Testing Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Jumper Settings for the Board Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Installing the A2F500-DEV-KIT-2 Board USB Serial Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Hooking up the Board and Programming Stick . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Programming the A2F500-DEV-KIT-2 Board (SmartFusion cSoC Device) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Setting Up the Test Terminal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Running the A2F500-DEV-KIT-2 Board Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

A2F500-DEV-KIT-2 Board Failures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

A List of Changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

B Product Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Customer Service . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Customer Technical Support Center . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Website . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Contacting the Customer Technical Support Center . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

ITAR Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

3 Revision 7

Page 4

Page 5

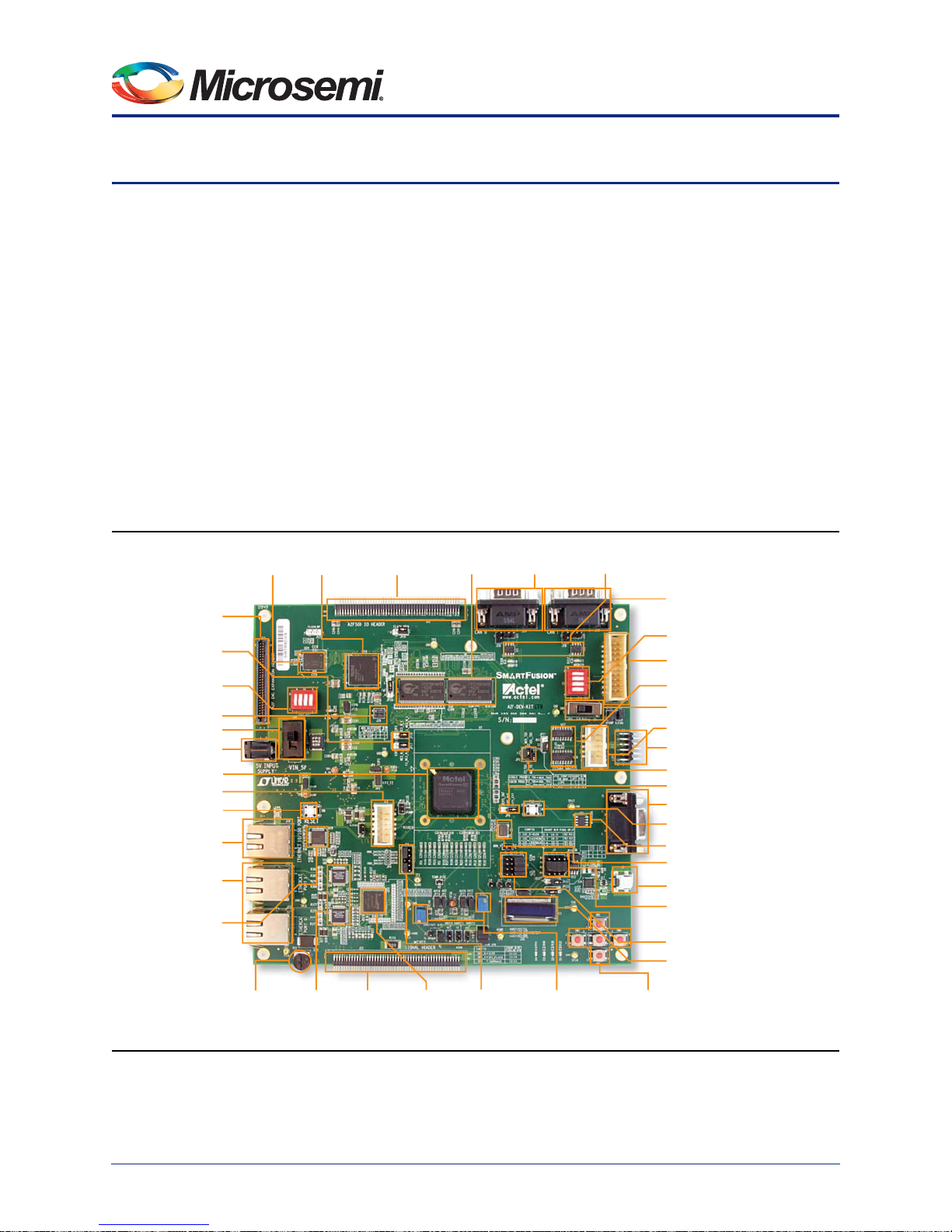

Introduction

DirectC Header

Board Reset Switch

Power Jack

Memory Device

Configuration Headers

AGLP DIP Switch

AGLP125V5-

CSG289

IGLOO PLUS Header

10/100 Ethernet PHY

RJ45 Connector for

10/100 Ethernet

AGLP Header

DACOUT/

ADC Headers

RJ45 Connectors for

EtherCAT Ports

SmartFusion Device

DB9 Connector

for CAN0

SRAM

(3.3 V)

CAN

Transceivers

DB9 Connector

for CAN1

A2F500

Connector

PSRAM

(1.8 V)

LCPS Connector

FlashPro Header

DIP Switch

JTAG_SEL Switch

JTAG Chain Configuration Header

1.5 V Header

PUB Switch

RS485 Transceiver

DB9 Connector for RS485 (UART1)

50 MHz Oscillator

SPI Headers

I

2

C Headers

USB Connector for UART0

OLED

Push-Button

Switches

RealView

®

Header

JTAG MUX

EtherCAT

PHYs

DAC0 and DAC1

Callibration POTs for

±15 V Bipolar Outputs

POT for

Current Monitor

Mixed-Signal

Header

EtherCAT

ASIC

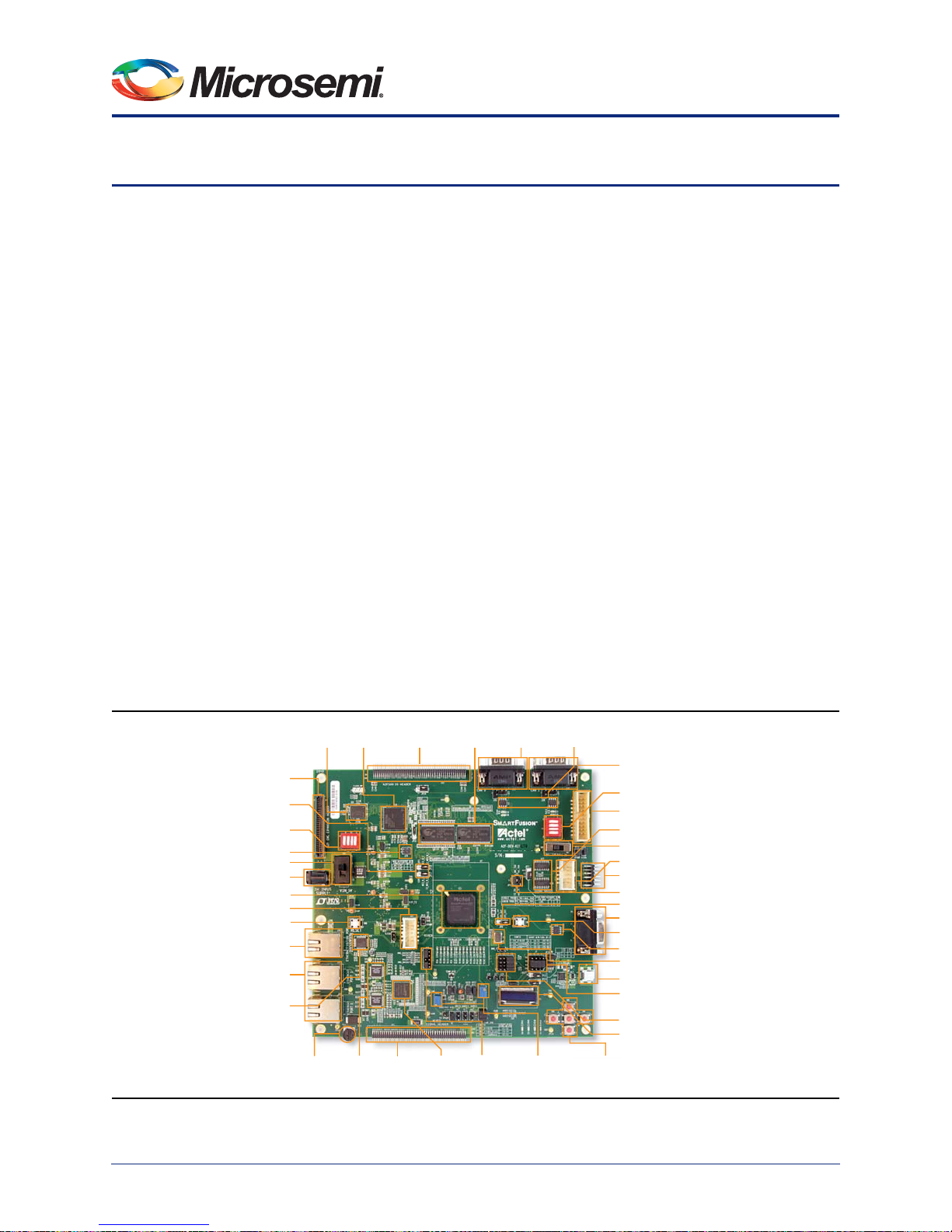

The RoHS-compliant SmartFusion® Development Kit (A2F500-DEV-KIT -2) enables designers to develop

applications that involve one or more of the following:

• Microcontroller applications

• Real-time operating system (RTOS)/OS development

• Embedded ARM

• Motor control

• System management

• Power sequencing, trimming, and management

• Touch screen display control

• Audio processing

•FieldBus

•EtherCAT

• Industrial network

The board also provides a standard 100-pin mixed signal header for interfacing to the analog pins. This

provides access for plugging in a daughter board with a mixed signal interface.

®

Cortex™-M3 processor based systems

®

demonstrator

®

Figure 1 • A2F500-DEV-KIT-2

Revision 7 5

Page 6

Introduction

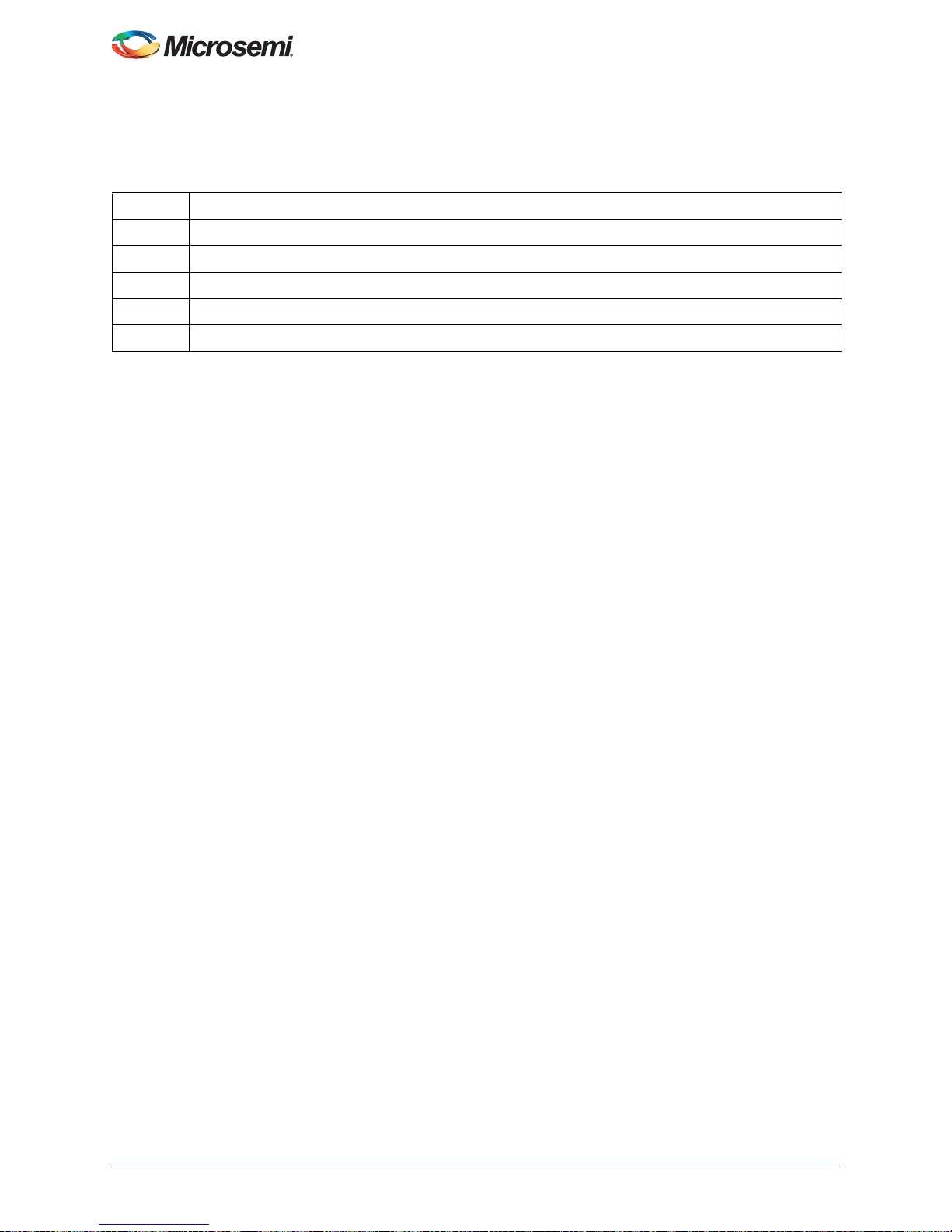

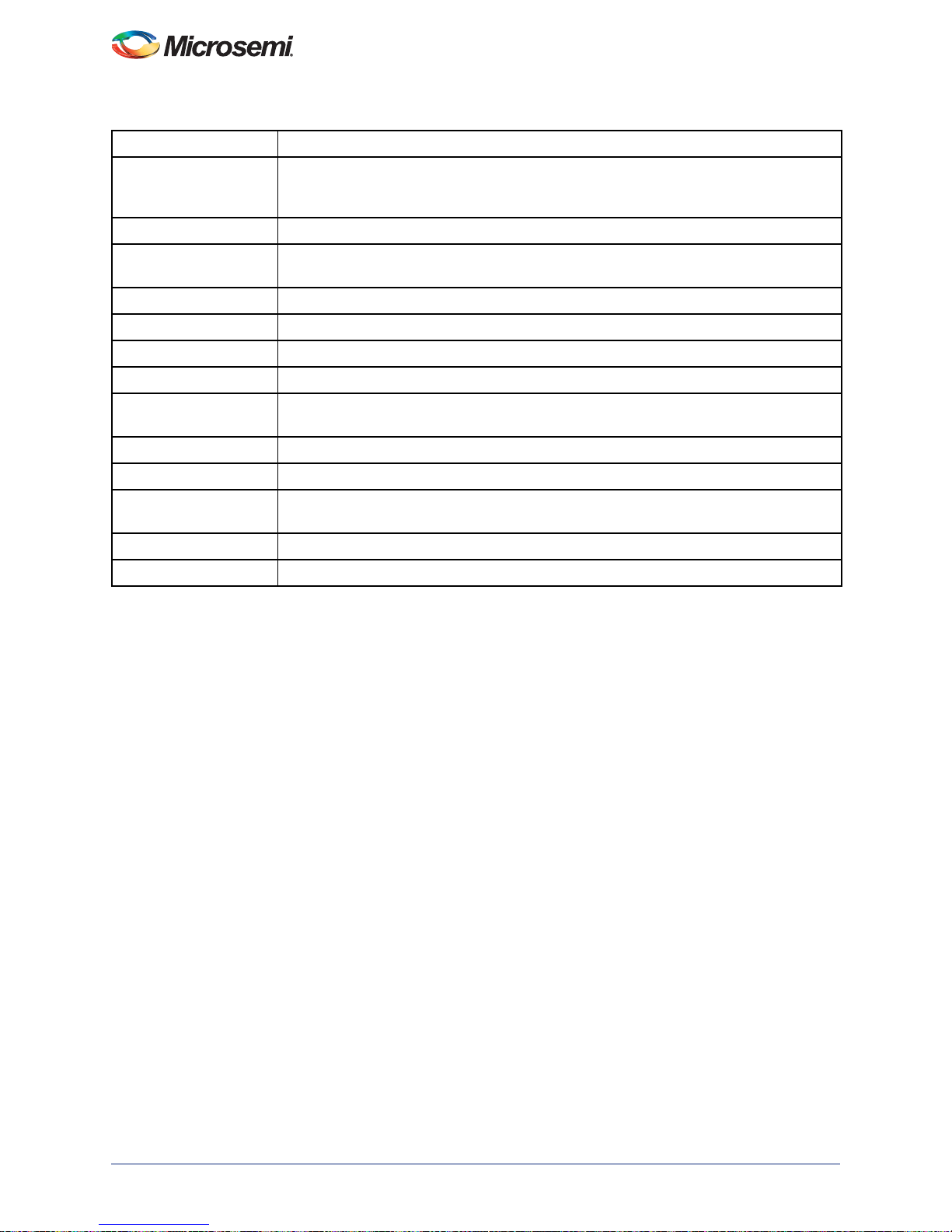

Kit Contents

Table 1 lists the contents of the SmartFusion Development Kit.

Table 1 • Kit Contents – A2F500-DEV-KIT-2

Quantity Description

1 SmartFusion Development Board with SmartFusion A2F500M3G-FGG484ES device

1 Low-cost programming stick (LCPS) or FlashPro 4 programmer

1 5 V power supply with international adapters

2 USB 2.0 A to mini-B cable

1 Quickstart card

SmartFusion Development Kit Web Resources

The SmartFusion Development Kit web resources are available on the Microsemi website:

www.microsemi.com/soc/products/hardware/devkits_boards/smartfusion_dev.aspx#rsc.

Board Description

The SmartFusion Development Kit Board is designed to pro vide a development platform for users to

evaluate all the features of the world’s only customizable system-on-chip (cSoC) with a hard ARM

Cortex-M3 processor powered microcontroller subsystem (MSS) along with programmable analog.

The board supports a SmartFusion cSoC device in an FG484 package. To enable the MSS, analog, and

evaluation of features, the board includes the following:

• Ethernet, EtherCAT, and USB-to-UART interface for communication with Ethernet and UART

peripherals of the SmartFusion MSS

• Static random access memory (SRAM), parallel flash, SPI flash, and electrically erasable

programmable read-only memory (EEPROM) that interface with EMC, SPI, and I2C peripherals of

the SmartFusion MSS

• Digital-to-analog converter (DAC) that interfaces either to SPI port 0 or SPI port 1 of the

SmartFusion MSS

• Organic light-emitting diode (OLED) that interfaces with either SPI or I

SmartFusion MSS

•I2C interface and temperature monitoring

• Mixed signal header for daughter card interfacing

• RealView ICE Simulation Unit (RVI) header for application programming and debug from either

®

Keil

ULINK® or IAR J-link

The board includes a FlashPro4 programming header to enable programming and debugging from

Microsemi design tools FlashPoint and SoftConsole.

®

2

C peripherals of the

6 Revision 7

Page 7

SmartFusion Development Kit

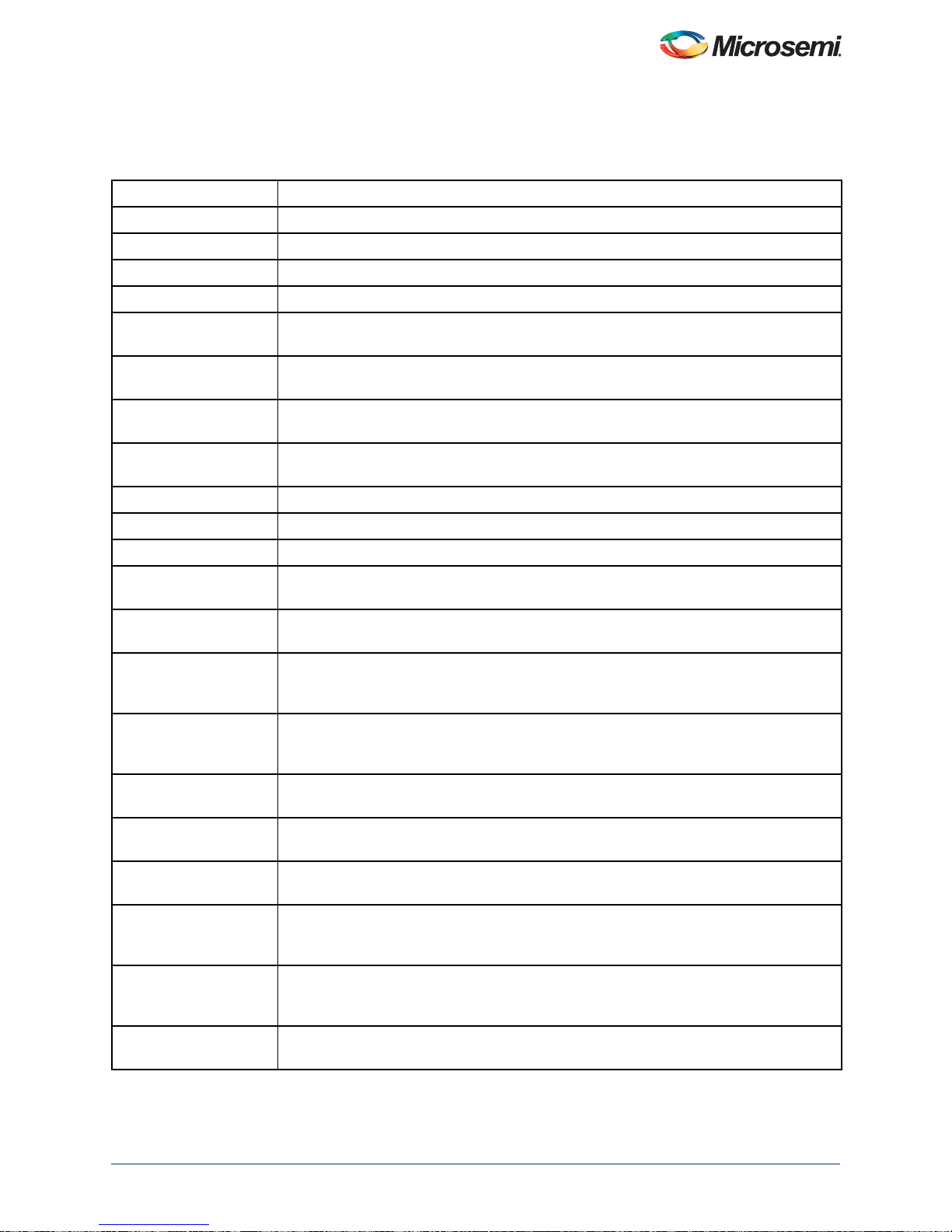

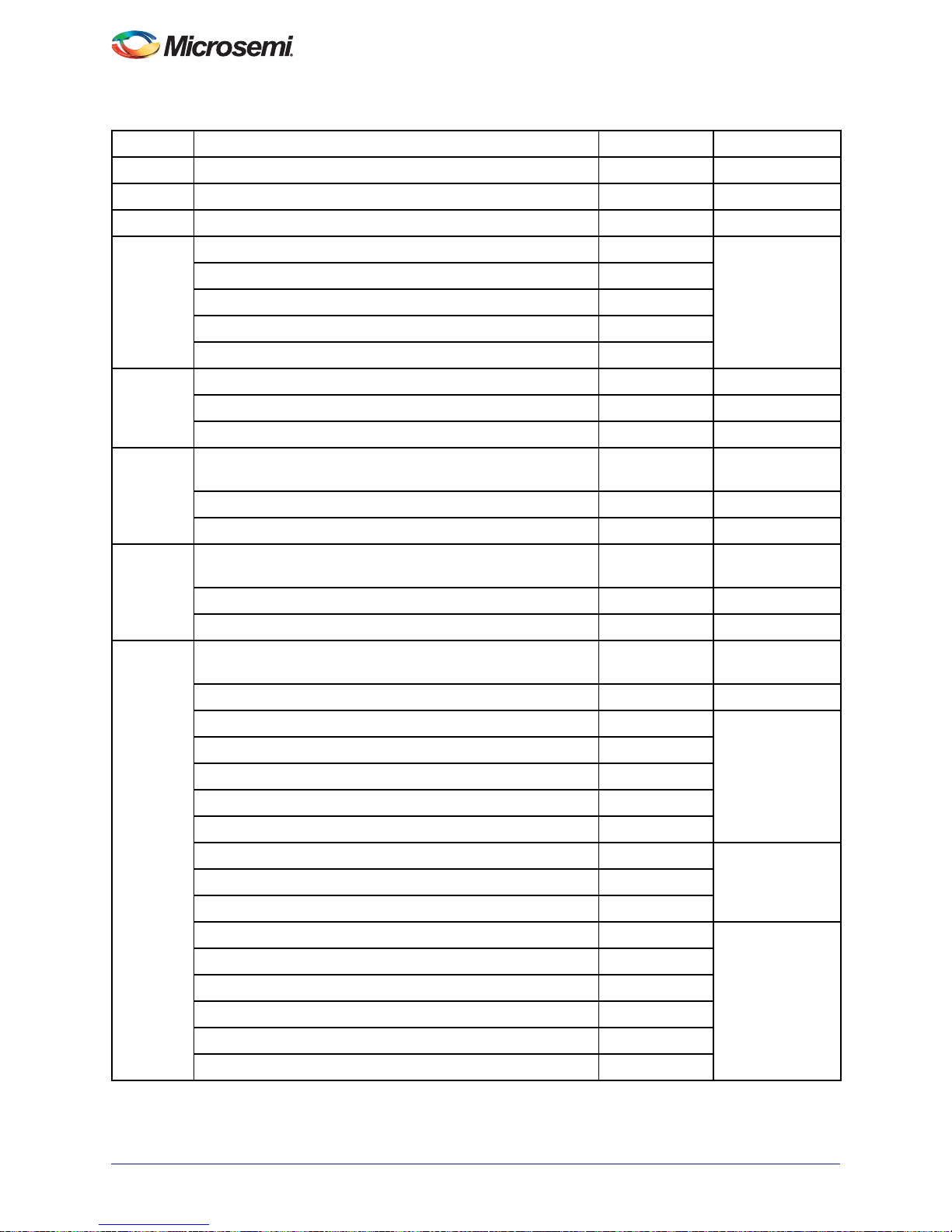

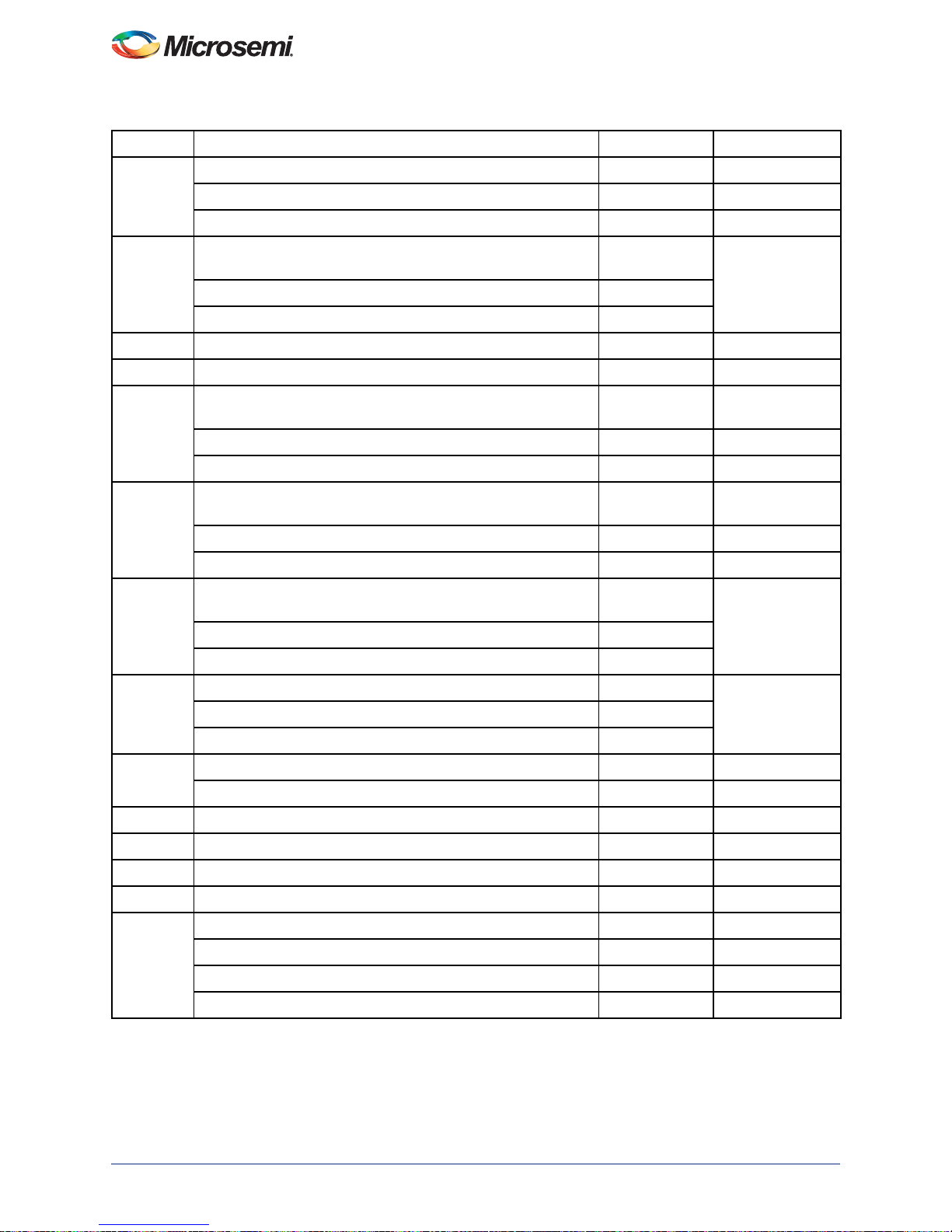

Table 2 describes SmartFusion Development Kit Board Components.

.

Table 2 • SmartFusion Development Kit Board Components

Name Description

A2F500M3G-FGG484ES Microsemi SmartFusion cSoC with hard ARM Cortex-M3 processor

CURRENT SENSING Current monitoring using thumbwheel POT (RV1)

PWM CIRCUIT Pulse Width Modulation Resistor Capacitor (PWMRC) circuit

OBD Three one-bit DACs used in comparator

OLED DISPLAY Organic 96×16 pixel

white OLED PMO18701 with option to interface to I

2

C port 0 or SPI

port 0 of the SmartFusion MSS

I2C EEPROM 512 Kbit I

2

C EEPROM ST M24512-WMN6TP connected to I2C port 1 of the SmartFusion

MSS

SPI FLASH 8 MByte SPI flash Atmel AT25DF641-MWH-T connected to SPI port 1 of the SmartFusion

MSS

SPI DAC 12-bit SPI DAC AD5320 with option to interface either to SPI port 0 or SPI port 1 of the

SmartFusion MSS

OSC-50 50 MHz clock oscillator

OSC-20 20 MHz/20 PPM clock oscillator

OSC-32 32.768 KHz low power oscillator

USB/UART USB-to-UART adapter chip CP2102 and connector interfacing with UART Port 0 of the

SmartFusion MSS

RS485 RS485 with DB9 female connector interfacing with MAX3240CSA, connected to UART

port 1 of the SmartFusion MSS

ETHERNET RJ45 connector (Ethernet jack with magnetics) interfacing with National Semiconductor

10/100 PHY chip DP83848C in RMII mode, interfacing with Ethernet port of the

SmartFusion MSS (on-chip MAC and external PHY)

®

AGLP125-CS289 IGLOO

PLUS FPGA implementing level converter between 3.3 V and 1.8 V to connect

1.8 V PSRAM/flash with external memory controller (EMC, which has native voltage level

of 3.3 V) of the SmartFusion MSS

EXPANSION When external memory controller (EMC) is not used, the I/Os are available as

3.3 V GPIOs.

Asynchronous SRAM Two 16-Mbit SRAM Cypress CY7C1061DV33-10ZSXI connected to each region of the

EMC interface of the SmartFusion MSS

FLASH Two 64-Mbit parallel flash memory Numonyx JS28F640J3D-75 connected to each region

of the EMC interface of the SmartFusion MSS

LG_PSRAM 128-Mbit, 1.8 V asynchronous PSRAM Micron MT45W8MW16BGX connected to the EMC

interface of the SmartFusion MSS. This provides the option of bigger memory as an

alternative to the SRAM for memory intensive applications.

LG_FLASH 128-Mbit, 1.8 V, parallel flash memory Numonyx JS28F128P30T85 873824 connected to

the EMC interface of the SmartFusion MSS. This provides the option of bigger memory as

an alternative to the flash for memory intensive applications.

CAN_IF Two CAN interfaces with DB9 female connector interfacing with MAXIMMAX3051 CAN

transceiver connected to four GPIOs of the SmartFusion MSS

Revision 7 7

Page 8

Introduction

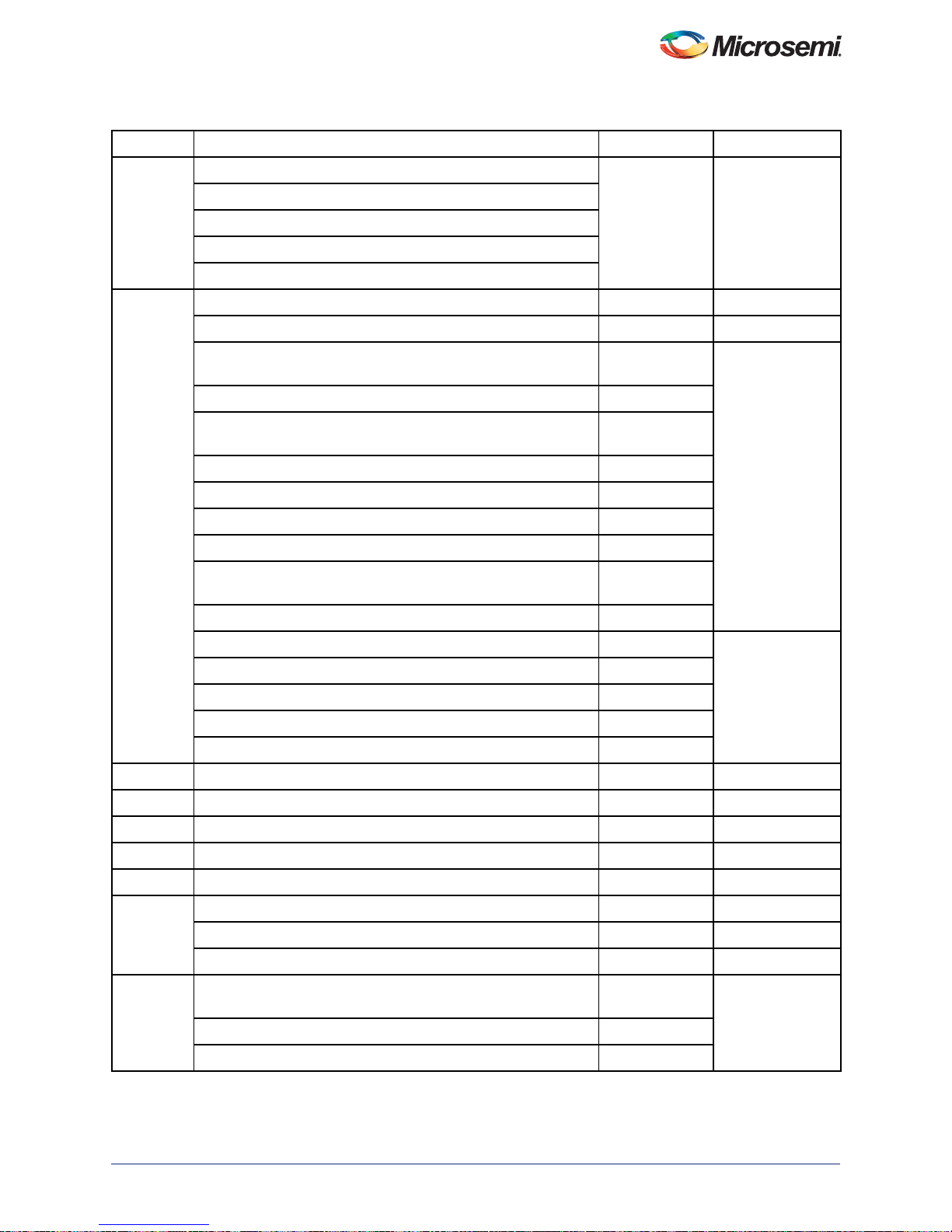

Table 2 • SmartFusion Development Kit Board Components (continued)

Name Description

ETHERCAT_IF Two RJ45 connectors (Ethernet jack with magnetics) for EtherCAT ports interfacing with

Beckhoff ET1 100 and Micrel KS8721BL and connecting to the SmartFusion cSoC via soft

SPI implemented in the fabric using six general purpose I/Os

RVI HEADER RVI header for application programming an d debug from Keil ULINK or IAR J-Link

FP4 Programming

HEADER

Flashpro4 programming header for FPGA and cSoC programming and debugging with

Microsemi tools

PROG HDR Direct-C programming header

TEMP DIODE Temperature diode

BATT BACKUP Battery backup circuit

DIPSWITCH Two 4-switch DIP switch packs for GPIO

LEDS Four active Low LEDs that can be connected to any user I/O for debug to power-on the

board

PUSH-BUTTON RESET Push-button system reset for SmartFusion System

MIXED_CONN100 To power-on the board mixed signal header

PUSH-BUTTON

Six push-button switches for test and navigation and PUB

SWITCHES

MIXED_CONN100 Mixed signal header

A2F500_CONN100 Microsemi SmartFusion A2F500M3F-FG484ES additional I/O connector

8 Revision 7

Page 9

1 – Installation and Settings

Software Installation

Download and install the latest release of Microsemi Libero® Integrated Design Environment (IDE), v9.0

or later, from the Microsemi website and register for your free Gold license. For instructions on how to

install Libero IDE and SoftConsole, refer to the Libero IDE Installation and Licensing Guide, available on

the Microsemi website. Refer to the Installing IP Cores and Drivers User’s Guide for download and

installation of Microsemi DirectCores, SGCores, and Driver firmware cores that must be localized on the

personal computer where Microsemi's Libero IDE is installed when designing with Microsemi FPGAs and

cSoCs. Microsemi has partnered with key industry leaders in the microcontroller space to provide the

robust SmartFusion ecosystem. Microsemi SmartFusion is supported by the latest release of IAR

Systems, the IAR Embedded Workbench for ARM. Refer to Designing SmartFusion with IAR Systems

document for more information. The Microsemi SmartFusion cSoC is also supported by the latest

release of Keil, the MDK-ARM Microcontroller Development Kit. Refer to the Designing SmartFusion with

Keil document for more information.

Hardware Installation

The FlashPro4 (FP4) programmer plugs directly into the A2F500-DEV-KIT-2 board. This allows

programming A2F500 and AGLP125 devices in chain mode or individually with appropriate jumper

settings (JP5).

Jumpers, Switches, LEDs and DIP Switch Settings

The recommended default jumpers, switches, LEDs, and dual in-line package (DIP) switch settings are

shown in Figure 1-1 and defined in Table 1-1 on page 10 through Table 1-4 on page 13. Connect the

jumpers with the default settings to enable the pre-programmed demonstration design to function

correctly.

IGLOO PLUS Header

Memory Device

Configuration Headers

AGLP DIP Switch

AGLP Header

Power Jack

SmartFusion Device

DirectC Header

Board Reset Switch

RJ45 Connector for

10/100 Ethernet

RJ45 Connectors for

EtherCAT Ports

10/100 Ethernet PHY

PSRAM

(1.8 V)

POT for

Current Monitor

AGLP125V5-

CSG289

EtherCAT

PHYs

A2F500

Connector

Mixed-Signal

Header

EtherCAT

ASIC

SRAM

(3.3 V)

DACOUT/

ADC Headers

DB9 Connector

for CAN0

Callibration POTs for

±15 V Bipolar Outputs

Transceivers

DAC0 and DAC1

CAN

DB9 Connector

for CAN1

DIP Switch

®

RealView

JTAG MUX

JTAG_SEL Switch

FlashPro Header

LCPS Connector

JTAG Chain Configuration Header

1.5 V Header

DB9 Connector for RS485 (UART1)

PUB Switch

RS485 Transceiver

50 MHz Oscillator

USB Connector for UART0

2

C Headers

I

SPI Headers

OLED

Push-Button

Switches

Header

Figure 1-1 • Jumper Locations

Revision 7 9

Page 10

Installation and Settings

Table 1-1 • Jumper Settings

Jumper Function Default Setting Notes

JP1 Jumper to select first 3.3 V power supply for board 1–2 Closed

JP2 Jumper to select second 3.3 V power supply for board 1–2 Closed

JP3 Jumper for SPI DAC output VOUT Open

JP4 Jumper settings to use comparator Pins 2, 6,10 are

Pin 3–4 = DACOUT0 to ADC0 Open

connected to

AGND

Pin 7–8 = DACOUT1 to ADC1 Open

Pin 1–3 = DACOUT0 to OBD_DACOUT0 Closed

Pin 7–9 = DACOUT1 to OBD_DACOUT1 Closed

JP5 Jumper for JTAG device option (A2F500 and AGLP125)

Pin 1–3 = A2F500 in chain Open

Pin 1–2 and Pin 4-3 = A2F500 and AGLP125 daisy chained Closed

JP6 Jumper to select either 1.5 V external regulator or SmartFusion

cSoC device 1.5 V internal regulator

Pin 1–2 = 1.5 V internal Open

Pin 3–2 = 1.5 V external Closed

JP7 Jumper to select between RVI header or LCPS header for

application debug

Pin 1–2 = LCPS for SoftConsole Closed

Pin 2–3 = RVI for Keil U-link/ IAR J-link Open

2

J7 Jumper/Header for SPI_0, I

C, EEPROM, OLED, and I2C

loopback

I2C0 to OLED

Pin 2–3 = I2C_0_SCL to OLED_SCL Closed Configuration 1:

Pin 14–15 = I2C_0_SDA to OLED_SDA_IN Closed

I2C0 -> OLED and

I2C1 -> EEPROM

I2C1 to EEPROM

Pin 6–7 = I2C_1_SCL to EEPROM_SCL Closed

Pin 10–11 = I2C_1_SDA to EEPROM_SDA Closed

I2C0 and I2C1 Loopback Configuration 2:

Pin 2–6 = I2C_0_SCL to I2C_1_SCL Open

I2C0 <-> I2C1

(Loop Back)

Pin 10–14 = I2C_1_SDA to I2C_0_SDA Open

SPI to OLED Configuration 3:

Pin 3–4 = SPI_SCK to OLED_SCL Open

SPI -> OLED and

I2C1 -> EEPROM

Pin 15–16 = SPI_SDA to OLED_SDA Open

I2C1 to EEPROM

Pin 6–7 = I2C_1_SCL to EEPROM_SCL Closed

Pin 10–11 = I2C_1_SDA to EEPROM_SDA Closed

10 Revision 7

Page 11

SmartFusion Development Kit

Table 1-1 • Jumper Settings (continued)

Jumper Function Default Setting Notes

J20 From AGLP125 CS289 Closed These pins are

Pin 1=AGLP_3.3V_SIG1

Pin 2=AGLP_3.3V_SIG2

brought out for

future and testing

purpose.

Pin 3=AGLP_3.3V_SIG3

Pin 4=AGLP_3.3V_SIG4

JP8 Jumper/Header for SPI, OLED, SPI flash, and loopback

SPI_0 to OLED

Pin 1–2 = SPI_0_OUT to OLED_SDA_IN (Need shunt pin 15–

Open Configuration 1:

16 jumper on J7)

Pin 5–6 = SDI_0_IN to OLED_SDA_OUT Open

Pin 9–10 = SCLK_0_OUT to OLED_SCL (Need shunt pin 3–4

Open

jumper on J7)

Pin 13–14 = SS_0_OUT to OLED_CS# Open

SPI_1 to SPI flash

Pin 3–4 = SDI_1_IN to SPI_1_SO (SO output of SPI flash) Closed

Pin 7–8 = SDO_1_OUT to SPI_1_SI (SI input of SPI flash) Closed

Pin 11–12 = SCLK_1_OUT to SPI_1_SCK (SCK input of SPI

Closed

flash)

Pin 15–16 = SS_1_OUT to SPI_CS_N (CS# input of SPI flash) Closed

SPI0 to SPI1 (loopback) Configuration 2:

Pin 2–3 = SDO_0_OUT to SDI_1_IN Open

Pin 6–7 = SDI_0_IN to SDO_1_OUT Open

Pin 10–11 = SCLK_0_OUT to SCLK_1_OUT Open

Pin 14–15 = SS_0_OUT to SS_1_OUT Open

JP11 Jumper to connect 3.3 V to VJTAG 1–2 Closed

JP12 Jumper to connect 3.3 V to VPUMP 1–2 Closed

JP13 VREF_OUT to OP_AMP (U44A & U51A) positive 1–2 Closed

JP14 OP_AMP (U44C) output to ABPS0 of FPGA fabric 1–2 Open

SPI_0 to OLED

and SPI_1 to SPI

flash

SPI0 and SPI1

loopback

JP15 OP_AMP (U44C) output to ABPS4 of FPGA fabric 1–2 Open

JP16 Jumper to control F*F of AGLP125 device

Pin 1–2 = F*F connected to 3.3 V (deasserted) Open

Pin 2–3 = F*F connected to GND (asserted) Closed

JP17 Jumper to select between 1.8 V and 3.3 V memory Interface

connected to region 0 of EMC

Pin 1–2 = 1.8 V interface Open

Pin 2–3 = 3.3 V interface Closed

To keep 3.3 V

devices tristated

Revision 7 11

Page 12

Installation and Settings

Table 1-1 • Jumper Settings (continued)

Jumper Function Default Setting Notes

JP18 Jumper to connect OLED_SDA_OUT and OLED_SDA_IN

2

Pin 1–2 = Closed for I

C configuration mode Closed

Pin 1–2 = Open for SPI mode

JP19 Jumper to select between 1.8 V and 3.3 V memory interface

connected to EMC

To keep 3.3 V

devices tristated

Pin 1–2 = 1.8 V interface Open

Pin 2–3 = 3.3 V interface Closed

JP20 Jumper to select positive 10 V power supply for board Closed

JP21 OP_AMP (U51C) output to ABPS1 of FPGA fabric 1–2 Open

JP22 Jumper to connect OLED_BS1 (MCU interface selection Input)

to 3.3 V or GND

2

Pin 1–2 = 3.3 V (needed for I

C mode) Open

Pin 2–3 = GND (needed for SPI mode) Closed

JP23 Jumper to connect OLED_BS2 (MCU interface selection input)

to 3.3 V or GND

Pin 1–2 = 3.3 V Closed

Pin 2–3 = GND (needed for both I2C & SPI modes) Open

JP24 Jumper to connect FLASH_VPEN of 64-Mbit parallel flash

connected to both regions of EMC

Identified as

FLASH

Pin 1–2 = FLASH_VPEN to 3.3 V (enabled) Closed

Pin 2–3 = FLASH_VPEN to GND (disabled) Open

JP25 Jumper to connect FLASH_WP# of 128-Mbit parallel flash Identified as

Pin 1–2 = FLASH_WP# to 1.8 V (disabled) Open

LG_FLASH

Pin 2–3 = FLASH_WP# to GND (enabled) Closed

JP26 Jumper to connect WE_N of EEPROM to 3.3 V

Pin 1–2 = 3.3 V (EEPROM write disabled) Closed

JP27 OP_AMP (U51C) output to ABPS5 of FPGA fabric

JP28 Jumper to select 1.8 V power supply for board 1–2 Closed

JP30 Jumper to connect VJTAG of PROG HDR to 3.3 V Open

JP31 Jumper to connect VPUMP of PROG HDR to 3.3 V Open

J32 VAREFOUT to ADC0, ADC1, ADC2 VAREF inputs

1–2 VAREFOUT to VAREF0 Closed

3–4 VAREFOUT to VAREF1 Closed

5–6 VAREFOUT to VAREF2 Closed

12 Revision 7

Page 13

SmartFusion Development Kit

Table 1-2 • SmartFusion Development Kit LEDs

LED SmartFusion Pin Comment

D1 B19 Test LED for user application

D2 B20 Test LED for user application

D3 C19 Test LED for user application

D4 H17 Test LED for user application

D5 N/A 5 V Power Supply Indicator LED. This LED is ON when board is powered on

D6 N/A SPEED LED: The LED is ON when device is in 100 Mbps and OFF when in 10 Mbps.

D8 N/A UART over USB link indicator LED

Table 1-3 • SmartFusion Development Board DIP Switches

DIP Switch (S1) SmartFusion Pin Comment

DIP1 H20 Test switch for user application

DIP2 C21 Test switch for user application

DIP3 D21 Test switch for user application

DIP4 F19 Test switch for user application

Table 1-4 • SmartFusion Development Kit Test Points

T est Point Comment

TP1, TP12 5 V power supply (measures 4.3 V due to diode drop)

TP2, TP5, TP6, TP7, TP8 Digital ground (GND)

TP3, TP4, TP13 Analog ground (AGND)

TP9 10 V rail for OLED

TP10 3.3 V supply for SmartFusion

TP11 3.3 V analog supply

Table 1-5 • SmartFusion Development Kit Push-Button Switches

Push-Button Switch SmartFusion Pin Comment

SW1 G19 Test and navigation switch

SW2 G20 Test and navigation switch

SW3 G21 Test and navigation switch

SW4 E1 Tes t and navigation switch

SW5 E14 Test and navigation switch

SW6 N/A Switch ON 5 V DC into SmartFusion cSoC device regulators

SW7 W7 Push-button switch for PUB. This negative active switch is connected to

the PUB pin, which is a digital input to the FPGA fabric. PUB is the

connection for the external momentary switch used to turn on the 1.5 V

voltage regulator.

SW8 R1 System reset for DUT

SW9 R16 (JTAGSEL) Switch to select A2F500 programming with FlashPro4 or Cortex-M3

processor debug. OFF position selects A2F500 programming and ON

position selects Cortex-M3 processor for application debug.

Revision 7 13

Page 14

Installation and Settings

Testing the Hardware

If the board is shipped directly from Microsemi, it contains a test program that determines whether the

board works properly. If while using the board you suspect that the board is damaged, you can rerun the

"Manufacturing Test" on page 79 to verify the key components of the board functionality.

14 Revision 7

Page 15

2 – Hardware Components

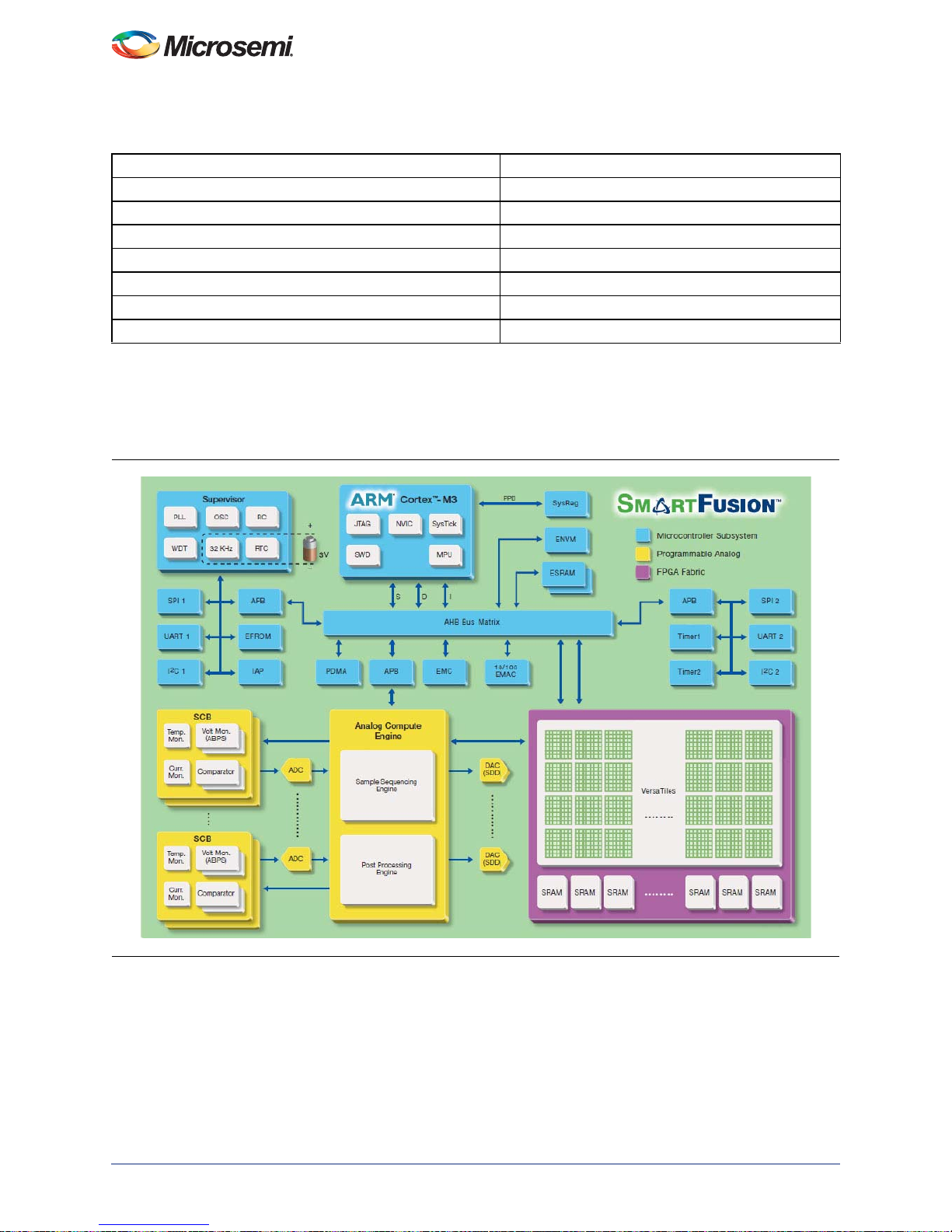

SmartFusion cSoC Description and Connections

The SmartFusion Development Kit Board is populated with a SmartFusion A2F500M3G-FGG484ES, the

world’s only cSoC with hard ARM Cortex-M3 processor. The key features of the SmartFusion cSoC are

listed below and in Table 2-1 on page 16.

The MSS consists of the following:

• 100 MHz 32-Bit ARM Cortex-M3 1.25 DMIPS/MHz throughput from zero wait state memory

• Internal memories

– Embedded flash memory (eNVM), 64 Kbytes to 512 Kbytes

– Embedded high-speed SRAM (eSRAM), 16 Kbytes to 64 Kbytes, implemented in two physical

blocks to enable simultaneous access from two different masters

• Multi-layer AHB communications matrix

– Provides up to 16 Gbps of on-chip memory bandwidth

• 10/100 Ethernet MAC with RMII interface

• Programmable external memory controller, which supports:

– Asynchronous memories

– NOR flash, SRAM, PSRAM

– Synchronous SRAMs

•Two I

• Two 16550 compatible UARTs

• Two SPI peripherals

• Two 32-bit timers

• 32-bit watchdog timer

• 8-Channel DMA controller

• Clock sources

• High-performance FPGA fabric

• Based on Microsemi's proven ProASIC

• Analog front-end (AFE)

• Up to three 12-Bit SAR ADCs

• One first-order ΣΔ DAC (sigma-delta) per ADC

• Up to five new high-performance analog signal conditioning blocks (SCB) per device

• Two high-speed comparators

• Analog compute engine (ACE)

2

C peripherals

– 1.5 MHz to 20 MHz main oscillator

– Battery-backed 32 KHz low-power oscillator with real-time counter (RTC)

– 100 MHz embedded RC oscillator 1% accurate

– Embedded PLL with 4 ou tput phases

®

3 FPGA fabric

– Offloads CPU from analog initialization and processing of ADC, DAC, and SCBs

– Sample sequence engine for ADC and DAC parameter set-up

– Post-processing engine for functions such as low-pass filtering and linear transformation

Revision 7 15

Page 16

Hardware Components

Table 2-1 • A2F500 I/Os

Device Package

A2F500 FG484

Direct analog input 12

Total analog input 32

Total analog output 3

MSS I/Os

FPGA I/Os 128

Total I/Os 204

Notes:

1. 16 MSS I/Os are multiplexed and can be used as FPGA I/Os, if no t needed for the MSS. These I/Os support

2. 9 MSS I/Os are primarily for 10/00 Ethernet MAC and are also multiplexed and can be used as FPGA I/Os if

1, 2

Schmitt triggers and support only LVTTL and LVCMOS (1.5 / 1.8 / 2.5, and 3.3 V) standards.

Ethernet MAC is not used in a design. These I/Os support Schmitt triggers and support only LVTTL and LVCMOS

(1.5 / 1.8 / 2.5, and 3.3 V) standards.

41

Figure 2-1 • SmartFusion Block Diagram

I/O Pin Connections

The pin list is provided in the "Pin List" section on page 61.

16 Revision 7

Page 17

SmartFusion Development Kit

SmartFusion cSoC Hard ARM Cortex-M3 Processor

The SmartFusion cSoC comes with a hard Cortex-M3 advanced processor-based MSS. The ARM

Cortex-M3 microcontroller is a low power processor that features low gate count, low predictable

interrupt latency, and low-cost debug. It is intended for deeply embedded applications that require fast

interrupt response features. SmartFusion cSoCs use the R1P1 version of the Cortex- M3 processor core.

Some of the important subsystems are listed below:

• Memory protection unit (MPU)

• Single-cycle multiplication and hardware divide

• JTAG debug (4 wire), Serial Wire Debug (SWD – 2 wire) and serial wire viewer (SWV) interfaces

The development board is populated with components to enable development using the MSS. These

components include SRAM, PSRAM, flash, SPI flash, I2C, EEPROM, OLED, SPI DAC, communication

interfaces such as Ethernet, and USB-to-UART.

Revision 7 17

Page 18

Hardware Components

Power Sources

This board is powered through an external 5 V power supply brick.

SmartFusion Power Sources

Seven voltage rails (10 V, 5 V, 3.3 V, 1.8 V, 1.5 V, and ± 15 V) are provided on the board:

• A single regulator, Linear LT3684EMSE (3.3 V, 2 A), supplies both analog and digital 3.3 V going

to the SmartFusion cSoC device. Sufficient isolation is provided through low-pass filter and layout

to prevent noise from the digital domain to propagate to the analog domain.

• Linear LT3684EMSE (1.8 V, 2 A), supplies 1.8 V rails.

• Linear LT3684EMSE (1.5 V, 2 A), supplies 1.5 V rails.

• Linear LT1615 step-up converter supplies 10 V, 100 mA typical, for driving OLED.

• A single regulator, Linear L T1615, supplies both the +15 V and –15 V with 4 mA rating required by

the DAC comparators.

18 Revision 7

Page 19

3 – Components Description and Operation

VAREF_OUT

VAREF_1

VAREF_OUT

VAREF_OUT

VAREF_OUT

VAREF_0

VAREF_1

VAREF2

VAREF2

VAREF_0

AGND

AGND

AGND

AGND

AGND

C63

10uF

C63

10uF

12

J5

HEADER 1x2

J5

HEADER 1x2

2

4

6

1

3

5

J32

HEADER 3X2

J32

HEADER 3X2

C62

10uF

C62

10uF

1

J2

HEADER 1

J2

HEADER 1

12

J6

HEADER 1x2

J6

HEADER 1x2

C61

10uF

C61

10uF

C79

10uF

C79

10uF

12

J8

HEADER 1x2

J8

HEADER 1x2

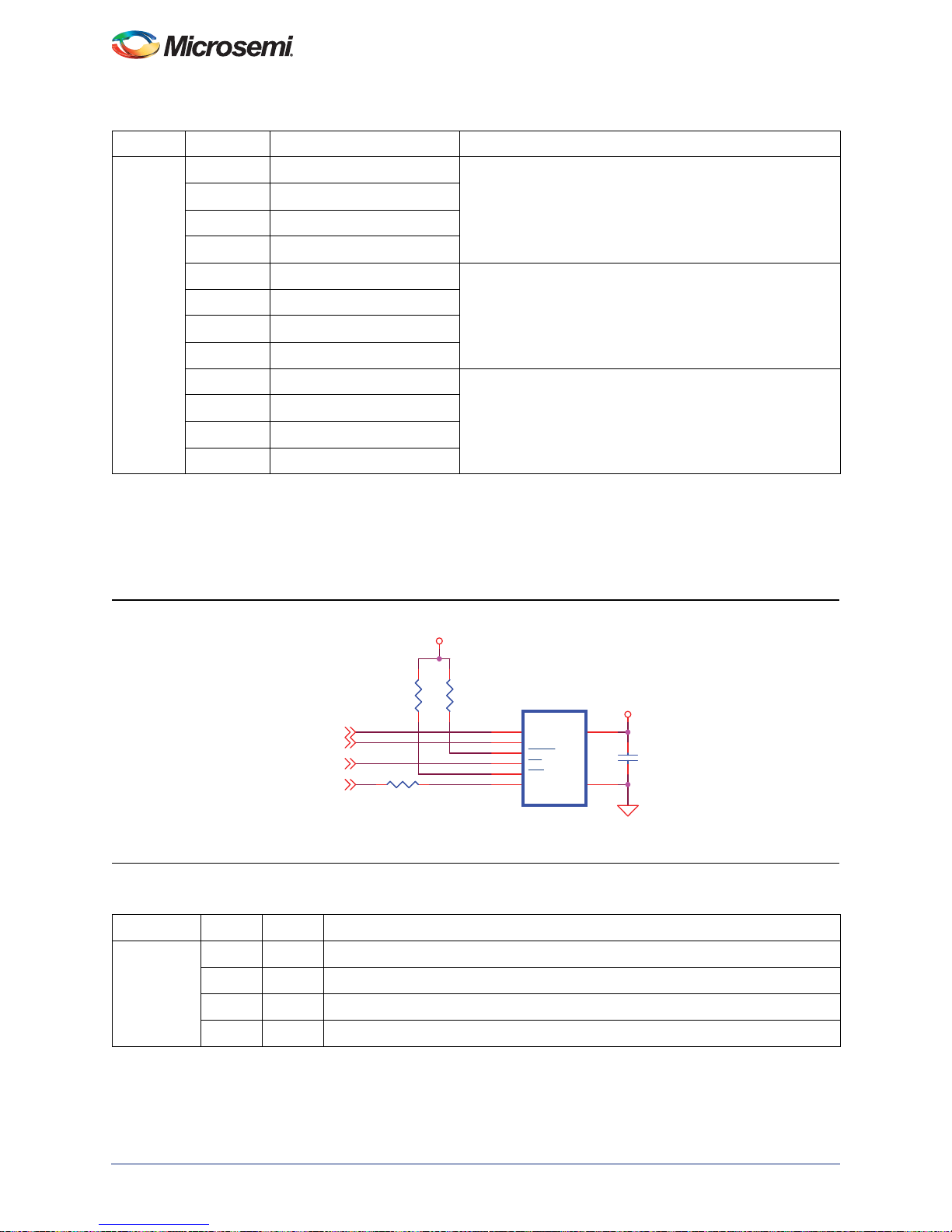

VAREF Connections

The SmartFusion cSoC has one external VAREF input pin for each of the ADCs. The internal VAREF is

brought out as an output, available as VAREFOUT output pin. There are multiple options available to

drive the VAREF0 and VAREF1 from either external VAREF or the internal VAREF through VAREFOUT

output of the FPGA fabric.

Figure 3-1 • VAREF Jumper Selections

Table 3-1 • Use as Internal VAREF

Jumper Function

J32 1–2 VAREFOUT to VAREF0

Notes:

VAREF0 corresponds to ADC[3:0], CM[1:0], TM[1:0]

VAREF1 corresponds to ADC[7:4], CM[3:2], TM[3:2]

VAREF2 corresponds to ADC[11:8], CM4, TM4 (A2F500 only)

3–4 VAREFOUT to VAREF1

5–6 VAREFOUT to VAREF2

Revision 7 19

Page 20

Components Description and Operation

Table 3-2 • Using External VAREF

VAREF Jumper Settings Comment

VAREF0 J32: 1–2 Open

Connect external voltage across J8 pins 1–2 Do not place a jumper on J8

VAREF1 J32: 3–4 Open

Connect external voltage across J5 pins 1–2 Do not place a jumper on J5

VAREF2 J32: 5–6 Open

Connect external voltage across J6 pins 1–2 Do not place a jumper on J6

Note: You need an external VAREF to monitor voltages greater than 2.56 V on the DC/AC/AT channels. An internal

VREF is sufficient to monitor voltages less than 2.56 V on the ADC/AC/AT channels. All ABPS channels can

monitor voltages greater than 2.56 V using an internal VREF.

Current Sensing Circuit

For applications using the embedded current monitor, a current sensing circuit is provided on the

SmartFusion Development Kit board. The current monitoring is performed across AC0 and AT0 pins of

the SmartFusion cSoC device. The voltage across the potentiometer can be monitored via the AT0 pin.

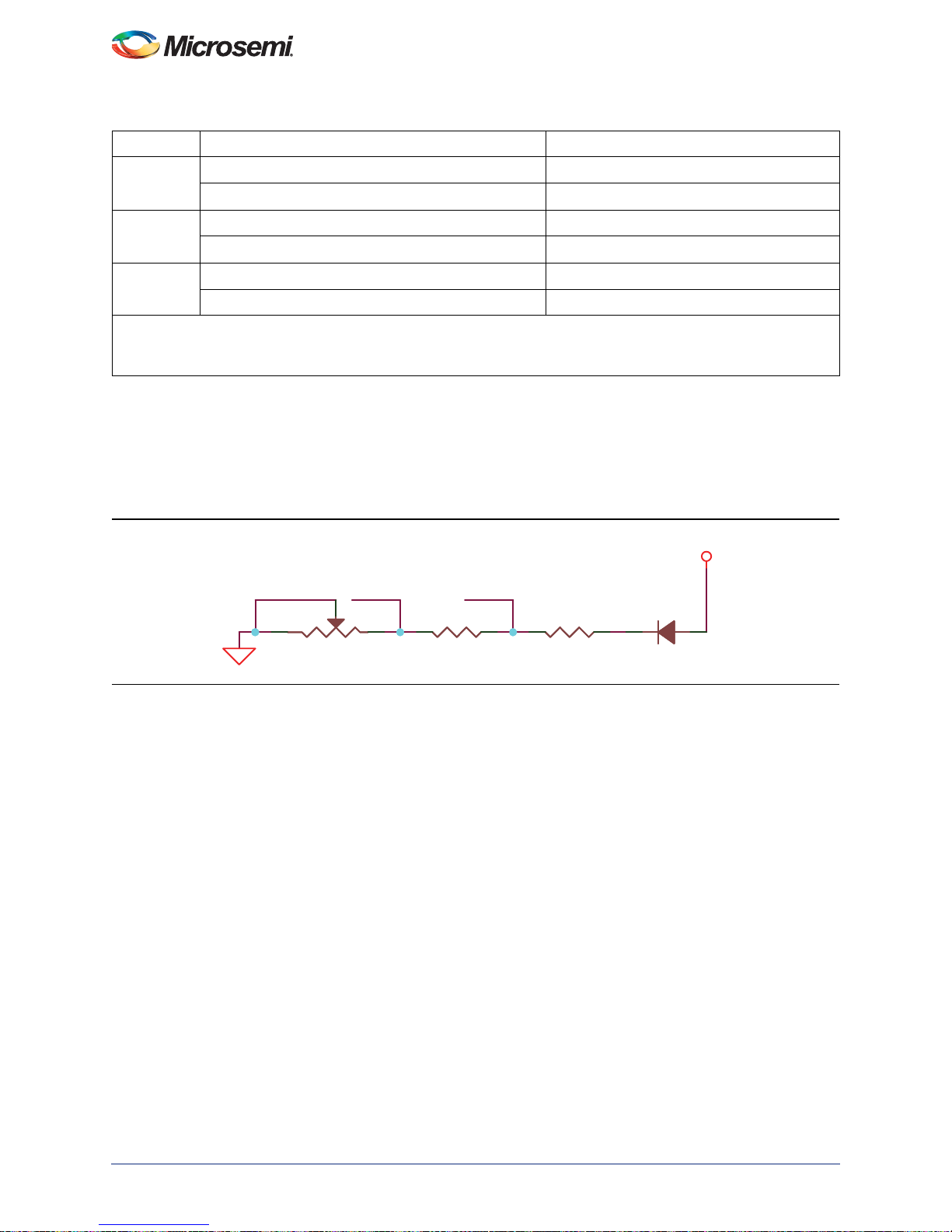

The current sensing circuits is for the 3.3 V voltage rail as shown in Figure 3-2.

3

RV1

RV1

Figure 3-2 • Current Sensing

Note: The current monitoring circuit on the SmartFusion Development Kit board is connected to the

SmartFusion cSoC devices CM0 and TM0 inputs. CM0 can also be used to monitor the voltage

across the potentiometer. This input does not have a prescaler circu it. Because of the value chosen

for the potentiometer, the full-scale input is reached after turning the potentiometer about one

quarter of the maximum travel. Although this will not damage the SmartFusion cSoC device, you

may notice the potentiometer is very sensitive.

PWM Circuit

The PWM RC circuit depicted in Figure 3-3 and Figure 3-4 on page 21 can be used with Microsemi

CorePWM instantiated in the FPGA fabric to generate various voltage waveforms. These voltage

waveforms can be displayed on the OLED or used via the mixed signal header. In addition, one PWM RC

circuit source is routed to the AV input pin of an analog quad. This AV pin can be used to monitor the

generated voltage with high accuracy, depending on the ADC resolution configured in the FPGA fabric.

CURRENT MONITORING

AT0

2

1

R6

50K

50K

R6

AC0

100,1%

100,1%

R7

R7

5.36k

5.36k

S5BC-13-F

S5BC-13-F

D22

D22

V3P3

20 Revision 7

Page 21

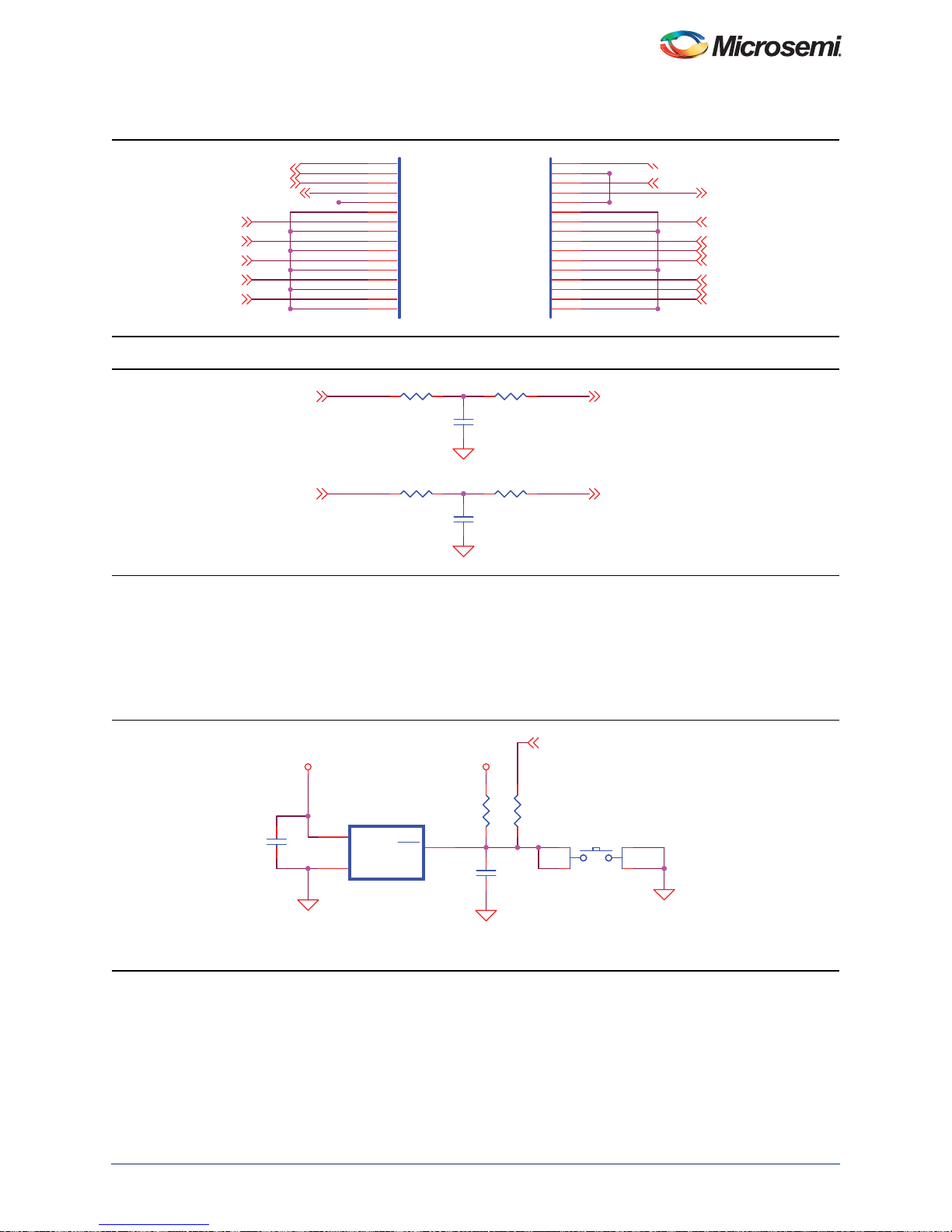

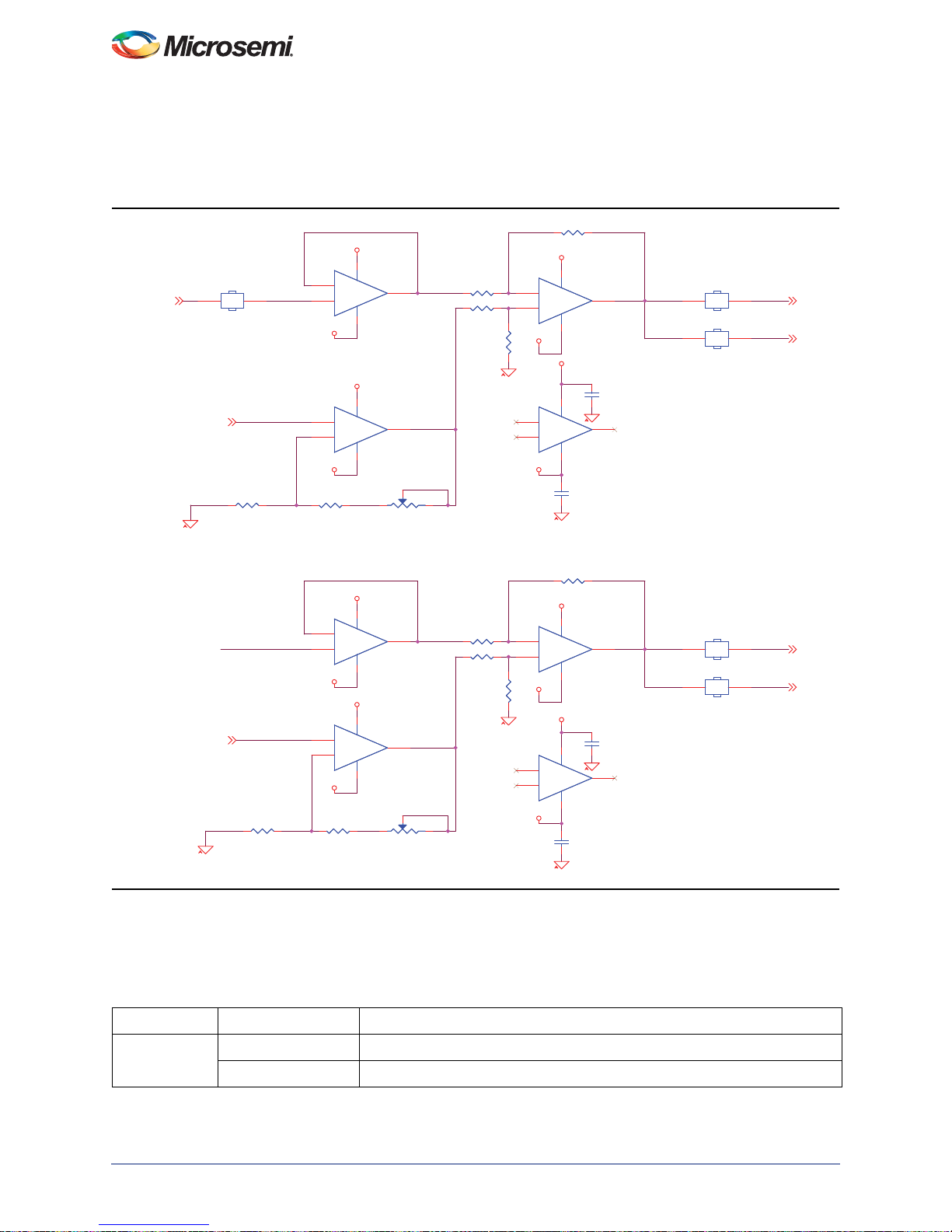

Figure 3-3 shows the A2F500 pins driving PWM and the PWM circuit.

PWM0 PWM1

F2-200-IO_8

F2-200-IO_6

F2-200-IO_7

DACOUT0{6}

AC4{6}

AC2{6}

AC3{6}

AV1_1{6}

DACOUT1 {6}

AT2 {6}

AT3 {6}

AV2_1 {6}

ATGND1 {6}

AT4 {6}

ATGND2 {6}

F2-200-4-FPGAIO

F2-200-6-FPGAIO

35

F2-200-7-FPGAIO

37

F2-200 PWM0

39

DGND8

41

AGND1

43

OBD0

45

AGND3

47

AC2

49

AGND5

51

AC3

53

AGND6

55

AC4

57

AGND8

59

AV1_1

61

63

F2-200-5-FPGAIO

DGND7

36

F2-200-8-FPGAIO

38

F2-200 PWM1

40

DGND9

42

AGND2

44

OBD1

46

AGND4

48

AT2

50

ATGND1

52

AT3

54

AGND7

56

AT4

58

ATGND2

60

AV2_1

62

64

PWM0

PWM1

F2-200-PWM1

F2-200-PWM0

C284

220nF

C284

220nF

R3164.7K R3164.7K

C283

220nF

C283

220nF

R3144.7K R3144.7K

R289100K R289100K

R281

100K

R281

100K

V3P3

V3P3

MSS_SYSRESETB {8,9,15,20,21,27}

Mfr P/N :DS1818R-10+T&R

Mfr: Dallas

RST

Mfr P/N :EVQ-PAD04M

Panasonic - ECG

Notes;

R35 need to place at U15

1

2

3

4

SW8

EVQ-PAD04M

SW8

EVQ-PAD04M

VCC

2

GND

3

RST

1

U15

DS1818

U15

DS1818

R34

10K

R34

10K

C74

1uF

C74

1uF

C73

0.1uF

C73

0.1uF

R3539R35

39

Figure 3-3 • PWM Pins

SmartFusion Development Kit

Figure 3-4 • PWM Circuit

Push-Button System Reset

A push-button system reset switch with a Schmitt trigger is provided on the board (Figure 3-5). The

Schmitt trigger reduces noise on the system reset push-button. SmartFusion MSS reset is synchronized

with this reset.

Figure 3-5 • Push-Button System Reset

Revision 7 21

Page 22

Components Description and Operation

V3P3

V3P3

V3P3

V3P3

V3P3

SWITCH1

SWITCH2

SWITCH4

SWITCH5

SWITCH3

Mfr P/N :KSC403J 50SH LFG

Panasonic - C&K Components

Mfr P/N :KSC403J 50SH LFG

Panasonic - C&K Components

Mfr P/N :KSC403J 50SH LFG

Panasonic - C&K Components

Mfr P/N :KSC403J 50SH LFG

Panasonic - C&K Components

Mfr P/N :KSC403J 50SH LFG

Panasonic - C&K Components

1

2

3

4

SW1

KSC403J 50SH LFG

SW1

KSC403J 50SH LFG

R46

10K

R46

10K

1 2

3 4

SW2

KSC403J 50SH LFG

SW2

KSC403J 50SH LFG

R48

10K

R48

10K

1 2

3 4

SW4

KSC403J 50SH LFG

SW4

KSC403J 50SH LFG

1 2

3

4

SW5

KSC403J 50SH LFG

SW5

KSC403J 50SH LFG

R47

10K

R47

10K

1 2

3 4

SW3

KSC403J 50SH LFG

SW3

KSC403J 50SH LFG

R44

10K

R44

10K

R43

10K

R43

10K

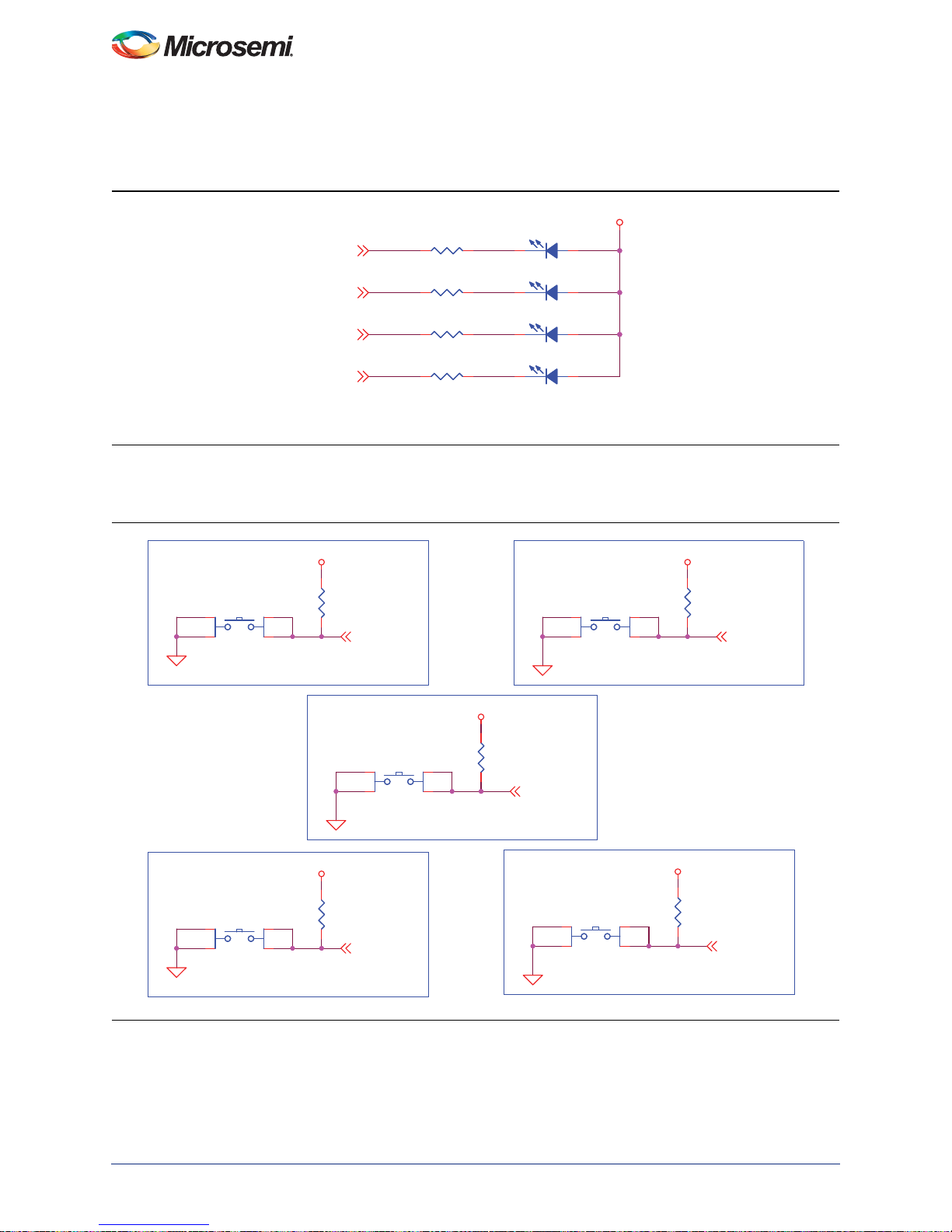

Push-Button, DIP Switches, and User LEDs

Push-button switches and user LEDs can also be used for debugging and for various applications, such

as gaming.

Figure 3-6 • Test LEDs

The board provides users access to four active Low LEDs, which are connected to the SmartFusion pins

B19, B20, C19, and H17.

LED1_N

LED2_N

LED3_N

LED4_N

R32 1.5KR32 1.5K

R38 1.5KR38 1.5K

R40 1.5KR40 1.5K

R41 1.5KR41 1.5K

Mfr P/N :SML-512DWT86

Mfr: Rohm

D1

D1

LED_ORANGE

LED_ORANGE

D2

D2

LED_ORANGE

LED_ORANGE

D3

D3

LED_ORANGE

LED_ORANGE

D4

D4

LED_ORANGE

LED_ORANGE

ACTIVE LOW

V3P3

Figure 3-7 • Push-Button Switches

22 Revision 7

The board comes with Two four input DIP switches.

Page 23

The inputs of AGLP_DIP switch are connected to pins N13,P16,R2,T2 of Bank 2 of the AGLP125

AGLP_3.3V_SIG1AGLP_3.3V_SIG1

AGLP_3.3V_SIG2AGLP_3.3V_SIG2

AGLP_3.3V_SIG3AGLP_3.3V_SIG3

AGLP_3.3V_SIG4AGLP_3.3V_SIG4

1

2

4

J20

HEADER 2X2

3

AGLP_3.3V_DIP1AGLP_3.3V_DIP1

AGLP_3.3V_DIP2AGLP_3.3V_DIP2

AGLP_3.3V_DIP3AGLP_3.3V_DIP3

AGLP_3.3V_DIP4AGLP_3.3V_DIP4

AGLP_DIP

R158

R161

R163

R164

4.7K

4.7K

4.7K

4.7K

AGLP_DIP

S2

V3P3

5

6

7

8

Mfr P/N: 76SB04ST

Mfr: GrayhillInc

2

3

4

1

CS289.

Figure 3-8 • AGLP_ DIP

The inputs of A2F_ DIP switch are connected to pins H20, C21, D21, and F19 of the

SmartFusion cSoC.

SmartFusion Development Kit

V3P3

R33 4.7KR33 4.7K

R36 4.7KR36 4.7K

R37 4.7KR37 4.7K

R39 4.7KR39 4.7K

1

2

3

4

Mfr P/N :76SB04ST

Mfr: Grayhill Inc

Figure 3-9 • Input Push-Button Switch

In addition, the board includes five push-button switches that are connected to pins G19, G20, G21, E1,

and F14 of the SmartFusion cSoC.

U7-17

U7-17

LED1_N

LED2_N

LED3_N

LED4_N

DIP1

DIP2

DIP3

B19

GBB0/IO18NDB0V0

B20

GBB1/IO18PDB0V0

C19

GBA0/IO19NPB0V0

H17

IO25NDB1V0

H20

GCC0/IO26NPB1V0

C21

GBC2/IO21PDB1V0

D21

IO21NDB1V0

F2-200/500-FGG484

F2-200/500-FGG484

Figure 3-10 • LED, DIP, and Push-Button I/Os

S1

8

7

6

5

A2F_DIPS1A2F_DIP

LED , DIP & PB

LED , DIP & PB

GCA2/IO23PDB1V0

GCB2/IO24PDB1V0

GFC2/IO67PPB5V0

GBC0/IO17NPB0V0

IO23NDB1V0

IO24NDB1V0

DIP1

DIP2

DIP3

DIP4

F19

G19

G20

G21

E1

E14

DIP4

SWITCH1

SWITCH2

SWITCH3

SWITCH4

SWITCH5

Revision 7 23

Page 24

Components Description and Operation

One-Bit DAC (OBD) Circuit

For applications that require conversion from a digital to analog domain , two analog conditi oning circui ts

are provided. This is useful in closed-loop applications. Figure 3-11 shows the circuit. Table 3-5 on

page 25 and Table 3-6 on page 26 show the jumper settings.

VAREF_OUT{6}

OBD_DACOUT0

{6}

AGND

OBD_DACOUT1{6}

AGND

JP13

JP13

12

HEADER 1x2

HEADER 1x2

R140 1K,1%R140 1K,1%

VREF_OUT

R151 1K,1%R151 1K,1%

VREF_OUT

1P15V

U44A

U44A

2

-

-

3

+

+

1N15V

1P15V

U44B

U44B

5

+

+

6

-

-

1N15V

R139 500,1%R139 500,1%

1P15V

U51A

U51A

2

-

-

3

+

+

1N15V

1P15V

U51B

U51B

5

+

+

6

-

-

1N15V

R152 500,1%R152 500,1%

411

AD824ARZ-14

AD824ARZ-14

AD824ARZ-14

AD824ARZ-14

11 4

1 3

411

AD824ARZ-14

AD824ARZ-14

AD824ARZ-14

AD824ARZ-14

11 4

1 3

R147 5.8K,1%R147 5.8K,1%

1P15V

411

U44C

U44C

AGND

R178

R178

5.8K,1%

5.8K,1%

10

13

12

9

-

-

+

+

AD824ARZ-14

AD824ARZ-14

1N15V

MANUFACTURER P/N = AD824ARZ-14

MANUFACTURER P/N = AD824ARZ-14

1P15V

MANUFACTURER = Analog Devices Inc

MANUFACTURER = Analog Devices Inc

C161

C161

411

U44D

1N15V

U44D

-

-

+

+

AD824ARZ-14

AD824ARZ-14

C162

C162

0.01uF

0.01uF

0.01uF

0.01uF

8

AGND

14

1

7

2

1K

R21 1K,1%R21 1K,1%

R22 1K,1%R22 1K,1%

RV21KRV2

JP14

JP14

JP15

JP15

12

HEADER 1x2

HEADER 1x2

12

HEADER 1x2

HEADER 1x2

AV1_0 {6}

AV1_2 {6}

AGND

R148 5.8K,1%R148 5.8K,1%

1P15V

411

U51C

U51C

AGND

R179

R179

5.8K,1%

5.8K,1%

9

-

-

10

+

+

AD824ARZ-14

AD824ARZ-14

1N15V

1P15V

411

U51D

U51D

13

-

-

12

+

+

AD824ARZ-14

AD824ARZ-14

MANUFACTURER P/N = AD824ARZ-14

MANUFACTURER P/N = AD824ARZ-14

1N15V

MANUFACTURER = Analog Devices Inc

MANUFACTURER = Analog Devices Inc

C163

C163

0.01uF

0.01uF

8

C164

C164

0.01uF

0.01uF

AGND

14

1

7

2

R149 1K,1%R149 1K,1%

R150 1K,1%R150 1K,1%

RV31K RV31K

JP21

JP21

JP27

JP27

12

HEADER 1x2

HEADER 1x2

12

HEADER 1x2

HEADER 1x2

AV2_0 {6}

AV2_2 {6}

AGND

Figure 3-11 • OBD_DACOUT

The OBDs can be used in two applications.

These circuits take the OBD output of the SmartFusion quad and feed it back to the SmartFusion analog

inputs of ADC0 and ADC1 (Table 3-3). This is useful in closed-loop applications.

Table 3-3 • OBD Output to Loopback to ADC

Jumper Pin Function

JP4 3-4 DACOUT0 to ADC0

7-8 DACOUT1 to ADC1

24 Revision 7

Page 25

SmartFusion Development Kit

The OBDs can also be fed into a voltage gain circuit as shown in Figure 3-11 on page 24 and described

in Table 3-4. In this application, the OBD sweep of 0–2.56 V can be translated to –15 V to +15 V. This is

useful in closed-loop applications for ABPS channels with prescalers.

Table 3-4 • OBD Connections for Voltage Gain

Jumper Pin Pin

JP4 1–3 DACOUT0 to OBD_DACOUT0

7–9 DACOUT1 to OBD_DACOUT1

JP13 1–2 Connect VAREF_OUT to bias the opamp

The output of the Opamp can be configured to be monitored by the ABPS channel (Table 3-5). This can

be done as below:

Table 3-5 • Output of the Opamps to ABPS Channels

Jumper Pin Pin Function

JP14 1 2 OP_AMP (U44C) output to ABPS0 of FPGA fabric

JP15 1 2 OP_AMP (U44C) output to ABPS4 of FPGA fabric

JP21 1 2 OP_AMP (U51C) output to ABPS1 of FPGA fabric

JP27 1 2 OP_AMP (U51C) output to ABPS5 of FPGA fabric

OLED Display

A 9616-pixel low-power OLED is made available on the board for display. This low-power device, WHITE

OLED, requires 3.3 V and 10 V power supplies. Either one of the SmartFusion MSS I2C0 or SPI0 can be

interfaced with the OLED.

The OLED displays sharp gaming images or text. For example, the SmartFusion RTC current time or

time between two events can be displayed on the OLED. Figure 3-12 on page 26 shows the OLED

connections on the board along with jumpers for BS1 and BS2 and the jumper settings for accessing the

OLED from SPI0.

Revision 7 25

Page 26

Components Description and Operation

OLED_BS1 OLED_BS2

OLED_BS1 OLED_BS2

OLED_CS#

V3P3

V3P3 V3P3

V10P

V3P3

OLED_D/C#{27}

MSS_SYSRESETB{8,12,15,20,21,27}

OLED_SCL {10}

OLED_SDA_OUT {10,11}

OLED_SDA_IN {10}

OLED_CS#

{11}

SCL

SDA

Mfr P/N :PMO13701

Mfr: PACER

Mfr P/N :3-644456-3

Mfr:Tyco Electronics

Mfr P/N :3-644456-3

Mfr:Tyco Electronics

TANT

R202MR20

2M

+

C67

4.7uF 25V

+

C67

4.7uF 25V

C68

0.01uF

C68

0.01uF

R201

10K

R201

10K

R17

10K

R17

10K

1

2

3

JP22JP22

R202

10K

R202

10K

R1651KR165

1K

R203

10K

R203

10K

R18

10K

R18

10K

1

2

3

JP23JP23

R3651KR365

1K

R207

10K

R207

10K

R19

10K

R19

10K

C69

1uF

C69

1uF

VCC

30

VCOMH

29

IREF

28

VDD

11

BS1

12

BS2

13

NC11NC28NC39NC410NC514NC6

31

VSS

2

TEST1

7

TEST2

6

TEST3

5

TEST4

4

TEST5

3

D0

20

D1

21

D2

22

D3

23

D4

24

D5

25

D6

26

D7

27

RD#

19

WR#

18

D/C#

17

RES#

16

CS#

15

U11

PMO13701

U11

PMO13701

Refer to the "Jumper Settings" section on page 26 for accessing the OLED from I2C0 and SPI0.

Figure 3-12 • OLED Connections

Jumper Settings

Table 3-6 • Interface MSS I2C0 to the OLED

Jumper Pin Pin Connection Details

J7 2 3 I2C_0_SCL to OLED_SCL

14 15 I2C_0_SDA to OLED_SDA_IN

JP18 1 2 Closed

JP23 1 2 OLED_BS1 connected to 3.3 V

JP22 2 3 OLED_BS2 connected to GND

Table 3-7 • Interface MSS SPI0 to the OLED

Jumper Pin Pin Connection Details

J7 3 4 SPI_SCK to OLED_SCL

JP8 1 2 SPI_0_OUT to OLED_SDA_IN

JP18 1 2 Open

JP23 2 3 OLED_BS1 connected to GND

JP22 2 3 OLED_BS2 connected to GND

26 Revision 7

15 16 SPI_SDA to OLED_SDA

5 6 SDI_0_IN to OLED_SDA_OUT

9 10 SCLK_0_OUT to OLED_SCL

13 14 SS_0_OUT to OLED_CS#

Page 27

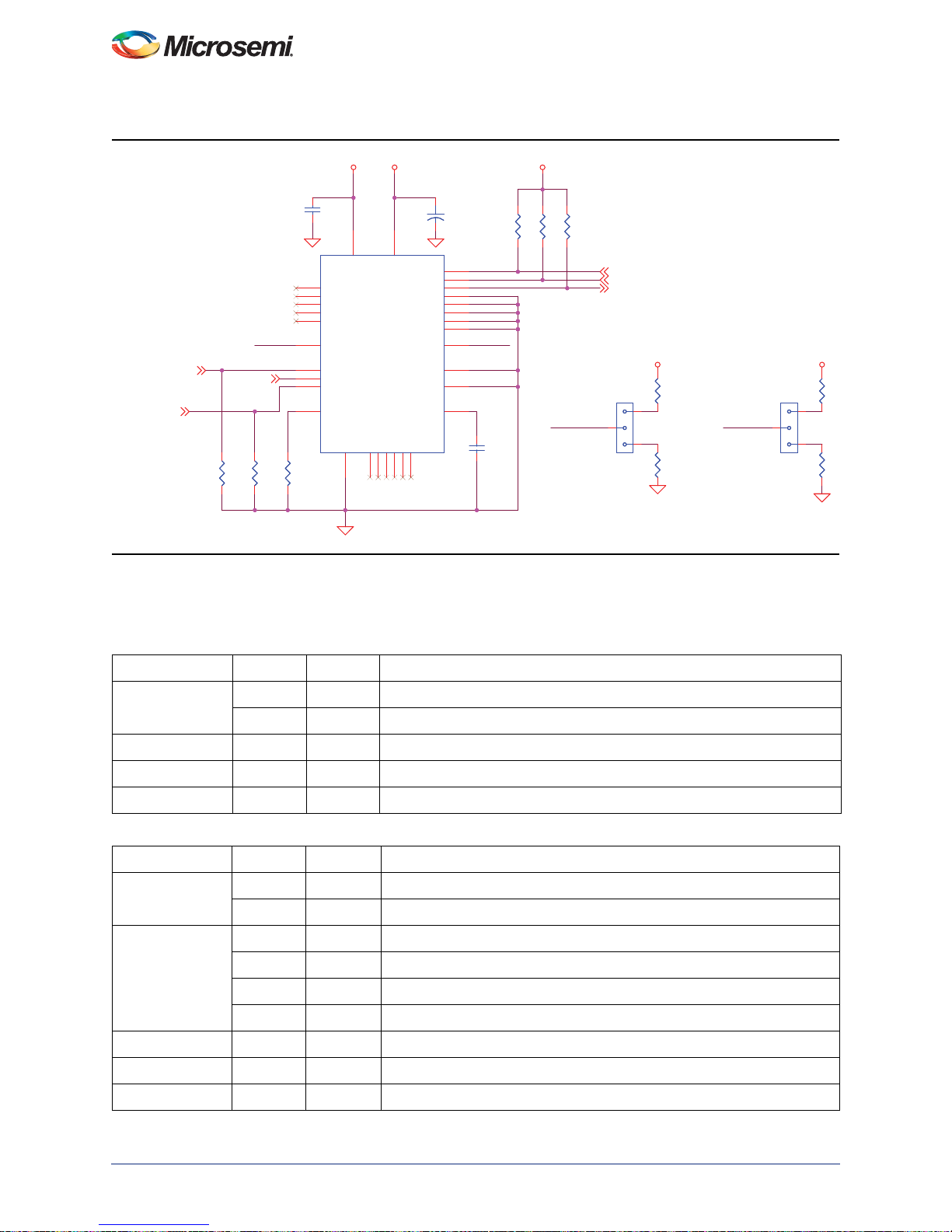

Figure 3-13 • JP8 Jumper Details

OLED_CS#

{9}

SPI_0_SCK

{10}

SDO_0_OUT

SDI_0_IN

SCLK_0_OUT

SS_0_OUT

SS_1_OUT

SCLK_1_OUT

SPI_1_SO

SPI_1_SI

SPI_1_SCK

SPI_CS_N

SDI_1_IN

SDO_1_OUT

SPI_0_SI

{10}

OLED_SDA_OUT{9,10}

2

3

4

6

7

8

10

11

12

14

15

16

1

5

9

13

JP8

HDR4X4

JP8

HDR4X4

SPI Configuration –1

SPI Port 0

SPI Port 1

OLED

SPI Flash

OLED

Display

SPI

Port 0

SPI

Port 1

SPI

Flash

OLED

Display

SPI

Port 0

SPI

Port 1

SPI

Flash

SmartFusion Development Kit

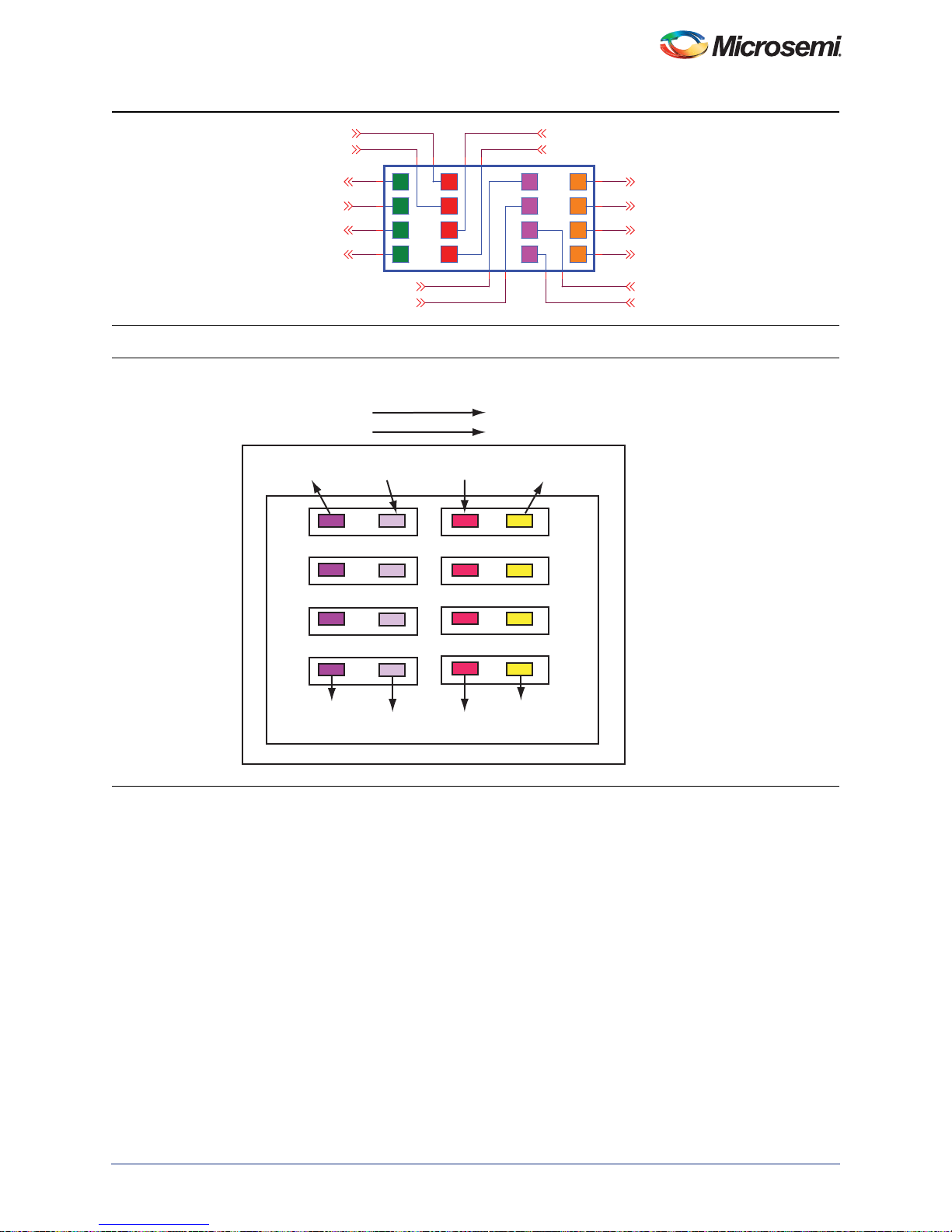

Figure 3-14 • MSS SPI0 and SPI1 Settings

Revision 7 27

Page 28

Components Description and Operation

SPI_SO

V3P3

V3P3

SPI_CS_N

SPI_1_SI

SPI_1_SCK

SPI_1_SO

8 MByte

Mfr P/N : AT25DF641-MWH-T

Mfr: Atmel

R28

10K

R28

10K

R293

10K

R293

10K

SI

5

SCK

6

HOLD

7

CS

1

WP

3

VCC

8

GND

4

SO

2

U13

AT25DF641-MWH-T

U13

AT25DF641-MWH-T

C70

0.1uF 10V

C70

0.1uF 10V

R206 39R206 39

Table 3-8 • MSS SPI0 and MSS SPI1 Loopback and Off-Board SPI Device Connections

Jumper Pin Signal Connection Details

JP8 6 SPI0_SDI To interface any SPI device to MSS SPI0

2 SPI0_SDO

10 SPI0_SCK

14 SPI0_SS

3 SPI1_SDI To interface any SPI device to MSS SPI1

7 SPI1_SDO

11 SPI1_SCK

15 SPI1_SS

6 7 MSS SPI0 and SPI1 loopback

23

10 11

14 15

SPI Flash

One 8-MByte SPI flash Atmel AT25DF641-MWH-T is also offered on the board. This can optionally be

interfaced to either the SPI0 or SPI1 peripherals of the SmartFusion MSS. Figure 3-15 and Figure 3-16

show the SPI flash circuit and the jumper settings to access it from SPI1.

Figure 3-15 • SPI Flash

Table 3-9 • MSS SPI1 to SPI Flash

Jumper Pin Pin Connection Details

JP8 3 4 SDI_1_IN to SPI_1_SO (SO output of SPI flash)

7 8 SDO_1_OUT to SPI_1_SI (SI input of SPI flash)

11 12 SCLK_1_OUT to SPI_1_SCK (SCK input of SPI flash)

15 16 SS_1_OUT to SPI_CS_N (CS# input of SPI flash)

28 Revision 7

Page 29

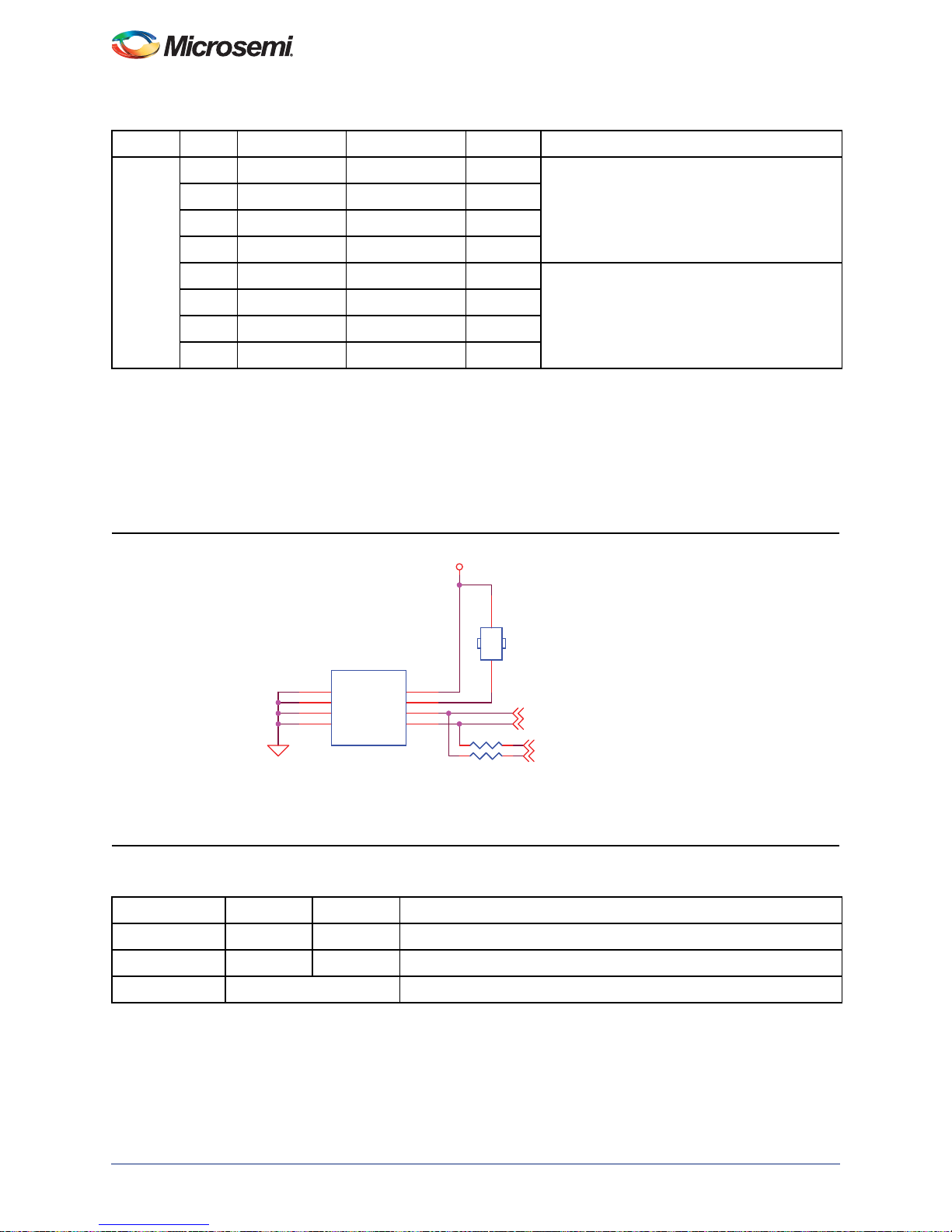

SPI DAC

One 12-bit SPI DAC AD5320 is available on the board. This can be optionally interfaced to either the

SPI0 or SPI1 of the SmartFusion MSS. Figure 3-16 shows the SPI DAC instance along with the header

that must be connected to the SPI_x_SDI, SPI_x_SCK, SPI_x_SS, and SPI_x_SDO pins of SPI0 or

SPI1.

HEADER 1

HEADER 1

HEADER 1

HEADER 1

HEADER 1

HEADER 1

J16

J16

J17

J17

J18

J18

SmartFusion Development Kit

V3P3

C72

ANA_V

C72

10uF 16V

10uF 16V

JP3

JP3

1

HEADER 1x2

HEADER 1x2

2

C71

C71

3

U14

U14

1

1

1

R30

R30

R31

R31

50 NL

50 NL

50 NL

50 NL

R29

R29

50 NL

50 NL

4

DIN

VDD

5

6

SCLK

SYNC

VOUT

GND

AD5320_NL

AD5320_NL

2

0-1uF 10V

0-1uF 10V

1

Figure 3-16 • SPI DAC

Revision 7 29

Page 30

Components Description and Operation

I2C_WC_N

V3P3

I2C_EEPROM_SCL

I2C_EEPROM_SDA

ET1100_I2C_EEPROM_SCL {31}

ET1100_I2C_EEPROM_SDA {31}

Device Select Code: " 0 0 0 "

R309 0R309 0

12

JP26

HEADER 1x2

JP26

HEADER 1x2

R307 0R307 0

E0

1

E1

2

E2

3

VSS

4

SDA

5

SCL

6

WC_N

7

VCC

8

U12

M24512-WMN6TP

MANUFACTURER P/N = M24512-WMN6TP

MANUFACTURER = STMicroelectronics

U12

M24512-WMN6TP

MANUFACTURER P/N = M24512-WMN6TP

MANUFACTURER = STMicroelectronics

Table 3-10 • To Interface MSS SP10 or MSS SPI1 to SPI DAC

Jumper Pin Signal Header/Jumper Signal Connection Detai ls

JP8 6 SPI0_SDI J16 DIN To Interface SPI DAC to MSS SPI0

2 SPI0_SDO JP3 (Pin1) VOUT

10 SPI0_SCK J17 SCK

14 SPI0_SS J18 SYNC#

3 SPI1_SDI J16 DIN T o Interface SPI DAC to MSS SPI1

7 SPI1_SDO JP3 (Pin1) VOUT

1 1 SPI1_SCK J17 SCK

15 SPI1_SS J18 SYNC#

I2C EEPROM

One 512-Kbit I2C EEPROM ST M24512-WMN6TP is available on the board to interface with I2C Port1 of

the SmartFusion MSS. Alternatively the EtherCAT chip, Beckhoff ET1100, can interface with the

EEPROM.

Figure 3-17, and Figure 3-18 and Figure 3-19 on page 31 show the EEPROM connections, I2C interface,

and header with jumper settings for access to EEPROM.

Figure 3-17 • I2C EEPROM

Table 3-11 • To Interface MSS I2C1 to EEPROM

Jumper Pin Pin Connection Details

J7 6 7 I2C_1_SCL to EEPROM_SCL

14 15 I2C_1_SDA to EEPROM_SDA

JP26 Closed To write protect EEPROM (WE_N)

30 Revision 7

Page 31

SmartFusion Development Kit

SPI_0_SCK {11}

SPI_0_SI {11}

I2C_SCL_0_IN

I2C_SCL_1_IN

I2C_SDA_1_IN

I2C_SDA_0_IN

OLED_SCL {9}

I2C_EEPROM_SDA

OLED_SDA_IN {9}

I2C_EEPROM_SCL

1

5

9

13

14415

7

11

16

3

2

10 6

8

12

J7

I2C INTERFACE

J7

I2C INTERFACE

Figure 3-18 • MSS I2C0 and I2C1 Jumper Settings

Table 3-12 • To Interface EtherCAT ET1100 to EEPROM

EEPROM PIN ET1100 PIN Connection details Comment

5 G11 EEPROM CLK of ET1100 to SCL of EEPROM When MSS I2C1 is not

6 F11 EEPROM DATA of ET1100 to SDA of EEPROM

driving EEPROM

JP26 Closed To write protect EEPROM (WE_N)

V3P3

R24

Figure 3-19 • I

I2C_SDA_0_IN

I2C_SCL_0_IN

I2C_SDA_1_IN

I2C_SCL_1_IN

2

C Interface Terminations

R23

R23

10K

10K

R24

10K

10K

R25

R25

10K

10K

R26

R26

10K

10K

U7-16

U7-16

I2C INTERFACE

I2C INTERFACE

V21

I2C_0_SDA/GPIO_22

U21

I2C_0_SCL/GPIO_23

V22

I2C_1_SDA/GPIO_30

U20

I2C_1_SCL/GPIO_31

F2-200/500-FGG484

F2-200/500-FGG484

PORT0

PORT0

PORT1

PORT1

Revision 7 31

Page 32

Components Description and Operation

V3P3

V3P3

CLK_50MHZ {27}

MSS_RMII_CLK {15}

E/D

1

GND

2

VDD

4

OUTPUT

3

Y3

50Mhz_HC73

Y3

50Mhz_HC73

R231 39R231 39

C75 0.01uFC75 0.01uF

R45 39R45 39

R42 10KR42 10K

PTBASE

V1P5_INTV1P5_INTV1P5_INT

RTC_SW

Mfr P/N :EVQ-PAD04M

Mfr: Panasonic - ECG

RESET CIRCUIT

AGND AGND

AGND AGND

U7-2

F2-500-FGG484

U7-2

F2-500-FGG484

PCAP

AB5

NCAP

AB6

PU_N

W17

PTBASE

AB20

PTEM

Y18

MAINXIN

AA16

LPXIN

AA18

MAINXOUT

AA17

LPXOUT

AA19

C49

2.2uF 16V

C49

2.2uF 16V

12

C51

30pF

C51

30pF

C53

0.1uF

C53

0.1uF

C52

30pF

C52

30pF

C48

18pF

C48

18pF

SW7

EVQ-PAD04M

SW7

EVQ-PAD04M

12

34

C50

18pF

C50

18pF

Y2

32.768 KHZ

Y2

32.768 KHZ

Y1

20MHZ 20 PPM

Y1

20MHZ 20 PPM

Clock Oscillator

A 50 MHz cloc k oscillator with 20 PPM is available on the board (Figure 3-20). This cl ock oscillator is

connected to the FPGA fabric to provide a system reference clock and connected to the PHY to provide

the RMII_CLK. An on-chip SmartFusion PLL can be configured to generate a wide range of highprecision clock frequencies.

Figure 3-20 • 50 MHz RC OSC

20 MHz Oscillator

A 20 MHz resonator o f 20 PPM is placed across the MAINXIN and MAINXOUT pins of the SmartFusion

cSoC with the appropriate 18 pF capacitors. This is used to generate high precisio n clock for Ethernet

MAC and also in RTC based applications.

32.768 KHz (low power) Oscillator

A 32.768 KHz resonator, CM519, is placed across the LPXIN and LPXOUT pins of the SmartFusion

cSoC with the appropriate 30 pF capacitors. This low-power resonator is useful in RTC based

applications.

Figure 3-21 • 20 MHz and 32.768 KHz Oscillators

32 Revision 7

Page 33

SmartFusion Development Kit

USB-to-UART Interface

Included on the development board is a USB-to-UART interface with ESD protection (Figure 3-22). This

interface includes an integrated USB-to-UART bridge controller (U16) to provide a standard UART

connection with the SmartFusion MSS UART0 port.

One application of the USB-to-UART interface is to allow HyperTermina l on a PC to communicate with

the SmartFusion cSoC. HyperTerminal is a serial communications application program that can be

installed in the Windows

Windows.

With a USB driver properly installed, and the correct COM port and communication settings selected, you

can use the HyperTerminal program to communicate with a design running on the SmartFusion cSoC.

Table 3-13 lists the supported UART parameters, such as baud rate, for HyperTerminal application.

Table 3-13 • UART HyperTerminal Settings

Supported HyperTerminal Parameters

Baud Rates Data Bits Parity Types STOP BIT

110 5, 6, 7, 8 NO/ODD/EVEN/MARK (1)/SPACE (0) ONE/ONE-HALF/TWO

300

1200

2400

®

operating system. A basic HyperTe rminal program is usually distributed with

4800

9600

19200

38400

57600

115200

230400

460800

921600

TXD_0_OUT

RXD_0_IN

R236 39R236 39

U7-9

U7-9

UART INTERFACE

UART INTERFACE

Y22

UART_0_TXD/GPIO_20

U18

UART_0_RXD/GPIO_21

F2-500-FGG484

F2-500-FGG484

PORT0

PORT0

Figure 3-22 • USB-to-UART

Revision 7 33

Page 34

Components Description and Operation

V3P3

RXD_1_IN

RS485_B

RS485_A

TXD_1_OUT

RS485_DE

RS485_RE

R28839R288

39

R566

120

R566

120

R

D

U56

MAX3430CSA

R

D

U56

MAX3430CSA

R0

1

RE

2

DE

3

DI

4

VCC

8

B

7

A

6

GND

5

C81

0.1uF

C81

0.1uF

RS485_RE

RS485_DE

RXD_1_IN

TXD_1_OUT

R28739R287

39

UART HANDSHAKING

PORT1

U7-18

F2-500-FGG484

UART HANDSHAKING

PORT1

U7-18

F2-500-FGG484

GDA2/IO42NDB1V0

L18

GDB1/IO39PDB1V0

L20

UART_1_TXD/GPIO_28

V20

UART_1_RXD/GPIO_29

W22

RS485 Interface

Included on the development board is an RS485 with DB9 female connector, interfacing with the

MAX3240CSA connected to UART port 1 (Figure 3-23, Figure 3-24, and Figure 3-25 on page 35) of the

SmartFusion MSS. This is provided for applications that require RS485, for which the UART port needs

to be used in MODEM mode.

Figure 3-23 • RS485

Figure 3-24 • SmartFusion UART Port 1

34 Revision 7

Page 35

P1

P1

1

6

SmartFusion Development Kit

11

G3

DCD

DSR

Figure 3-25 • DB9 Connector

Ethernet Interface

One Ethernet interface, configured for RMII full d uplex mode, and a low-powe r 10/100 Mbps single-port

Ethernet physical layer transceiver (U19) are provided on-board (Fig ure 3-27 on page 36). The Ethernet

physical layer features integrated sub-layers to support both 10BASE-T and 100BASE-TX Ethernet

protocols. These sub-layers ensure compatibility and interoperability with many other standards-based

Ethernet solutions.

The Ethernet RJ45 interface and physical layer, the interface with the SmartFusion MSS Ethernet media

access controller (MAC) which supports RMII, serves many purposes. For example, this interface can be

used to access the SmartFusion cSoC to monitor the ADC data over a network. The embedded system

memory and control registers can be accessed and processed remotely to support system management.

RS485_B

RS485_A

2

TX

7

RTS

3

RX

8

CTS

4

DTR

9

RI

5

G1

G2

CONNECTOR DB9F

CONNECTOR DB9F

Manufacturer P/N = 152-3409

Manufacturer P/N = 152-3409

10

Manufacturer = Kobiconn

Manufacturer = Kobiconn

Clocking Scheme for RMII CLK

The 10/100 MAC RMII interface requires a 50 MHz clock. The PHY device also requires a 50 MHz

20 PPM clock for proper operation. While there are a few possible ways of providing the clock, the

following two schemes are discussed:

Clocking Scheme 1: From 50 MHz clock oscillator

• 50 MHz oscillator goes as input to CCC and to the X1 clock input of Ethernet PHY through GPIO

• The GLC output of CCC, which is also at 50 MHz, feeds MAC_CLK of 10/100 MAC

Revision 7 35

Page 36

Components Description and Operation

Clocking Scheme 2: From 20 MHz clock oscillator

• 20 MHz oscillator goes as input to CCC. GLC output of CCC is configured at 50 MHz

• The GLC output of CCC feeds MAC_CLK of 10/100 MAC

• The same GLC output of CCC feeds X1 clock input of Ethernet PHY through GPIO

Clock Conguration 1

A2F500

X1 Input

50 MHz OSC

Clock Conguration 2

20 MHz OSC

Figure 3-26 • Ethernet Clocking

FPGA_ENA_MDC

FPGA_ENA_MDIO

FPGA_ENA_TXEN

FPGA_ENA_TXD0

FPGA_ENA_TXD1

22

22

R24222R242

R23322R233

R23422 R23422

CCC

50 MHz

GLC

A2F500

CCC

GLC

50 MHz

U7-14

AA3

MAC_MDC/IO57RSB4V0

V4

MAC_MDIO/IO58RSB4V0

Y4

MAC_TXEN/IO61RSB4V0

AA5

MAC_TXD[0]/IO65RSB4V0

W5

MAC_TXD[1]/IO64RSB4V0

10/100 MAC

MAC_CLK

10/100 MAC

MAC_CLK

ETHERNETETHERNET

MAC_CRSDV/IO60RSB4V0

MAC_RXER/IO59RSB4V0

MAC_RXD[0]/IO63RSB4V0

MAC_RXD[1]/IO62RSB4V0

TXD

RXD

TXD

RXD

MAC_CLK

W4

AA4

V5

U5

T6

Ethernet

PHY

50 MHz Clk

Output

X1 Input

Ethernet

PHY

50 MHz Clk

Output

FPGA_ENA_CRS

FPGA_ENA_RXER

FPGA_ENA_RXD0

FPGA_ENA_RXD1

MSS_RMII_CLK {12}

Figure 3-27 • Ethernet Interface

36 Revision 7

F2-500-FGG484

Page 37

Memory Section Overview

Part Number

CY7C1061DV33–10ZSXI(1M X 16)

JS28F640J3D–75 (4M X 16)

Part#

MT45W8MW16BGX (8M X 16)

JS28F128P30T85873824 (16M X 16)

Logic 0 – All Out Buffers are tristated

Logic 1 – Channeling is in use

SRAM

and Flash

SRAM

SRAM

PSRAM

and

Flash

PSRAM

Flash

Flash

Flash

When memory is not used the

Expansion connector will be used

As 3.3V GPIOs

3.3 V

Interface

3.3 V

Interface

1.8 V

Interface

Expansion

Connector

0 Ohm

Isolation

Resistors

Design 1: GPIOs are channeled from

A2F500 to Expansion Header Pins

A2F500

AGLP

CS289

Design 2: GPIOs are channeled from

A2F500(EMC) to PSRAM/Header Pins

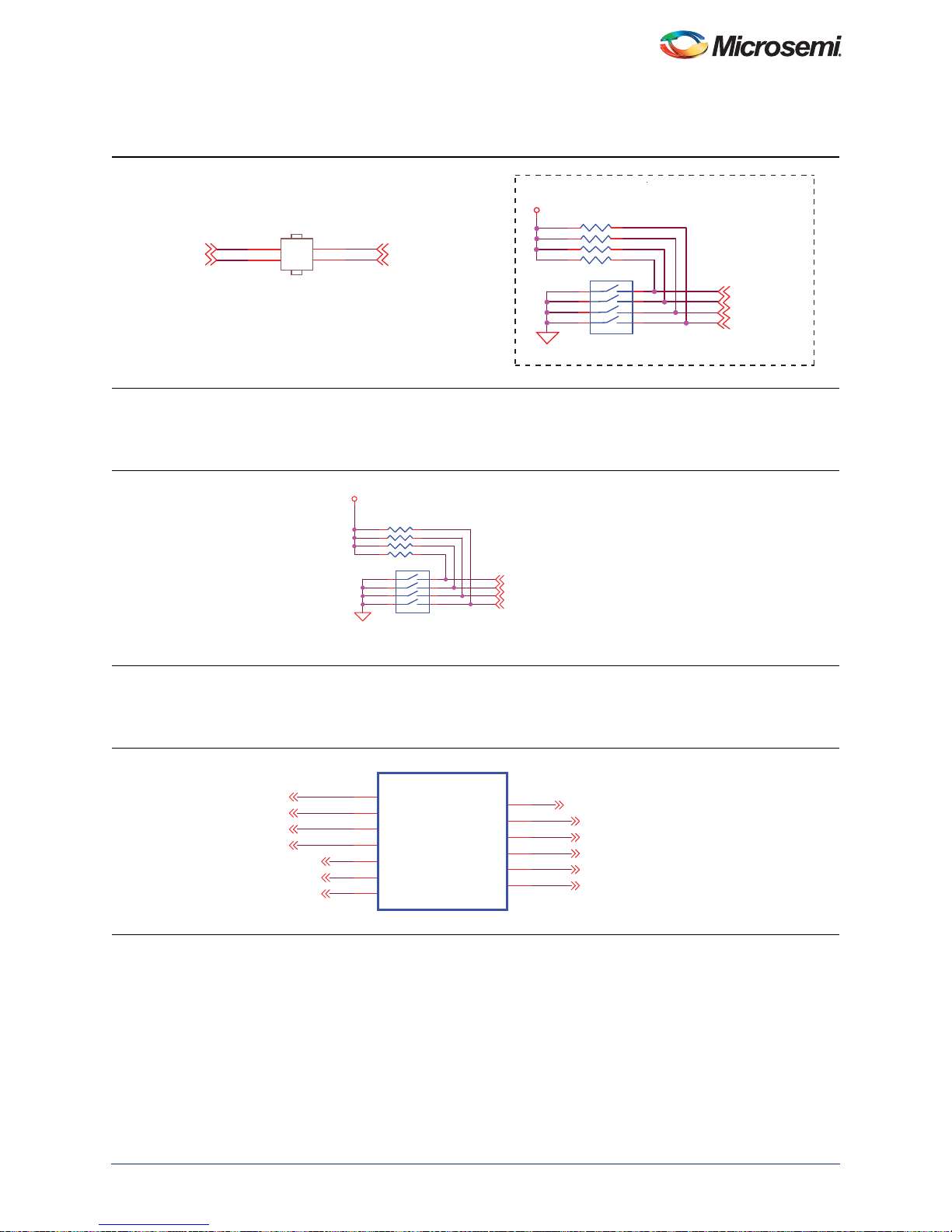

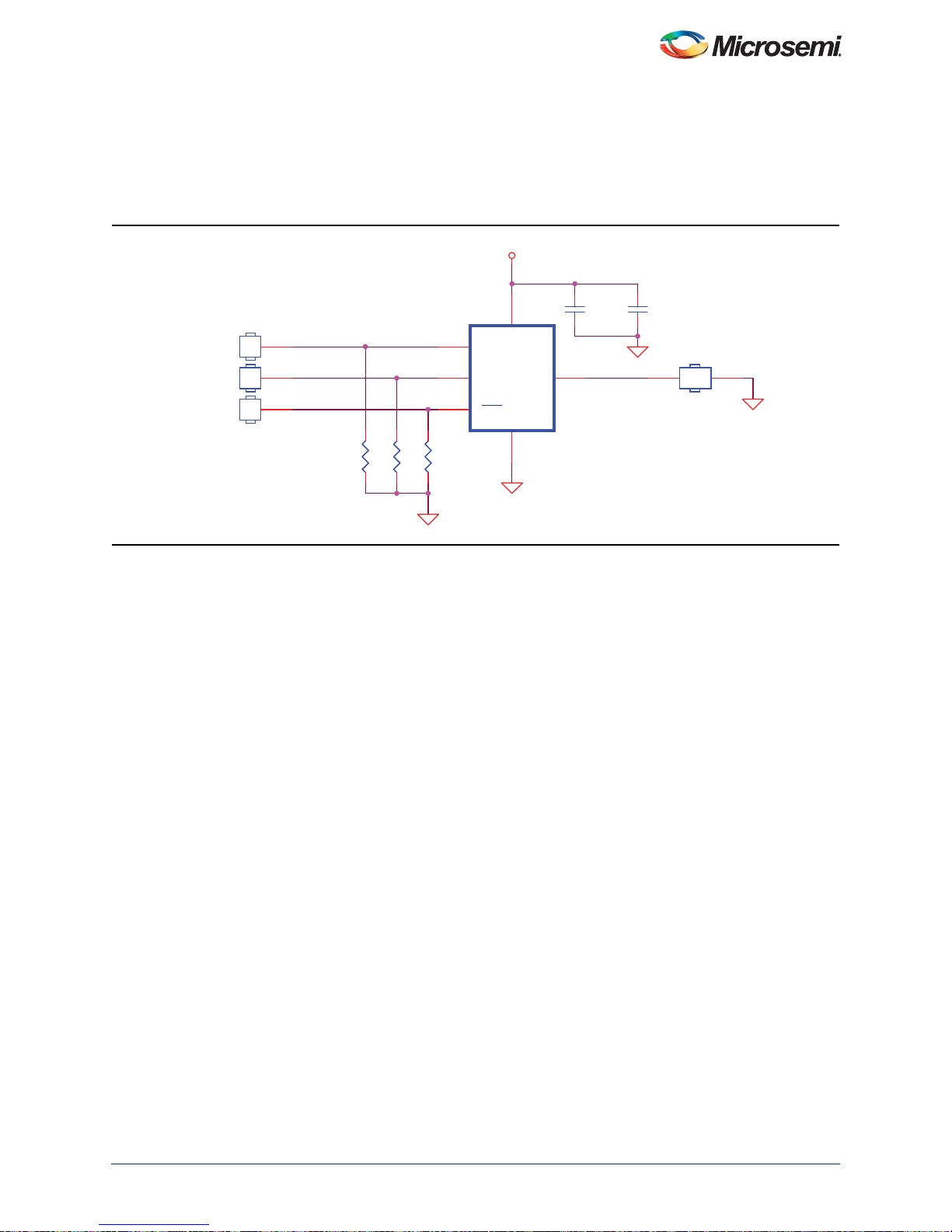

The SmartFusion MSS provides options to interface with a variety of external memory devices such as

NOR flash and synchronous or asynchronous SRAM for large applications co de. The external memory

controller (EMC) interface of SmartFusion MSS is 3.3 V LVTTL compliant. This interfaces directly with

3.3 V SRAM and flash devices. On the development board, two 16-Mbit SRAM Cypress

CY7C1061DV33-10ZSXI and two 64-Mbit parallel flash memory Numonyx JS28F640J3D-75 memories

interface with EMC region0 and region1. Microsemi expects these memories to be used in most

SmartFusion applications.

For applications that require larger SRAM memory than this, an alternative 128-Mbit, 1.8 V

asynchronous PSRAM Micron

only available at 1.8 V, coupled with the fact that the EMC interface does not allow region0 and region1 to

be completely independent of each other due to shared chip select, 128-Mbit, 1.8 V, parallel flash

memory Numonyx JS28F128P30T85 873824 is mounted on the board as a companion for the 1.8 V

SRAM. This requires a 3.3 V to 1.8 V conversion to interface the 3.3 V EMC with these 1.8 V memories.

If the EMC is not used, the shared EMC I/Os are available as 3.3 V GPIO at the expansion connector. To

provide the option of a 1.8 V interface and to make the EMC I/Os available to user application, an

AGLP125 FPGA is used as an I/O translator on the board. Based on the EMC configuration selected, the

AGLP125 can be programmed either as a 3.3 V to 1.8 V level converte r or I/O extender (with all 3.3 V

and 1.8 V memories held in tristate). This device can be selectively programmed by choosing appropriate

jumper settings to select the JTAG chain.

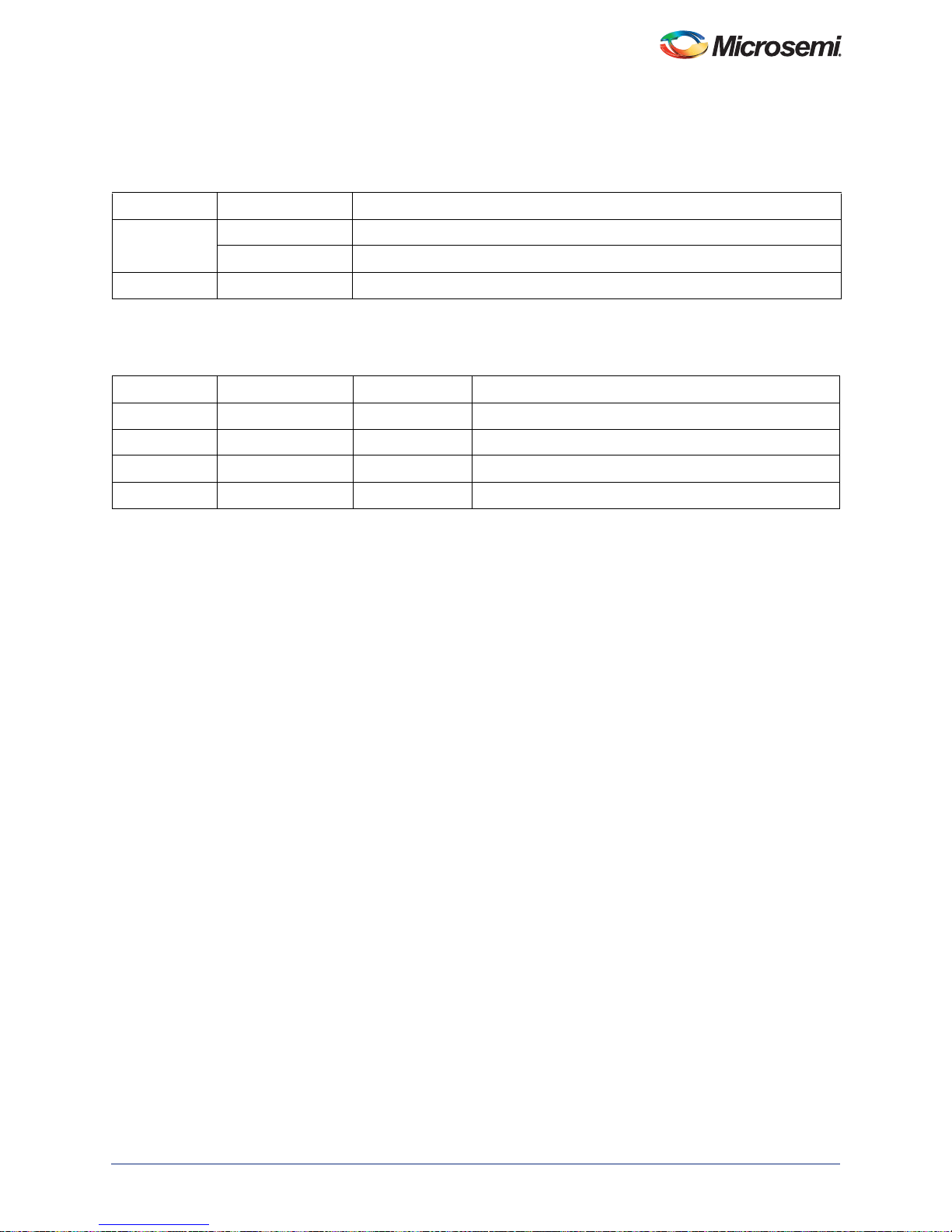

Figure 3-28 captures the memory section overview.

®

MT45W8MW16BGX is also offered. Given that memories of this size are

SmartFusion Development Kit

Figure 3-28 • Memory Top Level

Revision 7 37

Page 38

Components Description and Operation

3.3 V Memory Section

Mounted on the development board are two instances of 16-Mbit asynchronous SRAM. Also included are

two 64-Mbit parallel flash memories (FLASH). Both instances of the asynchronous SRAM are connected

to region0 of the EMC interface of the SmartFusion MSS. Similarly both instances of the flash are

connected to region1 of the EMC interface of the SmartFusion MSS. These operate at 3.3 V and are

directly interfaced to the EMC. The AGLP125 FPGA is not use d in this case and is he ld in Flash*Freeze

mode to avoid any power consumption.

Table 3-14 gives the summary of jumper settings needed to access the 3.3 V memories.

Table 3-14 • Jumper Settings to Interface EMC with 3.3 V Memories (SRAM and flash)

Jumper Pin Pin Connection Details

JP17 2 3 EMC chip select for region0 to CS1 of SRAM

JP19 2 3 EMC chip select for region1 to CS1 of flash

JP24 1 2 FLASH_VPEN to 3.3 V (to enable 3.3 V flash)

JP16 2 3 To keep AGLP125 in Flash*Freeze mode

Asynchronous SRAM Memory Components

The 3.3 V asynchronous SR AMs populated on the board are 16-Mb it SRAM Cypress CY7C1061DV3310ZSXI (PSRAM), as shown in Figure 3-29 on page 39. These interface with the EMC port of the

SmartFusion MSS. They provide a reasonable off-chip memory at high speed that the hard ARM

Cortex-M3 processor can use for applications such as RTOS.

Performance Note: Table 3-15 describes the External Memory Controller settings for 100 MHz and 80

MHz system performance. A slower speed device might work at higher speed—but it is not always

guaranteed. These are obtained on the development board with an application that uses asynchronous

SRAM extensively.

Tab le 3-15 • EMC Settings for 3.3 V Asynchronous SRAM Performance

Port Size: Half Word

Latency in FCLK(HCLK) Cycles

Read Latency for First Access 1 1

Read Latency for Remaining Accesses 1 1

Write Latency 0 0

Note: Make sure to keep AGLP125 device in Flash*Freeze mode by closing pins 2-3 of JP16.

System Clock Frequency FCLK (HCLK)

100 MHz 80 MHz

38 Revision 7

Page 39

SmartFusion Development Kit

V3P3

50

29

23

14

2

U21

U21

DATA0 {20,21,26}

DATA1 {20,21,26}

DATA2 {20,21,26}

DATA1

DATA2

DATA0

22

25

IO0

IO124IO2

VCC5

VCC4

VCC3

VCC2

VCC1

A0

A2

A1

9

10

11

ADDRESS1

ADDRESS3

ADDRESS2

ADDRESS1

ADDRESS2{20,21,26}

ADDRESS3

{20,21,26}

{20,21,26}

DATA0 {20,21,26}

DATA1 {20,21,26}

DATA4 {20,21,26}

DATA3 {20,21,26}

DATA5 {20,21,26}

DATA3

DATA4

DATA5

27

28

30

IO3

IO4

IO5

A38A4

A5

7

48

ADDRESS4

ADDRESS5

ADDRESS6

ADDRESS6

ADDRESS4

ADDRESS5{20,21,26}

{20,21,26}

{20,21,26}

DATA3 {20,21,26}

DATA4 {20,21,26}

DATA2 {20,21,26}

DATA6 {20,21,26}

DATA7 {20,21,26}

DATA8 {20,21,26}

DATA6

DATA7

DATA8

49

33

31

IO8

IO6

IO7

A845A944A10

A6

A7

47

46

ADDRESS9

ADDRESS7

ADDRESS8

ADDRESS7{20,21,26}

ADDRESS8{20,21,26}

ADDRESS9

{20,21,26}

DATA5 {20,21,26}

DATA6 {20,21,26}

DATA7 {20,21,26}

DATA9 {20,21,26}

DATA11 {20,21,26}

DATA10 {20,21,26}

DATA9

DATA10

DATA11

DATA12

52

51

1

54

IO9

IO11

IO10

A11

37

36

38

ADDRESS10

ADDRESS11

ADDRESS12

ADDRESS13

ADDRESS11

ADDRESS12

ADDRESS10{20,21,26}

{20,21,26}

{20,21,26}

DATA9 {20,21,26}

DATA10 {20,21,26}

DATA8 {20,21,26}

DATA12 {20,21,26}

DATA14 {20,21,26}

DATA13 {20,21,26}

DATA13

DATA14

3

IO12

IO144IO13

A1434A15

A13

A12

35

ADDRESS14

ADDRESS15

ADDRESS13{20,21,26}

ADDRESS14

ADDRESS15

{20,21,26}

{20,21,26}

DATA13 {20,21,26}

DATA11 {20,21,26}

DATA12 {20,21,26}

DATA15 {20,21,26}

DATA15

6

IO15

A17

A16

19

20

21

ADDRESS19

ADDRESS16

ADDRESS17

ADDRESS18

ADDRESS16{20,21,26}

ADDRESS17

ADDRESS18{20,21,26}

{20,21,26}

DATA14 {20,21,26}

DATA15 {20,21,26}

ADDRESS21 {20,21,26}

MCS_N_0

MBYTEN_0 {21,26}

MBYTEN_1 {21,26}

39

12

16

13

BLE

CE2

CE1

BHE

A19

A18

17

18

ADDRESS20

ADDRESS19{20,21,26}

ADDRESS20

{20,21,26}

SRAM1_ADDRESS21

MCS_N_0

MBYTEN_0 {21,26}

MBYTEN_1 {21,26}

40

NC243NC1

MANUFACTURER P/N = CY7C1061AV33-10ZXC

MANUFACTURER P/N = CY7C1061AV33-10ZXC

MANUFACTURER = Cypress Semiconductor

MANUFACTURER = Cypress Semiconductor

VSS5

53

VSS4

41

VSS3

32

VSS2

26

VSS1

5

OE

WE

42

15

CY7C1061AV33-10ZXC

CY7C1061AV33-10ZXC

MOE_N_0{21,26}

MRW_N{20,21,26}MOE_N_0{21,26}

V3P3

R2221KR222

23

Shunt b/w

JP17 pins

Memory Device

Config

3.3V INTERFACE

1.8V INTERFACE 1 2

MCS_N_0

MANUFACTURER P/N = 3-644456-3

MANUFACTURER = Tyco Electronics

MANUFACTURER P/N = 3-644456-3

MANUFACTURER = Tyco Electronics

JP17

JP17

123

1K

F2_MCS_N_0{21,26}

V3P3

Figure 3-29 • PSRAM Connections

50

29

23

14

2

U20

U20

DATA0

DATA1

DATA2

25

22

IO0

IO124IO2

VCC5

VCC4

VCC3

VCC2

VCC1

A0

A110A2

9

11

ADDRESS2

ADDRESS3

ADDRESS1

ADDRESS1

ADDRESS2

ADDRESS3

{20,21,26}

{20,21,26}

{20,21,26}

DATA3

DATA4

DATA5

28

27

IO530IO6

IO3

IO4

A548A6

A3

A4

7

8

ADDRESS4

ADDRESS5

ADDRESS6

ADDRESS4

ADDRESS5

ADDRESS6

{20,21,26}

{20,21,26}

{20,21,26}

DATA6

DATA7

DATA8

33

31

49

IO8

IO7

A7

A8

46

45

47

ADDRESS8