Micronas Intermetall SDA9589X, SDA9489X Datasheet

PRELIMINARY DATA SHEET

SDA 9489X PIP IV Advanced

SDA 9589X SOPHISTICUS

High-End

Picture-In-Picture ICs

Edition Feb. 28, 2001

6251-562-1PD

SDA 9489X

Preliminary Data Sheet

SDA 9589X

High-end Picture-In-Picture (PIP) ICs

Version 1.3 CMOS

General Description

SDA 9489X ’PIP IV Advanced’ and SDA 9589X

’SOPHISTICUS’ belong to a new generation of Picturein-Picture (PiP) processors that combine high-quality

digital PIP signal processing, digital multistandard

color decoding and AD/DA conversion on a single chip.

Both devices are equipped with CVBS and Y/C input

interfaces. In addition the SDA SDA 9589X is also able

P-DSO28-1

to process YUV input signals for displaying high quality

video signals e.g. coming from a DVD source.

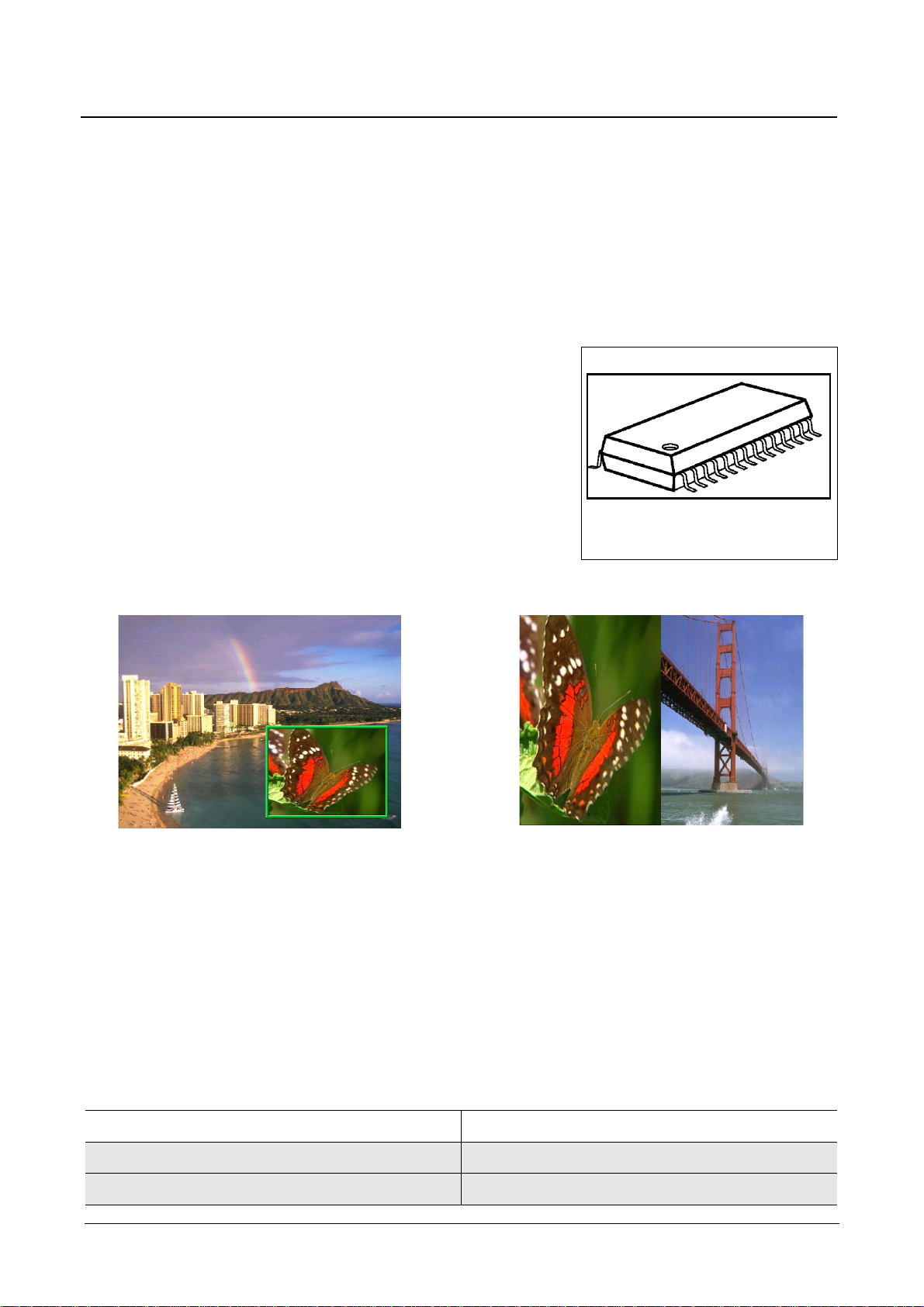

Figure 0-1 Picture-In-Picture

The integrated digital color decoder is able to decode all analog TV standards (PAL,

NTSC and SECAM) and detects the standard automatically. Therefore the IC is suited

for world-wide use.

A picture reduction from 1/4 to 1/81 of original size selectable in fine steps is possible.

The transfer functions of the decimation filters are optimally matched to the selected

picture size reduction and can furthermore be adjusted to the viewer’s requirements by

a selectable peaking. A maximum of 324 luminance and 2x81 chrominance pixels per

line are stored in the memory. The PiP supports split-screen applications as well as

multi-PiP display.

Type Package

SDA 9489X P-DSO28-1

SDA 9589X P-DSO28-1

Micronas -2

SDA 9489X

Preliminary Data Sheet

SDA 9589X

1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

2 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4 System Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.1 Analog Frontend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.1.1 Input Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.1.2 AD-Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.1.3 Automatic Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

4.1.4 Signal Magnitudes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

4.2 Inset Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

4.3 Chroma Decoding And Standard Identification . . . . . . . . . . . . . . . . . . . . . .13

4.4 Comb Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

4.5 Luminance Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

4.6 Decimation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

4.6.1 Single PIP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

4.6.2 Continuos Zoom . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

4.6.3 Horizontal And Vertical Fine Positioning . . . . . . . . . . . . . . . . . . . . . . . . .19

4.6.4 Multi Display Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

4.6.5 Split Screen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

4.6.6 Multi-PiP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

4.7 Display Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

4.7.1 100 Hz Frame Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

4.7.2 Mixed Standard Applications And (S)VGA Support . . . . . . . . . . . . . . . . .26

4.7.3 Display standard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

4.7.4 Picture Positioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

4.7.5 Wipe In / Wipe Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

4.8 Output Signal Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

4.8.1 Luminance Peaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

4.8.2 RGB Matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

4.8.3 Frame Generation And Colored Background . . . . . . . . . . . . . . . . . . . . .32

4.8.4 16:9 Inset Picture Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

4.8.5 Parent Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

4.8.6 Select Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

4.8.7 Automatic Brightness Reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

4.9 On Screen Display (OSD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

4.9.1 Display Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

4.9.2 Character Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

4.9.3 Character and Character Background Color . . . . . . . . . . . . . . . . . . . . . .36

4.10 DA-Conversion And RGB / YUV Switch . . . . . . . . . . . . . . . . . . . . . . . . . . .36

4.10.1 Pedestal Level Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

4.10.2 Contrast, Brightness and Peak Level Adjustment . . . . . . . . . . . . . . . . . .38

Micronas -3

SDA 9489X

Preliminary Data Sheet

SDA 9589X

4.11 Data Slicer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

4.11.1 Closed Caption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

4.11.2 Widescreen Signalling (WSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

4.11.3 Indication Of New Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.11.4 Violence Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5 Application Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

6 I2C Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

6.1 I2C Bus Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.2 I2C-Bus Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

6.3 I2C bus Command Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

6.4 I2C Bus Command Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

7 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

8 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

9 Recommended Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

10 Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

11 Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

12 Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Micronas -4

SDA 9489X

SDA 9589X

Preliminary Data Sheet

Features

1Features

• Single chip solution:

– AD-conversion for CVBS or Y/C or YUV

1)

, multistandard color decoding, PLL for

synchronization of inset channel, decimation filtering, embedded memory, RGBmatrix, DA-conversion, RGB/YUV switch, data-slicer and clock generation

integrated on chip

• Analog inputs:

– 3x CVBS or 1x CVBS and 1x Y/C or 1xYUV

1)

alternatively

– Clamping of each input

– All ADCs with 8 bit amplitude resolution

– Automatic Gain Control (AGC) for Y and CVBS

• Inset Synchronization:

– Multiple time constants for reliable synchronization

– Automatic recognition of 625 lines / 525 lines standard

• Color Decoder:

– PAL-B/G, PAL-M, PAL-N(Argentina), PAL60, NTSC-M, NTSC4.4 and SECAM

– Adjustable color saturation

– Hue control for NTSC

– Automatic Chroma Control (-24 dB ... +6 dB)

– Automatic recognition of chroma standards: different search strategies selectable

– Single crystal for all standards

– IF-characteristic compensation filter

• Decimation:

– PIP sizes between 1/81 and 1/4 adjustable with steps of 2 lines and 4 pixel

– Resolution up to 324 luminance and 2x81 chrominance pixels per inset line

– Horizontal and vertical filtering dependent on picture size

– Automatic zoom in/out possible with three speeds

• Display Features:

– 7 bit per pixel stored in memory

– Field and joint-line free frame mode display (even at 100/120 Hz AABB with picture

sizes<=1/9)

– Two ’split-screen’ modes with horizontal decimation of 2 and vertical of 1.5 or 1.0

–POP display

– Up to 12 pictures of 1/36th size (11 still and 1 moving)

– Up to 6 pictures of 1/16th size (5 still and 1 moving)

– Up to 3 pictures of 1/9th size (2 still and 1 moving)

– Display on VGA and SVGA screen (f

limited to 40kHz)

H

– 8 different read frequencies for 16:9 compatibility

– Line doubling mode for progressive scan applications

1)

SDA 9589X only

Micronas 1-5

SDA 9489X

SDA 9589X

Preliminary Data Sheet

– Freeze picture

– Coarse positioning at 4 corners of the parent picture

– Fine positioning at steps of 4 pixels and 2 lines

– Wipe in / out programmable with 3 time periods

• Output signal processing:

–7 Bit DAC

– RGB or YUV switch: insertion of an external source without PIP processing

– Digital interpolation for anti-imaging

– Adjustable transient improvement for luma (peaking)

– Contrast, Brightness and Pedestal Level adjustable

– Analog outputs: Y, +(B-Y), +(R-Y), or Y, -(B-Y), -(R-Y) or RGB

– Three RGB matrices available: NTSC(Japan), NTSC(USA) or EBU

– 64 different background colors and 4096 different frame colors

– Plain or 3D frame with variable width and height

• Data Slicing:

– Slicing of closed-caption (CC) or wide-screen-signaling (WSS) data

– Violence blocking capability (V-chip)

– Several filter for XDS data extraction

• On-screen display:

– 64 characters programmable

– 5 characters displayed in every PIP picture or 3 rows of 20 characters each

– 4 different character luminance values or frame color

– 4 background luminance values or (semi-) transparent mode

2

•I

C-Bus control (400 kHz)

• High stability clock generation

• PDSO 28-1 package (SMD)

• Full SDA 9488X and SDA 9588X backward compatibility

• SDA 9388X / SDA 9389X pinout compatibility

• 3.3V supply voltage (5V input capable)

Features

Micronas 1-6

SDA 9489X

SDA 9589X

Preliminary Data Sheet

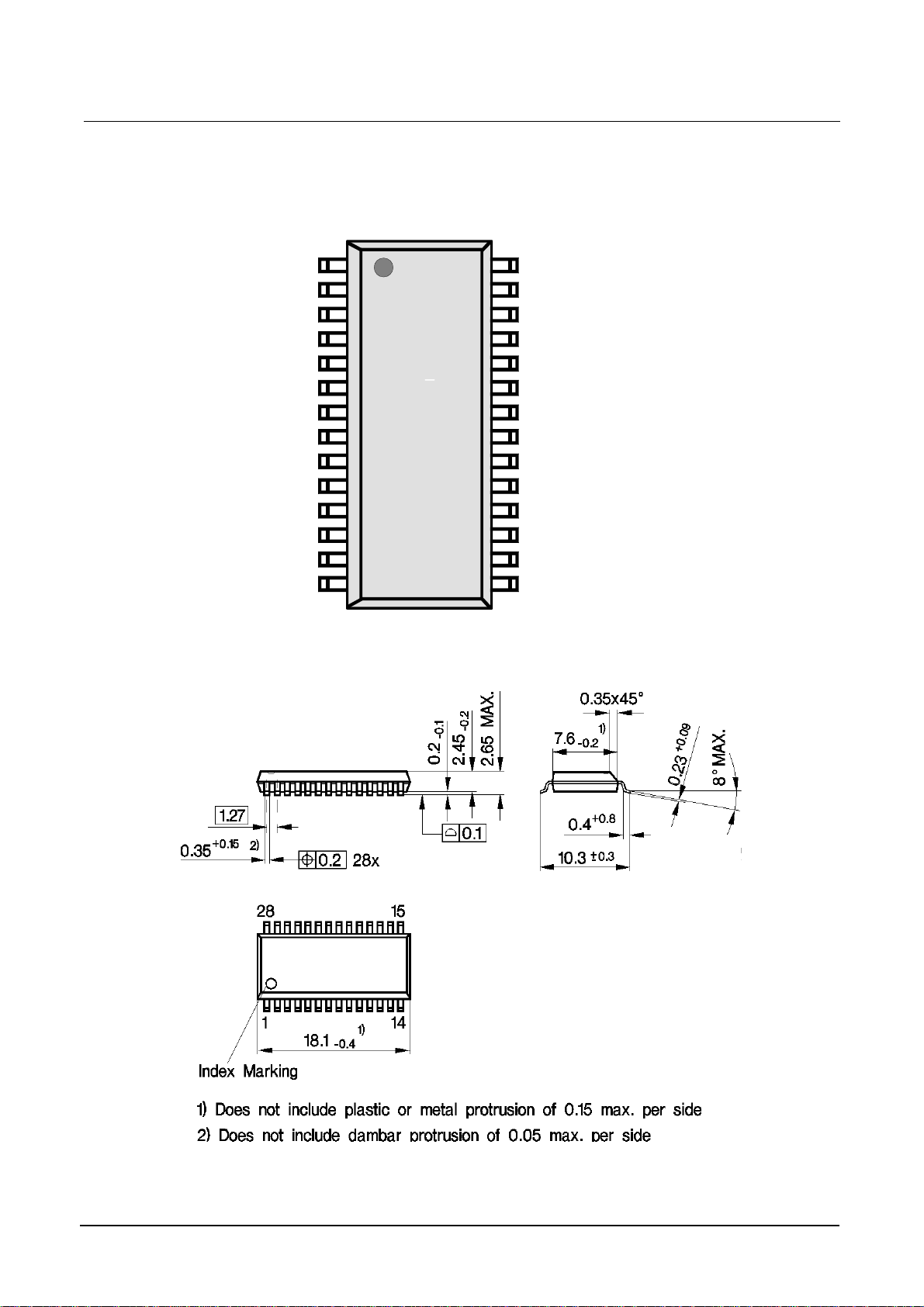

2 Pin Configuration

XIN

XQ

HSP

VSP

SDA

SCL

VDD

VSS

I2C

INT

IN1

IN2

IN3

FSW

Pin Configuration

1

2

3

4

5

6

7

8

9

10

11

12

13

14

PDSO 28 -1

28

27

26

25

24

23

22

21

20

19

18

17

16

15

CVBS1

VREFM

CVBS2

VREFL

CVBS3

VSSA1

VDDA1

VREFH

VSSA2

VDDA2

OUT1

OUT2

OUT3

SEL

Figure 2-1 Pinning

Figure 2-2 Package Outlines

Micronas 2-7

SDA 9489X

SDA 9589X

Preliminary Data Sheet

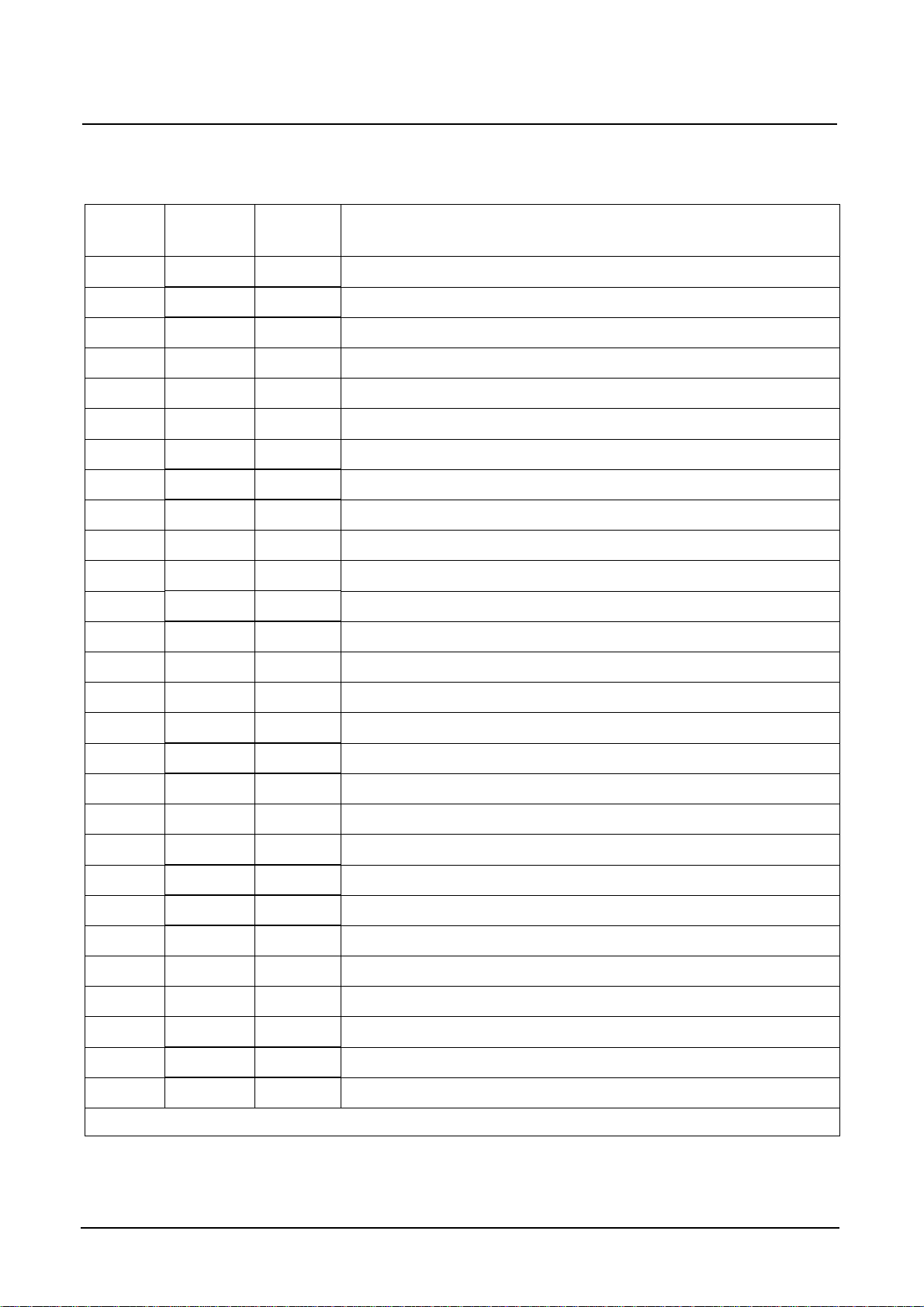

Numb

er

1 XIN I crystal oscillator (input) or external clock input

2 XQ O crystal oscillator (output)

3 HSP I/TTL horizontal sync for parent channel

4 VSP I/TTL vertical sync for parent channel

5SDAI/OI

6SCL II

7 VDD S digital supply voltage

8 VSS S digital ground

9I2C II

10 INT O/TTL interrupt

11 IN1 I/ana V/R input for external YUV/RGB source

Name Type Description

2

C-bus data

2

C-bus clock

2

C Address

Pin Configuration

12 IN2 I/ana Y/G input for external YUV/RGB source

13 IN3 I/ana U/B input for external YUV/RGB source

14 FSW I fast switch input for YUV/RGB switch

15 SEL O fast blanking output for PIP

16 OUT3 O/ana analog output: chrominance signal +(B-Y) or -(B-Y) or B

17 OUT2 O/ana analog output: luminance signal Y or G

18 OUT1 O/ana analog output: chrominance signal +(R-Y) or -(R-Y) or R

19 VDDA2 S analog supply voltage for DAC

20 VSSA2 S analog ground for DAC

21 VREFH I/ana uppper reference voltage for ADC and DAC

22 VDDA1 S analog supply voltage for ADC

23 VSSA1 S analog ground for ADC

24 CVBS3 I/ana CVBS3 or V (SDA 9589X) or C Input

25 VREFL I/O lower reference voltage for ADC

26 CVBS2 I/ana CVBS2 or U (SDA 9589X) or Y (from Y/C) Input

27 VREFM I/O mid-level reference voltage for ADC

28 CVBS1 I/ana CVBS1 or Y (from YUV, SDA 9589X) Input

I= Input / ana=analog / O= Output / TTL=Digital (TTL) / S=Supply voltage

Table 2-1 Pin Description

Micronas 2-8

SDA 9489X

W

3

SDA 9589X

Preliminary Data Sheet

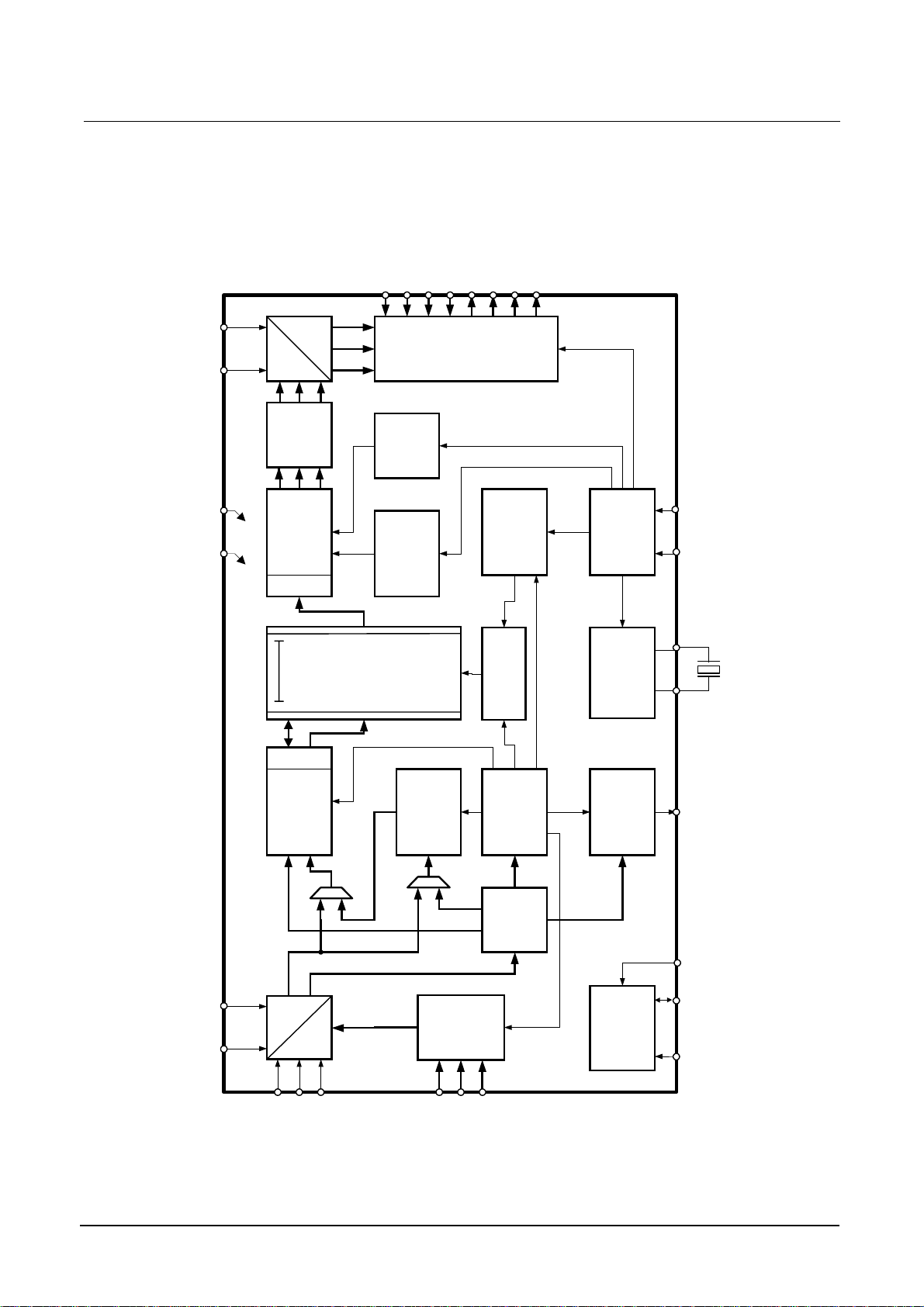

3 Block Diagram

DAC

Triple

VDDA2VSSA2VDD VSS

RGB

8

Over-

Peaking

DEMUX

Block Diagram

IN2

13

OSD

Generation

IN3

FS

18

14

Fast

RGB/YUV

OUT1OUT2OUT

16

17

Switch

Display

Controller

15

SEL

Parent

Sync

Processing

HSP VSP

IN1

12

11

3x7bit

Matrix

Insertion

sampling

Frame

MUX

H/V Scaler

Decimation

Skewcomp.

DUV/DCHR

DCVBS/DY

1)

22 23 71920

VDDA1 VSSA1

27

ADC

Triple

3x8bit

25

21

eDRAM

Color

Decoder

Input

28

kbit

Memory

768

PAL/ SECAM/ NTSC

Select

26

Clamp

24

Inset

Y/C and

Gain

Controller

Sync

Sync

Processing

Sep.

Clock

Data Slicer

C

2

I

1210965 34

Synthesizer

Acquisition

Controller

XIN XQI2CSCL SDA

INTR

XTAL

20.25 MHz

1) SDA 9589X, SDA 9489X: 2x8bit

VREFH

VREFM

VREFL

CVBS1

CVBS2

CVBS3

Figure 3-1 Block Diagram

Micronas 3-9

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

4 System Description

4.1 Analog Frontend

4.1.1 Input Selection

An analog inset CVBS signal can be fed to the inputs CVBS1-3 of SDA 9589X/SDA

9489X. Each of these sources is selectable via I

2

C bus (CVBSEL). CVBS2 and CVBS3

can be used as separate Y/C inputs. At SDA 9589X YUV sources can be connected to

CVBS1, CVBS2 and CVBS3 provided YUV operation being enabled (YUVSEL). Using

an external switch SDA 9589X can operate in applications with both YUV and CVBS

signals.

CVBSEL YUVSEL Input remark

D1 D0

CVBS1 CVBS2 CVBS3

0 0 0 CVBS

0 1 0 CVBS

1 0 0 Y (VBS) C Y/C mode

1 1 0 CVBS

X X 1 Y (VBS) U (CB) V (CR) YUV mode

(only SDA 9589X)

Table 4-1 Input selection

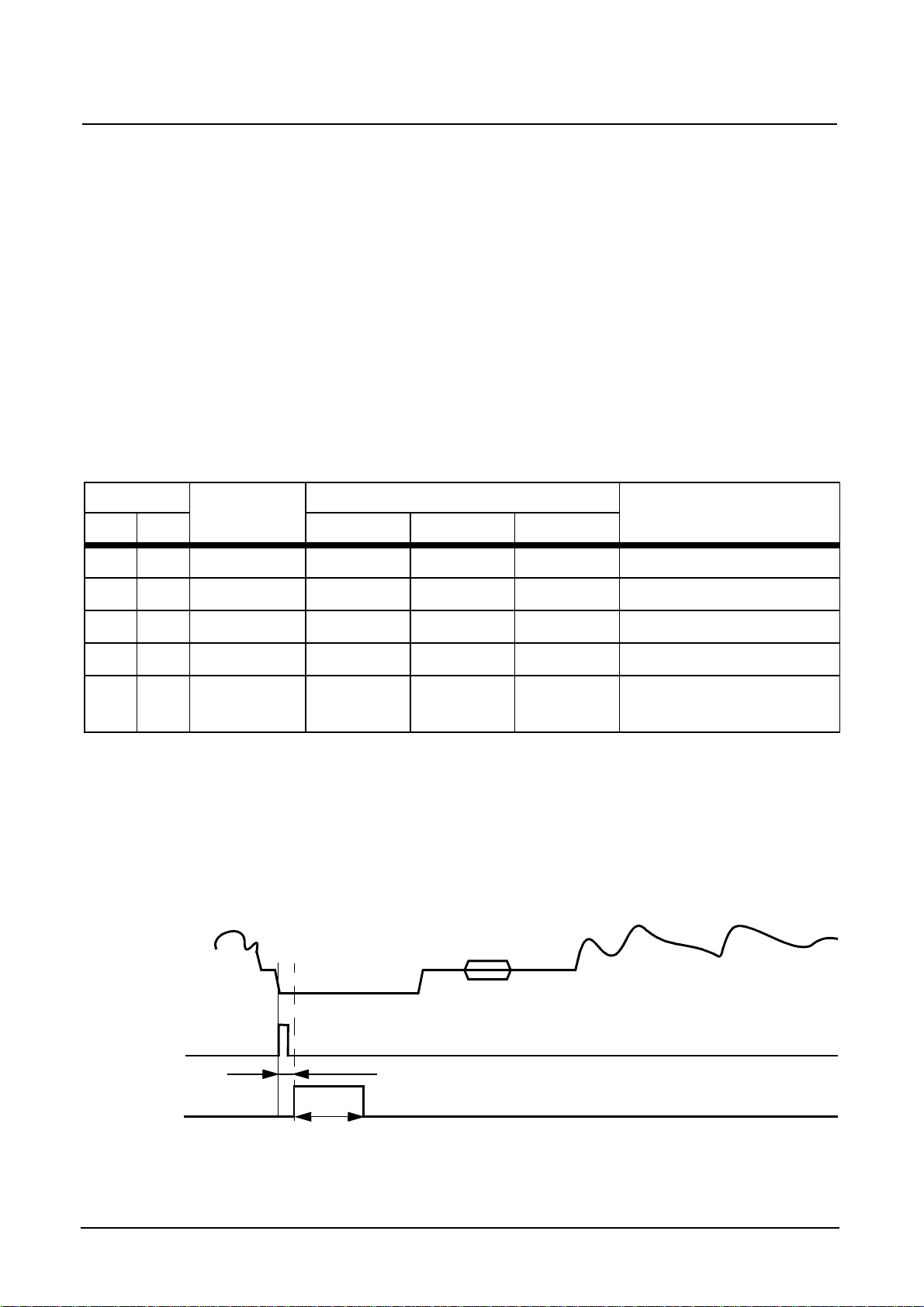

4.1.2 AD-Conversion

All signal are clamped and AD-converted with an amplitude resolution of 8bit. CVBS and

Y signals are clamped to the sync bottom whereas U/V and C signals are clamped to

their mid-level during blanking.

Inset

Video

HD

CLMPIST

CLAMPI

CLMPID

Figure 4-1 Clamping timing

Micronas 4-10

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

The clamping pulse can be shifted in position (CLMPIST) and length (CLMPID) to adjust

to the specific application. The ADCs are driven by a 20.25 MHz free running crystal

clock which is not related to the incoming CVBS signal.

To avoid aliasing by subsampling the CVBS signal and the Y/C signals should be bandlimited to 10MHz. In the same manner the U/V signal frequency spectrum should not

exceed 5 MHz. The digital filtering suppresses all frequencies above the usable

spectrum.

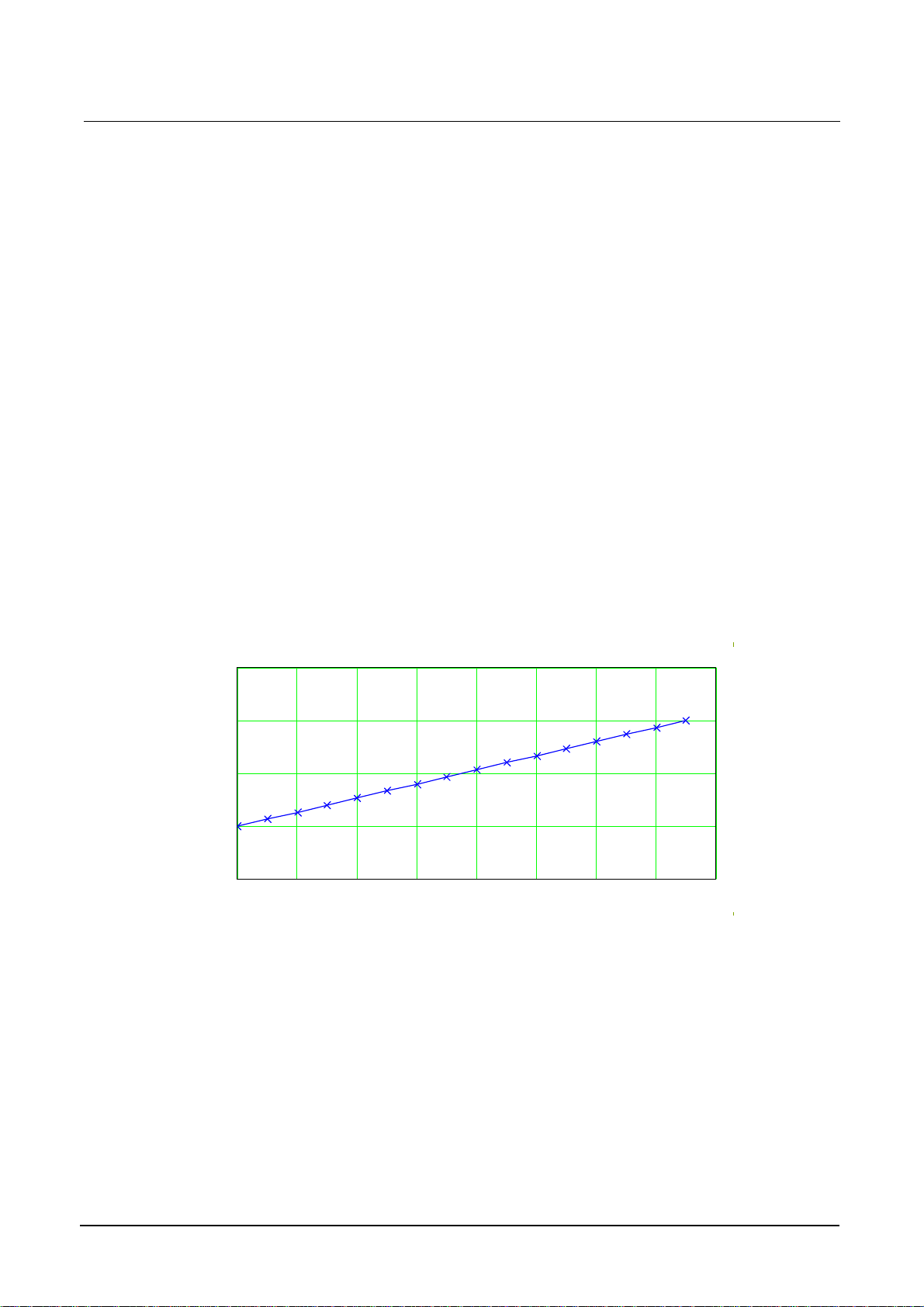

4.1.3 Automatic Gain Control

To accommodate to different CVBS input voltages an automatic gain control has been

implemented. The chip works correctly for input voltages in the range from 0.5 to 1.5V

pp

For best signal-to-noise ratio, the maximum CVBS amplitude is recommended if

available. The AGC behavior can be chosen out of four possibilities (AGCMDE).

The sync height serves as reference for the gain control in the typical application. When

using overflow detection only, the gain is set to maximum and is reduced whenever an

overflow occurs. This procedure will be executed again when a channel change is

detected or the gain control is manually reset by AGCRES.

.

2

1.5

1

Input Voltage [V]

0.5

0

0 2 4 6 8 10 12 14 16

Automatic Gain Control Characteristic

AGCVAL

Figure 4-2 AGC characteristic

4.1.4 Signal Magnitudes

The nominal CVBS signal with 75% color has a magnitude of 1 V

is left to permit signals with 100% color resulting in 1.23 V

pp

. The upper headroom

pp

. The Y signal must always

contain the sync part. Its levels correspond to the CVBS levels except for the missing

color and burst. After A/D conversion the video part is clamped to its black value and is

amplified to 224 digital steps. The nominal signal levels ensure correct brightness and

saturation. The YUV signal levels conform to the ITU 601 recommendation.

Micronas 4-11

SDA 9489X

SDA 9589X

Preliminary Data Sheet

CRYC = 1.2 Vpp

255

224

128

32

burst

0

255

217

68

upper headroom

white

black

burst

4

0

lower headroom

SRY = 1 Vpp

Figure 4-3 CVBS/Y and chroma ADC input signal range

255

240

212

255

240

212

System Description

upper headroom

75% chroma

lower headroom

upper headroom upper headroom

100% chroma

SRC = 0.89 Vpp

CRYC = 1.2 Vpp

75% U

128

SRUV = 0.7 Vpp

44

16

0

lower headroom

Figure 4-4 UV input signal range

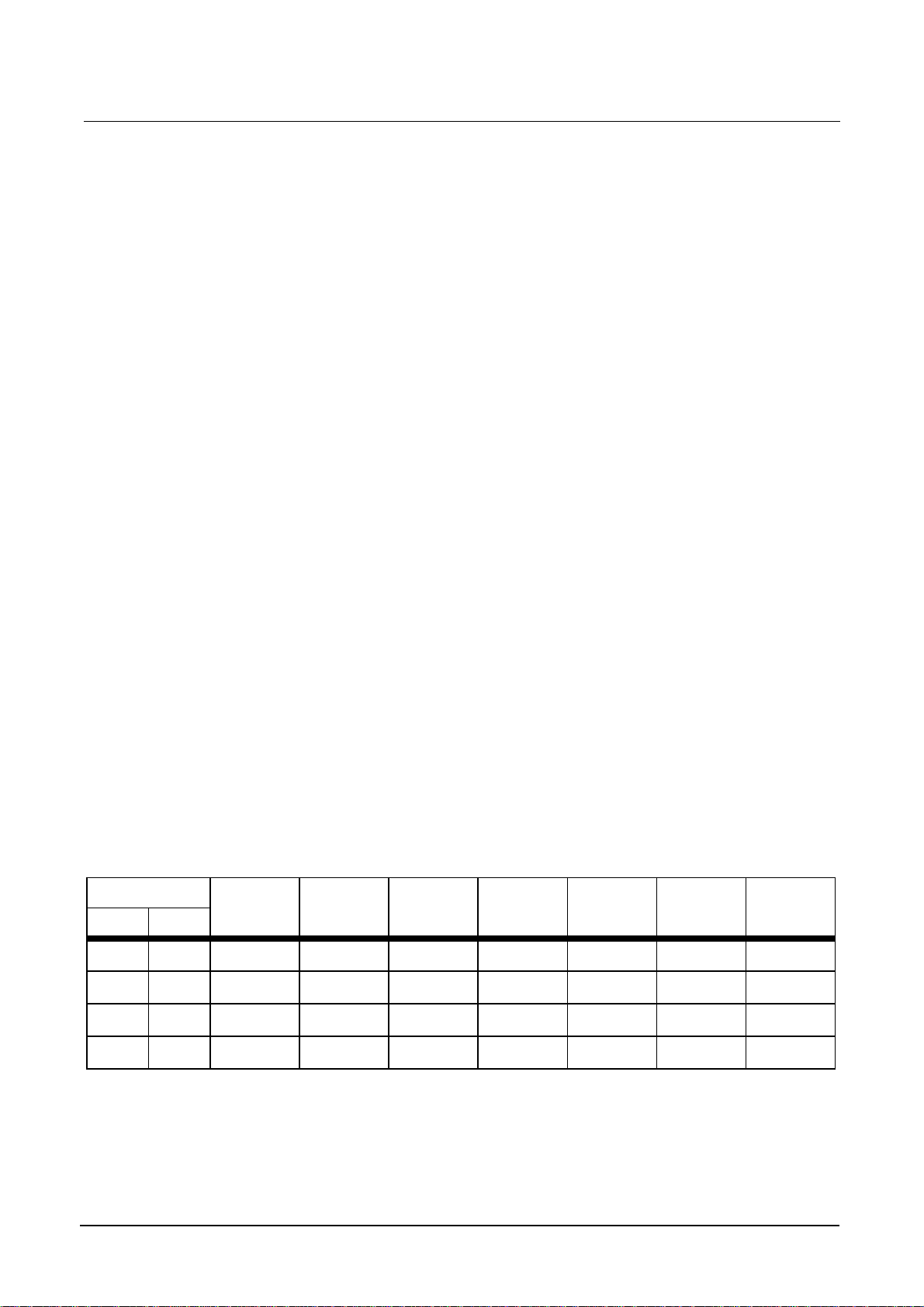

AGCVAL Conversion

D3 D2 D1 D0

Range

CRYC

0000 0.5Vpp0.42V

... ... ...

1000 1.2V

pp

... ... ...

CRUV = 0.8 Vpp

Signal

Range

SRY

1.0V

pp

128

44

16

pp

75% V

CRUV = 0.8 Vpp

SRUV = 0.7 Vpp

0

Signal

Range

SRC

0.89V

lower headroom

pp

Conversion

Range

CRUV

0.8V

pp

Signal

Range

SRUV

0.7V

pp

1111 1.5V

pp

1.25V

pp

Table 4-2 ADC conversion range and required input signal voltage

Micronas 4-12

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

4.2 Inset Synchronization

Horizontal and vertical sync pulses are separated after elimination of the high frequency

components of the CVBS signal by a low pass filter. Horizontal sync pulses are

generated by a digital phase-locked-loop (DPLL). Its time constant is adjustable between

fast and slow behavior in four steps (PLLITC) to consider different input sources (e.g.

VCR). Noisy input signals become more stable when a noise-reduction is enabled

(NSRED). Additionally weak input signals from a satellite dish (’fishes’) become more

stable when SATNR is enabled. Both should be enabled to have best available

performance. When NOSIGB is enabled, a colored background is shown instead of the

picture when PIP is out of synchronization. The detected line standard is indicated by

SYNCSTAT.

4.3 Chroma Decoding And Standard Identification

The system is able to decode NTSC and PAL signals with a subcarrier of 3.58MHz and

4.43MHz (PAL B/M/N/60, NTSC M/4.4) as well as SECAM signals with 4.05/4.2MHz

subcarrier. The system may be forced to a certain standard, or an automatic standard

detection can be used (CSTAND). For automatic standard detection, some standards

which are not likely to be received can be ignored to improve the detection process.

Depending on the detected line standard (525 or 625 lines) the color standard detection

circuit searches for 60 Hz signals (NTSC-M / PAL-M / PAL 60 / NTSC44) or 50 Hz signals

(PAL-B / SECAM / PAL-N) respectively. Within each line standard, the standard is

detected by consequently switching from one to another. This standard detection

process can be set to medium or fast behavior (LOCKSP). In medium behavior 30 fields

(in fast 20) are used to detect the standard. If not being successful within this time period

the system tries to detect another one. For SECAM detection, a choice between two

recognition levels is possible (SCMIDL) and the evaluated burst position is selectable

(BGPOS).

.

CSTANDEX NTSC-

D1 D0

M

PAL60 PAL-N PAL-M PAL-B SECAM NTSC

44

00

0 .

1

10

11

Table 4-3 Considered color standards for automatic standard detection

For getting the chrominance information the digitized video signal is multiplied with the

regenerated color subcarrier once in-phase and once phase-shifted by 90°. After

lowpass filtering digital UV is available for PAL and NTSC. The subcarrier is regenerated

Micronas 4-13

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

by a digital PLL. At SECAM operation the PLL runs free and generates the line-wise

alternating subcarriers. A CORDIC structure demodulates the frequency-modulated UV

signals. The following SECAM de-emphasis filter characteristic is adjustable (DEEMP).

The chroma signal can be filtered before demodulation by means of a selectable IFprefilter (IFCOMP).

0

5

10

gain [dB]

15

DEEMP = ’00’

DEEMP = ’01’

DEEMP = ’10’

DEEMP = ’11’

5

2.5

IFCOMP = ’00’

0

IFCOMP = ’01’

2.5

gain [dB]

IFCOMP = ’10’

5

7.5

3.58 4.4

20

0 0.5 1 1.5 2 2.5

frequency [MHz]

10

2 3 4 5 6

frequency [MHz]

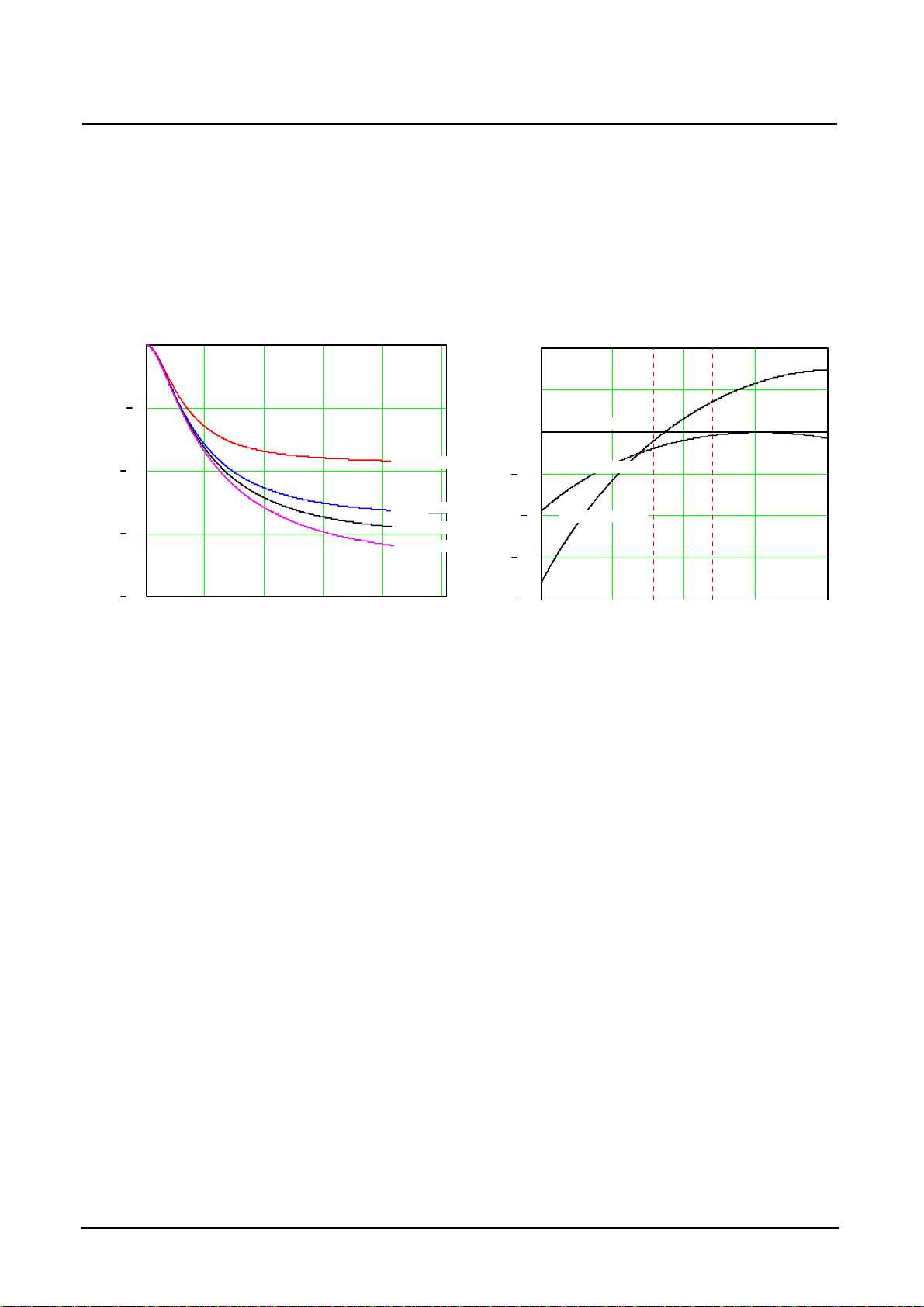

Figure 4-5 SECAM de-emphasis filter characteristic and IF-compensation filter

characteristic

The Hue Control (HUE) influences the phase of the demodulation subcarrier between

-44.8° and 43.4° in steps of 1.4°. This is provided for NTSC only and adjustment is

ineffective for PAL and SECAM signals.

The reference for the subcarrier generation is a crystal stable clock of 20.25000 MHz. In

order to avoid color standard detection problems, the maximum deviation of this

frequency should not exceed 100ppm. For a good PLL locking behavior a maximum

deviation of 40ppm is recommended. A small frequency adjustment (-150 ... +310 ppm)

is possible for using a crystal with small frequency deviations (SCADJ). For test

purposes, CPLL allows to open the loop of the chroma PLL.

For deviations in the chroma signal up to 30dB, a stable output amplitude after chroma

decoding is achieved due to the ACC (Automatic Chroma Control). If the chroma signal

(color burst) is below a selectable threshold (CKILL), the color will be switched off.

Alternatively the color-killer can be bypassed and the color can be switched on or off

under all conditions (COLON). By setting ACCFIX, the automatic chroma control is

disabled and set to a default value.

Micronas 4-14

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

CKILL COLON color killed at damping of

D1 D0

0 0 0 30 dB

0 1 0 18 dB

1 1 0 24 dB

1 1 0 color always off

X X 1 color always on

Table 4-4 Color-killer adjustment

The bandwidth of the chroma filter is adjustable via CHRBW. The bandwidth depends

on whether the decoder is in SECAM operation or not. A change in CHRBW does not

result in a chrominance position shift on the screen.

CKSTAT can be read out and gives information whether the color is switched on or off.

STDET indicates the detected color standard. Additionally PALID signals whether a PAL

signal or a NTSC signal is applied.

4.4 Comb Filtering

Depending on the selected picture size and color standard, a comb filtering is performed

for luminance and chrominance. A comb filter uses the spectral interleaving of the

encoded luminance and chrominance to separate both without cross artifacts. Thus

cross-color and cross-luminance are suppressed effectively. For NTSC sources, a comb

filtering is performed for all picture sizes. Due to reduced bandwidth in horizontal and

vertical direction a strong reduction of cross artifacts can be achieved for PAL signals.

The same applies for the luminance signal of SECAM signals.

4.5 Luminance Processing

The A/D-converted CVBS (or Y) signal is digitally clamped to back porch. Depending on

the transmitted standard and operational area, an offset between black- and blanking

level can be found in the incoming signal (’7.5 IRE’). As for some applications a black

offset is not desired, controlling may be done using LMOFST. The positive or negative

offset is added to the Y signal before scaling.

Micronas 4-15

SDA 9489X

SDA 9589X

Preliminary Data Sheet

Received signal Processed signal

BLANK value

LMOFST

BLANK value

LMOFST

BLACK value

='00' (no additional offset)

BLACK value

='00' (no additional offset)

BLANK value

LMOFST

BLANK value

LMOFST

BLACK value

='10' (reduction of 16 LSB)

BLACK value

='01' (addition of 16 LSB)

Figure 4-6 Black level correction of luminance signal

System Description

M standard signals

B/G/H/I/N standard signals

The color carrier is removed out of a CVBS signal by means of a notch filter. It is set to

the corresponding color carrier (3.58 or 4.4 MHz) only if the standard is detected

permanently. This prevents the luminance sharpness of being changed within the

standard search process. For Y signals the notch is disabled.

For a fine adjustment of delaycompensation between luminance and chrominance,

YCDEL allows a luminance shifting in 16 steps of 50ns.

4.6 Decimation

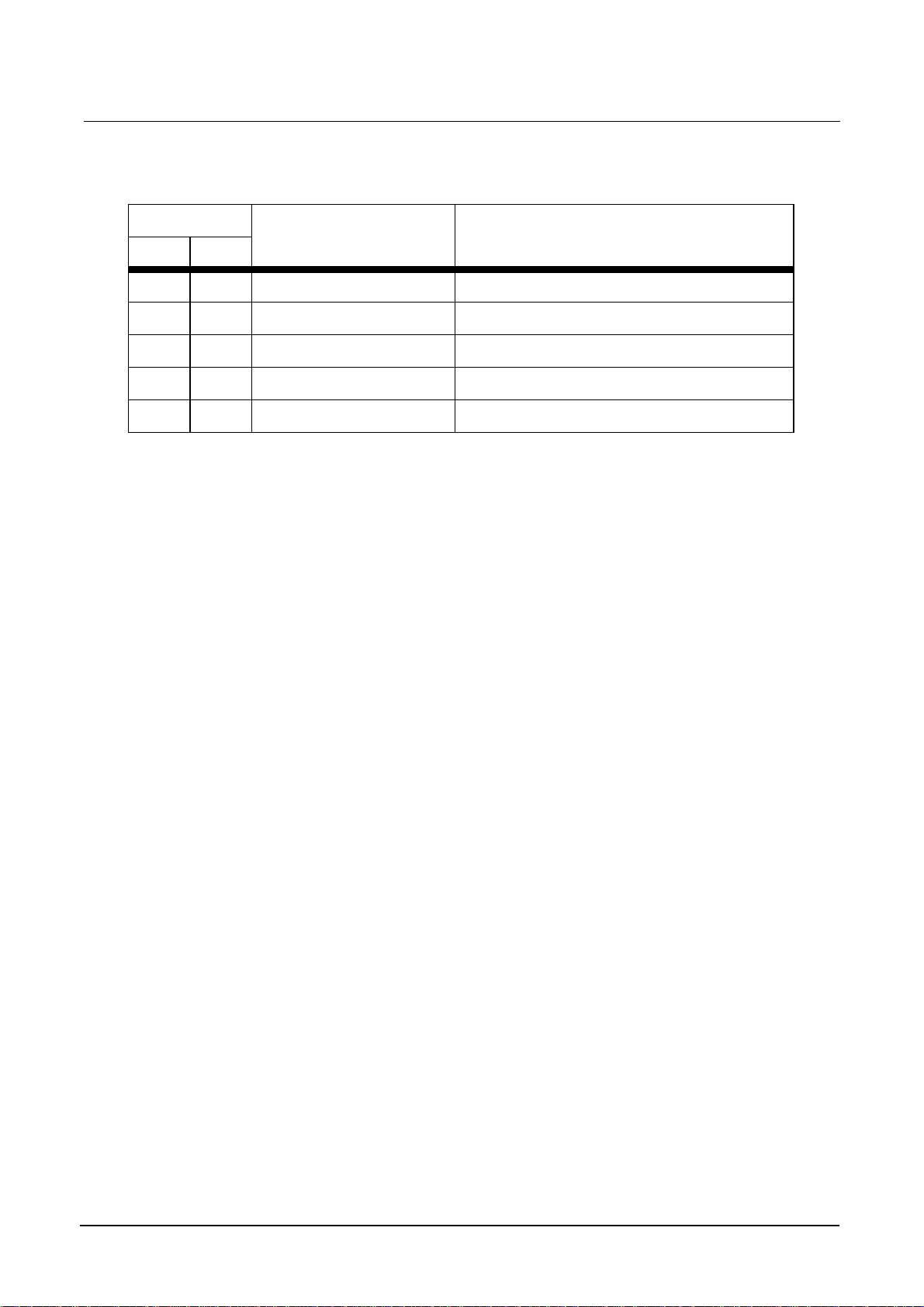

4.6.1 Single PIP Mode

Luminance and chrominance signals are filtered in horizontal and vertical direction. The

coarse horizontal and vertical picture size (1/2, 1/3, 1/4, 1/6) is independently

programmable with SIZEHOR and SIZEVER. A fine adjustment in steps of 4 pixel and 2

lines is possible by HSHRINK and VSHRINK, which allows correct aspect ratio for

multistandard applications (50/60 Hz mixed mode, (S)VGA).

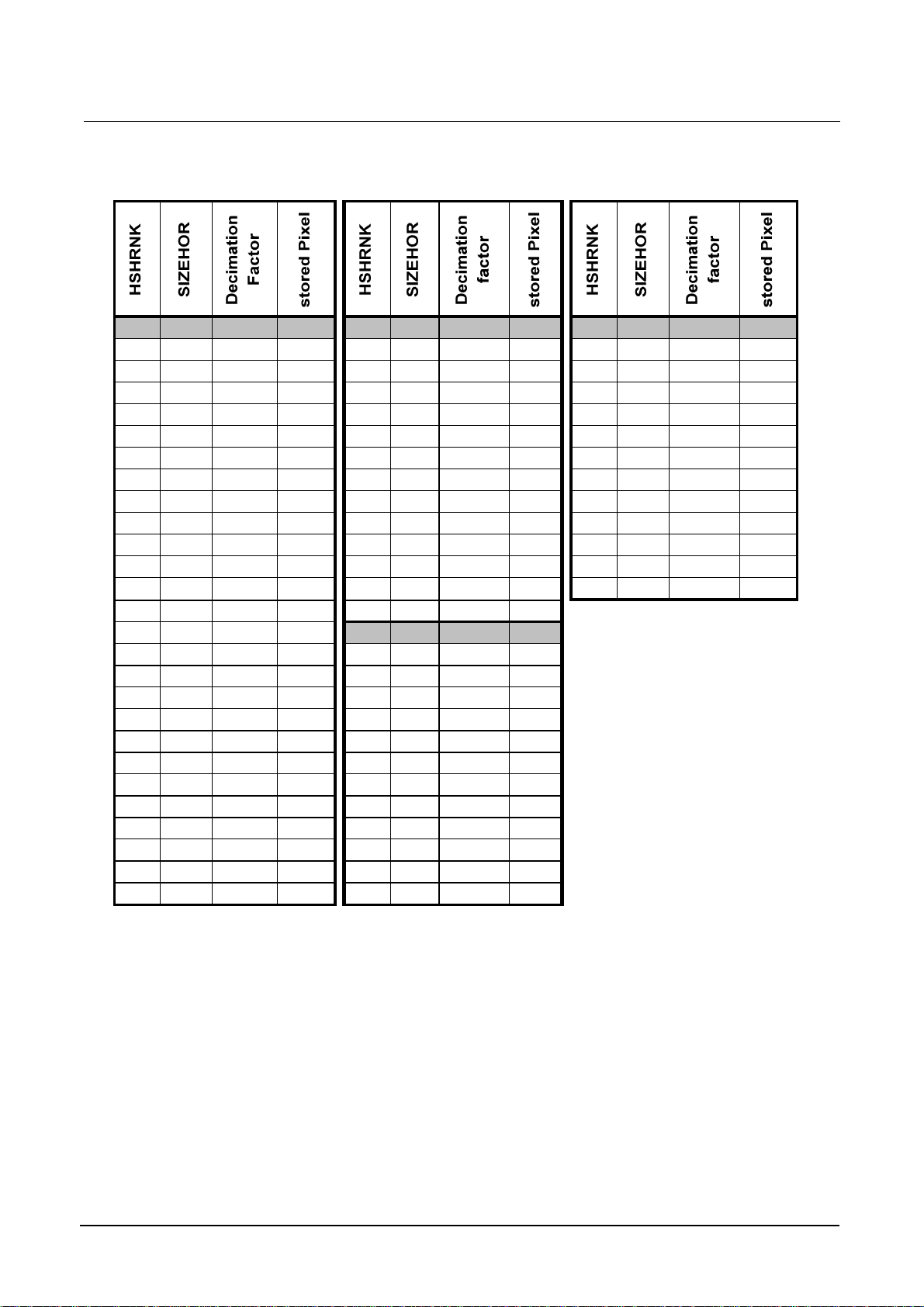

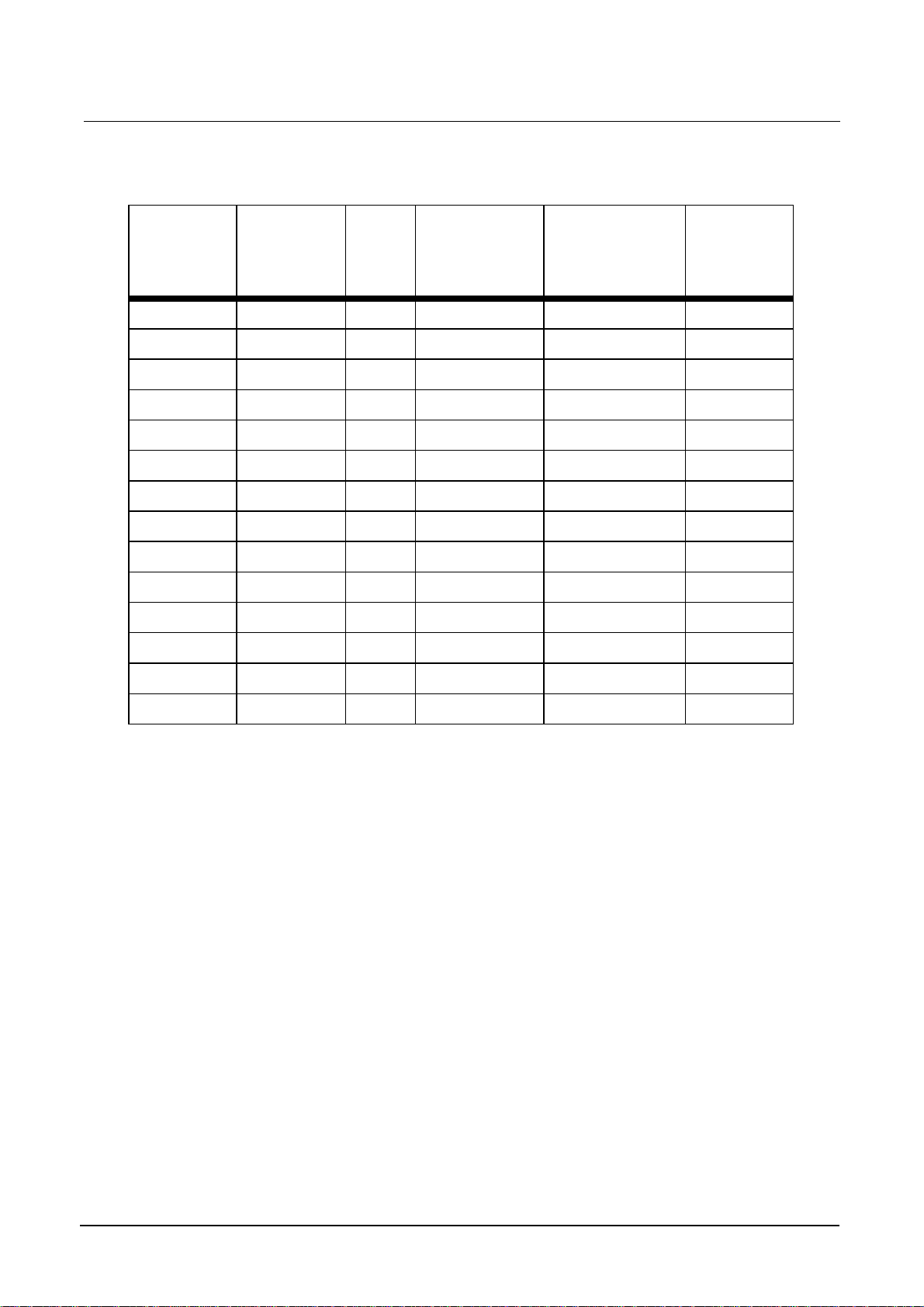

For main decimation factors, the stored number of pixel and lines are listed in the

following tables.

Micronas 4-16

SDA 9489X

SDA 9589X

Preliminary Data Sheet

SIZEHOR horizontal

scaling

D1 D0

PIP Pixel per line

Y (B-Y) (R-Y)

System Description

0 0 2:1 324 81 81

0 1 3:1 216 54 54

1 0 4:1 160 40 40

1 1 6:1 108 27 27

Table 4-5 Number of stored pixel per line dependent on SIZEHOR

SIZEVER vertical scaling PIP lines

D1 D0

625 lines source 525 lines source

0 0 2:1 132 108

01 3:1 88 72

10 4:1 66 54

11 6:1 44 36

Table 4-6 Number of stored lines per field

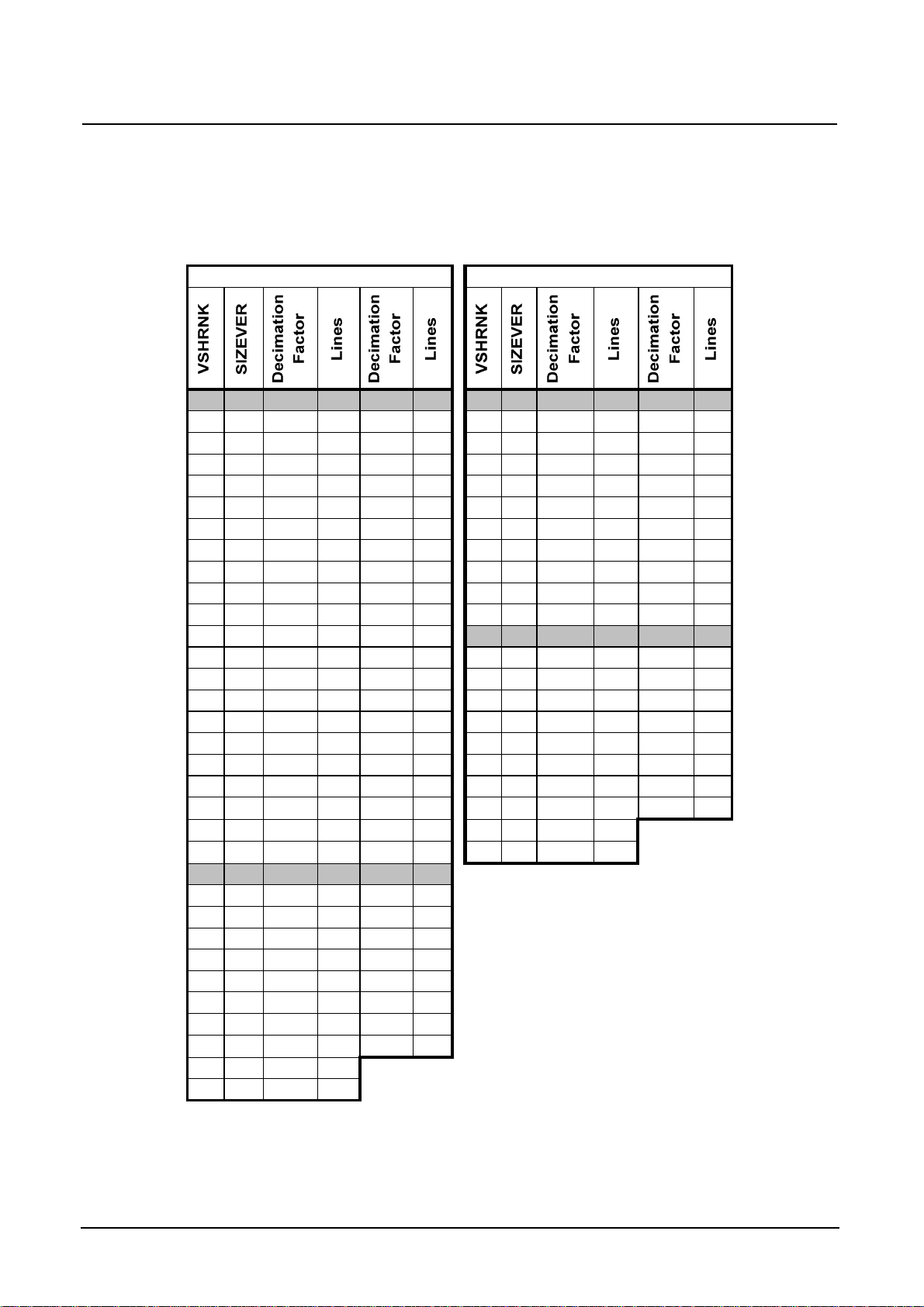

4.6.2 Continuos Zoom

The continuos zoom feature changes the picture size rapidly in an animated manner. It

is available in single-PIP mode for picture sizes smaller or equal 1/4 of the undecimated

picture.

There are three possibilities of using the zoom feature:

• The PIP is zoomed via HSHRINK and VSHRINK manually. This requires an I

2

C

protocol each time the picture size should change. CZMEN should be used to

synchronize the update of HSHRNK/VSHRNK with SIZEHOR/SIZEVER.

• A different way is to make usage of the automatic zooming. The zoom speed can be

controlled by CZMSPD. When switching PIP on or off by using PIPON, the PIP zooms

automatically to the selected picture size or disappears at size of 1/81.

• A zooming between two picture sizes can be performed by changing the HSHRINK,

VSHRINK, SIZEHOR, SIZEVER values when CZMEN is enabled. Then the new

picture size is obtained by zooming and not taken immediately.

Automatic zooming is only possible in frame mode. Being in field mode, the picture size

remains stable until frame mode occurs or until the internal counter reaches the desired

Micronas 4-17

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

picture size. Then the size changes immediately. Equal to the wipe process, the zooming

direction depends on the coarse position (CPOS).

625 lines 525 lines 625 lines 525 lines

0 0 2132 2108 02 4664,0154

1 0 2,03 130 2,03 106 1 2 4,13 64 4,15 52

2 0 2,06 128 2,08 104 2 2 4,25 62 4,31 50

3 0 2,09 126 2,13 102 3 2 4,41 60 4,5 48

4 0 2,13 124 2,16 100 4 2 4,56 58 4,69 46

5 0 2,16 122 2,2 98 5 2 4,72 56 4,9 44

6 0 2,2 120 2,25 96 6 2 4,88 54 5,13 42

7 0 2,23 118 2,3 94 7 2 5,06 52 5,39 40

8 0 2,28 116 2,34 92 8 2 5,28 50 5,7 38

9 0 2,31 114 2,41 90 9 2 5,5 48

10 0 2,36 112 2,45 88 10 2 5,75 46

11 0 2,41 110 2,52 86 0 3 6 44 6 36

12 0 2,44 108 2,58 84 1 3 6,28 42 6,38 34

13 0 2,48 106 2,64 82 2 3 6,61 40 6,75 32

14 0 2,53 104 2,7 80 3 3 6,94 38 7,22 30

15 0 2,59 102 2,77 78 4 3 7,31 36 7,73 28

16 0 2,64 100 2,84 76 5 3 7,78 34 8,3 26

17 0 2,69 98 2,92 74 6 3 8,25 32 9 24

18 0 2,75 96 7 3 8,81 30 9,8 22

19 0 2,81 94 8 3 9,42 28 10,78 20

20 0 2,88 92 9 3 10,17 26

21 02,9490 10311,0224

01 388 372

1 1 3,07 86 3,09 70

2 1 3,14 84 3,19 68

3 1 3,21 82 3,28 66

413,3803,3864

5 1 3,38 78 3,49 62

6 1 3,47 76 3,61 60

7 1 3,56 74 3,73 58

8 1 3,66 72 3,87 56

9 1 3,77 70

10 1 3,89 68

Table 4-7 Number of stored lines per field dependent on VSHRNK

Micronas 4-18

SDA 9489X

SDA 9589X

Preliminary Data Sheet

0 0 2,00 324 0 1 3,00 216 0 3 6,00 108

1 0 2,02 320 1 1 3,04 212 1 3 6,23 104

2 0 2,05 316 2 1 3,11 208 2 3 6,48 100

3 0 2,08 312 3 1 3,17 204 3 3 6,75 96

4 0 2,10 308 4 1 3,23 200 4 3 7,04 92

5 0 2,13 304 5 1 3,29 196 5 3 7,35 88

6 0 2,16 300 6 1 3,37 192 6 3 7,70 84

7 0 2,19 296 7 1 3,44 188 7 3 8,10 80

8 0 2,22 292 8 1 3,51 184 8 3 8,52 76

9 0 2,25 288 9 1 3,60 180 9 3 8,99 72

10 0 2,28 284 10 1 3,67 176 10 3 9,51 68

11 0 2,31 280 11 1 3,76 172 11 3 10,12 64

12 0 2,35 276 12 1 3,84 168 12 3 10,64 60

13 0 2,38 272 13 1 3,94 164

14 0 2,41 268 0 2 4,05 160

15 0 2,45 264 1 2 4,16 156

16 0 2,49 260 2 2 4,27 152

17 0 2,53 256 3 2 4,38 148

18 0 2,57 252 4 2 4,50 144

19 0 2,61 248 5 2 4,63 140

20 0 2,66 244 6 2 4,77 136

21 0 2,70 240 7 2 4,91 132

22 0 2,74 236 8 2 5,06 128

23 0 2,80 232 9 2 5,22 124

24 0 2,84 228 10 2 5,41 120

25 0 2,89 224 11 2 5,59 116

26 0 2,95 220 12 2 5,78 112

System Description

Table 4-8 Number of stored pixel per line dependent on HSHRNK

4.6.3 Horizontal And Vertical Fine Positioning

All picture sizes are pre-centered inside the frame. In addition, if necessary the vertical

and horizontal acquisition area can be shifted by VFP for vertical and HFP for horizontal

direction.

Micronas 4-19

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

4.6.4 Multi Display Mode

SDA 9589X and SDA 9489X offer the feature to display a sub-picture more than once.

The picture size and arrangement depends on the display mode (DISPMOD) and not on

SIZEHOR or SIZEVER. Hence variable scaling is not possible in these modes.

Display

Mode

100SIZEHOR/

DISPMOD Size Picture

D1 D0 625 525

configuration

single PIP mode 324

SIZEVER

HSRHNK/

Pixel Lines

132

-

60

-

24

108

-

20

VSHRNK

2 0 1 3 X1/9 one upon another

216 264 216

(same content)

3 1 0 4 X 1/16 one upon another

156 264 216

(same content)

Table 4-9 Multi-display modes

The display modes are shown in the appendix. The sizes of the partial pictures are listed

in table 4-11 .

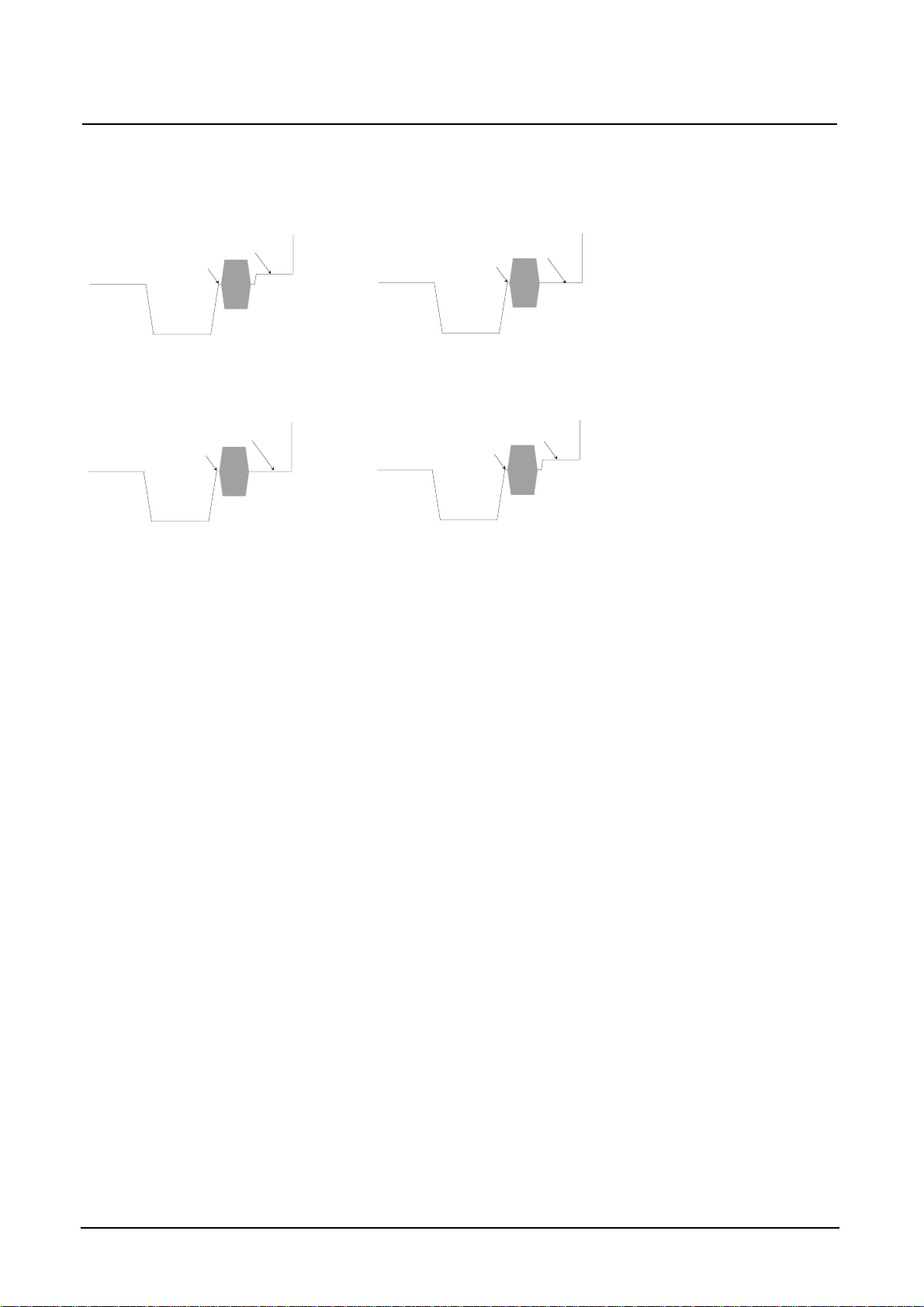

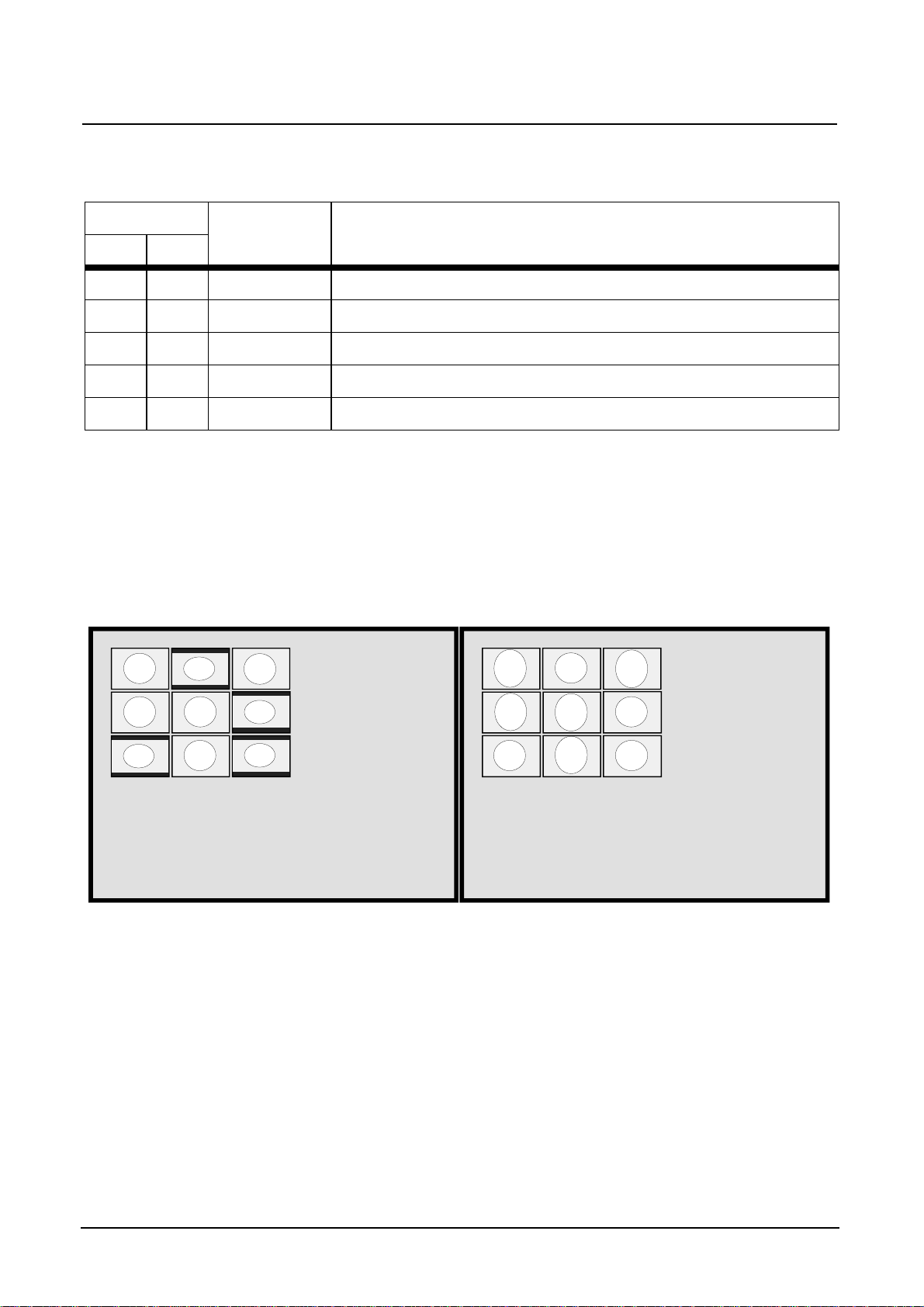

4.6.5 Split Screen

For split screen applications two selectable ’double window’ modes in which one half of

the picture is generated by the ’Sophisticus’/’PIP IV Advanced’ can be used. The split

screen mode can be selected by two possible combinations of DISPMOD.

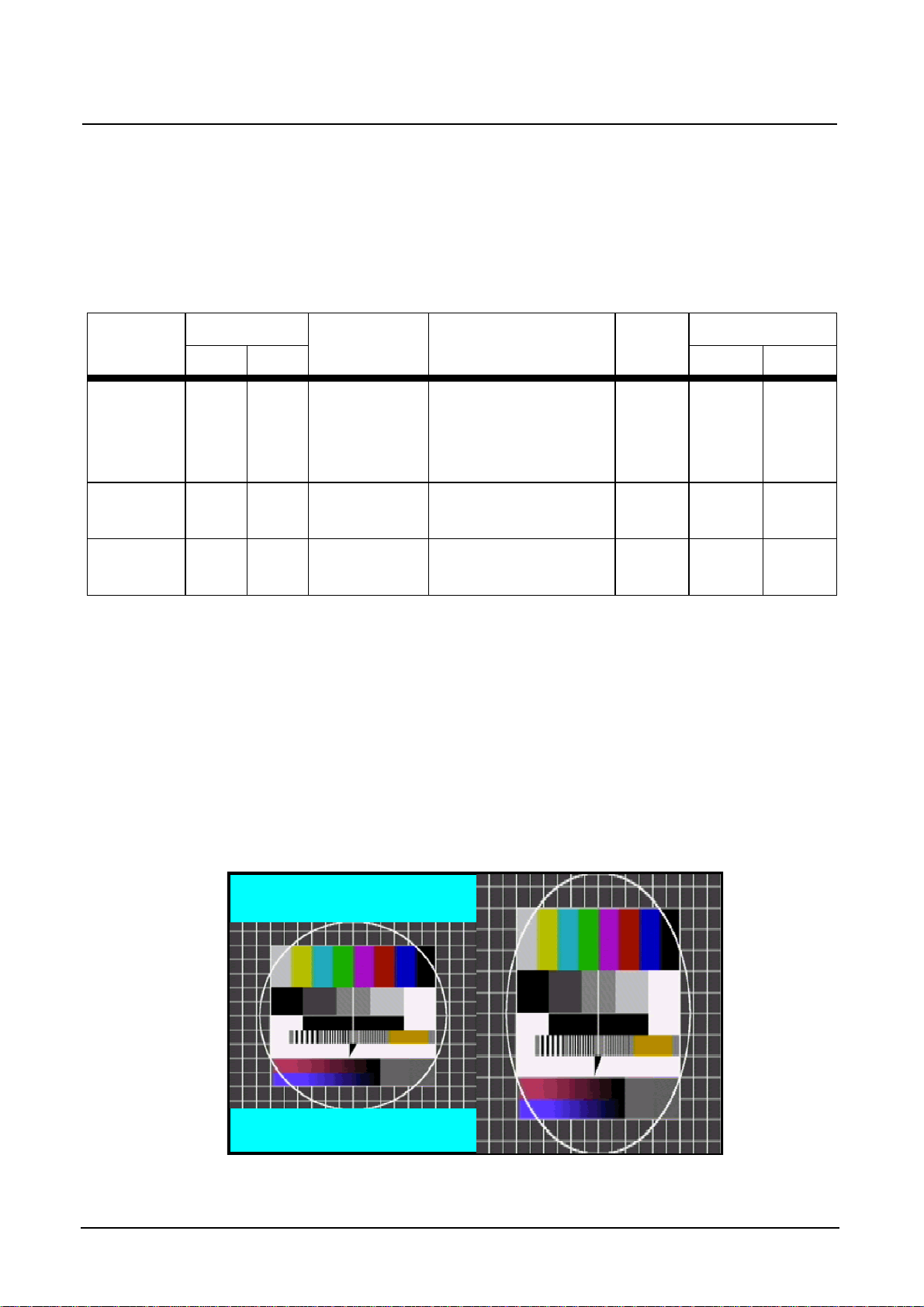

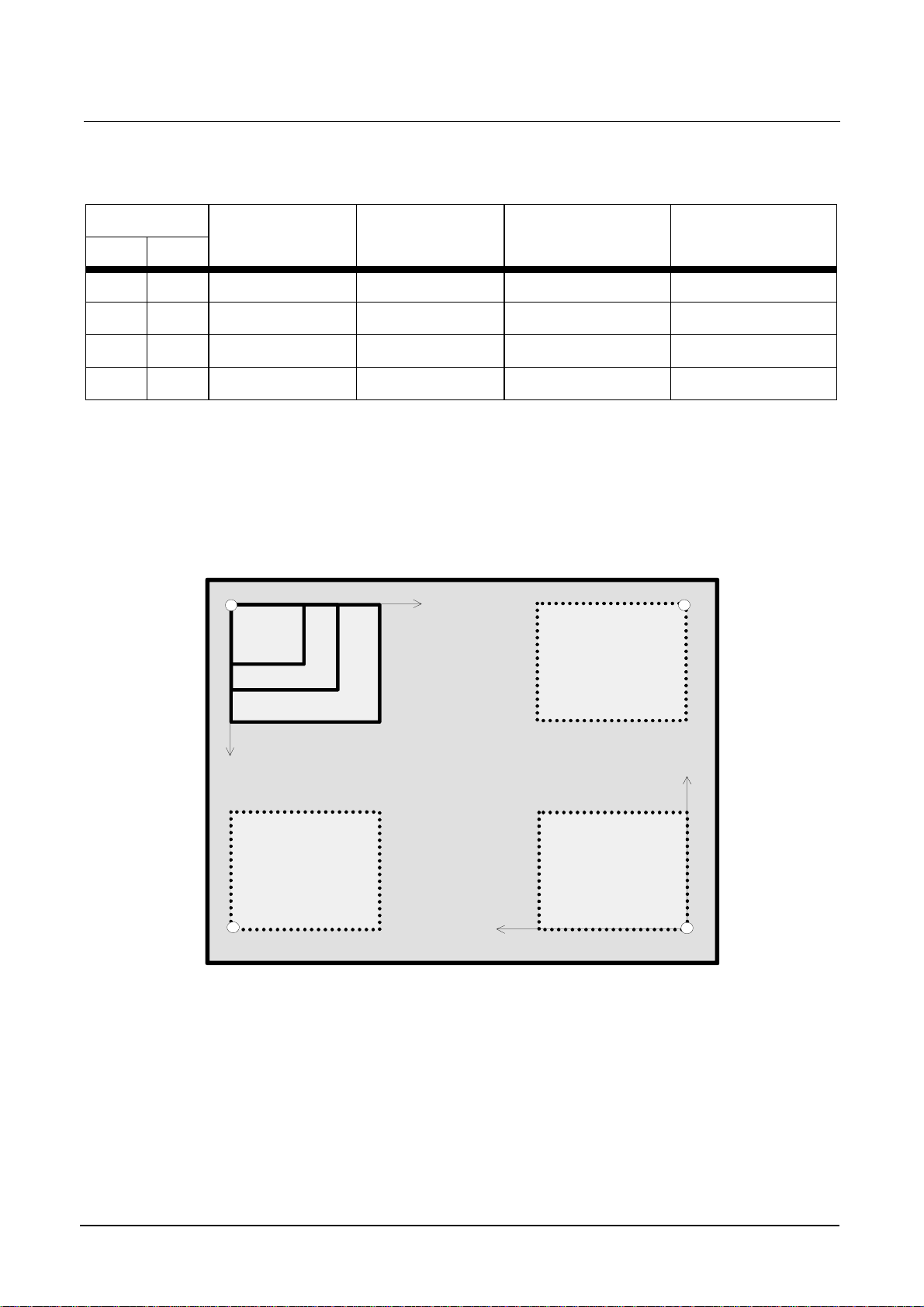

Figure 4-7 Double window mode 1.5 (left picture) and mode 1 (right picture)

Micronas 4-20

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

The D1.5 mode is suited for displaying split screen on 16:9 tubes keeping the aspect

ratio. The DW1 format covers the full height of the screen.

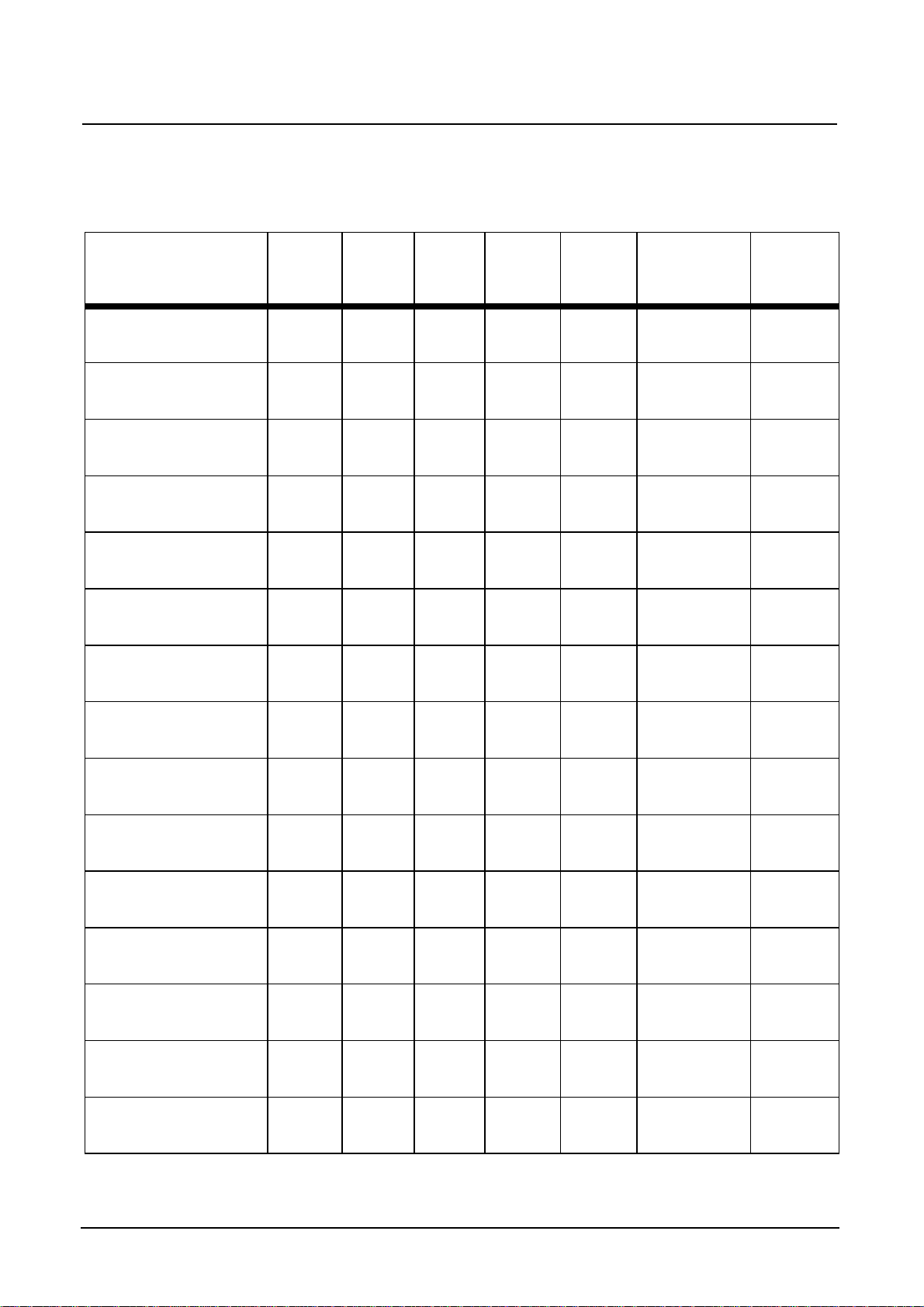

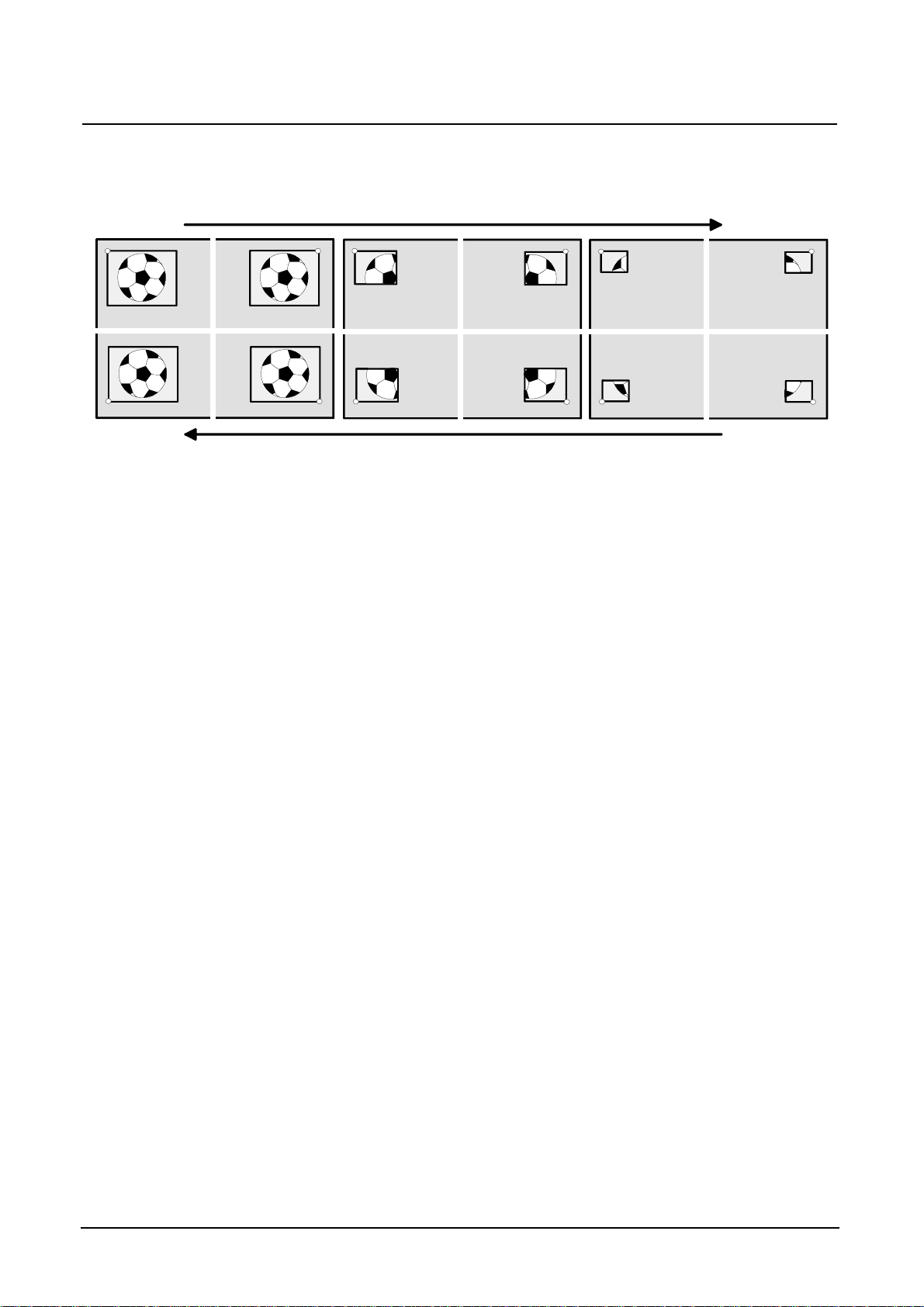

4.6.6 Multi-PiP Mode

There is a great variety of multi-pip modes available. Up to 11 different still pictures and

one moving picture can be shown. This is useful to give an overview over broadcasted

programmes (e.g. tuner-scan) or for supervising purposes. For multi-PiP modes only

three fixed picture sizes are available (1/9, 1/16 or 1/36). The picture size and

arrangement depends on the display mode (DISPMOD) and not on SIZEHOR or

SIZEVER. Variable scaling is thus not possible in these modes. Because of limited

memory capacity, the number of frozen multi-pictures is limited dependent on picture

size to the number shown in the table below:

picture sizes maximum number of pictures

(including one live picture)

1/9 3

1/16 6

1/36 12

Table 4-10 Maximum number of pictures in multi-PIP mode

The partial picture that is written is addressed via WRPOS. With INFRM, a frame for

separation of every PiP can be selected. This is adjustable to single or dual PIP mode

(INFRMOD). The current updated picture can be highlighted with PIPHLT. To avoid

garbage pictures after switching from one mode to another the selected picture can be

blanked with PIPBLK. MPIPBG defines wether the picture will be blanked with black or

with the adjusted background color.

For compatibility reasons to other devices, the DISPMOD register is split into two

segments. If a display mode is chosen that is not implemented, the PIP insertion is

switched off automatically (PIPON = ’0’). The sizes of the partial pictures correspond to

the sizes of the inset pictures of the single PIP modes.

Micronas 4-21

SDA 9489X

SDA 9589X

Preliminary Data Sheet

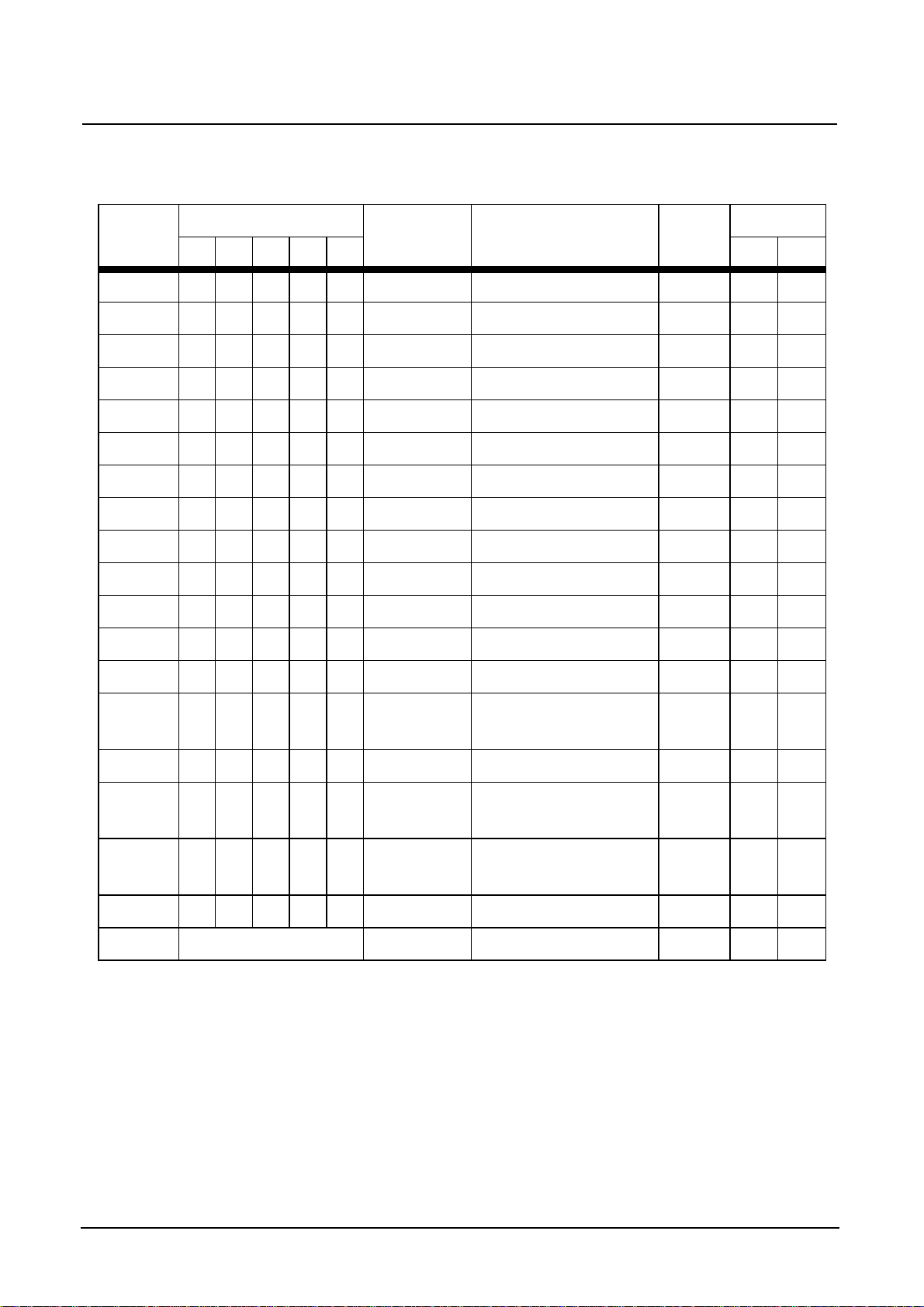

Display

Mode

DISPMOD Size Picture

D6 D5 D4 D3 D2 625 525

configuration

System Description

Pixel Lines

4 0 0 0 0 1 2 X 1/9, one upon another 216 176 144

5 0 0 0 1 0 2 X 1/9, side by side 432 88 72

6 0 0 0 1 1 3 X 1/9, side by side 648 88 72

7 0 0 1 0 0 3 X 1/9 one upon another 216 264 216

8 0 0 1 0 1 4 X 1/16 side by side 624 66 54

9 0 0 1 1 0 6 X 1/16 inverted U shaped 624 132 108

10 0 0 1 1 1 6 X 1/16 U shaped 624 132 108

11 0 1 0 0 0 4 X 1/16 2 rows of 2 pictures 312 132 108

12 0 1 0 0 1 4 X 1/16 one upon another 156 264 216

13 0 1 0 1 0 12 X 1/36 6 rows of 2 pictures 216 264 216

14 0 1 0 1 1 12 X 1/36 2 rows of 6 pictures 648 88 72

15 0 1 1 0 0 9 X 1/36 3 rows of 3 pictures 324 132 108

16 0 1 1 0 1 12 X 1/36 3 rows of 4 pictures 432 132 108

17 0 1 1 1 0 11 X 1/36 angular of 11

648 264 216

pictures

18 0 1 1 1 1 9 X 1/36 angular of 9 pictures 540 220 180

19 1 0 0 0 0 1X1/3 Double Window

324 176 144

(V=1.5)

20 1 0 0 0 1 1X1/2 Double Window

324 264 216

(V=1)

21 10010 OSD only

all other PIP off (PIPON=0)

Table 4-11 Display Modes

4.7 Display Control

The on-chip memory capacity is 768 kbits. Provided that the same standard (50 or 60

Hz)

video sources are applied to inset and parent channel, joint-line free frame mode

display is possible. This means that every incoming field is processed and displayed by

the SDA 9589X/SDA 9489X processors. The result is a high vertical and time resolution.

For this purpose the standard is analyzed internally and frame mode display is blocked

Micronas 4-22

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

automatically, if the described restrictions are not fulfilled. Then only every second

incoming field is shown (field mode). Field mode normally shows joint-lines. This is

caused by an update of the memory during read out. The result is that one part of the

picture contains new picture information and the other part contains one earlier written

field. The switching from or to frame mode is free of artifacts.

Activation of frame-mode display is blocked automatically if at least one of the following

conditions is not fulfilled:

• Inset and parent channel have the same field repetition frequency. This means that

frame mode is possible only for 50Hz inset and parent sources or 60Hz inset and

parent sources.

• Interlace signal is detected for inset and parent channel. For progressive scan or

(S)VGA display therefore only field mode is possible. For some VCRs in trick mode,

often no interlace is detected also.

• The number of lines is within a predefined range for inset (FMACTI) or parent

(FMACTP) channel (assuming standard signals according to ITU)

FMACTP parent

standard

number of

lines per field

FMACTI inset

standard

number of

lines per field

0 50 Hz 310...315 0 50 Hz 310...315

1 50 Hz 290...325 1 50 Hz 290...325

0 60 Hz 260...265 0 60 Hz 260...265

1 60 Hz 250...275 1 60 Hz 250...275

Table 4-12 Required number of lines for frame mode display

The system may be forced to field mode by means of FIESEL. Either first or second field

is selectable. ’One of both’ takes every second field independent of the field number.

This is meant for sources generating only one field (e.g. video-games).

For progressive scan conversion systems and HDTV / (S)VGA displays a line doubling

mode is available (PROGEN). Every line of the inset picture is read twice.

Memory writing is stopped by FREEZE bit. The field stored in the memory is then

continuously read. As the picture decimation takes place before storing, the picture size

of a frozen picture can not be changed.

Synchronization of memory reading with the parent channel is achieved by processing

the parent horizontal and vertical synchronization signals connected to the pin HSP for

horizontal synchronization and pin VSP for vertical synchronization. HSPINV or VSPINV

respectively allow an inversion of the expected signal polarity.

Micronas 4-23

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

HSP

VSP

VSPDEL VSPDEL

VSPD

(internal)

values in brackets () apply for 100Hz systems

field 0 window field 1 window

tH/2 = 32 (16)

←

s

tH = 64 (32) ←s

=151 (75) ←s

max

Figure 4-8 Field detection and phase adjustment of vertical pulse (VSP)

Depending on the phase between inset and parent signals a correction of the display

raster for the read out data is performed. As the external VSP and HSP signals may

come from different devices with different delay paths, the phase between V-sync and

H-sync is adjustable (VSPDEL). An incorrect setting of VSPDEL may result in wrong or

unreliable field detection of parent channel.

Normally a noise reduction of the incoming parent vertical pulse is performed. With this

function missing vertical pulses are compensated. The circuit works for 50/60 Hz

applications as well as progressive and 100/120Hz application. (S)VGA signals are

supposed to be very stable and therefore not supported by the noise suppression. By

means of VSPNSRQ, vertical noise suppression is switched off.

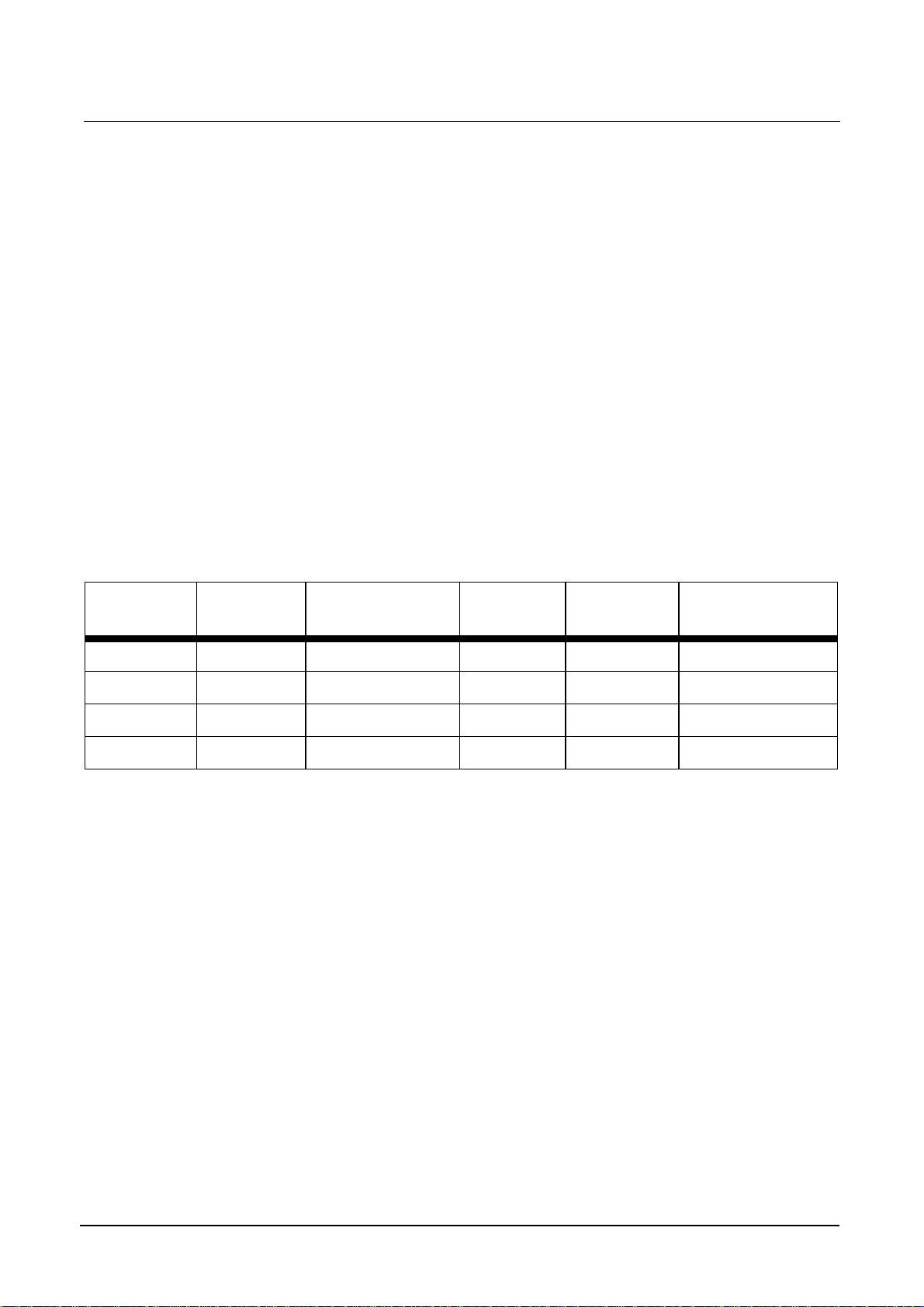

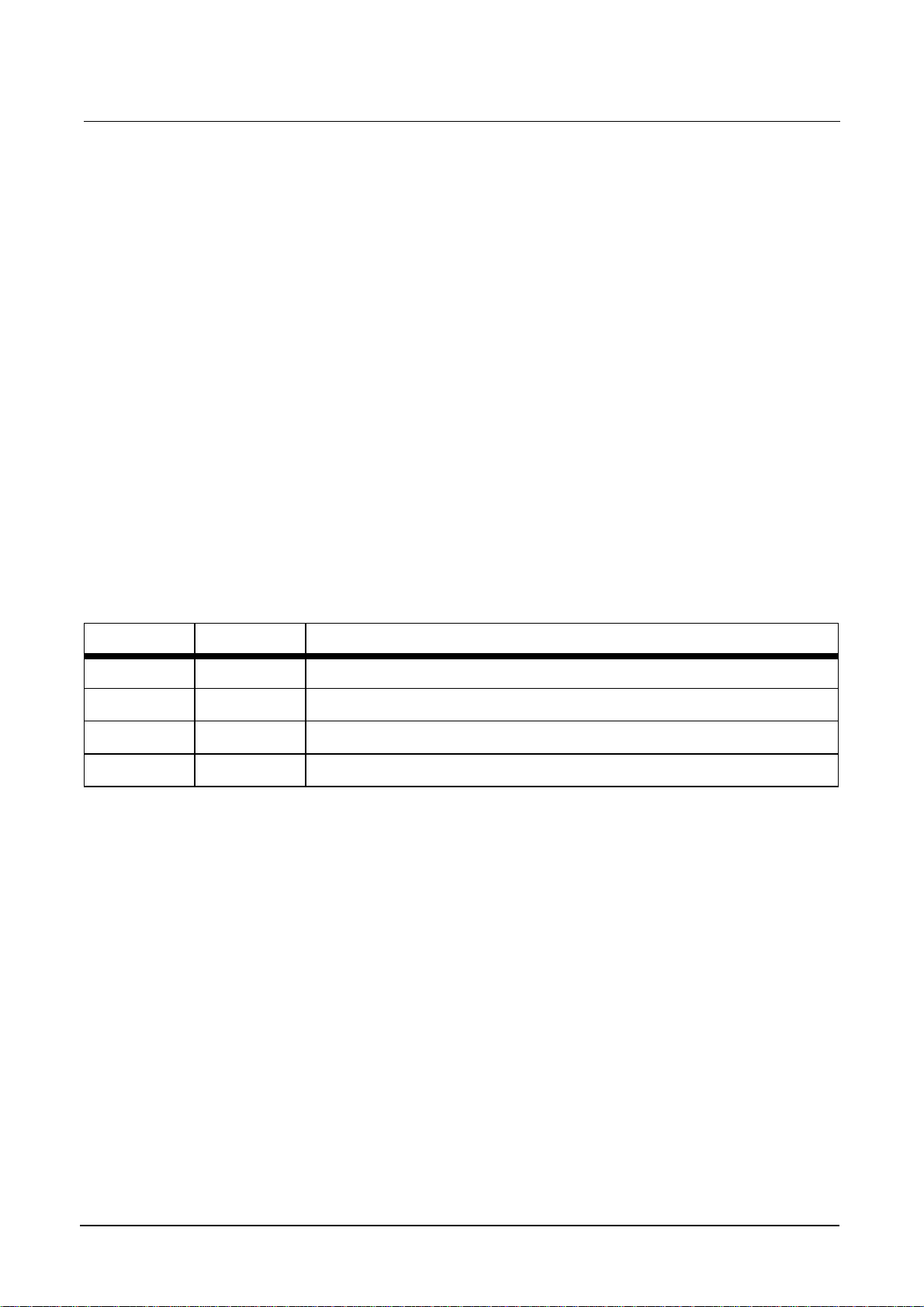

A great variety of combinations of inset and parent frequencies are possible. The

following table shows some constellations.

Micronas 4-24

SDA 9489X

SDA 9589X

Preliminary Data Sheet

Inset

Frequency

Parent

1)

Frequency

(HSP/VSP)

1)

frame

mode

correct aspect

ratio

(single pip)

correct aspect

ratio

(multi display)

System Description

vertical

noise

suppression

selectable

50 50i

50 60i

60 50i

60 60i

50 50p

50 60p

60 50p

60 60p

50 100i

2)

50 120i

60 100i

60 120i

50 (S)VGA

60 (S)VGA

1)

standard signals supposed

2)

AABB only and picture size smaller than 1/9

3)

valid for some parent frequencies. Please refer to Chapter 4.7.2

2)

3)

3)

Table 4-13 Available Features with varying inset and parent standards

4.7.1 100 Hz Frame Mode

If the picture size is smaller or equal than 1/9 PIP a true frame mode display for 100Hz

parent standard with a double field repetition rate is possible (display raster ∼∼ϒϒ only).

The picture size is indicated by the horizontal and vertical decimation factors that must

be equal or below 1/3 of undecimated picture size in both directions. This guarantees

enough memory for a joint-line free picture with full vertical resolution. For bigger pictures

only field mode is supported. The 100 Hz frame mode is activated if READD=’1’ for the

above mentioned picture sizes. For an acceptable quality without line flicker or motion

artifacts only the mode ∼∼ϒϒ is supported for HSP and VSP. If the sequence ∼ϒ∼ϒ is

detected, the field mode will be activated again. Continous switching between these

modes is possible, resulting in continous switching between field- and frame mode.

Micronas 4-25

SDA 9489X

SDA 9589X

Preliminary Data Sheet

4.7.2 Mixed Standard Applications And (S)VGA Support

remark

(N

apel

X N

aline

@ fV)

720X576@50Hz

(TV)

702X488@60Hz

(TV)

720X576@100Hz

(TV 100 Hz)

702X488@120Hz

(TV 120 Hz)

720X576@50Hz

(TV progressive)

fH

(kHz)

(

TH

←s)

T

Hact

(←s)

15.6 64.0 52.0 625/

15.7 63.6 52.7 525/

31.2 32.0 26.0 625/

31.2 31.8 26.4 525/

31.2 32.0 26.0 625/

lines/

active

576

488

576

488

576

f

dot

(MHz)

13.5 interlace

13.5 interlace

27 interlace

27 interlace

27 prog-

System Description

scan correct

aspect

ratio

ressive

702X488@60Hz

(TV progressive)

640X480@60Hz

(VGA)

640X480@72Hz

(VGA)

640X480@75Hz

(VGA)

800X600@56Hz

(SVGA)

800X600@60Hz

(SVGA)

800X600@72Hz

(SVGA)

800X600@75Hz

(SVGA)

31.2 31.8 26.4 525/

488

31.5 31.8 25.4 525/

480

37.9 26.4 20.3 520/

480

37.5 26.7 20.3 500/

480

35.2 28.4 22.2 625/

600

37.9 26.4 20.0 625/

600

48.1 20.8 16.0 666/

600

46.9 21.3 16.2 625/

600

27 prog-

ressive

25.2 progressive

31.5 progressive

31.5 progressive

36.0 progressive

40.0 progressive

50.0 progressive

49.5 progressive

800X600@85Hz

(SVGA)

1024X768@43Hz

(SVGA)

53.7 18.6 14.2 631/

600

35.5 28.2 22.8 817/

768

56.3 progressive

44.9 interlace

Table 4-14 Examples of supported parent signals

Micronas 4-26

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

SDA 9589X and SDA 9489X allow multiple scan rates for the use in desktop video

applications, VGA compatible or 100Hz TV sets. All features are provided in ’normal’

operating modes at auto detected 50Hz and 60 Hz parent and inset standards. 2f

modes (100/120Hz and progressive) are supported by line frequency- and pixel clock

doubling and are not detected automatically. Even on a 16:9 picture tube correct aspect

ratio can be displayed by selecting the suitable parent clock. The video synthesizer

generates also a special pixel clock for VGA display (see chapter 5.5.9 for details). As

(S)VGA consists of a variety of scan rates the correct aspect ratio is not adjustable for

all modes with the parent clock (HZOOM) because of the limited count of frequencies.

For single PIP only, correct aspect ratio is maintained by the vertical and horizontal

scaler (HSHRINK and VSHRINK).

It is possible to display (S)VGA sources for parent display, as long as the horizontal

frequency is lower than 40 kHz and the signal does not contain more than 1023 lines.

For progressive scan mode, PROGEN must be set. Additionally field-mode should be

forced to prevent unallowed frame-mode displaying (FIESEL). As the (S)VGA normally

does not fit to the display raster generated in the vertical noise suppression, VSPNSRQ

should be disabled. (S)VGA signals for inset channel are not supported.

H

PROGEN READD Expected input signal

0 0 50 or 60 Hz signal interlace

0 1 100 or 120 Hz signals interlace

1 0 (reserved)

1 1 50 or 60 Hz or (S)VGA signal progressive

Table 4-15 Selection of display field repetition

4.7.3 Display standard

For a single-PiP, the number of displayed lines depends on the selected picture size and

on the signal standard. For multi picture display, the number of displayed lines depends

on the selected picture size and on the signal standard of the parent signal. Additionally,

a standard can be forced by DISPSTD.

Micronas 4-27

SDA 9489X

SDA 9589X

Preliminary Data Sheet

System Description

DISPSTD DISPMOD Display Standard

D1 D0

0 0 0 PIP depends on detected inset standard (single pip)

0 0 >0 PIP depends on detected parent standard (multi display)

0 1 x PIP display is always in 625 lines mode

1 0 x PIP display is always in 525 lines mode

1 1 x freeze last detected display standard and size

Table 4-16 Display standard selection

If a 625 lines picture is shown with a 525 lines parent signal, some lines are missing on

top and bottom of picture. If a 525 lines picture is shown with a 625 lines display

standard, missing lines at top and bottom are filled with background color or black

depending on MPIPBG.

625 lines / 50 Hz

525 lines / 60 Hz

Figure 4-9 50 and 60 Hz Multi PiP display on 50 Hz and 60 Hz display

4.7.4 Picture Positioning

The display position of the inset picture is programmable to the 4 corners of the parent

picture (CPOS). From there PIP can be moved to the middle of the TV Picture with

POSHOR and POSVER. The corner positions can be centered coarsely on the screen

with POSOFH and POSOFV. Depending on coarse position, one PIP corner remains

stable when changing the picture size.

Micronas 4-28

SDA 9489X

SDA 9589X

Preliminary Data Sheet

CPOS Coarse

D1 D0

Position

Reference

corner of PiP

increasing

POSVER

System Description

increasing

POSHOR

0 0 upper left upper left down right

0 1 upper right upper right down left

1 0 lower left lower left up right

1 1 lower right lower right up left

Table 4-17 Coarse Positioning

There are 256 horizontal locations (4 pixel increments) and 256 vertical locations (2 line

increments). The pixel width on the screen depends on the selected HZOOM factor.

Even POP-positions (Picture Outside Picture) in 16:9 applications are possible.

CPOS='00'

POSVER

CPOS='10'

Figure 4-10 Coarse Positioning

4.7.5 Wipe In / Wipe Out

POSHOR

CPOS='01'

POSVER

CPOS='11'

POSHOR

With the wipe in / wipe out function it is possible to let appear or disappear the complete

inset picture starting or ending at the corner of the inset picture position defined by

CPOS. Thereby the size of the visible picture-part is continuously increased and

decreased respectively. During this procedure the frame is shown with its chosen widths.

3 different wipe in / out time periods or ’no wipe’ are programmable via WIPESPD. The

wipe algorithm always works in horizontal and vertical direction.

Micronas 4-29

SDA 9489X

SDA 9589X

Preliminary Data Sheet

CPOS='00'

CPOS='10'

CPOS='01'

CPOS='11'

wipe out

CPOS='00'

CPOS='10'

wipe in

CPOS='01'

CPOS='11'

System Description

CPOS='00'

CPOS='10'

CPOS='01'

CPOS='11'

Figure 4-11 Wipe display

If WIPESPD is set accordingly, PIPON controls the wipe operation. When PIPON

changes the wipe operation starts. During this period, the readable PIPSTAT indicates

the ongoing wipe-process. A transition of PIPON from ’0’ to ’1’ triggers the wipe-in. The

wipe-in process stops when the picture reaches its programmed size. When PIPON

changes from ’1’ to ’0’ the wipe-out starts. The wipe-out is finished when the PiP picture

vanishes. Even for multi-picture display wipe operation is possible. A change of PIPON

or WIPESPD during wipe operation has only an effect after the wipe operation has been

finished.

4.8 Output Signal Processing

4.8.1 Luminance Peaking

To improve picture sharpness, a peaking filter which amplifies higher frequencies of the

input signal is implemented. The amount of peaking can be varied in seven steps by

YPEAK. The setting ’000’ switches off the peaking. The value ’001’ is recommended as

This value provides a good compromise between sharpness impression and annoying

aliasing. The characteristic for all possible settings is shown in fig. (4-12). The

emphasized frequency depends on the adjusted decimation. The gain maximum is

always located before the band-limit ensuring optimal picture impression.

Micronas 4-30

Loading...

Loading...