Micronas Intermetall NVM3060 Datasheet

NVM 3060

4096-Bit EEPROM

Edition Feb. 14, 1990

6251-309-2/E

ITT Semiconductors

NVM 3060

Contents

Page Section Title

3 1. Introduction

4 2. Specifications

4 2.1. Outline Dimensions

4 2.2. Pin Connections

4 2.3. Pin Descriptions

5 2.4. Pin Circuits

5 2.5. Electrical Characteristics

5 2.5.1. Absolute Maximum Ratings

5 2.5.2. Recommended Operating Conditions

7 2.5.3. Characteristics

8 3. Functional Description

8 3.1. Memory Operation

8 3.2. Testing

8 3.3. Protected Matrix

8 3.4. Shipment

9 4. Test Functions

9 4.1. Block Programming

9 4.2. Read Reference Shifting

9 4.3. Charge Pump Disable

10 5. Description of the IM Bus

2

NVM 3060

4096-Bit EEPROM

1. Introduction

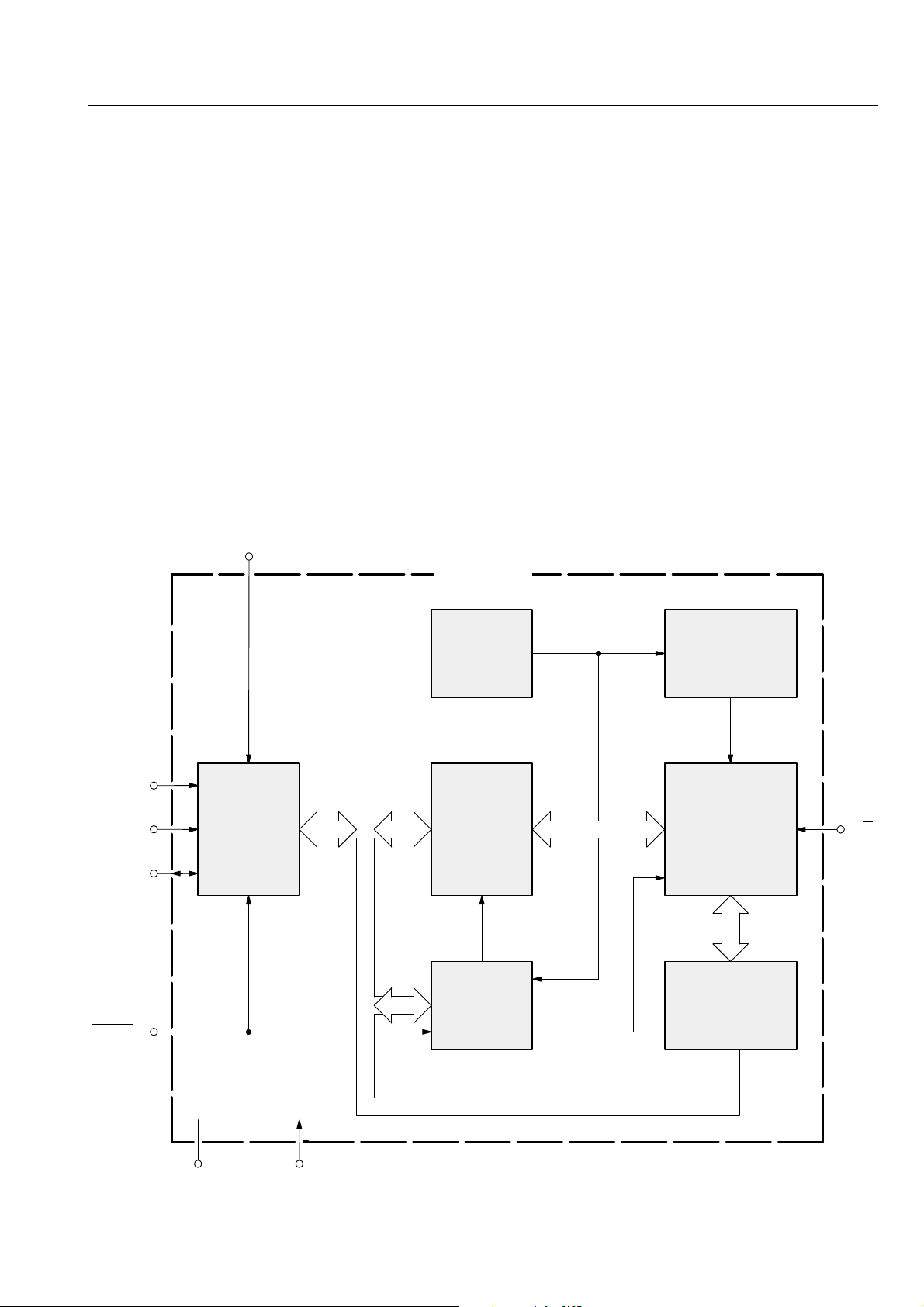

Electrically erasable programmable read-only memory

(EEPROM) in N-channel floating-gate technology with

a capacity of 512 words, 8 bits each.

The NVM 3060 is intended for use as a reprogrammable

non-volatile memory in conjunction with the CCU

2030/2050/2070/3000 series Central Control Units or

the SAA 12xx and TVPO 2066 Remote Control and Tuning ICs. It serves for storing the tuning information as

Option

3

NVM 3060

well as several analog settings, further alignment information given in the factory when producing the TV set.

The stored information remains stored even with the

supply voltages switched off. Reading and programming

operations are executed via the IM bus (see section 5.).

Input and output signals are TTL level. An address option input provides the possibility to operate two memories in parallel, to obtain a total storage capacity of 8192

bits.

The device contains an on-chip charge pump for high

programming voltage generation and an on-chip clock

oscillator.

Clock

Ident

Data

Reset

Clock

5

Charge

Pump

Data

6

IM Bus

Interface

7

Buffer

and

Input

Register

Sequence

Output

4

Control

EEPROM

Matrix

512 x 8

Decoder and

Register for the

Memory Address

2

S

+5 V

18

GND V

SUP

Fig. 1–1: Block diagram of the NVM 3060 EEPROM

3

NVM 3060

2. Specifications

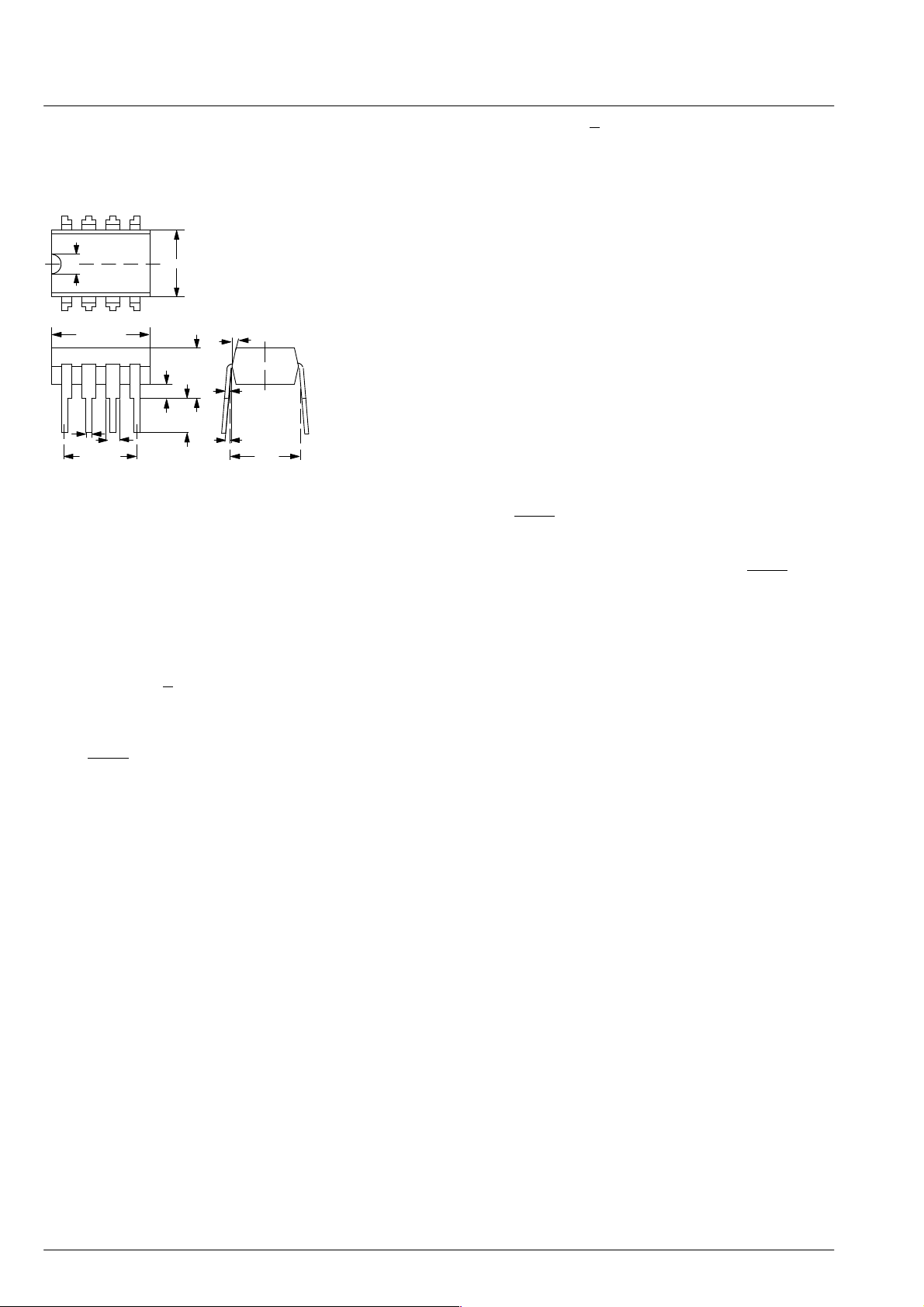

2.1. Outline Dimensions

58

...

2.5

14

max. 9.5

. .

0.5

1.1

3 x 2.54

min. 0.5

6.4

min.

2.8

max.

5.08

15

.

0.38

.

.

0 15

...

.

7.62

.

.

.

Fig. 2–1: NVM 3060 in 8-pin Dil Plastic Package

20 A 8 according to DIN 41870

Weight approx. 0.5 g Dimensions in mm

2.2. Pin Connections

1 Ground, 0

2 Safe Input S

Pin 2 – Safe Input S

Fig. 2–2 shows the internal configuration of this input.

Normally, with pin 2 at ground potential (low), one portion of the programming matrix is protected so that this

part of the memory cannot be reprogrammed inadvertently. Only when pin 2 receives high potential continuously , the protected portion of the memory matrix can be

programmed. Pin 2 is internally tied to ground via a transistor equivalent to a 40 kΩ resistor.

Pin 3 – Option Input Fig. 2–2 shows the internal configuration of this input. With pin 3 at ground potential (low)

or floating, the NVM 3060 reacts upon the IM bus addresses 128,129 and 131. With pin 3 continuously at

potential (high), the NVM 3060 reacts upon this IM

V

SUP

bus addresses 132,133 and 135 (see Fig.2–6). In this

way , parallel operation of two NVM 3060 is permitted, to

obtain 8192 bits of non-volatile storage directly accessible via the IM bus. Pin 3 is internally tied to ground via

a transistor equivalent to a 40 kΩ resistor.

Pin 4 – Reset

Input

This input has a configuration as shown in Fig. 2–3. Via

this input, the NVM 3060, together with the other circuits

belonging to the system, receives the Reset

which is derived from V

via an external RC circuit. A

SUP

signal

low level is required during power-up and power-down

procedures. Low level at pin 4 (max. 1.3 V) cancels a

programming procedure and an IM bus operation in progress. The memory address register is not erased. During operation, pin 4 requires high level (min. 2.4 V).

3 Option Input

4 Reset

Input

5 IM Bus Clock Input

6 IM Bus Ident Input

7 IM Bus Data Input/Output

8 Supply Voltage V

SUP

2.3. Pin Descriptions

Pin 1 – Ground, 0

This pin must be connected to the negative of the supplies.

Pins 5 to 7 – IM Bus Connections

These pins serve to connect the NVM 3060 EEPROM

to the IM bus (see section 5.), via which it communicates

with the CCU 2030/2050/2070/3000 Central Control

Units or the SAA 12xx and TVPO 2066 Remote Control

and Tuning ICs. Pins 5 (IM Bus Clock Input) and 6 (IM

Bus Ident Input) are inputs as shown in Fig. 2–3 and pin

7 (IM Bus Data) is an input/output as shown in Fig. 2–4.

The signal diagram for the IM bus is illustrated in Figs.

2–6 and Fig. 5–1. The required addresses which the

NVM 3060 EEPROM receives from the microcomputer,

are also shown in Fig. 2–6.

Pin 8 – Supply Voltage V

SUP

The supply voltage required is +5V (±5%), and the current consumption in active operation is approx. 30 mA.

Inserting or removing the NVM 3060 from a live socket

may alter programmed data!

4

Loading...

Loading...