Micronas Intermetall MSP3465G, MSP3425G, MSP3455G, MSP3445G, MSP3405G Datasheet

...

MSP 34x5G

Multistandard

Sound Processor Family

Edition March 5, 2001

6251-480-3PD

PRELIMINARY DATA SHEET

MICRONAS

MICRONAS

MSP 34x5G PRELIMINARY DATA SHEET

Contents

Page Section Title

5 1. Introduction

6 1.1. Features of the MSP 34x5G Family and Differences to MSPD

6 1.2. MSP 34x5G Version List

7 1.3. MSP 34x5G Versions and their Application Fields

8 2. Functional Description

9 2.1. Architecture of the MSP 34x5G Family

9 2.2. Sound IF Processing

9 2.2.1. Analog Sound IF Input

9 2.2.2. Demodulator: Standards and Features

10 2.2.3. Preprocessing of Demodulator Signals

10 2.2.4. Automatic Sound Select

10 2.2.5. Manual Mode

12 2.3. Preprocessing for SCART and I

12 2.4. Source Selection and Output Channel Matrix

12 2.5. Audio Baseband Processing

12 2.5.1. Automatic Volume Correction (AVC)

12 2.5.2. Loudspeaker Outputs

12 2.5.3. Quasi-Peak Detector

13 2.6. SCART Signal Routing

13 2.6.1. SCART DSP In and SCART Out Select

13 2.6.2. Stand-by Mode

2

13 2.7. I

S Bus Interface

14 2.8. ADR Bus Interface

14 2.9. Digital Control I/O Pins and Status Change Indication

14 2.10. Clock PLL Oscillator and Crystal Specifications

2

S Input Signals

15 3. Control Interface

2

15 3.1. I

C Bus Interface

15 3.1.1. Internal Hardware Error Handling

16 3.1.2. Description of CONTROL Register

16 3.1.3. Protocol Description

2

17 3.1.4. Proposals for General MSP 34x5G I

C Telegrams

17 3.1.4.1. Symbols

17 3.1.4.2. Write Telegrams

17 3.1.4.3. Read Telegrams

17 3.1.4.4. Examples

2

17 3.2. Start-Up Sequence: Power-Up and I

C-Controlling

17 3.3. MSP 34x5G Programming Interface

17 3.3.1. User Registers Overview

20 3.3.2. Description of User Registers

21 3.3.2.1. STANDARD SELECT Register

21 3.3.2.2. Refresh of STANDARD SELECT Register

21 3.3.2.3. STANDARD RESULT Register

2

23 3.3.2.4. Write Registers on I

25 3.3.2.5. Read Registers on I2C Subaddress 11

26 3.3.2.6. Write Registers on I2C Subaddress 12

C Subaddress 10

hex

hex

hex

2 Micronas

PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

MSP 34x5G

36 3.3.2.7. Read Registers on I2C Subaddress 13

37 3.4. Programming Tips

37 3.5. Examples of Minimum Initialization Codes

37 3.5.1. B/G-FM (A2 or NICAM)

37 3.5.2. BTSC-Stereo

37 3.5.3. BTSC-SAP with SAP at Loudspeaker Channel

38 3.5.4. FM-Stereo Radio

38 3.5.5. Automatic Standard Detection

38 3.5.6. Software Flow for Interrupt driven STATUS Check

40 4. Specifications

40 4.1. Outline Dimensions

42 4.2. Pin Connections and Short Descriptions

45 4.3. Pin Description

47 4.4. Pin Configurations

51 4.5. Pin Circuits

53 4.6. Electrical Characteristics

53 4.6.1. Absolute Maximum Ratings

54 4.6.2. Recommended Operating Conditions

54 4.6.2.1. General Recommended Operating Conditions

54 4.6.2.2. Analog Input and Output Recommendations

55 4.6.2.3. Recommendations for Analog Sound IF Input Signal

56 4.6.2.4. Crystal Recommendations

58 4.6.3. Characteristics

58 4.6.3.1. General Characteristics

59 4.6.3.2. Digital Inputs, Digital Outputs

60 4.6.3.3. Reset Input and Power-Up

61 4.6.3.4. I

62 4.6.3.5. I

64 4.6.3.6. Analog Baseband Inputs and Outputs, AGNDC

65 4.6.3.7. Sound IF Input

65 4.6.3.8. Power Supply Rejection

66 4.6.3.9. Analog Performance

69 4.6.3.10. Sound Standard Dependent Characteristics

2

C Bus Characteristics

2

S-Bus Characteristics

hex

73 5. Appendix A: Overview of TV Sound Standards

73 5.1. NICAM 728

74 5.2. A2 Systems

75 5.3. BTSC-Sound System

75 5.4. Japanese FM Stereo System (EIA-J)

76 5.5. FM Satellite Sound

76 5.6. FM-Stereo Radio

77 6. Appendix B: Manual/Compatibility Mode

77 6.1. Demodulator Write and Read Registers for Manual/Compatibility Mode

78 6.2. DSP Write and Read Registers for Manual/Compatibility Mode

79 6.3. Manual/Compatibility Mode: Description of Demodulator Write Registers

79 6.3.1. Automatic Switching between NICAM and Analog Sound

Micronas 3

MSP 34x5G PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

79 6.3.1.1. Function in Automatic Sound Select Mode

79 6.3.1.2. Function in Manual Mode

81 6.3.2. A2 Threshold

81 6.3.3. Carrier-Mute Threshold

82 6.3.4. Register AD_CV

83 6.3.5. Register MODE_REG

85 6.3.6. FIR-Parameter, Registers FIR1 and FIR2

85 6.3.7. DCO-Registers

87 6.4. Manual/Compatibility Mode: Description of Demodulator Read Registers

87 6.4.1. NICAM Mode Control/Additional Data Bits Register

87 6.4.2. Additional Data Bits Register

87 6.4.3. CIB Bits Register

88 6.4.4. NICAM Error Rate Register

88 6.4.5. PLL_CAPS Readback Register

88 6.4.6. AGC_GAIN Readback Register

88 6.4.7. Automatic Search Function for FM-Carrier Detection in Satellite Mode

89 6.5. Manual/Compatibility Mode: Description of DSP Write Registers

89 6.5.1. Additional Channel Matrix Modes

89 6.5.2. Volume Modes of SCART1 Output

89 6.5.3. FM Fixed Deemphasis

89 6.5.4. FM Adaptive Deemphasis

89 6.5.5. NICAM Deemphasis

90 6.5.6. Identification Mode for A2 Stereo Systems

90 6.5.7. FM DC Notch

90 6.6. Manual/Compatibility Mode: Description of DSP Read Registers

90 6.6.1. Stereo Detection Register for A2 Stereo Systems

90 6.6.2. DC Level Register

91 6.7. Demodulator Source Channels in Manual Mode

91 6.7.1. Terrestric Sound Standards

91 6.7.2. SAT Sound Standards

91 6.8. Exclusions of Audio Baseband Features

91 6.9. Compatibility Restrictions to MSP 34x5D

93 7. Appendix D: Application Information

93 7.1. Phase Relationship of Analog Outputs

94 7.2. Application Circuit

96 8. Appendix E: MSP 34x5G Version History

96 9. Data Sheet History

License Notice:

“Dolby Pro Logic” is a trademark of Dolby Laboratories.

Supply of this implementation of Dolby Technology does not convey a license nor imply a right under any patent, or any other industrial or intellectual property right of Dolby Laboratories, to use this implementation in any finished end-user or ready-to-use final product. Companies planning to

use this implementation in products must obtain a license from Dolby Laboratories Licensing Corporation before designing such products.

4 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

Multistandard Sound Processor Family

Release Note: Revision bars indicate significant

changes to the previous edition. The hardware and

software description in this document is valid for

the MSP 34x5G version B8 and following versions.

1. Introduction

The MSP 34x5G family of single-chip Multistandard

Sound Processors covers the sound processing of all

analog TV standards worldwide, as well as the NICAM

digital sound standards. The full TV sound processing,

starting with analog sound IF signal-in, down to processed analog AF-out, is performed in a single chip.

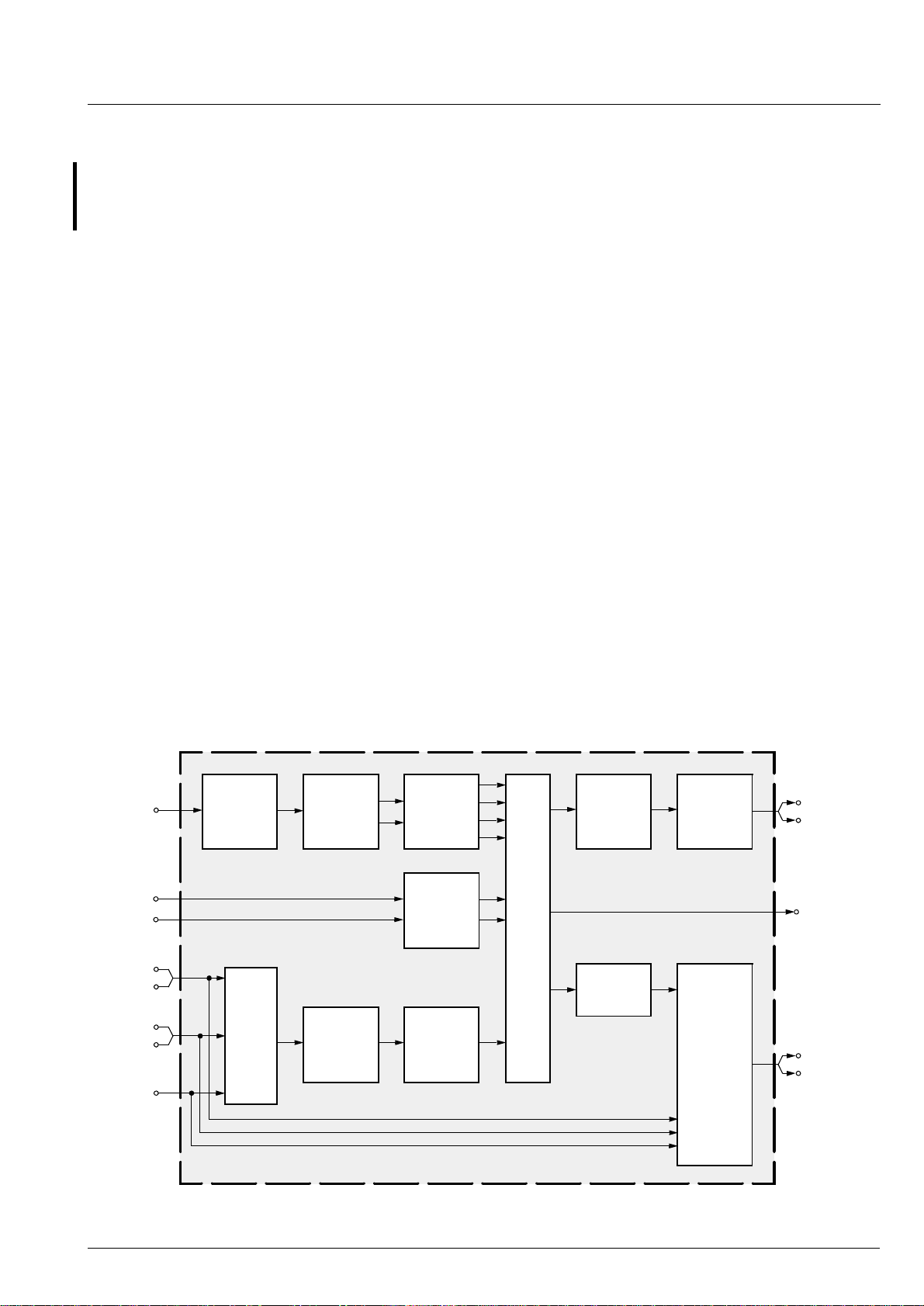

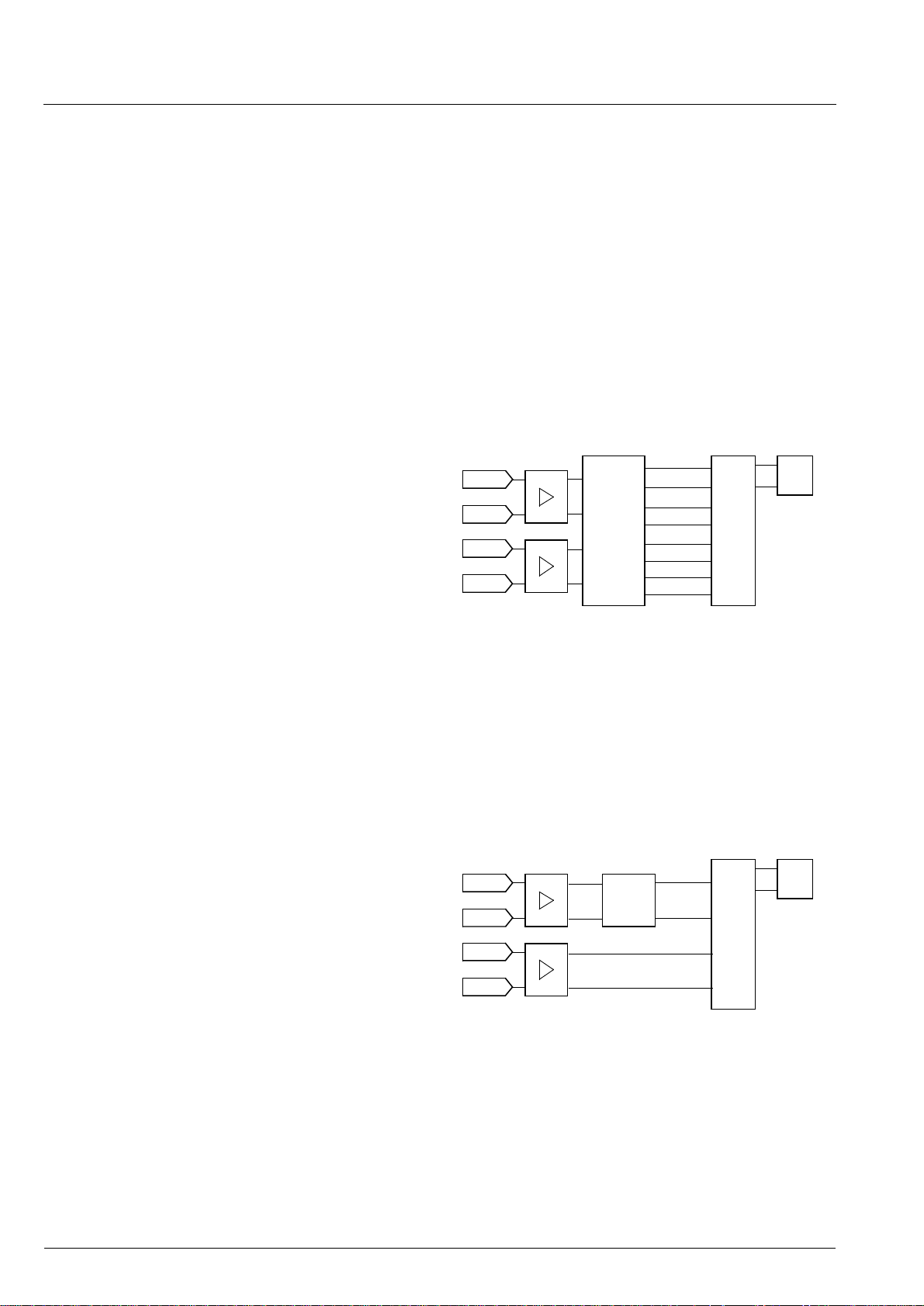

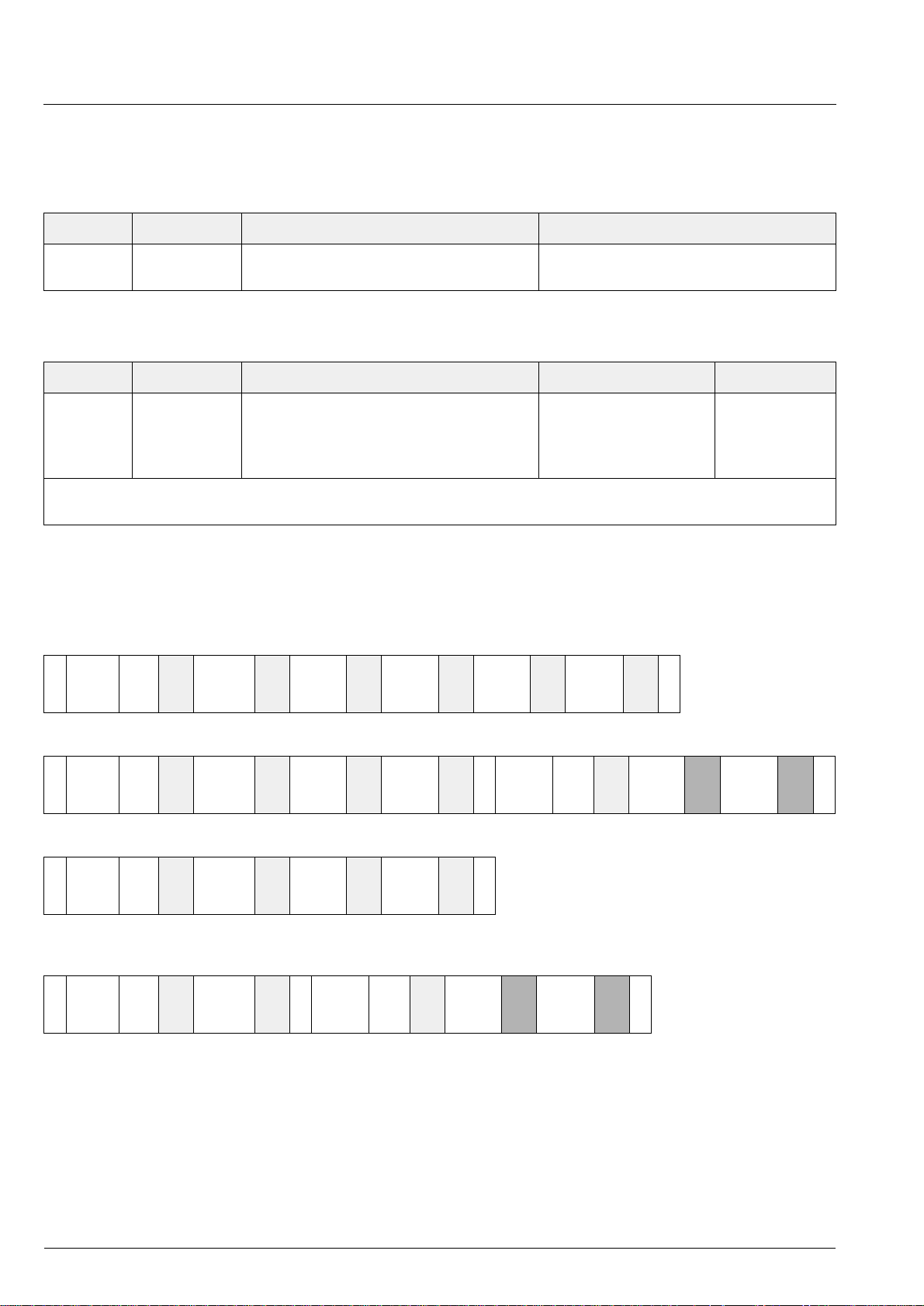

Figure 1–1 shows a simplified functional block diagram

of the MSP 34x5G.

These TV sound processing ICs include versions for

processing the multichannel television sound (MTS)

signal conforming to the standard recommended by

the Broadcast Television Systems Committe e (BTSC).

The DBX noise reduction, or alternatively, Micronas

Noise Reduction (MNR) is performed alignment free.

Other processed standards are the Japanese FM-FM

multiplex standard (EIA-J) and the FM-Stereo-Radio

standard.

Current ICs have to perform adjustment p rocedures in

order to achieve good stereo separatio n for BTSC and

EIA-J. The MSP 34x5G has optimum stereo performance without any adjustments.

All MSP 34xxG versions are pin compatible to the

MSP 34xxD. Only minor modifications are necessary

to adapt a MSP 34xxD controlling software to the

MSP 34xxG. The MSP 34x5G further simplifies controlling software. St andard selection requi res a single

2

C transmission only.

I

Note: The MSP 34x5G version has reduced control

registers and less functional pins. The remaining registers are software-compatible to the MSP 34x0G. The

pinning is compatible to the MSP 34x0G.

The MSP 34x5G has built-in automatic functions: The

IC is able to detect the actual sound standard automatically (Automatic Standard Detection). Furthermore,

pilot levels and identification sign als can be evaluated

internally with subsequent switching between mono/

stereo/bilingual; no I

2

C interaction is ne cessar y (Auto-

matic Sound Selectio n) .

The MSP 34x5G can handle very high FM deviation s

even in conjunction with NICAM processing. This is

especially impor tant for the introduction of NICAM in

China.

The ICs are produced in submicron CMOS technology.

The MSP 34x5G is available in the following packages:

PSDIP64, PSDIP52, PMQFP44, PLQFP64, and

PQFP80.

Sound IF1

I2S1

I2S2

SCART1

SCART2

MONO

SCART

DSP

Input

Select

De-

modulator

ADC

Pre-

processing

Prescale

Prescale

Fig. 1–1: Simplified functional block diagram of MSP 34x5G

Loud-

speaker

Sound

Processing

Source Select

DAC

DACADC

SCART

Output

Select

Loudspeaker

I2S

SCART1

Micronas 5

MSP 34x5G PRELIMINARY DATA SHEET

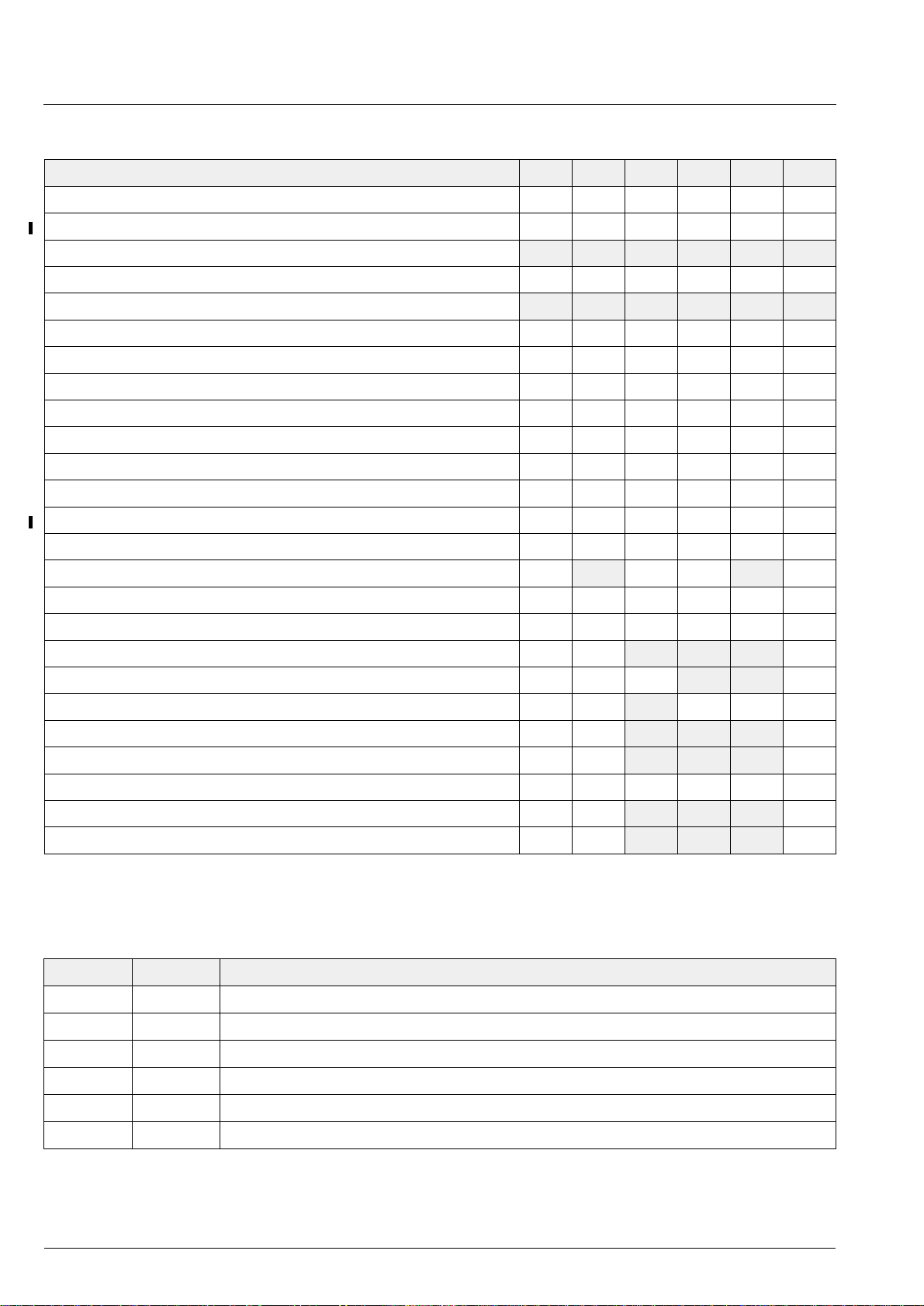

1.1. Features of the MSP 34x5G Family and Differences to MSPD

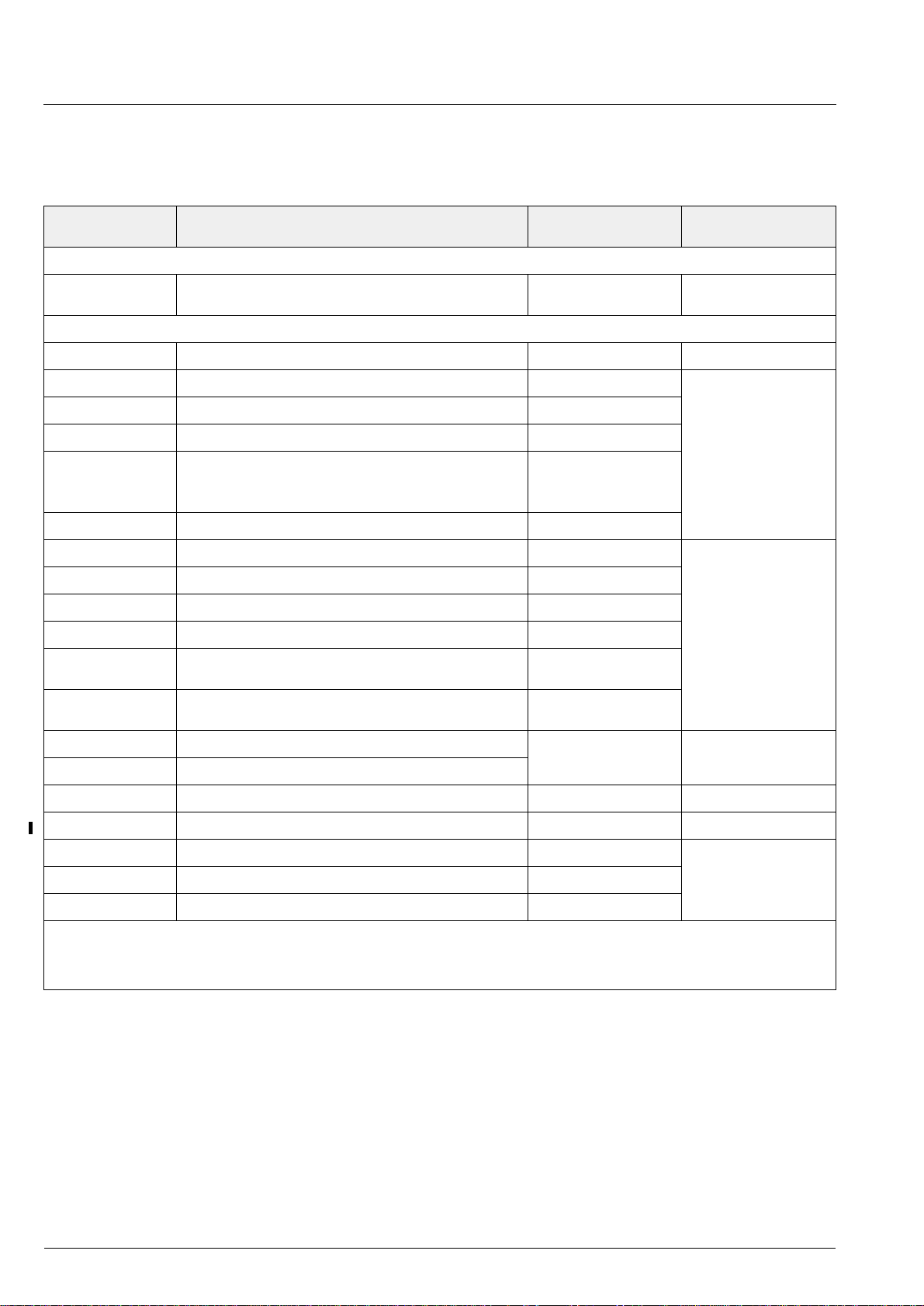

Feature (New features not available for MSPD are shaded gray. ) 3405 3415 3425 3445 3455 3465

Standard Selection with single I

Automatic Standard Detection of terrestrial TV standards X X X X X X

2

C transmission X X X X X X

Automatic Sound Selection (mono/stereo/bilingual), new registers MODUS, STATUS

Automatic Carrier Mute function X X X X X X

Interrupt output programmable (indicating status change)

Loudspeaker channel with volume, balance, bass, treble, loudness X X X X X X

AVC: Automatic Volume Correction X X X X X X

Spatial effect for loudspeaker channel X X X X X X

Two Stereo SCART (line) inputs, one Mono input; one Stereo SCART outputs X X X X X X

Complete SCART in/out switching matrix X X X X X X

2

S inputs; one I2S output X X X X X X

Two I

All analog Mono sound carriers including AM-SECAM L

All analog FM-Stereo A2 and satellite standards X X X

All NICAM standards XX

Simultaneous demodulation of (very) high-deviation FM-Mono and NICAM

Adaptive deemphasis for satellite (Wegener-Panda, acc. to ASTRA specification) X X X X

ASTRA Digital Radio (ADR) together with DRP 3510A X X X

Demodulation of the BTSC multiplex signal and the SAP channel

Alignment free digital DBX noise reduction for BTSC Stereo and SAP

X X X X X X

X X X X X X

X X X X X X

X X

X X X

X X

Alignment free digital Micronas Noise Reduction (MNR) for BTSC Stereo and SAP

BTSC stereo separation (MSP 3425/45G also EIA-J) significantly better than spec.

SAP and stereo detection for BTSC system

Korean FM-Stereo A2 standard X X X X X

Alignment-free Japanese standard EIA-J

Demodulation of the FM-Radio multiplex signal

X

X X X

X X X

X X X

X X X

1.2. MSP 34x5G Version List

Version Status Description

MSP 3405G available FM Stereo (A2) Version

MSP 3415G available NICAM and FM Stereo (A2) Version

MSP 3425G available NTSC Version (A2 Korea, BTSC with Micronas Noise Reduction (MNR), Japanese EIA-J system)

MSP 3445G available NTSC Version (A2 Korea, BTSC with DBX noise reduction, Japanese EIA-J system)

MSP 3455G available Global Stereo Version (all sound standards)

MSP 3465G available Global Mono Vers io n (all sound standards)

6 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

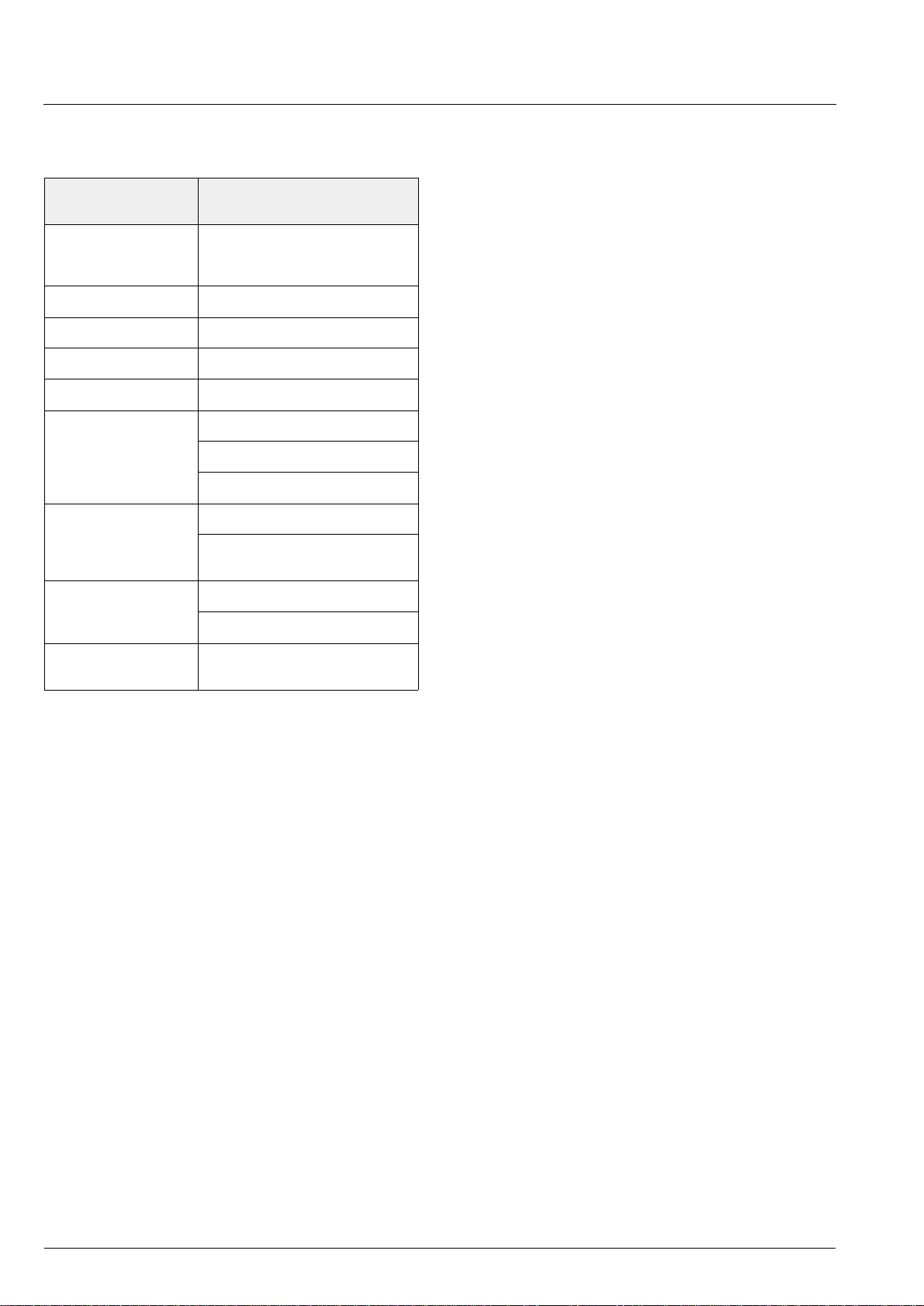

1.3. MSP 34x5G Versions and their Application Fields

Table 1–1 provides an overview of TV sound standards

that can be processed by the MSP 34x5G family. In

addition, the MSP 34x5G is able to handle the FMRadio standard. With the MSP 34x5G, a complete

multimedia receiver covering all TV sound standards

together with te rrestr ial/ cable and satel lite radio sou nd

can be built; even ASTRA Digital Radio can be processed (with a DRP 3510A coprocessor).

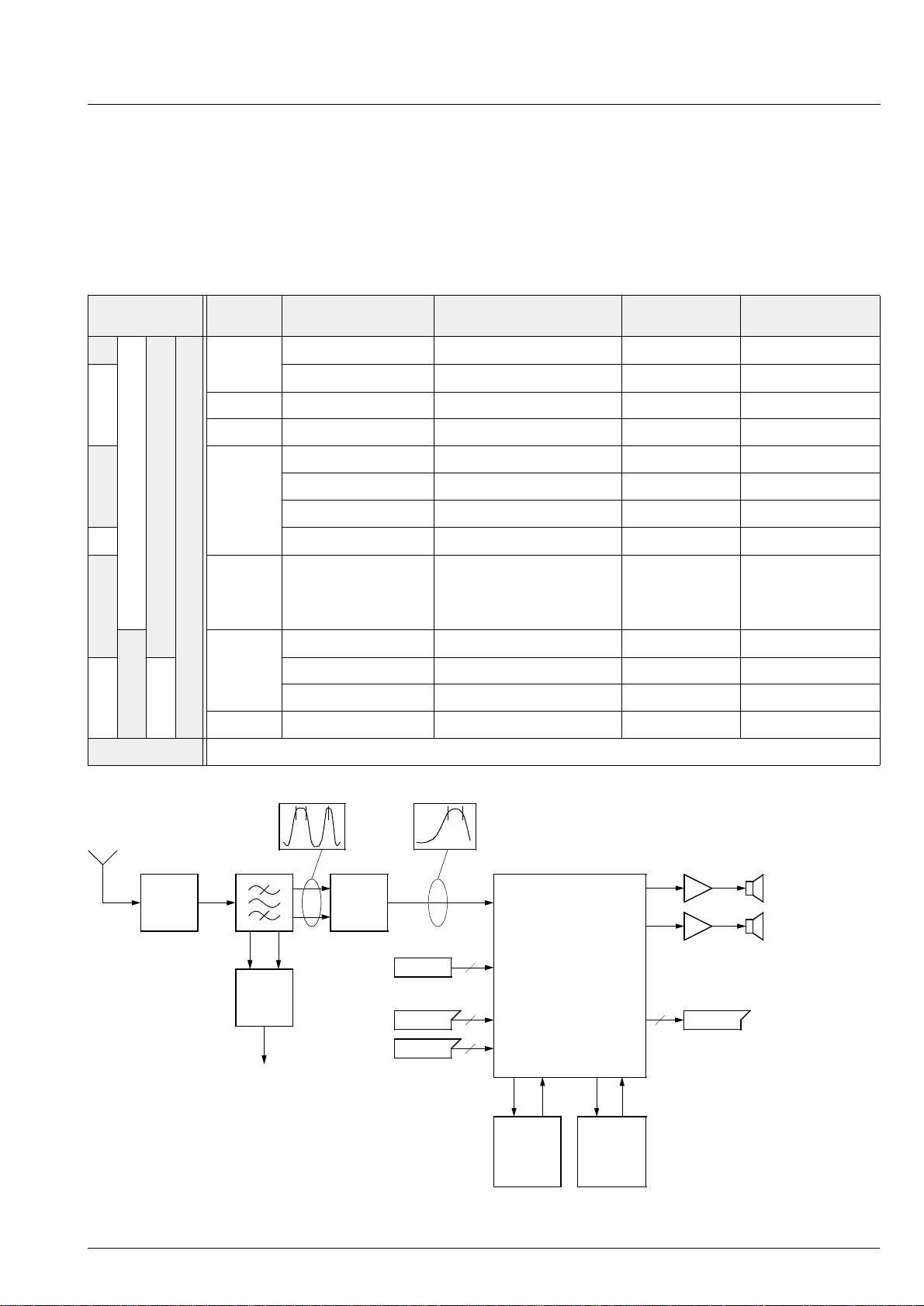

Table 1–1: TV Stereo Sound Standards covered by the MSP 34x5G IC Family (details see Appendix A)

MSP Version TV-

3405

3405

3405

3415

System

B/G

L 6.5/5.85 AM-Mono/NICAM SECAM-L France

I 6.0/6.552 FM-Mono/NICAM PAL UK, Hong Kong

D/K

3455

Satellite

Position of Sound

Carrier /MHz

5.5/5.7421875 FM-Stereo (A2) PAL Germany

5.5/5.85 FM-Mono/NICAM PAL Scandinavia, Spain

6.5/6.2578125 FM-Stereo (A2, D/K1) SECAM-East Slovak. Rep.

6.5/6.7421875 FM-Stereo (A2, D/K2) PAL currently no broadcast

6.5/5.7421875 FM-Stereo (A2, D/K3) SECAM-East Poland

6.5/5.85 FM-Mono/NICAM (D/K, NICAM) PAL China, Hungary

6.5

7.02/7.2

7.38/7.56

etc.

Sound

Modulation

FM-Mono

FM-Stereo

ASTRA Digital Radio (ADR)

with DRP 3510A

Color

System

PAL

Broadcast e.g. in:

Europe Sat.

ASTRA

4.5/4.724212 FM-Stereo (A2) NTSC Korea

M/N

3425, 3445

FM-Radio 10.7 FM-Stereo Radio USA, Europe

3465 All standards as above, but Mono demodulation only.

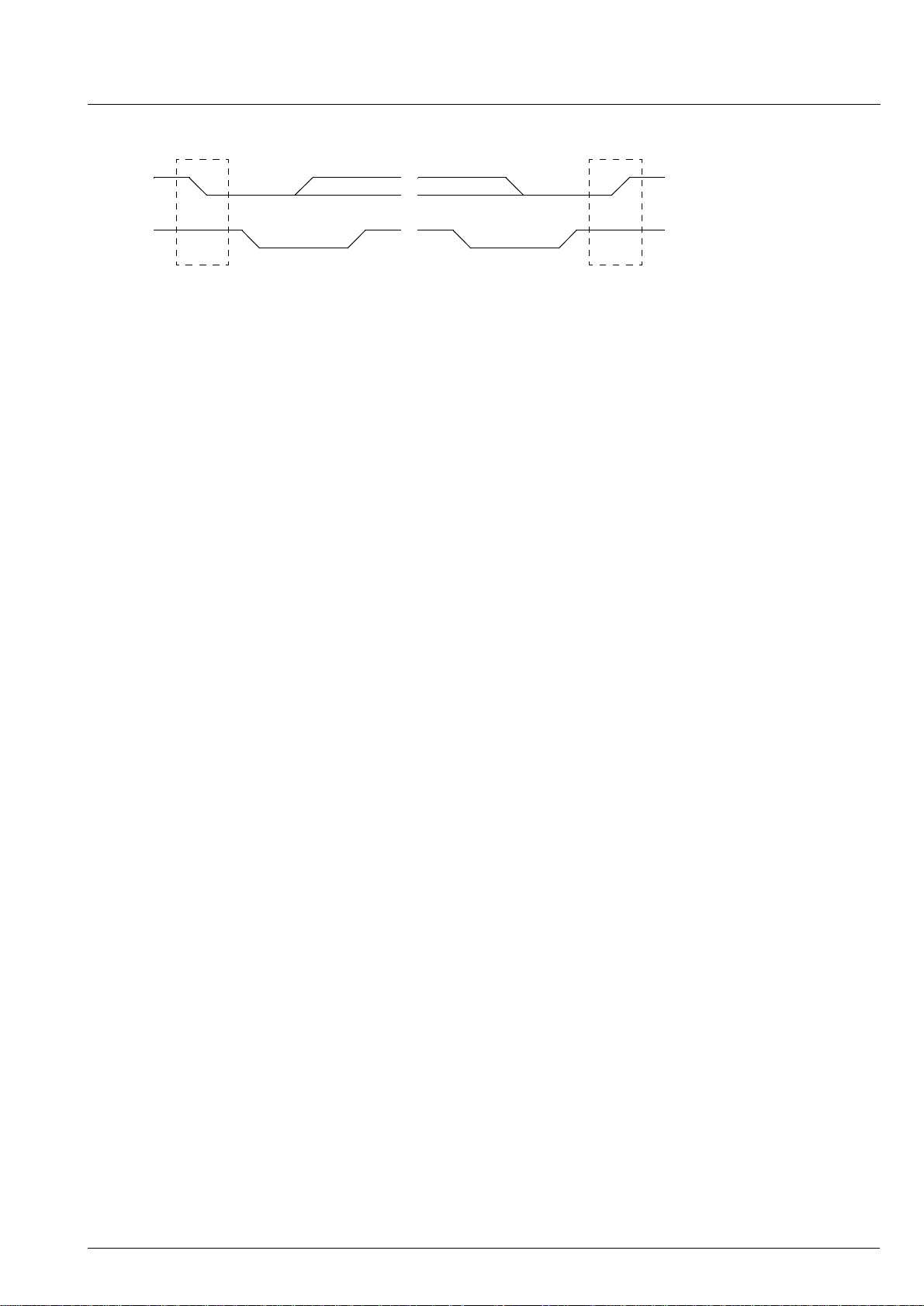

SAW Filter

Tuner

Composite

Video

4.5 FM-FM (EIA-J) NTSC Japan

4.5 BTSC-Stereo

33 34 39 MHz 4.5 9 MHz

Sound

IF

Mixer

1

2

2

Vision

Demodulator

SCART

Inputs

Mono

SCART1

SCART2

+ SAP NTSC, PAL USA, Argentina

Loudspeaker

MSP 34x5G

2

2

I

S1 ADR I2S2

SCART1

SCART Output

Dolby

Pro Logic

Processor

DPL 351xA

ADR

Decoder

DRP 3510A

Fig. 1–2: Typical MSP 34x5G application

Micronas 7

8 Micronas

ANA_IN1+

ADR-Bus

Interface

AGC

A

D

Standard Selection

DEMODULATOR

(incl. Carrier Mute)

Decoded

Standards:

−

NICAM

−

A2

−

AM

−

BTSC

−

EIA-J

−

SAT

−

FM-Radio

Deemphasis:

50/75 µs,

J17

DBX/MNR

Panda1

Deemphasis

J17

Standard

and Sound

Detection

FM/AM

Prescale

(0E

NICAM

Prescale

(10

I2C

Read

Register

Sound Select

)

hex

)

hex

Automatic

FM/AM

Stereo or A/B

Stereo or A

Stereo or B

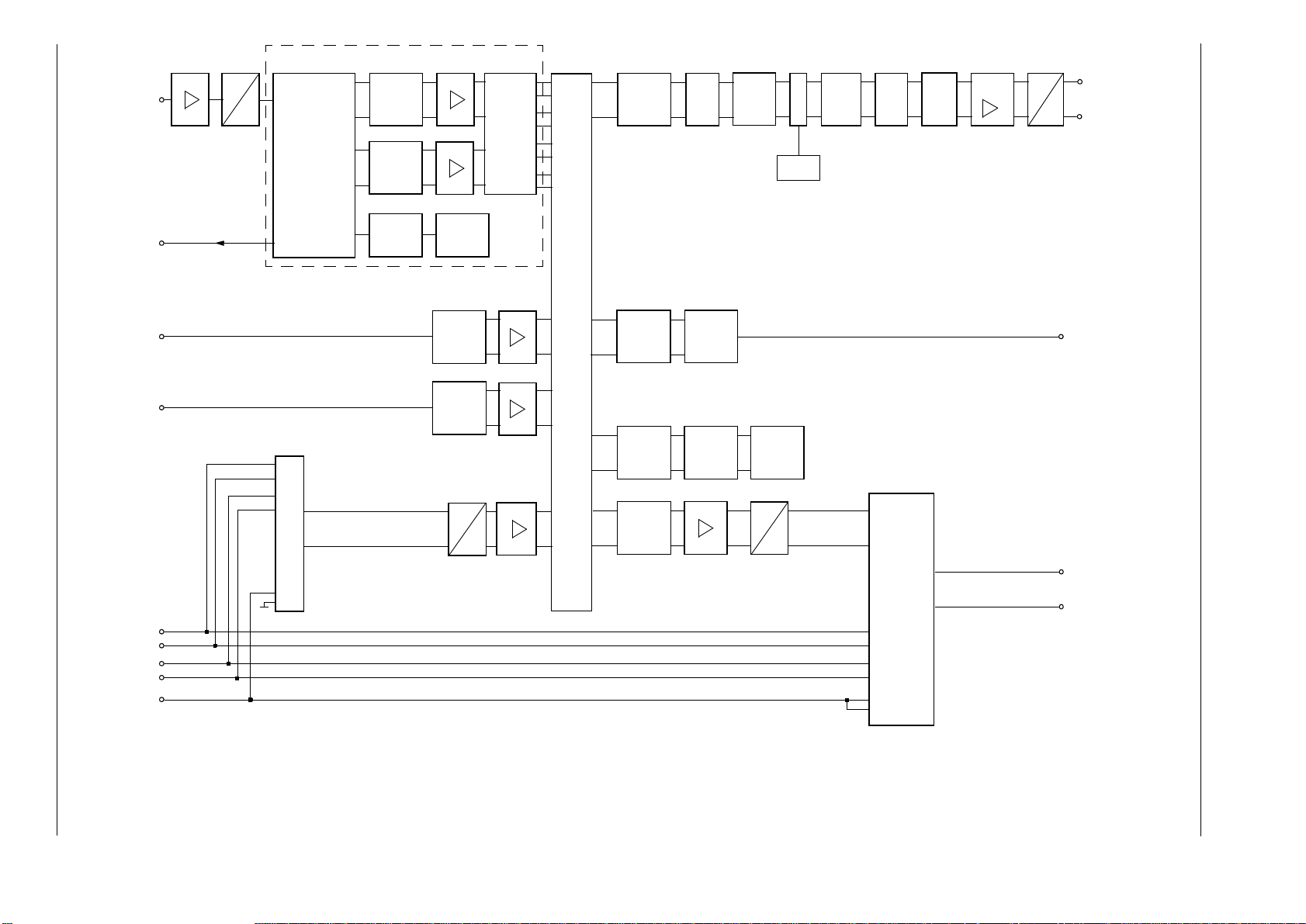

2. Functional Description

0

1

3

Loud-

speaker

Channel

Matrix

(08

AVC

)

hex

Bass/

Treble

)

(02

hex

)

hex

)

(03

hex

Loud-

Σ

ness

(04

hex

Spatial

Effects

)(05

)(01

hex

Balance

Volume

)

(00

hex

D

)(29

hex

DACM_L

A

DACM_R

MSP 34x5G PRELIMINARY DATA SHEET

Beeper

4

(14

)

hex

I2S_DA_IN1

I2S_DA_IN2

I2S

Interface

I2S

Interface

I2S1

Prescale

(16

I2S2

5

)

hex

Source Select

6

I2S

Channel

Matrix

(0B

I2S

Interface

)

hex

Prescale

(12

)

hex

SCART

A

D

Prescale

2

(0D

)

hex

Quasi-Peak

Channel

Matrix

(0C

hex

SCART1

Channel

Matrix

(0A

hex

Quasi-Peak

Detector

)

Volume

)(07

)

hex

I2C

Read

Register

D

A

(19

(1A

SCART DSP Input Select

(13

)

hex

SC1_IN_L

SC1_IN_R

SC2_IN_L

SC2_IN_R

MONO_IN

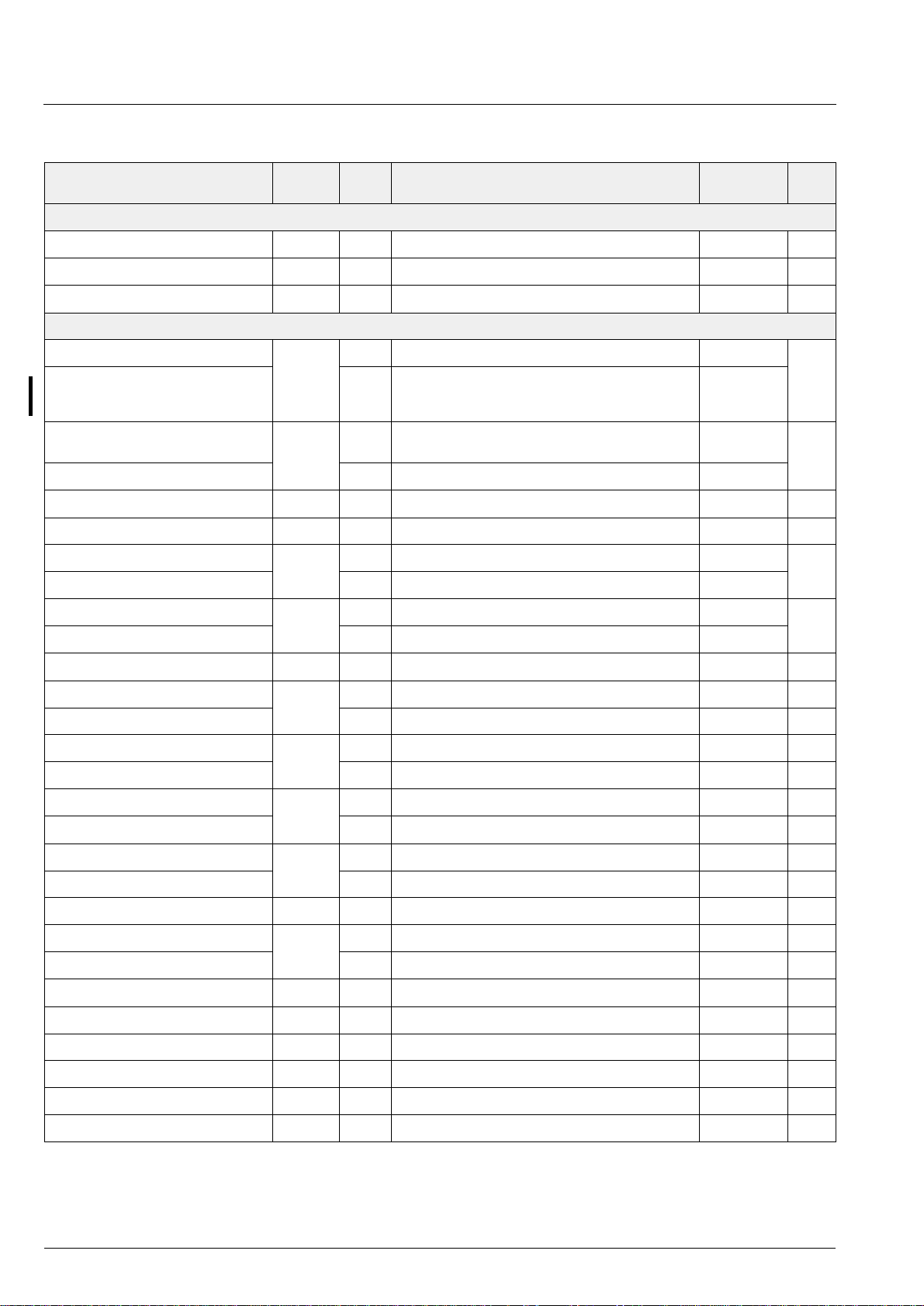

ig. 2–1: Signal flow block diagram of the MSP 34x5G (input and output names correspond to pin names).

I2S_DA_OUT

)

hex

)

hex

SCART1_L/R

SC1_OUT_L

SC1_OUT_R

SCART Output Select

)

(13

hex

PRELIMINARY DATA SHEET MSP 34x5G

2.1. Architecture of the MSP 34x5G Family

Fig. 2–1 on page 8 shows a simplified block diagram of

the IC. The block diagram contains all features of the

MSP 3455G. Other members of the MSP 34x5G family

do not have the complete set of features: The demodulator handles only a subset of the standards presented

in the demodulator block; NICAM processing is only

possible in the MSP 3415G and MSP 3455G (see

dashed block in Fig. 2–1).

2.2. Sound IF Processing

2.2.1. Analog Sound IF Input

The input pins ANA_ IN1+ and ANA _IN

sibility to connect sound IF (SIF) sources to the

MSP 34x5G. The analog-to-digital conversion of the

sound IF signal is done by an A/D-conver ter. An analog automatic gain circuit (AGC) allows a wide range of

input levels. The high-pass filter formed by the coupling capacitor at pin ANA_IN1+ (see Section 7.

“Appendix D: Application Information” on page 93) is

sufficient in most cases to suppress video components. Some combinations of SAW filters and sound IF

mixer ICs, however, show large picture components on

their outputs. In this case, further filtering is recommended.

− offer the pos-

BTSC-Mono + SAP: Detection and FM demodulation

of the aural carrier resulting in the MTS/MPX signal.

Detection and evaluation of the pilot car rier, detection

and FM demodulat ion of the SA P-sub carr ier. Processing of the DBX noise reduction or Micronas Noise

Reduction (MNR).

Japan Stereo: Detection and FM demodulation of the

aural carrier resulting in the MPX signal. Demodulation

and evaluation of the identification signal and FM

demodulation of the (L-R)-carrier.

FM-Satellite Sound: Demodulation of one or two FM

carriers. Processi ng of high-deviation mono or na rrow

bandwidth mono, stereo, or bilingual satellite sound

according to the ASTRA specification.

FM-Stereo-Radio: Detection and FM demodulation of

the aural carrier resu lting in the MPX si gnal. Detecti on

and evaluation of the pilot carrier and AM demodulation of the (L-R)-carrier.

The demodulator blocks of all MSP 34x5G versions

have identical user interfaces. Even completely different systems like the BTSC and NICAM systems are

controlled the same way. Standards are selected by

means of MSP Standard Cod es. Automatic processes

handle standard detection and identification without

controller interaction. The key features of the

MSP 34x5G demodulator blocks are

2.2.2. Demodulator: Standards and Features

The MSP 34x5G is able to demodulate all TV sound

standards worldwid e including the digital NICAM system. Depending on the MSP 34x5G version, the following demodulation modes can be performed:

A2-Systems: Detectio n and demodu lation of two separate FM carriers ( FM1 and FM2), demodulation and

evaluation of the identification signal of carrier FM2.

NICAM-Systems: Demodulation and decoding of the

NICAM carrier, detection and demodulation of the analog (FM or AM) carrier. For D/K-NICAM, the FM carrier

may have a maximum deviation of 384 kHz.

Very high deviation FM-Mono: Detection and robust

demodulation of on e FM carr ier with a maximum deviation of 540 kHz.

BTSC-Stereo: Detection and FM demodulation of the

aural carrier resulting in the MTS/MPX signal. Detection and evaluation of the pilot carr ier, AM demodulation of the (L-R)-carr ier and detec tion of the SA P subcarrier. Processing of the DBX noise reduction or

Micronas Noise Reduction (MNR).

Standard Selection: The controlling of the de modula tor is minimized: All parameters, such as tuning frequencies or filter bandwidth, are adjusted automatically by transmitting one single value to the

STANDARD SELECT reg ister. For all standards, specific MSP standard codes are defined.

Automatic Standard Detection: If the TV sound standard is unknown, the MSP 34x5G can automatically

detect the actual standard, switch to that standard, and

respond the actual MSP standard code.

Automatic Carrier Mute: To prevent noise effects or

FM identification problems in the absence of an FM

carrier, the MSP 34x5G offers a configurable carrier

mute feature, which is activated automatically if th e T V

sound standard is selected by means of the STANDARD SELECT register. If no FM carrier is detected at

one of the two MSP demodulator channels, the corresponding demodulator output is muted. This is indicated in the STATUS register.

Micronas 9

MSP 34x5G PRELIMINARY DATA SHEET

2.2.3. Preprocessing of Demodulator Signals

The NICAM signals must be processed by a deemphasis filter and adjusted in level. The analog demodulated signals must b e processed by a deemphas is filter, adjusted in level, and dematrixed. The correct

deemphasis filters are already selected by setting th e

standard in the STANDARD SELECT register. The

level adjustment has to be done by means of the FM/

AM and NICAM prescale registers. The necessary

dematrix function depends on the selected sound

standard and the actual broadcasted sound mode

(mono, stereo, or bilingual). It can be manually set by

the FM Matrix Mode register or automatically by the

Automatic Sound Selection.

2.2.4. Automatic Sound Select

In the Automatic Sound Select mode, the dematrix

function i s aut om a t ica l ly s el ec t ed ba se d on th e id ent if i cation information in the ST ATUS register. No I

2

C interaction is necessary when the broadcasted sound

mode changes (e.g. from mono to stereo).

The demodulator sup ports the identification ch eck by

switching between mono-compatible standards (standards that have the same FM-Mon o carrier) automatically and non-audible. If B/G-FM or B/G-NICAM is

selected, the MSP will switch between these standards. The same action is performed for the standards:

D/K1-FM, D/K2-FM, D/K3-FM and D/K-NICAM.

Switching is only d one in th e abse nce of a ny ste reo or

bilingual identification. If identification is found, the

MSP keeps the detected standard.

In case of high bit-error rates, the MSP 34x5G automatically falls back from digital NI CAM sound to analog FM or AM mono.

– “Stereo or A” channel: Analog or digital mono

sound, stereo if available. In case of bilingual broadcast, it contains language A (on left and right).

– “Stereo or B” channel: Analog or digital mono

sound, stereo if available. In case of bilingual broadcast, it contains language B (on left and right).

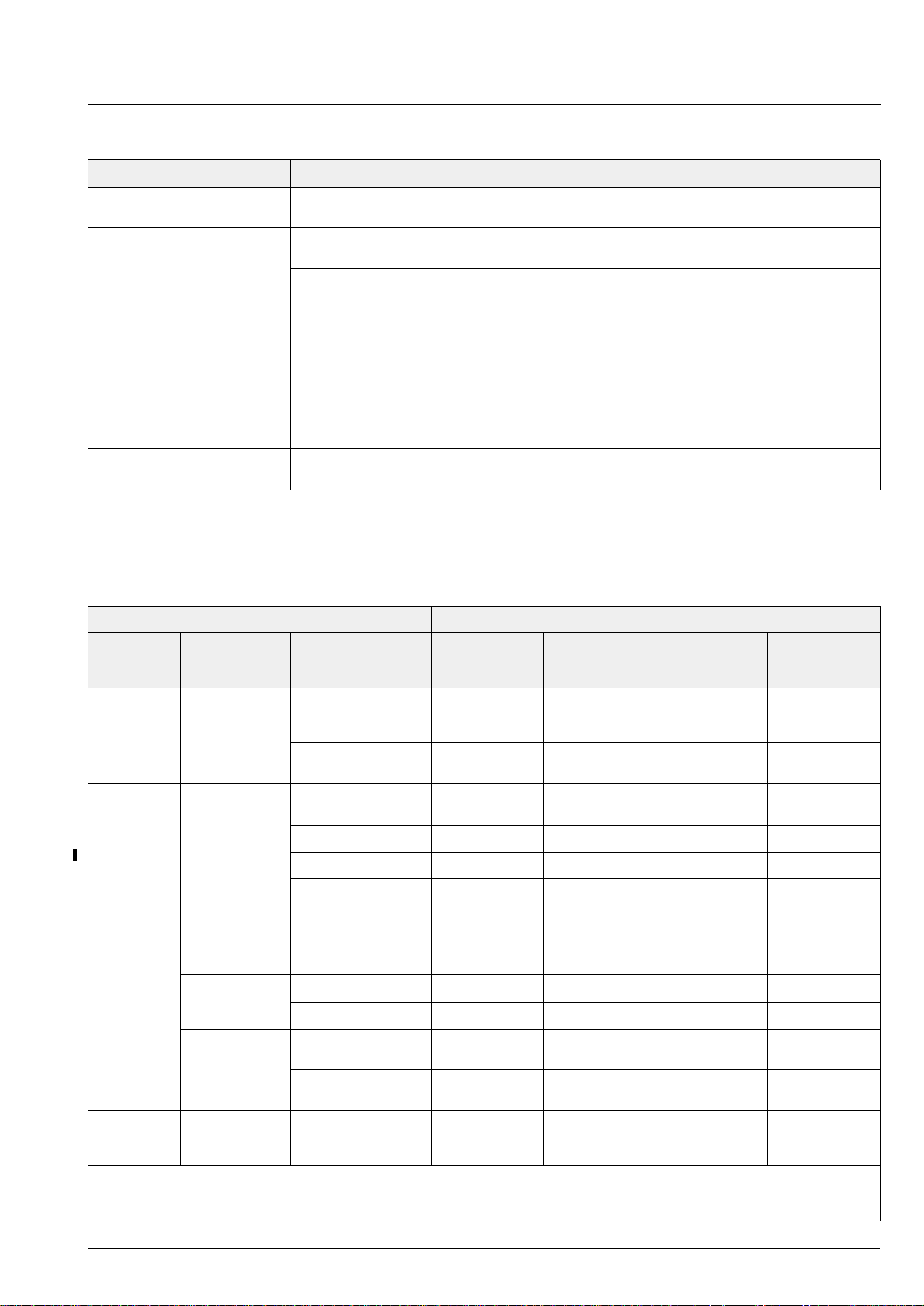

Fig. 2–2 and Table 2–2 show the source channel

assignment of the demodulated signals in case of

Automatic Sound Select mode for all sound standards.

Note: The analog primar y input channel contains the

signal of the mono FM/AM c arrie r or the L+R sig nal of

the MPX carrier. The secondary input channel contains the signal of the 2nd FM c arrier, the L-R signal of

the MPX carrier, or the SAP signal.

Source Select

LS Ch.

Matrix

Output-Ch.

matrices

must be set

once to

stereo.

primary

channel

secondary

channel

NICAM A

NICAM B

FM/AM

Prescale

NICAM

Prescale

Automatic

Sound

Select

FM/AM

Stereo or A/B

Stereo or A

Stereo or B

0

1

3

4

Fig. 2–2: Source channel assignment of demodulated

signals in Automatic Sound Select Mode

2.2.5. Manual Mode

Fig. 2–3 shows the source channel assignment of

demodulated signals in ca se of manual mode. If manual mode is required, more information can be found in

Section 6.7. “Demodulator Source Channels in Manual

Mode” on page 91.

Table 2–1 summarizes all actions that take place when

Automatic Sound Select is switched on.

To provide more fl exibility, the Automatic Sound Select

block prepares four different source channels of

demodulated sound (Fi g. 2–2). By choosing one of th e

four demodulator channels, the p referred sound mode

can be selected for each of the output chann els (loudspeaker, headphone, etc.). This is done by means of

primary

channel

secondary

channel

NICAM A

NICAM B

FM/AM

Prescale

NICAM

Prescale

FM-Matrix

FM/AM

NICAM

(Stereo or A/B)

0

1

Source Select

LS Ch.

Matrix

Output-Ch.

matrices

must be set

according to

the standard.

the Source Select registers.

The following source chan nels of demodulated sound

are defined:

Fig. 2–3: Source channel assignment of demodulated

signals in Manual Mode

– “FM/AM” channel: Analog mono sound, stereo if

available. In case of NICAM, analog mono only

(FM or AM mono).

– “Stereo or A/B” channel: Analog or digital mono

sound, stereo if available. In case of bilingual broadcast, it contains both languages A (left) and B

(right).

10 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

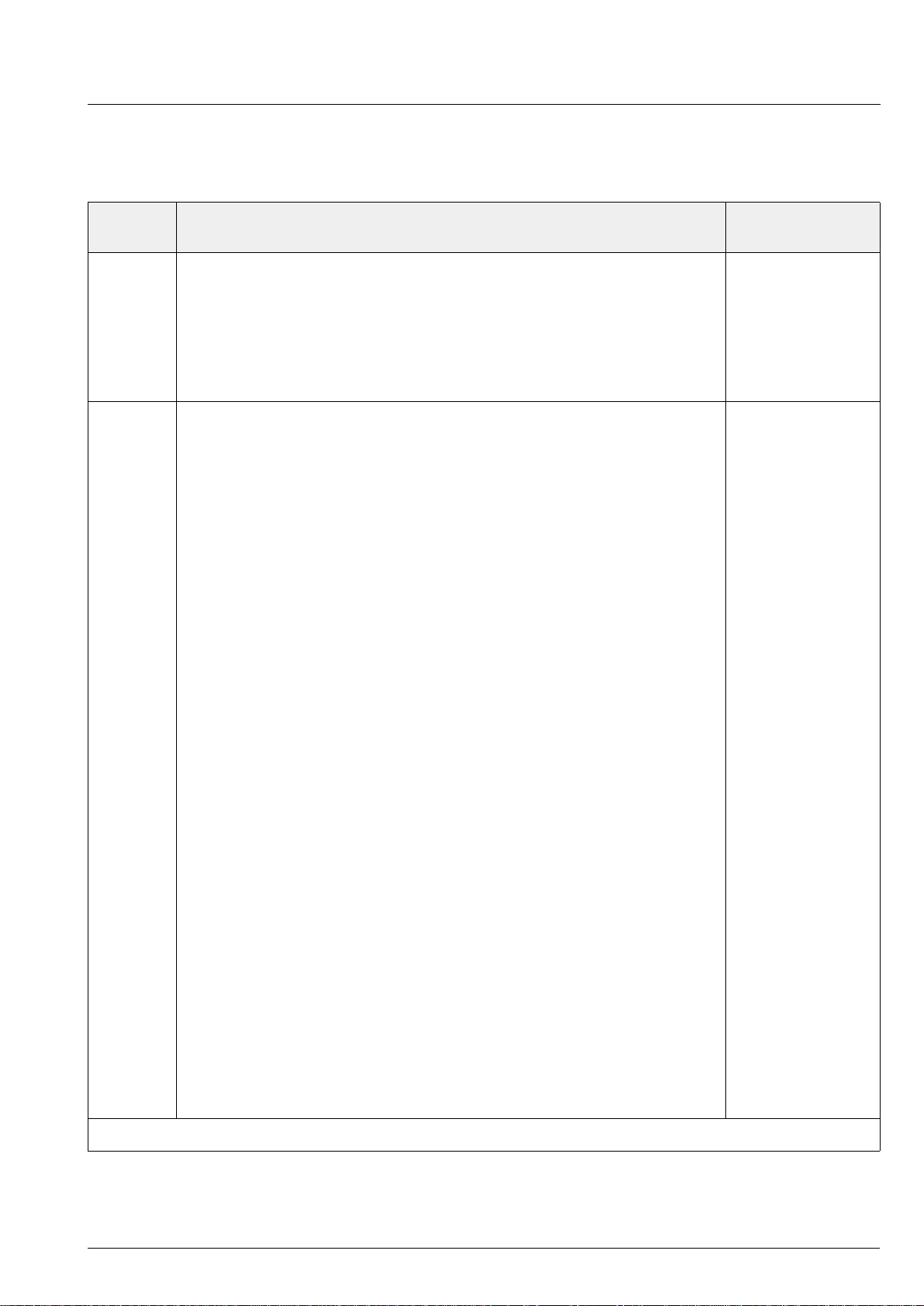

Table 2–1: Performed actions of the Automatic Sound Selection

Selected TV Sound Standard Performed Actions

B/G-FM, D/K-FM, M-Korea,

and M-Japan

B/G-NICAM, L-NICAM, I-NICAM,

D/K-NICAM

Evaluation of the identification signal and automatic switching to mono, stereo, or bilingual. Preparing four

demodulator source channels according to Table 2–2.

Evaluation of NICAM-C-bits and automatic switching to mono, stereo, or bilingual. Preparing four

demodulator source channels according to Table 2–2.

In case of bad or no NICAM reception, the MSP switches automatically to FM/AM mono and switches

back to NICAM if possible. A hys teresis prevents periodical switching.

B/G-FM, B/G-NICAM

or

D/K1-FM, D/K2-FM, D/K3-FM,

and D/K-NICAM

Automatic searching for stereo/bilingual-identification in case of mono transmission. Automatic and nonaudible changes between Dual-FM and FM-NICAM standards while listening to the basic FM-mono sound

carrier.

Example: If starting with B/G-FM-Stereo, there will be a periodical alternation to B/G-NICAM in the

absence of FM-Stereo/Bilingual or NICAM-identification. Once an identification is detected, the MSP

keeps the corresponding standard.

BTSC-STEREO, FM Radio Evaluation of the pilot signal and automatic switching to mono or stereo. Preparing four demodulator

source channels according to Table2–2. Detection of the SAP carrier.

M-BTSC-SAP In the absence of SAP, the MSP switches to BTSC-stereo if available. If SAP is detected, the MSP

switches automatically to SAP (see Table 2–2).

Table 2–2: Sound modes for the demodulator source channels with Automatic Sound Select

Source Channels in Automatic Sound Select Mode

Broadcasted

Sound

Standard

Selected

MSP Standard

3)

Code

Broadcasted

Sound Mode

FM/AM

(source select: 0)

Stereo or A/B

(source select: 1)

Stereo or A

(source select: 3)

Stereo or B

(source select: 4)

M-Korea

B/G-FM

D/K-FM

M-Japan

B/G-NICAM

L-NICAM

I-NICAM

D/K-NICAM

D/K-NICAM

(with high

deviation FM)

02

1)

03, 08

04, 05, 07, 0B

30

2)

08, 03

09

0A

2)

, 05

2)

0B, 04

0C, 0D

MONO Mono Mono Mono Mono

1)

STEREO Stereo Stereo Stereo Stereo

BILINGUAL:

Languages A and B Right = B

NICAM not available or

analog Mono analog Mono analog Mono analog Mono

Left = A

Right = B

AB

error rate too high

MONO analog Mono NICAM Mono NICAM Mono NICAM Mono

STEREO analog Mono NICAM Stereo NICAM Stereo NICAM Stereo

BILINGUAL:

Languages A and B

analog Mono Left = NICAM A

Right = NICAM B

NICAM A NICAM B

20, 21 MONO Mono Mono Mono Mono

STEREO Stereo Stereo Stereo Stereo

20 MONO + SAP Mono Mono Mono Mono

BTSC

21 MONO + SAP Left = Mono

STEREO + SAP Stereo Stereo Stereo Stereo

Right = SAP

STEREO + SAP Left = Mono

Right = SAP

Left = Mono

Right = SAP

Left = Mono

Right = SAP

Mono SAP

Mono SAP

FM Radio 40 MONO Mono Mono Mono Mono

STEREO Stereo Stereo Stereo Stereo

1)

The Automatic Sound Select process will automatically switch to the mono compatible analog standard.

2)

The Automatic Sound Select process will automatically switch to the mono compatible digital standard.

3)

The MSP Standard Codes are defined in Table 3–7 on page 20.

Micronas 11

MSP 34x5G PRELIMINARY DATA SHEET

2.3. Preprocessing for SCART and

2

S Input Signals

I

2

The SCART and I

level by means of the SCART and I

S inputs need only be a djusted in

2

S prescale re gis-

ters.

2.4. Source Selection and Output Channel Matrix

The Source Selec tor makes it possible to di stribute all

source signals (o ne of the demodulator source ch annels or SCART) to the desired out put channels (loudspeaker, etc.). All input and output signals can be processed simultaneously. Each source channel is

identified by a unique source address.

For each output channel, the soun d mode can be set

to sound A, sound B, stereo, or mono by means of the

output channel matrix.

If Automatic Sound Select is on, the output channel

matrix can stay fixed to stereo (transparent) for demodulated signals.

2.5. Audio Baseband Processing

2.5.1. Automatic Volume Correction (AVC)

Different sound sources (e.g. terrest rial ch annels, SAT

channels, or SCART) fairly often do not have the same

volume level. Advertisements during movies usually

have a higher volume level than the movie itself. This

results in annoying volume chang es. The AVC solves

this problem by equalizing the volume level.

To prevent clipping, th e AVC’s gain decreases quickly

in dynamic boost conditions. To suppress oscillation

effects, the gain increases rather slowly for low level

inputs. The decay time is programmable by means of

the AVC register (see page 30).

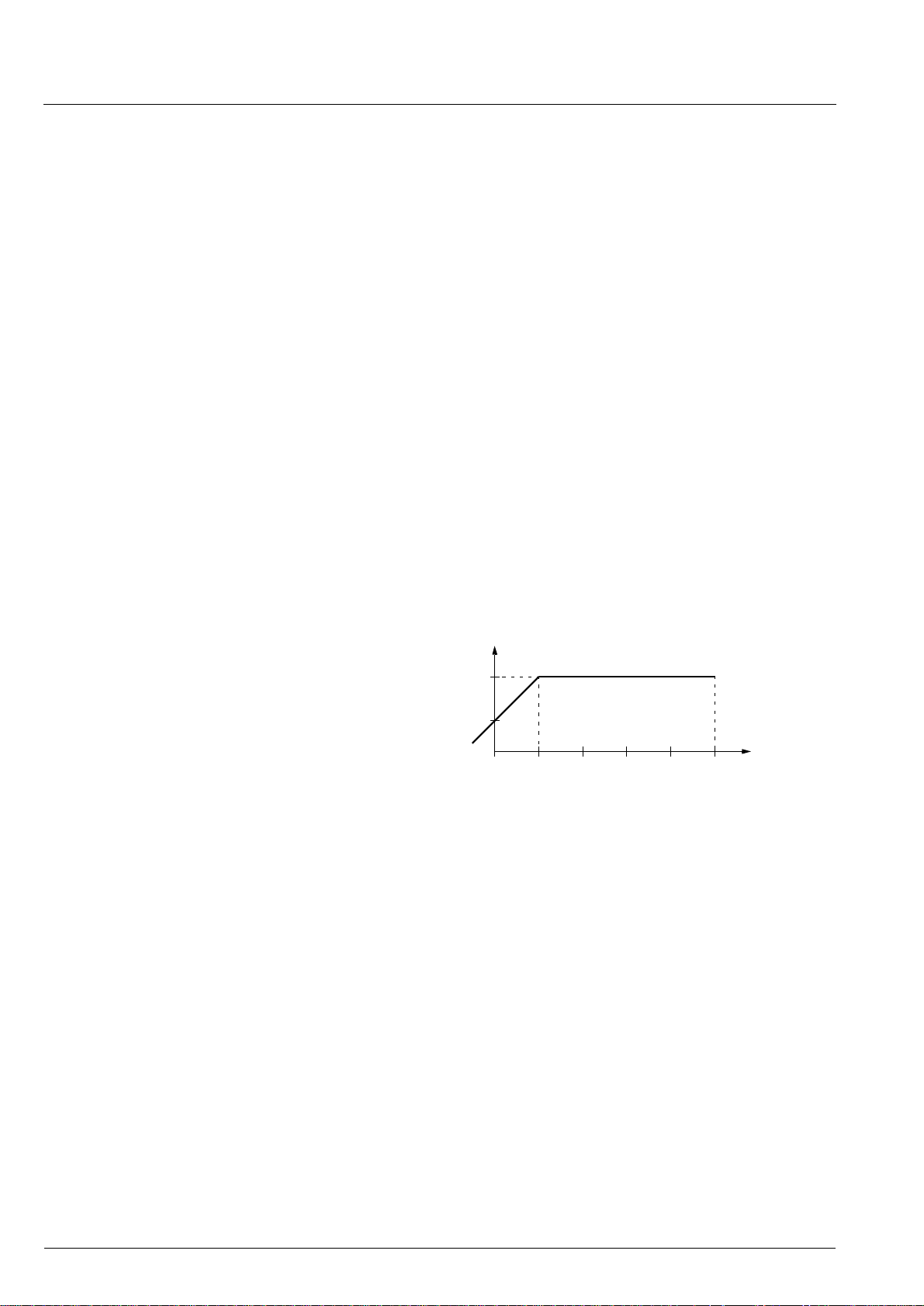

For input signals ranging from

AVC maintains a fixed output level of

−24 dBr to 0 dBr, the

−18 dBr. Fig. 2–4

shows the AVC output level versus its input level. For

prescale and volume registers set to 0 dB, a level of

0 dBr corresponds to full scale input/output. This is

– SCART input/output 0 dBr = 2.0 V

– Loudspeaker output 0 dBr = 1.4 V

rms

rms

output level

[dBr]

−18

−24

input level

−30 −24 −18 −12 −6

0

[dBr]

Fig. 2–4: Simplified AVC characteristics

2.5.2. Loudspeaker Outputs

The following baseband features are implemented in

the loudspeaker output channels: bass/treble, loudness, balance, and volume. A square wave beeper can

be added to the loudspeaker channel.

2.5.3. Quasi-Peak Detector

The quasi-peak r eadout register can be used to read

out the quasi-peak level of any input source. The feature is based on following filter time constants:

attack time: 1.3 ms

decay time: 37 ms

12 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

2.6. SCART Signal Routing

2.6.1. SCART DSP In and SCART Out Select

The SCART DSP Input Select and SCART Output

Select blocks include full matrix switching facilities. To

design a TV set with two pairs of SCART-inputs and

one pair of SCART-outputs, no external switching

hardware is required. The switches are controlled by

the ACB user register (see page 34).

2.6.2. Stand-by Mode

If the MSP 34x5G is switched off by first pulling

STANDBYQ low and th en (a fter >1

µs delay) switching

off DVSUP and AVSUP, but keeping AHVSUP

(‘Stand-by’-mode), the SCART switches maintain

their position and function. This allows the copying

from selected SCART-inp uts to SCART-outputs in the

TV set’s stand-by mode.

In case of power on or startin g from stand-by (switching on the DVSUP and AVSUP, RESETQ going high

2 ms later), all internal re giste rs except th e ACB register (page 34) are reset to the default configuration (see

Table 3–5 on p age 18). The reset position of th e ACB

register becomes active after the fir st I

2

C transmission

into the Baseband Processing part. By transmitting the

ACB register first, the reset state can be redefined.

2

S Bus Interface

2.7. I

The MSP 34x5G has a synchronous master/slave

input/output interface running on 32 kHz.

The interface accepts two formats:

2

S_WS changes at the word boundary

1. I

2

2. I

S_WS changes one I2S-cloc k period before the

word boundaries.

2

S options are set by means of the MODUS and

All I

the I2S_CONFIG registers.

2

S bus interface consists of five pins:

The I

– I 2 S _ D A _ I N 1 , I 2 S _ D A _ I N 2 :

2

I

S serial data input: 16, 18....32 bits per sample

– I2S_DA_OUT:

2

I

S serial data output: 16, 18...32 bits per sample

– I2S_CL:

2

I

S serial clock

– I2S_WS:

2

I

S word strobe signal defines the left and right

sample

If the MSP 34x5G serves as the master on the I

2

interface, the clock and word strobe lines are driven by

the IC. In this mode, only 1 6 o r 32 bi ts p e r s amp le c an

be selected. In slave mode, these lines are input to the

IC and the MSP clock is synchronized to 576 times the

I2S_WS rate (32 kHz) . NICAM operation is n ot possible in slave mode.

S

2

S timing diagram is shown in Fig. 4–28 on

An I

page 63.

Micronas 13

MSP 34x5G PRELIMINARY DATA SHEET

2.8. ADR Bus Interface

For the ASTRA Digital Radio System (ADR), the

MSP 3405G, MSP 3415G , and MSP 3455 G performs

preprocessing such as carrier selection and filtering.

Via the 3-line ADR-bus, the resulting signals are transferred to the DRP 3510A coprocessor, where the

source decoding i s performed. To be prep ared for an

upgrade to ADR with an a ddi ti onal D RP board, the following lines of MSP 34x5G should be provided on a

feature connector:

– I2S_DA_IN1 or I2S_DA_IN2

– I2S_DA_OUT

– I2S_WS

– I2S_CL

– ADR_CL, ADR_WS, ADR_DA

For more details, please refer to the DRP 3510A data

sheet.

2.9. Digital Control I/O Pins and Status Change Indication

2.10. Clock PLL Oscillator and Crystal Specifications

The MSP 34x5G derives all internal system clocks

from the 18.432 MHz oscillator. In NICAM or in I

2

SSlave mode, the clock is phase-locked to the corresponding source. Therefore, it is not possible to use

NICAM and I

2

S-Slave mode at the same time.

For proper performance, the MSP clock oscillator

requires a 18.432-MHz crystal. Note, that for the

phase-locked mode (NICAM, I

2

S slave), crystals with

tighter tolerance are required.

The static level of the digital input/output pins

D_CTR_I/O_0/1 is switchable between HIGH and

LOW via the I

(see page 34). This enables the controlling of external

hardware switches or other devices via I

2

C-bus by means of the ACB register

2

C-bus.

The digital input/ou tput pins can b e set to high imp edance by means of the MODUS register (see page 23).

In this mode, the pins can be used as input. The current state can be rea d ou t of the S TATUS register (see

page 25).

Optionally, the pin D_CTR_I/O_1 can be used as an

interrupt reque st signal to the co ntrol ler, indicating any

changes in the read register STATUS. This makes polling unnecessary; I

2

C-bus interactions are reduced to a

minimum (see STATUS register on page 25 and

MODUS register on page 23).

14 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

3. Control Interface

2

C Bus Interface

3.1. I

The MSP 34x5G is controlled via the I

2

C bus slave

interface.

The IC is selected by transmitting one of the

MSP 34x5G device addresses. In order to allow up to

three MSP ICs to be connected to a single bus, an

address select pin (ADR_SEL) has been implemented.

With ADR_SEL pulled to high, low, or left open, the

MSP 34x5G responds to different device addresses. A

device address pair is defined as a write address and a

read address (see Table 3–1).

Writing is done by sending the write device address,

followed by the subaddress byte, two address bytes,

and two data bytes.

Reading is done by sending the wr ite device address,

followed by the subaddress byte and two address

bytes. Without sending a stop c ondi tion, r ea din g of t he

addressed data is completed by sending the device

read address and reading two bytes of data.

2

Refer to Section 3.1.3. for the I

Section 3.4. “Programming T ips” on page 37 for proposals of MSP 34x5G I

2

C telegrams. See Table 3–2

C bus protocol and to

for a list of available subaddresses.

response time is about 0.3 ms. If the MSP cannot

accept another byte of data (e.g. while servicing an

internal int err upt), it ho lds th e clock line I2C_CL l ow to

force the transmitter into a wait state. The I

Master must read back the clock line to detect when

the MSP is ready to r ecei ve the next I

2

C transmission.

2

C Bus

The positions within a transmission where this may

happen are indicated by ’Wait’ in Section 3.1.3. The

maximum wait period of the MSP during normal operation mode is less than 1 ms.

3.1.1. Internal Hardware Error Handling

In case of any hardware problems (e.g. interruption of

the power supply of the MSP), the MSP’s wait period is

extended to 1.8 ms. After this time period elapses, the

MSP releases data and clock lines.

Indication and solving the error status:

To indicate the error status, the remaining acknowledge bits of the actual I

Additionally, bit[14] of CONTROL is set to one. The

MSP can then be r eset via the I

2

C-protocol will be left high.

2

C bus by transmitting

the RESET condition to CONTROL.

Indication of reset:

Besides the possibility of hardware reset, the MSP can

also be reset by means of the RE SET bit in the CONTROL register by the controller via I

Due to the architecture o f the MS P 34x5G, the IC cannot react immediately to an I

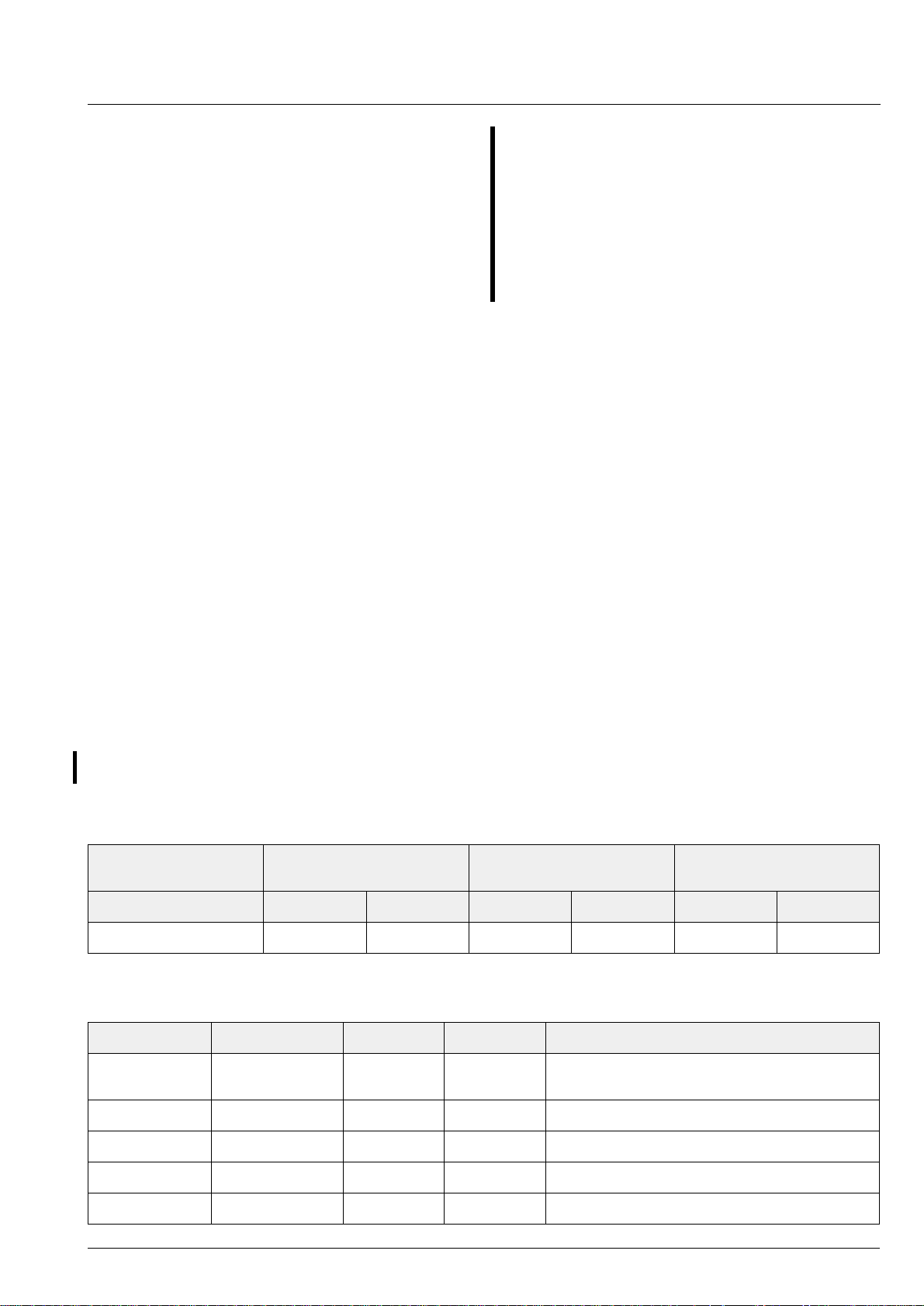

Table 3–1: I

ADR_SEL Low

Mode Write Read Write Read Write Read

MSP device address 80

2

C Bus Device Addresses

2

C bus.

2

C request. The typical

(connected to DVSS)

hex

81

hex

Any reset, even caused by an unstable reset line etc.,

is indicated in bit[15] of CONTROL.

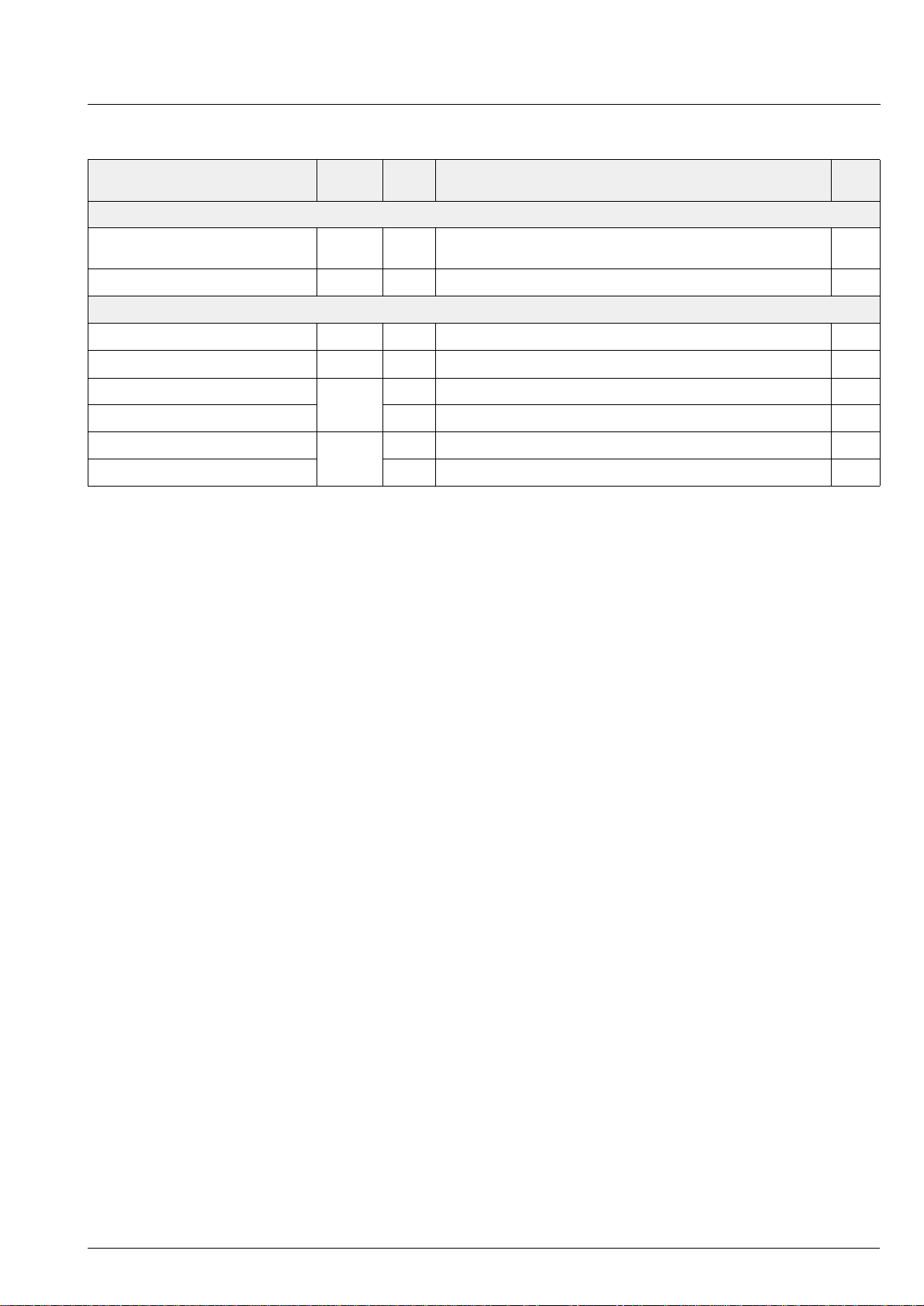

2

A general timing diagram of the I

C bus is shown in

Fig. 4–27 on page 61.

High

(connected to DVSUP)

84

hex

85

hex

88

hex

Left Open

89

Table 3–2: I2C Bus Subaddresses

Name Binary Value Hex Value Mode Function

CONTROL 0000 0000 00 Read/Write Write: Software reset of MSP (see Table 3–3)

Read: Hardware error status of MSP

WR_DEM 0001 0000 10 Write write address demodulator

hex

RD_DEM 0001 0001 11 Write read address demodulator

WR_DSP 0001 0010 12 Write write address DSP

RD_DSP 0001 0011 13 Write read address DSP

Micronas 15

MSP 34x5G PRELIMINARY DATA SHEET

3.1.2. Description of CONTROL Register

Table 3–3: CONTROL as a Write Register

Name Subaddress Bit[15] (MSB) Bits[14:0]

CONTROL 00

hex

1 : RESET

0 : normal

0

Table 3–4: CONTROL as a Read Register

Name Subaddress %LW>@06% Bit>@ BitV>@

CONTROL 00

hex

RESET status after last reading of

CONTROL:

0 : no reset occured

Internal hardware status:

0 : no error occured

1 : internal error occured

not of interest

1 : reset occured

Reading of CONTROL will reset the bits[15,14] of CONTROL. After Powe r-on,

bit[15] of CONTROL will be set; it must be

read once to be reset.

3.1.3. Protocol Description

Write to DSP or Demodulator

Swrite

device

address

Wait

ACK sub-addr ACK addr-byte

high

ACK addr-byte

low

ACK data-byte

high

ACK data-byte

low

ACK P

Read from DSP or Demodulator

Swrite

device

address

Wait

ACK sub-addr ACK addr-byte

high

ACK addr-byte

low

ACK S read

device

address

Wait

ACK data-byte-

high

ACK data-byte

Write to Control Register

Swrite

device

address

ACK sub-addr ACK data-byte

high

ACK data-byte

low

ACK P

Wait

Read from Control Register

Swrite

device

address

Wait

Note: S = I

P = I

ACK 00hex ACK S read

2

C-Bus Start Condition from master

2

C-Bus Stop Condition from master

device

address

Wait

ACK data-byte-

high

ACK data-byte

low

NAK P

ACK = Acknowledge-Bit: LOW on I2C_DA from slave (= MSP, light gray) or master (= controller, dark gray)

NAK = Not Acknowledge-Bit: HIGH on I2C_DA from master (dark gray) to indicate ‘End of Read’

or from MSP indicating internal error state

2

Wait = I

C-Clock line is held low, while the MSP is processing the I2C command.

This waiting time is max. 1 ms

NAK P

low

16 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

I2C_DA

1

0

S P

I2C_CL

Fig. 3 –1: I2C bus protocol (MSB first; data must be stable while clock is high)

3.1.4. Proposals for General MSP 34x5G

2

I

C Telegrams

3.1.4.1. Symbols

3.2. Start-Up Sequence:

Power-Up and I

After POWER-ON or RE SET (s ee F ig. 4–26), the IC is

in an inactive state. All registers are in the Res et posi-

daw write device address (80

dar read device address (81

< Start Condition

hex

hex

, 85

hex

hex

or 88

or 89

hex

hex

)

)

tion (see Table 3–5 and Table 3–6), the analog outputs

are muted. The controll er has to initialize all register s

for which a non-default setting is necessary.

, 84

> Stop Condition

aa Address Byte

dd Data Byte

3.3. MSP 3 4x5 G Programmin g Interf ace

2

C-Controlling

3.1.4.2. Write Telegr ams

<daw 00 d0 00> write to CONTROL register

<daw 10 aa aa dd dd> wr ite data into demodulator

<daw 12 aa aa dd dd> write data into DSP

3.1.4.3. Read Telegrams

<daw 00 <dar dd dd> read data from

CONTROL register

<daw 11 aa aa <dar dd dd> read data from demodulator

<daw 13 aa aa <dar dd dd> read data from DSP

3.1.4.4. Examples

<80 00 80 00> RESET MSP statically

<80 00 00 00> Clear RESET

<80 10 00 20 00 03> Set demodulator to stand. 03

<80 11 02 00 <81 dd dd> Read STATUS

<80 12 00 08 01 20> Set loudspeaker channe l

source to NICAM and

Matrix to STEREO

hex

3.3.1. User Registers Overview

The MSP 34x5G is controlled by means of user registers. The complete list of all user regist ers ar e given in

Table 3–5 and Table 3–6. The registers are partitioned

into the Demodulator section (Subaddress 10

writing, 11

ing sections (Subaddress 12

for reading) and the Baseband Process -

hex

for writing, 13

hex

hex

hex

for

for

reading).

Write and rea d registers are 16 bit wide, whereby the

MSB is denoted bit[15]. Transmissions via I

2

C bus have

to take place in 16-bit words (two byte transfers, with the

most significant byte transferred first). All write register s,

except the demodulator write registers are readable.

Unused parts of the 16-bit write registers must be zero.

Addresses not given in this table must not be

accessed.

For reasons of software compatibility to the

MSP 34xxD, a Manual /Com patibi li ty M ode i s available.

More read and wri te registers toge ther with a detailed

description can be found in “Appendix B: Manual/Compatibility Mode” on page 77.

More examples of typical application protocols are

listed in Section 3.4. “Programming Tips” on page 37.

Micronas 17

MSP 34x5G PRELIMINARY DATA SHEET

.

Table 3–5: List of MSP 34x5G Write Registers

Write Register Address

(hex)

I2C Sub-Address = 10

; Registers are not readable

hex

Bits Description and Adjustable Range Reset See

Page

STANDARD SELECT 00 20 [15:0] Initial Programming of the Demodulator 00 00 21

2

MODUS 00 30 [15:0] Demodulator, Automatic and I

2

I

S CONFIGURATION 00 40 [15:0] Configuration of I2S options 00 00 24

I2C Sub-Address = 12

; Registers are all readable by using I2C Sub-Address = 13

hex

S options 00 00 23

hex

Volume loudspeaker channel 00 00 [15:8] [+12 dB ... −114 dB, MUTE] MUTE 29

Volume / Mode loudspeaker channel [7:0] 1/8 dB Steps,

Reduce Volume / Tone Control / Compromise /

00

hex

Dynamic

Balance loudspeaker channel [L/R] 00 01 [15:8] [0..100 / 100 % and 100 /0..100 %]

[

−127..0 / 0 and 0 / −127..0 dB]

100 %/100 % 30

Balance mode loudspeaker [7:0] [Linear /logarithmic mode] linear mode

Bass loudspeaker channel 00 02 [15:8] [

Treble loudspeaker channel 00 03 [15:8] [

Loudness loudspeaker channel 00 04 [15:8] [0 dB ...

+20 dB ... −12 dB] 0 dB 31

+15 dB ... −12 dB] 0 dB 31

+17 dB] 0 dB 32

Loudness filter characteristic [7:0] [NORMAL, SUPER_B AS S] NORMAL

Spatial effect strength loudspeaker ch. 00 05 [15:8] [

−100 %...OFF...+100 %] OFF 33

Spatial effect mode/customize [7:0] [SBE, SBE+P SE ] SBE+PSE

Volume SCART1 output channel 00 07 [15:8] [

Loudspeaker source select 00 08 [15:8] [FM/AM, NICAM, SCART , I

+12 dB ... −114 dB, MUTE] MUTE 34

2

S1, I2S2] FM/AM 28

Loudspeaker channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO...] SOUNDA 28

2

SCART1 source select 00 0A [15:8] [FM/AM, NICAM, SCART, I

S1, I2S2] FM/AM 28

SCART1 channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO...] SOUNDA 28

2

S source select 00 0B [15:8] [FM/AM, NICAM, SCART, I2S1, I2S2] FM/AM 28

I

2

S channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO...] SOUNDA 28

I

2

Quasi-peak detector source select 00 0C [15:8] [FM/AM, NICAM, SCART, I

S1, I2S2] FM/AM 28

Quasi-peak detector matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO...] SOUNDA 28

Prescale SCART input 00 0D [15:8] [00

Prescale FM/AM 00 0E [15:8] [00

hex

hex

]00

hex

... 7F

]00

hex

hex

hex

27

26

... 7F

FM matrix [7:0] [NO_MAT, GSTERERO, KSTEREO] NO_MAT 27

... 7F

Prescale NICAM 00 10 [15:8] [00

2

Prescale I

S2 00 12 [15:8] [00

hex

hex

] (MSP 3410G, MSP 3450G only) 00

hex

... 7F

]10

hex

ACB : SCART Switches a. D_CTR_I/O 00 13 [15:0] Bits[15:0] 00

... 7F

]/[00

Beeper 00 14 [15:0] [00

2

Prescale I

S1 00 16 [15:8] [00

hex

hex

... 7F

hex

]10

... 7F

hex

hex

]0/035

hex

hex

hex

hex

hex

27

27

34

27

Automatic Volume Correction 00 29 [15:8] [off, on, decay time] off 30

18 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

Table 3–6: List of MSP 34x5G Read Registers

Read Register Address

(hex)

I2C Sub-Address = 11

; Registers are not writable

hex

STANDARD RESULT 00 7E [15:0] Result of Automatic Standard Detection (see Table 3–8)

Bits Description and Adjus table Range See

Page

25

(MSP 3415G, MSP 3440G, MSP 3455G only)

STATUS 02 00 [15:0] Monitoring of internal settings e.g. Stereo, Mono, Mute etc. 25

I2C Sub-Address = 13

Quasi-peak readout left 00 19 [15:0] [00

Quasi-peak readout right 00 1A [15:0] [00

MSP hardware version code 00 1E [15:8] [00

MSP major revision code [7:0] [00

MSP product code 00 1F [15:8] [00

MSP ROM version code [7:0] [00

; Registers are not writable

hex

... 7FFF

hex

... 7FFF

hex

... FF

hex

... FF

hex

... FF

hex

... FF

hex

] 16 bit two’s complement 36

hex

] 16 bit two’s complement 36

hex

]36

hex

]36

hex

]36

hex

]36

hex

Micronas 19

MSP 34x5G PRELIMINARY DATA SHEET

3.3.2. Description of User Registers

Table 3–7: Standard Codes for STANDARD SELECT register

MSP Standard Code

(Data in hex)

TV Sound Standard Sound Carrier

Frequencies in MHz

MSP 34x5G Version

Automatic Standard Detection

00 01 Starts Automatic Standard Detection and

all

sets detected standard

Standard Selection

00 02 M-Dual FM-Stereo 4.5/4.724212 3405, -15, -25, -45, -55

00 03 B/G-Dual FM-Stereo

00 04 D/K1-Dual FM-Stereo

00 05 D/K2-Dual FM-Stereo

00 06 D/K -FM-Mono with HDEV3

1)

2)

2)

3)

, not detectable by

5.5/5.7421875 3405, -15, -55

6.5/6.2578125

6.5/6.7421875

6.5

Automatic Standard Detection, for China

3)

HDEV3

SAT-Mono (i.e. Eutelsat, s. Table 6–18)

00 07 D/K3-Dual FM-Stereo 6.5/5.7421875

00 08 B/G-NICAM-FM

1)

5.5/5.85 3415, -55

00 09 L-NICAM-AM 6.5/5.85

00 0A I-NICAM-FM 6.0/6.552

00 0B D/K-NICAM-FM

2)

00 0C D/K-NICAM-FM with HDEV2

4)

, not detectable by

6.5/5.85

6.5/5.85

Automatic Standard Detection, for China

00 0D D/K-NICAM-FM with HDEV3

3)

, not detectable by

6.5/5.85

Automatic Standard Detection, for China

00 20 BTSC-Stereo 4.5 3425, -45, -55

00 21 BTSC-Mono

+ SAP

00 30 M-EIA-J Japan Stereo 4.5 3425, -45, -55

00 40 FM-Stereo Radio with 75

µs Deemphasis 10.7 3425, -45, -55

00 50 SAT-Mono (see Table6–18) 6.5 3405, -15, -55

00 51 SAT-Stereo (see Table6–18) 7.02/7.20

00 60 SAT ADR (Astra Digital Radio) 6.12

1)

In case of Automatic Sound Select, the B/G-codes 3

2)

In case of Automatic Sound Select, the D/K-codes 4

3)

HDEV3: Max. FM deviation must not exceed 540 kHz

4)

HDEV2: Max. FM deviation must not exceed 360 kHz

hex

hex

and 8

, 5

hex

are equivalent.

hex

, 7

, and B

hex

are equivalent.

hex

20 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

3.3.2.1. STANDARD SELECT Register

The TV sound standard of the MSP 34x5G demodulator is determined by the STANDARD SELECT regis ter.

There are two ways to use the STANDARD SELECT

register:

– Setting up the demodulator for a TV sound standard

by sending the corresponding standard code with a

single I

2

C bus transmission.

– Starting the Automatic Standard Detection for ter-

restrial TV standards. This is the most comfortable

way to set up the demodulator (not for MSP 3435G).

Within 0.5 s the detection and setup of the actual TV

sound standard is performed. The detected standard can be read out of the STANDARD RESULT

register by the control processor. This feature is recommended for the primary setup of a TV set. Outputs should be muted during Automatic Standard

Detection.

The Standard Codes are listed in Table 3–7.

Selecting a TV sound standard via the STANDARD

SELECT register initializes the demodulator. This

includes: AGC-settings and carrier mute, tuning frequencies, FIR-filter se ttings, demodulation mode ( FM,

AM, NICAM), deemphasis and identification mode.

TV stereo sound standards that are unavailable for a

specific MSP version are processed in analog mono

sound of the standard. In that case, stereo or bil ingual

processing will not be possible.

For a complete setup of the TV sound processing from

analog IF input to the source selection, the transmi ssions as shown in Section 3.5. are necessary.

For reasons of software compatibility to the

MSP 34xxD, a Manual/ Comp ati bil it y mode i s available.

A detailed description of this mode can be found on

page 77.

3.3.2.2. Refresh of STANDARD SELECT Register

A general refresh o f t he ST A NDAR D S EL ECT register

is not allowed. However, the following method

enables watching the MSP 34x5G “alive” status and

detection of accidental resets (only versions B6 and

later):

– After Power-on, bit[15] of CONTROL will be set; it

must be read once to enable the reset-detection

feature.

– Reading of the CONTROL register and checking

the reset indicator bit[15] .

– If bit[15] is “0”, any refresh of the STANDARD

SELECT register is not allowed.

– If bit[15] is “1”, indicating a reset, a refresh of the

STANDARD SELECT register and all other MSPG

registers is required.

3.3.2.3. STANDARD RESULT Register

If Automatic Standard Detection is selected in the

STANDARD SELECT reg ister, status and result of the

Automatic Standard Detection process can be read out

of the STANDARD RESULT register. The possible

results are based on the mentioned Standard Code

and are listed in Table 3–8.

In cases where no sound standard h as been detected

(no standard present, too much noise, strong interferers, etc.) the STANDARD RESULT register contains

00 00

. In that case, the controller has to start further

hex

actions (for example set the standard according to a

preference list or by manual input).

As long as the STANDARD RESULT register contain s

a value greater than 07 FF

, the Automatic Standard

hex

Detection is still active. During this period, the MODUS

and STANDARD SELECT registe r must not be written.

The STATUS register will be updated when the Automatic Standard Detection has finished.

If a present sound standard is unavailable for a specific

MSP-version, it detects and switches to the analog

mono sound of this standard.

Example:

The MSPs 3425G and 3445G will detect a B/G-NICAM

signal as stand ard 3 and will switch to t he analog FMMono sound.

Micronas 21

MSP 34x5G PRELIMINARY DATA SHEET

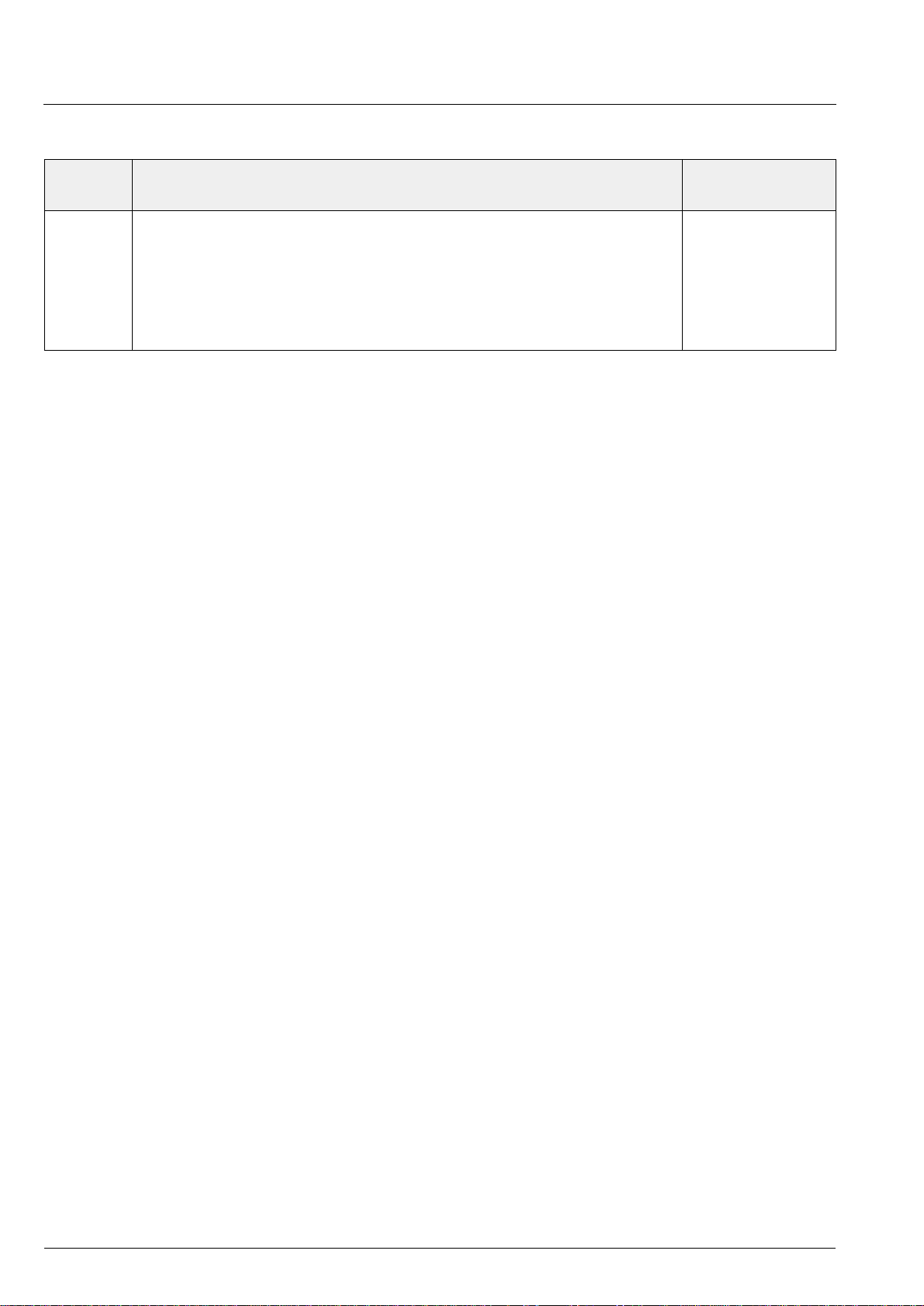

Table 3–8: Results of the Automatic Standard

Detection

Broadcasted Sound

Standard

Automatic Stan dard

Detection could not

STANDARD RESULT Register

Read 007E

0000

hex

hex

find a sound standard

B/G-FM 0003

B/G-NICAM 0008

I000A

FM-Radio 0040

M-Korea

M-Japan

M-BTSC

L-AM

D/K1

D/K2

D/K3

L-NICAM

D/K-NICAM

0002

0020

0030

0009

0004

0009

000B

hex

hex

hex

hex

(if MODUS[14,13]=00)

hex

(if MODUS[14,13]=01)

hex

(if MODUS[14,13]=10)

hex

(if MODUS[12]=0)

hex

(if MODUS[12]=1)

hex

(if MODUS[12]=0)

hex

(if MODUS[12]=1)

hex

Automatic Stan dard

Detection still active

>07FF

hex

22 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

3.3.2.4. Write Registers on I2C Subaddress 10

Table 3–9: Write registers on I2C subaddress 10

Register

Function Name

Address

00 20

hex

STANDARD SELECTION Register

Defines TV-Sound or FM-Radio Standard

bit[15:0] 00 01

00 02

start Automatic Standard Detection

hex

MSP Standard Codes (see Table 3–7)

hex

...

hex

00 30

hex

00 60

MODUS Register

Preference in Automatic Standard Detection:

bit[15] 0 undefined, must be 0

bit[14:13] detected 4.5 MHz carrier is interpreted as:

0 standard M (Korea)

1 standard M (BTSC)

2 standard M (Japan)

3 chroma carrier (M/N standards are ignored)

bit[12] detected 6.5 MHz carrier is interpreted as:

0 standard L (SECAM)

1 standard D/K1, D/K2, D/K3, or D/K NICAM

hex

hex

STANDARD_SEL

MODUS

1)

1)

General MSP 34x5G Options

bit[11:8] 0 undefined, must be 0

bit[7] 0/1 active/tristate state of audio clock output pin

AUD_CL_OUT

bit[6] I

2

S word strobe alignment

0 WS changes at data word boundary

1 WS changes one clock cycle in advance

bit[5] 0/1 master/slave mode of I

(= Master) in case of NICAM mode)

bit[4] 0/1 active/tristate state of I

bit[3] state of digital output pins D_CTR_I/O_0 and _1

0 active: D_CTR_I/O_0 and _1 are output pins

(can be set by means of the ACB register.

see also: MODUS[1])

1 tristate: D_CTR_I/O_0 and _1 are input pins

(level can be read out of STATUS[4,3])

bit[2] 0 undefined, must be 0

bit[1] 0/1 disable/enable STATUS change indication by means of

the digital I/O pin D_CTR_I/O_1

Necessary condition: MODUS[3] = 0 (active)

bit[0] 0/1off/on: Automatic Sound Select

1)

Valid at the next start of Automatic Standard Detection.

2

S interface (must be set to 0

2

S output pins

Micronas 23

MSP 34x5G PRELIMINARY DATA SHEET

2

Table 3–9: Write registers on I

C subaddress 10

, continued

hex

Register

Address

00 40

hex

Function Name

I2S CONFIGURATION Register

I2S_CONFIG

bit[15:1] 0 not used, must be set to “0”

bit[0] I2S_CL frequency and I

2

S data sample length for

master mode

0 2 x 16 bit (1.024 MHz)

1 2 x 32 bit (2.048 MHz))

24 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

3.3.2.5. Read Registers on I2C Subaddress 11

hex

Table 3–10: Read Registers on I2C Subaddress 11

Register

Function Name

Address

00 7E

hex

STANDARD RESULT Register

Readback of the detected TV sound or FM-Radio Standard

bit[15:0] 00 00

Automatic Standard Detection could not find

hex

a sound standard

00 02

MSP Standard Codes (see Table 3–8)

hex

...

02 00

hex

00 40

>07 FF

STATUS Register

hex

Automatic Standard Detection still active

hex

Contains all user relevant internal information about the status of the MSP

bit[15:10] undefined

bit[8] 0/1 “1” indicates bilingual sound mode or SAP present

(internally evaluated from received analog or digital identification signals)

hex

STANDARD_RES

STATUS

bit[7] 0/1 “1” indicates independent mono sound (only for

NICAM)

bit[6] 0/1 mono/stereo indication

(internally evaluated from received analog or digital identification signals)

bit[5,9] 00 analog sound standard (FM or AM) active

01 this pattern will not occur

10 digital sound (NICAM) available

11 bad reception condition of digital sound (NICAM) due

to:

a. high error rate

b. unimplemented sound code

c. data transmission only

bit[4] 0/1 low/high level of digital I/O pin D_CTR_I/O_1

bit[3] 0/1 low/high level of digital I/O pin D_CTR_I/O_0

bit[2] 0 detected secondary carrier (2nd A2 or SAP sub-carrier)

1 no secondary carrier detected

bit[1] 0 detected primary carrier (Mono or MPX carrier)

1 no primary carrier detect ed

bit[0] undefined

If STATUS change indication is activated by means of MODUS[1]: Each

change in the ST ATUS register sets the digital I/O pin D_CTR_I/O_1 to high

level. Reading the STATUS register resets D_CTR_I/O_1.

Micronas 25

MSP 34x5G PRELIMINARY DATA SHEET

3.3.2.6. Write Registers on I2C Subaddress 12

hex

Table 3–11: Write Registers on I2C Subaddress 12

Register

Function Name

Address

PREPROCESSING

00 0E

hex

FM/AM Prescale

bit[15:8] 00

hex

Defines the input prescale gain for the demodulated

... FM or AM signal

7F

hex

00

hex

off (RESET condition)

For all FM modes except satellite FM and AM-mode, the combinations of prescale value and FM deviation listed below lead to internal full scale.

FM mode

bit[15:8] 7F

48

30

24

18

13

hex

hex

hex

hex

hex

hex

28 kHz FM deviation

50 kHz FM deviation

75 kHz FM deviation

100 kHz FM deviation

150 kHz FM deviation

180 kHz FM deviation (limit)

hex

PRE_FM

FM high deviation mode (HDEV2, MSP Standard Code = C

bit[15:8] 30

14

hex

hex

150 kHz FM deviation

360 kHz FM deviation (limit)

hex

)

FM very high deviation mode (HDEV3, MSP Standard Code = 6 and D

bit[15:8] 20

1A

hex

hex

450 kHz FM deviation

540 kHz FM deviation (limit)

Satellite FM with adaptive deemphasis

bit[15:8] 10

hex

recommendation

AM mode (MSP Standard Code = 9)

bit[15:8] 7C

hex

recommendation for SIF input levels from

0.1 V

to 0.8 V

pp

pp

(Due to the AGC being switched on, the AM-output level

remains stable and independent of the actual SIF-level in

the mentioned input range)

hex

)

26 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

2

Table 3–11: Write Registers on I

C Subaddress 12

, continued

hex

Register

Address

(continued)

00 0E

hex

Function Name

FM Matrix Modes

FM_MATRIX

Defines the dematrix function for the demodulated FM signal

bit[7:0] 00

01

02

03

hex

hex

hex

hex

no matrix (used f o r bi lin gu al and un ma trixed stereo sound)

German stereo (Standard B/G)

Korean stereo (also used for BTSC, EIA-J and FM Radio)

sound A mono (left and right channel contain the mono

sound of the FM/AM mono carrier)

04

hex

sound B mono

In case of Automatic Sound Select = on, the FM Matrix Mode is set automati-

cally . Writing to the FM/AM prescale register (00 0E

In order not to disturb the automatic process, the low part of any I

high part) is still allowed.

hex

2

C transmission to this register is ignored. Therefore, any FM-Matrix readback values may

differ from data written previously.

In case of Automatic Sound Select = off, the FM Matrix Mode must be set as

shown in Table 6–17 of Appendix B.

To enable a Forced Mono Mode for all analog stereo systems by overriding the

internal pilot or id en ti fica ti on evaluation, the following steps must be tr an sm itte d:

1. MODUS with bit[0] = 0 (Automatic Sound Select off)

2. FM Presc./Matrix with FM Matrix = Sound A Mono (SAP: Sound B Mono)

3. Select FM/AM source channel, with channel matrix set to “Stereo” (transparent)

00 10

00 16

00 12

00 0D

hex

hex

hex

hex

NICAM Prescale

Defines the input prescale value for the digital NICAM signal

bit[15:8] 00

hex

... 7F

prescale gain

hex

examples:

00

20

5A

7F

hex

hex

hex

hex

off

0dB gain

9 dB gain (recommendation)

+12 dB gain (maximum gain)

I2S1 Prescale

I2S2 Prescale

Defines the input prescale value for digital I

bit[15:8] 00

hex

... 7F

prescale gain

hex

2

S input signals

examples:

00

10

7F

hex

hex

hex

off

0 dB gain (recommendation, RESET condition)

+18 dB gain (maximum gain)

SCART Input Prescale

Defines the input prescale value for the analog SCART input signal

PRE_NICAM

PRE_I2S1

PRE_I2S2

PRE_SCART

bit[15:8] 00

hex

... 7F

prescale gain

hex

examples:

00

19

7F

hex

hex

hex

off (RESET condition)

0dB gain (2 V

input leads to digital full scale)

RMS

+14 dB gain (400 mV

input leads to digital full scale)

RMS

Micronas 27

MSP 34x5G PRELIMINARY DATA SHEET

2

Table 3–11: Write Registers on I

C Subaddress 12

, continued

hex

Register

Function Name

Address

SOURCE SELECT AND OUTPUT CHANNEL MATRIX

Source for:

00 08

00 0A

00 0B

00 0C

hex

hex

hex

hex

Loudspeaker Output

SCART1 DA Output

2

S Output

I

Quasi-Peak Detector

bit[15:8] 0 “FM/AM”: demodulated FM or AM mono signal

1 “Stereo or A/B”: demodulator Stereo or A/B signal

(in manual mode, this source is identical to the NICAM

source in the MSP 3410D)

3 “Stereo or A”: demodul ato r Ste reo Soun d or

Language A (only defined for Automatic Sound Select)

4 “Stereo or B”: demodul ato r Ste reo Soun d or

Language B (only defined for Automatic Sound Select)

2 SCART input

5I

6I

2

S1 input

2

S2 input

SRC_MAIN

SRC_SCART1

SRC_I2S

SRC_QPEAK

00 08

00 0A

00 0B

00 0C

hex

hex

hex

hex

For demodulator sources, see Table 2–2.

Matrix Mode for:

Loudspeaker Output

SCART1 DA Output

2

I

S Output

Quasi-Peak Detector

bit[7:0] 00

10

20

30

hex

hex

hex

hex

Sound A Mono (or Left Mono) (RESET condition)

Sound B Mono (or Right Mono)

Stereo (transparent mode)

Mono (sum of left and right inputs divided by 2)

special modes are available (see Section 6.5.1. on page 89)

In Automatic Sound Select mode, the demodulator source channels are set

according to Table 2–2. Therefore, the matrix modes o f the correspondin g output channels should be set to “Stereo” (transparent).

MAT_MAIN

MAT_SCART1

MAT_I2S

MAT_QPEAK

28 Micronas

PRELIMINARY DATA SHEET MSP 34x5G

2

Table 3–11: Write Registers on I

C Subaddress 12

, continued

hex

Register

Function Name

Address

LOUDSPEAKER PROCESSING

00 00

hex

Volume Loudspeaker

bit[15:8] volume table with 1 dB step size

7F

hex

7E

hex

...

74

hex

73

hex

72

hex

...

02

hex

01

hex

00

hex

FF

hex

bit[7:5] higher resolution volume table

0

1

...

7

VOL_MAIN

+12 dB (maximum volume)

+11 dB

+1dB

0dB

−1dB

−113 dB

−114 dB

Mute (RESET condition)

Fast Mute (needs about 75 ms until the signal is completely ramped down)

+0dB

+0.125 dB increase in addition to the volume table

+0.875 dB increase in addition to the volume table

bit[4] 0 must be set to 0

bit[3:0] clipping mod e

0 reduce volume

1 reduce tone control

2 compromise

3 dynamic

With large scale input signals, positive volume settings may lead to signal clipping.

The MSP 34x5G loudspeaker and headphone volume function is divided into a

digital and an analog section. With Fast Mute, volume is reduced to mute position by digital volume only. Analog volume is not changed. This reduces any

audible DC plops. To turn volume on again, the volume step that has been used

before Fast Mute was activated must be transmitted.

If the clipping mode is set to “reduce volume”, the following rule is used: To

prevent severe clipping effects with bass, treble, or equalizer boosts, the internal volume is automatically limited to a level where, in combination with either

bass, treble, or equalizer setting, the amplification does not exceed 12 dB.

If the clipping mode is “reduce tone control”, the bass or treble value is

reduced if amplification exceeds 12 dB. If the equalizer is switched on, the gain

of those bands is reduced, where amplification together with volume exceeds

12 dB.

If the clipping mode is “compromise”, the bass or treble value and volume are

reduced half and half if amplification exceeds 12 dB. If the equalizer is switched

on, the gain of those bands is reduced half and half, where amplification

together with volume exceeds 12 dB.

If the clipping mode is “dynamic”, volume is reduced automatically if the signal

amplitudes would exceed

−2 dBFS within the IC.

Micronas 29

MSP 34x5G PRELIMINARY DATA SHEET

2

Table 3–11: Write Registers on I

C Subaddress 12

, continued

hex

Register

Address

00 29

hex

00 01

hex

Function Name

Automatic Volume Correction (A VC) Loudspeaker Channel

bit[15:12] 00

08

bit[11:8] 08

04

02

01

hex

hex

hex

hex

hex

hex

AVC off (and reset internal variables)

AVC on

8 sec decay time

4 sec decay time (recommended)

2 sec decay time

20 ms decay time (should be used for approx. 100 ms

AVC

AVC_DECAY

after channel change)

Note: AVC should not be used in any Dolby Prologic mode (with DPL35xx),

except in PANORAMA or 3D-PANORAMA mode, when only the loudspeaker

output is active.

Balance Loudspeaker Channel

BAL_MAIN

bit[15:8] Linear Mode

7F

7E

hex

hex

Left muted, Right 100%

Left 0.8%, Right 100%

...

01

00

FF

hex

hex

hex

Left 99.2%, Right 100%

Left 100%, Right 100%

Left 100%, Right 99.2%

...

82

81

hex

hex

Left 100%, Right 0.8%

Left 100%, Right muted

bit[15:8] Logarithmic Mode

7F

7E

hex

hex

Left −127 dB, Right 0 dB

Left −126 dB, Right 0 dB

...

01

00

FF

hex

hex

hex

Left −1 dB, Right 0 dB

Left 0 dB, Right 0 dB

Left 0 dB, Right −1dB

...

81

80

hex

hex

Left 0 dB, Right −127 dB

Left 0 dB, Right −128 dB

bit[7:0] Balance Mode

00

01

hex

hex

linear

logarithmic

Positive balance settings reduce the left channel without affecting the right

channel; negative settings reduce the right channel leaving the left channel

unaffected.

30 Micronas

Loading...

Loading...