Micronas Intermetall MSP3400D, MSP3410D Datasheet

MSP 3400D,

MSP 3410D

Multistandard

Sound Processors

Edition May 14, 1999

6251-482-2PD

PRELIMINARY DATA SHEET

MICRONAS

MICRONAS

MSP 34x0D PRELIMINARY DATA SHEET

Contents

Page Section Title

5 1. Introduction

5 1.1. Common Features of MSP 34x0D

5 1.2. Specific Features of MSP 3410D

6 2. Basic Features of the MSP 34x0D

6 2.1. Demodulator and NICAM Decoder Section

6 2.2. DSP Section (Audio Baseband Processing)

6 2.3. Analog Section

7 3. Application Fields of the MSP 34x0D

7 3.1. NICAM plus FM/AM-Mono

7 3.2. German 2-Carrier System (Dual-FM System)

10 4. Architecture of the MSP 34x0D

10 4.1. Demodulator and NICAM Decoder Section

10 4.1.1. Analog Sound IF – Input Section

11 4.1.2. Quadrature Mixers

11 4.1.3. Low-pass Filtering Block for Mixed Sound IF Signals

12 4.1.4. Phase and AM Discrimination

12 4.1.5. Differentiators

12 4.1.6. Low-pass Filter Block for Demodulated Signals

12 4.1.7. High-Deviation FM Mode

12 4.1.8. FM Carrier Mute Function in the Dual-Carrier FM Mode

12 4.1.9. DQPSK Decoder

12 4.1.10. NICAM Decoder

13 4.2. Analog Section

13 4.2.1. SCART Switching Facilities

13 4.2.2. Stand-by Mode

13 4.3. DSP Section (Audio Baseband Processing)

13 4.3.1. Dual-Carrier FM Stereo/Bilingual Detection

15 4.4. Audio PLL and Crystal Specifications

15 4.5. ADR Bus Interface

15 4.6. Digital Control Output Pins

2

16 4.7. I

S Bus Interface

17 5. I

2

C Bus Interface: Device and Subaddresses

18 5.1. Protocol Description

19 5.2. Proposal for MSP 34x0D I

2

C Telegrams

19 5.2.1. Symbols

19 5.2.2. Write Telegrams

19 5.2.3. Read Telegrams

19 5.2.4. Examples

2

20 5.3. Start-Up Sequence: Power-Up and I

C-Controlling

2 Micronas

PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

21 6. Programming the Demodulator and NICAM Decoder Section

21 6.1. Short-Programming and General Programming of the Demodulator Part

22 6.2. Demodulator Write Registers: Table and Addresses

22 6.3. Demodulator Read Registers: Table and Addresses

23 6.4. Demodulator Write Registers for Short-Programming: Functions and Values

23 6.4.1. Demodulator Short-Programming

24 6.4.2. AUTO_FM/AM: Automatic Switching between NICAM and FM/AM-Mono

25 6.5. Demodulator Write Registers for the General Programming Mode: Functions and Values

25 6.5.1. Register ‘AD_CV’

27 6.5.2. Register ‘MODE_REG’

28 6.5.3. FIR Parameter

30 6.5.4. DCO Registers

31 6.6. Demodulator Read Registers: Functions and Values

32 6.6.1. Autodetection of Terrestrial TV Audio Standards

32 6.6.2. C_AD_BITS

32 6.6.3. ADD_BITS [10...3] 0038

32 6.6.4. CIB_BITS

33 6.6.5. ERROR_RATE 0057

33 6.6.6. CONC_CT (for compatibility with MSP 3410B)

33 6.6.7. FAWCT_IST (for compatibility with MSP 3410B)

33 6.6.8. PLL_CAPS

33 6.6.9. AGC_GAIN

33 6.7. Sequences to Transmit Parameters and to Start Processing

35 6.8. Software Proposals for Multistandard TV Sets

35 6.8.1. Multistandard Including System B/G with NICAM/FM-Mono only

35 6.8.2. Multistandard Including System I with NICAM/FM-Mono only

35 6.8.3. Multistandard Including System B/G with NICAM/FM-Mono and German DUAL-FM

35 6.8.4. Satellite Mode

35 6.8.5. Automatic Search Function for FM Carrier Detecti on

hex

hex

MSP 34x0D

37 7. Programming the DSP Section (Audio Baseband Processing)

37 7.1. DSP Write Registers: Table and Add ress es

39 7.2. DSP Read Registers: Table and Addresses

40 7.3. DSP Write Registers: Functions and Values

40 7.3.1. Volume – Loudspeaker and Headphone Channel

41 7.3.2. Balance – Loudspeaker and Headphone Channel

41 7.3.3. Bass – Loudspeaker and Head pho ne Chann el

42 7.3.4. Treble – Loudspeaker and Headphone Channel

42 7.3.5. Loudness – Loudspea ke r and Head pho ne Chann el

43 7.3.6. Spatial Effects – Lo uds pe ak er Channel

44 7.3.7. Volume – SCART1 and SCART2 Channel

44 7.3.8. Channel Source Modes

45 7.3.9. Channel Matrix Modes

45 7.3.10. SCART Prescale

46 7.3.11. FM/AM Prescale

46 7.3.12. FM Matrix Modes (see also Table 4–1)

46 7.3.13. FM Fixed Deemphasis

Micronas 3

MSP 34x0D PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

46 7.3.14. FM Adaptive Deemphasis

47 7.3.15. NICAM Prescale

47 7.3.16. NICAM Deemphasis

47 7.3.17. I

47 7.3.18. ACB Register

48 7.3.19. Beeper

48 7.3.20. Identification Mode

48 7.3.21. FM DC Notch

48 7.3.22. Mode Tone Control

48 7.3.23. Automatic Volume Correction (AVC)

49 7.3.24. Subwoofer Channel

50 7.3.25. Equalizer Loudspeaker Channel

50 7.4. Exclusions for the Audio Baseband Features

50 7.5. Phase Relationship of Analog Outputs

50 7.6. DSP Read Registers: Functions and Values

50 7.6.1. Stereo Detection Register

51 7.6.2. Quasi-Peak Detector

51 7.6.3. DC Level Register

51 7.6.4. MSP Hardware Version Code

51 7.6.5. MSP Major Revision Code

51 7.6.6. MSP Product Code

51 7.6.7. MSP ROM Version Code

2

S1 and I2S2 Prescale

52 8. Differences between MSP 3400C, MSP 3400D, MSP 3410B, and MSP 3410D

55 9. Specifications

55 9.1. Outline Dimensions

57 9.2. Pin Connections and Short Descriptions

60 9.3. Pin Configurations

64 9.4. Pin Circuits (pin numbers refer to PLCC68 package)

66 9.5. Electrical Characteristics

66 9.5.1. Absolute Maximum Ratings

67 9.5.2. Recommended Operating Conditions

71 9.5.3. Characteristics

77 10. Application Circuit

79 11. Appendix A: MSP 34x0D Version History

80 12. Data Sheet History

4 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

Multistandard Sound Processors

Release Notes: The hardware description in this

document is valid for the MSP 34x0D version B3

and following versions. Revision bars indicate significant changes to the previous edition.

1. Introduction

The MSP 34x0D is designed as a single-chip Multistandard Sound Processor for applications in analog

and digital TV sets, satellite receivers, video recorders,

and PC cards.

The MSP 34x0D, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. It covers all European

TV standards (some examples are shown in Table3–1).

The MSP 3400D is fully pin and software-compatible

to the MSP 3410D, but is not able to decode NICAM. It

is also compatible to the MSP 3400C.

The IC is produced in submicron CMOS technology,

combined with high-performance digital signal processing. The MSP 34x0D is available in the following

packages: PLCC68, PSDIP64, PSDIP52, PQFP80,

and PLQFP64.

Note: The MSP 3410D version is fully downward-compatible to the MSP 3410B, the MSP 3400B, and the

MSP 3400C. To achieve full software-compatibility with

these types, the demodulator part must be programmed

as described in the data sheet of the MSP 3410B.

1.1. Common Features of MSP 34x0D

– AVC: Automatic Volume Correction

– Subwoofer Output

– 5-band graphic equalizer (as in MSP 3400C)

– Enhanced spatial effect (pseudostereo/basewidth

enlargement as in MSP 3400C)

– headphone channel with balance, bass, treble, loud-

ness

– balance for loudspeaker and headphone channels

in dB units (optional)

– D/A converters for SCART2 out

– improved oversampling filters (as in MSP 3400C)

– Four SCART inputs

– Full SCART in/out matrix without restrictions

– SCART volume in dB units (optional)

2

– Additional I

S input (as in MSP 3400C)

– New FM identification (as in MSP 3400C)

– Demodulator short programming

– Autodetection for terrestrial TV sound standards

– Improved carrier mute algorithm

– Improved AM demodulation

– ADR together with DRP 3510A

– Dolby Pro Logic together with DPL 351xA

– Reduction of necessary controlling

– Less external components

– Significant reduction of radiation

1.2. Specific Features of MSP 3410D

– All NICAM standards

– Precise bit-error rate indication

– Automatic switching from NICAM to FM/AM or vice-

versa

– Improved NICAM synchronization algorithm

Micronas 5

MSP 34x0D PRELIMINARY DATA SHEET

Loudspeaker

OUT

Subwoofer

OUT

Headphones

OUT

SCART1

OUT

SCART2

OUT

MSP 34x0D

2

2

2

2

1

2

35

ADR

I

2

SI2C

Sound IF 1

Sound IF 2

MONO IN

SCART1 IN

SCART2 IN

SCART3 IN

SCART4 IN

2

2

2

2

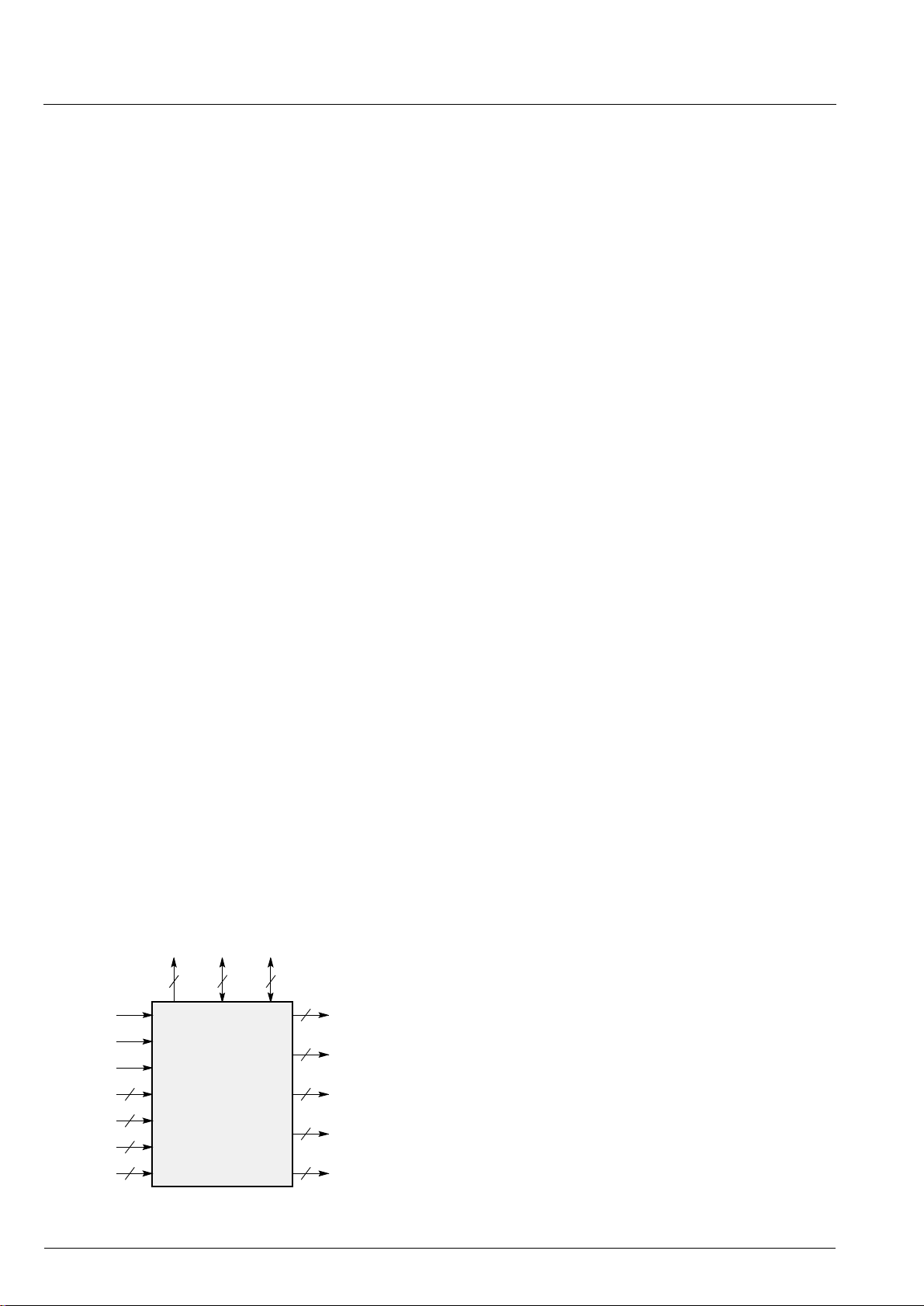

2. Basic Features of the MSP 34x0D

2.1. Demodulator and NICAM Decoder Section

The MSP 34x0D is designed to perform demodulation

of FM or AM-Mono TV sound. Alternatively, two-carrier

FM systems according to the German or Kor ean terrestrial specs or the satellite specs can be processed with

the MSP 34x0D.

Digital demodulation and decoding of NICAM-coded

TV stereo sound, is done only by the MSP 3410.

The MSP 34x0D offers a powerful feature to calculate

the carrier fie ld strength which can be used for automatic standard detection (te rrestrial) and search algorithms (satellite). The IC may be used in TV sets, as

well as in satellite tu ners and video rec orders. It offers

profitable multistandard ca pabil ity, including the following advantages:

– two selectable analog inputs (TV and SAT-IF

sources)

– Automatic Gain Control (AGC) for analog IF input.

Input range: 0.10–3V

pp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip

and is individually programmable

– easy realization of all digital NICAM standards (B/G,

I, L, and D/K) with MSP 3410.

– FM demodulation of all terrestrial standards (incl.

identification decoding )

– FM demodulation of all satellite standards

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search

algorithms and carrier mute function

– high-deviation FM-Mono mode (max. deviation:

approx.

±360 kHz)

2.2. DSP Section (Audio Baseband Processing)

– flexible selection of audio sources to be processed

2

– two digital input and one output interface via I

Sbus

for external DSP processors, featuring surround

sound, ADR etc.

– digital interface to process ADR (ASTRA Digital

Radio) together with DRP 3510A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components or controlling

– digitally performed FM identification decoding and

dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and

basewidth enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

2.3. Analog Section

– four selectable analog pairs of audio baseband

inputs (= four SCART inputs)

input level:

≤2V

input impedance:

RMS

≥25 kΩ

,

– one selectable analog mono input (i.e. AM sound):

input level:

≤2V

input impedance:

RMS

≥15 kΩ

,

– two high-quality A/D converters, S/N-Ratio: ≥85 dB

– 20 Hz to 20 kHz bandwidth for

SCART-to-SCART copy facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of fourfold oversampled D/A-converters

output level per channel: max. 1.4 V

RMS

output resistance: max. 5 kΩ

S/N-ratio: ≥85 dB at maximum volume

max. noise voltage in mute mode:

≤10 µV

(BW: 20 Hz ...16 kHz)

– two pairs of fourfold oversampled D/A converters

supplying two selectable pairs of SCART outputs.

output level per channel: max. 2 V

output resistance: max. 0.5 k

S/N-Ratio:

≥85 dB (20 Hz ... 16 kHz)

Ω,

RMS

,

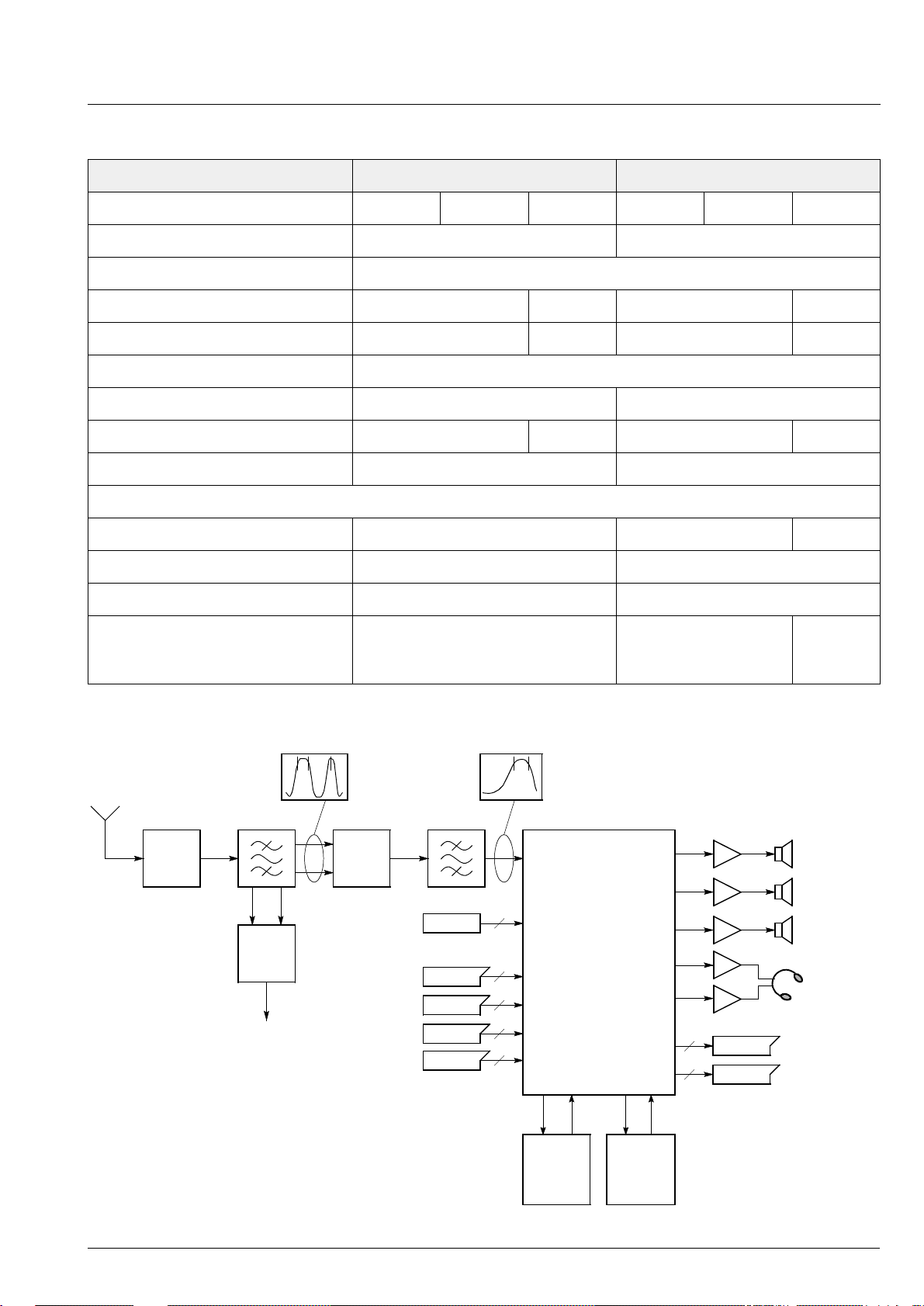

Fig. 2–1: Main I/O signals of the MSP 34x0D

6 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

3. Application Fields of the MSP 34x0D

In the following sections, a brief overview of the two

main TV sound standards, NICAM 728 and German

FM-Stereo, demonstrates the complex requirements of

a multistandard audio IC.

3.1. NICAM plus FM/AM-Mono

According to the British, Scandinavian, Spanish, and

French TV standards, high-quality stereo sound is

transmitted digitally. The systems allow two high-quality digital sound channel s to be added to the already

existing FM/AM channel. The sound coding follows the

format of the so-calle d Near Instanta neous Companding System (NICAM 728). Transmission is performed

using Differential Quadrature Phase Shift Keying

(DQPSK). Table 3–2 provides some specifications of

the sound coding (NI CAM); Table 3–3 offers an overview of the modulation parameters.

In the case of NICAM /FM (AM) mode, there are three

different audio channels available: NICAM A,

NICAM B, and FM/AM-Mono. NICAM A and B may

belong either to a stereo or to a dual-lang uage transmission. Information about operation mode and the

quality of the NICAM si gnal can be read by the CCU

via the control bus. In the cas e of low quality (h igh biterror rate), the CCU may decide to switch to the analog FM/AM-Mono sound. Alternatively, an automatic

NICAM-FM/AM switching may be applied.

3.2. German 2-Carrier System (Dual-FM System)

Since September 1981, stereo and dual-sound programs have been transmitted in Germany using the

2-carrier system. Sound transmission consists of the

already existing first sound carrier and a second sound

carrier additionally containing an identification signal.

More details of this standard are given in Tables 3–1

and 3–4. For D/K and M-Korea, very similar sys tems

are used.

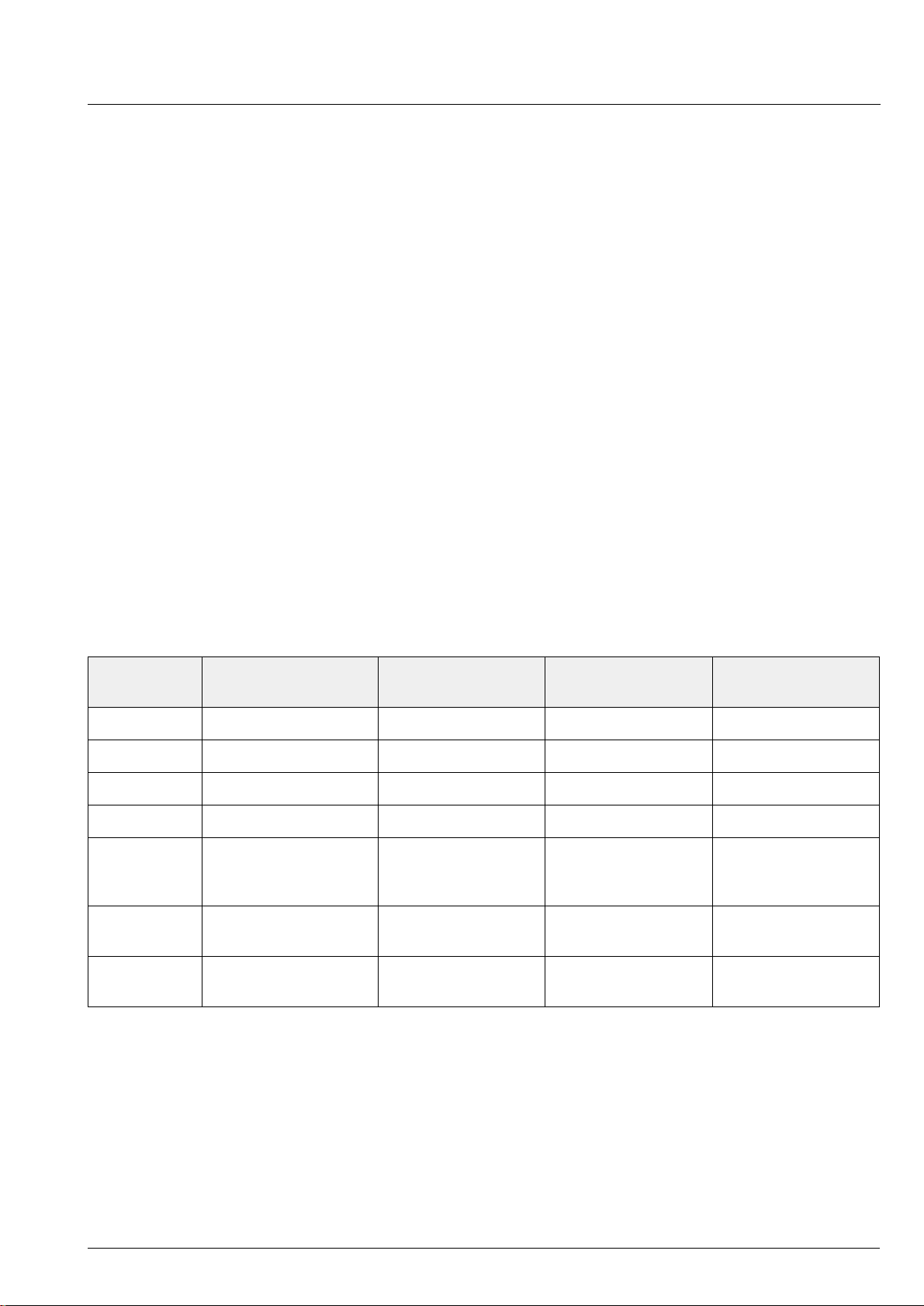

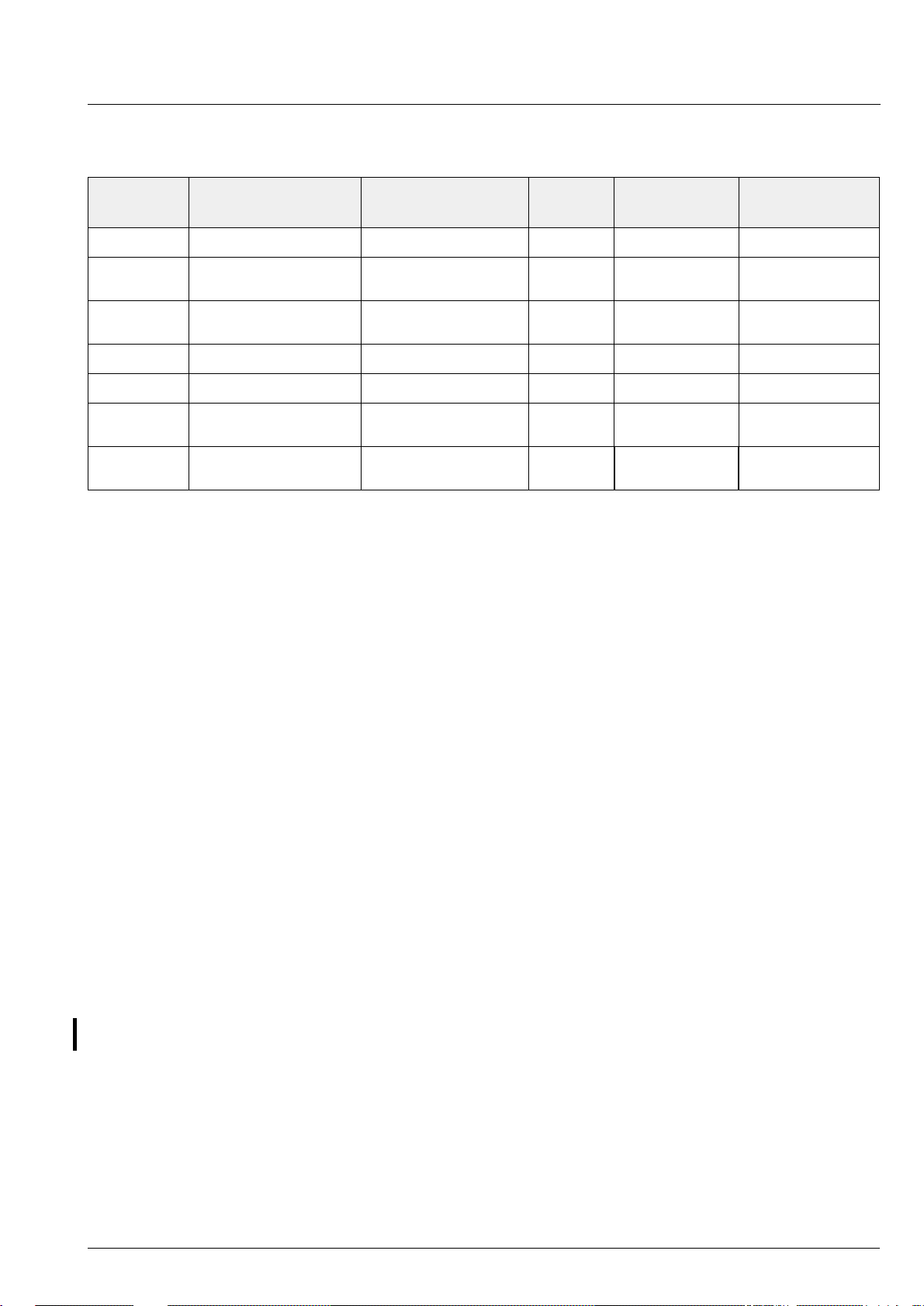

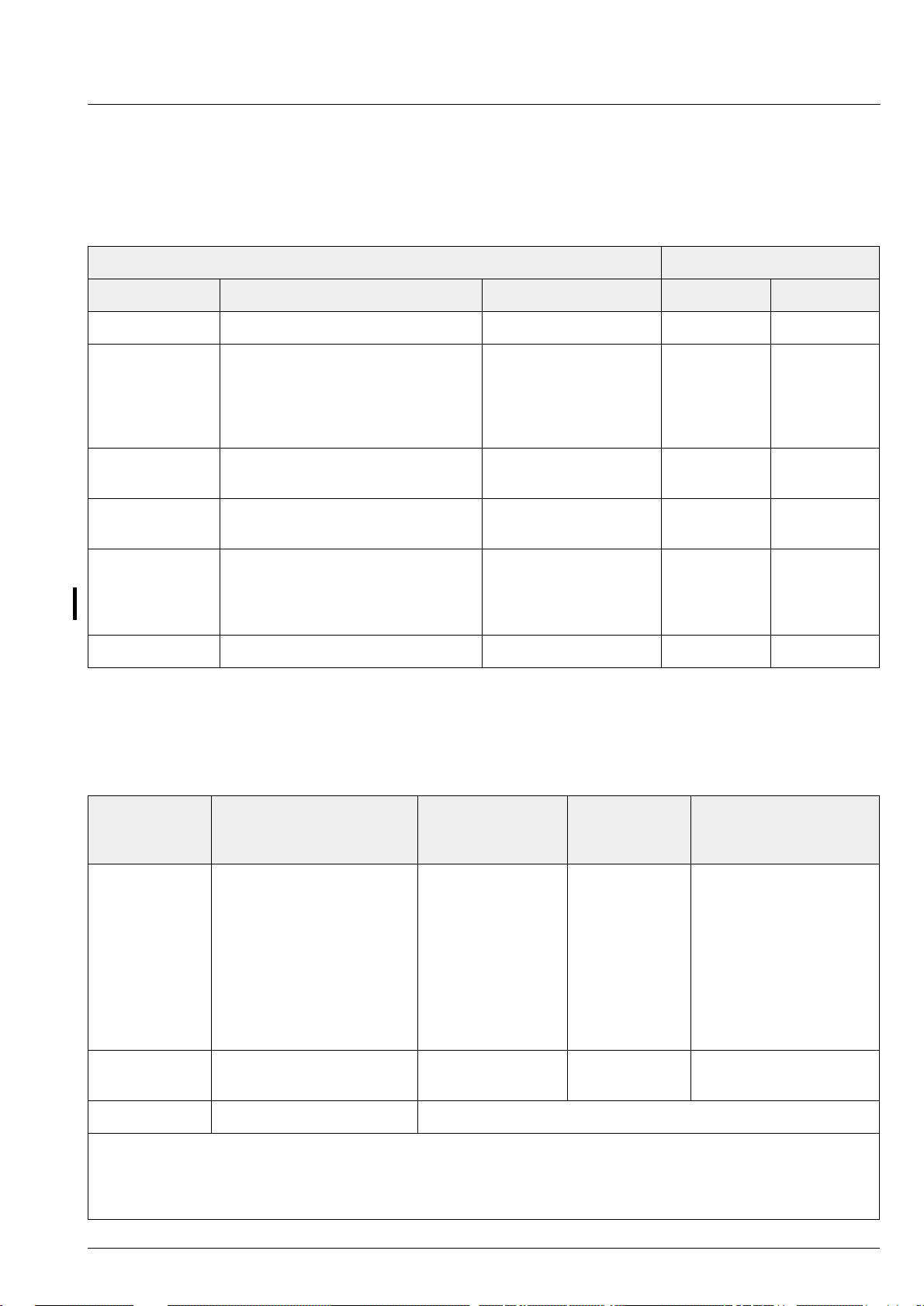

Table 3–1: TV standards

TV System Position of Sound

Carrier /MHz

B/G 5.5/5.7421875 FM-Stereo PAL Germany

B/G 5.5/5.85 FM-Mono/NICAM PAL Scandinavia, Spain

L 6.5/5.85 AM-Mono/NICAM SECAM-L France

I 6.0/6.552 FM-Mono/NICAM PAL UK

D/K 6.5/6.2578125 D/K1

6.5/6.7421875 D/K2

6.5/5.85 D/K-NICAM

M

M-Korea

Satellite

Satellite

Note: NICAM demodulation cannot be done with the MSP 3400D

4.5

4.5/4.724212

6.5

7.02/7.2

Sound

Modulation

FM-Stereo

FM-Mono/NICAM

FM-Mono

FM-Stereo

FM-Mono

FM-Stereo

Color System Country

SECAM-East USSR

Hungary

NTSC USA

Korea

PAL

PAL

Europe (ASTRA)

Europe (ASTRA)

Micronas 7

MSP 34x0D PRELIMINARY DATA SHEET

Table 3–2: Summary of NICAM 728 sound coding characteristics

Characteristics Values

Audio sampling frequency 32 kHz

Number of channels 2

Initial resolution 14 bits/sample

Companding characteristics near instantaneous, with compression to 10 bits/sample in 32-sample

(1 ms) blocks

Coding for compressed samples 2’s complement

Preemphasis CCITT recommendation J.17 (6.5 dB attenuation at 800 Hz)

Audio overload level +12 dBm measured at the unity gain frequency of the preemphasis

network (2 kHz)

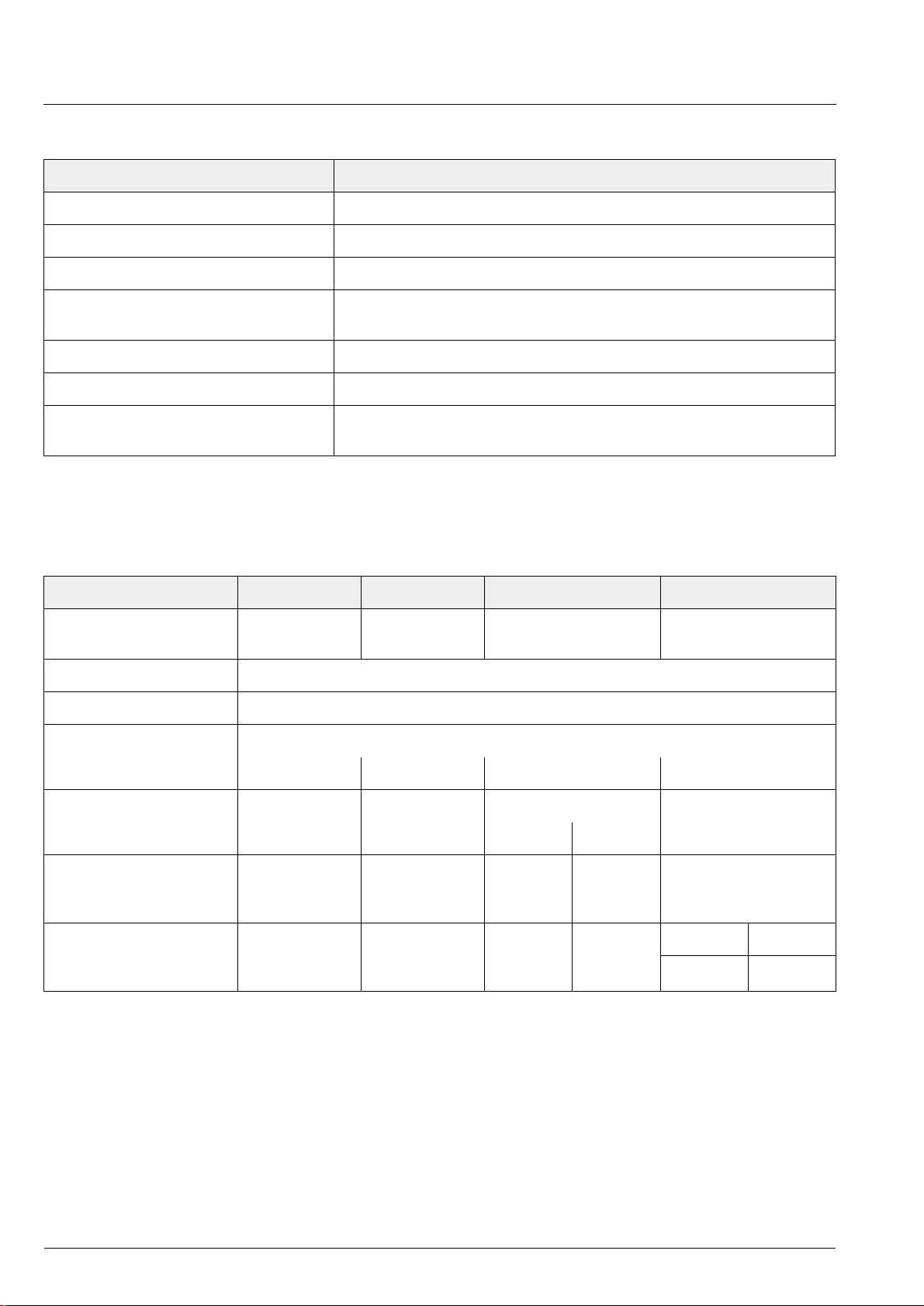

Table 3–3: Summary of NICAM 728 sound modulation parameters

Specification I B/G L D/K

Carrier frequency of

digital sound

Transmission rate 728 kbit/s

Type of modulation Differentially encoded quadrature phase shift keying (DQPSK)

Spectrum shaping

Roll-off factor

Carrier frequency of

analog sound component

Power ratio between

vision carrier and

analog sound carrier

Power ratio between

analog and modulated

digital sound carrie r

6.552 MHz 5.85 MHz 5.85 MHz 5.85 MHz

by means of Roll-off filters 1.0

1.0 0.4 0.4 0.4

6.0 MHz

FM mono

10 dB 13 dB 10 dB 16 dB 13 dB

10 dB 7 dB 17 dB 11 dB Hungary Poland

5.5 MHz

FM mono

6.5 MHz AM mono 6.5 MHz

FM-Mono

terrestrial cable

12 dB 7 dB

8 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

Table 3–4: Key parameters for B/G, D/K, and M 2-carrier sound system

Sound Carriers Carrier FM1 Carri er FM2

B/G D/K M B/G D/K M

Vision/sound power ratio 13 dB 20 dB

Sound bandwidth 40 Hz to 15 kHz

Preemphasis 50

Frequency deviation

µs75µs50µs75µs

±50 kHz ±25 kHz ±50 kHz ±25 kHz

Sound Signal Components

Mono transmission mono mono

Stereo transmission (L+R)/2 (L+R)/2 R (L

−R)/2

Dual-sound transmission language A language B

Identification of Transmission Mode on Carrier FM2

Pilot carrier frequency in kHz 54.6875 55.0699

Type of modulation AM

Modulation depth 50 %

Modulation frequency mono: unmodulated

33 34 39 MHz 59MHz

stereo: 117.5 Hz

dual: 274.1 Hz

According to the mixing characteristics

149.9 Hz

276.0 Hz

of the sound IF mixer, the sound IF

filter may be omitted.

SAW Filter Sound IF Filter

Sound

Tuner

Vision

Demodulator

Composite

Video

IF

Mixer

SCART

Inputs

Fig. 3–1: Typical MSP 34x0D application

Mono

SCART1

SCART2

SCART3

SCART4

1

2

2

2

2

MSP 34x0D

Dolby

Pro Logic

Processor

DPL35xxA

I2S2ADRI2S1

ADR

Decoder

DRP3510A

Loudspeaker

Subwoofer

Headphone

2

SCART1

2

SCART2

SCART

Outputs

Micronas 9

MSP 34x0D PRELIMINARY DATA SHEET

4. Architecture of the MSP 34x0D

Fig. 4–1 shows a simplified block diagram of the IC. Its

architecture is split into three main functional blocks:

1. demodulator and NICAM decoder section

2. digital signal processing (DSP) section performing

audio baseband processing

3. analog section containing two A/D-converters,

nine D/A-converters, and SCART Switching Facilities.

4.1. Demodulator and NICAM Decoder Section

4.1.1. Analog Sound IF – Input Section

The input pins AN A_IN1+, ANA_IN2+, and ANA_IN

offer the possibility to connect two different sound IF

(SIF) sources to the MSP 34x0D. By means of bit [8] of

AD_CV (see Table6–5 on page 25), either terrestrial

or satellite so und IF si gna ls c an b e s el ec ted . T h e a nalog-to-digital conversion of the preselected sound IF

signal is done by an A/D converter whose output is

used to control an analog autom atic gai n cir cuit (AGC)

providing an optimal level for a wide range of input levels. It is possible to switch between automatic gain

control and a fixed (setable) in put gain. In the optimal

case, the input range of the A/D converter is completely covered by the sound IF source. So me combinations of SAW filters and sound IF mixer ICs, however, show large picture components on their outputs.

In this case, filtering is recommended. It was found,

that the high-pass filters formed by the coupling capacitors at pins ANA_IN1+ and ANA_IN2+ and the IF

impedance (as s hown in the application dia gram) are

sufficient in most cases.

−

Sound IF

ANA_IN1+

ANA_IN2+

Mono

MONO_IN

SC1_IN_L

SCART1

SC1_IN_R

SC2_IN_L

SCART2

SC2_IN_R

SC3_IN_L

SCART3

SC3_IN_R

ADR-Bus I2S_DA_IN1

Demodulator

& NICAM

Decoder

A/D

A/D

I2S_DA_OUT

I2S_DA_IN2 I2S_WS

I2S Interface

I2S1/2L/R

FM1/AM

FM2

NICAM A

NICAM B

SUBWOOFER

IDENT

DSP

HEADPHONE L

HEADPHONE R

SCARTL

SCARTR

I2S_CL XTAL_OUTAUD_CL_OUT

I2S_L/R

LOUD-

SPEAKER L

LOUD-

SPEAKER R

D/A

D/A

D/A

D/A

D/A

SCART1_L

SCART1_R

SCART2_L

SCART2_R

D/A

D/A

D/A

D/A

XTAL_IN

Crystal PLL

2

D_CTR_OUT0/1

DACM_L

Loudspeaker

DACM_R

DACM_SUB

Subwoofer

DACA_L

Headphone

DACA_R

SC1_OUT_L

SCART 1

SC1_OUT_R

SC2_OUT_L

SCART 2

SC2_OUT_R

SC4_IN_L

SCART4

SC4_IN_R

SCART Switching Facilities

Fig. 4–1: Architecture of the MSP 34x0D

10 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

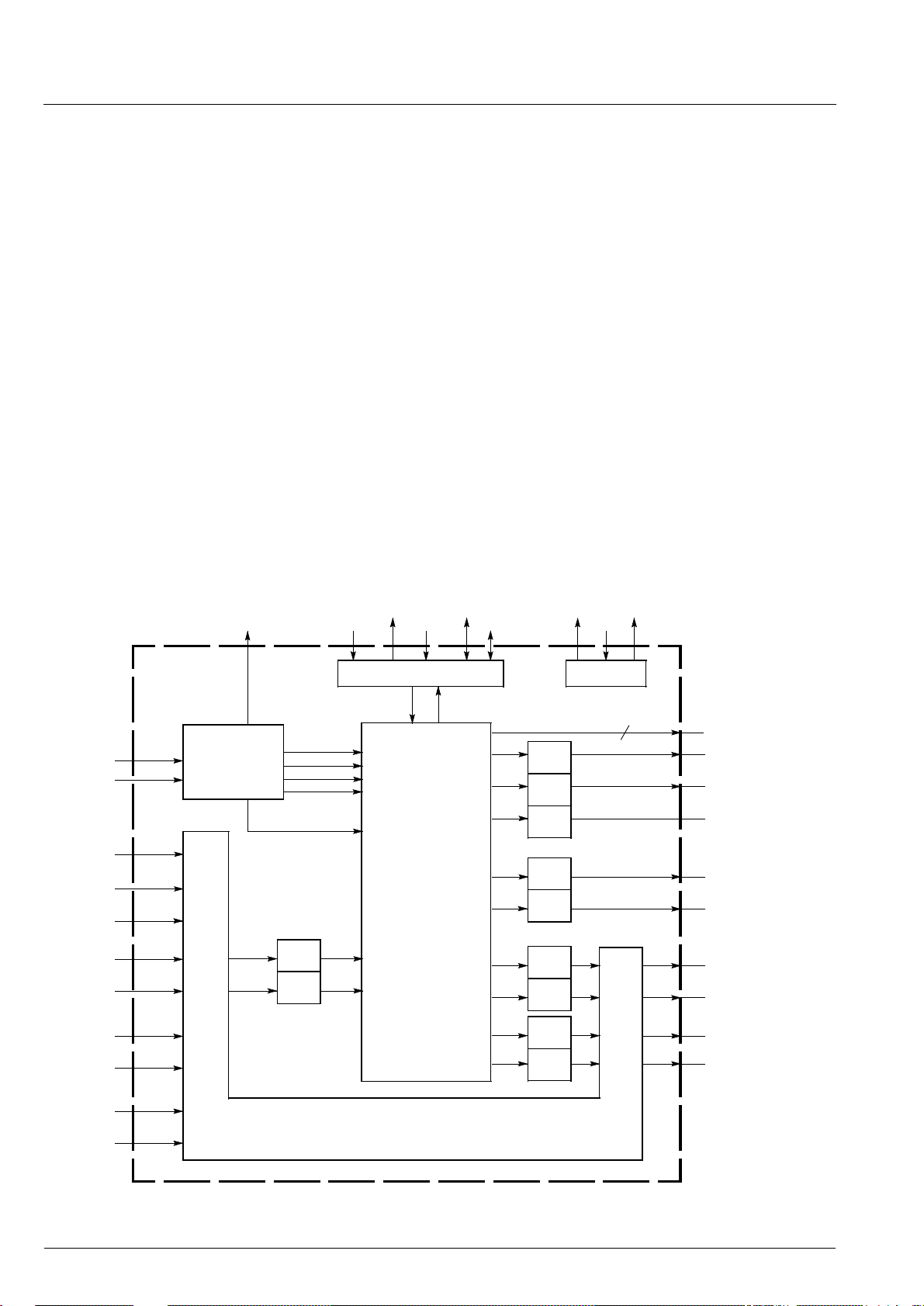

4.1.2. Quadrature Mixers

The digital input coming from the integrated A/D converter may contain audio information at a frequency

range of theoretically 0 to 9 MHz corresp onding to the

selected standards. By means of two programmable

quadrature mixers, two different audio sources, for

example NICAM and FM-Mono, may be shifted into

baseband position. In the following, the two main

channels are provided to process either:

– NICAM (MSP-Ch1) and FM/AM mono (MSP-Ch2)

simultaneously or, alternatively:

– FM-Mono (Ch2)

– FM2 (MSP-Ch1) and FM1 (MSP-Ch2).

Two programmable registers, to be divided up into a

low and a high part, determine frequency of the oscillator, which corresponds to the frequency of the desir ed

audio carrier.

4.1.3. Low-pass Filtering Block for Mixed Sound IF Signals

Data shaping and/or FM bandwidth limitation is performed by a linear phase fin ite impuls e r es po nse (FIR )

filter. Just like the oscillators’ frequency, the filter coefficients are programmable and are written into the IC by

the CCU via the control bus. Thus, for example, different NICAM versions can easily be i mplemented. Two

not necessarily different sets of coefficients are

required, one for MSP-Ch1 (NICAM or FM2) and one

for MSP-Ch2 (FM1 = FM-mono). In a corresponding

table several coefficient sets are proposed.

VREFTOP

ANA_IN1+

ANA_IN2+

ANA_IN-

FRAME

NICAMA

DCO2

AD_CV[7:1]

AGC

AD_CV[8]

Pins

Internal signal lines (see fig. 4–2)

Demodulator Write Registers

AD

DCO1

Oscillator

FIR1

Mixer

Lowpass

MSP sound IF channel 1

(MSP-Ch1: FM2, NICAM)

MSP sound IF channel 2

(MSP-Ch2: FM1, AM)

Mixer

Oscillator

DCO2

Lowpass

FIR2

Phase and

AM Discrimination

Amplitude

Phase and

AM Discrimination

MODE_REG[6]

Phase

Amplitude

Differentiator

Phase

DQPSK

Decoder

Differentiator

Carrier

Detect

AD_CV[9]

Carrier

Detect

MSP3410D only

NICAM

Decoder

MODE_REG[8]

Mute

Mute Lowpass

Lowpass

Mixer

ADR

NICAMA

NICAMB

FM2

IDENT

FM1/AM

Fig. 4–2: Architecture of demodulator and NICAM decoder section

Micronas 11

MSP 34x0D PRELIMINARY DATA SHEET

4.1.4. Phase and AM Discrimination

The filtered sound IF signals are demodulated by

means of the phase and amplitude discriminator block.

On the output, the phase and amplitude is available for

further processing. AM signals are derived from the

amplitude informati on, whereas the phase informa tion

serves for FM and NICAM (DQPSK) demodulation.

4.1.5. Differentiators

FM demodulation is completed by differentiating the

phase information output.

4.1.6. Low-pass Filter Block

for Demodulated Signals

The demodulated FM an d AM signals are further lowpass filtered and decimated to a final sampling frequency of 32 kHz. The usable bandwidt h of the final

baseband signals is about 15 kHz.

4.1.7. High-Deviation FM Mode

By means of MODE_REG [9], the maximum FM deviation can be extended to approximately

Since this mode can be applied only for the MSP

sound IF channel 2, the correspondi ng matr ices in the

baseband processing must be set to sound A. Apart

from this, the coefficient sets 380 kHz FIR2 or 500 kHz

FIR2 must be chosen for the FIR2. In relat ion to the

normal FM mode, the audio level of the high-deviation

mode is reduced by 6 dB. The FM prescaler should be

adjusted accordi ngly. In h igh-deviation FM mode, neither FM-Stereo nor FM iden tification nor NICAM processing is possible simultaneously.

±360 kHz.

4.1.8. FM Carrier Mute Function in the Dual-Carrier FM Mode

To prevent noise effects or FM identific ation problems

in the absence of one of the two FM carriers, the

MSP 34x0D offers a carrier detection feature, which

must be activated by means of AD_CV[9]. If no FM

carrier is available at th e MSPD channel 1, the co rresponding channel FM2 is muted. If no FM carrier is

available at the MSPD channel 2, the corresponding

channel FM1 is muted.

4.1.9. DQPSK Decoder

In case of NICAM mode, the phase samples are

decoded according the DQPSK-coding scheme. The

output of this block contains the original NICAM bitstream.

4.1.10. NICAM Decoder

Before any NICAM decoding can star t, the MSP must

lock to the NICAM frame structure by searching and

synchronizing to the so-called frame alignment words

(FAW).

To recon struct the original digital so und samples, the

NICAM bitstream has to be descrambled, deinterleaved, and rescaled. Also, bit-error detection an d correction (concealment) is performed in this block.

To facilitate the Central Control Unit CCU to switch the

(e.g.) TV set to the actual sou nd mode, control information on the NICAM mode and bit error rate are supplied by the NICAM decoder. It can be read ou t via th e

2

C bus.

I

An automatic switching facility (AUTO_FM) between

NICAM and FM/AM reduces the amount of

CCU instructions in case of bad NICAM reception.

12 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

4.2. Analog Section

4.2.1. SCART Switching Facilities

The analog input and output sections include full matrix

switching facilities, which are shown in Fig. 4–3. To

design a TV set with four pairs of SCART inputs and

two pairs of SCART outputs, no external switching

hardware is required.

The switches are control led by the ACB bits define d in

the audio processi ng interface (see section 7.3 .18. on

page 47).

SCART_IN

SC1_IN_L/R

SC2_IN_L/R

SC3_IN_L/R

SC4_IN_L/R

MONO_IN

Mute

ACB[5,9,8]

S1

ACB[6,11,10]

to Audio Baseband

Processing (DSP_IN)

A

D

SCARTL/R

selected SCART inputs to SCART outputs in the

TV set’s stand-by mode.

In case of power-on start or starting from st and -by, the

IC switches automatically t o the default configuration,

shown in Fig. 4–3. This action takes place after the

2

C transmission into the DSP part. By transmitting

first I

the ACB register first, the individual default setting

mode of the TV set can be defined.

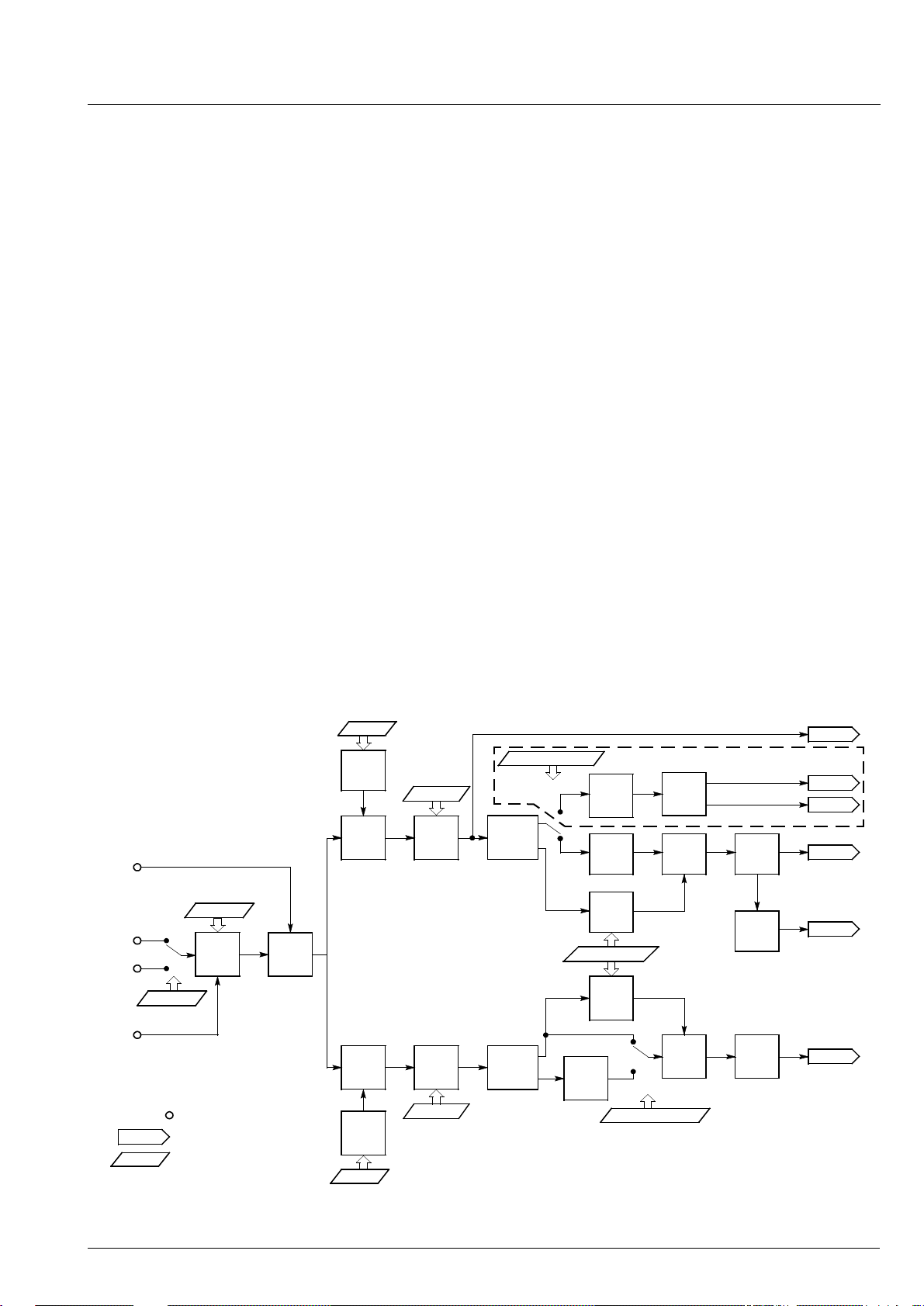

4.3. DSP Section (Audio Baseband Processing)

All audio baseband fu nctions are performed by digital

signal processing (DSP). The DSP functions are

grouped into three proce ss i ng p arts: input pr epr oces s ing, channel source selection, and channel postprocessing (see Fig.4–5 and section 7.).

The input preprocessing is intended to prepare the

various signals of all input sourc es in order to form a

standardized signal at the input to the channel sel ector. The signals can be adjusted in volume, are processed with the appropriate deemphasis, and are

dematrixed if necess ary.

SCART_OUT

SC1_OUT_L/R

S2

Mute

ACB[7,13,12]

SCART_OUT

from Audio Baseband

Processing (DSP_OUT)

SC2_OUT_L/R

S3

SCART1_L/R

SCART2_L/R

D

A

D

A

Mute

Fig. 4–3: SCART switching facilities (see 7.3.18.).

Switching positions show the default configuration

after power-on reset

Having prepared the signals that way, the channel

selector makes it possible to distribute all possible

source signals to the desired output channels.

The ability to ro ute in an exter nal c opro cessor for special effects, like surround processing and sound field

processing, is of special importance. Routing can be

done with each input source and output channel via

2

S inputs and outputs.

the I

All input and outp ut si gnals can be pr ocess ed si multa-

neously with the exception that FM2 cannot be processed at the same time as NICAM. FM ide ntification

and adaptive deemphasis are al so not possible simultaneously. Note, that the NICAM input signals are only

available in the MSP 3410D version.

4.3.1. Dual-Carrier FM Stereo/Bilingual Detection

For the terrestrial dual-FM carrier systems, audio information can be transmitted in three modes: mono, stereo, or bilingual. To obtain information about the current

audio operation mode, the MSP 34x0D detects the socalled identification signal. Information is supplied via

the Stereo Detection Register to an external CCU .

4.2.2. Stand-by Mode

If the MSP 34x0D is switched off by first pulling

STANDBY Q low, and th en disconnecting the 5 V, but

keeping the 8 V power supply (‘Stand-by’-mode), the

IDENT

AM

Demodu-

lation

Stereo

Detection

Filter

Bilingual

Detection

Filter

Level

Detect

Level

Detect

Stereo

Detection

−

Register

switches S1, S2, and S3 (see Fig. 4–3) main tain their

position and function. Thi s facilitates the copying from

Fig. 4–4: Stereo/bilingual detection

Micronas 13

14 Micronas

MSP 34x0D PRELIMINARY DATA SHEET

Analog

Inputs

Demodulated

IF

Inputs

I2S Bus

Inputs

NICAMA

SCARTL

SCARTR

DC level readout FM1

FM1/AM

FM2

NICAMA

NICAMB

I2S1L

I2S1R

I2S2L

I2S2R

Internal signal lines (see Fig. 4–2 and Fig. 4–3)

Adaptive

Deemphasis

Deemphasis

50/75 µs

J17

DC level readout FM2

Deemphasis

J17

SCART

Prescale

FM/AM

Prescale

NICAM

Prescale

I2S1

Prescale

I2S2

Prescale

FM-Matrix

Channel Source Select

Loudspeaker

Channel

Matrix

Headphone

Channel

Matrix

SCART1

Channel

Matrix

SCART2

Channel

Matrix

I2S

Channel

Matrix

Quasi-Peak

Channel

Matrix

AVC

Bass/

Treble

or

Equalizer

Bass/

Treble

Quasi-Peak

Detector

Σ

Beeper

Σ

Quasi peak readout L

Quasi peak readout R

Loudness

Loudness

Comple-

mentary

Highpass

Lowpass

Spatial

Effects

Balance

Level

Adjust

Balance

Volume

Volume

Volume

Volume

Loudspeaker L

Loudspeaker R

Subwoofer

Headphone L

Headphone R

SCART1_L

SCART1_R

SCART2_L

SCART2_R

I2SL

I2SR

Loudspeaker

Outputs

Headphone

Outputs

SCART

Outputs

I2S

Outputs

Fig. 4–5: Audio baseband processing (DSP firmware)

PRELIMINARY DATA SHEET MSP 34x0D

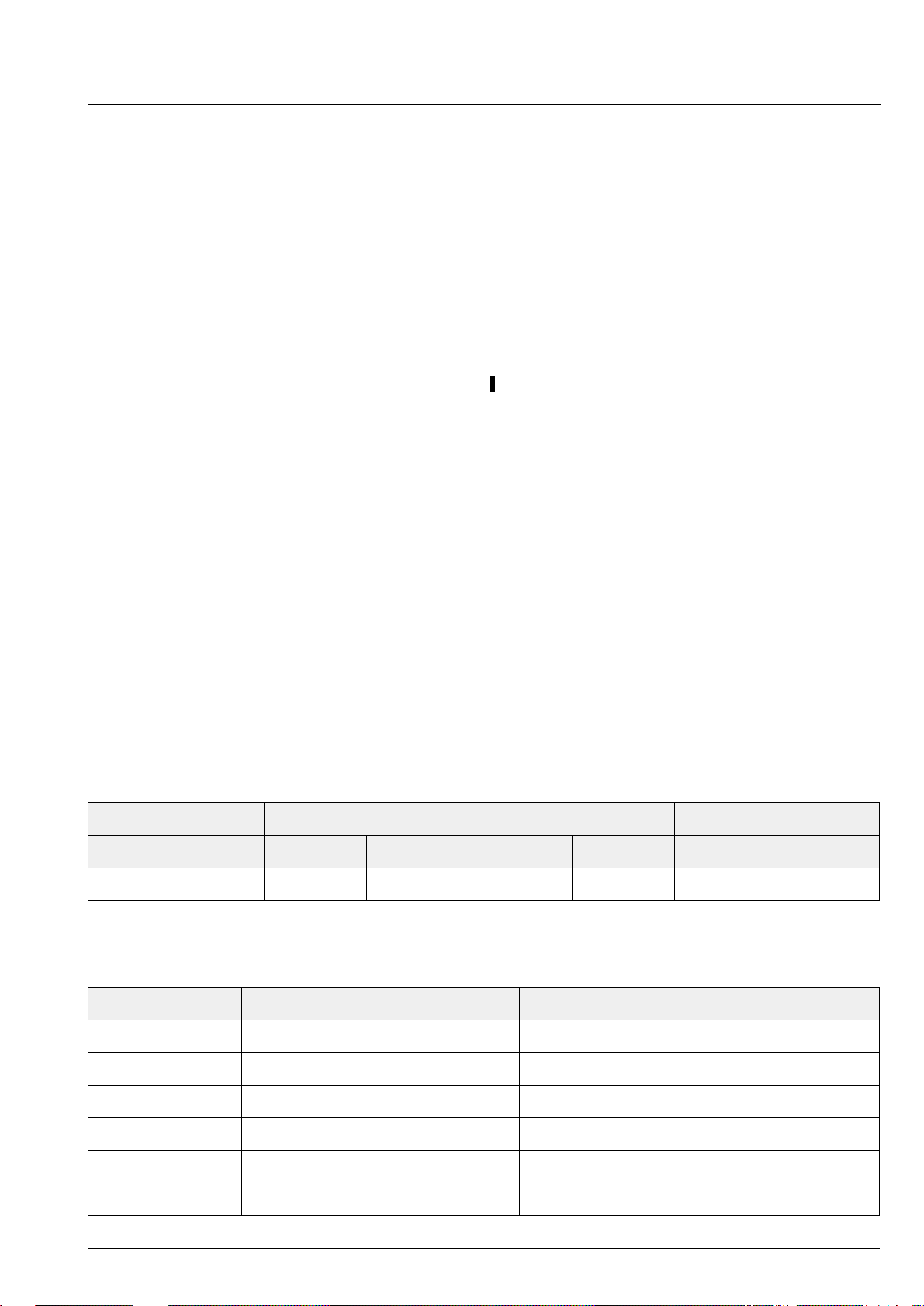

Table 4–1: Some examples for recommended channel assignments for demodulator and audio processing part

Mode MSP Sound IF-

Channel 1

B/G-Stereo FM2 (5.74 MHz): R FM1 (5.5 MHz): (L+R)/2 B/G Stereo Speakers: FM Stereo

B/G-Bilingual FM2 (5.74 MHz): Sound B FM1 (5.5 MHz): Sound A No Matrix Speakers: FM

NICAM-I-ST/

FM-mono

Sat-Mono not used FM (6.5 MHz): mono No Matrix Speakers: FM Sound A

Sat-Stereo 7.2 MHz: R 7.02 MHz: L No Matrix Speakers: FM Stereo

Sat-Bilingual 7.38 MHz: Sound C 7.02 MHz: Sound A No Matrix Speakers: FM

Sat-High Dev.

Mode

NICAM (6.552 MHz) FM (6.0 MHz): mono No Matrix Speakers: NICAM

don’t care 6.552 MHz No Matrix Speakers: FM

4.4. Audio PLL and Crystal Specifications

The MSP 34x0D requires a 18.432MHz (12 pF, parallel) crystal. The clock supply of the whole system

depends on the MSP 34x0D operation mode:

1. FM-Stereo, FM-Mono:

The system clock runs free on the crystal’s

18.432 MHz.

2. NICAM:

An integrated clock PLL uses the 364 kHz baud

rate, accomplished in the NICAM demodulator block

to lock the system clock to the bit rate, respectively,

32-kHz sampling rat e of the NICAM transmitter. As

a result, the whole audio syst em is supplied with a

controlled 18.432 MHz clock.

2

S slave operation:

3. I

In this case, the system clock is locked to a synchronizing signal (I2S_CL, I2S_WS) supplied by the

coprocessor chip.

MSP Sound IFChannel 2

FMMatrix

ChannelSelect

H. Phone: FM

H. Phone: FM

H. Phone: FM

H. Phone: FM

Channel

Matrix

Speakers: Sound A

H. Phone: Sound B

Speakers: Stereo

H. Phone: Sound A

Speakers: Sound A

H. Phone: Sound B=C

Speakers: Sound A

H. Phone: Sound A

4.5. ADR Bus Interface

For the ASTRA Digital Radio System (ADR), the

MSP 34x0D performs preprocess ing, as ther e are car rier selection an d filteri ng. Via the 3-line AD R bus, the

resulting signals are transferred to the DRP 3510A,

where the source decoding is performed. To be prepared for an upgrade to ADR with an additional DRP

board, the following lines of MSP 34x0D should be

provided on a feature connector:

– AUD_CL_OUT

– I2S_DA_IN1 or I2S_DA_IN2

– I2S_DA_OUT

– I2S_WS

– I2S_CLK

– ADR_CL

– ADR_WS

Remark on using the crystal:

– ADR_DA

External cap acitors at each crys tal pin to ground are

required (see General Crystal Recommendations on

page 69).

4.6. Digital Control Output Pins

The static level of two output pins of the MSP 34x0D

(D_CTR_OUT0/1) is switchable between HIGH and

LOW by means of the I

trolling of external hardware-controlled switches or

other devices via I

2

C bus. This enables the con-

2

C bus (see section 7.3.18. on page

47).

Micronas 15

MSP 34x0D PRELIMINARY DATA SHEET

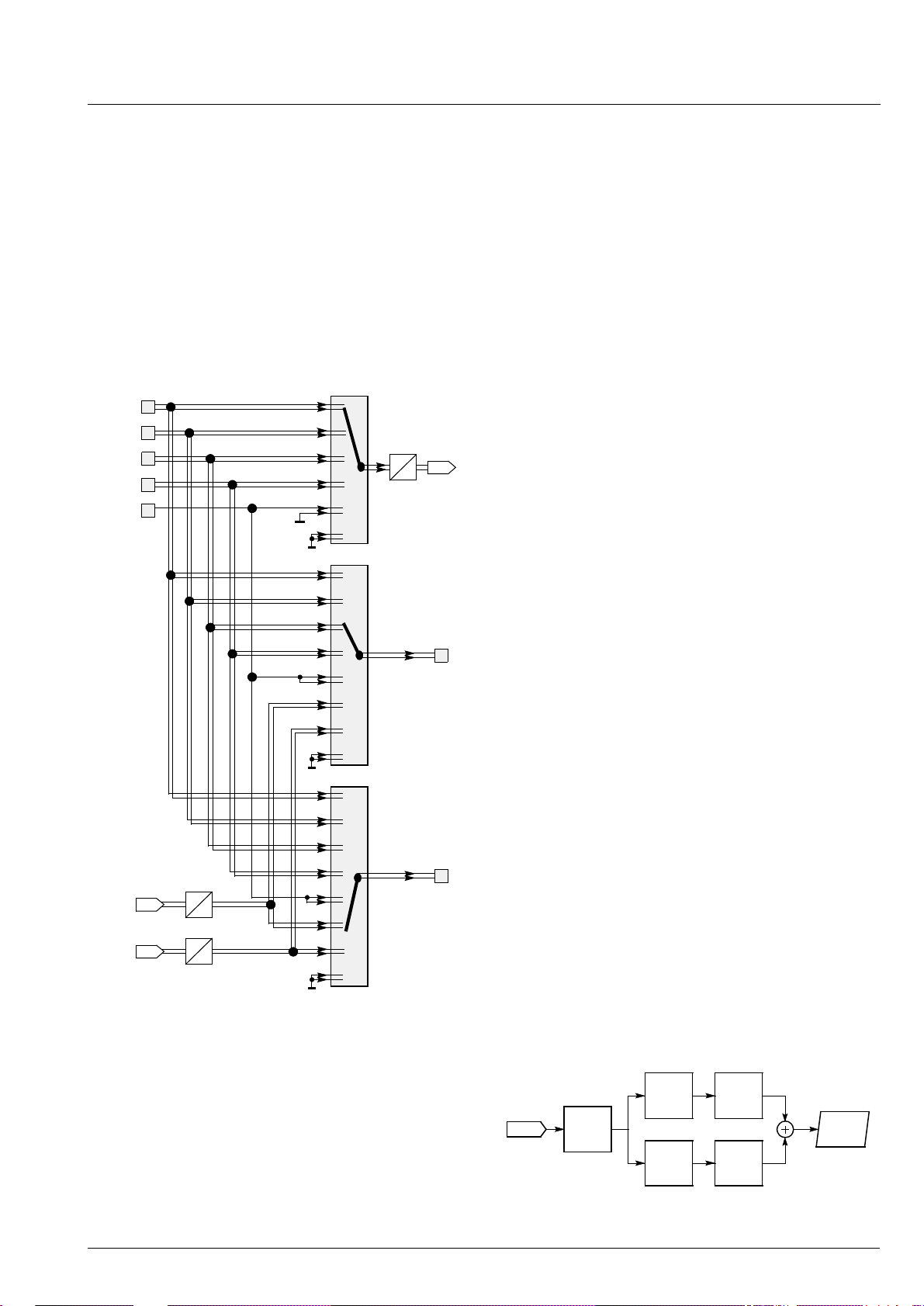

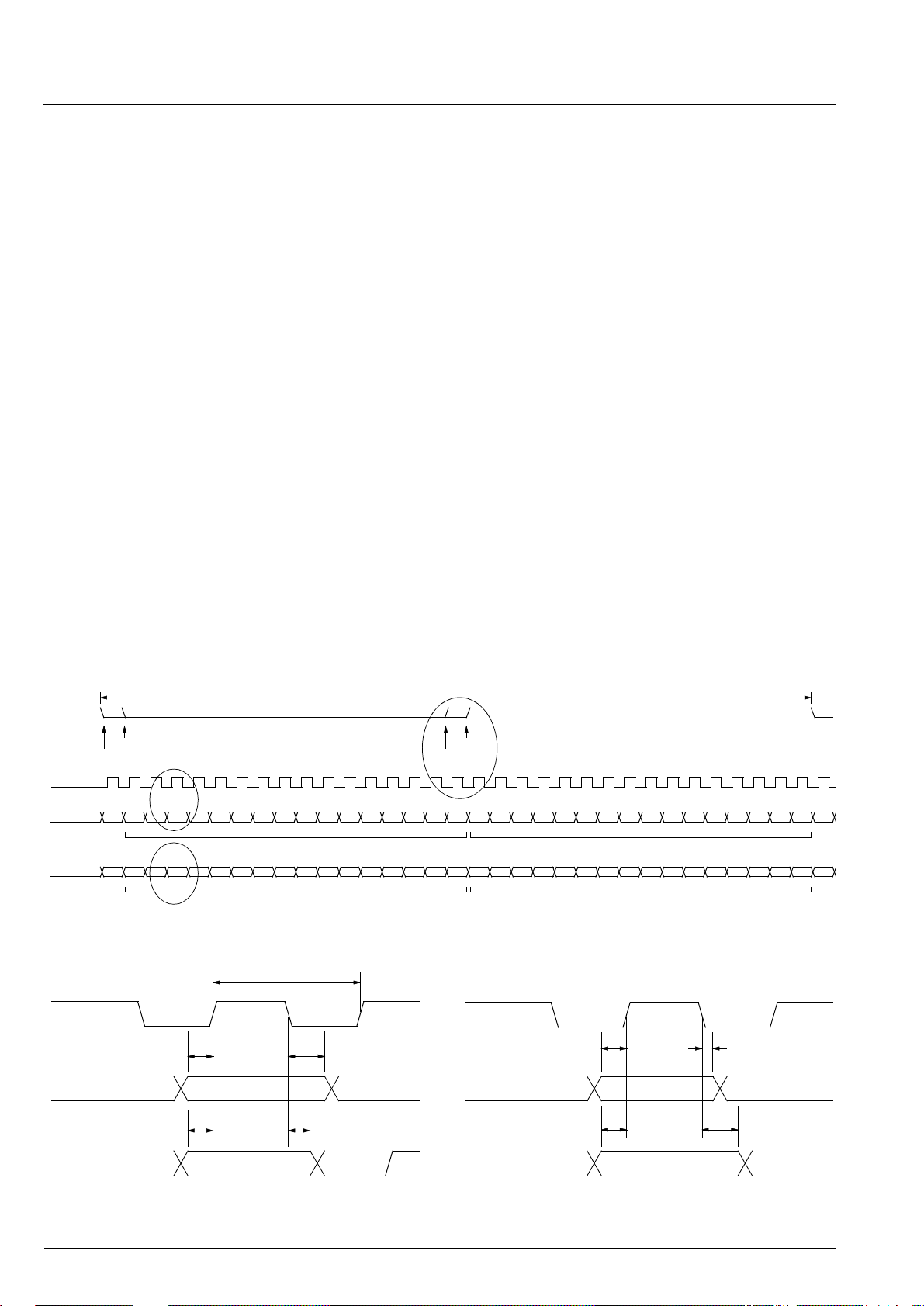

4.7. I2S Bus Interface

By means of this standardized interface, additional

feature processors can be connected to the

MSP 34x0D. Two possible format s ar e supp or te d: Th e

standard mode (MODE _REG[4]=0) select s the SONY

format, where the I2S_WS signal ch anges at the word

boundaries. The so-called PHILIPS format, which is

characterized by a change of th e I2S_WS signal one

I2S_CL period before the word boundaries, is selected

by setting MODE_REG[4]=1.

The MSP 34 x0D no rma lly ser ves as th e master on the

2

S interface. Here, the clock and word strobe lines are

I

driven by the MSP 34x0D. By setting

MODE_REG[3]=1, the MSP 34x0D is switched to a

slave mode. Now, these lines are input to the

MSP 34x0D and the master clock is synchronized to

576 times the I2S_WS rate (32 kHz). NICA M operation

is not possible in th is m ode .

2

S bus interface consists of five pins:

The I

1. I2S_DA_IN1, I2S_DA_IN2:

For input, four channels (two channels per line,

2*16 bits) per sampling cycle (32 kHz) are transmitted.

2. I2S_DA_OUT:

For output, two channels (2*16 bits) per sampling

cycle (32 kHz) are transmitted.

3. I2S_CL:

Gives the timing for the transmission of I

2

S serial

data (1.024 MHz).

4. I2S_WS:

The I2S_WS word strobe line defines the left and

right sample.

2

A precise I

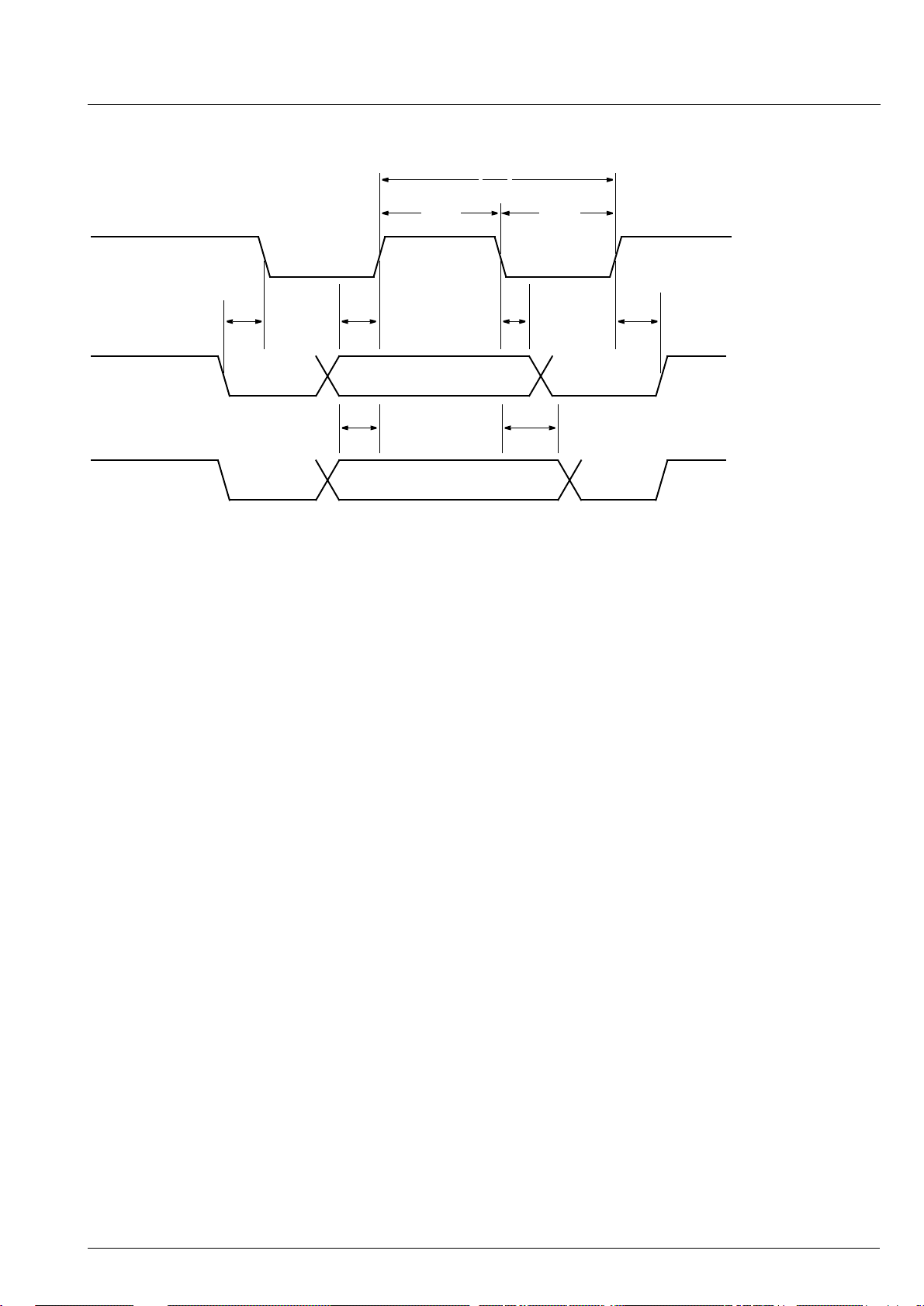

S timing diagram is shown in Fig. 4–6.

(Data: MSB first)

I2S_WS

SONY Mode

PHILIPS Mode

I2S_CL

I2S_DAIN

I2S_DAOUT

R LSB L MSB

R LSB

L MSB

Detail C

I2S_CL

I2S_WS as INPUT

PHILIPS/SONY Mode programmable by MODE_REG[4]

Detail A

16 bit left channel

Detail B

1/F

I2SCL

T

I2SWS1

T

I2SWS2

F

I2SWS

Detail C

SONY Mode

PHILIPS Mode

L LSB

R MSB

L LSB

R MSB

Detail A,B

I2S_CL

I2S_DA_IN

16 bit right channel

16 bit right channel16 bit left channel

T

I2S1

R LSB L LSB

R LSB L LSB

T

I2S2

I2S_WS as OUTPUT

Fig. 4–6: I

T

I2S5

2

S bus timing diagram

T

I2S6

I2S_DA_OUT

T

I2S3

T

I2S4

16 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

5. I2C Bus Interface: Device and Subaddresses

As a slave receiver, the MSP 34x0D can be controlled

2

C bus. Access to internal memory locations is

via I

achieved by subaddressing. The demodulator and the

DSP processor par ts have two separate subaddressing register banks.

In order to allow for more MSP 34x0D ICs to be connected to the control bus, an ADR_SEL pin has be en

implemented. With ADR_SEL pulled to HIGH, LOW, or

left open, the MSP 34x0D responds to changed device

addresses. Thus, three identical devices can be

selected.

By means of the RESET bit in the CONTROL register,

all devices with the same device address are reset.

The IC is selected by asserting a special device

address in the addre ss part of an I

2

C transmission . A

device address pair is def ined as a write add ress (80,

84, or 88

) and a read address (81, 85, or 89

hex

hex

(see Table 5–1). Writin g is don e by sending the device

write address, followed by the subaddress byte, two

address bytes, and two data bytes. Reading is done by

sending the device write addr ess, followed by the subaddress byte and two addres s bytes. Without sendi ng

a stop condition, reading of the addressed data is completed by sending the device read a ddress (81, 85, or

) and reading two bytes of data (see Fig. 5–1:

89

hex

2

C Bus Protocol” and section 5.2. “Proposal for

“I

MSP 34x0D I

2

C Telegrams”).

Due to the internal architecture of the MSP 34x 0D, the

IC cannot react immediately to an I

2

C request. The typical response time is about 0.3 ms for the DSP processor part and 1 ms for the demodulator part if NICAM

processing is active. If the receiver (MSP) can’t receive

another complete byte of data until it has performed

some other function; for example, servicing an internal

interrupt, it can hold the clock line I2C_CL LOW to

force the transmitter into a wait state. The positions

within a transmission where this may happen are indicated by ’Wait’ in section 5.1. The maximum wait

period of the MSP during normal operation mode is

less than 1 ms.

2

C bus error caused by MSP hardware problems:

I

In case of any internal error, the MSPs wait period is

extended to 1.8 ms. Afterwards, the MSP does not

acknowledge (NAK) the device address. The data line

will be left HIGH by the MSP and the clock line will be

released. The master can then generate a STOP condition to abort the transfer.

)

By means of NAK, the master is able to recognize the

error state and to reset the IC via I

2

C bus. While transmitting the reset protoc ol (see section 5.2.4. on page

19) to ‘CONTROL’, the master must ignore the not-

acknowledge bits (NAK) of the MSP.

2

A general timing diagram of the I

C Bus is shown in

Fig. 5 –2 on page 19.

Table 5–1: I

2

C Bus Device Addresses

ADR_SEL Low High Left Open

Mode Write Read Write Read Write Read

MSP device address 80 hex 81 hex 84 hex 85 hex 88 hex 89 hex

Table 5–2: I2C Bus Subaddresses

Name Binary Value Hex Value Mode Function

CONTROL 0000 0000 00 W software reset

TEST 0000 0001 01 W only for internal use

WR_DEM 0001 0000 10 W write address demodulator

RD_DEM 0001 0001 11 W read address demodulator

WR_DSP 0001 0010 12 W write address DSP

RD_DSP 0001 0011 13 W read address DSP

Micronas 17

MSP 34x0D PRELIMINARY DATA SHEET

Table 5–3: Control Register (Subaddress: 00 hex)

Name Subaddress MSB 14 13..1 LSB

CONTROL 00 hex 1 : RESET

0 : normal

5.1. Protocol Description

Write to DSP or Demodulator

Swrite

device

address

Wait ACK subaddr AC K addr byte

Read from DSP or Demodulator

Swrite

device

address

ACK subaddr ACK addr byte

Wait

ACK addr byte

high

high

000

ACK addr byte

ACK S read

low

low

ACK data byte

device

address

Wait

high

ACK data byte

ACK data byte

high

low

ACK data byt e

low

ACK P

NAK P

Write to Control or Test Registers

Swrite

Note: S = I

device

address

P = I

2

C bus Start Condition from master

2

C bus Stop Condition from master

Wait ACK subaddr ACK data byte high ACK data byte low ACK P

ACK = Acknowledge-Bit: LOW on I2C_DA from slave (

or master (

=CCU, hatched)

NAK = Not-Acknowledge Bit: HIGH on I2C_DA from master (

or from MSP indicating internal error state

Wait = I

I2C_DA

2

C clock line held low by the slave (=MSP) while interrupt is serviced (<1.8 ms)

1

0

S P

I2C_CL

2

Fig. 5–1: I

C bus protocol (MSB first; data must be stable while clock is high)

=MSP, gray)

=CCU, hatched) to indicate ‘End of Read’

18 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

(Data: MSB first)

1

f

I2C

I2C_CL

T

I2C4

T

I2C3

T

I2C1

I2C_DA as input

I2C_DA as output

Fig. 5–2: I

2

C bus timing diagram

5.2. Proposal for MSP 34x0D I

5.2.1. Symbols

daw write device address

dar read device address

< start condition

> stop condition

aa address byte

dd data byte

T

I2C5

2

C Telegrams

T

I2COL2

T

I2C6

T

I2COL1

T

I2C2

5.2.2. Write Telegrams

<daw 00 d0 00> write to CONTROL register

<daw 10 aa aa dd dd> write data into demodulator

<daw 12 aa aa dd dd> write data into DSP

5.2.3. Read Telegrams

<daw 11 aa aa <dar dd dd> read data from demodulator

<daw 13 aa aa <dar dd dd> read data from DSP

5.2.4. Examples

<80 00 80 00> RESET MSP statically

<80 00 00 00> clear RESET

<80 12 00 08 01 20> set loudspeaker channel source

to NICAM and matrix to STEREO

Micronas 19

MSP 34x0D PRELIMINARY DATA SHEET

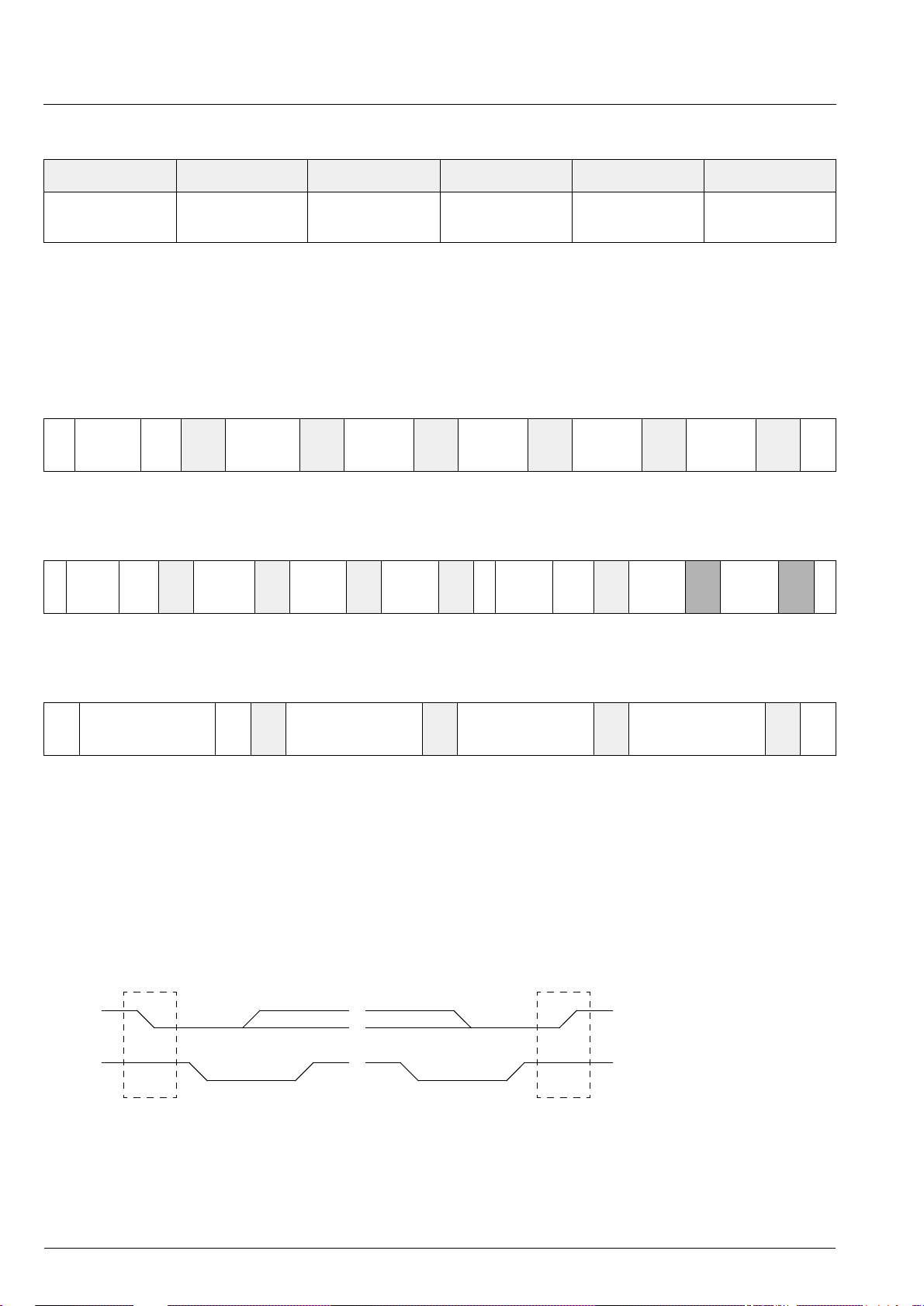

5.3. Start-Up Sequence: Power-Up and I2C-Controlling

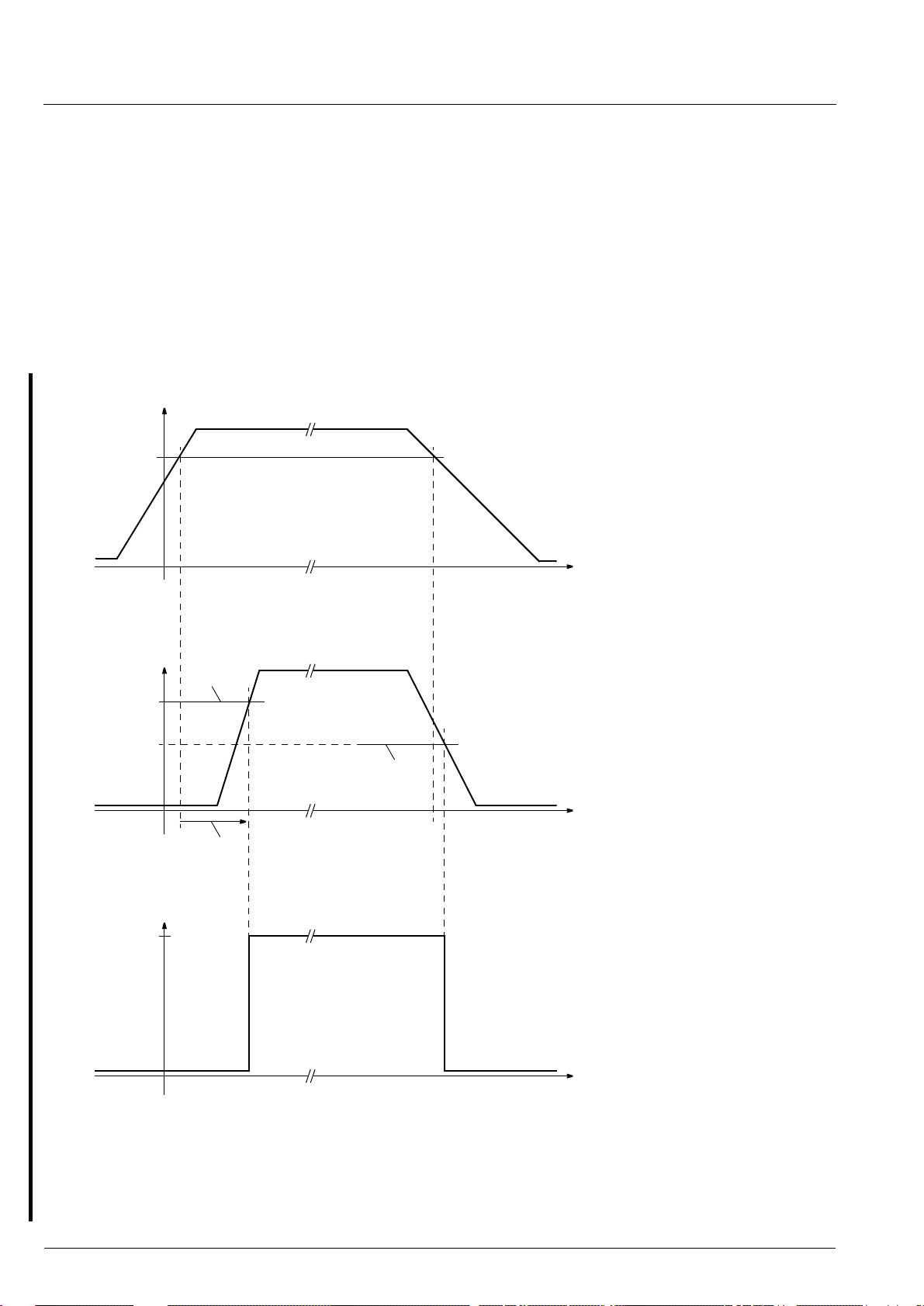

After power-on or RESET (see Fig. 5–3), the IC is in

an inactive state. The CCU has to transmit the

required coefficient set for a given operation via the

2

C bus. Initialization should start with the demodulator

I

part. If required for any reason, the audio processin g

part can be loaded before the demodulator part.

DVSUP

AVSUP

4.5 V

RESETQ

0.7×DVS UP

0.45...0.55

Internal

Reset

t/ms

Low-to-High

Threshold

×DVSUP

High-to-Low

Threshold

t/ms

Reset Delay

>2 ms

High

Low

t/ms

Note: The reset should

not reach high level before the oscillator has

Power-Up Reset: Threshold and Timing

(Note: 0.7×DVSUP means 3.5 Volt with DVSUP=5.0 Volt)

started. This requires a

reset delay of >2 ms

Fig. 5–3: Power-up sequence

20 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

6. Programming the Demodulator

and NICAM Decoder Section

6.1. Short-Programming and General

Programming of the Demodulator Part

The demodulator pa rt of the MSP 34x0D can b e programmed in two different modes:

1. Demo du lat or Sh ort-P r o gramming provides a com-

fortable way to set up the demodulator for many terrestrial TV sound standards with one single I

2

C bus transmission. The coding is listed in section 6.4.1. If a

parameter does not coincide with the individual programming concept, it simply can be overwritten by

using the General Programming Mode. Some bits of

the registers AD_CV (see section 6.5.1. on page 25)

and MODE_REG (see section 6.5.2. on page 27) are

not affected by the short-programming. They must be

transmitted once if their reset status does not fit. The

Demodulator Short-Programming is not compatible to

MSP 3410B and MSP 3400C.

Autodetection for terrestrial TV standards is part of

the Demodulator Short-Programming. This feature

enables the detection and set-up of the actual TV

sound standard wi thin 0.5 s. Since the detected standard is readable by the contro l processor, the Autodetection feature is mainly re commended for the primar y

set-up of a TV set: after having once de termined the

corresponding TV channels, their sound standards can

be stored and later on programmed by the Demodulator Short -Programming (see s ection 6.4.1. on page 23

and section 6.6.1. on page 32).

2. General Programming ensures the so ftware-compatibility to other MS Ps. It offers a very flexible way to

apply all of the M SP 34x0 D demodulator facilities. All

registers except 0020

(Demodulator Short-Pro-

hex

gramming) have to be written with values corresponding to the individual requirements. For satellite applications, with their many variations, this mode must be

selected.

All transmission s on the control bus are 16 bits wi de.

However, data for the de modulator par t have only 8 or

12 significant bits. These data have to be inserted

LSB-bound and filled with zero bits into the 16-bit

transmission word. Table 4–1 explains how to assign

FM carriers to the MSP Sound IF channels and the

corresponding matrix modes in the audio processing

part.

Micronas 21

MSP 34x0D PRELIMINARY DATA SHEET

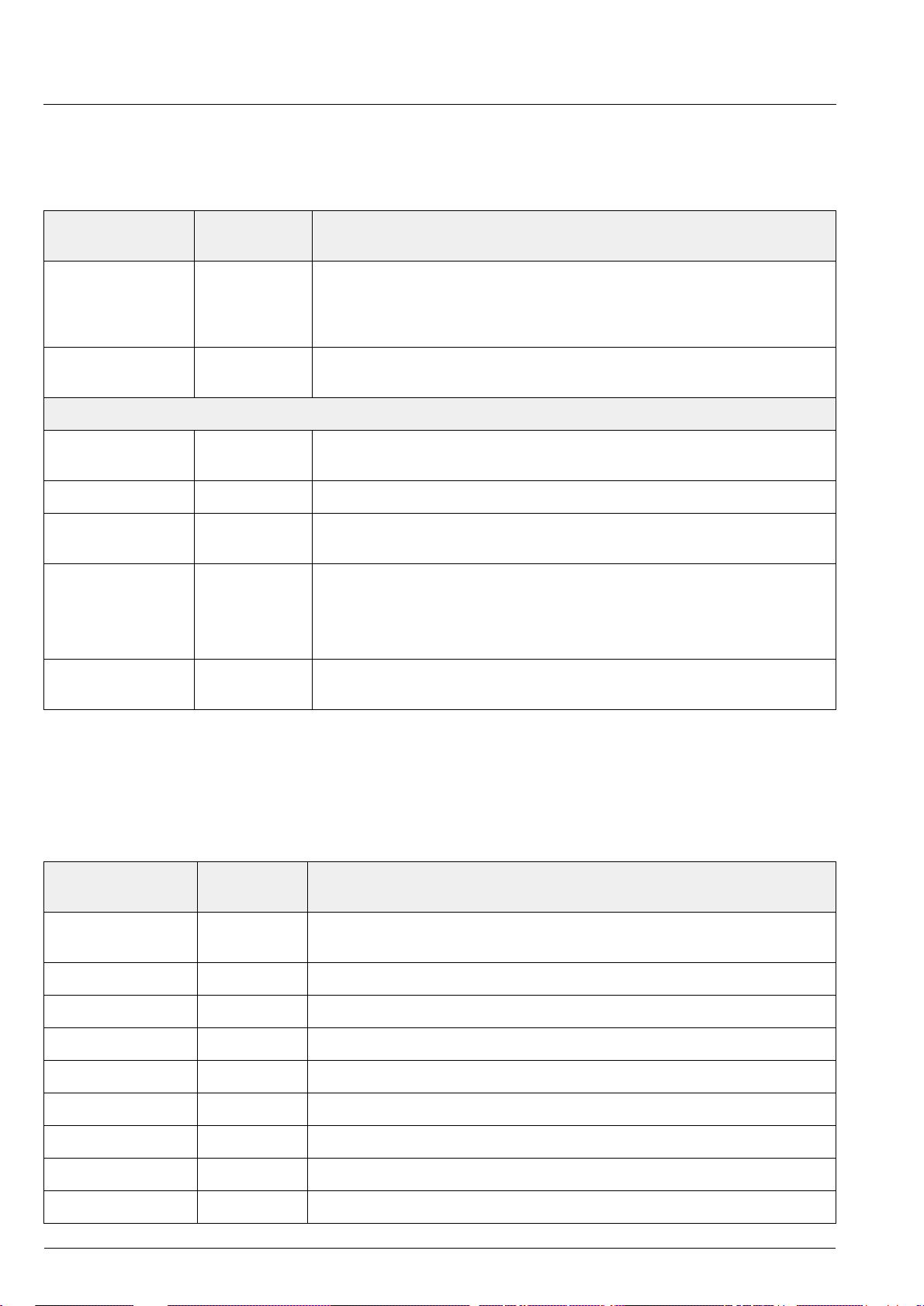

6.2. Demodulator Write Registers: Table and Addresses

Table 6–1: Demodulator Write Registers; Subaddress: 10

Demodulator

Write Registers

Demodulator

ShortProgramming

AUT O_FM/AM 0021 Only for NICAM: Automatic switching between NICAM and FM/AM in case

Write Registers n ec es sa ry for General Programming Mode only

AD_CV 00BB input selection, configuration of AGC, Mute Function and selection of

MODE_REG 0083 mode register

FIR1

FIR2

DCO1_LO

DCO1_HI

DCO2_LO

DCO2_HI

Address

(hex)

0020 Write into this register to apply Demodulator Short Programming (see sec-

0001

0005

0093

009B

00A3

00AB

Function

tion 6.4.1. on page 23). If the internal setting coincidences with the individual requirements no more of the remaining Demodulator Write Registers

have to be transferred.

of bad NICAM reception (see section 6.4.2. on page 24)

A/D converter, FM Carrier Mute on/off

filter coefficients channel 1 (6

filter coefficients channel 2 (6

increment channel 1 low part

increment channel 1 high part

increment channel 2 low part

increment channel 2 high part

; these registers are not readable!

hex

× 8 bit)

× 8 bit), + 3 × 8 bit offset (total 72 bits)

PLL_CAPS 001F switchable PLL capacitors to tune open-loop frequency; to use only if

NICAM of MODE_REG = 0 ; normally not of interest for the customer

6.3. Demodulator Read Registers: Table and Addresses

Table 6–2: Demodulator Read Registers; Subaddress: 11

Demodulator

Read Registers

Result of

Autodetection

C_AD_BITS 0023 NICAM Sync bit, NICAM C bits, and three LSBs of additional data bits

ADD_BITS 0038 NICAM: bit [10:3] of additional data bits

CIB_BITS 003E NICAM: CIB1 and CIB2 control bits

ERROR_RATE 0057 NICAM error rate, updated with 182 ms

CONC_CT 0058 only to be used in MSPB compatibility mode

Address

(hex)

007E (see Table 6–13)

Function

; these registers are not writable!

hex

FAWCT_IST 0025 only to be used in MSPB compatibility mode

PLL_CAPS 021F Not for customer use.

AGC_GAIN 021E Not for customer use.

22 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

6.4. Demodulator Write Registers for Short-Programming: Functions and Values

In the following, the functions of some registers are explained and their (default) values are defined:

6.4.1. Demodulator Short-Programming

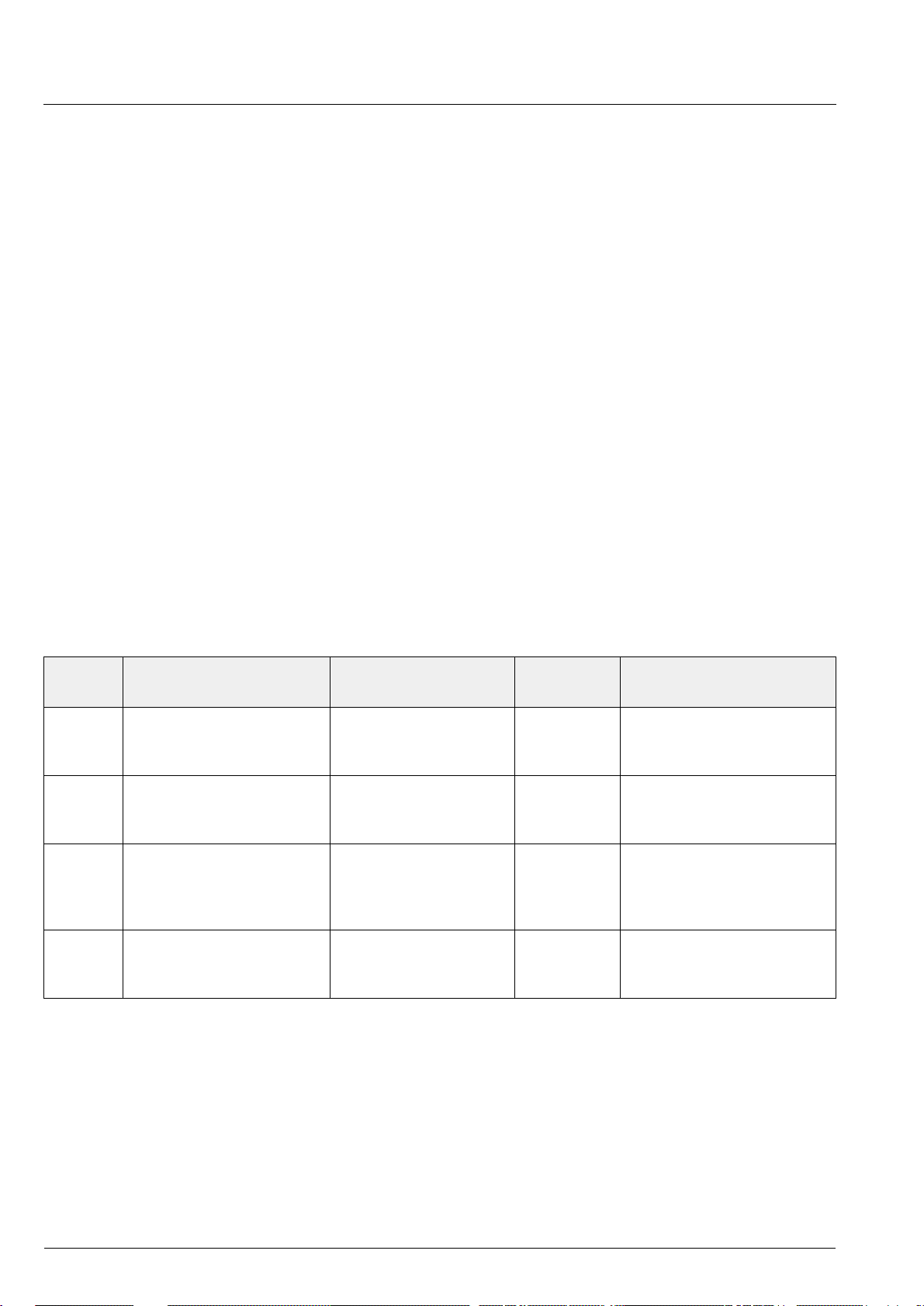

Table 6–3: MSP 34x0D Demodulator Short-Programming

Demodulator Short-Programming 0020

hex

TV Sound Standard Internal Setting

Description Code

(hex)

AD_CV

(see Table 6–5)

2)

MODE_

2)

REG

(see

Table 6–8)

DCO1

(MHz)

DCO2

(MHz)

FIR1/2

Coefficients

Identification

Mode

Autodetection 0001 Detects and sets one of the standards listed below, if available. Results are to be

read out of the demodulator read register “Result of Autodetection” (section 6.6.1.)

M Dual-FM 0002 AD_CV- FM M1 4.72421 4. 5

Reset, then

Standard M

see T able 6–11:

B/G Dual-FM 0003 AD_CV-FM M1 5.74218 5.5

D/K1 Dual-FM 0004 AD_CV-FM M1 6.25781 6.5

Terrestrial TV

Standards

Reset, then

Standard

B/G

D/K2 Dual-FM 0005 AD_CV-FM M1 6.74218 6.5

0006/

0007

reserved for future dual-FM standards

AUTO_

FM/AM

B/G NICAM FM 0008 AD_CV-FM M2 5.85 5.5

L NICAM AM 0009 AD_CV-AM M3 5.85 6.5

I NICAM FM 000A AD_CV-FM M2 6.552 6.0

see T able 6–11:

Terrestrial TV

Standards

1)

D/K NICAM FM 000B AD_CV-FM M2 5.85 6.5

>000B reserved for future NICAM Standards

1)

corresponds to the actual setting of AUTO_FM (Address = 0021

2)

bits of AD_CV or MODE_REG, which are not affected by the short-programming, must be transmitted

hex

)

separately if their reset status does not fit.

Note: All parameters in the DSP section (Audio Baseband Processing), except the identification mode register,

are not affected by the Demodulator Short-Programming. They still have to be defined by the control processor.

Micronas 23

MSP 34x0D PRELIMINARY DATA SHEET

6.4.2. AUTO_FM/AM: Automatic Switching

between NICAM and FM/AM-Mono

In case of bad NICAM transmission or loss of the

NICAM carrie r, the MSPD offers a comfor table mod e to

switch back to the FM/AM-Mono signal. If automatic

switching is active, the MSP internally evaluates the

ERROR_RATE. All output channels which are assigned

to the NICAM source are switched back to the

FM/AM-Mono source without any further CCU instruction, if the NICAM carrier fails or the ERROR_RATE

exceeds the definable threshold.

Note, that the channel matrix of the corresponding output channels must be set according to the NICAM

mode and need not be changed in the FM/AM fall-back

case. An appropriate hysteresis algorithm avoids oscillating effects. The MSB of the Register C_AD_BITS

(Addr: 0023

FM/AM Status (see section 6.6.2. on page 32).

) informs about the actual NICAM

hex

There are two possibilities to define the threshold

deciding for NICAM or FM/AM-Mono (see Table 6–4):

1. default value of the MSPD (internal threshold = 700,

i.e. switch to FM/AM if ERROR_RATE > 700)

2. definable by the customer (recommendable range:

threshold = 50...2000, i.e. Bits [10...1] = 25...1000).

Note: The auto_FM feature is only active if the NICAM

bit of MODE_REG is set.

Table 6–4: Coding of automatic NICAM FM/AM switching (reset status: mode 0)

Mode Auto_FM [11...0]

Addr. = 0021

0

default

1 Bit [0] = 1

2 Bit [0] = 1

3 Bit [11] = [0] = 1

Bit [0] = 0

Bits [11...1] = 0

Bit [11...1] = 0

Bit [10...1] = 25..1000 int

Bit [11] = 0

Bit [10...1] = 0

hex

= threshold/2

Selected Sound at the

NICAM Channel Select

always NICAM none Compatible to MSP 3410B,

NICAM or FM/AM,

depending on

ERROR_RATE

NICAM or FM/AM,

depending on

ERROR_RATE

always FM/AM none Forced FM-Mono mode, i.e.

Threshold Comment

700 dec automatic switching with

set by

customer

i.e. automatic switching is

disabled

internal threshold

automatic switching with

external threshold

automatic switching is

disabled

24 Micronas

PRELIMINARY DATA SHEET MSP 34x0D

6.5. Demodulator Write Registers for the General Programming Mode: Functions and Values

6.5.1. Re gister ‘AD_CV’

Table 6–5: AD_CV Register (reset status: all bits are “0”)

AD_CV 00BB

hex

Set by Short-Programming

Bit Meaning Settings AD_CV-FM AD_CV-AM

AD_CV [0] not used must be set to 0 0 0

AD_CV [6...1] Reference level in case of Auto-

101000 100011

matic Gain Control = on (see Table

6–6). Constant gain factor when

Automatic Gain Control = off

(see Table 6–7)

AD_CV [7] Determination of Automatic Gain or

Constant Gain

AD_CV [8] Selection of Sound IF source 0 = ANA_IN1+

0 = constant gain

1 = automatic gain

11

not affected not affected

1 = ANA_IN2+

AD_CV [9] MSP Carrier Mute Function

(Must be switched off in

High Deviation Mode)

AD_CV [15

...10] not used must be set to 0 000000 000000

0 = off: no mute

1 = on: mute as described in section 4.1.8.

on page 12

10

Table 6–6: Reference values for active AGC (AD_CV[7] = 1)

Application Input Signal Contains AD_CV [6...1]

Ref. Value

AD_CV [6...1]

(dec)

Range of Input Signal

at pin ANA_IN1+

and ANA_IN2+

Terrestrial TV

Dual-Carr. FM

NICAM/FM

NICAM/AM

2 FM Carriers

1 FM and 1 NICAM Carrier

1 AM and 1 NICAM Carrier

101000

101000

100011

40

40

35

0.10

− 3V

0.10 − 3V

0.10 − 1.4 V

pp

pp

1)

1)

pp

recommended:

− 0.8 V

NICAM only

1 NICAM Carrier only

SAT 1 or more

0.10

010100

20

0.05 − 1.0 V

100011 35 0.10 − 3V

pp

pp

pp

1)

FM Carriers

ADR FM a. ADR carriers see DRP 3510A data sheet

1)

For signals above 1.4 Vpp, the minimum gain of 3 dB is switched and overflow of the A/D converter may result.

Due to the robustness of the internal processing, the IC works up to and even more than 3 V

, if norm conditions

pp

of FM/NICAM or FM1/FM2 ratio are supposed. In this overflow case, a loss of FM S/N ratio of about 10 dB may

appear.

Micronas 25

Loading...

Loading...