Micronas Intermetall MAS3509F Datasheet

MAS 35x9F

MPEG Layer 2/3,

AAC Audio Decoder,

G.729 Annex A Codec

Edition October 31, 2000

6251-505-2AI

ADVANCE INFORMATION

MICRONAS

MICRONAS

MAS 35x9F ADVANCE INFORMATION

Contents

Page Section Title

5 1. Introduction

5 1.1. Features

6 1.2. Features of the MAS 35x9F Family

7 1.3. Application Overview

8 2. Functional Description of the MAS 35x9F

82.1.Overview

8 2.2. Architecture of the MAS 35x9F

8 2.3. DSP Core

8 2.3.1. RAM and Registers

9 2.3.2. Firmware and Software

9 2.3.2.1. Internal Program ROM and Firmware, MPEG-Decoding

9 2.3.2.2. Program Download Feature

9 2.4. A udio Codec

9 2.4.1. A/D Converter and Microphone Amplifier

9 2.4.2. Baseband Processing

9 2.4.2.1. Bass, Treble, and Loudness

9 2.4.2.2. Micronas Dynamic Bass (MDB)

10 2.4.2.3. Automatic Volume Control (AVC)

10 2.4.2.4. Balance and volume

10 2.4.3. D/A Converters

10 2.4.4. Output Amplifiers

11 2.5. Clock Management

11 2.5.1. DSP Clock

11 2.5.2. Clock Output At CLKO

11 2.6. Power Supply Concept

11 2.6.1. Power Supply Regions

12 2.6.2. DC/DC Converters

12 2.6.3. Power Supply Configurations

14 2.7. Battery Voltage Supervision

15 2.8. Interfaces

15 2.8.1. I2C Control Interface

15 2.8.2. SPDIF Input Interface

15 2.8.3. S/PDIF Output

15 2.8.4. Multiline Serial Audio Input (SDI, SDIB)

15 2.8.5. Multiline Serial Output (SDO)

15 2.8.6. Parallel Input/Output Interface (PIO)

16 2.9. MPEG Synchronization Output

16 2.10. Default Operation

16 2.10.1. Stand-by Functions

16 2.10.2. Power-Up of the DC/DC Converters and Reset

17 2.10.3. Control of the Signal Processing

17 2.10.4. Start-up of the Audio Codec

17 2.10.5. Power-Down

2 Micronas

ADVANCE INFORMATION

Contents, continued

Page Section Title

18 3. I2C Interface

18 3.1. General

18 3.1.1. Device Address

18 3.1.2. I2C Registers and Subaddresses

19 3.1.3. Naming Convention

20 3.2. Direct Configuration Registers

20 3.2.1. Write Direct Configuration Registers

20 3.2.2. Read Direct Configuration Register

25 3.3. DSP Core

25 3.3.1. Access Protocol

26 3.3.1.1. Run and Freeze

26 3.3.1.2. Read Register (Code Ahex)

26 3.3.1.3. Write Register (Code Bhex)

26 3.3.1.4. Read D0 Memory (Code Chex)

27 3.3.1.5. Short Read D0 Memory (Code C4hex)

27 3.3.1.6. Read D1 Memory (Code Dhex)

27 3.3.1.7. Short Read D1 Memory (Code D4hex)

27 3.3.1.8. Write D0 Memory (Code Ehex)

28 3.3.1.9. Short Write D0 Memory (Code E4hex)

28 3.3.1.10. Write D1 Memory (Code Fhex)

28 3.3.1.11. Short Write D1 Memory (Code F4hex)

28 3.3.1.12. Clear SYNC Signal (Code 5hex)

28 3.3.1.13. Default Read

29 3.3.1.14. Fast Program Download

29 3.3.1.15. Serial Program Download

29 3.3.2. List of DSP Registers

30 3.3.3. List of DSP Memory Cells

30 3.3.3.1. Application Select and Running

30 3.3.3.2. Application Specific Control

40 3.3.4. Ancillary Data

40 3.3.5. DSP Volume Control

41 3.3.6. Explanation of the G.729 Data Format

41 3.4. Audio Codec Access Protocol

41 3.4.1. Write Codec Register

41 3.4.2. Read Codec Register

42 3.4.3. Codec Registers

49 3.4.4. Basic MDB Configuration

MAS 35x9F

50 4. Specifications

50 4.1. Outline Dimensions

51 4.2. Pin Connections and Short Descriptions

53 4.3. Pin Descriptions

53 4.3.1. Power Supply Pins

53 4.3.2. Analog Reference Pins

53 4.3.3. DC/DC Converters and Battery Voltage Supervision

54 4.3.4. Oscillator Pins and Clocking

54 4.3.5. Control Lines

Micronas 3

MAS 35x9F ADVANCE INFORMATION

Contents, continued

Page Section Title

54 4.3.6. Parallel Interface Lines

54 4.3.6.1. PIO Handshake Lines

54 4.3.7. Serial Input Interface (SDI)

54 4.3.8. Serial Input Interface B (SDIB)

54 4.3.9. Serial Output Interface (SDO)

54 4.3.10. S/PDIF Input Interface

55 4.3.11. S/PDIF Output Interface

55 4.3.12. Analog Input Interfaces

55 4.3.13. Analog Output Interfaces

55 4.3.14. Miscellaneous

56 4.4. Pin Configurations

58 4.5. Internal Pin Circuits

60 4.6. Electrical Characteristics

60 4.6.1. Absolute Maximum Ratings

61 4.6.2. Recommended Operating Conditions

64 4.6.3. Digital Characteristics

2

65 4.6.3.1. I

66 4.6.3.2. Serial (I

68 4.6.3.3. Serial Output Interface Characteristics (SDO)

70 4.6.3.4. S/PDIF Input Characteristics

71 4.6.3.5. S/PDIF Output Characteristics

72 4.6.3.6. PIO As Parallel Input Interface: Demand Mode

73 4.6.3.7. PIO as Parallel Output Interface

74 4.6.4. Analog Characteristics

77 4.6.5. DC/DC Converter Characteristics

78 4.6.6. Typical Performance Characteristics

80 4.7. Typical Application in a Portable Player

81 4.8. Recommended DC/DC Converter Application Circuit

C Characteristics

2

S) Input Interface Characteristics (SDI, SDIB)

82 5. Data Sheet History

License Notice

Supply of this implementation of AAC technology does not convey a license nor imply any right to use this implementation in any finished end-user or ready-to-use final product. An independant license for such use is required.

contact: aacla@dolby.com

4 Micronas

ADVANCE INFORMATION MAS 35x9F

MPEG Layer 2/3, AAC Audio Decoder,

G.729 Annex A Codec

Release Note: Revision bars indicate significant

changes to the previous edition. This data sheet

applies to MAS 35x9F version A2 .

1. Introduction

The MAS 35x9F is a single-chip, low-power MPEG

layer 2/3 and MPEG2-AAC audio stereo decoder. It

also contains the G.729 Annex A speech co mpress ion

and decompression technology for use in memorybased or broadcas t applica tions. Additiona l function ality is achievable via download software (e.g. CELP

voice decoder, Micronas SC4 (ADPCM) encoder /

decoder)

The MAS 35x 9F decoding block accepts compressed

digital da t a str e ams as serial bits tr ea m s , or pa rallel format and provides serial PCM and/or S/PD IF output

of decompressed au dio. In addition to the signal processing function the IC incorporates a high-performance stereo D/A co nverter, headphone amplifiers, a

stereo A/D converte r, a microphone amplifier, and two

DC/DC converters.

1.1. Features Firmware

– MPEG 1/2 layer 2 and layer 3 decoder

– Extension to MPEG 2 layer 3 for low bit rates

(“MPEG 2.5”)

– Extraction of MPEG Ancillary Data

–MPEG 2 AAC

2)

decoder (low complexity profile)

– Master or slave clock operation

– Adaptive bit rates (bit rate switching)

– Intelligent power management (processor clock is

dependent on sampling frequencies)

– Micronas G.729 Annex A speech compression and

decompression

– SDMI-compliant security technology

1)

– Stereo channel mixer

– Bass, treble and loudness function

– Micronas Dynamic Bass (MDB)

– Automatic Volume Control (AVC)

Thus, the MAS 35x9F provides a true ’ALL-IN-ONE’

solution that is ideally suited for highly optimized memory based portable music players with integrated

speech decoding function.

In MPEG 1 (IS O 11172-3), three hierarchical layers of

compression have been standardized. The most

sophisticated and complex, layer 3, allows compression rates of approximately 12:1 for mono and stereo

signals while still maintaining CD audio quality. Layer 2

(widely used in e.g. in DVD) achieves a compression of

8:1 without significant losses in audio quality.

The MAS 35x9F supports the ’Advanced Audio Coding’ (AAC) that is also defined as aprt of MPEG 2. AAC

provides compression rates up to 16:1. MPEG 2

defines several profiles for different applications. This

IC decodes the ’low complexity profile’ that is especially optimized for portable applications.

The MAS 35x9 F also imp lement s a voice encoder and

decoder that is c ompliant to the ITU Standard G.7 29

Annex A.

SC4 is a propr ietary Mic ronas speech codec technology that can be downloaded to the MAS 35x9F to

allow recording and playing back speech at various

sampling rates.

Interfaces

– 2 serial asynchronous interfaces for bitstreams and

uncompressed digital audio

– Parallel handshake bit stream input

2

– Serial audio output via I

S and related formats

– S/PDIF data input and output

2

– Controlling via I

C interface

Hardware Features

– Two independent embedded DC/DC converters

(e.g. for DSP and flash RAM supply)

– Low DC/DC converter start-up voltage (0.9 V)

– DC converter efficiency up to 95 %

– Battery voltage monitor

– Low supply voltage (down to 2.2 V)

– Low power dissipation (<70 mW)

– High-performance RISC DSP core

– On-chip crystal oscillator

– Hardware power management and power-off func-

tions

– Microphone amplifier

– Stereo A/D converter for FM/AM-radio and speech

input

– CD quality stereo D/A converter

– Headphone amplifier

Micronas 5

MAS 35x9F ADVANCE INFORMATION

– Noise and power-optimized volume

– External clock or crystal frequency of 13...20 MHz

1)

Not yet supported in version A2

2)

See License Note on page 4

– Standby current < 10 µA

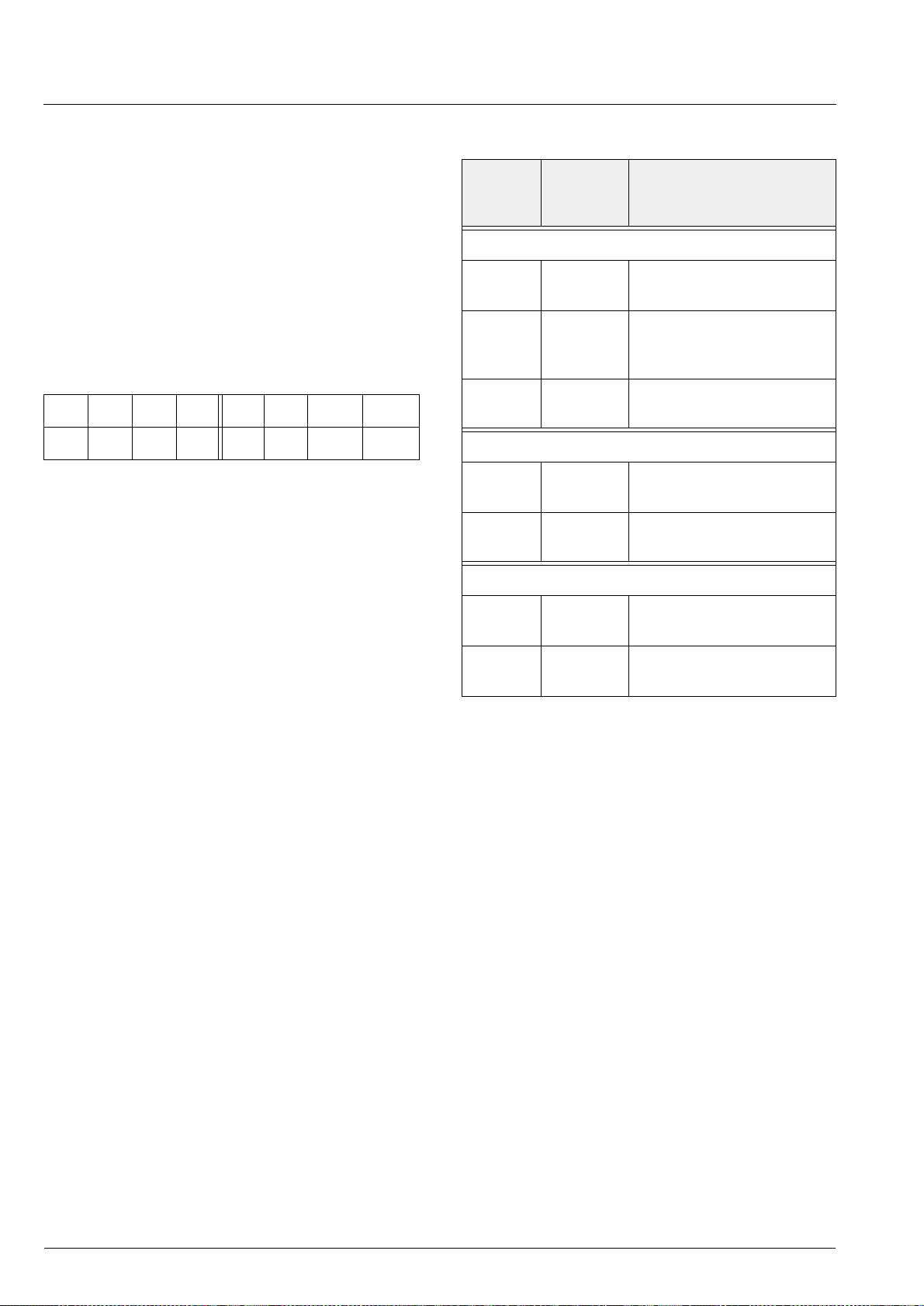

1.2. Features of the MAS 35x9F Family

Feature 3509 3519 3529 3539 3549 3559

Layer 3 Decoder XXXX

G.729 Encoder/Decoder X X X

AAC Decoder XX X

6 Micronas

ADVANCE INFORMATION MAS 35x9F

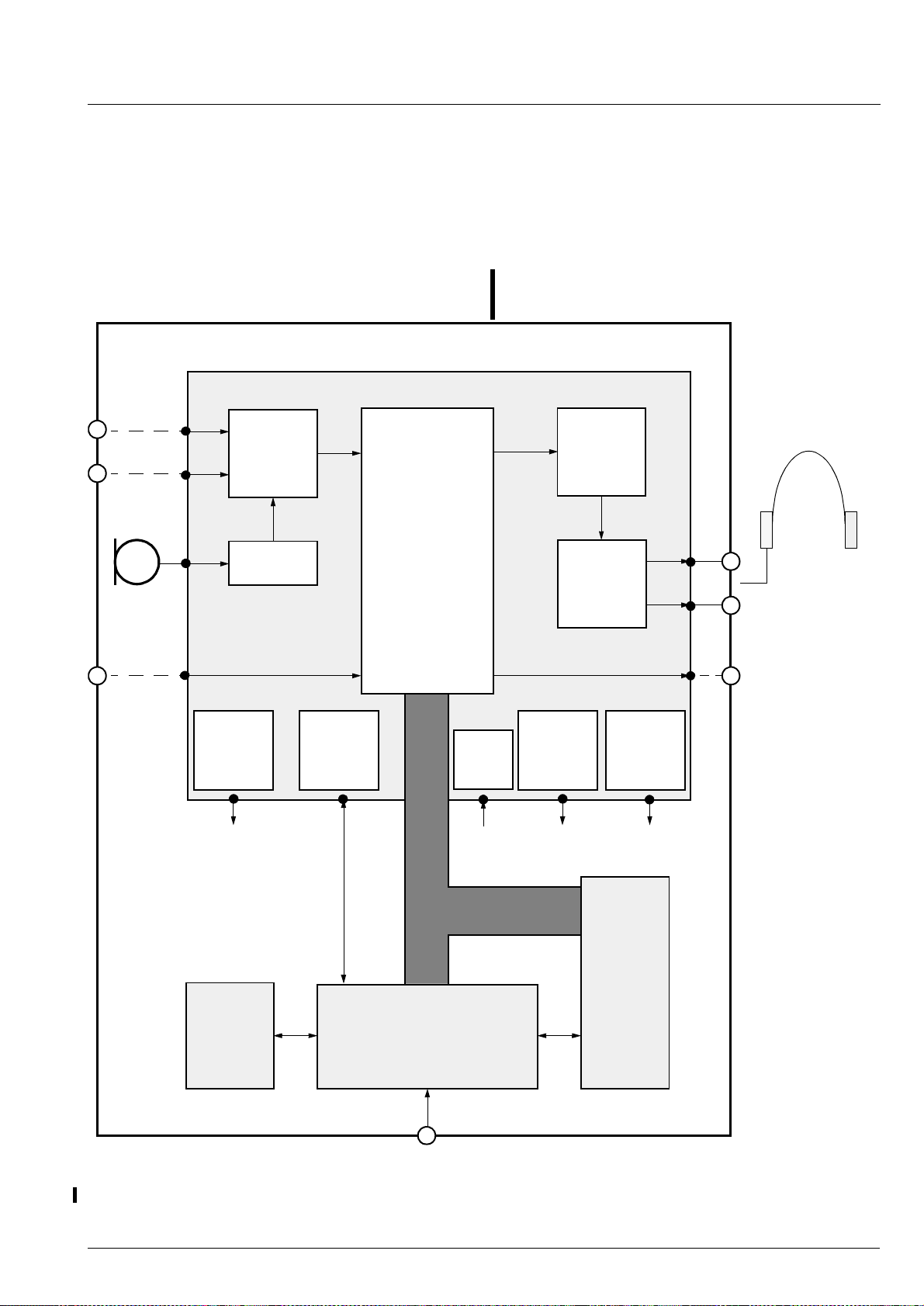

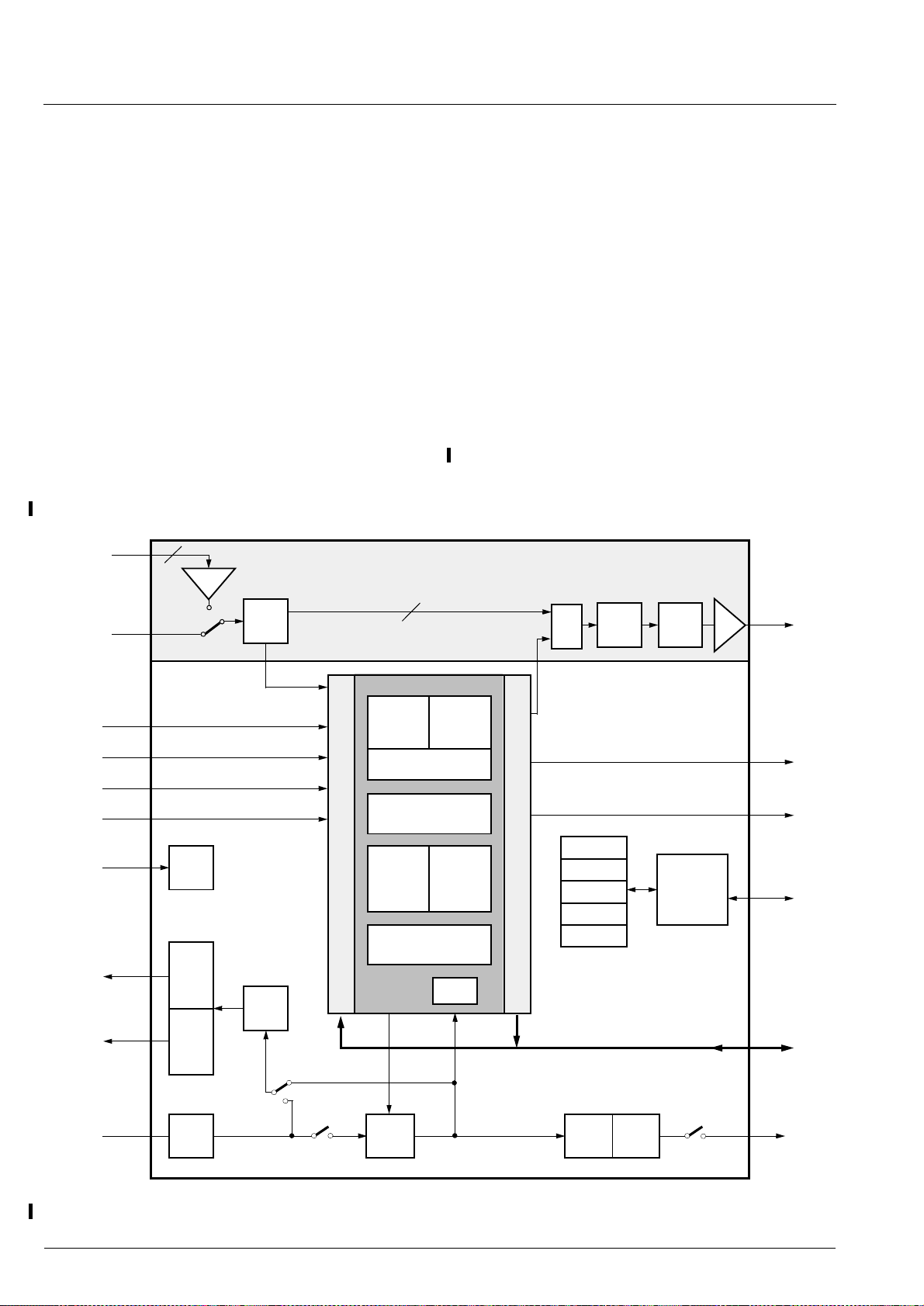

1.3. Application Overview

The following block diagram shows an example appl ication for the MAS 35x9F in a portable audio player

device. Besides a simple controller and the external

flash memories, all required components are integrated in the MAS 35x9F. The MAS 35x9F supports

both speech and ra dio quality audio enco ding, as well

as compressed-audio decoding tasks.

Portable Digital Music Player

MAS 35x9F

optional

line in

optional

digital in

S/PDIF

or

serial

Microphone

amplifier

Crystal

Osc./PLL

A/D

2

C DC/DC2

Audio

baseband

features

DSP Core

MP3

AAC

G.729

Optional

Software

Downloads

Battery

Voltage

Monitor

Fig. 1–1 depicts a portable audio application that is

power optimized. The two embedde d DC/DC converters of the MAS 35x9F generate optimum power supply

voltages for the DSP core and also for state-of-the art

flash memories that typically require 2.7 to 3.3 V supply.

The performance of the DC/DC converters reaches

efficiencies up to 95 %.

D/A

Headphone

amplifier

Volume

DC/DC1I

Headphone

digital out

S/PDIF or serial

System clock e.g. 2.2 V e.g. 3.0 V

C Control

2

I

Display

Keyboard

Fig. 1–1: Example application for the MAS 35x9F in a portable audio player device

Micronas 7

Parallel I/O Bus

PC Connector

C

µ

e.g. 1.0 V

I2C

Flash RAM

MAS 35x9F ADVANCE INFORMATION

2. Functional Description of the MAS 35x9F

2.1. Overview

The MAS 35x9F is intended for use in portable consumer audio applications. It receives S/PDIF, parallel

or serial data streams and decodes MPEG Layer 2

and 3 (including the low sampling frequency extensions) and MPEG 2 AAC. In addition, special downloadable software expands the function to a low-bitrate

CELP codec for speech recording. Other download

options (SDMI, other audio encoders/decoders) are

available on request. Compressed speech data may

be stored in an external memory via the parallel port.

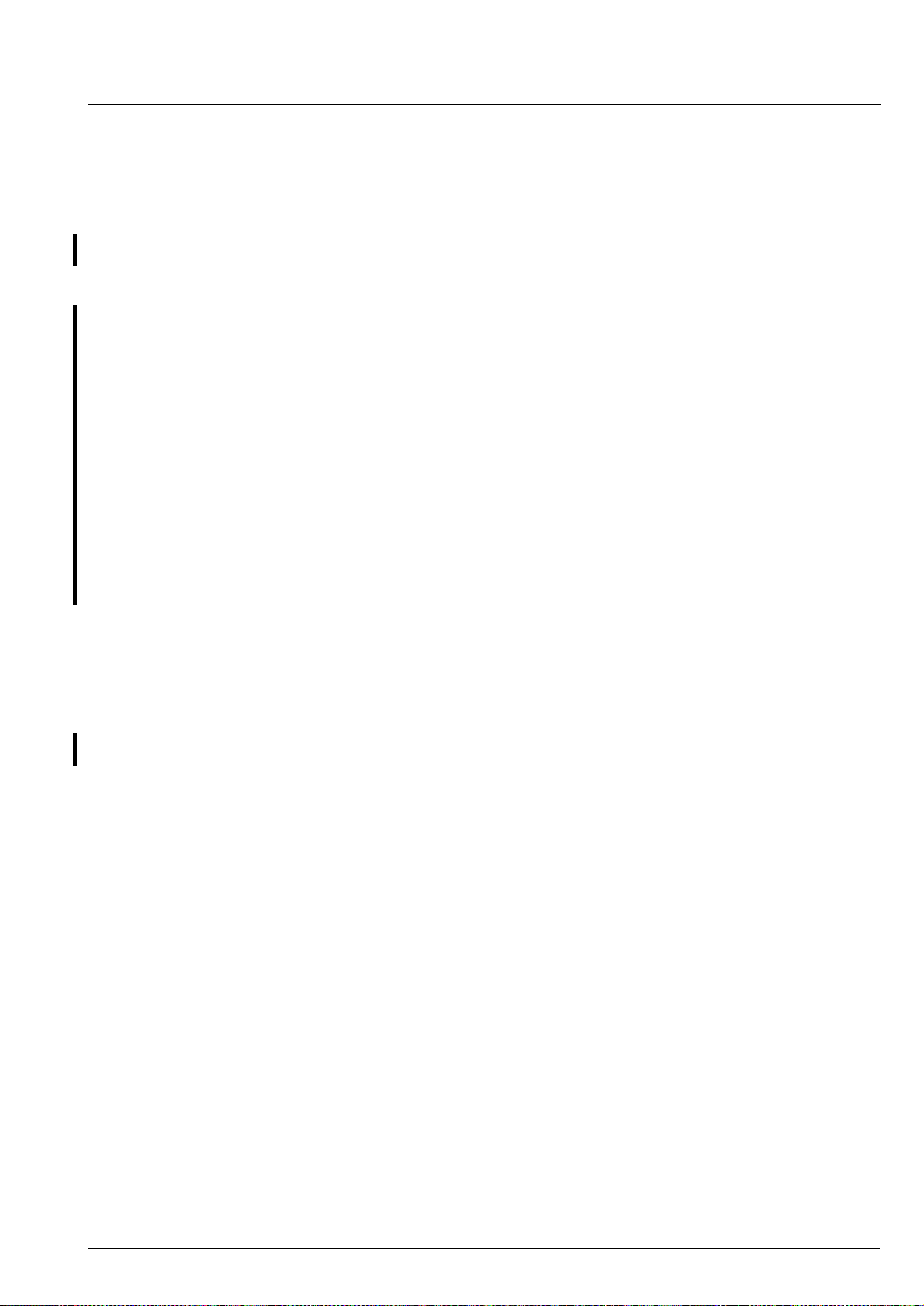

2.2. Architecture of the MAS 35x9F

The hardware of the MAS 35x9F consists of a highperformance RISC Digital Signal Processor (DSP),

Mic. Input

(incl. Bias)

Audio Codec

Line Input

1

2

A/D

and appropriate interfaces. A hardware overview of the

IC is shown in Fig. 2–1.

2.3. DSP Core

The internal processor is a dedicated DSP for

advanced audio applications.

2.3.1. RAM and Registers

The DSP core has access to two RAM banks de noted

D0 and D1. All RAM a ddresses can be accessed in a

20-bit or a 16-bit mode via I

2

C bus. For fast access of

internal DSP states the processor core has an address

space of 256 data regi ste rs which can be acce ss ed by

2

C bus. For more details please refer to Section 3.3.

I

on page 25.

2

MIX

Audio

Proc.

D/A

Audio

2

Output

S/PDIF Input 1

S/PDIF Input 2

Serial Audio

(I2S, SDI)

Serial Audio

(stream, SD IB)

V

BAT

V1

V2

Xtal

18.432 MHz

Volt.

Mon.

DC/DC 2 DC/DC 1

Div.

DSP Core

ALU MAC

Accumulators

Input Select

D0 D1

PLL

Synth.

ROM

Registers

Div.

Synthesizer

Clock

Serial

Audio

(I2S, SDO)

S/PDIF

Output

Control

Output Select

DCFR

DCCF

2

C

I

Interface

2

I

C

control

DSP

Codec

Parallel

I/O Bus

(PIO)

CLKO

ScalerOsc.

2

÷

Fig. 2–1: The MAS 35x9F architecture

8 Micronas

ADVANCE INFORMATION MAS 35x9F

2.3.2. Firmware and Software

2.3.2.1. Internal Program ROM and Firmware,

MPEG-Decoding

The firmware im pleme nted in the pr ogram ROM of the

MAS 35x9F provides MPEG 1/2 Layer 2, MPEG 1/2

Layer 3 and MPEG 2 AAC-decoding as well as a

G.729 encoder and decoder.

The DSP operating sy stem starts the firmware in the

“Application Selecti on Mode”. By setting the appro priate bit in the Application Select memory cell (see

Tab le3–6 on page 31) the MPEG audio deco der or the

G.729 Codec can be activated.

The MPEG decoder provides an automatic standard

detection mode. If all MPEG audio decoders are

selected, the Layer 2, Layer 3 or AAC bitstream is re cognized and decoded automatically.

To add/remove MPEG layers while running in MPEG

decoding mode (e.g. Layer 2, Layer 3 (0x0c) to

Layer 2, Layer 3, AAC (0x1c)), the application selection has to be reset before writing the new value.

For general control purposes, the operation system

provides a set of I

2

C instructions that give access to

internal DSP registers and memory areas.

2.4. Audio Codec

A sophisticated set of audio converters and sound features has been implemented to comply with various

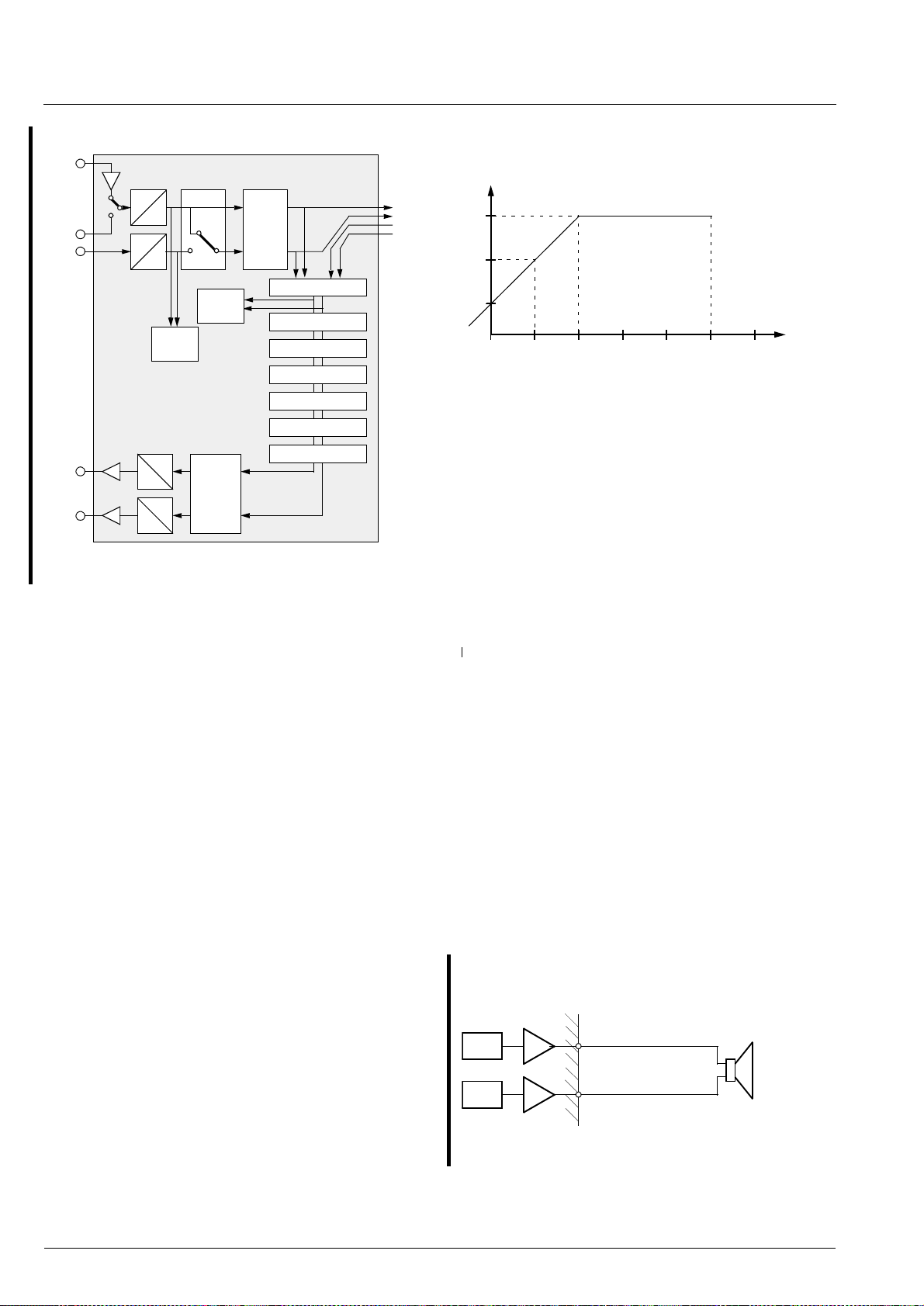

kinds of operating environ ments t hat range up to h ighend equipment (see Fig. 2–2 on page 10).

2.4.1. A/D Converter and Microphone Amplifier

A pair of A/D converters is provided for recording or

loop-through purposes. In addition, a microphone

amplifier inclu ding voltage supply function for an electret type microphone has been integrated.

2.4.2. Baseband Processing

The several baseband functions are applied to th e dig ital audio signal immediately before D/A conversion.

2.4.2.1. Bass, Treble, and Loudness

Standard baseband functions such as bass, treble,

and loudness are provided.

2.4.2.2. Micronas Dynamic Bass (MDB)

An auxiliar y digital volume control and mixer matrix is

applied to the digital stereo audio data. This ma trix is

capable of performing the balance control and a simple

kind of stereo basewidth enhanc ement. A ll four factors

LL, LR, RL, and RR are adjustable, please refer to Fig.

3–3 on page 40.

2.3.2.2. Program Download Feature

The standard functions of the MAS 35x9F can be

extended or substituted by downloading up to

4 kWords (1 Word = 20 bits) of program code and

additionally up to 4 kWords of coefficients into the

internal RAM .

The code must be downloaded by the

Download

command (see Section 3.3.1.14. on

Fast Program

page 29) into an area of RAM that is switchable from

Run

data memory to program memory. A

command

(see Section 3.3.1.1. on page 26) starts the operation.

The Micronas Dynamic Bass system (MDB) was

developed to extend the frequency range of loudspeakers or headphones below the cutoff frequen cy of

the speakers. In addit ion to dynamic ally ampl ifying the

low frequency bass signa ls, the MDB exploits the ps ychoacoustic phenomenon of the ‘missing fundamental’. Adding harmonics of the frequency components

below the cutoff frequency gives the impression of

actually hearing t he low frequency fundamental, while

at the same tim e retai ning t he loudne ss of t he or iginal

signal. Due to the parametric implementation of the

MDB, it can be customized to create different bass

effects and adapted to var ious loudsp eaker characteristics.

Micronas 9

MAS 35x9F ADVANCE INFORMATION

Mic-In

A

D

A

D

Line-In

Deemphasis

Mono

50µs / 75µs

Mixer

Mono/Stereo

AVC

Bass/Treble

Loudness

Right invert

A

D

A

D

Volume

Balance

Audio

Codec

Mic-Amplifier incl. Bias

DSP

Output

MDB

Headphone

Amplifier

Q-peak

Q-peak

output level

dBr

9

−

15

−

21

−

30

−

24

−

Fig. 2–3: Simplified AVC characteristics

2.4.2.4. Balance and volume

18−12

−

6

−

6

+

0

input level

dBr

To minimize quantization nois e, the main volume control is automatically split into a digital and an analog

part. Th e volume range is −114...+12 dB wit h an addi-

Fig. 2–2: Signal flow block diagram of Audio Codec

2.4.2.3. Automatic Volume Control (AVC)

In a collection of tracks from different sources fairly

often the average volume level varies. Especially in a

noisy listening environment the user must adjust the

volume to achieve a comfortable listening en joyment.

The Automatic Volume Correction (AVC) solves this

problem by equalizing the volume level.

To prevent clipping, the AVC’s gain decreases quickly

in dynamic boost conditions. To suppress oscillation

effects, the gain increases rather slowly for low level

inputs. The decay time is programmable by means of

the AVC register (see Table 3–13 on page 42).

For input levels of -18 dBr to 0 dBr, the AVC maintains

a fixed output level of -9 dBr. Fig. 2–3 shows the AVC

output level versus its input level. For volume and

baseband registe rs set to 0 dB, a level of 0 dBr corresponds to full scale input/output.

tional mute position. A balance function is provided.

2.4.3. D/A Converters

A pair of Micronas’ unique multibit sigma-delta D/A

converters is used to convert th e audio data with high

linearity and a superior S/N. In order to attenuate highfrequency noise caused by noise-shaping, internal

low-pass filters are included. They require additional

external capacitors between pins FILTx and OUTx.

2.4.4. Output Amplifiers

The integrated output amplifiers are capable of directly

driving stereo headphones or loudspeakers of

16...32Ω impedance via 22-Ω series re s i sto rs. I f m o re

output power is required, the right output signal can be

inverted and a single loudspeaker can be connected

as a bridge between pins OUTL and OUTR. In this

case for optimized power the source should be set to

mono.

MASF

DAC

DAC

OUTL

OUTR

R≥32

Fig. 2–4: Bridge operation mode

10 Micronas

Ω

ADVANCE INFORMATION MAS 35x9F

2.5. Clock Management

The MAS 35x9F is driven by a single crystal-controlled

clock with a frequency of 18.432 MHz. It is possible to

drive the MAS 35x9F with other reference clocks. In

this case, the nominal crystal frequen cy must be written into memory location D0:348. The crystal clock

acts as a reference for the embedded syn thesizer that

generates the internal clock.

For compressed audio data re cepti on, the MA S 35x9F

may act either as the clock master (De mand Mode) or

as a slave (Broadcast Mode) as defined by bit 1 in

IOControlMain memory cell (see Table 3–7 on

page 32). In both mode s, the output of the clock synthesizer depends on t he sample rate of the decoded

data stream as shown in Table 2–1.

In the BROADCAST MODE (PLL on), the incoming

audio data controls the clock synthesizer via a PLL.

In the DEMAND MODE (PLL off) t he MAS 35x9F acts

as the system master clock. The da ta transfer is triggered by a demand signal at pin EOD

.

2.5.1. DSP Clock

The DSP clock has sep arate divider. For power conservation it is set to th e lowest acceptable rate of the

synthesizer clock which is capable to allow the processor core to perform all tasks.

2.6. Power Supply Concept

The MAS 35x9 F ha s been de si gn ed for minimal power

dissipation. In order to optimize the battery management in por table players, two DC/DC converters have

been implemented to supply the complete portable

audio player with regulated voltages.

2.6.1. Power Supply Regions

The MAS 35x9F has five power supply regions.

The VDD/VSS pin pa ir suppl ies all di gital p ar ts inc lud-

ing the DSP core, the XVDD/XVSS pin pair is connected to the digital signal pin output buffers, the

AVDD0/AVSS0 supply is for the analog output amplif iers, AVDD1/AVSS1 for all other analog circuits like

clock oscillator, PLL circuits, system clock synthesi zer

and A/D and D/A converter s. The I

own supply region via pin I 2CVDD. Connecting this to

the microcontroller supply assures that the I

2

C interface has an

2

C bus

always works as long as t he mic rocontr olle r is al ive so

that the operating modes can be selected.

Beside these regions, the DC/DC converters have

start-up circuits of their own which get their power via

pin VSENSx .

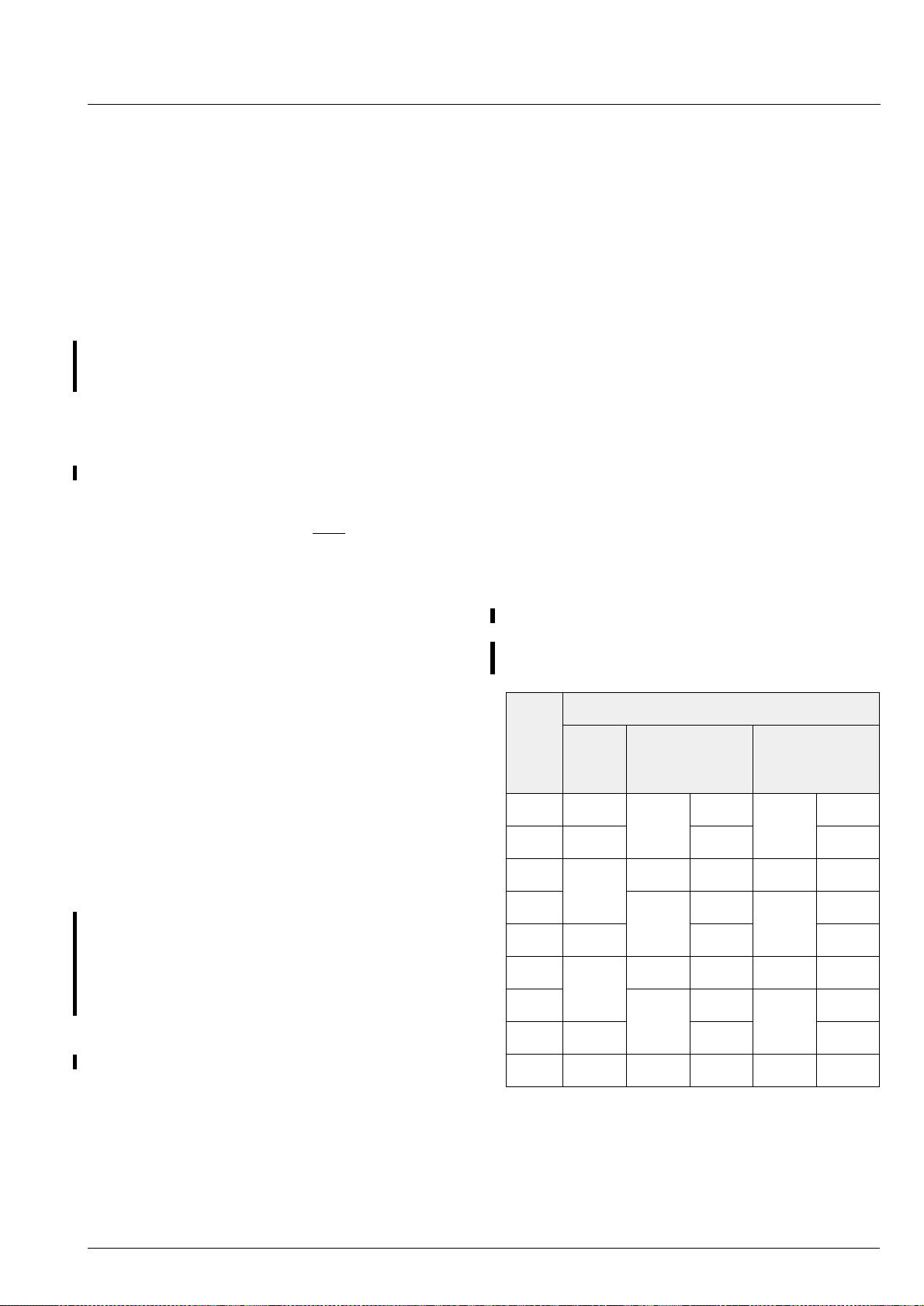

Table 2–1: Settings of bits 8 and 17 in OutClkConfig

and resulting CLKO output frequencies

Output Frequency at CLKO/MHz

2.5.2. Clock Output At CLKO

If the DSP or audio codec functions are enabled (bits

11 or 10 in the Control Register at I

), the reference clock at pin CLKO is derived from

6a

hex

2

C subaddress

the synthesizer clock.

Dependent on the sample rate of the decoded signal a

scaler is applied which auto m at ic ally div id es the c lo ckout by 1, 2, or 4, as shown in Table 2–1. An additional

division by 2 may be selected by setting bit 17 of the

OutClkConfig memory cell (see Table 3–7 on

page 32). The scaler can be disabled by setting bit 8 of

this cell.

The controlling at OutClkConfig is only possible as

long as the DSP is ope rational (bit 10 of the Control

Register). Setting s remain valid if the DSP i s disabled

by clearing bit 10.

Synth.

fs/kHz

Clock

bit 8=1

48 24.576

44.1 22.5792 22.5792 11.2896

32

Scaler On

bit 8=0, bit 17=0

Extra Division

bit 8=0, bit 17=1

24.576

512⋅f

s

24.576 384⋅fs 12.288

768⋅f

s

256⋅fs

Scaler Plus

12.288

24.576

24

512⋅f

22.05 22.5792 11.2896 5.6448

16

768⋅f

12.288

s

12.288 384⋅fs 6.144

s

256⋅fs

6.144

24.576

12

512⋅f

11.025 22.5792 5.6448 2.8224

8 24.576 768⋅f

6.144

s

6.144 384⋅fs 3.072

s

256⋅fs

3.072

Micronas 11

MAS 35x9F ADVANCE INFORMATION

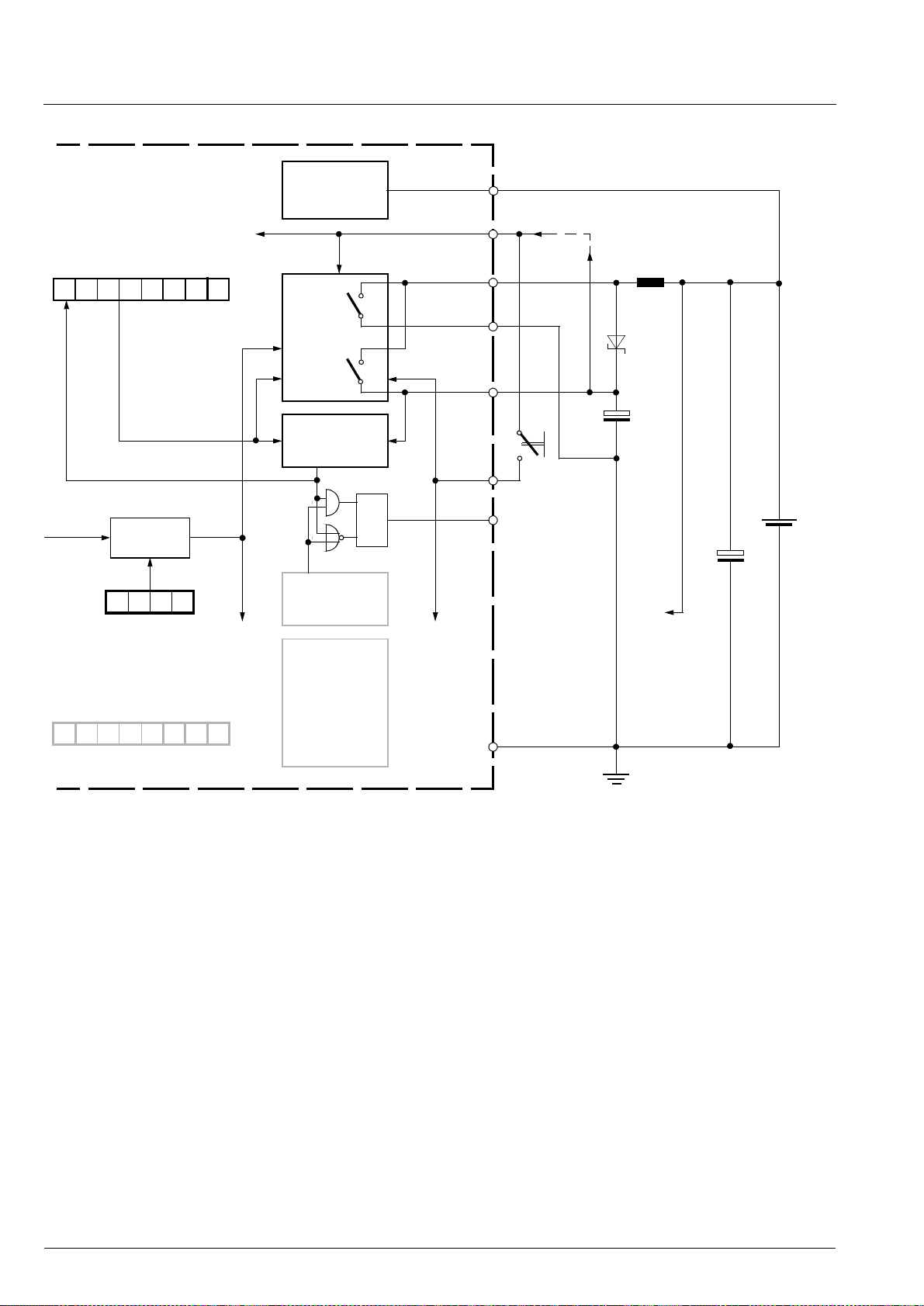

2.6.2. DC/DC Converters

The MAS 35x9F has two em bed ded high-performance

step-up DC/DC co nverters with sy nchronous recti fiers

to supply both the DSP core itself and external circuitry

such as a controller or flas h memory at two different

voltage levels. An overview is given in Fig. 2–9 on

page 14.

The DC/DC converters are designed to generate an

output voltage between 2.0 V and 3.5 V which ca n be

programmed separately for each converter via the I

2

interface (see table 3.3). Bot h converters are of bo otstrapped type allowing to start up from a voltage down

to 0.9 V f or us e wi th a si ngl e ba tt ery or Ni Cd/N iMH c el l.

The default output voltages a re 3.0 V. Both converters

are enabled with a high level at pin DCEN and

enabled/disabled by the I

2

C interface.

The MAS 35x9F DC/DC converters feature a constantfrequency, low noise pulse width modulation (PWM)

mode and a low quiescent current, pulse frequency

modulation (PFM) mode for improved efficiencies at

low current loads. Both m odes – PWM or PFM – ca n

be selected indepe ndently for each converter via I

2

interface. The default mode is PWM.

In PWM mode the switching frequen cy of the power-

MOSFET-switches is derived from the crystal oscillator. Switching harmonics generated by constant frequency operation are consistent and predictable.

When the audio codec is enabled the switching frequency of the conver ters is synchroni sed to the audi o

codec clock to avoid interferences into the aud io band .

The actual switching frequency can be selected via the

2

C-interface between 300 kHz and 580 kHz (for

I

details see DCFR Register in Table 3–3 on page 21).

In PFM operation mode the switching frequency is

controlled by the converters themself, it will be just

high enough to service the output load thus resulting in

the best possible effic iency at low current lo ads. PFM

mode does not need a clock signal from the crystal

oscillator. If both converters do not use the PWMmode, the cryst al clock will be shut down as lon g it is

not needed from other internal blocks.

The synchronous rectifier bypasses the external

Schottky diode to re duce losses caused by the d iode

forward voltage providing up to 5% efficiency imp rovement. By default, the P-channel syn chronous rectifier

switch is turned on when the voltage at pin(s) DCS On

exceeds the converter’s output voltage at pin(s)

VSENSn and turns off when the inductor current drops

below a threshold. If one or both converters are disabled, the corresponding P-channel switch will be

turned on, connecting the battery voltage to the DC/

DC converters output voltage at pin VSENSn. However, it is possible to individuall y disable both sy nchronous rectifier switches by setting the corresponding

bits (bit 8 and 0 in DCCF-register).

If both DC/DC-converters are off, a high signal may be

applied at pin DCE N. This will star t the converters in

their default mode (PWM with 3.0 V output voltage).

The PUP signal will change from low to high when both

converters have reached their nominal output voltage

and will return to low when both converters output voltages have dropped 200 mV below their programmed

output voltage. The signal at pin PUP ca n be used to

control the reset of an external microcontroller (see

Section 2.10.2. on page 16 for details on start up procedure).

C

If only DC/DC-converter 1 is used, the output of the

unused converter 2 (VSEN S2) must be connected to

the output of converter 1 (VSENS1) to make the PUP

signal work proper ly. Also, if a DC/DC-converter is not

used (no inducto r connected), the pin DCSO must be

left vacant.

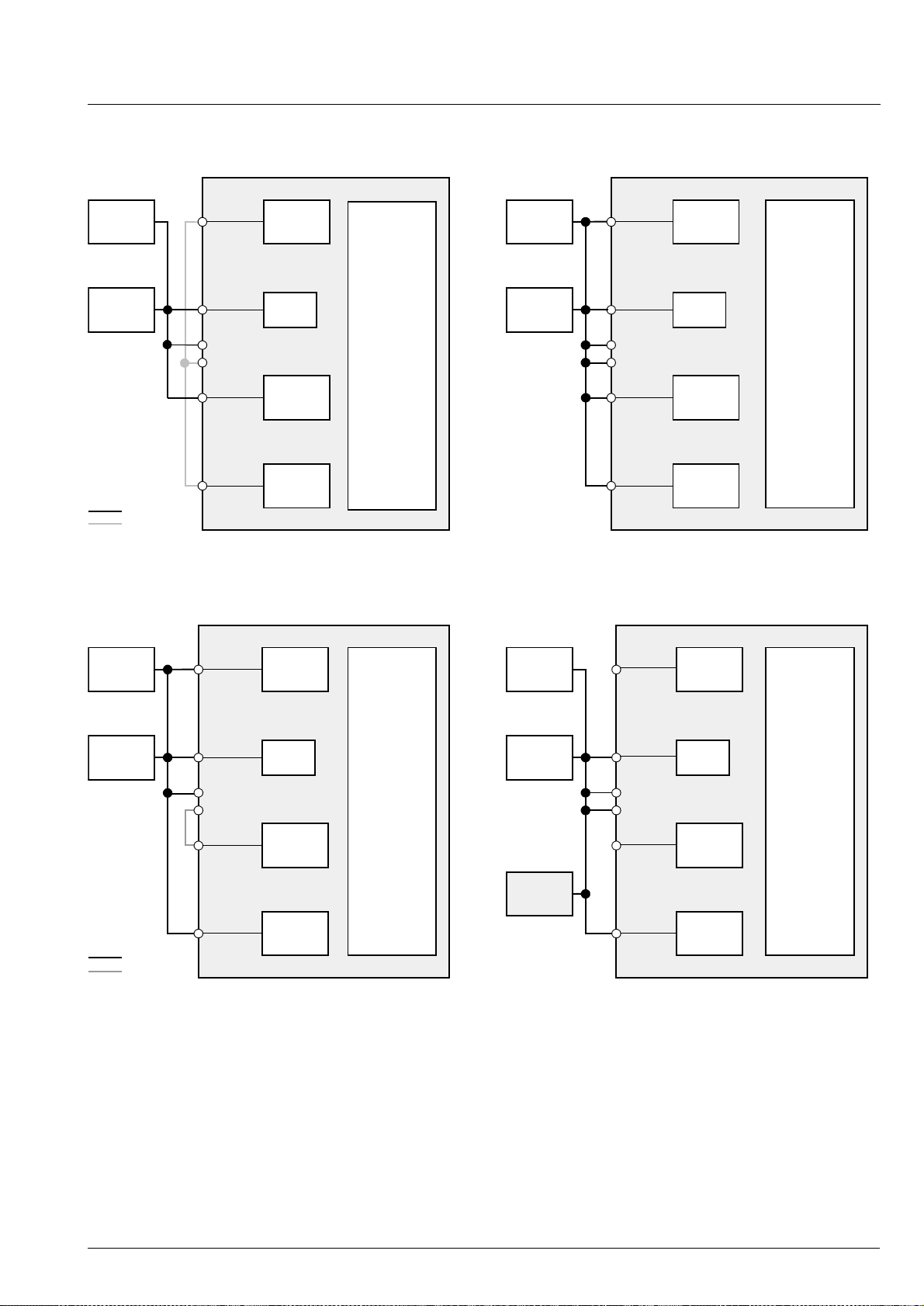

2.6.3. Power Supply Configurations

One of the following supply configurations may be

used:

C

– Power-optimized solution (recommended opera-

tion). DC/DC 1 (e.g. 2.2 V) drives the MAS 35x9F

DSP and the audio circuitry, DC/DC 2 (e.g. 2.7 V)

supplies controller and flash (see Fig. 2–5 on

page 13)

– Volume-optimized solution. DC/DC 1 (e.g. 2.7 V)

supplies controller, flash and MAS 35x9F audio

parts, DC/DC 2 generates e.g. 2.2 V for the

MAS 35x9F DSP (see Fig. 2–6 on page 13).

– Minimized external components. DC/DC 1 operates

on e.g. 2.7 V and feeds all components, DC/DC 2

remains off (see Fig. 2–7 on page 13).

– External power supply . All components are powered

by an external source, no DC/DC converter is used

(see Fig. 2–8 on page 13).

If DC/DC converter 1 is used, it must supply the analog

circuits (pins AVDD0, AVDD1) of the MAS 35x9F.

If only one DC/DC converter is required, DC/DC1 must

be used. Pin DCSO2 must be left vacant, pin VS ENS 2

should be connected to pin VSENS1.

If the DC/DC converters a re not us ed, pi n DCEN mus t

be connected to VSS, DCSOx must be left vacant.

12 Micronas

ADVANCE INFORMATION MAS 35x9F

Flash

C

µ

VSENS1

2

CVDD

I

XVDD

VDD

VSENS2

AVDD0/1

DC/DC 1

on

2

I

C

DC/DC 2

on

Analog

Parts

e.g. 2.7 V

e.g. 2.2 V

Fig. 2–5: Solution 1: Power-optimized

Flash

VSENS1

DC/DC1

on

DSP

Flash

e.g. 2.7 V

C

µ

VSENS1

2

CVDD

I

XVDD

VDD

VSENS2

AVDD0/1

DC/DC1

on

I2C

DC/DC2

off

Analog

DSP

Parts

Fig. 2–7: Solution 3: Minimized components

Flash

VSENS1

DC/DC1

off

2

CVDD

C

µ

e.g. 2.7 V

e.g. 2.2 V

I

XVDD

VDD

VSENS2

AVDD0/1

I2C

DC/DC2

on

Analog

Parts

Fig. 2–6: Solution 2: Volume-optimized

DSP

2

I

C

µ

CVDD

VDD

XVDD

VSENS2

I2C

DC/DC2

off

External

Supply

AVDD0/1

e.g. 2.7 V

Analog

Parts

Fig. 2–8: Solution 4: External power supply

DSP

Micronas 13

MAS 35x9F ADVANCE INFORMATION

to I2C interface

DCCF (76

15 8

)

hex

set voltage

frequency

system

or crystal

clock

divider

factor

30

DCFR (77

hex

)

battery

voltage

monitor

DC/DC

converter 2

voltage

monitor

voltage

monitor

VBAT

PUP

supply

StartPUP2

output 1

D1

+

−

330µF

L1

22µH

C1

V

in

+

−

+

−

I2CVDD

DCSO2

DCSG2

VSENS2

DCEN

S

R

DCCF (76

70

hex

)

converter 1

VSS

Fig. 2–9: DC/DC converter overview. The DCEN input must be connected to pin I2CVDD via the start-up push

button.

2.7. Battery Voltage Supervision

A battery voltage super vision circuit (at pin VBAT) is

provided which is independe nt of the DC/DC converters. It can be programmed to supervise one or two battery cells. The voltage is measured by subsequently

setting a series of voltage t hr eshol ds and c he cking the

DC/DC

respective comparison result in register 77

hex

.

14 Micronas

ADVANCE INFORMATION MAS 35x9F

2.8. Interfaces

2

The MAS 35x9F uses an I

input interface for MPEG bit streams, and a digital

audio output inter face for the decoded audio data (I

C control interface, a serial

2

or similar). Alter natively, SPDIF input and output interfaces can be used. A parallel I/O interface (PIO) m ay

be used for fast data exchange.

2

2.8.1. I

For controlling and program download purposes, a

standard I

C Control Interface

2

C slave interface is implemented. A detailed

description of all functions can be found in Section 3.

2.8.2. SPDIF Input Interface

The SPDIF interface receives a one-wire serial bus

signal. In addition to the signal input pin SPDI1/SPDI2,

a reference pin SPDIR is provided to support balanced

signal sources or twisted pair transmission lines.

The synchronization time on the input signal is

<50ms.

In case of the Deman d Mode (see Section 2.5.), the

signal clock coming from the data source must be

higher than the nominal data transmission rate (e.g.

128 kbit/s). Pin EOD

S

whenever the input buffer of the MAS 35x9F is filled.

is used to interrupt the data flow

For controlling details please refer to Table 3–7 on

page 32.

2.8.5. Multiline Serial Output (SDO)

The serial au dio output interface of the MAS 35x9F is

a standard I

2

S-like interface consisting of the data

lines SOD, the word strobe SOI and t he clock signal

SOC. It is possible to choose between two standard

interface configurations (16-bit data words with word

strobe time offset or 32-bit data words with inverted

SOI-signal).

If the serial output generates 32 bits per audio sample,

only the first 20 bits will carry valid audio data. The

12 trailing bits are set to zero by default.

2.8.6. Parallel Input/Output Interface (PIO)

The SPDIF input signal can also be switched to the

SPDO pin. In this case the analog input ci rcuit of the

SPDIF inputs (see Fig. 4–18 on page 59) restores the

SPDIF input signal to a full swing signal at SPDO.

For controlling details please refer to Table 3–7 on

page 32.

2.8.3. S/PDIF Output

In the next version of the IC the S/PDIF ou tput of the

baseband audio signals will be provided at pin SPDO.

2.8.4. Multiline Serial Audio Input (SDI, SDIB)

There are two multiline serial audio input interfaces

(SDI, SDIB) each consisting of the three pins SI(B)C,

SI(B)I, and SI(B)D. The standard firmware only supports SDIB for bitstream signals.

The interfaces can be configured as continuous bit

stream or word-oriented inputs. For the MPEG bitstreams the word strobe pin SI BI must always be connected to V

, bits must be sent MS B first as creat ed

SS

by the encoder.

The parallel interface of the MAS 35x9F consists of the

8 data lines PI12...PI19 (MSB) and the control lines

, PR, PRTR, PRTW, and EOD. It can be used for

PCS

data exchange with an external memory, for fast program download and for other special purposes as

defined by the DSP software.

For MPEG-data input, the PI O inte rface is ac tivated by

setting bits 9,8 in D0:346 to 01. For the handshake

protocol please refer to Section 4.6.3.6. on page 72

If the optional downloadable software uses th e inputs

for PCM data, the interface acts as a I

2

S-type with

SI(B)I as a word strobe.

Micronas 15

MAS 35x9F ADVANCE INFORMATION

V

h

V

l

t

read

t

frame

= 24...72 ms

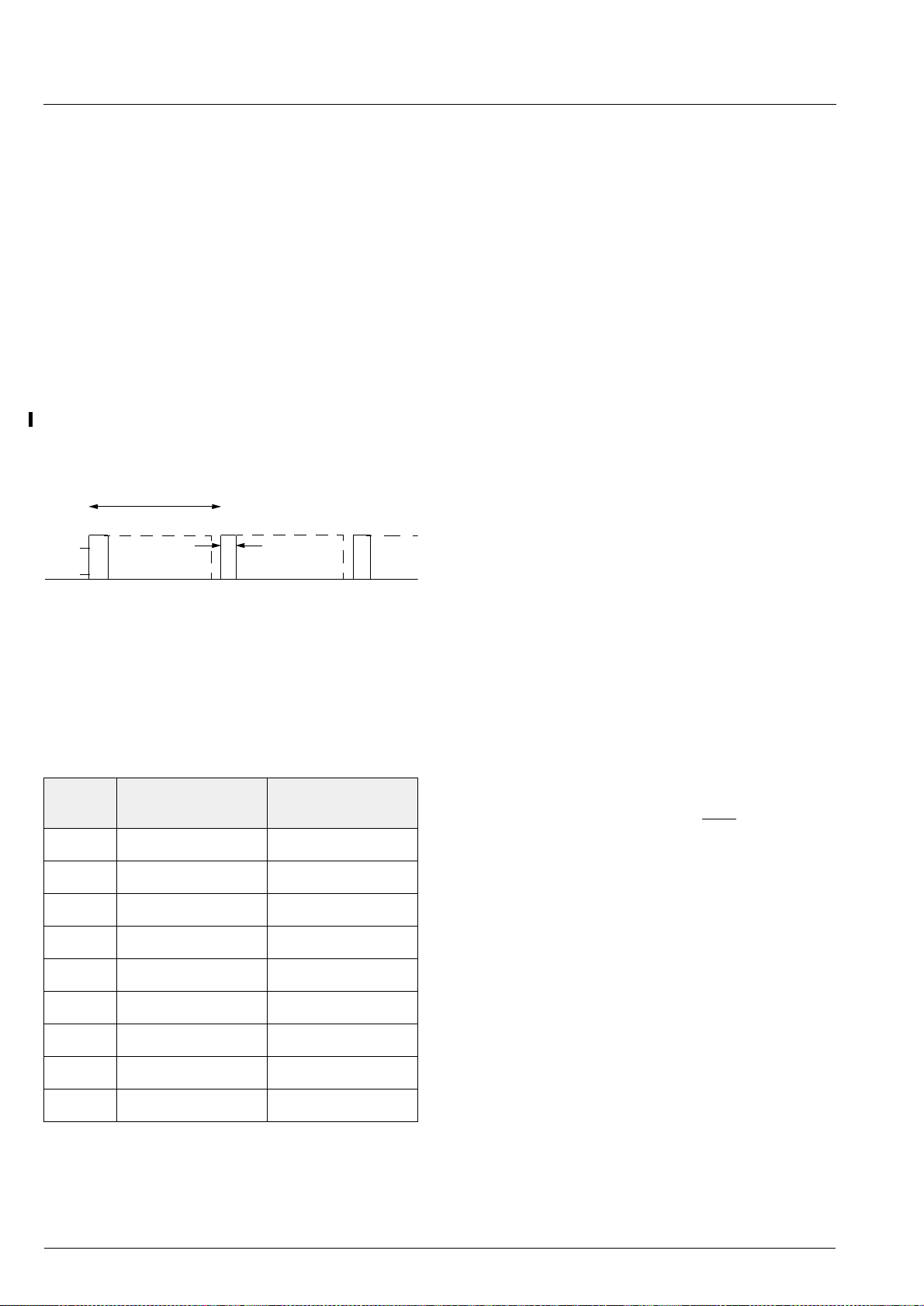

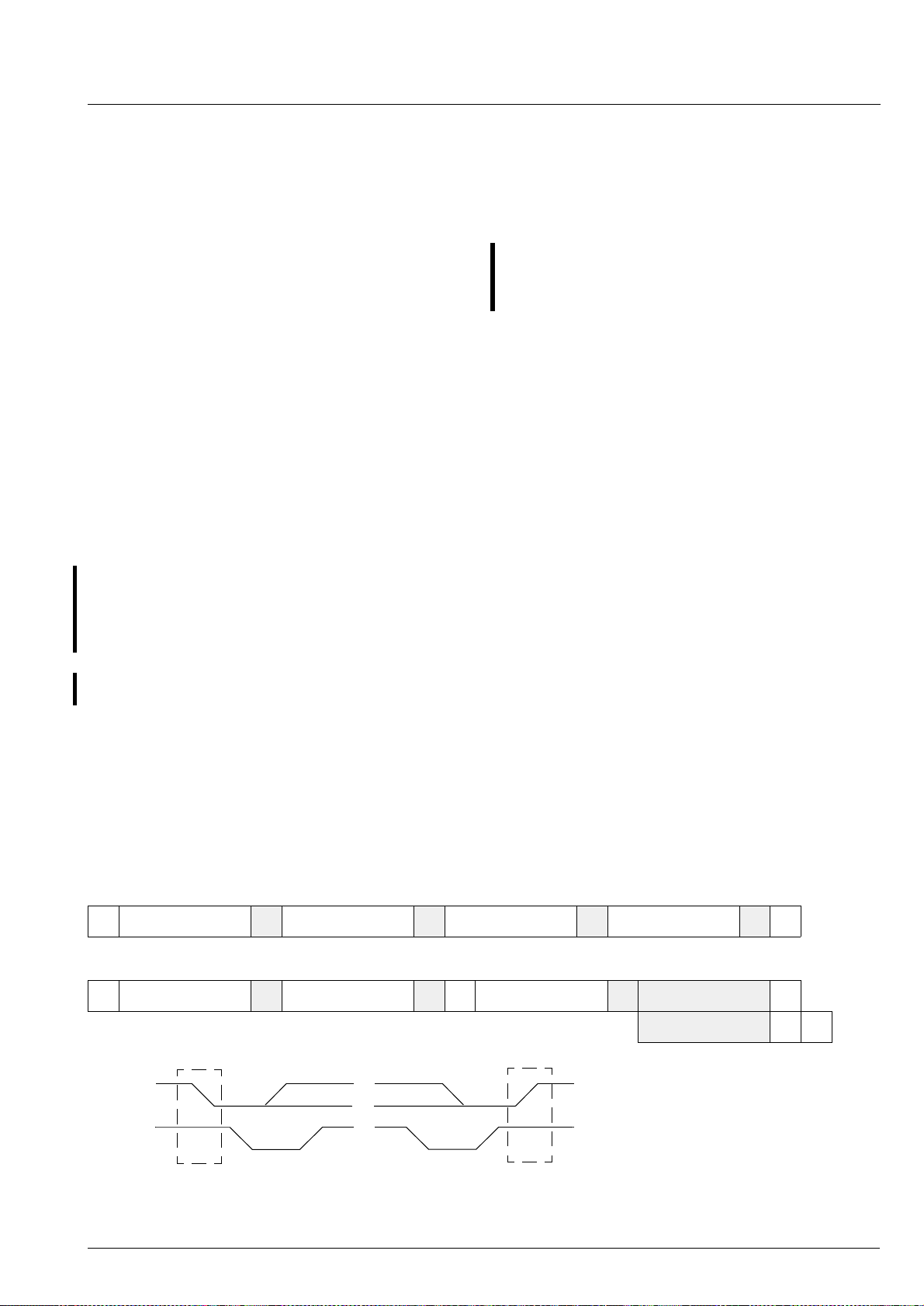

2.9. MPEG Synchronization Output

The signal at pin S YNC is set to ‘1’ after the inter nal

decoding for the MPEG header has been finished for

one frame. The rising e dge of this signal can be used

as an interrupt input for the controller that triggers th e

read out of the control in formation and ancillar y data.

As soon as the MAS 35x9F has received the SYNC

reset command (see Section 3.3.1.12. on page 28),

the SYNC signal is clea red. If the controller does not

issue a reset comman d, the SY NC signal returns to ’0’

as soon as the decodi ng of the next MPEG frame is

started. MPEG status and ancillary data become

invalid until the frame is completely de coded and the

signal at pin SYNC rises again. The controller must

have finished reading all MPEG information before it

becomes invalid. The MPEG Layer 2/3 frame lengths

are given in Table 2–2. AAC has no fixed frame length.

Fig. 2–10: Schematic timing of the signal at pin SYNC.

The signal is cleared at t

when the controller has

read

issued a Clear SYNC Signal command (see Section

3.3.1.12. on page 28). If no command is issued, the

signal returns to ’0’ just before the decoding of the next

MPEG frame.

Table 2–2: Frame length in MPEG Layer 2/3

fs/kHz Frame Length

Layer 2

Frame Length

Layer 3

48 24 ms 24 ms

44.1 26.12 ms 26.12 ms

32 36 ms 36 ms

24 24 ms 24 ms

22.05 26.12 ms 26.12 ms

16 36 ms 36 ms

12 not available 48 ms

11.025 not available 52.24 ms

8 not available 72 ms

2.10.De fau lt Operatio n

This sections refers to the standard operation mode

”power-optimized solution” (see Section 2.6.3.).

2.10.1.Stand-by Functions

After applying the battery voltage, the system will

remain stand-by, as long as the DCEN pin level is kept

low. Due to the low stand-by current of CMOS circuit s,

the battery may remain connected to DCSOn/VSENSn

at all times.

2.10.2.Power-Up of the DC/DC Converters and Reset

The battery voltage must b e appl ied to p in DCSOn via

the 22-µH inductor and, further more, to the sense pin

VSENSn via a Schottky diode (see Fig. 2–9 on

page 14).

For start-up, the pin DCEN must be co nnected via an

external “start” push button to the I2CVDD supply,

which is equivalent to the battery supply voltage

(> 0.9 V) at start-up.

The supply at DCEN must be appli ed until the D C/DC

converters have started up (signal at pin PUP) and

then removed for normal operation.

As soon as the outp ut voltag e at VS E NSn r eaches th e

default voltage monitor reset level of 3.0 V, the respective internal PUPn bit will be set. When both PUPn bits

are set, the signa l at pin PUP will go high and can be

used to start and reset the microcontroller.

2

Before transmitting any I

must issue a power-on reset to pin POR

supply pin I2CVDD assures that the I

C commands, the controller

. The separate

2

C interface

works indepentently of the DSP or the audio codec.

Now the desired supply voltage can be programmed at

2

C subaddress 76

I

The signal at pin PUP will return to low only when both

PUPn flags (I

2

.

hex

C subaddress 76

) have returned to

hex

zero. Care must be taken when changing bo th DC/DC

output voltages to higher values. In this case, both output voltages are momentarily insufficient to keep the

PUPn flags up; the resulting dip in the signal at the

PUP pin may in turn reset the microcontroller. To avoid

this condition, on ly one DC/DC output voltage should

be changed at a time. Before modifying the second

voltage, the microcontroller must wait for the PUPn flag

of the first voltage to be set again.

The operating mode (pulse width modulation or pulse

frequency modula tion, sy nchron ized rect ifier for higher

efficiency) are control led at I

16 Micronas

operating frequency at I

2

C subaddress 76

2

C subaddress 77

hex

.

hex

, the

ADVANCE INFORMATION MAS 35x9F

2.10.3.Control of the Signal Processing

Before starting the DSP, the controller should check for

a sufficient voltage supply (respective flag PUPn at I

subaddress 76

appropriate b it in the Co ntrol register (I

). The nominal freque ncy of the crys tal oscillator

6a

hex

). The DSP is enabled by setting the

hex

2

C subaddress

2

must be written into D0:348. After an initialization

phase of 5 ms, the DSP data registers can be

accessed via I

2

C.

Input and output control is performed via memory location D0:346 and D0:347. The serial input interface

SDIB is the default. The d ecoded a udio can be routed

to either the SPDIF, the SDO and the analog ou tputs.

The output clock signal at pin CLKO is defined in

D0:349.

All changes in the D0-mem ory cells become effective

synchronously upon setting the LSB o f Main I/O Con-

trol (see Table 3–7 on page 32). Therefore, this cell

should always be written at last.

The digital volume contr ol (see Table 3–7 on page 32)

is applied to the output signal of the DSP. The decoded

audio data will be available at the SPDO output interface in the next version.

2.10.5.Power-Down

All analog outputs s hould be muted and the A/D and

C

the D/A converters must be switched off (register

00 10

and 00 00

hex

at I2C subaddress 6c

hex

hex

). The

DSP and the audio codec must be disabled (clear

DSP_EN and CODEC_EN bits in the Control register,

2

C subaddress 6a

I

enable flags in the Control register (I

), the microcont roller can power down the c om-

6a

hex

). By clearing both DC/DC

hex

2

C subaddress

plete system.

The DSP does not have to be star ted if its functions

are not needed, e.g. for routing audio via the A/D and

the D/A converters through the codec part of the IC.

2.10.4.Start-up of the Audio Codec

Before enabling the audio codec, the controlle r should

check for a sufficient voltage supply (respective flag

PUPn at I

The audio codec is enabled by setting the app ropriate

bit at the Control register (I

an initialization phase of 5 ms, the DSP data registe rs

can be accessed via I

ers must be switched on explicitly (00 00

address 6c

data from the A/D converte rs or th e output o f the DSP,

or a mix of bo th

subaddress 6c

ume (00 10

2

C subaddress 76

2

C.The A/D and the D/A convert-

). The D/A converters may either ac cept

hex

1)

(register 00 06

). Finally, an appropriate output vol-

hex

at I2C subaddress 6c

hex

).

hex

2

C subaddress 6a

hex

and 00 07

hex

hex

at I2C sub-

) must be

hex

hex

). After

at I2C

selected.

1)

mixer available in version A2 and later; in version A1

please use selector 00 0f

hex

.

Micronas 17

MAS 35x9F ADVANCE INFORMATION

3. I2C Interface

3.1. General

3.1.1. Device Address

2

Controlling the MAS 35x9F is done via an I

interface. The device addresses are 3C/3E

write) and 3D/3F

1. The device address pair 3C/3D

(device read) as shown in Table 3–

hex

applies if the DVS

hex

C slave

(device

hex

pin is connected to VSS, the device address pair 3E/

applies if the DVS pin is connected to VDD.

3F

hex

Table 3–1: I

2

C device address

A7 A6 A5 A4 A3 A2 A1 W/R

001111DVS0/1

2

C clock synchronization is used to slow down the

I

interface if required.

2

3.1.2. I

C Registers and Subaddresses

The interface uses one level of subaddresses. The

MAS 35x9F interface has 7 subaddresses allocated for

the correspondin g I

2

C registers. The registers can be

divided into three categories as shown in Table 3–2.

The address 6A

is used for basic con trol, i.e. reset

hex

and task select. The other addresses are used for data

transfer from/to the MAS 35x9F.

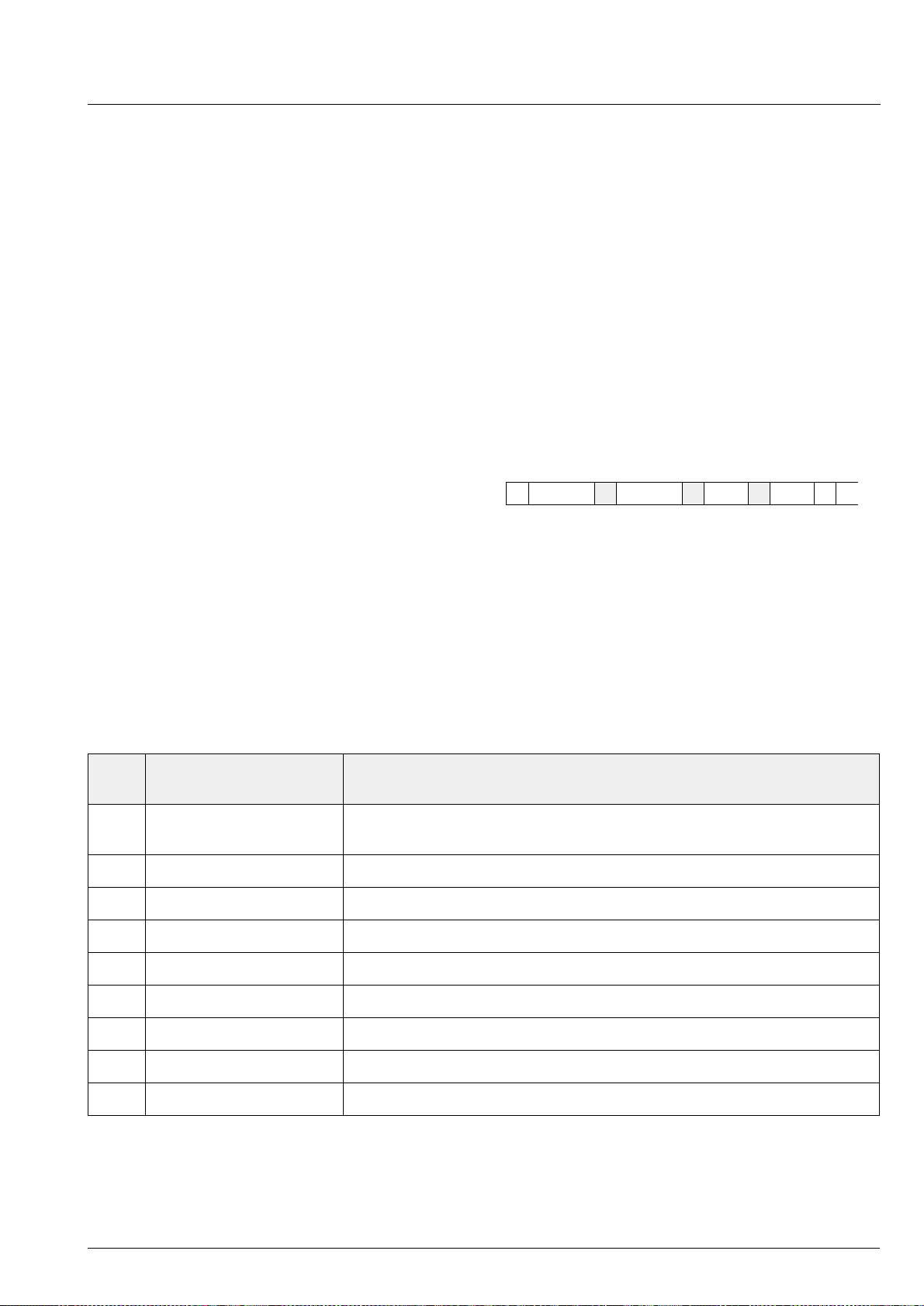

Table 3–2: I2C subaddresses

Subaddress

(hex)

I2CRegister

Name

Function

Direct Configuration

6A CON-

TROL

Controller writes to

MAS 35x9F control register

76 DCCF Controller writes to first

DC/DC configuration register

77 DCFR Controller writes to

second DC/DC config reg.

DSP Core Access

68 DATA

(WRITE)

69 DATA

(READ)

Controller writes to

MAS 35x9F DSP

Controller reads from

MAS 35x9F DSP

Codec Access

6C CODEC

(WRITE)

6D CODEC

(READ)

Controller writes to

MAS 35x9F codec register

Controller reads from

MAS 35x9F codec register

2

C registers of the MAS 3 5x9F are 16 bits wide,

The I

the MSB is denoted as bit[15] . Transmissions via I

2

bus have to take place in 16-bit words (two byte transfers, MSB sent first); thus, for each register access,

two 8-bit data words must be sent/received via I

2

bus.

C

C

18 Micronas

ADVANCE INFORMATION MAS 35x9F

3.1.3. Naming Convention

The description of the various controller commands

uses the following formalism:

– Abbreviations used in the following descriptions:

a address

d data value

n count value

o offset value

r register number

x don’t care

– A data value is split into 4-bit nibbles which are num-

bered beginning with 0 for the least significant nibble.

– Data values in nibbles are always shown in hexa-

decimal notation.

– A hexadecimal 20-bit number d is written, e.g. as

d = 17C63

d0 = 3

hex

d4 = 1

hex

– Variables used in the following descriptions:

2

C address:

I

DW 3C/3E

DR 3D/3F

, its five nibbles are

hex

, d1 = 6

, d2 = C

hex

.

hex

hex

, d3 = 7

hex

hex

, and

DSP core:

data_write 68

data_read 69

hex

hex

Codec:

codec_write 6C

codec_read 6D

hex

hex

– Bus signals

SStart

PStop

A ACK = Acknowledge

N NAK = Not acknowledge

– Symbols in the telegram examples

< Start Condition

> Stop

dd

xx

data bytes

ignore

All telegram numbe rs are hexadecimal, data originating from the MAS 35x9F are greyed.

Example:

dd dd

<DW 68

<DW 69 <DR

> write data to DSP

dd dd

> read data from DSP

and stop with NAK

2

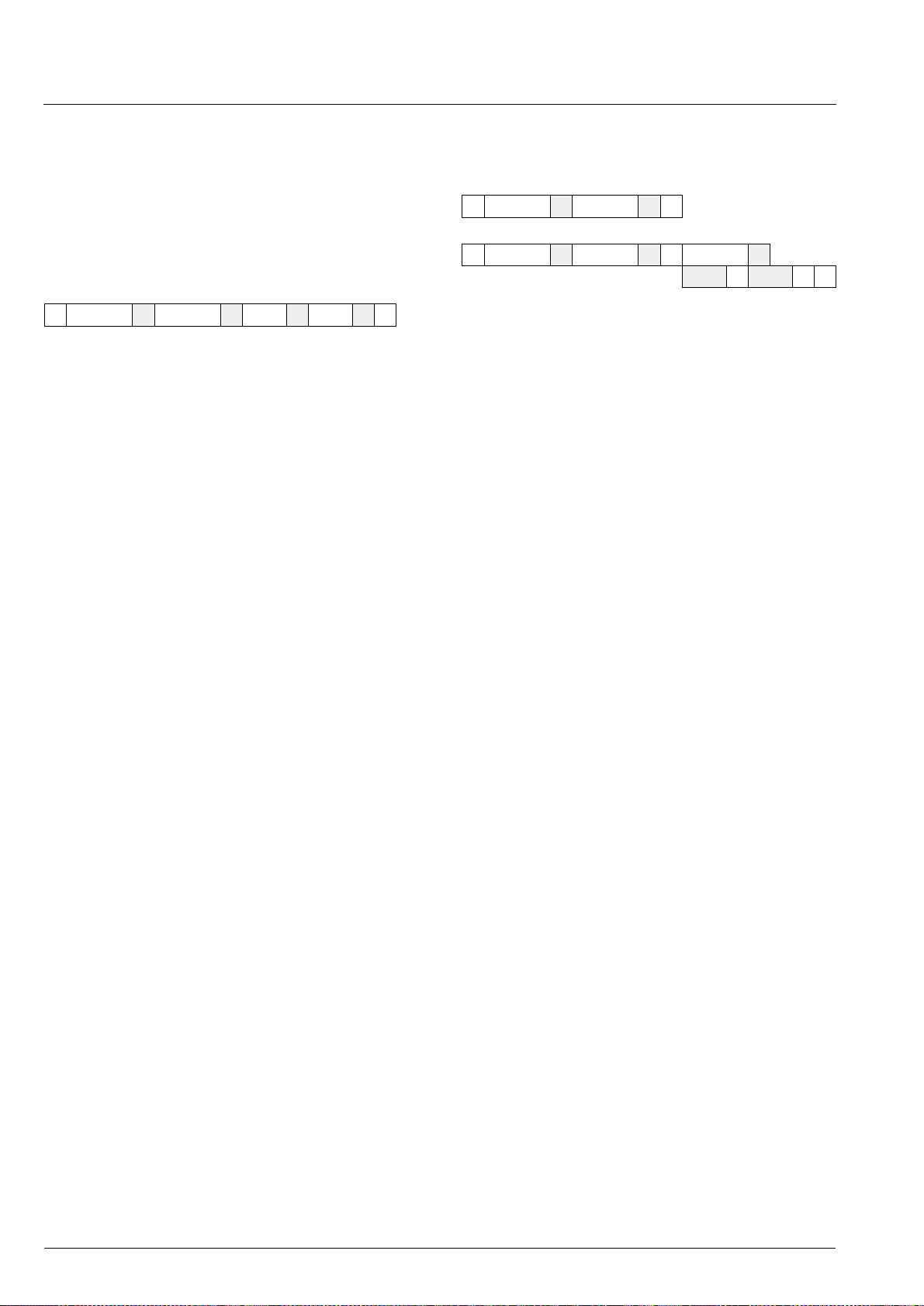

Fig. 3–1 shows I

C bus protocols for write and read

operations of the interface; the read operatio ns requir e

an extra start condition and repetition of the chip

address with the device read command (DR). Fields

with signals/data or iginating from the MAS 35x9F are

marked by a gray background. Note that in some

cases the data reading proc ess must be conc luded by

a NAK condition.

Example: I

2

C write access

low data wordAhigh data wordAsubaddressADWS A P

2

Example: I

C read access

high data wordADRSAsubaddressADWS A

NPlow data word

SDA

SCL

S

Fig. 3–1: Example of an I

2

C bus protocol for the MAS 35x9F (MSB first; data must be stable while clock is high)

1

0

P

A

=

0 (ACK)

=

N

S

P

1 (NAK)

=

Start

=

Stop

Micronas 19

MAS 35x9F ADVANCE INFORMATION

AP

d1,d0

AAAS

DW subaddress d3,d2

3.2. Direct Configuration Registers

The task selection of the DSP and the DC/DC converters are controlled i n the direct configuration registe rs

Control, DCCF, and DCFR.

3.2.1. Write Direct Configuration Registers

The write protoc ol for the direct confi guration re gisters

only consists o f device address, subaddress and one

16-bit data word.

3.2.2. Read Direct Configuration Register

1) send subaddress

DW subaddress

SAAP

2) get register value

DW subaddress DR

SAASA

d3,d2 d1,d0

AN

P

To check the PUP1 and PUP2 power-up flags, it is

necessary to read back the content of the direct configuration registers.

20 Micronas

ADVANCE INFORMATION MAS 35x9F

Table 3–3: Direct Configuration Registers

I2C Sub-

Function Name

address

(hex)

6A Control Register (reset value = 30 00

bit[15:14] Analog Supply Voltage Range

Code AGNDC recommended for voltage range of AVDD

00 1.1 V 2.0 ... 2.4 V (reset)

01 1.3 V 2.4 ... 3.0 V

10 1.6 V 3.0 ... 3.6 V

11 reserved reserved

Higher voltage ranges permit higher output levels and thus a better signal-to-

noise ratio.

bit[13] enable DC/DC 2 (reset=1)

bit[12] enable DC/DC 1 (reset=1)

Both DC/DC converters are switched on by default.

bit[11] enable and reset audio codec

bit[10] enable and reset DSP core

For normal operation (MPEG-decoding and D/A conversion), both, the DSP

core and the audio codec have to be enabled after the power-up procedure.

The DSP can be left off if an audio signal is routed from the analog inputs to

the analog outputs (set bit[15] in codec register 00 0F

can be left off if the DSP uses digital inputs and outputs only.

hex

)

). The audio codec

hex

CONTROL

6B

bit[9] reset codec

bit[8] reset DSP core

bit[7] disable task 7 of DSP core

bit[6] disable task 6 of DSP core

bit[5] disable task 5 of DSP core

bit[4] disable task 4 of DSP core

bit[3] set task 3 of DSP core

bit[2] set task 2 of DSP core

bit[1] set task 1 of DSP core

bit[0] set task 0 of DSP core

1)

bit[7]

bit[6:0]

1)

bit[15:8] reserved, must be set to zero

1)

enable XTAL input clock di vider

(extended crystal range up to 28 MHz)

reserved, must be set to zero

DSP_TASK

bit[7] disable task 7 of DSP core

bit[6] disable task 6 of DSP core

bit[5] disable task 5 of DSP core

bit[4] disable task 4 of DSP core

bit[3] set task 3 of DSP core

bit[2] set task 2 of DSP core

bit[1] set task 1 of DSP core

bit[0] set task 0 of DSP core

Unless downloaded optional software is used, the bits 7...0 must be set to

zero.

1)

available in the next version

Micronas 21

MAS 35x9F ADVANCE INFORMATION

Table 3–3: Direct Configuration Registers

I2C Sub-

Function Name

address

(hex)

76 DCCF Register (reset = 5050

DC/DC Converter 2

bit[15] PUP2: Voltage monitor 2 flag (readback)

bit[14:11] Voltage between VSENS2 and DCSG2

Code Nominal set level reset level

output volt. of PUP2 of PUP2

1111 3.5 V 3.4 V 3.3 V

1110 3.4 V 3.3 V 3.2 V

1101 3.3 V 3.2 V 3.1 V

1100 3.2 V 3.1 V 3.0 V

1011 3.1 V 3.0 V 2.9 V

1010 3.0 V 2.9 V 2.8 V (reset)

1001 2.9 V 2.8 V 2.7 V

1000 2.8 V 2.7 V 2.6 V

0111 2.7 V 2.6 V 2.5 V

0110 2.6 V 2.5 V 2.4 V

0101 2.5 V 2.4 V 2.3 V

0100 2.4 V 2.3 V 2.2 V

0011 2.3 V 2.2 V 2.1 V

0010 2.2 V 2.1 V 2.0 V

0001

0000

1)

1)

2.1 V 2.0 V 1.9 V

2.0 V 1.9 V 1.8 V

) DCCF

hex

bit[10] Mode

1 Pulse frequency modulation (PFM)

0 Pulse width modulation (PWM) (reset)

bit[9] reserved, must be set to zero

bit[8] Disable synchronized rectifier

1 disable synchronized recitifier

0 enable synchronized recitifier (reset)

The DC/DC converters are up-converters only. Thus, if the battery voltage is

higher than the selected nominal voltage, the output voltage will exceed the

nominal voltage.

1)

refer to Section 4.6.2. on page 61

22 Micronas

ADVANCE INFORMATION MAS 35x9F

Table 3–3: Direct Configuration Registers

I2C Subaddress

(hex)

76

(continued)

Function Name

DC/DC Converter 1

bit[7] PUP1: Voltage monitor 1 flag (readback)

bit[6:3] Voltage between VSENS1 and DCSG1 (see table above)

bit[2] Mode

1 Pulse frequency modulation (PFM)

0 Pulse width modulation (PWM) (reset)

bit[1] reserved, must be set to zero

bit[0] Disable synchronized rectifier

1 disable synchronized recitifier

0 enable synchronized recitifier (reset)

Note, that the reference voltage for DC/DC converter 1 is derived from the

main reference source supplied via pin AVDD1. Therefore, if this DC/DC converter is used, its output must be connected to the analog supply.

The DC/DC converters are up-converters only. Thus, if the battery voltage is

higher than the selected nominal voltage, the output voltage will exceed the

nominal voltage.

Micronas 23

MAS 35x9F ADVANCE INFORMATION

Table 3–3: Direct Configuration Registers

I2C Subaddress

(hex)

77 DCFR Register (reset = 00

Function Name

Battery Voltage Monitor

bit[15] Comparison result (readback)

1 input voltage at pin VBAT above defined threshold

0 input voltage at pin VBAT below defined threshold

bit[14] Number of battery cells

0 1 cell (range 0.8...1.5 V) (reset)

1 2 cells (range 1.6...3.0 V)

bit[13:10] Voltage threshold level

1 cell 2 cells

1111 1.5 3.0 V

1110 1.45 2.9 V

...

0010 0.85 1.7 V

0001 0.8 1.6 V

0000 Battery voltage supervision off (reset)

bit[9:8] Reserved, must be set to 0

The result is stable after 1 ms after enabling. The setup time for switching

between two thresholds is negligibly small.

) DCFR

hex

For power management reasons, the battery voltage monitor should be

switched off by setting bit[13:10] to zero when the measurement is completed.

DC/DC Converter Frequency Control (PWM)

bit[7:4] Reserved, must be set to 0

bit[3:0] Frequency of DC/DC converter

Reference: 24.576 22.5792 18.432 MHz

0111 315.1 289.5 297.3 kHz

0110 323.4 297.1 307.2 kHz

0101 332.1 305.1 317.8 kHz

0100 341.3 313.6 329.1 kHz

0011 351.1 322.6 341.3 kHz

0010 361.4 332.0 354.5 kHz

0001 372.4 342.1 368.6 kHz

0000 384.0 352.8 384.0 kHz (reset)

1111 396.4 364.2 400.7 kHz

1110 409.6 376.3 418.9 kHz

1101 423.7 389.3 438.9 kHz

1100 438.9 403.2 460.8 kHz

1011 455.1 418.1 485.1 kHz

1010 472.6 434.2 512.0 kHz

1001 491.5 451.6 542.1 kHz

1000 512.0 470.4 576.0 kHz

2

If the audio codec is not enabled (bit 11 of the Control register at I

dress 6A

from the crystal frequency (nominal 18.432 MHz). Otherwise, the synthesizer

clock is used as the reference (please refer to the respective column in

Table 2–1 on page 11).

is zero), the clock for the DC/DC converters is directly derived

hex

C-subad-

24 Micronas

ADVANCE INFORMATION MAS 35x9F

3.3. DSP Core

The DSP Core of the MAS 35x 9F has two RAM ba nks

denoted D0 and D1. The wo rd size is 20 bi ts. All RAM

addresses can be accessed in a 20-bit or a 16-bit

mode via I

2

C bus. For fast access of internal DSP

states, the processor cor e also has an addres s space

of 256 data regis ters. All registe r and RAM ad dresses

are given in hexadecimal notation.

3.3.1. Access Protocol

The access of the DSP Core in the MAS 35x9F uses a

special command syntax. The commands are executed by the DSP during it s normal operation witho ut

any loss or interr uption of the i ncoming data or outgoing audio data stream. Thes e I

2

C commands allow the

controller accessing the internal DSP registers and

RAM cells and thus, monitoring internal states and setting the parameters for the DSP firmware. This acces s

also provides a download option for alternative software mod u l e s.

The MAS 35 x9F firmware scans th e I

2

C interface periodically and checks for pending or new commands.

However, due to some time critical fir mware par ts, a

certain latency time for the response has to be

expected. The theoretical worst case response time

does not exceed 4 ms. However, the typical response

time is less than 0.5 ms.

Table 3–4 gives an overview over the different commands which the DS P Core receives via th e I

2

C data

register. The “Code” is always the first data nibble

transmitted after the “data_write” subaddress byte. A

second auxiliary code nibble is used for the short

memory (16-bit) access commands.

2

Due to the 16-bit width of the I

C data register, all

actions transmit telegrams with multiples of 16 data

bits.

DW data_write Code, ... ..., ... ...

AASA

A

Fig. 3–2: General core access protocol

Table 3–4: Basic controller command codes

Code

Command Function

(hex)

Run

0...3 Run Start execution of an internal program.

with start address 0 means

freeze the operating system.

5 Read Ancillary Data The controller reads a block of MPEG Ancillary Data from the MAS 35x9F

6 Fast Program Download The controller downloads custom software via the PIO interface

A Read from Register The controller reads an internal register of the MAS 35x9F

B Write to Register The controller writes an internal register of the MAS 35x9F

C Read D0 Memory The controller reads a block of the DSP memory

D Read D1 Memory The controller reads a block of the DSP memory

E Write D0 Memory The controller writes a block of the DSP memory

F Write D1 Memory The controller writes a block of the DSP memory

Micronas 25

Loading...

Loading...