Micronas Intermetall DPL4519G Datasheet

DPL 4519G

Sound Processor for

Digital and Analog

Edition Oct. 31, 2000

6251-512-1PD

PRELIMINARY DATA SHEET

MICRONAS

MICRONAS

Surround Systems

DPL 4519G PRELIMINARY DATA SHEET

Contents

Page Section Title

4 1. Introduction

5 1.1. Features of the DPL 4519G

6 1.2. Application Fields of the DPL 4519G

7 2. Functional Description

7 2.1. Architecture of the DPL 4519G Family

8 2.2. Preprocessing I

8 2.3. Selection of Internal Processed Surround Signals

8 2.4. Source Selection and Output Channel Matrix

8 2.5. Audio Baseband Processing

8 2.5.1. Main and Aux Outputs

8 2.6. Surround Processing

8 2.6.1. Surround Processing Mode

8 2.6.1.1. Decoder Matrix

9 2.6.1.2. Surround Reproduction

9 2.6.1.3. Center Modes

9 2.6.1.4. Useful Combinations of Surround Processing Modes

10 2.6.2. Examples

11 2.6.3. Application Tips for using 3D-PANORAMA

11 2.6.3.1. Sweet Spot

11 2.6.3.2. Clipping

11 2.6.3.3. Loudspeaker Requirem ents

11 2.6.3.4. Cabinet Requirements

11 2.6.4. Input and Output Levels for Dolby Surround Pro Logic

11 2.7. SCART Signal Routing

11 2.7.1. SCART Out Select

12 2.7.2. Stand-by Mode

2

12 2.8. I

S Bus Interfaces

12 2.8.1. Synchronous I

12 2.8.2. Asynchronous I

12 2.8.3. Multichannel I

12 2.8.4. Asynchronous Multichannel I

13 2.9. Digital Control I/O Pins

13 2.10. Clock PLL Oscillator and Crystal Specifications

2

S Input Signals

2

S-Interface(s)

2

S-Interface

2

S-Output

2

S-Input

14 3. Control Interface

2

14 3.1. I

C Bus Interface

14 3.1.1. Device and Subaddresses

14 3.1.2. Internal Hardware Error Handling

15 3.1.3. Description of CONTROL Register

15 3.1.4. Protocol Description

2

16 3.1.5. Proposals for General DPL 4519G I

C Telegrams

16 3.1.5.1. Symbols

16 3.1.5.2. Write Telegrams

16 3.1.5.3. Read Telegrams

16 3.1.5.4. Examples

2

16 3.2. Start-Up Sequence: Power-Up and I

C Controlling

2 Micronas

PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

16 3.3. DPL 4519G Programming Interface

16 3.3.1. User Registers Overview

19 3.3.2. Description of User Registers

2

19 3.3.2.1. Write Registers on I

21 3.3.2.2. Read Registers on I2C Subaddress 11

21 3.3.2.3. Write Registers on I2C Subaddress 12

33 3.3.2.4. Read Registers on I2C Subaddress 13

C Subaddress 10

hex

hex

hex

hex

34 3.4. Programming Tips

34 3.5. Examples of Minimum Initialization Codes

34 3.5.1. Micronas Dolby Digital chipset (with MAS 3528E)

35 4. Specifications

35 4.1. Outline Dimensions

37 4.2. Pin Connections and Short Descriptions

40 4.3. Pin Descriptions

43 4.4. Pin Configurations

45 4.5. Pin Circuits

47 4.6. Electrical Characteristics

47 4.6.1. Absolute Maximum Ratings

48 4.6.2. Recommended Operating Conditions (T

= 0 to 70 °C)

A

48 4.6.2.1. General Recommended Operating Conditions

48 4.6.2.2. Analog Input and Output Recommendations

49 4.6.2.3. Crystal Recommendations

50 4.6.3. Characteristics

50 4.6.3.1. General Characteristic s

51 4.6.3.2. Digital Inputs, Digital Outputs

52 4.6.3.3. Reset Input and Power-Up

2

53 4.6.3.4. I

54 4.6.3.5. I

C-Bus Characteristics

2

S-Bus Characteristics

56 4.6.3.6. Analog Baseband Inputs and Outputs, AGNDC

58 4.6.3.7. Power Supply Rejection

58 4.6.3.8. Analog Performance

DPL 4519G

61 5. Appendix A: Application Information

61 5.1. Phase Relationship of Analog Outputs

62 5.2. Application Circuit

64 6. Data Sheet History

License Notice:

“Dolby Pro Logic” and “Dolby Digital” are trademarks of Dolby Laboratories.

Supply of this implementation of Dolby T echnolog y does not conv ey a license nor imply a right under any patent, or any other industrial or intellec-

tual property right of Dolby Laboratories, to use this implementation in any finished end-user or ready-to-use final product. Companies planning to

use this implementation in products must obtain a license from Dolby Laboratories Licensing Corporation before designing such products.

Micronas 3

DPL 4519G PRELIMINARY DATA SHEET

Sound Processor for Digital and Analog Surround

Systems

The hardware and software description in this document is valid for the DPL 4519G version A1 and following versions.

1. Introduction

The DPL 4519G processor is designed as par t of the

Micronas chip set for digital a nd analog Surroun d S ystems i. e. Dolby Digital, MPEG 2 Audio, or Dolby ProLogic. The combination of MAS 3528E, DPL 4519G,

and MSP 44x0G is a complete 5.1 channel Dolby Digital decoder and playback solution, while DPL 4519G

and MSP 44x0G alone, represent a complete Dolby

Surround Pro Logic system.

The DPL 4519G receives its incomi ng data via highly

flexible I

can be configured as three asynchronous I

2

S interfaces. The three I2S input interfaces

2

S inputs or

two synchronous a nd one asynchronous in terface. In

the latter case, the asynchronous interface allows

reception of 2-8 channels with arbitrary sample rate

ranging from 8 to 48 kHz. The synchronization is performed by means of an adaptive high-quality sample

rate converter.

In an application together with the Dolby Digital

decoder MAS 3528E, eight channels (left, right, surround left, surround r ig ht, c ent er, subwoofer, Pro Logic

encoded left, Pro Logic encoded right) are fed in and

processed in the DPL 4519G.

Similar to the multichannel I

is provided with an 8-channel I

2

S input interface, the DPL

2

S output interface,

which can be conne cted to a MSP 44x0G. Therefore

all 8 channels can be routed to each output in both

ICs.

The baseband processing including e.g. balance,

bass, treble, and loudness is performed at a fixed sample rate of 48 kHz.

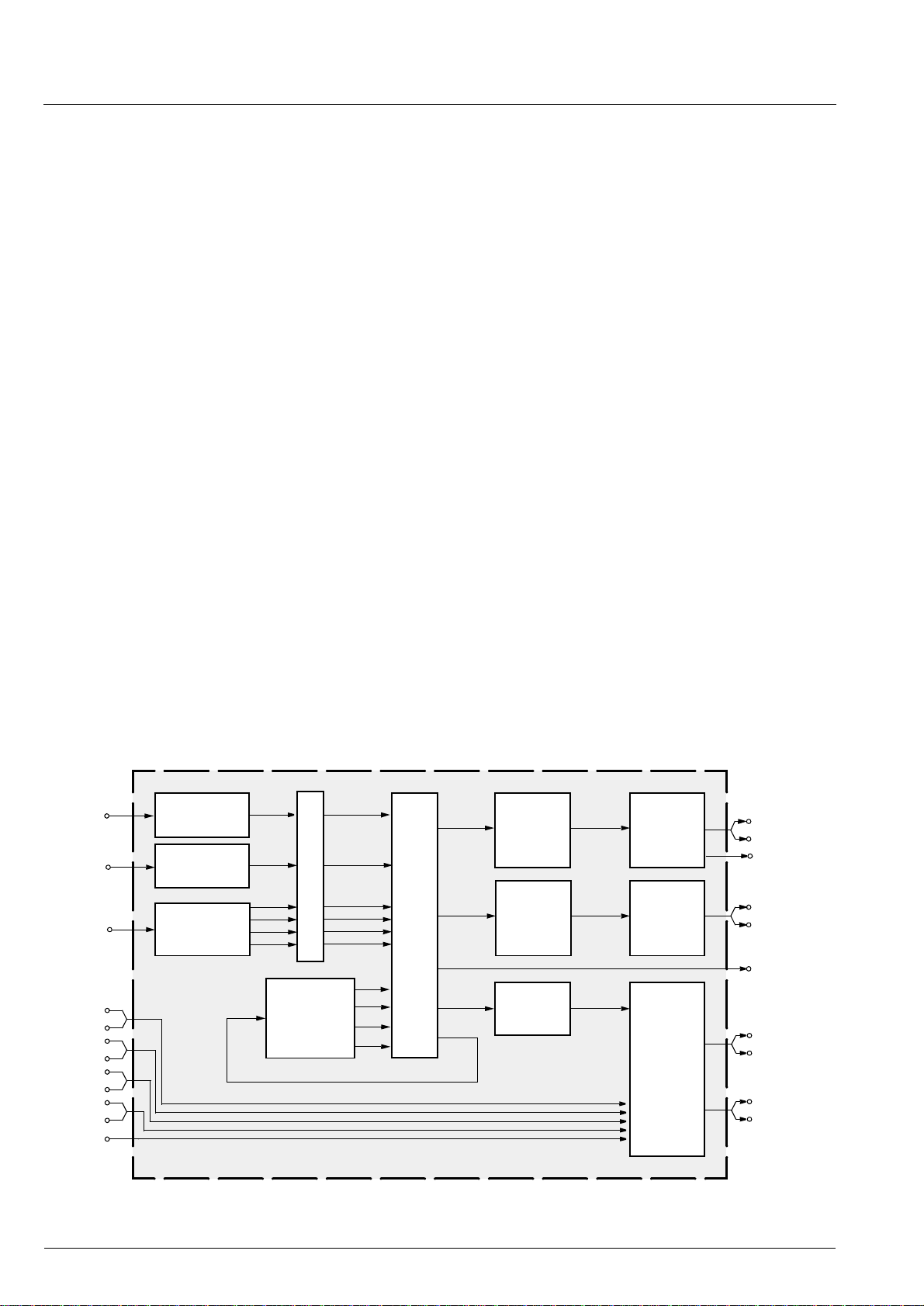

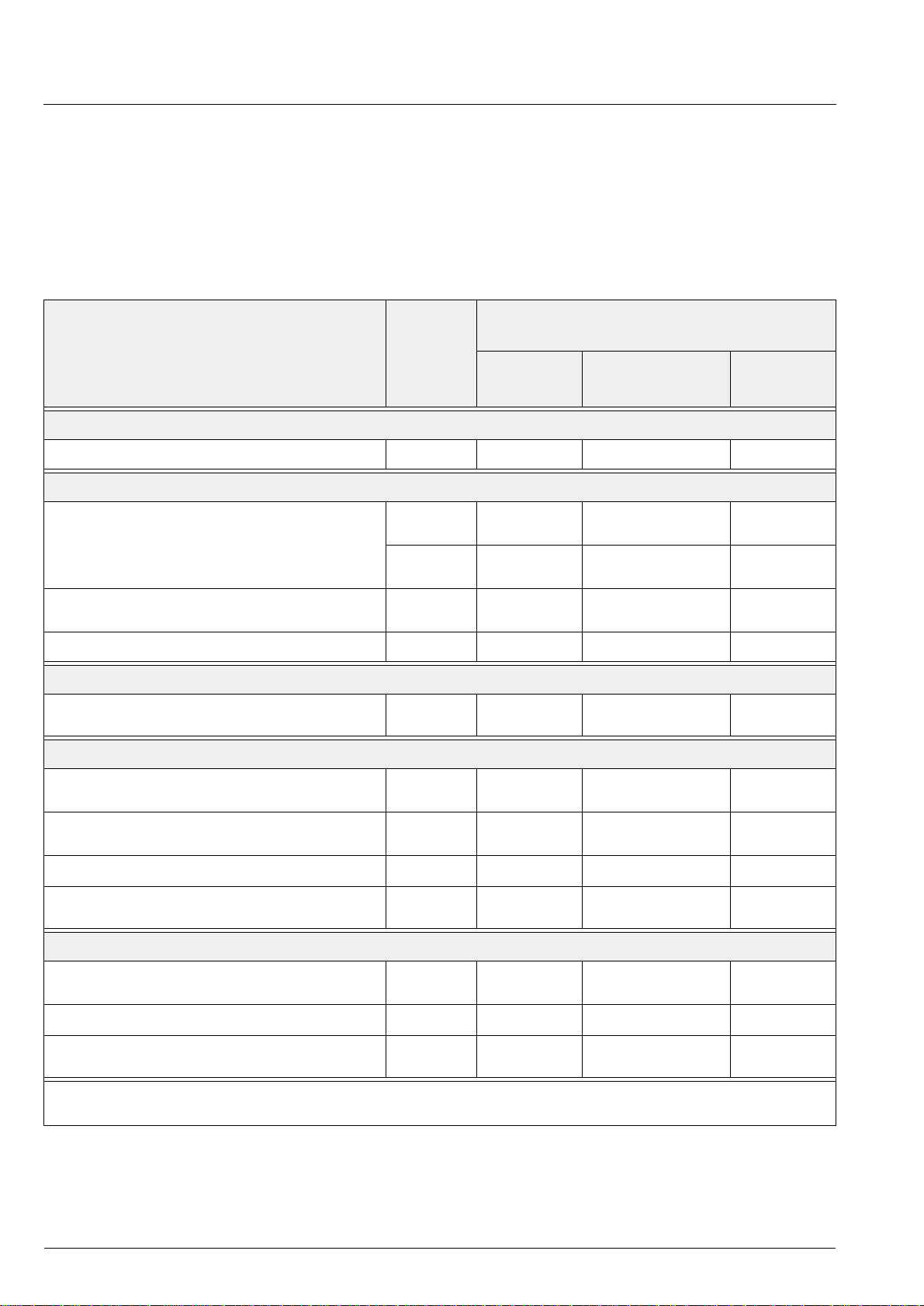

Fig. 1–1 shows a simplified functional block diagram of

the DPL 4519G.

The DPL 4519G is pin-compatible to members of the

MSP 34xx family. This speeds up PCB development

for customers using MSPs.

The software interface of the DPL 4519G is also

largely the same as for members of the MSP family.

The ICs are prod uc ed in s ub mi cro n CM O S tec hn ology

and are available in PQFP80, PLQFP64 and in

PSDIP64 packages.

I2S1

I2S2

I2S3

SCART1

SCART2

SCART3

SCART4

MONO

I2S

I2S

Prescale

I2S

(2..8-channel)

ProLogic

processing

Fig. 1–1: Simplified block diagram of the DPL 4519G

Source Select

Main

Sound

Processing

AUX

Sound

Processing

DAC

DAC

DAC

SCART

Output

Select

Main

Subwoofer

AUX

I2S

(8-channel)

SCART1

SCART2

4 Micronas

PRELIMINARY DATA SHEET DPL 4519G

1.1. Features of the DPL 4519G

2

– 8-channel asynchonou s I

+ 2 synchronous I

2

S input channels (e.g. for MSP and ADR)

S input interface (multichannel mode)

or

2

3 asynchronous two-channel I

S input interfaces

– Main and AUX channel with balance, bass, treble, loudness, volume

– 5-band graphic equalizer for Main channel

– Dolby Surround Pro Logic Adaptive Matrix

– Micronas Effect Matrix

– Micronas “3D-Panorama” virtualizer compliant to “Virtual Dolby Surround” technology

– Micronas Panorama sound mode (3D Surround sound via two loudspeakers)

– Noise Generator

– Spatial Effect for Surround

– 30-ms Surround delay

– Surround matrix control: Adaptive/Passive/Effect

– Center mode control: Normal/Phantom/Wide/Off

– Surround reproduction control: Rear speaker, Front speaker, Panorama, 3D-Panorama

2

– Two digital input/output pins controlled by I

C bus

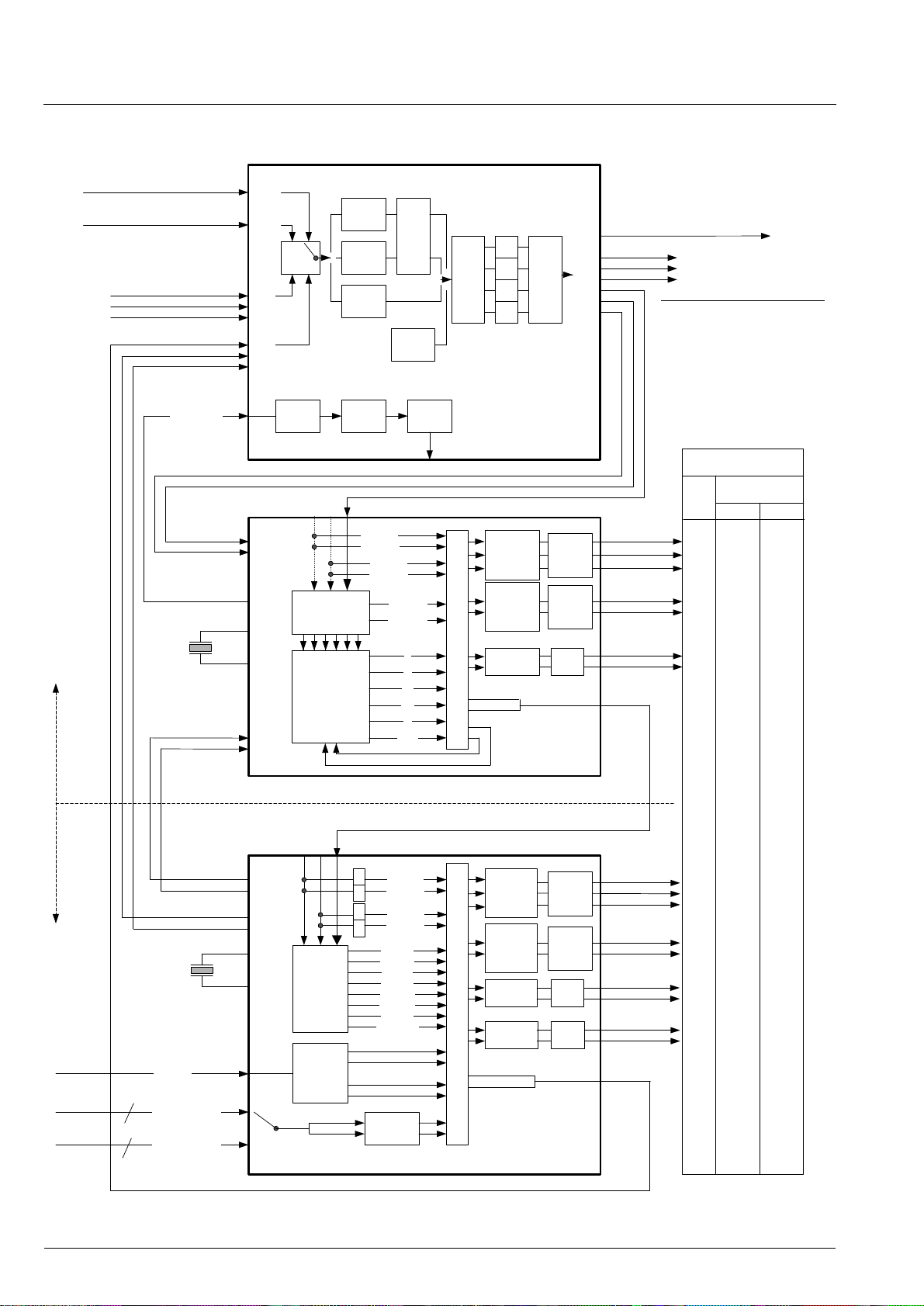

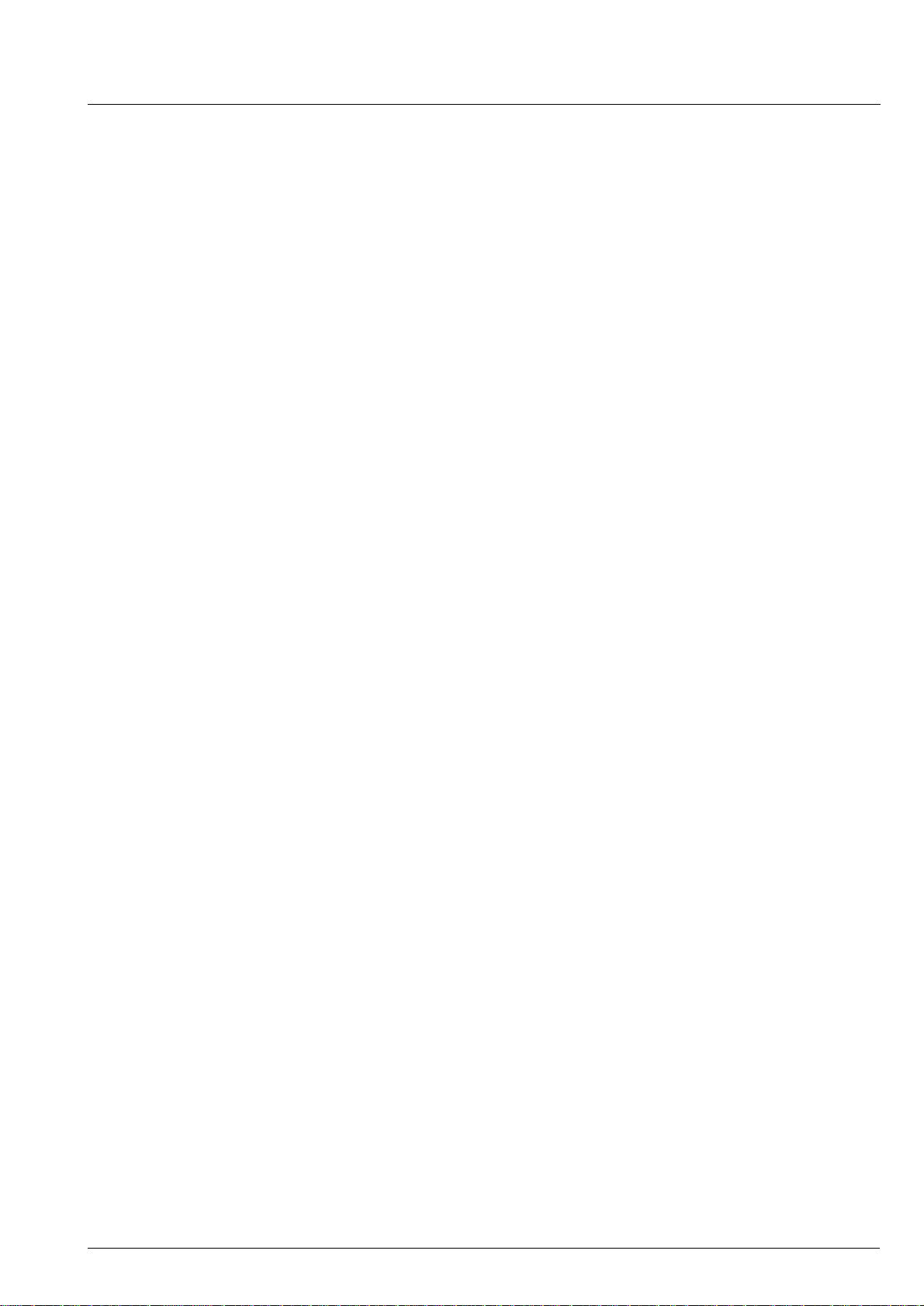

Fig. 1–2 shows a typical Dolby Digital application using DPL 4519G, MSP 4450G, and MAS 3528E.

Micronas 5

DPL 4519G PRELIMINARY DATA SHEET

1.2. Application Fields of the DPL 4519G

S/PDIF In 1/2

AC-3, MPEG L2, PCM or other Format

I2S-In: Slave

18.432 MHz

18.432

MHz

Dolby

Digital

Upgrade

Module

Basic

TV-

Sound

System

18.432

MHz

S/PDI1

S/PDI2

SID*

SII*

SIC*

SID

SII

SIC

I2S_WS3

I2S_CL3

AUDIO_

CL_OUT

I2S_WS

I2S_CL

I2S_WS3

I2S_CL3

I2S_WS

I2S_CL

Input

Buffer

Amp./

Osc.

I2S_Inputs

123

2-8 Ch. Input

(LT, RT,L, R

S

, SR,C, SUB)

L

6 Channel

Loop-through

Dolby

Pro Logic

Decoder

I2S_Inputs

123

2-8

Channel

Serial

Input

PCM

MPEG

Deemphasis

AC-3

Noise

Gen.

PLL Synth.

CLKO

I2S-Mode:Multichannel Mode auf D0

(6 - 8 Channels, fs=32, 44.1 or 48 kHz,

I2S_1_L

I2S_1_R

I2S_2_L

I2S_2_R

I2S_3_L

I2S_3_R

16,18,....32 Bit)

t

t

L

R

or

S

L

S

R

C

SUB

Dolby Digital: (Lt, Rt, L, R, SL, SR, C, SUB)

Pro Logic: (L

I2S_1_L

I2S_1_R

I2S_2_L

I2S_2_R

I2S_3_L

t

I2S_3_R

t

I2S_3_L

I2S_3_R

I2S_3_S

L

I2S_3_S

R

I2S_3_C

I2S_3_SUB

L

2

R

Ls

Rs

C/

Sub

Delay Lines

Lt

Post Processing

Rt

MAS 3528E

Dolby Digital Decoder

MPEG-L2 Decoder

Bass

Treble

Balance

Volume

Bass

Treble

Balance

Volume

Volume

DPL 4519G

Pro Logic Decoder

, Rt, L, R, C, SubW)

t

Sound-

Process.

Balance

Volume

Bass

Treble

Balance

Volume

Volume D/A

Volume

Multipl.

analog

Volume

analog

Volume

D/A

analog

Volume

analog

Volume

D/A

D/A

D/A

D/A

D/A

SPDO

SOD3

SOD2

SOD1

SOD

SOI

SOC

S/PDIF Out

PCM-Format (Lt/Rt or L/R or Lo/Ro)

or Loop-through (e.g. DTS)

Dolby Digital / Pro Logic Configurations

Example 1:

- internal L, C, R

- internal woofer for low freq. of L, (C), R

- ext. Surround speakers S

- ext. Subwoofer for SUB channel.

Example 2:

- internal Left and Right used as C

- internal woofer for low freq. of C

- ext. L, R

- ext. Surround speakers S

- ext. Subwoofer for SUB channel.

Configuration Examples

normal

Main

---

---

SUB

(C

Aux

SCART1

I2S_Out_L/R

Main

Aux

SCART1

SCART2

---

---

---

---

---

Subw

C, SUB

SL, SR

L

L

Subw

R

L

R

L

R

L

R

, S

L

R

, S

L

R

Dolby Digital /

Pro Logic

12

C

L

ext

int

SUB

ext

ext

R

)---

ext

int

S

S

L

S

R

L, R

t

L

R

R

R

R

L

, R

L

L

L

L

S

R

R

L

t

t

R

t

t

L, R

C, SUB

SL, SR

L

, R

t

t

t

C

int

int

Subw

int

int

C

int

int

L

t

t

R

t

t

L

t

t

R

t

t

L

t

t

R

t

t

2

SIF-IN

SCART1_In

SCART4_In

Demod

.

.

.

A/D

MSP 4450G

I2S_Out_L/R

L, R

L, R

L, R

Multistandard Sound Processor

Fig. 1–2: Typical DPL 4519G application

6 Micronas

PRELIMINARY DATA SHEET DPL 4519G

2. Functional Description

2.1. Architecture of the DPL 4519G Family

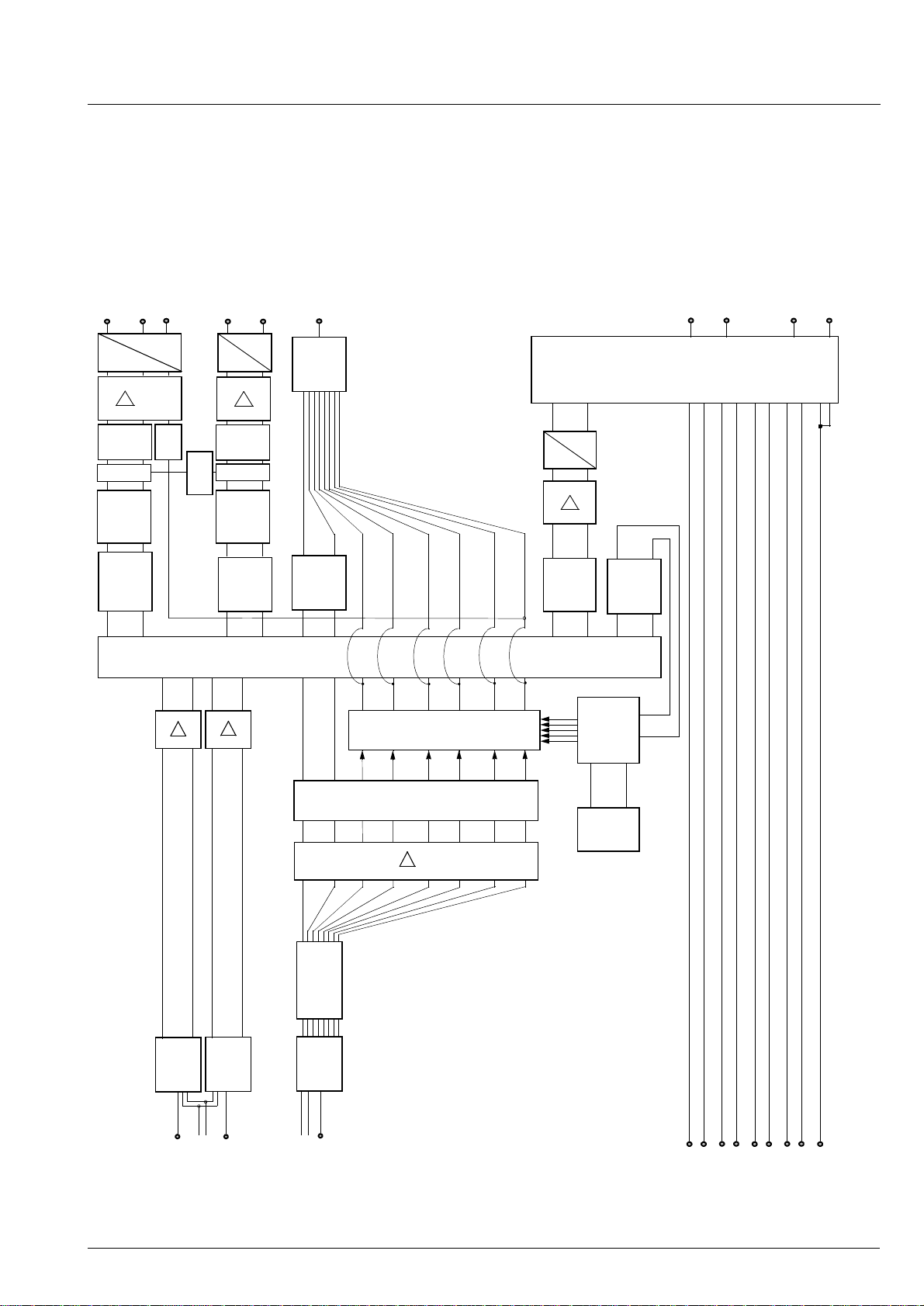

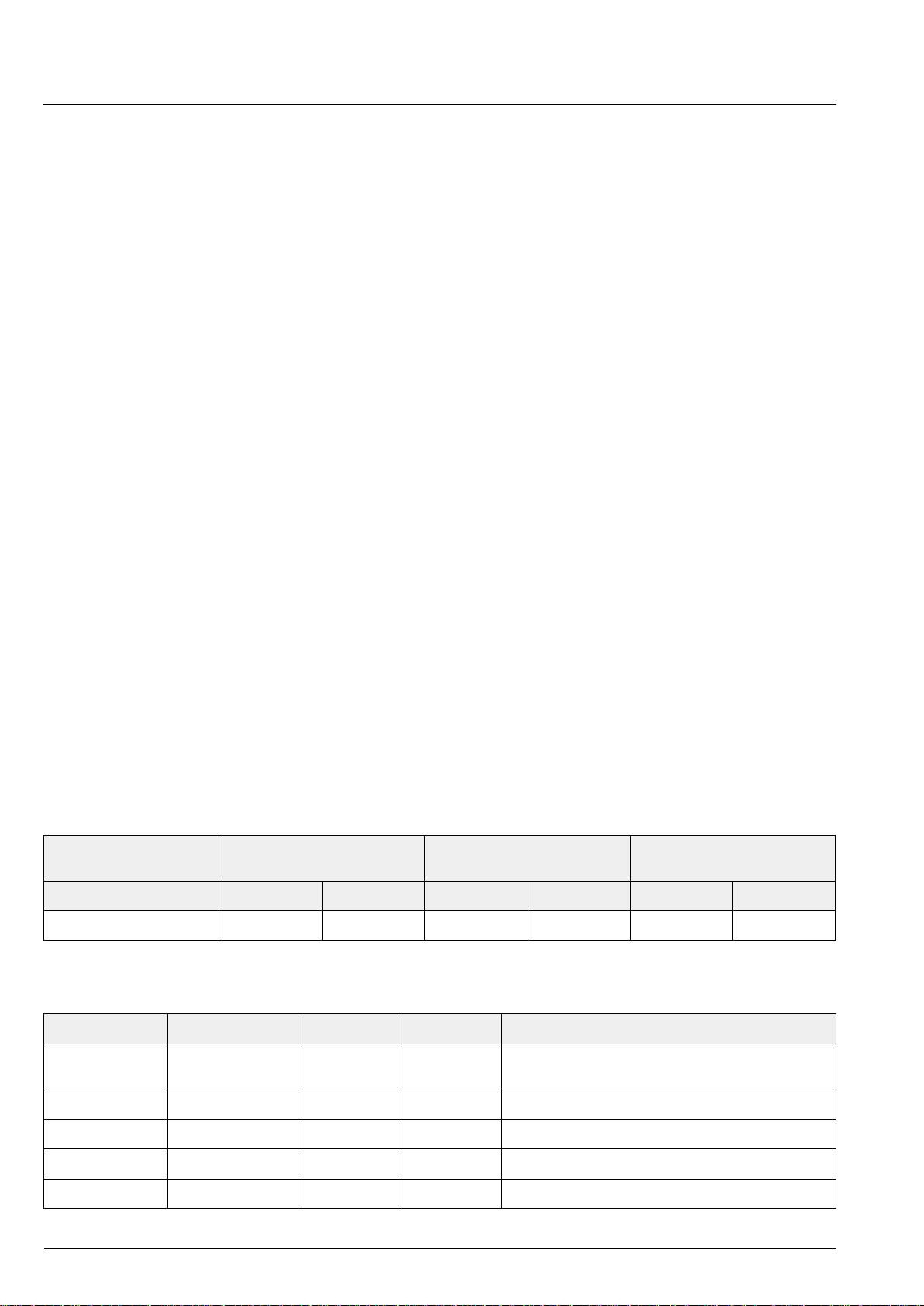

Fig. 2–1 shows a simplified block diagram of the IC.

(sync. 48kHz)

DACM_R

DACM_L

D

Volume

)

hex

(01

Balance

Bass/

Tre ble/

Main

Channel

Σ

Loudness/

Matrix

DACM_SUB

A

)

hex

(00

)

hex

(2C

Adjust

fer Level

Subwoo-

Beeper

)

)

hex

hex

)

(14

hex

Equalizer

(02/03/04

(20..25

)

hex

(08

DACA_R

DACA_L

A

D

Volume

)

Balanc

(30

Σ

Bass/

Tre ble/

Loudness

Aux

Matrix

Channel

I2S_DA_OUT

I2S

)

Interface

hex

(06

hex

)

hex

(31/32/33

S

2

I

)

hex

(09

Channel

)

Matrix

hex

(0B

SCART1_L/R

A

D

)

hex

(07

Volume

)

Matrix

SCART1

Channel

Matrix

Channel

hex

Surround

(0A

SC1_OUT_L

SC1_OUT_R

)

hex

(48

SC2_OUT_L

SC2_OUT_R

SCART Output Select

Source Select

5

S1

2

I

6

)

hex

(16

Prescale

)

hex

(12

S2

2

I

Prescale

7

t

L

8

L

t

L

R

S3

2

I

9

L

R

S

L

R

S

S

I2S_3 Resorting Matrix

Prescale

10

R

C

S

Internal/External Switch

R

SUB

)

)

)

hex

(36

C

SUB

)

hex

(36

)

hex

(11

Surround

Noise

Processing

Generator

)

)

hex

hex

hex

hex

(4B

(4C

(49

(4A

)

hex

(4D

synchronization

S

2

I

Interface

I2S_DA_IN1

(sync. 48kHz)

S

2

I

Interface

I2S_CL

I2S_WS

I2S_DA_IN2

(sync. 48kHz)

S

2

I

Interface

I2S_CL3

I2S_WS3

I2S_DA_IN3

(async. 8-48 kHz)

SC2_IN_L

SC1_IN_L

SC2_IN_R

SC1_IN_R

SC4_IN_L

SC3_IN_L

SC3_IN_R

MONO_IN

SC4_IN_R

Micronas 7

Fig. 2–1: Signal flow block diagram of the DPL 4519G (input and output names correspond to pin names)

DPL 4519G PRELIMINARY DATA SHEET

2.2. Preprocessing I2S Input Signals

2

S inputs can be adjusted in level by means of the

The I

2

S prescale registers.

I

2

S_3 interface is able to receive more tha n two

The I

channels (see Sect ion 2.6. on page 8) . The incoming

signals can be resor ted by a programmable matrix in

order to obtain a certain order, which means an unified

postprocessing afterwards.

2

Since the I

S_3 interface is asynchronous, incoming

sound signals with arbi trary sampl e rates in the range

of 8-48 kHz are in terpolated to 4 8 k Hz by mean s of a n

adaptive high quality sampl e rate converter. Therefore

all subsequent processing is calculated on a fixed

sampling rate, which even can be synchronized to

I2S_WS e.g. to a MSP 4450 being locked to an incoming NICAM signal.

2.3. Selection of Internal Processed

Surround Signals

2

Instead of having an multichannel input vi a the I

S_3

interface, a multichannel signal can be created by an

internal Dolby Pro Logic decoder. In that case channels 3..8 of the multicha nnel input are replaced by the

internally generated signals.

2.4. Source Selection and Output Channel Matrix

The Source Selec tor makes it possible to di stribute all

source signals (I

2

S input signals) to the des ired output

channels (Main, Aux, etc.). All input and output signa ls

can be processed simultane ously. Each sourc e channel is identified by a unique source address.

For each output channel, the output channel matrix

can be set to sound A (left mono), sound B (right

mono), stereo, or mono (sound left and right).

2.5. Audio Baseband Processing

2.5.1. Main and Aux Outputs

The following baseband features are implemented in

the Main and Aux output chann els: bass/treble, loudness, balance, and volume. A square wave beeper can

be added to these outputs. The Main channel additionally suppor ts an equal izer function (this is not simultaneously available with bass/treble).

2.6. Surround Processing

2.6.1. Surround Processing Mode

Surround sound processing is controlled by three functions:

The "Decoder Matrix" defines whi ch met hod is used to

create a multichannel signal (L, C, R, S) out of a stereo

input.

The "Surround Reprodu ction" deter mines whether the

surround signal “S” i s fed to surround speakers. If no

surround speaker is actuall y connected, it defines the

method that is used to create surround effects.

The “Center Mode ” determines how the center signal

“C” is to be proce ssed. It can be left un modified, distributed to left and right, discarded or high pass filtered, whereby the low pass signals are distr ibuted to

left and right.

2.6.1.1. Decoder Matrix

The Decoder Matrix allows three settings:

– ADAPTIVE:

The Adaptive Matrix is used for Dolby Surround Pro

Logic. Even sound material not encoded in Dolby

Surround will produce good surround effects in this

mode. The use of the Adaptive Matrix requires a

license from Dolby Laboratories (See License

Notice on page 3).

– PASSIVE:

A simple fixed matrix is used for surround sound.

– EFFECT:

A fixed matrix that is used for mono sound and special effects. With Adaptive or Passive Matrix no surround signal is present in case of mono, moreover in

Adaptive mode even the left and right output channels carry no signal (or just low frequency signals in

case of Center Mode = NORMAL). If surround

sound is still required for mono signals, the Effect

Matrix can be used. This forces the surround channel to be active. The Effect Matrix can be used

together with 3D-PANORAMA. The result will be a

pseudo stereo effect or a broadened stereo image

respectively.

8 Micronas

PRELIMINARY DATA SHEET DPL 4519G

2.6.1.2. Surround Reproduction

Surround sound can be reproduced with four choices:

– REAR_SPEAKER:

If there are any surround speakers connected to the

system, this mode should be used. Useful loudspeaker combinations are (L, C, R, S) or (L, R, S).

– FRONT_SPEAKER:

If there is no surround speaker connected, this

mode can be used. Surround information is mixed to

left and right output but without creating the illusion

of a virtual speaker. It is similar to stereo but an

additional center speaker can be used. This mode

should be used with the Adaptive decoder Matrix

only. Useful loudspeaker combinations are (L, C, R)

(Note: the surround output channel is muted).

– PANORAMA:

The surround information is mixed to left and right in

order to create the illusion of a virtual surround

speaker. Useful loudspeaker combinations are (L,

C, R) or (L, R) (Note: the surround output channel is

muted).

– 3D-PANORAMA:

Like PANORAMA with improved effect. This algorithm has been approved by the Dolby Laboratories

for compliance with the "Virtual Dolby Surround"

technology. Useful loudspeaker combinations are

(L, C, R) or (L, R) (Note: the surround output channel is muted).

2.6.1.3. Center Modes

Four center modes are supported:

– NORMAL:

small center speaker connected, L and R speakers

have better bass capability. Center signal is high

pass filtered.

– WIDE:

L, R, and C speakers all have good bass capability.

2.6.1.4. Useful Combinations of Surround Processing Modes

In principle, "Decoder Matrix", "Surround Reproduction", and "Center Modes" are independent settings (all

"Decoder Matrix" settings can be used with all "Surround Reproduction" and "Center Modes") but there

are some combinations that do not create "good"

sound. Useful combina tio ns ar e

Surround Reproduction and Center Modes

– REAR_SPEAKER:

This mode is used if surround speakers are available. Useful center modes are NORMAL, WIDE,

PHANTOM, and OFF.

– FRONT_SPEAKER:

This mode can be used if no surround speaker but a

center speaker is connected. Useful center modes

are NORMAL and WIDE.

– PANORAMA or 3D-PANORAMA:

No surround speaker used. Two (L and R) or three

(L, R, and C) loudspeakers can be used. Useful

center modes are NORMAL, WIDE, PHANTOM,

and OFF.

Center Modes and Decoder Matrix

– PHANTOM:

Should only be used together with ADAPTIVE

Decoder Matrix.

– NORMAL and WIDE:

Can be used together with any Surround Decoder

Matrix.

– OFF:

This mode can be used together with the PASSIVE

and EFFECT Decoder Matrix (no center speaker

connected).

– PHANTOM:

No center speaker used. Center signal is distributed

to L and R (Note: the center output channel C is

muted).

– OFF:

No center speaker used. Center signal C is discarded (Note: the center output channel C is

muted).

Micronas 9

DPL 4519G PRELIMINARY DATA SHEET

2.6.2. Examples

Table 2–1 shows some examples of how these modes

can be used to configure the IC. The list is not

intended to be complete, more modes are possible.

Table 2–1: Examples of Surround Configurations

Configurations

Stereo

Stereo

Surround Modes as defined by Dolby Laboratories

Dolby Surround Pro Logic

Dolby 3 Stereo

Virtual Dolby Surround

Surround Modes that use the Dolby Adaptive Matrix

3-Channel Virtual Surround

Passive Matrix Surround Sound

Speaker

Config-

1)

uration

(L,R) −− −

2)

(L,C,R,S) ADAPTIVE REAR_

(L,R,S) ADAPTIVE REAR_

(L,C,R) ADAPTIVE FRONT_

(L,R) ADAPTIVE 3D_PANORAMA PHANTOM

2)

(L,C,R) ADAPTIVE 3D_PANORAMA NORMAL

Surround Processing Mode

Register (4B

Decoder Matrix

[15:8]

hex

)

Surround

Reproduction

[7:4]

SPEAKER

SPEAKER

SPEAKER

Center Mode

[3:0]

NORMAL

WIDE

PHANTOM

NORMAL

WIDE

WIDE

4-Channel Surround

3-Channel Surround

2-Channel Micronas 3D Surround Sound (MSS)

3-Channel Micronas 3D Surround Sound (MSS)

(L,C,R,S) PASSIVE REAR_

SPEAKER

(L,R,S) PASSIVE REAR_

SPEAKER

(L,R) PASSIVE 3D_PANORAMA OFF

(L,C,R) PASSIVE 3D_PANORAMA NORMAL

NORMAL

WIDE

OFF

WIDE

Special Effects Surround Sound

4-Channel Surround for mono

2-Channel Virtual Surround for mono

3-Channel Virtual Surround for mono

1)

Speakers not in use are muted automatically.

2)

The implementation in products requires a license from Dolby Laboratories Licensing Corporation (see note on page 3).

(L,C,R,S) EFFECT REAR_

SPEAKER

(L,R) EFFECT 3D_PANORAMA OFF

(L,C,R) EFFECT 3D_PANORAMA NORMAL

NORMAL

WIDE

WIDE

10 Micronas

PRELIMINARY DATA SHEET DPL 4519G

2.6.3. Application Tips for using 3D-PANORAMA

2.6.3.1. Sweet Spot

Good results are on ly obtained in a rather close area

along the middle axis between the two loudspeakers:

the sweet spot. Moving away from this position

degrades the effect.

2.6.3.2. Clipping

For the test at Dolby Labs, it is very impor tant to h ave

no clipping effects even with worst case signals. The

2

S-prescale register has to be set to values of max

I

(16

10

hex

). This is sufficient in terms of clipping.

dec

However, it was found, that by reducing the prescale to

a value lower than 16

more convincing effects are

dec

generated in case of very high dynamic signals. A

value of 10

is a good compromise between overall

dec

volume and additional headroom.

Test signals : sine sweep with 0 dB FS; L only, R only,

L&R equal phase, L&R anti phase.

Listening tests: Dolby Trailers (train trailer, city trailer,

canyon trailer...)

Great care has to be taken with sys tems that us e one

common subwoofer: A single loudspeaker cannot

reproduce vir tual sound locations. The cros sove r frequency must be lower than 120 Hz.

2.6.3.4. Cabinet Requirements

During listeni ng tests at Dolby Laboratories, no resonances in the cabinet should occur.

Good material to check for resonances are the Dolby

Trailers or other dynamic sound tracks.

2.6.4. Input and Output Levels for

Dolby Surround Pro Logic

2

The nominal inpu t level (in put sensitivity) for the I

Inputs is −15 dBFS. The highest possible input level of

0 dBFS is a ccepted with out inter nal overflow. The I

S-

2

S-

prescale value should be set to values of max 0 dB

).

(16

dec

With higher prescale values lower input sensitivities

can be accommodated. A higher input sensitivity is not

possible, because at least 15 dB headr oo m is requ ired

for every input according to the Dolby specifications.

2.6.3.3. Loudspeaker Requirements

The loudspeakers used and their positioning inside the

TV set will greatly influence the performance of the virtualizer. The algorithm works with the direct sound

path. Reflected sound waves reduce the effect. So it’s

most important to have as much direct sound as possible, compared to indirect sound.

To obtain the approval for a TV set, Dolby Laboratories

require mounting the loudspeakers at the front of t he

set. Loudspeakers radiat ing to the side of the TV set

will not produce co nvincing effects. Good d irect ional ity

of the loudspeakers towards the listener is optimal.

The virt ualizer was specially developed for implementation in TV sets. Even for rather small stereo TV's, sufficient sound effects can be obtained. For small set s,

the loudspeaker placement should be to the side of the

CRT; for large screen sets (or 16:9 sets), mounting the

loudspeakers below the CRT is a ccep table (larg e separation is preferred, low frequency sp eakers shoul d be

outmost to avoid cancellation effects). Using externa l

loudspeakers with a la rge stereo base will not create

optimal effects.

A full-scale left only i nput (0 dBFS ) will produce a full scale left only output (at 0 dB volume). The typical output level is 1.37 Vrms for DACM_L. The same holds

true for right only signa ls (1.37 Vrms for DACM_R). A

full-scale inp ut level on both inputs (Lin=Rin=0 dBFS)

will give a center only output with maximum level. A

full-scale input level on both inputs (but Lin and Rin

with inverted phases) will give a surround-only signal

with maximum level.

For reproducing Dolby Pro Logic according to its specifications, the center and surround outputs must be

amplified by 3 dB with respect to th e L and R output

signals. This can be done in two ways:

1. By implementing 3 dB more amplification for center

and surround loudspeaker outputs.

2. By always selecting volume for L and R 3 dB lower

than center and surround. Method 1 is preferable,

as method 2 lowers the achievable SNR for left and

right signals by 3 dB.

2.7. SCART Signal Routing

2.7.1. SCART Out Select

The loudspeakers should be able to reproduce a wi de

frequency range. The most impor tant fr equency range

starts from 160 Hz and ranges up to 5 kHz.

The SCART Output Select block includes full matrix

switching facilities. The switches are controlled by the

ACB user register (see page page 30).

Micronas 11

DPL 4519G PRELIMINARY DATA SHEET

2.7.2. Stand-by Mode

If the DPL 4519G is switched off by first pulling

STANDBYQ low and th en ( aft er >1 µs delay) switching

off DVSUP and AVSUP, but k eeping AHVSUP (‘Stand-

by’-mode), the SCART switches maintain their position and function. This allows the copying from

selected SCART-inputs to SCART-outputs in the TV

set’s stand-by mode.

In case of power on or starting from stand-by (see

details on the power-up sequence in Fig. 4–19 on

page 52), all internal registers except the ACB register

(page 30) are reset to the default configuration (see

Table 3–5 on page 17) . The reset positio n of the ACB

register becomes ac ti ve after the fi rst I

2

C transmission

into the Baseband Processing part (subaddress

). By transmitting the ACB regis ter firs t, the rese t

12

hex

state can be redefined.

2

S Bus Interfaces

2.8. I

The DPL 451 9G has two kin ds of interfaces: synch ron

master/slave input/output interfaces running on 48 kHz

and an asynchron slave interface.

The interfaces accept a variety of formats with different

sample width, bit-orientation, and wordstrobe timing.

2

S options are set by means of the MODUS or

All I

2

S_CONFIG register.

I

2

2.8.1. Synchronous I

The synchronous I

S-Interface(s)

2

S bus interface consists of the

pins:

– I2S_DA_IN1, I2S_DA_IN2/3 (I2S_DA_IN2 in

PQFP80 package):

2

S serial data input, 16, 18...32 bits per sample.

I

2.8.2. Asynchronous I

The asynchronous I

2

S-Interface

2

S slave interface allows the

reception of digi tal audio s ignals with arbitrar y sample

rates from 5 to 50 kHz. The synchronization is performed by means of an adaptive sample rate converter. No oversampling clock is required.

The following pins are us ed for the asynchronous I

2

bus interface (serve only as input):

– I2S_WS3

– I2S_CL3

– I2S_DA_IN2/3 (I2S_DA_IN3 in PQFP80 package).

2

The interface accepts I

S-input streams with MS B first

and with sample widths of 16,18...32 bits. With left/

right alignment and wordstrobe timing polarity, there

are additional paramete rs available for the adaption to

a variety of formats i n the I2S CONF IGURATION register.

2

2.8.3. Multichannel I

S-Output

Bit[0:1] of the I2S CONFIGURATION register (see

page 20) switches the output to 8 channel multichannel output mode. The bit res olution per channel is 32

bit in master mode. While the first two channels can be

selected on the source s elect matr ix, chann els 3- 8 are

always connected to the I2S_3 input channels 3-8.

Both, master and slave mode is possible, as long as as

the wordstrobe has only one positive edge per frame in

slave mode.

2

2.8.4. Asynchronous Multichannel I

S-Input

The DPL 4519 G supports two kinds of asynchronous

multichannel input:

S

–I2S_DA_OUT:

2

S serial data output, 16, 18...32 bits per sample.

I

– I2S_CL:

2

S serial clock.

I

–I2S_WS:

2

S word strobe signal defines the left and right

I

sample.

If the DPL 4519G serves as the master on the I

2

interface, the clock and word strobe lines are driven by

S

– the asynchronous I2S_3 interface can be switched

to multichannel mode (bit [8] of the I2S CONFIGURATION register is set to 1. The number of channels must be even and less or equal eight.

– All I2S input lines (I2S_DA_IN1, I2S_DA_IN2 and

I2S_DA_IN3 in PQFP80 package) can be switched

to asynchronous two channel mode (bit[2] set to 1 in

the I2S CONFIGURATION register). The common

clock is I2S_WS3 and I2S_CL3. No synchronous

I2S interfaces are available in this mode.

the DPL 4519G. In this mode, only 16, 32 bits per

sample can be selected. In slave mode, these lines are

input to the DPL 4519G and the DPL 4519G clock is

synchronized to 384 times the I2S_WS rate (48 kHz).

2

S timing diagram is shown in Fig. 4–21 on

An I

page 55.

12 Micronas

PRELIMINARY DATA SHEET DPL 4519G

2.9. Digital Control I/O Pins

The static level of the digital input/output pins

D_CTR_I/O_0/1 is switchable between HIGH and

LOW via the I

(see page 30). This enables the contro lling o f externa l

hardware switch es or other devices via I

2

C-bus by means of the ACB register

2

C-bus.

The Modus Register can set the digital input/output

pins to high impedance (see page 19). So the pins can

be used as input. The current state can be read out of

the STATUS register (see page page 21).

2.10. Clock PLL Oscillator and Crystal Specifications

The DPL 4519G derives all internal system clocks

from the 18.432 MHz oscillator. In I

2

S-slave mode of

the synchronous interface, the clock is phase-locked to

the corresponding source.

For proper performance, the DPL clock oscillator

requires a 18.432-MHz crystal. Note that for the

phase-locked modes (I

tolerance are required. The asynchronous I

2

S-slave), crystals with tighter

2

S3 slave

interface uses a different locking mechanism and does

not require tighter crystal tolerances.

Micronas 13

DPL 4519G PRELIMINARY DATA SHEET

3. Control Interface

2

C Bus Interface

3.1. I

3.1.1. Device and Subaddresses

2

The DPL 4519G is controlled via the I

C bus slave

interface.

The IC is selected by transmitting one of the

DPL 4519G device addres ses. In order to allow up to

three DPL or MSP ICs to be connected to a single bus,

an address select pin (ADR_SEL) has been implemented. With ADR_SEL pulled to high, low, or left

open, the DPL 4519G responds to different device

addresses. A device addr ess pair is defi ned as a wr it e

address and a read address (see Table 3–1).

Writing is done by sending the device write address,

followed by the subaddress byte, two address bytes,

and two data bytes. Reading is done by sending the

write device addres s, followed by the subaddress byte

and two address bytes. Wit hout sendin g a stop c ondition, reading of the addressed data is completed by

sending the device read address and reading two

bytes of data. Refer to Sectio n 3.1.4. for the I

protocol and to Section 3.4. “Programming Tips” on

page 34 for proposals of DPL 4519G I

2

2

C bus

C telegrams.

See Table 3–2 for a list of available subaddresses.

typical respons e time is a bout 0.3 ms. If the DPL cannot accept another complete byte of data until it has

performed some other function (for example, serv icing

an internal in terrupt), it wi ll hold the clock line I2C_ CL

LOW to force the transmitter into a wait state. The

positions within a transmissio n wher e thi s may happen

are indicated by “Wait” in S ec tio n 3.1.4. The ma xi mum

wait period of the DPL dur ing normal operation mode

is less than 1 ms.

3.1.2. Internal Hardware Error Handling

In case of any internal hardware error (e.g. interruption

of the power supply of the DPL), the DP L’s wait period

is extended to 1.8 ms. After this time period elapses,

the DPL releases data and clock lines.

Indicating and solving the error status:

To indicate the error status, the remaining acknowledge bits of the actual I

Additionally, bit[14] of CONTROL is set to one. The

DPL can then be reset via the I

2

C-protocol will be left high.

2

C bus by transmitting

the reset condition to CONTROL.

Indication of reset:

Besides the possib ility of ha rdware res et, the DPL can

also be reset by means of the RE SET bit in the CO NTROL register by the controller via I

Due to the interna l architec ture of the DPL 4519G, the

IC cannot react immediately to an I

2

Table 3–1: I

ADR_SEL Low

Mode Write Read Write Read Write Read

DPL device add res s 80

C Bus Device Addresses

2

C bus.

2

C request. The

(connected to DVSS)

hex

81

hex

Any reset, even caused by an unstable reset line etc.,

is indicated in bit[15] of CONTROL.

2

A general timing diagram of the I

C bus is shown in

Fig. 4–21 on page 55.

High

(connected to DVSUP)

84

hex

85

hex

88

hex

Left Open

89

Table 3–2: I2C Bus Subaddresses

Name Binary Value Hex Value Mode Function

CONTROL 0000 0000 00 Read/Write Write: Sof tware reset of DPL (see Table 3– 3)

Read: Hardware error status of DPL

WR_DEM 0001 0000 10 Write write address demodulator

hex

RD_DEM 0001 0001 11 Write read address demodulator

WR_DSP 0001 0010 12 Write write address DSP

RD_DSP 0001 0011 13 Write read address DSP

14 Micronas

PRELIMINARY DATA SHEET DPL 4519G

3.1.3. Description of CONTROL Register

Table 3–3: CONTROL as a Write Register

Name Subaddress Bit[15] (MSB) Bits[14:0]

CONTROL 00 hex 1 : RESET

0

0 : normal

Table 3–4: CONTROL as a Read Register (only DPL 4519G-versions from A2 on)

Name Subaddress Bit[15] (MSB) Bit[14] Bits[13:0]

CONTROL 00 hex Reset status after last reading of CONTROL:

0 : no reset occured

1 : reset occured

Reading of CONTROL will reset the bits[15,14] of CONTROL. After Power-on,

Internal hardware status:

not of interest

0 : no error occured

1 : internal error occured

bit[15] of CONTROL will be set; it must be

read once to be resetted.

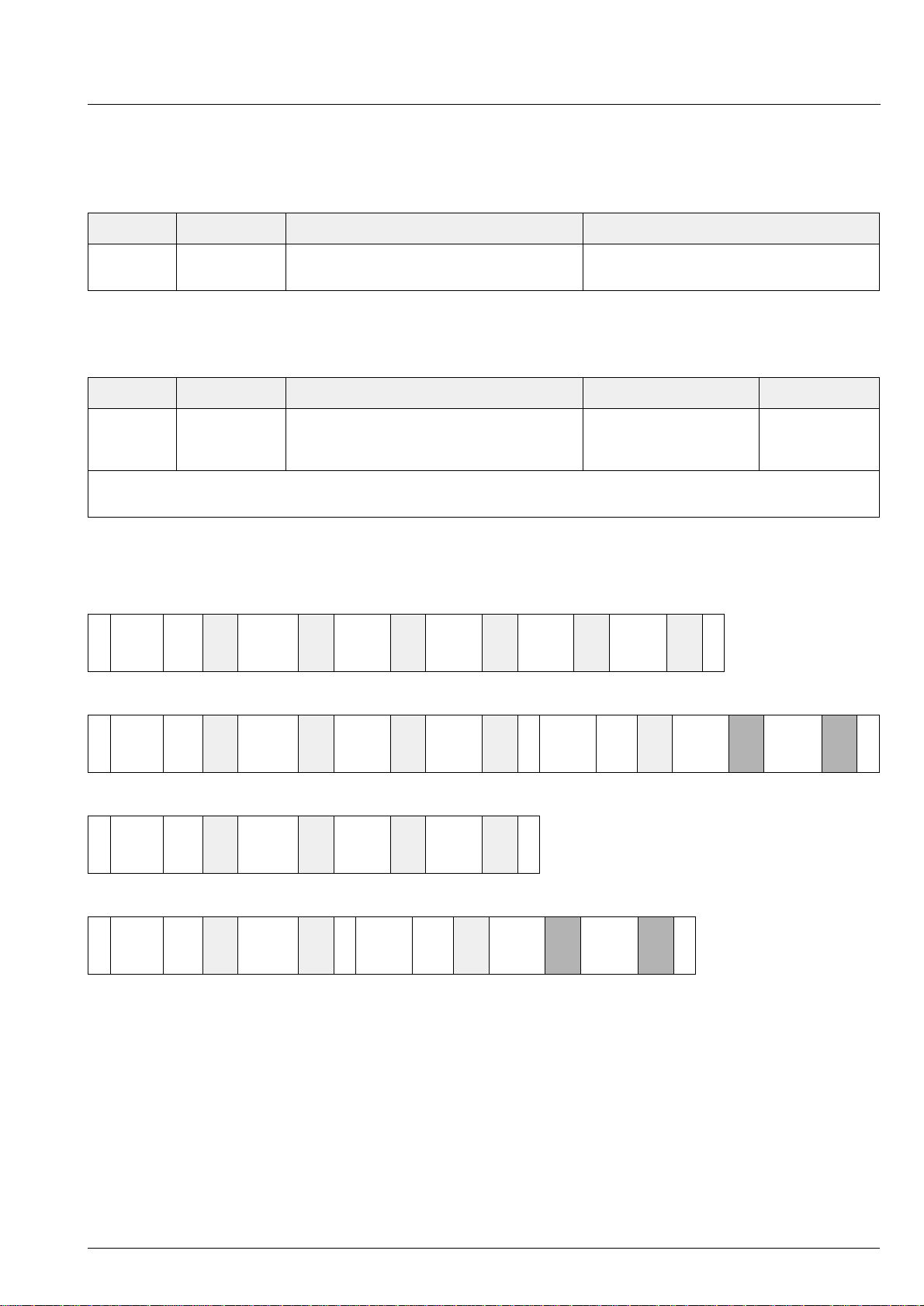

3.1.4. Protocol Description

Write to DSP

Swrite

device

address

Wait

ACK sub-addr ACK addr-byte

high

ACK addr-byte

low

ACK data-byte-

high

ACK data-byte

low

ACK P

Read from DSP

Swrite

device

address

ACK sub-addr ACK addr-byte

Wait

high

ACK addr-byte

low

ACK S read

device

address

Wait

ACK data-byte-

high

ACK data-byte

Write to Control

Swrite

device

address

ACK sub-addr ACK data-byte

Wait

high

ACK data-byte

low

ACK P

Read from Control

Swrite

device

address

Wait

Note: S = I

P = I

ACK 00hex ACK S read

2

C-Bus Start Condition from master

2

C-Bus Stop Condition from master

device

address

Wait

ACK data-byte-

high

ACK data-byte

low

NAK P

ACK = Acknowledge-Bit: LOW on I2C_DA from slave (= DPL, light gray) or master (= controller dark gray)

NAK = Not Acknowledge-Bit: HIGH on I2C_DA from master (dark gray) to indicate ‘End of Read’

or from DPL indicating internal error state

2

Wait = I

C-Clock line is held low, while the DPL is processing the I2C command.

This waiting time is max. 1 ms

NAK P

low

Micronas 15

DPL 4519G PRELIMINARY DATA SHEET

I2C_DA

1

0

S P

I2C_CL

Fig. 3–1: I2C bus protocol (MSB first; data must be stable while clock is high)

3.1.5. Proposals for General DPL 4519G

2

C Telegrams

I

3.1.5.1. Symbols

3.2. Start-Up Sequence:

Po wer-Up and I

After POWER ON or RESET (see Fi g. 4–21), the IC is

in an inactive state. All register s are in the reset pos i-

daw write device address (80

dar read device address (81

< Start Condition

hex

hex

, 85

hex

hex

or 88

or 89

hex

hex

)

)

tion, the analog out puts are muted. Th e controller has

to initialize all r egisters for which a non-default setting

is necessary.

, 84

> Stop Cond iti on

aa Address Byte

dd Data Byte

3.3. DPL 4519G Programming Interface

2

C Controlling

3.1.5.2. Write Telegrams

<daw 00 d0 00> write to CONTROL register

<daw 10 aa aa dd dd> write data into demodulator

<daw 12 aa aa dd dd> write data into DSP

3.1.5.3. Read Telegrams

<daw 00 <dar dd dd> read data from

CONTROL register

<daw 11 aa aa <dar dd dd> read data from demodulator

<daw 13 aa aa <dar dd dd> read data from DSP

3.1.5.4. Examples

<80 00 80 00> RESET DPL statically

<80 00 00 00> Clear RESET

<80 12 00 08 08 20> Set Main channel

source to I2S3 - L/R

<80 12 00 00 73 00> Set Main volume to 0 dB

More examples of typical application protocols are

listed in Section 3 .4. “P rogrammi ng Tips” on page 34.

3.3.1. User Registers Overview

The DPL 451 9G is controlled by mean s of user registers. The complete list of all user registers is given in

the following tables. The registers ar e partitioned into

two sections:

1. Subaddress 10

2. Subaddress 12

for writing, 11

hex

for writing, 13

hex

Write and read regis ters are 16-bit wide, whereby the

MSB is denoted bit[15]. Transmissions via I

for reading and

hex

for reading.

hex

2

C bus

have to take place in 16-bit words (two byte transfers,

with the most significant byte transferred first). All write

registers, except MODUS and I2S CONFIGURATION,

are readable.

Unused parts of the 16-bit write registers must be zero.

Addresses not given in this table must not be

accessed.

16 Micronas

PRELIMINARY DATA SHEET DPL 4519G

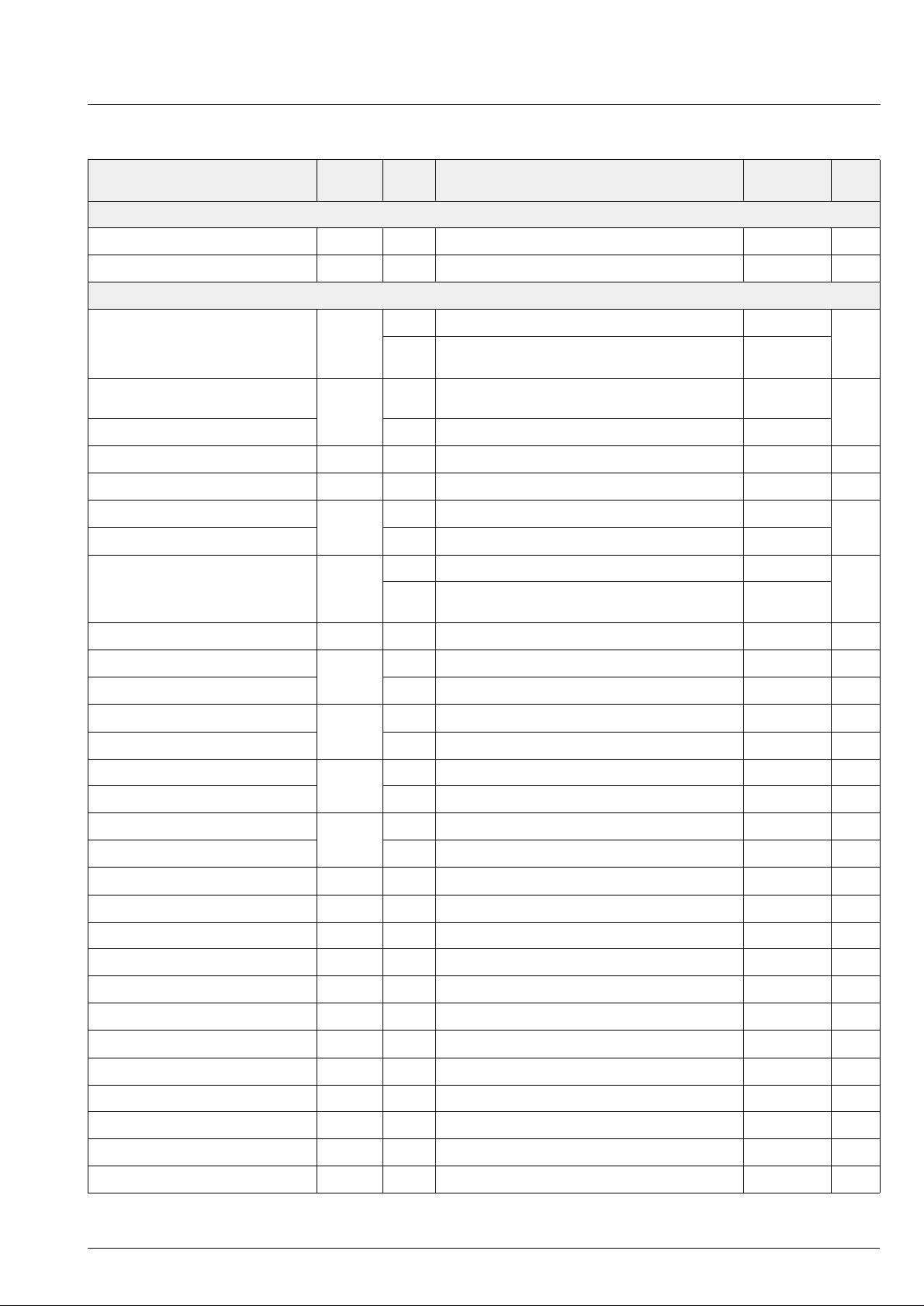

Table 3–5: List of DPL 4519G Write Registers

Write Register Address

(hex)

I2C Subaddress = 10

; Registers are

hex

not

MODUS 00 30 [15:0] I

I2S CONFIGURATION 00 40 [15:0] Configuration of I

I2C Subaddress = 12

; Registers are

hex

all

readable by using I2C Subaddress = 13

Bits Description and Adjustable Range Reset See

readable

2

S options, D_CTR_I/O modes 00 00 19

2

S format 00 00 20

hex

Page

Volume Main channel 00 00 [15:8] [+12 dB ... −114dB, MUTE] MUTE 24

[7:5]

[4:0]

Balance Main channel [L/R] 00 01 [15:8] [0...100 / 100% and 100 / 0...100%]

1/8 dB Steps

must be set to 0

000

bin

00000

bin

100%/100% 25

[−127...0 / 0 and 0 / −127...0 dB]

Balance mode Main [7:0] [Linear / logarithmic mode] linear mode

Bass Main channel 00 02 [15:8] [+20 dB ... −12dB] 0 dB 26

Treble Main channel 00 03 [15:8] [+15 dB ... −12dB] 0 dB 27

Loudness Main channel 00 04 [15:8] [0 dB ... +17 dB] 0 dB 28

Loudness filter characteristic [7:0] [NORMAL, SUPER_BASS] NORMAL

Volume A ux channel 00 06 [15:8] [+12 dB ... −114dB, MUTE] MUTE 24

[7:5]

[4:0]

1/8 dB Steps

must be set to 0

000

bin

00000

bin

Volume SCAR T1 output channel 00 07 [15:8] [+12 dB ... −114dB, MUTE] MUTE 29

2

Main source select 00 08 [15:8] [I

S1, I2S2, I2S3 ch1&2, I2S3 ch3&4,...] undefined 23

Main channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO] SOUNDA 23

2

Aux source select 00 09 [15:8] [I

S1, I2S2, I2S3 ch1&2, I2S3 ch3&4,...] undefined 23

Aux channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO] SOUNDA 23

2

SCART1 source select 00 0A [15:8] [I

S1, I2S2, I2S3 ch1&2, I2S3 ch3&4,...] undefined 23

SCART1 channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO] SOUNDA 23

2

S source select 00 0B [15:8] [I2S1, I2S2, I2S3 ch1&2, I2S3 ch3&4,...] undefined 23

I

2

S channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO] SOUNDA 23

I

2

Prescale I

Prescale I

S3 00 11 [15:8] [00

2

S2 00 12 [15:8] [00

ACB: SCART Switches a. D_CTR_I/O 00 13 [15:0] Bits [15:0] 00

Beeper 00 14 [15:0] [00

2

Prescale I

S1 00 16 [15:8] [00

hex

hex

hex

hex

... 7F

... 7F

... 7F

... 7F

]10

hex

]10

hex

]/[00

hex

hex

... 7F

hex

]10

] 00/00

hex

hex

hex

hex

hex

hex

21

21

30

30

21

Mode tone control 00 20 [15:8] [BASS/TREBLE, EQUALIZER] BASS/TREB 26

Equalizer Main ch. band 1 00 21 [15:8] [+12 dB ... −12 dB] 0 dB 27

Equalizer Main ch. band 2 00 22 [15:8] [+12 dB ... −12 dB] 0 dB 27

Equalizer Main ch. band 3 00 23 [15:8] [+12 dB ... −12 dB] 0 dB 27

Equalizer Main ch. band 4 00 24 [15:8] [+12 dB ... −12 dB] 0 dB 27

Equalizer Main ch. band 5 00 25 [15:8] [+12 dB ... −12 dB] 0 dB 27

Subwoofer level adjust 00 2C [15:8] [0 dB ... −30 dB, mute] 0 dB 29

Micronas 17

DPL 4519G PRELIMINARY DATA SHEET

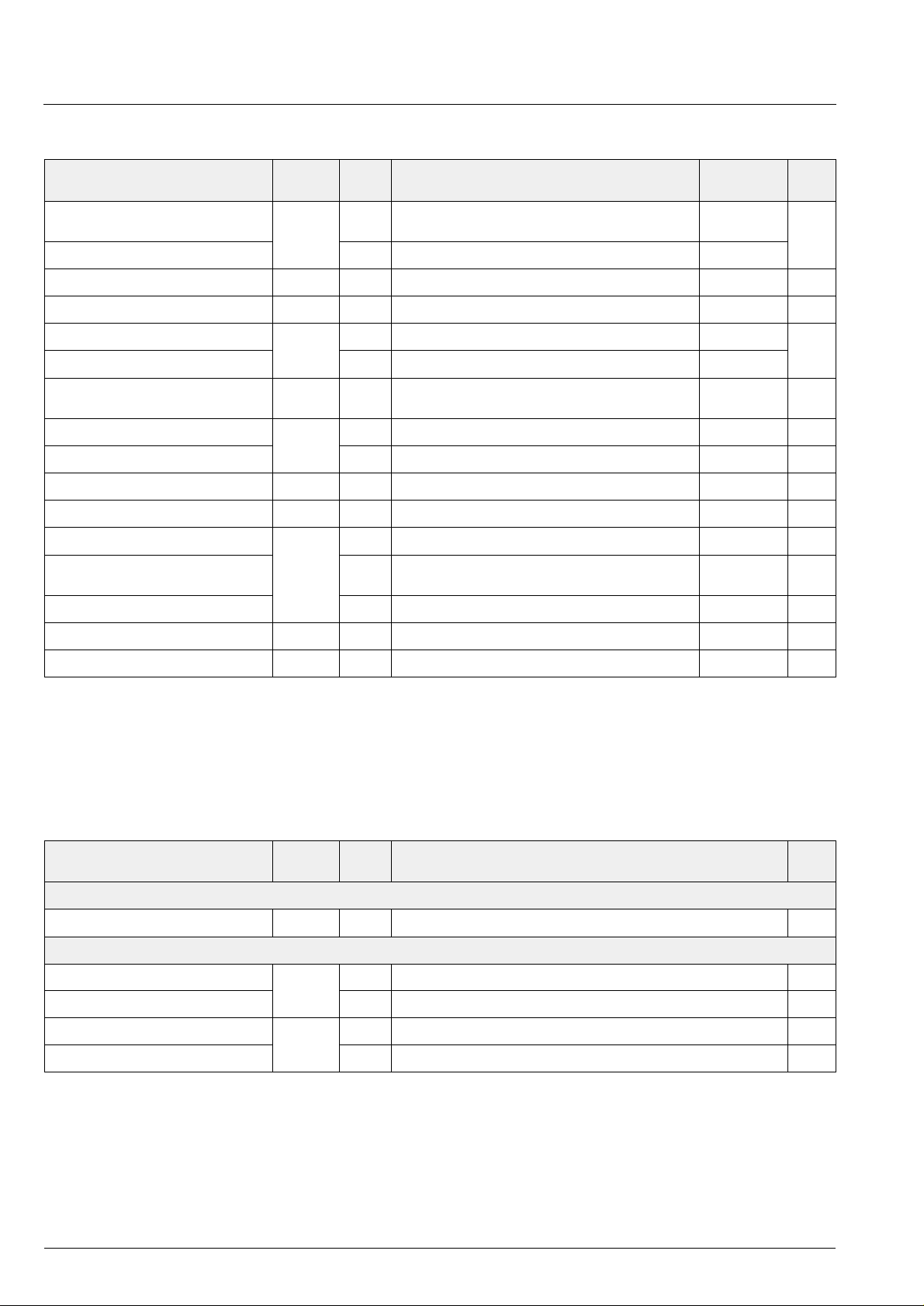

Table 3–5: List of DPL 4519G Write Registers, continued

Write Register Address

(hex)

Balance Aux channel [L/R] 00 30 [15:8] [0...100 / 100% and 100 / 0...100%]

Bits Description and Adjustable Range Reset See

Page

100 %/100 % 25

[−127...0 / 0 and 0 / −127...0 dB]

Balance mode Aux [7:0] [Linear mode / logarithmic mode] linear mode

Bass Aux channel 00 31 [15:8] [+20 dB ... −12 dB ] 0 dB 26

Treble Aux channel 00 32 [15:8] [+15 dB ... −12 dB] 0dB 27

Loudness Aux channel 00 33 [15:8] [0 dB ... +17 dB] 0 dB 28

Loudness filter characteristic [7:0] [NORMAL, SUPER_BASS] NORMAL

2

S3 Resorting 00 36 [15:8] through, straight eight, l/r eight, l/r six, l/r four,

I

2ch through

2

Surround source select 00 48 [15:8] [I

S1, I2S2, I2S3 ch1&2, I2S3 ch3&4,...] undefined 23

00

hex

22

Surround channel matrix [7:0] [SOUNDA, SOUNDB, STEREO, MONO] SOUNDA 23

Spatial effect for surround processing 00 49 [15:8] [0% - 100%] 00

Virtual surround effect strength 00 4A [15:8] [0% - 100%] 00

Decoder matrix 00 4B [15:8] [ADAPTIVE/PASSIVE/EFFECT] 00

Surround reproduction [7:4] [REAR_SPEAKER/FRONT_SPEAKER/PANORAMA/

0

3D_PANORAMA]

Center mode [3:0] [PHANTOM/NORMAL/WIDE/OFF] 0

Surround delay 00 4C [15:0] [5...31ms] 00

Noise Generator 00 4D [15:0] [NOISEL, NOISEC, NOISER, NOISES] 00

hex

hex

hex

hex

hex

hex

hex

31

31

32

32

32

32

32

Table 3–6: List of DPL 4519G Read Registers

Read Register Address

(hex)

I2C Subaddress = 11

; Registers are

hex

not

STATUS 02 00 [15:0] M onitoring of settings e.g. D_CTR_I/O 21

I2C Subaddress = 13

; Registers are

hex

not

writable

DPL hardware version code 00 1E [15:8] [00

DPL major revision code [7:0] [00

DPL product code 00 1F [15:8] [00

DPL ROM version code [7:0] [00

Bits Description and Adjustable Range See

writable

... FF

hex

hex

hex

hex

]33

hex

... FF

]33

hex

... FF

]33

hex

... FF

]33

hex

Page

18 Micronas

PRELIMINARY DATA SHEET DPL 4519G

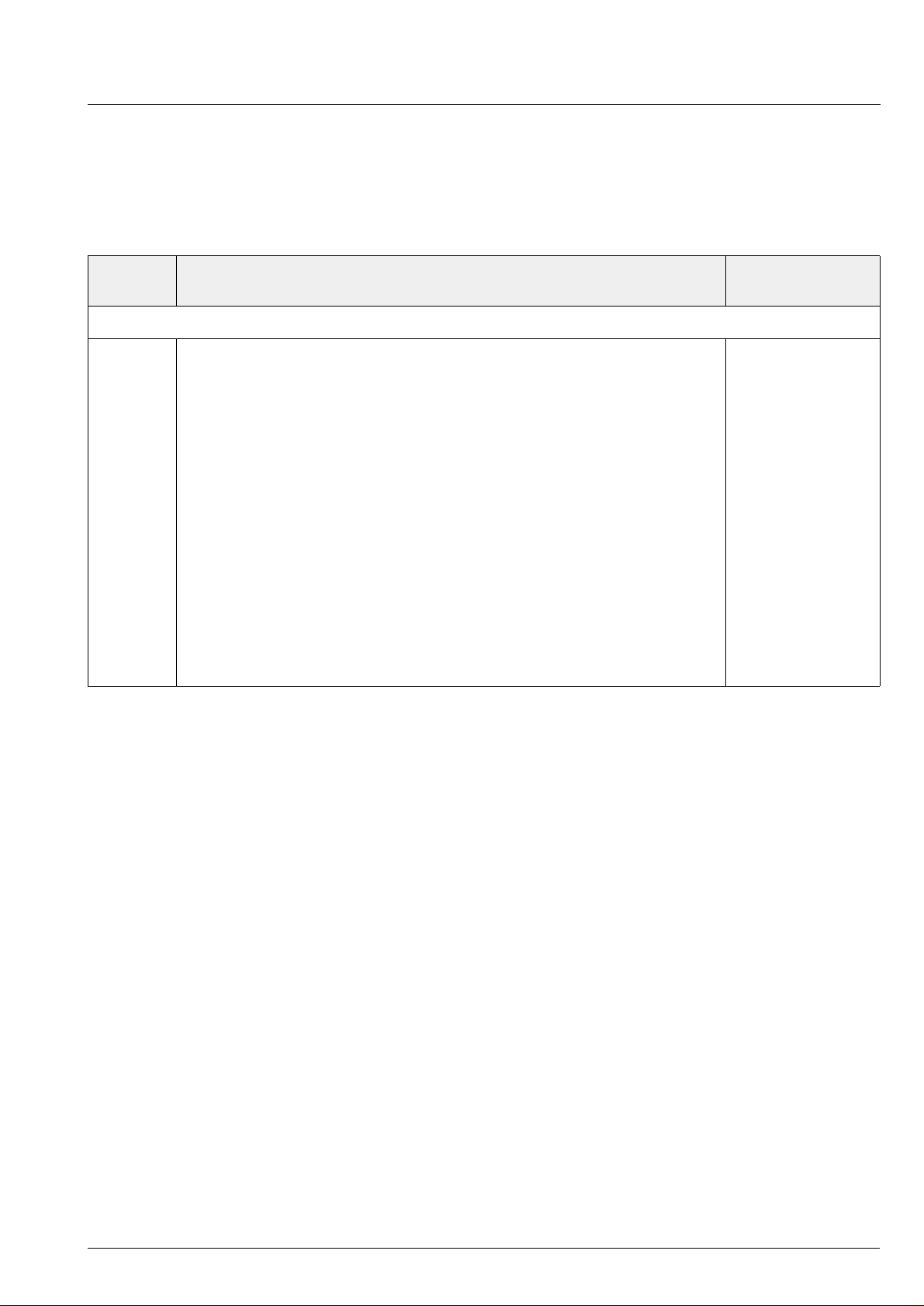

3.3.2. Description of User Registers

2

3.3.2.1. Write Registers on I

C Subaddress 10

hex

Table 3–7: Write Registers on I2C Subaddress 10

Register

Function Name

Address

MODUS

00 30

hex

MODUS Register

bit[15:8] 0 undefined, must be 0

bit[7] 0/1 active/tristate state of audio clock output pin

AUD_CL_OUT

bit[6] word strobe alignment (synchronous I

0 WS changes at data word boundary

1 WS changes one clock cycle in advance

bit[5] 0/1 master/slave mode of I

bit[4] 0/1 active/tristate state of I

bit[3] state of digital output pins D_CTR_I/O_0 and _1

0 active: D_CTR_I/O_0 and _1 are output pins

(can be set by means of the ACB register)

1 tristate: D_CTR_I/O_0 and _1 are input pins

(level can be read out of STATUS[4,3])

bit[2:0] 0 undefined, must be 0

hex

2

S interface

2

S output pins

MODUS

2

S)

Micronas 19

DPL 4519G PRELIMINARY DATA SHEET

Table 3–7: Write Registers on I

Register

Function Name

Address

I2S CONFIGURA TI ON

00 40

hex

I2S CONFIGURATION Register

1)

I2S3

bit[11] I2S data alignment (must be 0 if bit[2] = 1)

0/1 left/right aligned

bit[10] wordstrobe polarity (must be 0 if bit[2] = 1)

1 0 = right, 1 = left

0 1 = right, 0 = left

bit[9] wordstrobe alignment (asynchronous I2S_3)

0 WS changes at data word boundary

1 WS changes one clock cycle in advance

bit[8] Sample Mode

0/1 Two/Multi sample

bit[7:4] Word length of each data packet = (n−2)/2

bit[3]=0, bit[8]=1 (multi-sample input mode)

0111 16 bit

1000 18 bit

...

1111 32 bit

2

C Subaddress 10

, continued

hex

I2S_CONFIG

I2S3_ALIGN

I2S3_WS_POL

I2S3_WS_MODE

I2S3_MSAMP

I2S3_MBIT

bit[3]=0, bit[8]=0 (two-sample input mode)

xxxx 16...32 bit, 18-bit valid

bit[3]=1, bit[8]=1 (multi-sample output mode)

1111 32 bit

bit[3]=1, bit[8]=0 (two-sample output mode)

0111 16 bit

1111 32 bit

2

bit[3] I

S3 Mode

1 output (I2S3 CL/WS active)

0 input (I2S3 CL/WS tristate)

2

S1/2/3

I

2

bit[2] I

S1/2/3 Timing

1I

2

S3 timing for all I2S inputs (1/2/3)

0 default mode

2

S Out

I

bit[1:0] I2S_CL frequency and I2S_DA_OUT sample length

00 2 * 16 bit (1.536 MHz Clk)

01 2 * 32 bit (3.072 MHz Clk)

10 8 * 32 bit (12.288 MHz Clk)

1)

I2S_CL3 frequency depends on bit[8] and bits[7:4] as follows:

[8] = 0, [7:4] = 0111 f = fs*(2*16)

[8] = 0, [7:4] = else f = fs*(2*32)

[8] = 1 f = fs*(8*32)

I2S3_MODE

I2S_TIMING

20 Micronas

Loading...

Loading...