Micronas Intermetall CIP3250A Datasheet

CIP 3250A

Component Interface

Processor

Edition Oct. 9, 1996

6251-403-3AI

ADVANCE INFORMATION

MICRONAS

CIP 3250A

Contents

Page Section Title

4 1. Introduction

4 1.1. Block Diagram

4 1.2. System Configurations

7 2. Functional Description

7 2.1. Analog Front End

7 2.2. Clamping

7 2.3. Matrix

7 2.4. YUV Control (on RGB-path only)

8 2.5. Delay Adjustment

8 2.6. Skew Filter

8 2.7. Fast Blank Processing

8 2.7.1. Soft Mixer

9 2.7.2. Fast Blank Monitor

9 2.8. FSY Front Sync and AVI Active Video In

10 2.9. Digital Input Formats

10 2.9.1. The Chroma Demultiplexers

11 2.10. YUVin Interpolator (LPF 4:4:4)

11 2.11. YUV Output Low-pass Filter 4:2:2 and 4:1:1

13 2.12. Selectable RGB/YUV Output Formats

14 2.12.1. DIGIT 2000 4:1:1 Output Format

14 2.12.2. DIGIT 2000 4:2:2 Output Format

14 2.12.3. DIGIT 3000 Orthogonal 4:2:2 Output Format

15 2.12.4. Orthogonal 4:1:1 Output Format

15 2.12.5. YUV Output Levels

15 2.13. I/O Code Levels

15 2.14. AVO Active Video Output

15 2.15. PRIO Interface

16 2.16. I

2

C Serial Bus Control

ADV ANCE INFORMATION

27 3. Specifications

27 3.1. Outline Dimensions

27 3.2. Pin Connections and Short Descriptions

30 3.3. Pin Descriptions

32 3.4. Pin Configuration

33 3.5. Pin Circuits

35 3.6. Electrical Characteristics

35 3.6.1. Absolute Maximum Ratings

35 3.6.2. Recommended Operating Conditions

36 3.6.3. Characteristics

36 3.6.3.1. Characteristics Standby Input

36 3.6.3.2. Characteristics Test Input

36 3.6.3.3. Characteristics Reset Input

37 3.6.3.4. Characteristics Main Clock Input

37 3.6.3.5. Characteristics Active Video Output

38 3.6.3.6. Characteristics Active Video Input

38 3.6.3.7. Characteristics Fsync Input

39 3.6.3.8. Characteristics I

39 3.6.3.9. Characteristics Luma/Chroma Input

2 Micronas

2

C Bus Interface Input/Output

ADV ANCE INFORMATION

Contents, continued

Page Section Title

40 3.6.3.10. Characteristics Priority Input/Output

41 3.6.3.11. Characteristics Picture Output

42 3.6.3.12. Characteristics Analog R, G, B Inputs

42 3.6.3.13. Characteristics Analog FBL Input

43 4. Application Circuit

44 5. Data Sheet History

CIP 3250A

3Micronas

CIP 3250A

ADV ANCE INFORMATION

Component Interface Processor

Release Notes: Revision bars indicate significant

changes to the previous edition.

1. Introduction

The CIP 3250A is a new CMOS IC that contains on a

single chip the entire circuitry to interface analog YUV/

RGB/Fast Blank to a digital YUV system. The Fast Blank

signal is used to control a soft mixer between the digitized RGB and an external digital YUV source. The CIP

supports various output formats such as YUV

4:1:1/4:2:2 or RGB 4:4:4.

T ogether with the DIGIT 3000 (e.g. VPC 32xxA) or DIGIT

2000 (e.g. DTI 2250), an interface to a TV-scanrate conversion circuit and/or multi-media frame buffer can be

obtained.

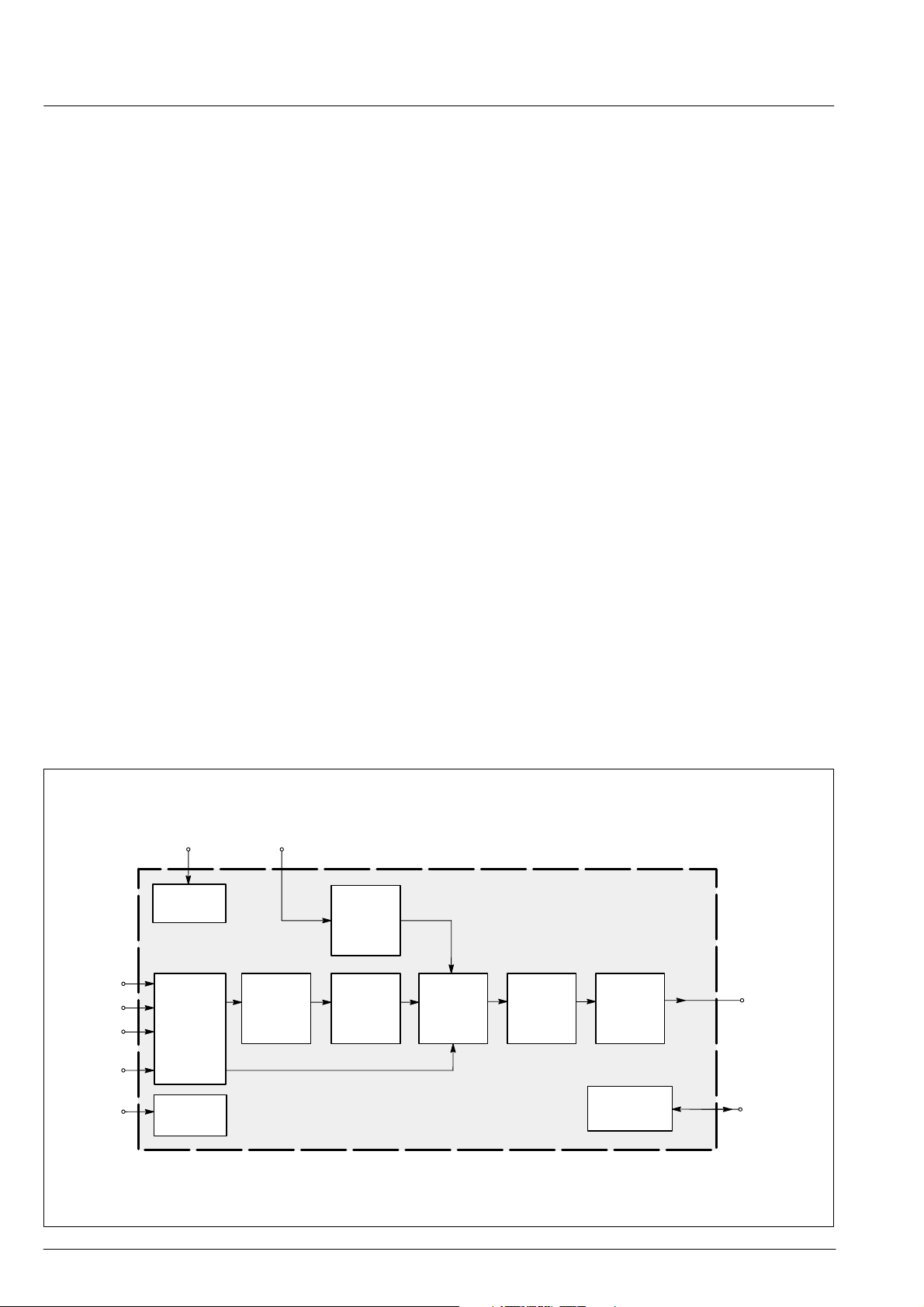

1.1. Block Diagram

The CIP 3250A contains the following main functional

blocks (see Fig.1–1):

– digital matrix RGB ⇒ YUV (Y, B–Y, R–Y)

– luma contrast and brightness correction for signals

from analog input

– color saturation and hue correction for signals from

analog input

– digital input for DIGIT 2000 or DIGIT 3000 formats

– digital interpolation to 4:4:4 format

– high quality soft mixer controlled by Fast Blank signal

– programmable delays to match digital YUVin and ana-

log RGB/YUV

– variable low pass filters for YUV output

– digital output in DIGIT 2000 and DIGIT 3000 formats,

as well as RGB 4:4:4

2

–I

C bus interface

– clock frequency 13.5...20.25 MHz

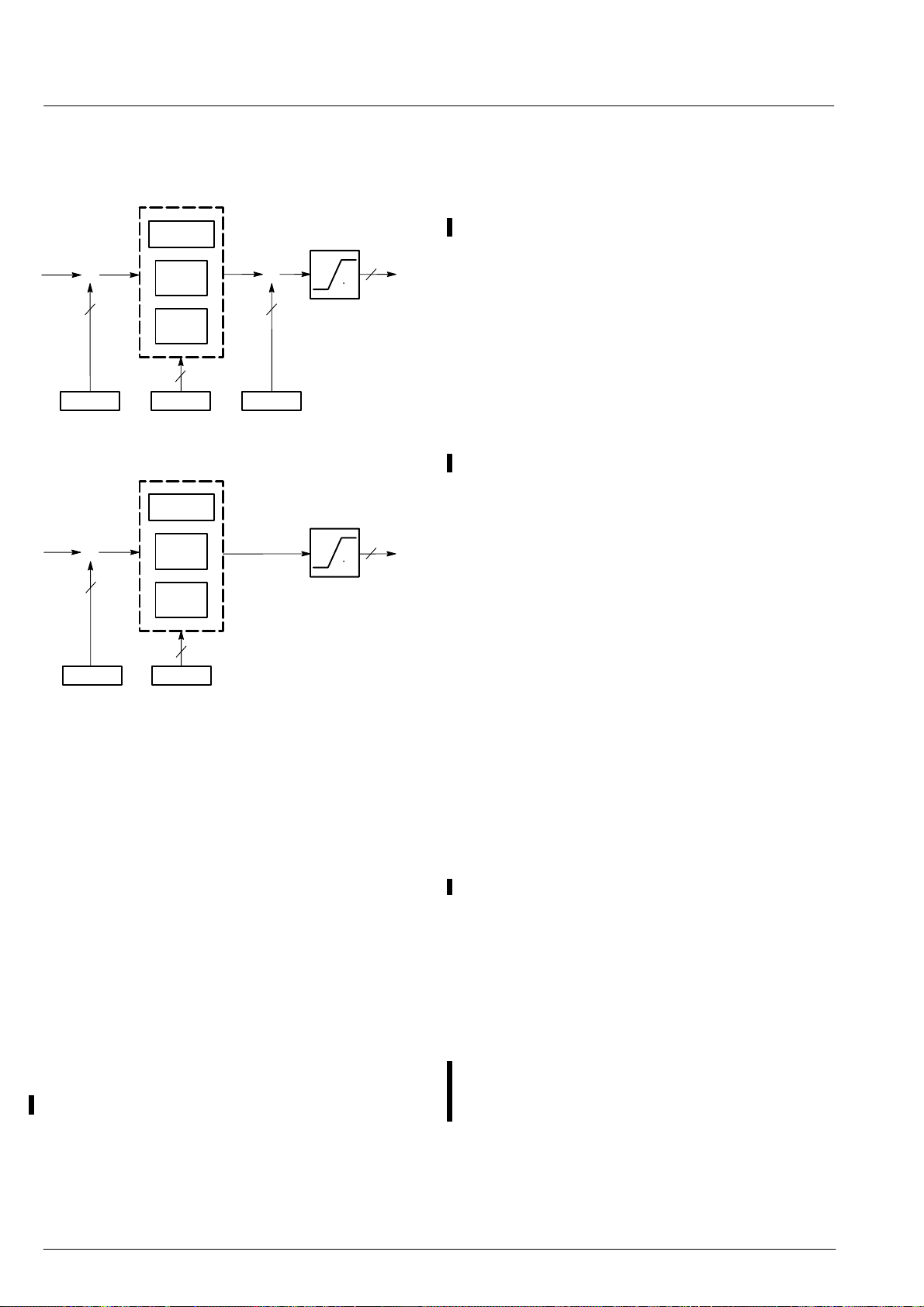

1.2. System Configurations

– analog input for RGB or YUV and Fast Blank

– triple 8 bit analog to digital converters for RGB/YUV

with internal programmable clamping

– single 6 bit analog to digital converter for Fast Blank

signal

YUV 4:1:1

YUV 4:2:2

MATRIX

(on/off)

Format

Conversion

4:4:4

CT

BR

SAT

R/V

G/Y

B/U

FSY

FSY

interface

ADC

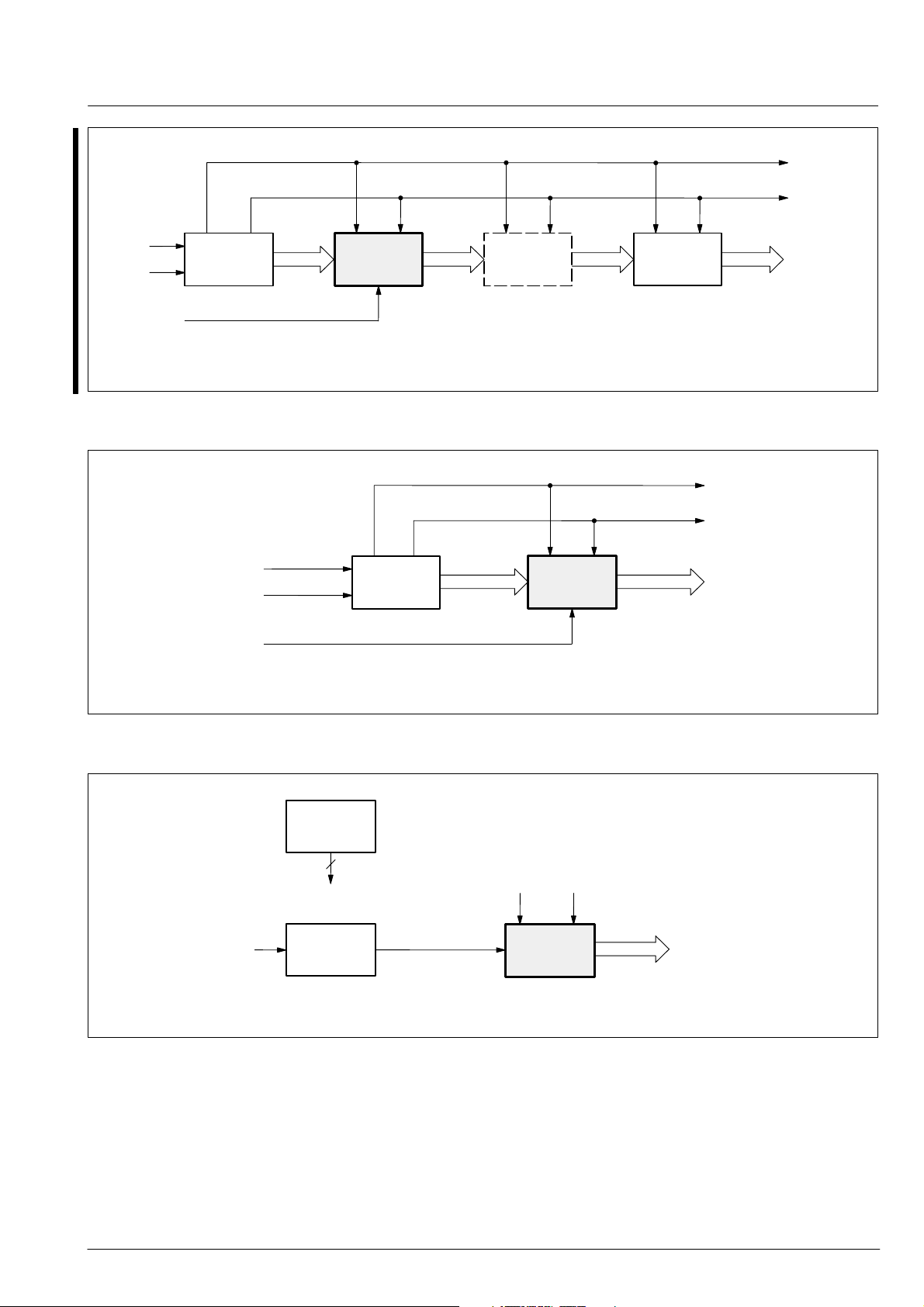

The following figures, 1–2 and 1–3, show different basic

system applications for the CIP 3250A in the DIGIT 3000

environment. Beyond that, a stand alone application

(figure 1–4) also shows the flexibility of the CIP 3250A

in implementing simple analog video interfaces to digital

standards.

YUV 4:1:1

YUV 4:2:2

SOFT

MIXER

(4:4:4)

Adjustable

LPF

Format

Conversion

RGB 4:4:4

FBL

CLK

clock

buffer

I2C

interface

I2C

Bus

Fig. 1–1: Block diagram of the CIP 3250A Component Interface Processor

4 Micronas

ADV ANCE INFORMATION

CIP 3250A

H,V-Sync

Clock

CVBS

Y, C

VPC32xxA

CIP3250A

100 Hz/PAL+

Feature Box

RGB/YUV

Fast Blank

Fig. 1–2: Complete DIGIT 3000 application for 100 Hz and/or PAL+

CVBS

VPC32xxA

CIP3250A

Y, C

RGB/YUV

Fast Blank

Fig. 1–3: DIGIT 3000 video front-end for ITUR-601 or square pixel data output

DDP3310B

CRT

H,V-Sync

Clock

YUV Data

CCU 3000

2

CVBS

2

I

C Bus

TV Module

RGB/YUV

Clock

CIP3250A

HSYNC, VSYNC

orthogonal

YUV pixel

Fig. 1–4: CIP 3250A in a stand alone video application for multimedia or scan rate conversion

5Micronas

6 Micronas

CIP 3250A

R/V

G/Y

B/U

FBL

FSY

SKEW FSY AVI HSYNC VSYNC

*1)

clamp clamp clamp

AVI

*2) RGB–ADC

8

ADC 8 bit

8

ADC 8 bit

8

ADC 8 bit

6

6 bit

ADC

mode

ctrl

clamp control

12, 16

Matrix (on/off)

YUVin

CT

BR

SAT

DL1

adjust

(78)

Formatter

UV–mux

WR

RD

DL2

adjust

(48...212)

Input

LPF

4:4:4

Skew

Filter

*2) *1)

Skew

Filter

*2)

SOFT

MIX

Skew

Filter

Video

Control

Logic

AVI

Adjustable

LPF

UV–mux

Formatter

Output

72 Bit

PRIO

coder

12

16

24

AVO

R/UV

G/Y

B

3

PRIO

clock

buffer

CLK I2C Bus

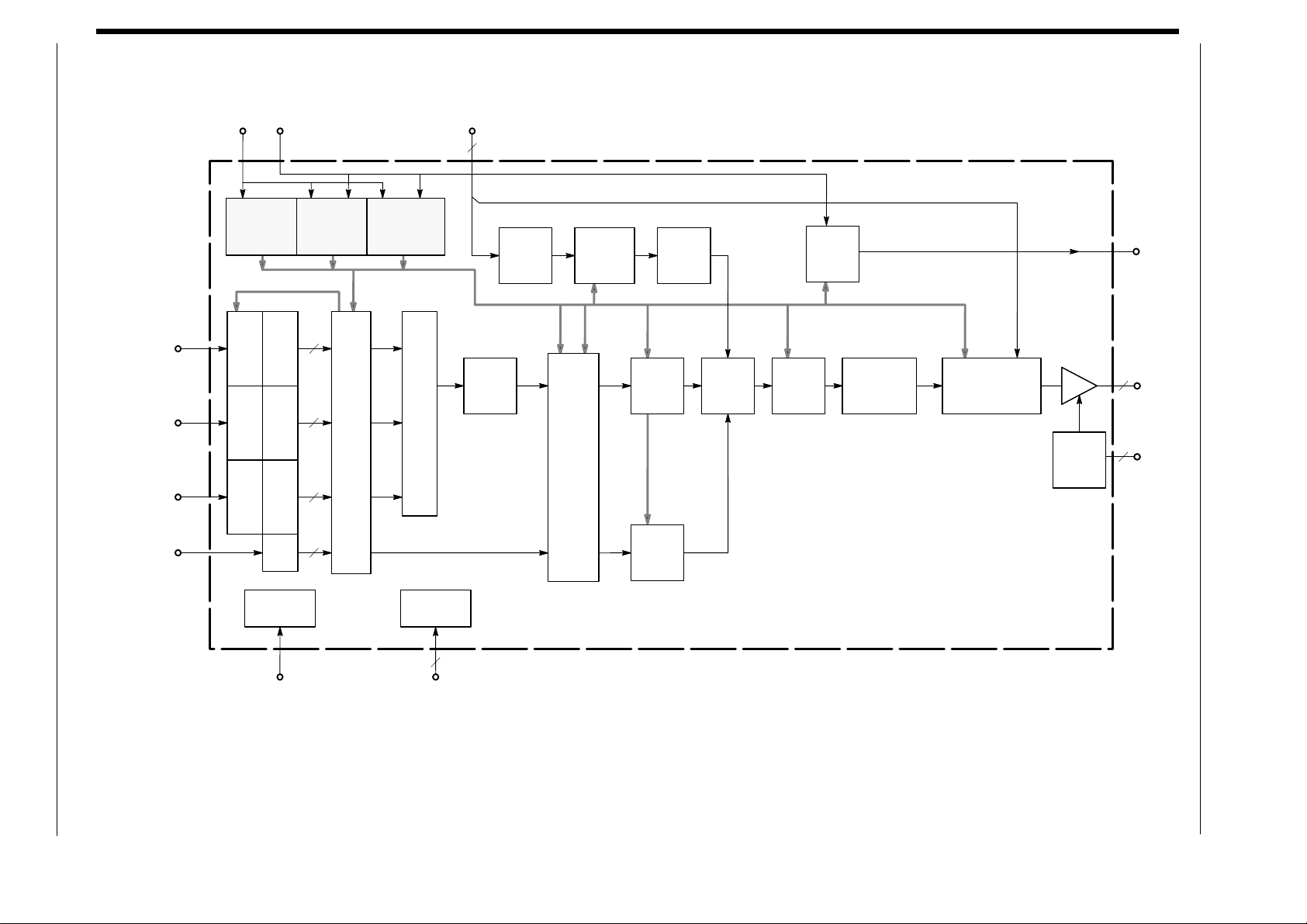

Fig. 2–1: CIP 3250A block diagram

Note:

*1) Only used in DIGIT 2000 mode

*2) Only used in DIGIT 3000 mode

I2C

interface

2

CIP 3250A

ADV ANCE INFORMATION

ADV ANCE INFORMATION

CIP 3250A

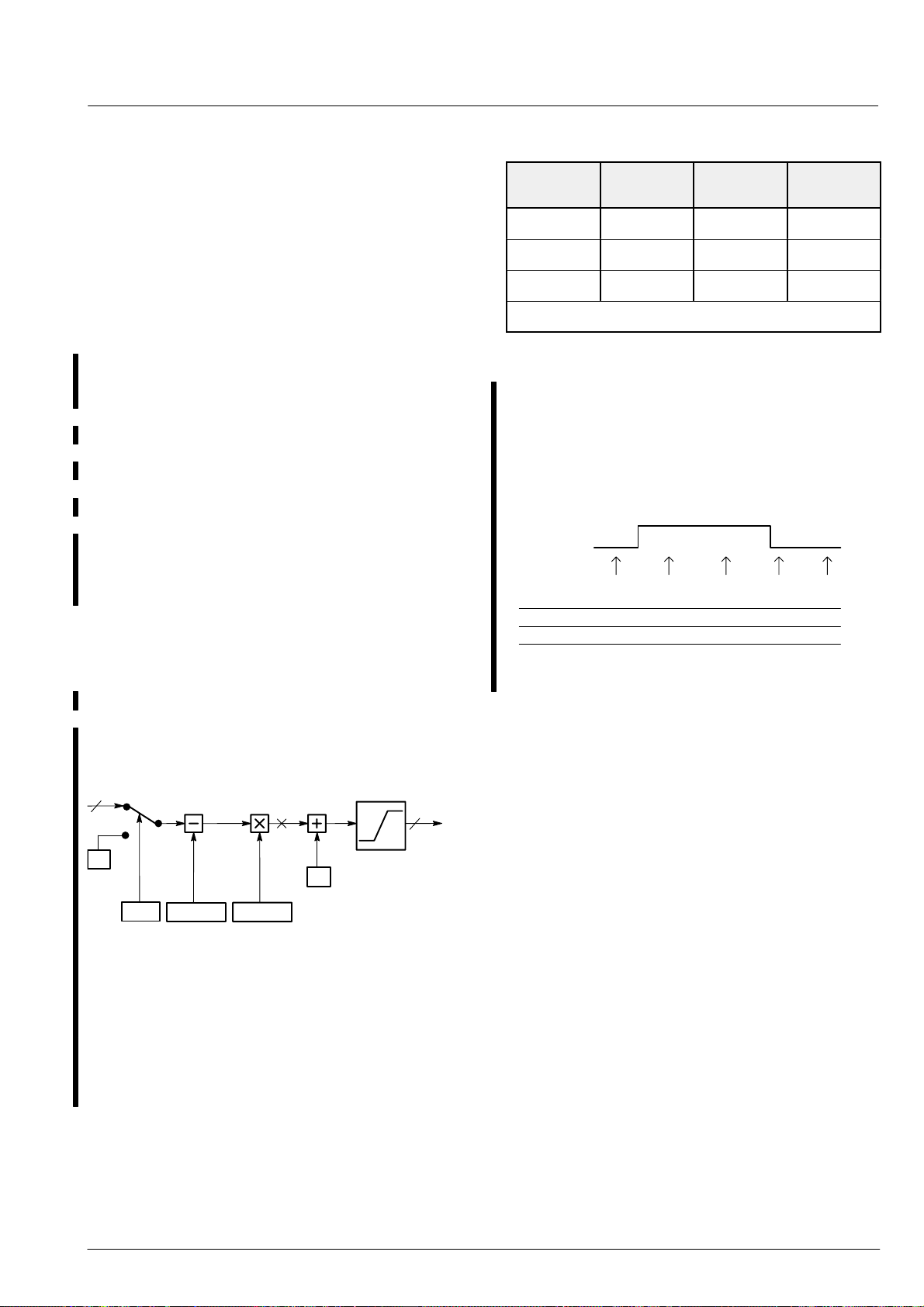

2. Functional Description

This section describes the functionality of the various

blocks shown in the block diagram of Fig. 2–1 in detail.

The CIP 3250A is controlled via an I

2

C bus interface. For

information regarding how to program the registers of

the CIP 3250A, please refer to the register list (see

Tables 2–9 and 2–10). The I

addressing to access the register. In the following, I

2

C bus interface uses sub-

2

registers are referenced by the sub-addresses given in

parenthesis; for example, I

2

C register <9>. To interface

correctly , a pin description for the CIP 3250A is given in

section 3.3.

2.1. Analog Front End

– SCART-level inputs (RGB/YUV and

Fast Blank = 1.0 Vpp, Fast Blank must be ext. clipped)

– triple 8-bit ADC for RGB/YUV

– 6 bit ADC for Fast Blank

– sampling rate 13.5 to 20.25 MHz

– no sync separation included

All analog video input signals and the analog Fast Blank

signal must be band limited to 5 MHz before analog to

digital conversion.

ue via I

2

C registers <18> and <19>. A window size of 32

or 64 sample clocks is recommended. Clamping is disabled if start and stop values are equal after reset. Once

enabled it can not be switched off. Using a coupling capacitor of 220 nF, a hum of approximately 400 mV at

50 Hz can be compensated.

2.3. Matrix

C

– matrix RGB ⇒ Y(R–Y)(B–Y):

Y = 0.299*R + 0.587*G + 0.114*B

(R–Y) = 0.701*R – 0.587*G – 0.114*B

(B–Y) = –0.299*R – 0.587*G + 0.886*B

– fixed coefficients with a resolution of 8 bits.

– matrix enable/disable for analog RGB/YUV input pro-

grammable via I2C register

The matrix of the CIP 3250A converts the digitized RGB

signals to the intermediate signals Y, R–Y, and B–Y. Enable the matrix via I

2

C register <04>MAON. The intermediate signals at the output of the matrix can be converted to YUV signals of the DIGIT 2000 system or to

YC

of the DIGIT 3000 system by the YUV control (see

rCb

section 2.4.). To omit conversion from RGB to

Y(R–Y)(B–Y), switch off the matrix and the CTBRST

block via I2C register <04>MAON and <04>CBSON.

2.4. YUV Control (on RGB-path only )

The CIP 3250A can process either analog YUV input

signals or analog RGB input signals which are ACcoupled with a nominal input voltage level of 700 mV +

3 dB (1 V

). There is no circuitry implemented for inter-

PP

nal sync separation. Input voltage range of the Fast

Blank signal is 0 to 1 V. The Fast Blank input signal is

DC-coupled.

2.2. Clamping

– internal clamping for RGB and YUV with adjustable

start and width

– black level reference only during horizontal and verti-

cal blanking interval on RGB/YUV inputs

– no proper clamping if sync is on G

In RGB mode, clamping takes place on black level (digi-

tal 16 or 8) using a clamping window as described below.

In YUV mode, clamping is done on black level (digital 16)

for Y (luma) and on saturation level zero (digital 128) for

UV (chroma) using a clamping window. Select between

RGB mode and YUV mode via I

2

C register <09>YUV.

The black level reference value (digital 16 or 8) can be

selected via I

2

C register <09>CLMPOFS. In a standard

DIGIT 2000 application without a conversion of Y (luma)

to ITUR code levels at the digital inputs (see section 2.9.

<10>YLEVEL), convert the black level to digital 32 via

2

I

C register <04>CLSEL.

– Y contrast (ct) and brightness (br) with rounding or

noise shaping and limiting to 8 bit:

Y = Y*ct + br

ct = 0...63/32 in 64 steps

br = –128...+127 in 256 steps

– UV saturation (sat) with rounding or noise shaping and

limiting to 8 bit (controllable by CCU via I

U

= (B–Y) * Usat

EXT

V

= (R–Y) * Vsat

EXT

2

C bus):

Usat,Vsat = 0...63/32 in 64 steps

(U

= [0.5*(B–Y)] * Usat

INT

V

= [0.875*(R–Y)] * Vsat)

INT

Within the CTBRST block, switched on via I

2

C register

<04>CBSON, two different options can be used to convert from (R–Y)(B–Y) to UV (PAL standard). In internal

mode (UV

), conversion to PAL standard is done be-

INT

fore the multiplication of the contents of the saturation

registers. Using the external mode (UV

EXT

) of

<04>SMODE, the user has to implement the conversion

factors via the two saturation registers (Usat, Vsat).

Since the two saturation registers can be programmed

separately , it is also very easy to convert to YC

rCb

(Stu-

dio standard) of the DIGIT 3000 system.

Contrast, brightness, and saturation can be adjusted for

the video signals of the analog input via I

2

C registers

<00> to <03>. A functional description of this circuit can

be found in figures 2–2 and 2–3 respectively.

The clamping window is programmable in reference to

the H-sync signal (see Fig. 2–13) by a start and stop val-

T o improve the amplitude resolution of the luma (Y) and

chroma (UV) video signals after multiplication with the

7Micronas

CIP 3250A

ADV ANCE INFORMATION

weighting factors (ct) and (sat), the user can select between rounding and two different modes of noise shaping (1 bit error diffusion or 2 bit error diffusion).

Rounding

Y

6 8

ct br

1 bit

Err. Diff.

2 bit

Err. Diff.

2

Select

255

I2C Registers

Y

0

8

Fig. 2–2: Luma Contrast & Brightness Adjustment

Rounding

–128

VR–Y

U

8

B–Y

sat

1 bit

Err. Diff.

6

2 bit

Err. Diff.

Select

2

I2C Registers

127

Fig. 2–3: Chroma Saturation Adjustment

2.5. Delay Adjustment

– DL1 to compensate internal processing delay of the

CIP 3250A in reference to digital YUVin

– DL1 to compensate processing delay of the DIGIT

2000 SPU chroma channel in SECAM mode

– DL2 to compensate delay between digital YUVin and

analog RGBin or FSY; as for example, produced by

ACVP or SPU.

T o mix the analog RGB/YUV input signals and the digital

YUVin input signals at the soft mixer correctly, in reference to the horizontal synchronization pulse, two processing delay adjustments can be made. In many system applications, ICs in front of the CIP 3250A cause a

fixed processing delay in the digital YUVin path. Therefore, a delay of up to 210 sample clocks can be programmed via I

2

C register <21>DL2 to match analog

RGB/YUV data with digital YUV data . If the delay is less

than 48 sample clocks, the DL1 block can be activated

(80 sample clocks) via I

2

C register <10>DL1ON to get

a value for <21>DL2 within the range of 48 to 210.

In applications where there will be no fixed delay be-

tween digital YUVin and analog RGB/YUV, the pixel

skew correction can be switched on via I

2

C register

<17>PXSKWON. In this mode, the DL2 block serves as

a variable delay to match the analog RGB/YUV data with

digital YUV data. The first pixel of analog RGB/YUV written into the DL2 block (which works like a FIFO) is selected by <21>DL2. Read of the DL2 block starts synchronously with the AVI input, which in turn marks the

first pixel in digital YUV data (see Fig. 2–14). Care must

be taken that the number of pixels stored in DL2 block

must be within the limits of 48 to 210.

In case of SECAM processing in the DIGIT 2000 environment, the digital luma and chroma signals do not

match in front of the CIP 3250A. Therefore, the I

2

C register <10>SECAM must be enabled, and fine adjustment

has to be carried out within the ACVP.

2.6. Skew Filter

Two interpolation filters perform data orthogonalization

(= skew correction) for luma and chroma in case of a

non-line-locked system clock. The skew value is serially

input via the FSY input. In a system environment where

digital YUV data are orthogonal (e.g. DIGIT 3000), the

skew correction must be set to DIGIT 3000 mode via I

2

register <04>SKWCBS in order to apply skew correction

to analog RGB/YUV data only. Additionally, the skew

correction must be switched on via I

2

C register

<04>SKWON. This has to be done in order to mix the

analog input with the digital YUV input correctly and to

output the mixed YUV signal in an orthogonal format.

For standard DIGIT 2000 operation, the skew correction

should be switched off via I

2

C register <04>SKWON, in

order to output the mixed YUV data with the same skew

values as the digital YUV input. Only in special applications (e.g. multi media), where the output connects to a

field or frame memory which processes orthogonal data,

the skew correction for mixed YUV data has to be

switched on and set to DIGIT 2000 mode via I

2

C register

<04>SKWCBS.

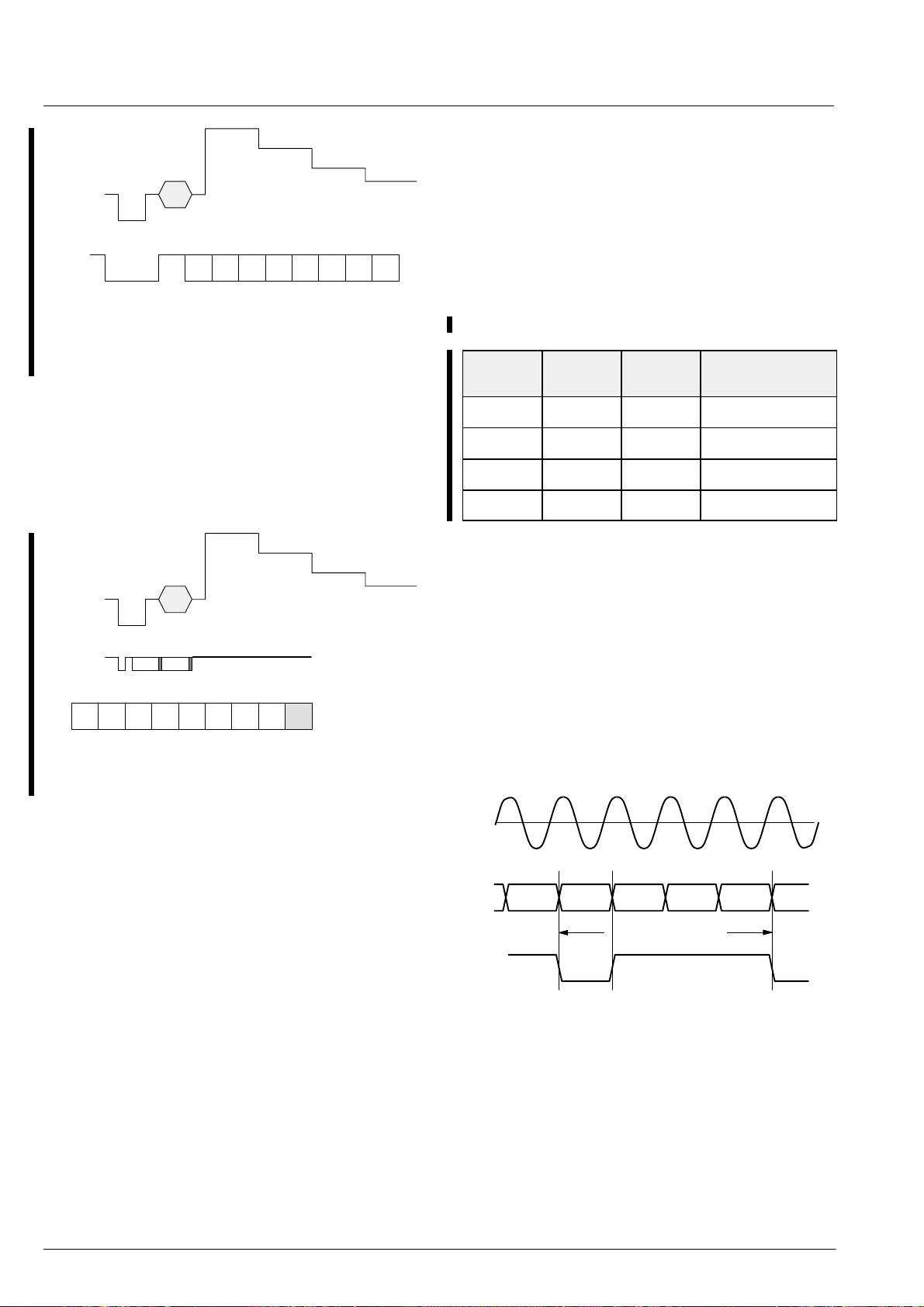

2.7. Fast Blank Processing

– mixing of RGB-path and YUV-path in YUV 4:4:4 format

controlled by the Fast Blank signal

– linear or nonlinear mixing technique selectable

– programmable polarity of Fast Blank signal

– programmable step response of Fast Blank signal

– RGB-path or YUV-path can be statically selected

– Fast Blank signal monitoring

2.7.1. Soft Mixer

In the Fast Blank signal path, special hardware is supplied to improve edge effects, such as blurring because

of band limiting in the analog front end. Different step responses are user selectable via I

2

C register <12>MIX-

AMP, still obtaining high quality phase resolution. Also,

C

8 Micronas

ADV ANCE INFORMATION

CIP 3250A

the polarity of the Fast Blank signal can be changed via

2

I

C register <12>MIXAMP. The I2C register

<11>FBLOFF influences the phase delay between the

RGB path and the Fast Blank signal (see Fig. 2–4).

Additionally, a delay of –1 to 2 clocks between the Fast

Blank signal and the RGB-path is programmable via I

2

register <16>FBLDEL. By selecting a positive delay,

shadowing of characters can be obtained, if the background color of the RGB-path is set to black.

With the built-in linear mixer, the CIP 3250A is able to

support simple AB roll techniques between analog input

(A) and digital YUV input (B):

VideoOut = A * (1 – FBLMIX/32) + B * FBLMIX/32,

controllable via the Fast Blank signal (FBL):

FBLMIX = INT[(FBL – FBLOFF)* MIXAMP/2] + 16,

with FBL of values from 0 to 63. The mixing coefficient

FBLMIX resolves 32 steps within the range from 0 to 32

(dependent on step response chosen via I2C register

<12>MIXAMP) (see Fig. 2–4).

When the I2C register bit <16>FBLCLP is enabled, the

soft mixer operates independently of the analog Fast

Blank input. FBL is clamped to digital 31 (see Fig. 2–4).

Mixing between RGB-path and YUV-path is controllable

via the I

2

C register <11>FBLOFF .

Table 2–1: Source selection of soft mixer

<11>

PASSRGB

0 X X RGB

C

1 0 MIX YUV/RGB

1 1 X YUV

X: don’t care

<06>

PASSYUV

Fast Blank

signal

Source

2.7.2. Fast Blank Monitor

Bits 0 to 3 of I2C register <27> are monitoring the analog

Fast Blank input. Reading I2C register <27> Fig. 2–5 displays the contents depending on the analog FBL input

signal.

analog fast

blank input

<27>FBLSTAT

<27>FBLRISE

<27>FBLFALL

<27>FBLHIGH

2

C

reading I

register <27>

0 1100

01 00

00 01

01 110

0

0

Fig. 2–5: Fast Blank Monitor

2.8. FSY Front Sync and AVI Active Video In

FBL (0...63)

FBLMIX

32

0

I2C Registers

6

31

0

6

1

fblclp

fbloff mixamp

1/2

16

Fig. 2–4: Fast Blank Processing

Select the linear mixer or the nonlinear mixer via I2C register <12>SELLIN. If the nonlinear mixer is selected, a

dynamic delay control of the analog RGB/YUV input can

be chosen, to avoid edge artefacts of the RGB/YUV signal (e.g. shading), during transition time of Fast Blank

signal with the I2C register <12>CTRLDLY.

In some applications, it is desired to disable the control

by the Fast Blank signal and to pass through the digital

YUVin path or the analog RGB/YUV path. This is possible by adequately programming the I

2

C registers

<06>PASSYUV and <11>PASSRGB (Table 2–1).

– DIGIT 2000 chroma sync detection

– DIGIT 2000 throughput of 72-bit data and clock

– skew data input for DIGIT 2000

– skew data input for DIGIT 3000

– HSYNC as timing reference for clamping pulse gener-

ator

– active video input to indicate valid video data and to

synchronize chroma multiplex for DIGIT 3000

The FSY input and the AVI input are used to supply all

synchronization information necessary. Three basic

modes of operation can be selected via I

2

C registers

<06>D2KIN, <17>D2KSYNC, <17>SYNCSIM, and

<17>P72BEN.

In a DIGIT 2000 system environment, the CIP 3250A receives the synchronization information at the FSY input

via the DIGIT 2000 SKEW-protocol. The A VI Input may

be connected to ground GND or VDD (see section

2.14.).

9Micronas

CIP 3250A

input

analog

video

Skew

data

Bit:

(not in scale)

skew

MSB

01234567

skew

LSB

ig–

ig–

nored

nored

V: Vert. sync

0 = off

1 = on

V

ADV ANCE INFORMATION

DIGIT 2000, and the YUV 4:2:2 (16 bit) standard from

DIGIT 3000. Therefore, the CIP 3250A can be used in

either the DIGIT 2000 system environment or the DIGIT

3000 system environment. Refer to I

2

C registers

<06>DELA YU, <10>UVFRM3, and <10>UVFRM1 for a

correct setup. Additionally, within the DIGIT 2000 system, a Y (luma) format conversion to ITU-R 601 can be

achieved via programming the I

2

C register <10>YLE-

VEL.

Table 2–2: Digital input selection

Fig. 2–6: DIGIT 2000 skew data

In a DIGIT 3000 system environment, the CIP 3250A receives the synchronization information at the FSY input

via the DIGIT 3000 FSY -protocol (see Fig. 2–7). The A VI

input receives the chroma multiplex information implicitly with the rising edge of the AVI signal.

input

analog

video

FSY

skew

F1

MSB

F0, F2...F5: reserved

F0

F1

skew

ig–

LSB

nored

(not in scale)

ig–

V

nored

Parity

V: Vert. sync

0 = off

1 = on

Fig. 2–7: DIGIT 3000 front sync format

<06>

DELAYU

<11>

UVFRM3

<11>

UVFRM1

Digital

Input Format

0 0 0 DIGIT 2000 4:2:2

0 0 1 DIGIT 2000 4:1:1

1 1 0 DIGIT 3000 4:2:2

1 0 0 MAC

2.9.1. The Chroma Demultiplexers

In DIGIT 2000 mode, via pins 36 to 39, the CIP 3250A

receives the V and U signals from the C0 to C3 outputs

of the color decoder, time-multiplexed in 4-bit nibbles

(Fig. 2–8). For the digital signal processing, the 4-bit V

and U chroma nibbles are demultiplexed to 8-bit signals

by the V and U demultiplexers. Both demultiplexers are

clocked by the main clock. They are synchronized to the

V and U transmission during the vertical blanking period.

In a stand alone application, for example, RGB-analogto-digital conversion, a horizontal sync pulse must serve

the FSY input, and a vertical sync pulse must serve the

AVI input. The polarity of these two sync pulses can be

programmed via I

2

C registers <10>AVIINV and

<07>FSYINV.

Inside the CIP 3250A, synchronization information is be-

ing decoded and used to control clamping, DL2, skew filters, video control logic, input formatter, and output formatter as shown in Fig. 2–1.

2.9. Digital Input Formats

– YUV 4:2:2 (16 bit) from DIGIT 2000 and DIGIT 3000

(YUV as well as YCrCb)

– YUV 4:1:1 (12 bit) from DIGIT 2000

– input levels according to DIGIT 2000/DIGIT 3000

The CIP 3250A supports the YUV 4:1:1 (12 bit) standard

from DIGIT 2000, the YUV 4:2:2 (16 bit) standard from

a)

H

b)

U MSB V LSB V MSB U LSB U MSB

L

four clock periods

H

c)

L

Fig. 2–8: Timing diagram of the multiplexed color difference signal transfer between decoder and CIP

3250A

Notes to Fig. 2–8:

a) CLK main clock signal

b) Multiplexed color difference signals from PVPU/

ACVP/SPU/VSP/DMA to DTI 2260

c) Sync pulse on C0 output during sync time in vertical

blanking interval.

10 Micronas

ADV ANCE INFORMATION

CIP 3250A

2.10. YUVin Interpolator (LPF 4:4:4)

– UV-Interpolation 4:1:1 or 4:2:2 ⇒ 4:4:4

In order to mix the digital input data with the 4:4:4 video

standard from the analog RGB/YUV input, correctly, the

chroma samples of the digital input have to be interpolated.

In case of YUV 4:1:1 input from DIGIT 2000, a two stage

interpolation filter is implemented. In the first stage, an

interpolation filter is used, which converts the YUV 4:1:1

standard into the YUV 4:2:2 standard.

In the second stage, the interpolation is from the YUV

4:2:2 to YUV 4:4:4.

In the case of YUV 4:2:2 input, only the second stage is

necessary.

Refer to I

and <10>UVFRM1 to choose the correct interpolation

filters (see Fig. 2–2).

2

C registers <06>DELAYU, <10>UVFRM3,

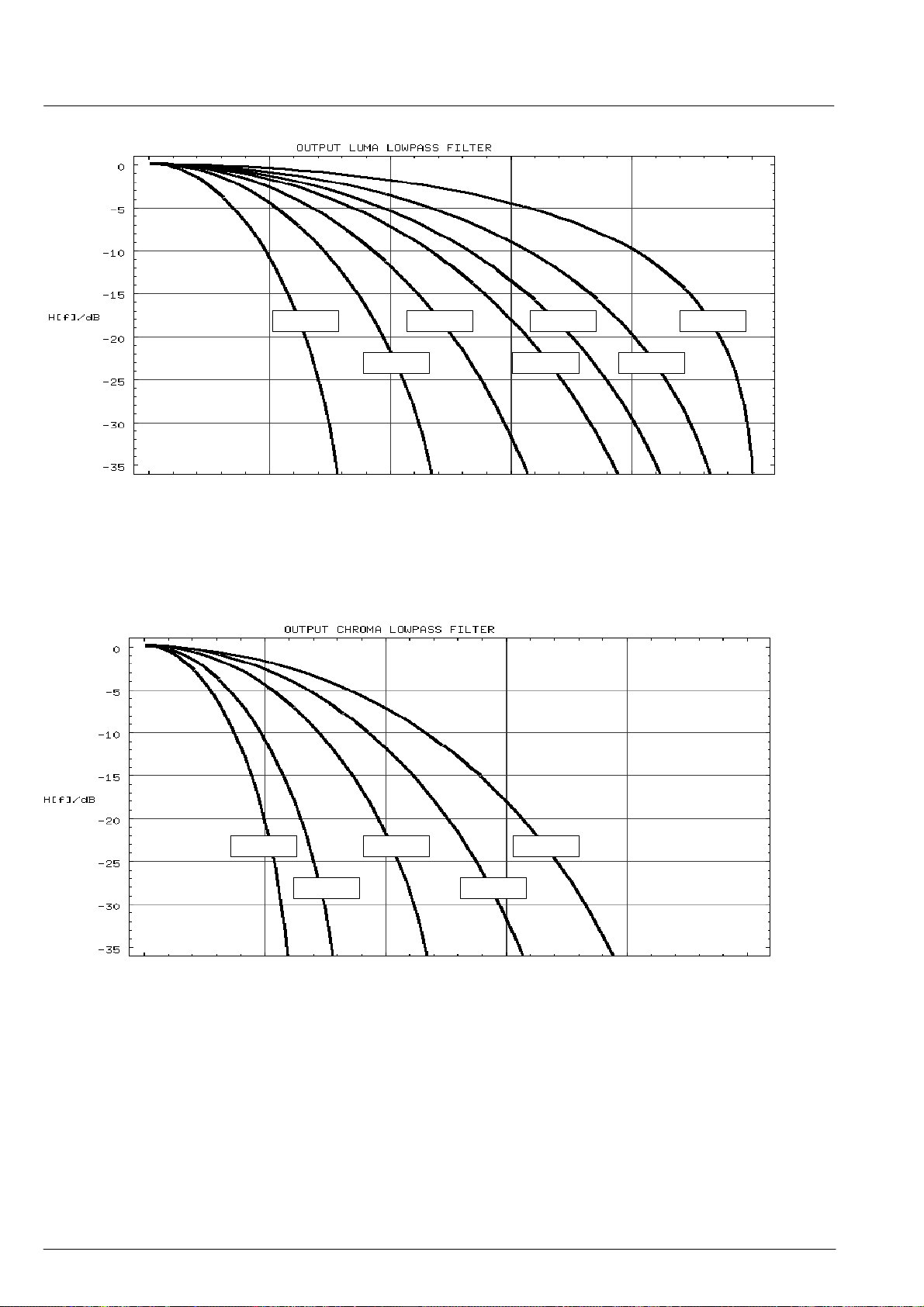

2.11. YUV Output Low-pass Filter 4:2:2 and 4:1:1

– Y low-pass filter with 7 selectable cutoff frequencies

– UV low-pass decimation filter 4:4:4 ⇒ 4:2:2/4:1:1 with

5 selectable cutoff frequencies

To meet the bandwidth requirements of different video

standards, such as 4:2:2 or 4:1:1 at various sampling

frequencies, the luma signal (Y) and the chroma signal

(UV) can be lowpass filtered. There are 7 different cutoff

frequencies selectable for luma, via I

<05>LPFLUM and 5 different cutoff frequencies selectable for chroma, via I

spectra of the luminance filters are shown in Fig. 2–9,

and the spectra of the chrominance filters are shown in

Fig. 2–10.

2

C register <07>LPFCHR. The

2

C register

11Micronas

CIP 3250A

0 0.1*fs 0.2*fs 0.3*fs 0.4*fs 0.5*fs

ADV ANCE INFORMATION

Y7 Y5 Y3 Y1

Y6 Y4 Y2

Fig. 2–9: Spectra of selectable luminance filters

UV5

UV4 UV2

0 0.1*fs 0.2*fs 0.3*fs 0.4*fs 0.5*fs

UV3 UV1

Fig. 2–10: Spectra of selectable chrominance filters

12 Micronas

ADV ANCE INFORMATION

CIP 3250A

2.12. Selectable RGB/YUV Output Formats

– RGB, 8-bit pure binary (24 bit)

– YUV 4:2:2 (16 bit) for DIGIT 2000, DIGIT 3000, and

Philips/Siemens

– YUV 4:1:1 (12 bit) for DIGIT 2000 and Philips/Siemens

– UV format selectable between 2’s complement and

binary offset

In a first stand alone application, the CIP 3250A can

serve as a RGB video analog-to-digital converter to output digital R, G, and B in a pure binary format, 8 bits pure

binary per channel, and a sampling rate between 13.5

MHz and 20.25 MHz.

In a second stand alone application, the CIP 3250A can

serve as a YUV or RGB (with the matrix switched on) video analog-to-digital converter to output digital YUV , supporting various formats such as YUV 4:1:1 (12 bit) from

DIGIT 2000 and Philips, YUV 4:2:2 (16 bit) from DIGIT

2000 and DIGIT 3000, or YUV 4:2:2 (16 bit) industry

standard. Additionally, the signed format of the UV signal is programmable between 2’s complement and

binary offset. A sampling rate between 13.5 MHz and

20.25 MHz can be selected, and the YUV output data

can be low pass filtered.

In a DIGIT 2000 environment, the CIP 3250A can process either RGB or YUV signals from the analog Input,

mix it with the digital YUV Input data – controlled by the

Fast Blank input, and generate low pass filtered output

data in the YUV 4:1:1 (12 bit) DIGIT 2000 format. A sampling rate locked to the color subcarrier frequency (4*fsc)

for the NTSC or PAL video standard has to be used.

In a DIGIT 3000 environment, the CIP 3250A can process either RGB or YUV signals from the analog input,

mix it with the digital YUV input data – controlled by the

Fast Blank input, and generate low pass filtered output

data in the YUV 4:2:2 (16 bit) DIGIT 3000 format. Additionally, the signed format of the UV signal is programmable between 2’s complement and binary offset. The

sampling rate is derived from the VPC 320x and ranges

from 13.5 to 20.25 MHz for all of the video standards.

The U and V chrominance samples are transmitted in

multiplex operation. Depending on the application, the

CIP 3250A provides the following different output formats of the YUV signals (selectable via I

– 4:1:1 orthogonal output format for DIGIT 3000 applica-

tions

– 4:2:2 orthogonal output format for DIGIT 3000 applica-

tions

– 4:1:1 output format for standard DIGIT 2000 applica-

tions

– 4:2:2 output format for DIGIT 2000 applications

Refer to I

output format. Additionally , the CIP 3250A provides conversion of ITURY (luma) to DIGIT 2000 Y (luma) output

black levels, selectable via I

A programmable two-dimensional active video signal

(A VO) allows the write control of external video memory

directly. The characteristic of the YUV output is selectable between open-drain or push-pull.

2

C registers <15> to <16> to select the desired

2

C register <16>ADD16Q.

2

C-Bus):

Table 2–3: Digital output selection

<15>

YUVO

1 1 0 0 0 DIGIT 2000 4:1:1

1 1 1 0 0 orthogonal 4:1:1

1 0 0 1 1 DIGIT 2000 4:2:2

1 0 1 0 0 DIGIT 3000 4:2:2

0 0 0 0 0 4:4:4

<15>

MOD411ON

<15>

IND

<15>

UVSW

<15>

DTI

Digital

Output Format

13Micronas

CIP 3250A

ADV ANCE INFORMATION

2.12.1. DIGIT 2000 4:1:1 Output Format

The DIGIT 2000 4:1:1 output format is shown in Tables

2–4 and 2–5. A control signal for the chroma multiplex

is transmitted during the vertical blanking interval (see

Section 2.9.1.).

Table 2–4: Bit map of DIGIT 2000 4:1:1 format

Luma

Y

1

Y

2

Y

3

Y

4

Chroma

C

, C

3

C

, C

2

C1 , C

C

, C

0

Note: U

3

7

6

5

4

Y

x

V

2

2

V

2

1

V

2

0

V

2

x = pixel number and y = bit number

7

V

2

6

V

2

5

V

2

4

V

2

3

U

1

2

U

1

1

U

1

0

U

1

7

U

1

6

U

1

5

U

1

4

U

1

Table 2–5: Sampling raster of DIGIT 2000 4:1:1 format

Luma

Y

1

Y

2

Y

3

Y

4

Y

5

Chroma

Table 2–6: DIGIT 2000 4:2:2 output format

Luma

Y

1

Y

2

Y

3

Y

4

Chroma

C

7

C

6

C

5

C

4

C

3

C

2

C

1

C

0

Note: U

7

V

2

6

V

2

5

V

2

4

V

2

3

V

2

2

V

2

1

V

2

0

V

2

Y

x = pixel number and y = bit number

x

7

U

1

6

U

1

5

U

1

4

U

1

3

U

1

2

U

1

1

U

1

0

U

1

7

V

4

6

V

4

5

V

4

4

V

4

3

V

4

2

V

4

1

V

4

0

V

4

7

U

3

6

U

3

5

U

3

4

U

3

3

U

3

2

U

3

1

U

3

0

U

3

2.12.3. DIGIT 3000 Orthogonal 4:2:2 Output Format

The DIGIT 3000 orthogonal 4:2:2 output format is compatible to the industry standard. The U and V samples

are skew corrected and interpolated to an orthogonal

sampling raster, e.g. every line starts with the current U

pixel (see Table 2–7).

line 1

line 2

line 3

line 4

line 5

V

2L

U

XM

U

XL

V

1M

V

2L

V

2M

V

3L

U

XM

U

XL

V

2M

U

1L

V

3M

V

4L

U

XM

U

1L

U

1M

U

2L

V

4M

V

5L

U

1M

V

6L

U

2M

U

3L

V

5M

V

6L

Note: Uxy x = pixel number and y = LSB/MSB nibble

pixel no. X indicates an invalid sample at the

beginning of the line

2.12.2. DIGIT 2000 4:2:2 Output Format

In the DIGIT 2000 4:2:2 output format, the U and V samples are non-orthogonal (calculated from adjacent pixel,

e.g. line n starts with a V pixel and line (n+1) starts with

a U pixel (see Table 2–6).

Table 2–7: Orthogonal 4:2:2 output format

Luma

Y

1

Y

2

Y

3

Chroma

C

7

C

6

C

5

C

4

C

3

C

2

C

1

C

0

Note: U

7

U

1

6

U

1

5

U

1

4

U

1

3

U

1

2

U

1

1

U

1

0

U

1

Y

x = pixel number and y = bit number

x

7

V

1

6

V

1

5

V

1

4

V

1

3

V

1

2

V

1

1

V

1

0

V

1

7

U

3

6

U

3

5

U

3

4

U

3

3

U

3

2

U

3

1

U

3

0

U

3

Y

4

7

V

3

6

V

3

5

V

3

4

V

3

3

V

3

2

V

3

1

V

3

0

V

3

14 Micronas

Loading...

Loading...