Micronas VPX3225D, VPX3224D Datasheet

VPX 3225D,

VPX 3224D

Video Pixel Decoders

Edition Nov. 9, 1998

6251-432-2PD

PRELIMINARY DATA SHEET

MICRONAS

MICRONAS

VPX 3225D, VPX 3224D

Contents

Page Section Title

6 1. Introduction

7 1.1. System Architecture

8 2. Functional Description

8 2.1. Analog Front-End

8 2.1.1. Input Selector

8 2.1.2. Clamping

8 2.1.3. Automatic Gain Control

8 2.1.4. Analog-to-Digital Converters

8 2.1.5. ADC Range

8 2.1.6. Digitally Controlled Clock Oscillator

10 2.2. Color Decoder

10 2.2.1. IF-Compensation

10 2.2.2. Demodulator

11 2.2.3. Chrominance Filter

11 2.2.4. Frequency Demodulator

1 1 2.2.5. Burst Detection

11 2.2.6. Color Killer Operation

11 2.2.7. PAL Compensation/1-H Comb Filter

12 2.2.8. Luminance Notch Filter

13 2.3. Video Sync Processing

13 2.4. Macrovision Detection (version D4 only)

14 2.5. Component Processing

15 2.5.1. Horizontal Resizer

16 2.5.2. Skew Correction

16 2.5.3. Peaking and Coring

16 2.5.4. YCbCr Color Space

16 2.5.5. Video Adjustments

17 2.6. Video Output Interface

17 2.6.1. Output Formats

17 2.6.1.1. YUV 4:2:2 with Separate Syncs/ITU-R601

18 2.6.1.2. Embedded Reference Headers/ITU-R656

20 2.6.1.3. Embedded Timing Codes (BStream)

20 2.6.2. Bus Shuffler

20 2.6.3. Output Multiplexer

20 2.6.4. Output Ports

21 2.7. Video Data Transfer

21 2.7.1. Single and Double Clock Mode

22 2.7.2. Half Clock Mode

23 2.8. Video Reference Signals

23 2.8.1. HREF

23 2.8.2. VREF

23 2.8.3. Odd/Even Information (FIELD)

25 2.8.4. VACT

PRELIMINARY DATA SHEET

2 Micronas

PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

26 2.9. Operational Modes

26 2.9.1. Open Mode

26 2.9.2. Scan Mode

28 2.10. Windowing the Video Field

29 2.11. Temporal Decimation

30 2.12. Data Slicer

30 2.12.1. Slicer Features

30 2.12.2. Data Broadcast Systems

31 2.12.3. Slicer Functions

31 2.12.3.1. Input

31 2.12.3.2. Automatic Adaptation

31 2.12.3.3. Standard Selection

31 2.12.3.4. Output

33 2.13. VBI Data Acquisition

33 2.13.1. Raw VBI Data

34 2.13.2. Sliced VBI Data

35 2.14. Control Interface

35 2.14.1. Overview

35 2.14.2. I

35 2.14.3. Reset and I

35 2.14.4. Protocol Description

36 2.14.5. FP Control and Status Registers

37 2.15. Initialization of the VPX

37 2.15.1. Power-on-Reset

37 2.15.2. Software Reset

37 2.15.3. Low Power Mode

38 2.16. JTAG Boundary-Scan, Test Access Port (TAP)

38 2.16.1. General Description

38 2.16.2. T AP Architecture

38 2.16.2.1. T AP Controller

38 2.16.2.2. Instruction Register

38 2.16.2.3. Boundary Scan Register

39 2.16.2.4. Bypass Register

39 2.16.2.5. Device Identification Register

39 2.16.2.6. Master Mode Data Register

39 2.16.3. Exception to IEEE 1149.1

39 2.16.4. IEEE 1 149.1–1990 Spec Adherence

39 2.16.4.1. Instruction Register

39 2.16.4.2. Public Instructions

40 2.16.4.3. Self-Test Operation

40 2.16.4.4. Test Data Registers

40 2.16.4.5. Boundary-Scan Register

40 2.16.4.6. Device Identification Register

40 2.16.4.7. Performance

44 2.17. Enable/Disable of Output Signals

2

C-Bus Interface

2

C Device Address Selection

VPX 3225D, VPX 3224D

3Micronas

VPX 3225D, VPX 3224D

Contents, continued

Page Section Title

45 3. Specifications

45 3.1. Outline Dimensions

48 3.2. Pin Connections and Short Descriptions

45 3.3. Pin Descriptions

47 3.4. Pin Configuration

48 3.5. Pin Circuits

50 4. Electrical Characteristics

50 4.1. Absolute Maximum Ratings

51 4.2. Recommended Operating Conditions

51 4.2.1. Recommended Analog Video Input Conditions

52 4.2.2. Recommended I

52 4.2.3. Recommended Digital Inputs Levels of RES, OE, TCK, TMS, TDI

53 4.2.4. Recommended Crystal Characteristics

54 4.3. Characteristics

54 4.3.1. Current Consumption

54 4.3.2. Characteristics, Reset

54 4.3.3. XTAL Input Characteristics

55 4.3.4. Characteristics, Analog Front-End and ADCs

56 4.3.5. Characteristics, Control Bus Interface

56 4.3.6. Characteristics, JTAG Interface (Test Access Port TAP)

57 4.3.7. Characteristics, Digital Inputs/Outputs

57 4.3.8. Clock Signals PIXCLK, LLC, and LLC2

58 4.3.9. Digital Video Interface

58 4.3.10. Characteristics, TTL Output Driver

59 4.3.10.1. TTL Output Driver Description

2

C Conditions

PRELIMINARY DATA SHEET

60 5. Timing Diagrams

60 5.1. Power-up Sequence

60 5.2. Default Wake-up Selection

61 5.3. Control Bus Timing Diagram

62 5.4. Output Enable by Pin OE

63 5.5. Timing of the Test Access Port TAP

63 5.6. Timing of all Pins connected to the Boundary-Scan-Register-Chain

64 5.7. Timing Diagram of the Digital Video Interface

64 5.7.1. Characteristics, Clock Signals

65 6. Control and Status Registers

65 6.1. Overview

68 6.1.1. Description of I

72 6.1.2. Description of FP Control and Status Registers

2

C Control and Status Registers

4 Micronas

PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

83 7. Application Notes

83 7.1. Differences between VPX 3220A and VPX 322xD

83 7.2. Impact to Signal to Noise Ratio

83 7.3. Control Interface

83 7.3.1. Symbols

2

83 7.3.2. Write Data into I

83 7.3.3. Read Data from I

83 7.3.4. Write Data into FP Register

83 7.3.5. Read Data from FP Register

84 7.3.6. Sample Control Code

84 7.4. Xtal Supplier

85 7.5. Typical Application

88 8. Data Sheet History

C Register

2

C Register

VPX 3225D, VPX 3224D

5Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

Video Pixel Decoder

Release Note: This data sheet describes functions

and characteristics of VPX 322xD–C3 and D4. Revision bars indicate significant changes to the previous edition.

1. Introduction

The Video Pixel Decoders VPX 3225D and VPX 3224D

are the second generation of full feature video acquisition ICs for consumer video and multimedia applications. All of the processing necessary to convert an analog video signal into a digital component stream have

been integrated onto a single 44-pin IC. Moreover, the

VPX 3225D provides text slicing for intercast, teletext,

and closed caption. Both chips are pin compatible to

VPX 3220A, VPX 3216B, and VPX 3214C. Notable features include:

Video Decoding

– multistandard color decoding:

• NTSC-M, NTSC-443

• P AL-BGHI, PAL-M, PAL-N, PAL-60

• SECAM

• S-VHS

– NTSC with Y/C comb filter

– two 8-bit video A/D converters with clamping and auto-

matic gain control (AGC)

– four analog inputs with integrated selector for:

• 3 composite video sources (CVBS), or

• 2 Y/C sources (S-VHS), or

• 2 composite video sources and one Y/C source.

– horizontal and vertical sync detection for all standards

– decodes and detects Macrovision 7.1 protected video

(version D4 only)

Video Processing

– hue, brightness, contrast, and saturation control

Video Interfacing

– YC

– ITU-R 601 compliant output format

– ITU-R 656 compliant output format

– BStream compliant output format

– square pixel format (640 or 768 pixel/line)

– 8-bit or 16-bit synchronous output mode

– 13.5 MHz/16-bit and 27 MHz/8-bit output rate

– VBI bypass and raw ADC data output

Data Broadcast Support (VPX 3225D only)

– high-performance data slicing in hardware

– multistandard data slicer

– full support for

– programmable to new standards via I2C

– automatic slice level adaptation

– VBI and Full-Field mode

– data insertion into video stream

– simultaneous acquisition of teletext, VPS, WSS, and

Miscellaneous

– 44-pin PLCC package

– total power consumption of below 1 W

– I

– single on-chip clock generation, only one crystal need-

– user programmable output pins

– power-down mode

4:2:2 format

bCr

• NABTS, WST

• CAPTION (1x,2x), VPS, WSS, Antiope

• teletext, intercast, wavetop,

• WebTV for windows, EPG services

caption

2

C serial control, 2 different device addresses

ed for all standards

– dual window cropping and scaling

– horizontal resizing between 32 and 864 pixels/line

– vertical resizing by line dropping

– high-quality anti-aliasing filter

– scaling controlled peaking and coring

6 Micronas

– IEEE 1149.1 (JTAG) boundary scan interface

Software Support

– MediaCVR Software Suite

• Video for Windows driver

• TV viewer applet, teletext browser

• intercast/wavetop browser

– WebTV for Windows

• Video capture and VBI services

PRELIMINARY DATA SHEET

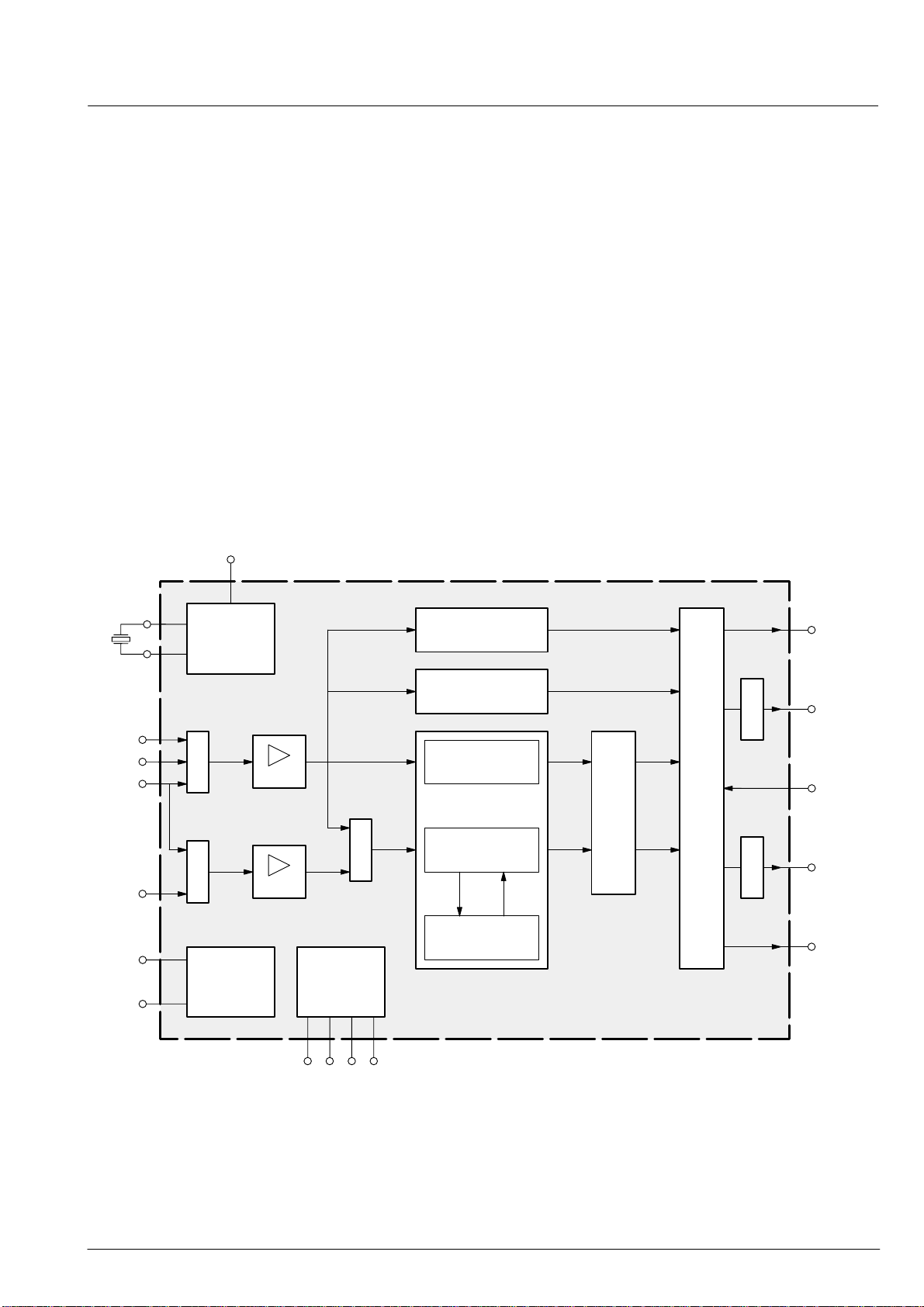

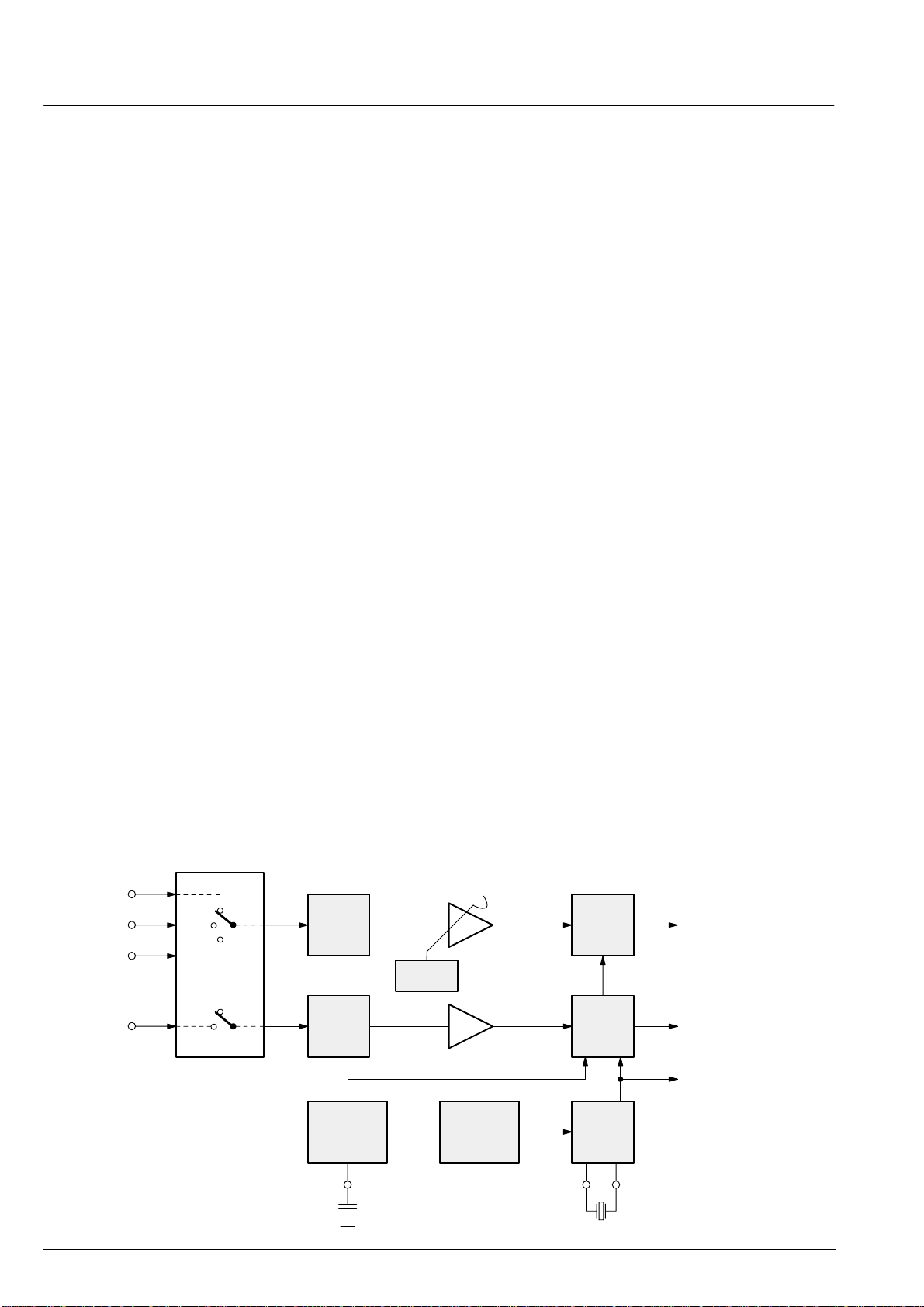

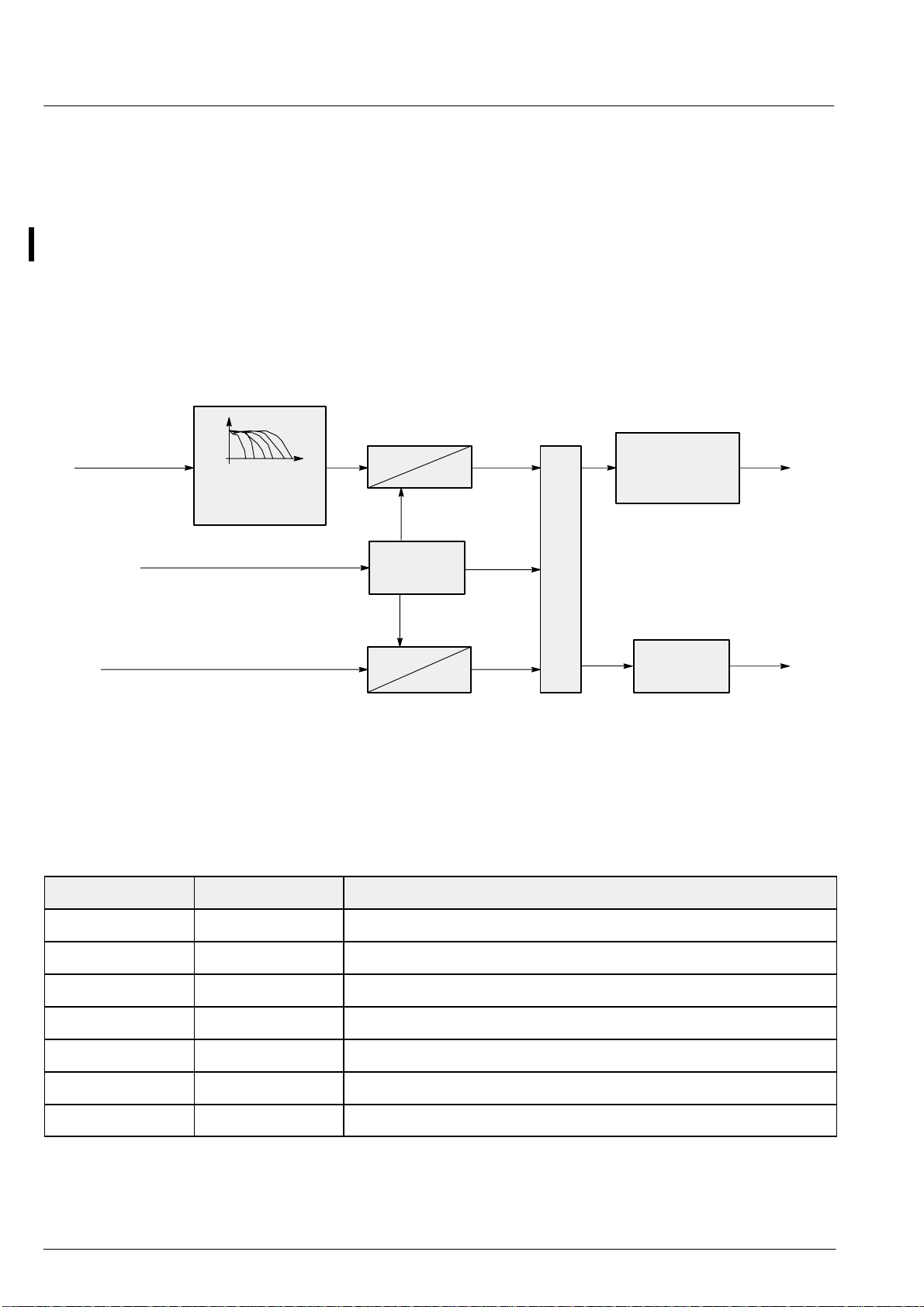

1.1. System Architecture

The block diagram (Fig. 1–1) illustrates the signal flow

through the VPX. A sampling stage performs 8-bit A/D

conversion, clamping, and AGC. The color decoder separates the luma and chroma signals, demodulates the

chroma, and filters the luminance. A sync slicer detects

the sync edge and computes the skew relative to the

sample clock. The video processing stage resizes the

YCbCr samples, adjusts the contrast and brightness,

and interpolates the chroma. The text slicer extracts

lines with text information and delivers decoded data

bytes to the video interface.

Note: The VPX 3225D and VPX 3224D are not register

compatible with the VPX 3220A, VPX 3216B, and

VPX 3214C family.

VPX 3225D, VPX 3224D

CVBS/Y

Chroma

SDA

SCL

RESQ

Clock Gen.

DCO

MUX

MUX

ADC

ADC

I2C JTAG

MUX

Sync Processing

Text Slicer

(VPX 3225D only)

Luma Filter

Video Decoder

Chroma

Demodulator

Line Store

YY

C

bCr

CbC

Video Processing

Video Interface

r

PortPort

HREF

VREF

FIELD

A[7:0]

OEQ

B[7:0]

PIXCLK

LLC

VACT

TDI

TMS

TDO

TCK

Fig. 1–1: Block diagram of the VPX 3224D, VPX 3225D

7Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

2. Functional Description

The following sections provide an overview of the different functional blocks within the VPX. Most of them are

controlled by the Fast Processor (‘FP’) embedded in the

decoder. For controlling, there are two classes of regis-

2

ters: I

C registers (directly addressable via I2C bus) and

FP-RAM registers (ram memory of the FP; indirectly addressable via I

2

C bus). For further information, see sec-

tion 2.14.1.

2.1. Analog Front-End

This block provides the analog interfaces to all video inputs and mainly carries out analog-to-digital conversion

for the following digital video processing. A block diagram is given in Fig. 2–1.

Clamping, AGC, and clock DCO are digitally controlled.

The control loops are closed by the embedded processor.

2.1.1. Input Selector

Up to four analog inputs can be connected. Three inputs

(VIN1–3) are for input of composite video or S-VHS luma

signal. These inputs are clamped to the sync back porch

and are amplified by a variable gain amplifier. Two inputs, one dedicated (CIN) and one shared (VIN1), are

for connection of S-VHS carrier-chrominance signal.

The chrominance input is internally biased and has a

fixed gain amplifier.

pacitors and is generated by digitally controlled current

sources. The clamping level is the back porch of the video signal. S-VHS chroma is AC coupled. The input pin

is internally biased to the center of the ADC input range.

2.1.3. Automatic Gain Control

A digitally working automatic gain control adjusts the

magnitude of the selected baseband by +6/–4.5 dB in 64

logarithmic steps to the optimal range of the ADC. The

gain of the video input stage including the ADC is 213

steps/V with the AGC set to 0 dB.

2.1.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals.

Each converter runs with 20.25 MHz and has 8-bit resolution. An integrated bandgap circuit generates the required reference voltages for the converters. The two

ADCs are of a 2-stage subranging type.

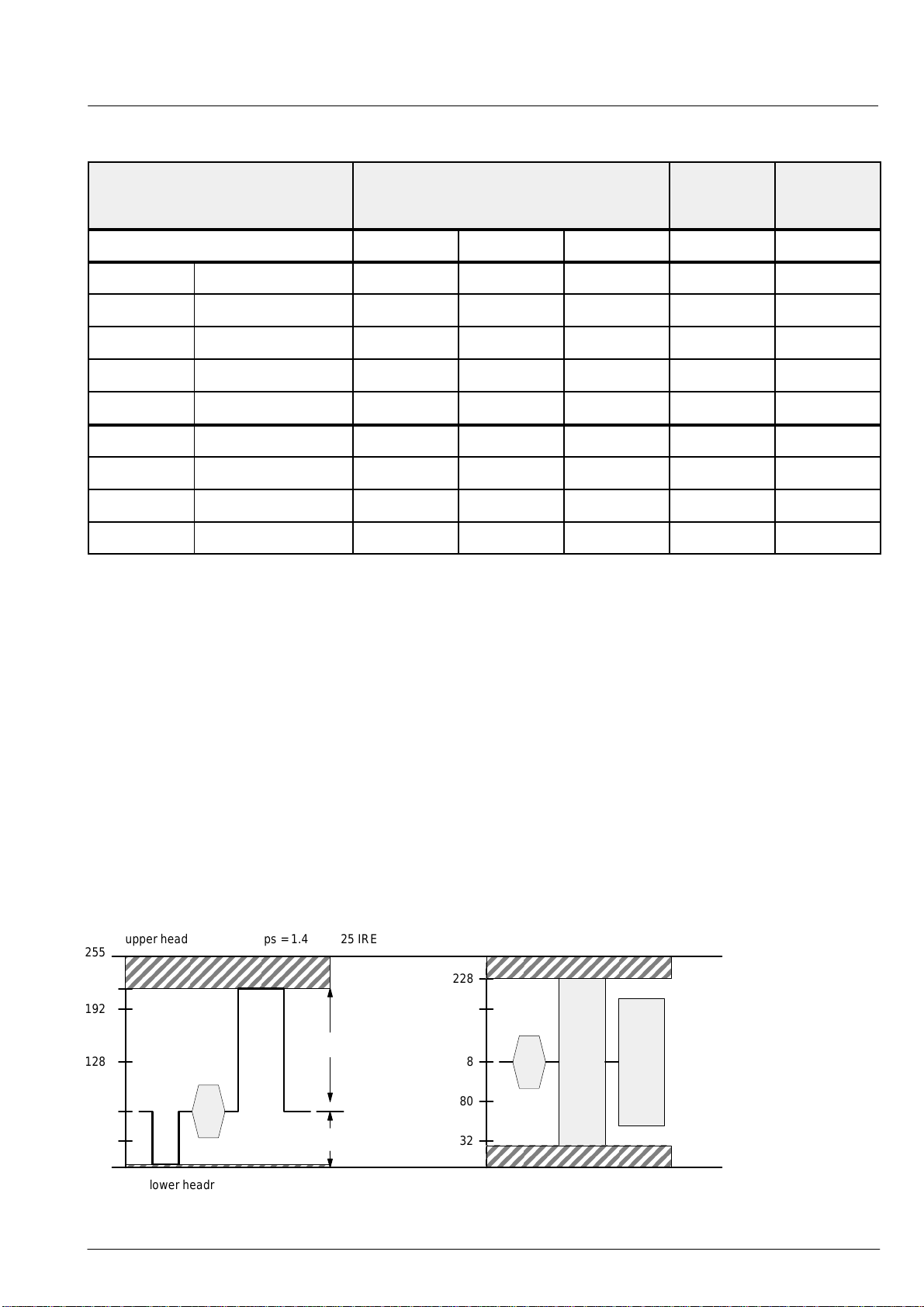

2.1.5. ADC Range

The ADC input range for the various input signals and

the digital representation is given in Table 2–1 and Fig.

2–2. The corresponding output signal levels of the

VPX 32xx are also shown.

2.1.6. Digitally Controlled Clock Oscillator

2.1.2. Clamping

The composite video input signals are AC coupled to the

IC. The clamping voltage is stored on the coupling ca-

CVBS/Y

CVBS/Y

CVBS/Y/C

Chroma

VIN3

VIN2

clamp

VIN1

CIN

bias

input mux

reference

generation

AGC

+6/–4.5 dB

gain

The clock generation is also a part of the analog front

end. The crystal oscillator is controlled digitally by the

FP; the clock frequency can be adjusted within

±150 ppm.

digital CVBS or Luma

digital Chroma

system clocks

frequency

ADC

ADC

DCVO

±150

ppm

20.25 MHz

Fig. 2–1: Analog front-end

8 Micronas

PRELIMINARY DATA SHEET

VPX 3225D, VPX 3224D

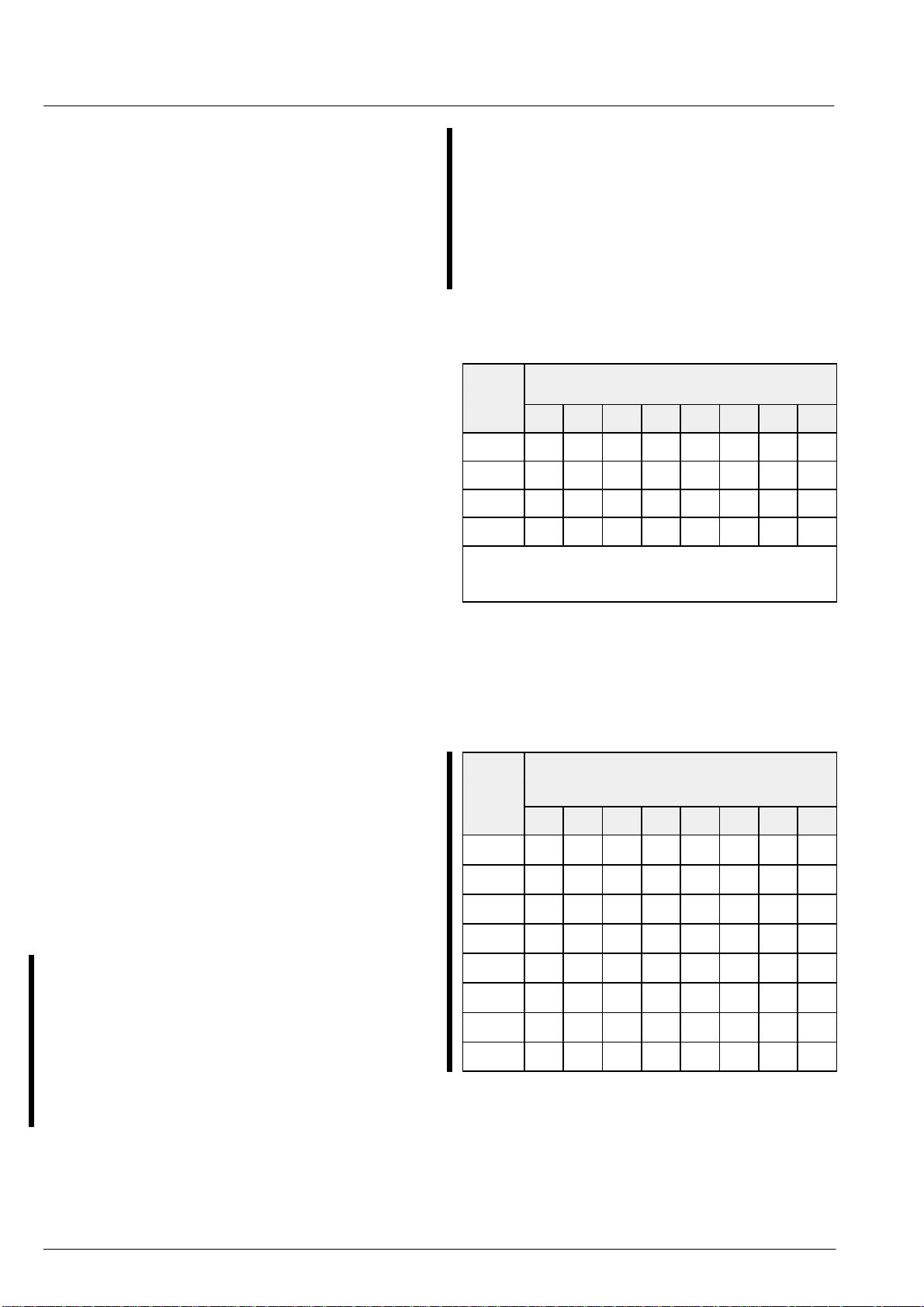

Table 2–1: ADC input range for PAL input signal and corresponding output signal ranges

Signal Input Level [mVpp] ADC

Range

–6 dB 0 dB +4.5 dB [steps] [steps]

CVBS 100% CVBS 667 1333 2238 252 –

75% CVBS 500 1000 1679 213 –

video (luma) 350 700 1175 149 224

sync height 150 300 504 64 –

clamp level 68 16

Chroma burst 300 64 –

100% Chroma 890 190 128$112

75% Chroma 670 143 128$84

bias level 128 128

YCrC

b

Output

Range

CVBS/Y Chroma

upper headroom = 38 steps = 1.4 dB = 25 IRE

255

217

192

128

68

32

0

lower headroom = 4 steps = 0.2 dB

white

black

= clamp

level

video = 100 IRE

sync = 41 IRE

headroom = 56 steps = 2.1 dB

228

192

128

80

32

burst

Fig. 2–2: ADC ranges for CVBS/Luma and Chroma, PAL input signal

100% Chroma

75% Chroma

9Micronas

VPX 3225D, VPX 3224D

–

–

–

PRELIMINARY DATA SHEET

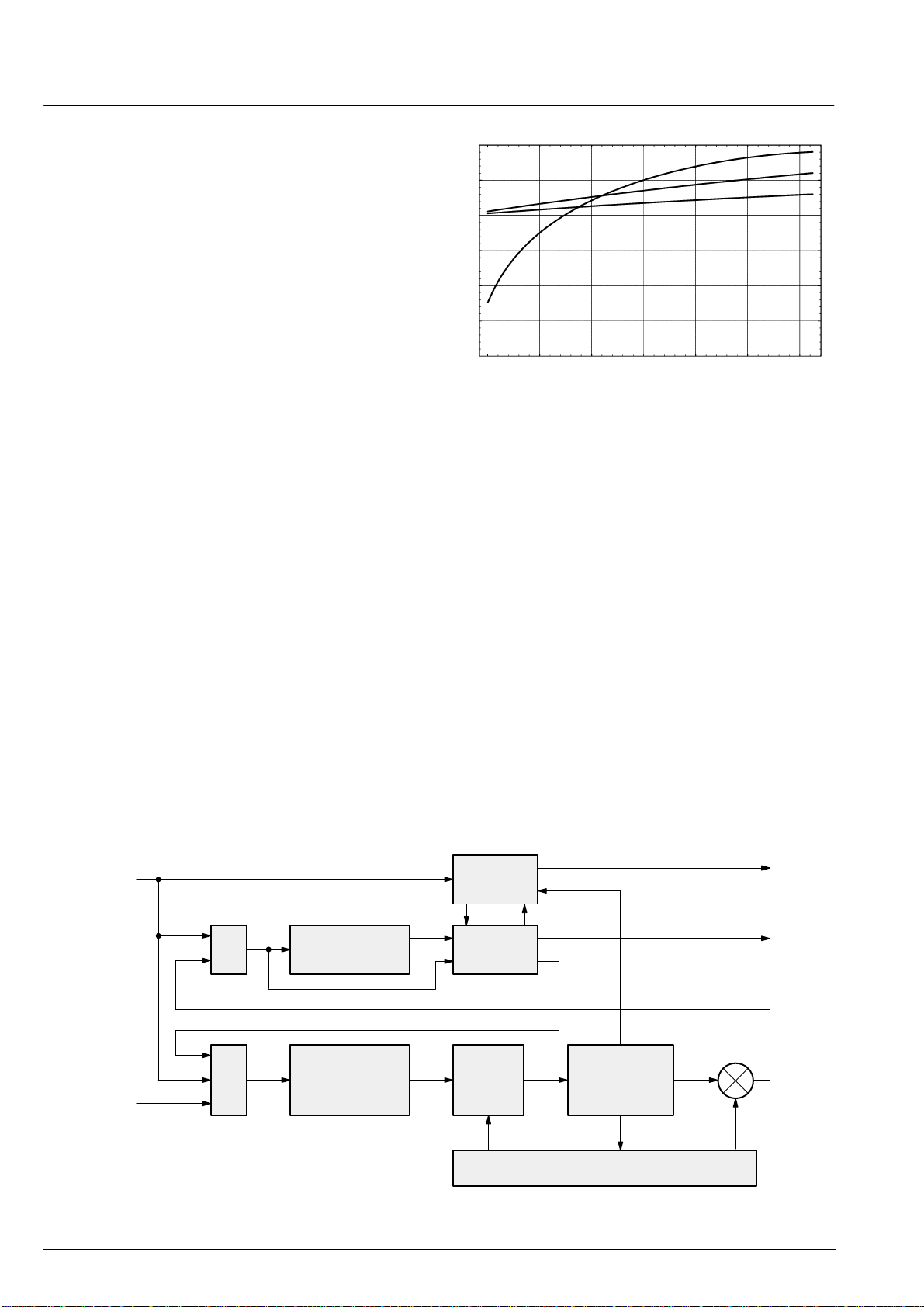

2.2. Color Decoder

In this block, the standard luma/chroma separation and

multi-standard color demodulation is carried out. The

color demodulation uses an asynchronous clock, thus

allowing a unified architecture for all color standards.

A block diagram of the color decoder is shown in Fig.

2–4. The luma, as well as the chroma processing, is

shown here. The color decoder also provides several

special modes; for example, wide band chroma format

which is intended for S-VHS wide bandwidth chroma.

The output of the color decoder is YC

in a 4:2:2 for-

rCb

mat.

2.2.1. IF-Compensation

With off-air or mistuned reception, any attenuation at

higher frequencies or asymmetry around the color subcarrier is compensated. Four different settings of the IFcompensation are possible:

– flat (no compensation)

– 6 dB/octave

– 12 dB/octave

– 10 dB/MHz

dB

10

5

0

–5

10

15

20

3.5 3.75 4 4.25 4.5 5

4.75

MHz

Fig. 2–3: Freq. response of chroma IF-compensation

2.2.2. Demodulator

The entire signal (which might still contain luma) is now

quadrature-mixed to the baseband. The mixing frequency is equal to the subcarrier for PAL and NTSC, thus

achieving the chroma demodulation. For SECAM, the

mixing frequency is 4.286 MHz giving the quadrature

baseband components of the FM modulated chroma.

After the mixer, a lowpass filter selects the chroma components; a downsampling stage converts the color difference signals to a multiplexed half rate data stream.

The last setting gives a very large boost to high frequencies. It is provided for SECAM signals that are decoded

using a SAW filter specified originally for the PAL standard.

Luma / CVBS

MUXMUX

Chroma

1 H Delay

IF Compensation

DC-Reject

The subcarrier frequency in the demodulator is generated by direct digital synthesis; therefore, substandards

such as PAL 3.58 or NTSC 4.43 can also be demodulated.

Notch

Filter

CrossSwitch

MIXER

ACC

Lowpass Filter

Phase/Freq.

Demodulator

Luma

Chroma

Fig. 2–4: Color decoder

Color-PLL/Color-ACC

10 Micronas

PRELIMINARY DATA SHEET

VPX 3225D, VPX 3224D

2.2.3. Chrominance Filter

The demodulation is followed by a lowpass filter for the

color difference signals for P AL/NTSC. SECAM requires

a modified lowpass function with bell-filter characteristic.

At the output of the lowpass filter, all luma information is

eliminated.

The lowpass filters are calculated in time multiplex for

the two color signals. Four bandwidth settings (narrow,

normal, broad, wide) are available for each standard.

The filter passband can be shaped with an extra peaking

term at 1.25 MHz. For P AL/NTSC, a wide band chroma

filter can be selected. This filter is intended for high

bandwidth chroma signals; for example, a nonstandard

wide bandwidth S-VHS signal.

dB

0

–10

–20

–30

–40

2.2.4. Frequency Demodulator

The frequency demodulator for demodulating the SECAM signal is implemented as a CORDIC-structure. It

calculates the phase and magnitude of the quadrature

components by coordinate rotation.

The phase output of the CORDIC processor is differentiated to obtain the demodulated frequency . After a programmable deemphasis filter, the Dr and Db signals are

scaled to standard C

amplitudes and fed to the cross-

rCb

over-switch.

2.2.5. Burst Detection

In the PAL/NTSC-system, the burst is the reference for

the color signal. The phase and magnitude outputs of

the CORDIC are gated with the color key and used for

controlling the phase-lock-loop (APC) of the demodulator and the automatic color control (ACC) in P AL/NTSC.

The ACC has a control range of +30...–6 dB.

For SECAM decoding, the frequency of the burst is measured. Thus, the current chroma carrier frequency can

be identified and is used to control the SECAM processing. The burst measurements also control the color killer operation; they can be used for automatic standard

detection as well.

–50

012345

PAL/NTSC

dB

0

–10

–20

–30

–40

–50

012345

SECAM

MHz

MHz

Fig. 2–5: Frequency response of chroma filters

2.2.6. Color Killer Operation

The color killer uses the burst-phase / burst-frequency

measurement to identify a PAL/NTSC or SECAM color

signal. For PAL/NTSC, the color is switched off (killed)

as long as the color subcarrier PLL is not locked. For SECAM, the killer is controlled by the toggle of the burst frequency. The burst amplitude measurement is used to

switch off the color if the burst amplitude is below a programmable threshold. Thus, color will be killed for very

noisy signals. The color amplitude killer has a programmable hysteresis.

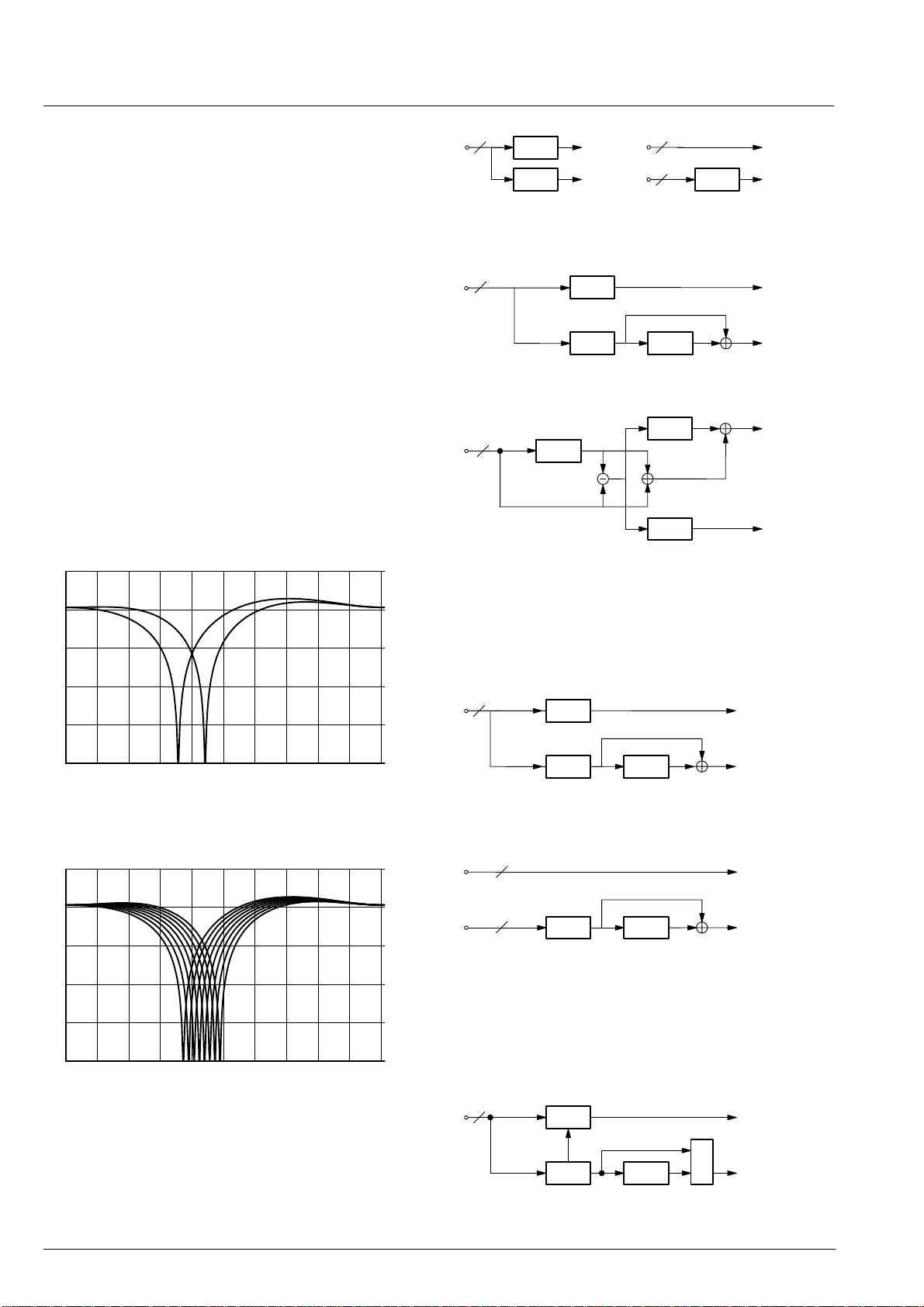

2.2.7. PAL Compensation/1-H Comb Filter

The color decoder uses one fully integrated delay line.

Only active video is stored.

The delay line application depends on the color standard:

– NTSC: 1-H comb filter or color compensation

– PAL: color compensation

– SECAM: crossover-switch

11Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

In the NTSC compensated mode, Fig. 2–7 c), the color

signal is averaged for two adjacent lines. Thus, crosscolor distortion and chroma noise is reduced. In the

NTSC combfilter mode, Fig. 2–7 d), the delay line is in

the composite signal path, thus allowing reduction of

cross-color components, as well as cross-luminance.

The loss of vertical resolution in the luminance channel

is compensated by adding the vertical detail signal with

removed color information.

2.2.8. Luminance Notch Filter

If a composite video signal is applied, the color information is suppressed by a programmable notch filter. The

position of the filter center frequency depends on the

subcarrier frequency for PAL/NTSC. For SECAM, the

notch is directly controlled by the chroma carrier frequency. This considerably reduces the cross-luminance. The frequency responses for all three systems

are shown in Fig. 2–6. In S-VHS mode, this filter is bypassed.

dB

10

CVBS

8

Notch

filter

Chroma

Process.

Y

C C

r b

Luma

8

Chroma

8

a) conventional b) S-VHS

CVBS

8

Notch

filter

Chroma

Process.

1 H

Delay

c) compensated

Notch

CVBS

8

1 H

Delay

filter

Chroma

Process.

d) comb filter

Chroma

Process.

Y

Y

CrC

Y

CrC

CrC

b

b

b

0

–10

–20

–30

–40

024 68 10

PAL/NTSC notch filter

dB

10

0

–10

–20

–30

MHz

Fig. 2–7: NTSC color decoding options

CVBS

8

Notch

filter

Chroma

Process.

1 H

Delay

a) conventional

Luma

8

Chroma

Chroma

8

Process.

1 H

Delay

b) S-VHS

Fig. 2–8: PAL color decoding options

Y

Y

CrC

CrC

b

b

–40

024 68 10

SECAM notch filter

Fig. 2–6: Frequency responses of the luma

notch filter for PAL, NTSC, SECAM

MHz

CVBS

8

Notch

filter

Chroma

Process.

1 H

Delay

MUX

Y

CrC

b

Fig. 2–9: SECAM color decoding

12 Micronas

PRELIMINARY DATA SHEET

VPX 3225D, VPX 3224D

2.3. Video Sync Processing

Fig. 2–10 shows a block diagram of the front-end sync

processing. To extract the sync information from the

video signal, a linear phase lowpass filter eliminates all

noise and video contents above 1 MHz. The sync is separated by a slicer; the sync phase is measured. The internal controller can select variable windows to improve

the noise immunity of the slicer. The phase comparator

measures the falling edge of sync, as well as the integrated sync pulse.

The sync phase error is filtered by a phase-locked loop

that is computed by the FP. All timing in the front-end is

derived from a counter that is part of this PLL, and it thus

counts synchronously to the video signal.

A separate hardware block measures the signal back

porch and also allows gathering the maximum/minimum

of the video signal. This information is processed by the

FP and used for gain control and clamping.

For vertical sync separation, the sliced video signal is integrated. The FP uses the integrator value to derive vertical sync and field information.

2.4. Macrovision Detection (version D4 only)

Video signals from Macrovision encoded VCR tapes are

decoded without loss of picture quality . However, it might

be necessary in some applications to detect the presence of Macrovision encoded video signals. This is possible by reading a set of I2C registers (FP-RAM

0x170–0x179) in the video front-end.

Macrovision encoded video signals typically have AGC

pulses and pseudo sync pulses added during VBI. The

amplitude of the AGC pulses is modulated in time. The

Macrovision detection logic measures the VBI lines and

compares the signal against programmable thresholds.

The window in which the video lines are checked for Macrovision pulses can be defined in terms of start and stop

line (e.g. 6–15 for NTSC).

Frequency and phase characteristics of the analog video signal are derived from PLL1. The results are fed to

the rest of the video processing system in the backend.

The resizer unit uses them for data interpolation and

orthogonalization. A separate timing block derives the

timing reference signals HREF and VREF from the horizontal sync.

video

input

lowpass

1 MHz &

sync

slicer

horizontal

sync

separation

phase

comparator

& lowpass

counter

PLL1

front

sync

generator

front sync

skew

vblank

field

clamp &

signal

measurement

Fig. 2–10: Sync separation block diagram

clamping

front-end

timing

color key FIFO_write

clock

synthesizer

syncs

clock

H/V syncs

13Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

2.5. Component Processing

Recovery of the YCbCr components by the decoder is

followed by horizontal resizing and skew compensation.

Contrast enhancement with noise shaping can also be

applied to the luminance signal. Vertical resizing is supported via line dropping.

Fig. 2–11 illustrates the signal flow through the component processing stage. The YCbCr 4:2:2 samples are

separated into a luminance path and a chrominance

Y

in

Active Video

Reference

Luma Filter

with peaking

& coring

Resize

Sequence

Control

path. The Luma Filtering block applies anti-aliasing lowpass filters with cutoff frequencies adapted to the number of samples after scaling, as well as peaking and coring. The Resize and Skew blocks alter the effective

sampling rate and compensate for horizontal line skew.

The YCbCr samples are buffered in a FIFO for continuous burst at a fixed clock rate. For luminance samples,

the contrast and brightness can be adjusted and noise

shaping applied. In the chrominance path, Cb and Cr

samples can be swapped. Without swapping, the first

valid video sample is a Cb sample. Chrominance gain

can be adjusted in the color decoder.

Contrast,

Skew

Luma

Phase Shift

Latch

F

I

F

O

Brightness &

Noise shaping

Y

out

CbCr

Chroma

Phase Shift

in

Resize

Skew

16 bit

Cb/Cr-

swapping

Fig. 2–11: Component processing stage

Table 2–2: Several rasters supported by the resizer

NTSC PAL/SECAM Format Name

640 x 480 768 x 576 Square pixels for broadcast TV (4:3)

704 x 480 704 x 576 Input Raster for MPEG-2

320 x 240 384 x 288 Square pixels for TV (quarter resolution)

352 x 240 352 x 288 CIF – Input raster for MPEG-1, H.261

160 x 120 192 x 144 Square pixels for TV (1/16 resolution), H.324, H.323

Cr

out

176 x 120 176 x 144 QCIF – Input raster for H.261

32 x 24 32 x 24 Video icons for graphical interfaces (square)

14 Micronas

VPX 3225D, VPX 3224DPRELIMINARY DATA SHEET

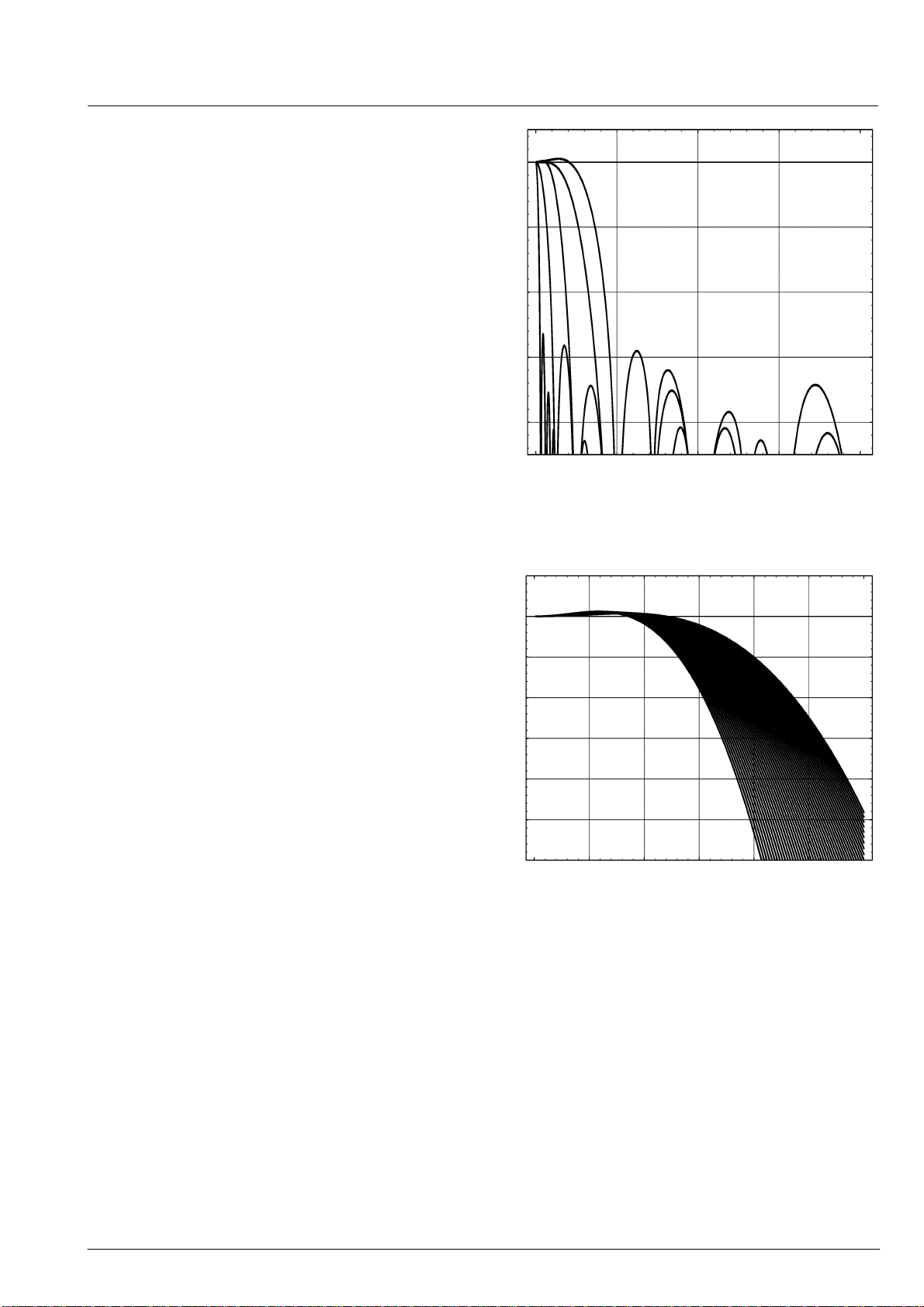

2.5.1. Horizontal Resizer

The operating range of the horizontal resizer was chosen to serve the widest possible range of applications

and source formats (number of lines, aspect ratio, etc...).

T able 2–2 lists several examples for video sourced from

525/625 line TV systems.

The horizontal resizer alters the sampling raster of the

video signal, thereby varying the number of pixels (NPix)

in the active portion of the video line. The number of pixels per line is selectable within a range from 32 to 864

in increments of 2 pixels (see section 2.10.: Windowing

the Video Field). T able 2–2 gives an overview of several

supported video rasters. The visual quality of a sampling

rate conversion operation depends on two factors:

– the frequency response of the individual filters, and

– the number of available filters from which to choose.

The VPX is equipped with a battery of FIR filters to cover

the five octave operating range of the resizer. Fig. 2–12

shows the magnitude response of five example filters

corresponding to 1054, 526, 262, 130, and 32 pixels.

The density of the filter array can be seen in Fig. 2–13.

The magnitude response of 50 filters lying next to each

other are shown. Nevertheless, these are only 10% of all

filters shown. As a whole, the VPX comes with a battery

of 512 FIR filters. Showing these 512 Filters in Fig. 2–12

would result in a large black area. This dense array of filters is necessary in order to maintain constant visual

quality over the range of allowable picture sizes. The alternative would be to use a small number of filters whose

cutoff frequencies are regularly spaced over the spectrum. However, it has been found that using few filters

leads to visually annoying threshold behavior. These effects occur when the filters are changed in response to

variations in the picture size.

dB

0

10

20

30

40

010203040

MHz

Fig. 2–12: Freq. response of 5 widely spaced filters

dB

0

–2

–4

–6

–8

10

Filter selection is performed automatically by the internal

processor based on the selected resizing factor (NPix).

This automated selection is optimized for best visual

performance.

12

0 0.5 1.5 2 3

1 2.5

Fig. 2–13: Freq. response of 50 neighbored filters

MHz

15Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

2.5.2. Skew Correction

The VPX delivers orthogonal pixels with a fixed clock

even in the case of non-broadcast signals with substantial horizontal jitter (VCRs, laser disks, certain portions

of the 6 o’clock news...).

This is achieved by highly accurate sync slicing combined with post correction. Immediately after the analog

input is sampled, a horizontal sync slicer tracks the position of sync. This slicer evaluates, to within 1.6 ns, the

skew between the sync edge and the edge of the pixelclock. This value is passed as a skew on to the phase

shift filter in the resizer. The skew is then treated as a

fixed initial offset during the resizing operation.

The skew block in the resizer performs programmable

phase shifting with subpixel accuracy . In the luminance

path, a linear interpolation filter provides a phase shift

between 0 and 31/32 in steps of 1/32. This corresponds

to an accuracy of 1.6 ns. The chrominance signal can be

shifted between 0 and 7/8 in steps of 1/8.

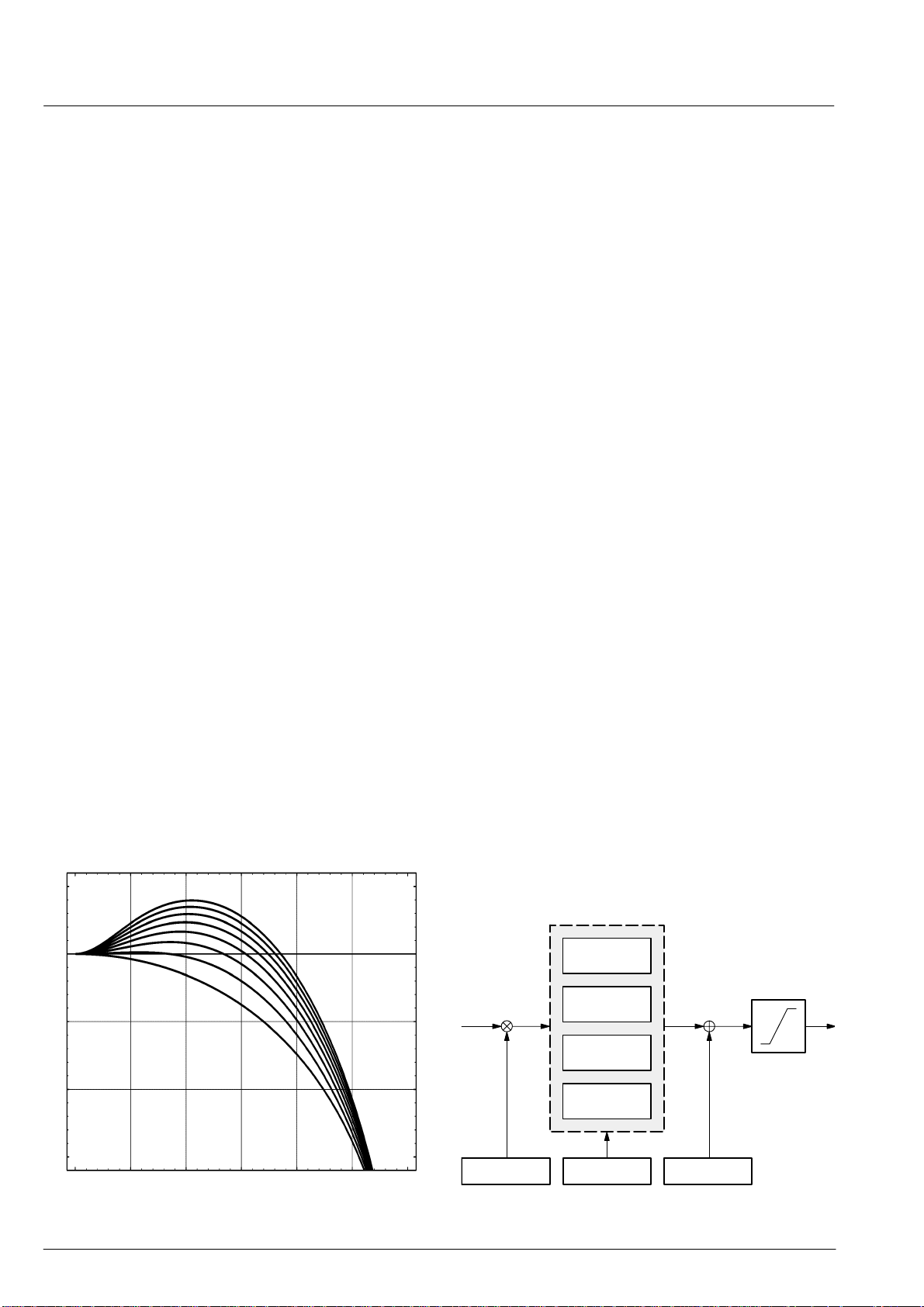

2.5.3. Peaking and Coring

The horizontal resizer comes with an extra peaking filter

for sharpness control. The center frequency of the peaking filter is automatically adjusted to the image size in

512 steps. The peaking value to each center frequency

can be controlled by the user with up to eight steps via

FP-RAM 0x126/130. Fig. 2–14 shows the magnitude response of the eight steps of the peaking filter corresponding to an image size of 320 pixels.

2.5.4. YCbCr Color Space

The color decoder outputs luminance and one multiplexed chrominance signal at a sample clock of

20.25 MHz. Active video samples are flagged by a separate reference signal. Internally, the number of active

samples is 1080 for all standards (525 lines and 625

lines). The representation of the chroma signals is the

ITU-R 601 digital studio standard.

In the color decoder, the weighting for both color difference signals is adjusted individually . The default format

has the following specification:

– Y = 224*Y + 16 (pure binary),

– C

= 224*(0.713*(R–Y)) + 128 (offset binary),

r

– C

= 224*(0.564*(B–Y)) + 128 (offset binary).

b

2.5.5. Video Adjustments

The VPX provides a selectable gain (contrast) and offset

(brightness) for the luminance samples, as well as additional noise shaping. Both the contrast and brightness

factors can be set externally via I

2

C serial control of FPRAM 0x127,128,131, and 132. Fig. 2–15 gives a functional description of this circuit. First, a gain is applied,

yielding a 10-bit luminance value. The conversion back

to 8-bit is done using one of four selectable techniques:

simple rounding, truncation,1-bit error diffusion, or 2-bit

error diffusion. Bit[8] in the ‘contrast’-register selects between the clamping levels 16 and 32.

After the peaking filter, an additional coring filter is implemented to the horizontal resizer. The coring filter subtracts 0, 1/2, 1, or 2 LSBs of the higher frequency part of

the signal. Note, that coring can be performed independently of the peaking value adjustment.

dB

10

0

–10

–20

–30

01 34 6

25

MHz

Fig. 2–14: Frequency response of peaking filter

I

= c * I

out

+ b c = 0...63/32 in 64 steps

in

b = –127...128 in 256 steps

In the chrominance path, Cb and Cr samples can be

swapped with bit[8] in FP-RAM 0x126 or 130. Adjustment of color saturation and gain is provided via FPRAM 0x30–33 (see section 2.2.5.).

Rounding

Truncation

1 bit

Err. Diff.

2 bit

Err. Diff.

Contrast Select Brightness

FP-RAM

Registers

Fig. 2–15: Contrast and brightness adjustment

16 Micronas

VPX 3225D, VPX 3224DPRELIMINARY DATA SHEET

2.6. Video Output Interface

Contrary to the component processing stage running at

a clock rate of 20.25 MHz, the output formatting stage

(Fig. 2–16) receives the video samples at a pixel transport rate of 13.5 MHz. It supports 8 or 16-bit video formats with separate or embedded reference signals, provides bus shuffling, and channels the output via one or

both 8-bit ports. Data transfer is synchronous to the internally generated 13.5 MHz pixel clock.

The format of the output data depends on three parameters:

– the selected output format

S YUV 4:2:2, separate syncs

S YUV 4:2:2, ITU-R656

S YUV 4:2:2, embedded reference codes (BStream)

– the number of active ports (A only, or both A and B)

– clock speed (single, double, half).

In 8-bit modes using only Port A for video data, Port B

can be used as programmable output.

2.6.1. Output Formats

The VPX supports the YUV 4:2:2 video format only . During normal operation, all reference signals are output

separately. To provide a reduced video interface, the

VPX offers two possibilities for encoding timing references into the video data stream: an ITU-R656 compliant output format with embedded timing reference

headers and a second format with single timing control

codes in the video stream. The active output format can

be selected via FP-RAM 0x150 [format].

2.6.1.1. YUV 4:2:2 with Separate Syncs/ITU-R601

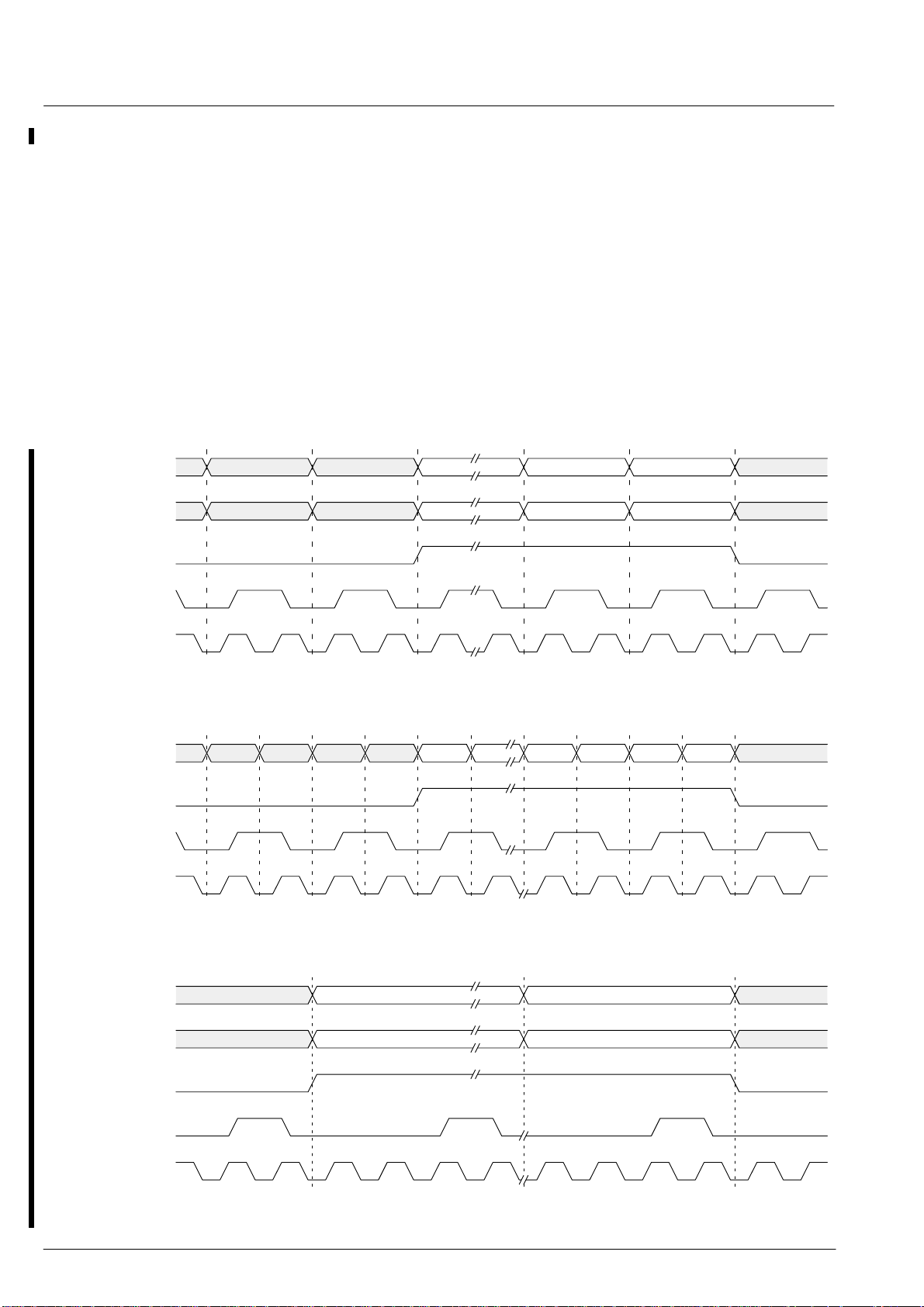

The default output format of the VPX is a synchronous

16-bit YUV 4:2:2 data stream with separate reference

signals. Port A is used for luminance and Port B for chrominance-information. Video data is compliant to ITUR601. Bit[1:0] of FP-RAM 0x150 has to be set to 00. Figure 2–17 shows the timing of the data ports and the

reference signals in this mode.

Video

Samples

Reference

Signals

16 8

Output Formats

Fig. 2–16: Output format stage

Luminance

(Port A)

Chrominance

(Port B)

VACT

8

8

Bus Shuffler

8

Clock

Generation

Output Multiplex

Y

1

C

1

8

8

Y

n–1

C

n–1

Y

n

C

n

Port A

OE

Port B

PIXCLK

LLC

LLC2

HREF

VREF

VACT

PIXCLK

LLC

Fig. 2–17: Detailed data output (single clock mode)

17Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

2.6.1.2. Embedded Reference Headers/ITU-R656

The VPX supports an output format which is designed to

be compliant with the ITU-R656 recommendation. It is

activated by setting Bit[1:0] of FP-RAM 0x150 to 01. The

16-bit video data must be multiplexed to 8 bit at the

double clock frequency (27 MHz) via FP-RAM 0x154, bit

9 set to 1 (see also section 2.6.3.: Output Multiplexer).

In this mode, video samples are in the following order:

Cb, Y, Cr, Y, ... The data words 0 and 255 are protected

since they are used for identification of reference headers. This is assured by limitation of the video data. Timing reference codes are inserted into the data stream at

the beginning and the end of each video line in the following way: A ‘Start of active video’-Header (SA V) is inserted before the first active video sample. The ‘end of

active video’-code (EA V) is inserted after the last active

video sample. They both contain information about the

field type and field blanking. The data words occurring

during the horizontal blanking interval between EA V and

SA V are filled with 0x10 for luminance and 0x80 for chrominance information. T able 2–3 shows the format of the

SAV and EAV header.

Note that the following changes and extensions to the

ITU-R656 standard have been included to support horizontal and vertical scaling, transmission of VBI-data,

etc.:

– Both the length and the number of active video lines

varies with the selected window parameters. For compliance with the ITU-R656 recommendation, a size of

720 samples per line must be selected for each window. To enable a constant line length even in the case

of different scaling values for the video windows, the

VPX provides a programmable ‘active video’ signal

(see section 2.8.4.).

– During blanked lines, the V ACT signal is suppressed.

VBI-lines can be marked as blanked or active, thus allowing the choice of enabled or suppressed V ACT during the VBI-window. The vertical field blanking flag (V)

in the SAV/EAV header is set to zero in any line with

enabled VACT signal (valid VBI or video lines).

– During blanked lines, SAV/EAV headers can be sup-

pressed in pairs with FP-RAM 0x150, bit9. To assure

vertical sync detection, some SAV/EAV headers are

inserted during field blanking.

– The flags F , V , and H encoded in the SAV/EA V headers

change on SAV. With FP-RAM 0x150, bit10 set to 1,

they change on EA V . The programmed windows, however, are delayed by one line. Header suppression is

applied for EAV/SAV pairs.

– For data within the VBI-window (e.g. sliced or raw tele-

text data), the user can select between limitation or reduction to 7-bit resolution with an additional LSB assuring odd parity (0 and 255 never occur). This option

can be selected via FP-RAM 0x150 [range].

– Ancillary data blocks may be longer than 255 bytes (for

raw data) and are transmitted without checksum. The

secondary data ID is used as high byte of the data

count (DC1; see Table 2–5).

– Ancillary data packets must not follow immediately af-

ter EAV or SAV.

– The total number of clock cycles per line, as well as

valid cycles between EAV and SAV may vary.

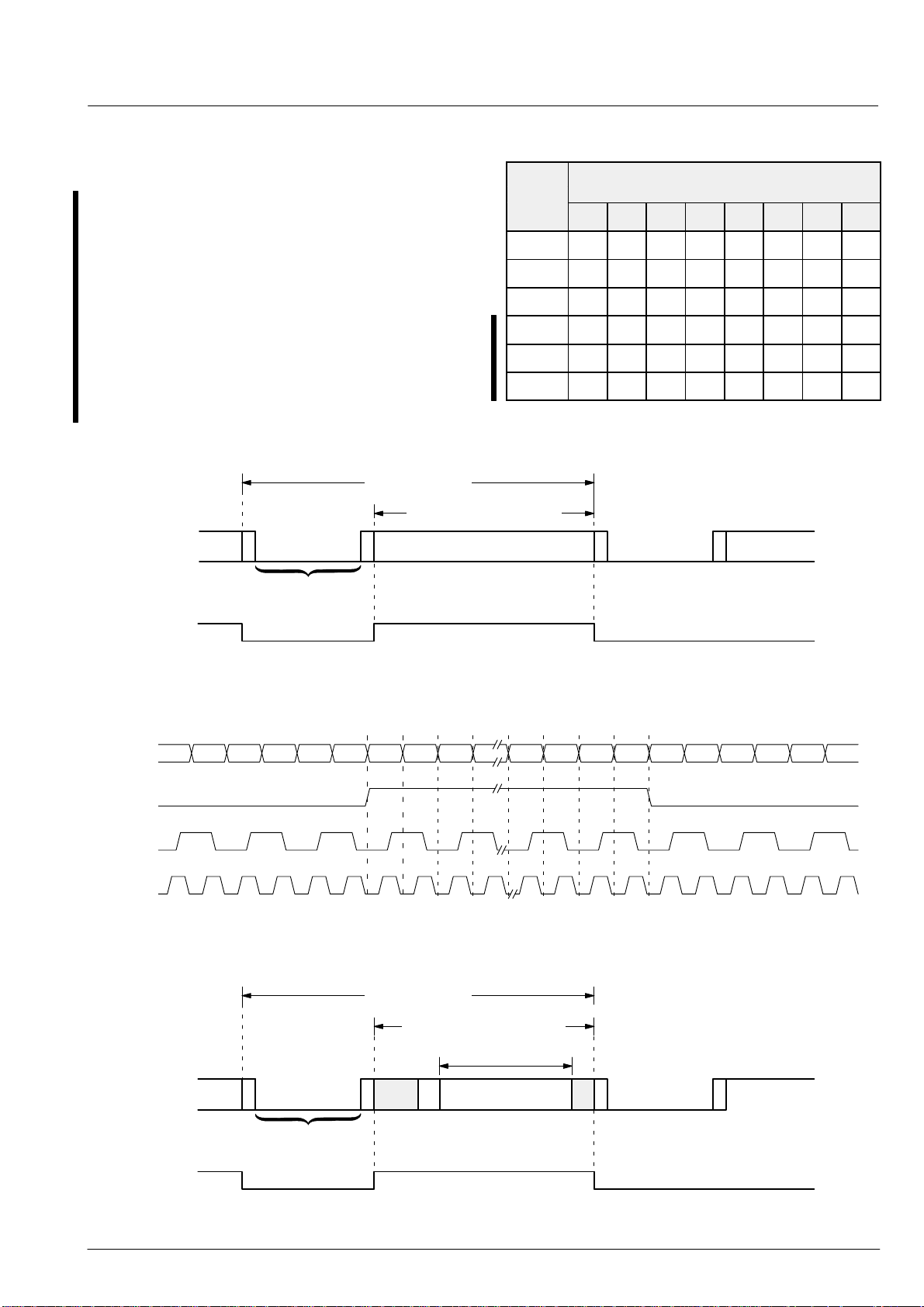

Table 2–3: Coding of the SAV/EAV-header

Bit No.

Word MSB LSB

7 6 5 4 3 2 1 0

First 1 1 1 1 1 1 1 1

Second 0 0 0 0 0 0 0 0

Third 0 0 0 0 0 0 0 0

Fourth 1 F V H P3 P2 P1 P0

F = 0 during field 1, F = 1 during field 2

V = 0 during active lines V = 1 during vertical field blanking

H = 0 in SAV, H = 1 in EAV

The bits P0, P1, P2, and P3 are protection bits. Their

states are dependent on the states of F, V, and H as

shown in Table 2–4.

Table 2–4: Coding of the protection bits

Bit No.

Code

(hex)

80 1 0 0 0 0 0 0 0

9D 1 0 0 1 1 1 0 1

AB 1 0 1 0 1 0 1 1

B6 1 0 1 1 0 1 1 0

C7 1 1 0 0 0 1 1 1

DA 1 1 0 1 1 0 1 0

EC 1 1 1 0 1 1 0 0

F1 1 1 1 1 0 0 0 1

MSB LSB

F V H P3 P2 P1 P0

The VPX also supports the transmission of VBI-data as

vertical ancillary data during blanked lines in the interval

starting with the end of the SAV and terminating with the

beginning of EAV. In this case, an additional header is inserted directly before the valid active data. In this mode,

the position of SAV and EA V depends on the settings for

the programmable VACT signal. These parameters will

18 Micronas

VPX 3225D, VPX 3224DPRELIMINARY DATA SHEET

be checked and corrected if necessary to assure an appropriate size of VACT for both data and ancillary header.

Table 2–5 shows the coding of the ancillary header information. The word I[2:0] contains a value for data type

identification (1 for sliced and 3 for raw data during odd

fields, 5 for sliced and 7 for raw data during even fields).

M[5:0] contains the MSBs and L[5:0] the LSBs of the

number of following D-words (32 for sliced data, 285 for

raw data). DC1 is normally used as secondary data ID.

The value 0 for M[5:0] in the case of sliced data marks

an undefined format. Bit 6 is even parity for bit5 to bit0.

Bit 7 is the inverted parity flag. Note that the following

user data words (video data) are either limited or have

odd parity to assure that 0 and 255 will not occur. Bit 3

in RAM 0x150 selects between these two options.

current line length

dependent on window size

Digital

Video Output

EAV

SAV

CB Y CR Y ...

Table 2–5: Coding of the ancillary header information

Bit No.

Word MSB LSB

7 6 5 4 3 2 1 0

Pream1 0 0 0 0 0 0 0 0

Pream2 1 1 1 1 1 1 1 1

Pream3 1 1 1 1 1 1 1 1

DID NP P 0 1 0 I2 I1 I0

DC1 NP P M5 M4 M3 M2 M1 M0

DC2 NP P L5 L4 L3 L2 L1 L0

CB Y CR Y ...

EAV

SAV

constant during

horizontal blanking

Y = 10

hex

; C

= C

= 80

R

B

hex

SAV: “start of active video” header

EAV: “end of active video” header

VACT

Fig. 2–18: Output of video or VBI data with embedded reference headers (according to ITU-R656)

DATA

(Port A)

VACT

PIXCLK

LLC

SAV1SAV2SAV3SAV

10h80h 80h 10hEAV1EAV2EAV3EAV

4

C

B1Y1

CR1Y2C

Bn–1Yn–1

C

Rn–1Yn

Fig. 2–19: Detailed data output (double clock mode)

current line length

size of programmable VACT

dependent on VBI-window size

4

Digital

Video Output

EAV

constant during

horizontal blanking

Y = 10

hex

; C

= C

R

B

= 80

SAV

hex

VACT

Fig. 2–20: Output of VBI-data as ancillary data

D1 D2 D3 D4 ...

ANC

CB Y CR Y ...

EAV

SAV: “start of active video” header

EAV: “end of active video” header

SAV

19Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

2.6.1.3. Embedded Timing Codes (BStream)

In this mode, several event words are inserted into the

pixel stream for timing information. It is activated by setting Bit[1:0] of FP-RAM 0x150 to 10. Each event word

consists of a chrominance code value containing the

phase of the color-multiplex followed by a luminance

code value signalling a specific event. The allowed control codes are listed in table 2–6 and 2–7.

At the beginning and the end of each active video line,

timing reference codes (start of active video: SAV; end

of active video: EA V) are inserted with the beginning and

the end of VACT. Since VACT is suppressed during

blanked lines, video data and SA V/EA V codes are present during active lines only . If raw/sliced data should be

output, V ACT has to be enabled during the VBI window

with bit 2 of FP-RAM 0x138! In the case of several windows per field, the length of the active data stream per

line can vary. Since the qualifiers for active video (SAV/

EAV) are independent of the other reference codes,

there is no influence on horizontal or vertical syncs, and

sync generation can be performed even with several different windows. For full compliance with applications requiring data streams of a constant size, the VPX provides a mode with programmable ‘video active’ signal

V ACT which can be selected via bit 2 of FP-RAM 0x140.

The start and end positions of V ACT relative to HREF is

determined by FP-RAM 0x151 and 0x152. The delay of

valid data relative to the leading edge of HREF is calculated with the formulas given in table 2–8 and 2–9. The

result can be read in FP-RAM 0x10f (for window 1) and

0x1 1f (for window 2). Be aware that the largest window

defines the size of the needed memory. In the case of

1140 raw VBI-samples and only 32 scaled video samples, the graphics controller needs 570 words for each

line (the VBI-samples are multiplexed to luminance and

chrominance paths).

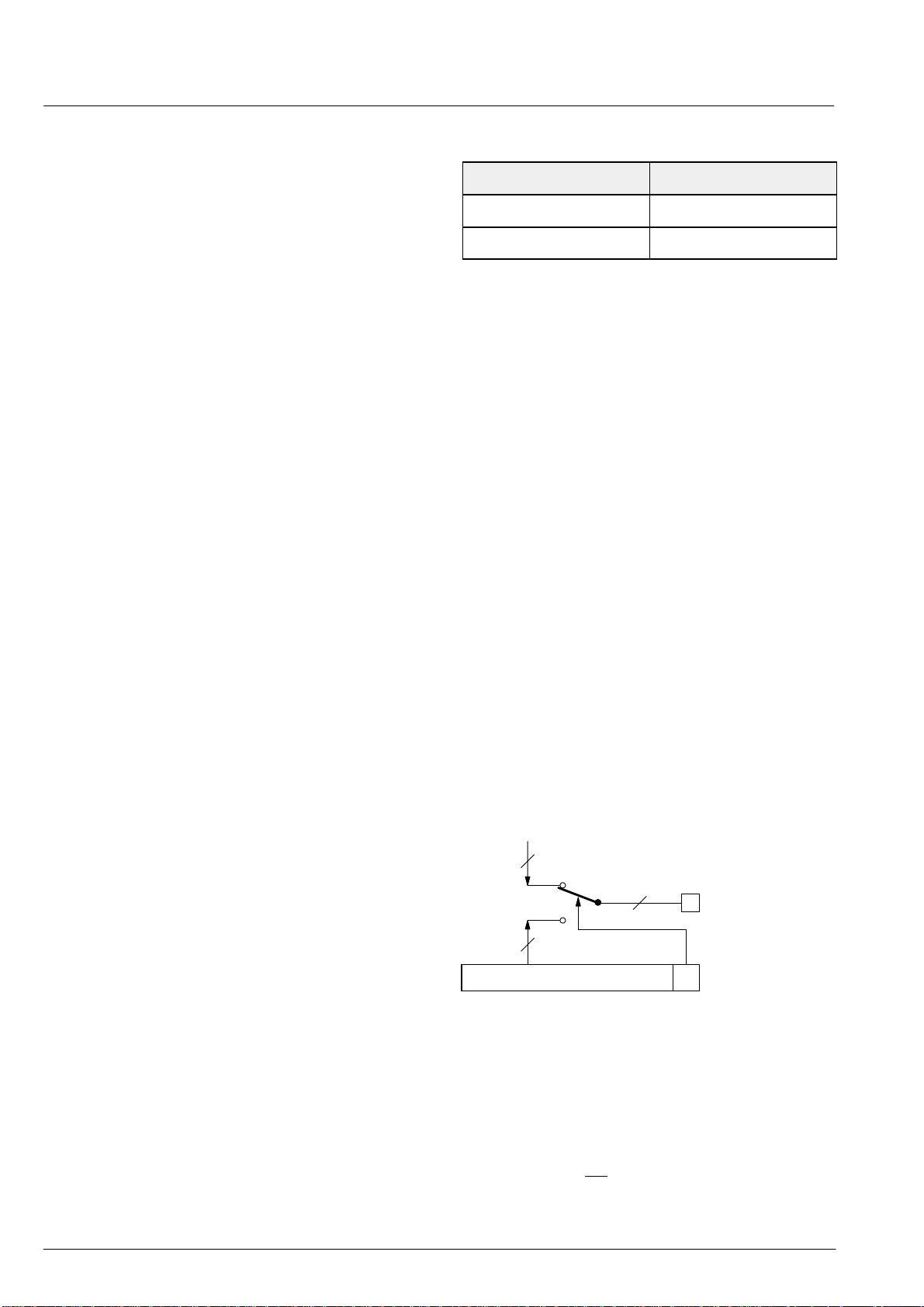

Table 2–6: Chrominance control codes

Chroma Value Phase Information

FE Cr pixel

FF Cb pixel

2.6.2. Bus Shuffler

In the YUV 4:2:2 mode, the output of luminance data is

on port A and chrominance data on Port B. With the bus

shuffler , luminance can be switched to Port B and chrominance to port A. In 8-bit double clock mode, shuffling

can be used to swap the Y and C components. It is selected with FP-RAM 0x150.

2.6.3. Output Multiplexer

During normal operation, a 16-bit YUV 4:2:2 data stream

is transferred synchronous to an internally generated

PIXCLK at a rate of 13.5 MHz. Data can be latched onto

the falling edge of PIXCLK or onto the rising edge of LLC

during high PIXCLK. In the double clock mode, luminance and chrominance data are multiplexed to 8 bit and

transferred at the double clock frequency of 27 MHz in

the order Cb, Y , Cr , Y ...; the first valid chrominance value

being a Cb sample. With shuffling switched on, Y and C

components are swapped. Data can be latched with the

rising edge of LLC or alternating edges of PIXCLK. This

mode is selected with bit 9 of FP-RAM 0x154. All 8-bit

modes use Port A only . In this case, Port B can be activated as programmable output with bit 8 of FP-RAM

0x154. Bit 0–7 determine the state of Port B.

video data

The leading edge of HREF indicates the beginning of a

new video line. Depending on the type of the current line

(active or blanked), the corresponding horizontal reference code is inserted. For big window sizes, the leading

edge of HREF can arrive before the end of the active

data. In this case, hardware assures that the control

8

=0

8

B[7:0]

video port

=1

8

code for HREF is delayed and inserted after EAV only.

The VREF control code is inserted at the falling edge of

7:0 8

VREF. The state of HREF at this moment indicates the

current field type (HREF = 0: odd field; HREF = 1: even

field).

FP-RAM 0x154 [outmux]

Fig. 2–21: Programmable output port

In this mode, the words 0,1,254, and 255 are reserved

for data identifications. This is assured by limitation of

the video data.

2.6.4. Output Ports

The two 8-bit ports produce TTL level signals coded in

binary offset. The Ports can be tristated either via the

output enable pin (OE

) or via I2C register 0xF2. For more

information, see section 2.17. “Enable/Disable of Output

Signals”.

20 Micronas

VPX 3225D, VPX 3224DPRELIMINARY DATA SHEET

Table 2–7: Luminance control codes

Luma Value Video Event Video Event Phase Information

01 VACT end last pixel was the last active pixel refers to the last pixel

02 VACT begin next pixel is the first active pixel refers to the next pixel

03 HREF active line begin of an active video line refers to the current pixel

04 HREF blank line begin of a blank line refers to the current pixel

05 VREF even begin of an even field refers to the current pixel

06 VREF odd begin of an odd field refers to the current pixel

DATA

(Port A)

VACT

HREF

PIXCLK

LLC

FFh 02h03hFFh FEh 01h

C

B1Y1

CR1Y2C

Bn–1Yn–1

Fig. 2–22: Detailed data output with timing event codes (double clock mode)

2.7. Video Data Transfer

The VPX supports a synchronous video interface. Video

data arrives to each line at the output in an uninterrupted

burst with a fixed transport rate of 13.5 MHz. The duration of the burst is measured in clock periods of the transport clock and is equal to the number of pixels per output

line.

2.7.1. Single and Double Clock Mode

Data is transferred synchronous to the internally generated PIXCLK. The frequency of PIXCLK is 13.5 MHz.

The LLC signal is provided as an additional support for

both the 13.5 MHz and the 27 MHz double clock mode.

The LLC consists of a doubled PIXCLK signal (27 MHz)

for interface to external components which rely on the

Philips transfer protocols. In the single clock mode, data

The data transfer is controlled via the signals: PIXCLK,

V ACT, and LLC. An additional clock signal LLC2 can be

switched to the TDO output pin to support different timings.

can be latched onto the falling edge of PIXCLK or at the

rising edge of LLC during high PIXCLK. In double clock

mode, output data can be latched onto both clock edges

of PIXCLK or onto every rising edge of LLC. Combined

with the half-clock mode, the available transfer band-

The V ACT signal flags the presence of valid output data.

Fig. 2–23, 2–24, and 2–25 illustrate the relationship be-

widths at the ports are therefore 6.75 MHz, 13.5 MHz,

and 27.0 MHz.

tween the video port data, VACT, PIXCLK, and LLC.

Whenever a line of video data should be suppressed

(line dropping, switching between analog inputs), it is

done by suppression of VACT.

C

Rn–1Yn

21Micronas

VPX 3225D, VPX 3224D

2.7.2. Half Clock Mode

For applications demanding a low bandwidth for the

transmission between video decoder and graphics controller, the clock signal qualifying the output pixels

(PIXCLK) can be divided by 2. This mode is enabled by

setting Bit 5 of the FP-RAM 0x150 [halfclk]. Note that the

output format ITU-R601 must be selected. The timing of

the data and clock signals in this case is described in Figure 2–25.

If the half-clock mode is enabled, each second pulse of

PIXCLK is gated. PIXCLK can be used as a qualifier for

valid data. To ensure that the video data stream can be

spread, the selected number of valid output samples

should not exceed 400.

PRELIMINARY DATA SHEET

Luminance

(Port A)

Chrominance

(Port B)

VACT

PIXCLK

LLC

Fig. 2–23: Output timing in single clock mode

Video

(Port A)

VACT

PIXCLK

LLC

Y

1

C

1

C

Y

1

1

Y

n–1

C

n–1

C

n–1

Y

n–1

Y

n

C

n

C

Y

n

n

Fig. 2–24: Output timing in double clock mode

Luminance

(Port A)

Chrominance

(Port B)

VACT

PIXCLK

LLC

Y

1

C

1

Y

n

C

n

Fig. 2–25: Output timing in half clock mode

22 Micronas

VPX 3225D, VPX 3224DPRELIMINARY DATA SHEET

2.8. Video Reference Signals

The complete video interface of the VPX runs at a clock

rate of 13.5 MHz. It mainly generates two reference signals for the video timing: a horizontal reference (HREF)

and a vertical reference (VREF). These two signals are

generated by programmable hardware and can be either free running or synchronous to the analog input video. The video line standard (625/50 or 525/60) depends

on the TV-standard selected with FP-RAM 0x20 [sdt].

The polarity of both signals is individually selectable via

FP-RAM 0x153.

The circuitry which produces the VREF and HREF signals has been designed to provide a stable, robust set

of timing signals, even in the case of erratic behavior at

the analog video input. Depending on the selected operating mode given in FP-RAM 0x140 [settm], the period

of the HREF and VREF signals are guaranteed to remain within a fixed range. These video reference signals

can therefore be used to synchronize the external components of a video subsystem (for example the ICs of a

PC add-in card).

In addition to the timing references, valid video samples

are marked with the ‘video active’ qualifier (V ACT). In order to reduce the signal number of the video interface,

several 8-bit modes have been implemented, where the

reference signals are multiplexed into the data stream

(see section 2.6.1.).

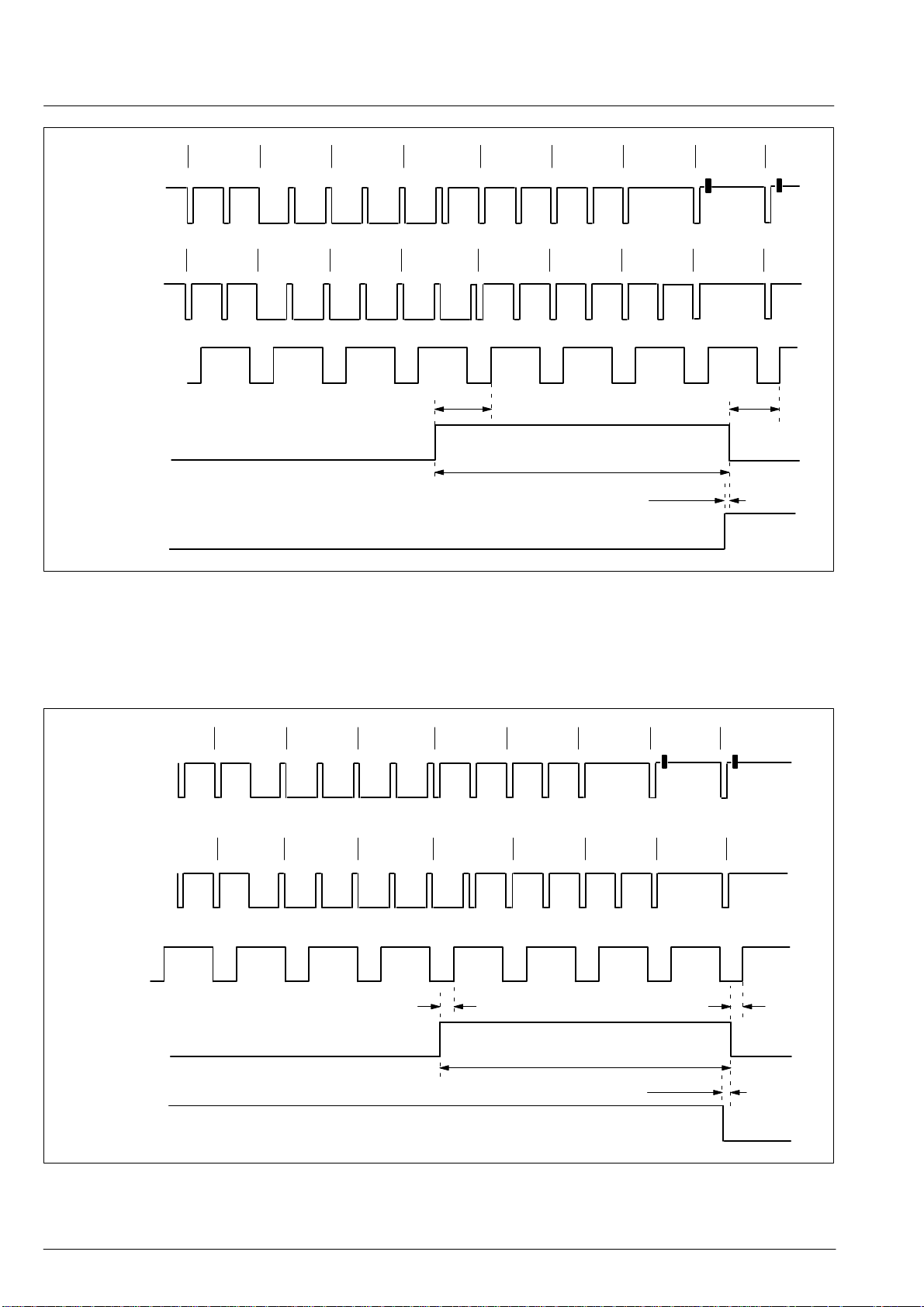

2.8.2. VREF

Figs. 2–27 and 2–28 illustrate the timing of the VREF

signal relative to field boundaries of the two TV standards. The start of the VREF pulse is fixed, while the

length is programmable in the range between 2 and 9

video lines via FP-RAM 0x153 [vlen].

2.8.3. Odd/Even Information (FIELD)

Information on whether the current field is odd or even

is supplied through the relationship between the edge

(either leading or trailing) of VREF and level of HREF.

This relationship is fixed and shown in Figs. 2–27 and

2–28. The same information can be supplied to the

FIELD pin, which can be enabled/disabled as output in

FP-RAM 0x153 [enfieldq]. FP-RAM 0x153 [oepol] programs the polarity of this signal.

During normal operation the FIELD flag is filtered since

most applications need interlaced signals. After filtering,

the field type is synchronized to the input signal only if

the last 8 fields have been alternating; otherwise, it always toggles. This filtering can be disabled with FPRAM 0x140 [disoef]. In this case, the field information

follows the odd/even property of the input video signal.

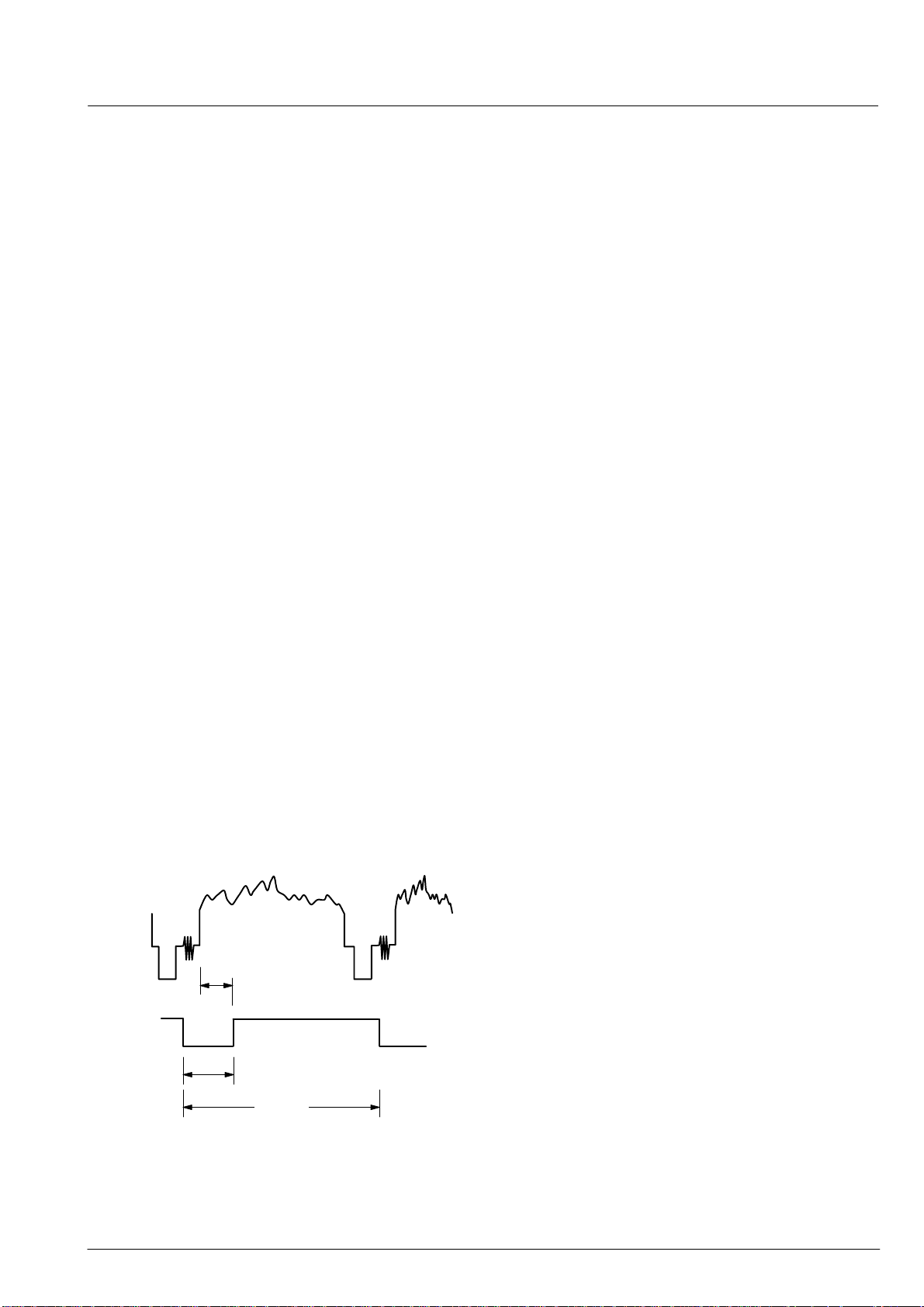

2.8.1. HREF

Fig. 2–26 illustrates the timing of the HREF signal relative to the analog input. The inactive period of HREF has

a fixed length of 64 periods of the 13.5 MHz output clock

rate. The total period of the HREF signal is expressed as

F

Analog

Video

Input

HREF

and depends on the video line standard.

nominal

VPX

Delay

4.7 µs (64 cycles)

F

nominal

Fig. 2–26: HREF relative to input video

23Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

625

1234567

Input CVBS

(50 Hz), PAL

34567 8 910

Input CVBS

(60 Hz), NTSC

HREF

VREF

FIELD

Fig. 2–27: VREF timing for ODD fields

361 t

CLK13.5

2 .. 9 H

> 1 t

CLK13.5

361 t

CLK13.5

Input CVBS

(50 Hz), PAL

Input CVBS

(60 Hz), NTSC

HREF

VREF

FIELD

313 314 315 316 317 318 319312 320

265 266 267 268 269 270 271 272 273

46 t

CLK13.5

2 .. 9 H

46 t

> 1 t

CLK13.5

CLK13.5

Fig. 2–28: VREF timing for EVEN fields

24 Micronas

VPX 3225D, VPX 3224DPRELIMINARY DATA SHEET

2.8.4. VACT

supported [FP-RAM 0x140, vactmode]. The start and

end position for the VACT signal relative to the trailing

The ‘video active’ signal is a qualifier for valid video samples. Since scaled video data is stored internally, there

are no invalid pixel within the V ACT interval. VACT has

edge of HREF can be programmed within a range of 0

to 864 [FP-RAM 0x151, 0x152]. In this case, VACT no

longer marks valid samples only.

a defined position relative to HREF depending on the

window settings (see section 2.10.). The maximal window length depends on the minimal line length of the input signal. It is recommended to choose window sizes of

less than 800 pixels. Sizes up to 864 are possible, but for

non-standard input lines, VACT is forced inactive 4

PIXCLK cycles before the next trailing edge of HREF.

The position of the valid data depends on the window

definitions. It is calculated from the internal processor.

The calculated delay of V ACT relative to the trailing edge

of HREF can be read via FP-RAM 0x10f (window 1) or

0x1 1f (window 2). T ables 2–8 and 2–9 show the formulas

for the position of valid data samples relative to the trail-

ing edge of HREF.

During the VBI-window, VACT can be enabled or suppressed with FP-RAM 0x138. Within this window, the

VPX can deliver either sliced text data with a constant

length of 64 samples or 1 140 raw input samples. For applications that request a uniform window size over the

whole field, a mode with a free programmable VACT is

Fig. 2–29 illustrates the temporal relationship between

the VACT and the HREF signals as a function of the

number of pixels per output line and the horizontal di-

mensions of the window. The duration of the inactive pe-

riod of the HREF is fixed to 64 clock cycles.

Table 2–8: Delay of valid output data relative to the trailing edge of HREF (single clock mode)

Mode Data Delay Data End

Video data (HBeg+HLen)*(720/NPix)–Hlen for NPix < 720

DataDelay + HLen

HBeg*(720/NPix) for NPix ≥ 720

Raw VBI data 150 720

Sliced VBI data 726 790

Table 2–9: Delay of valid output data relative to the trailing edge of HREF (half clock mode)

Mode Data Delay Data End

Video data (HBeg+HLen)*(720/NPix)–2*Hlen for NPix < 360

DataDelay + 2*HLen

HBeg*(720/NPix) for NPix ≥ 360

Raw VBI data not possible! not possible!

Sliced VBI data 662 790

DATA

(Port A or B)

VACT

data delay

64 cycles

HREF

D

1

D

n–1

D

n

data end

PIXCLK

LLC

Fig. 2–29: Relationship between HREF and VACT signals (single clock mode)

25Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

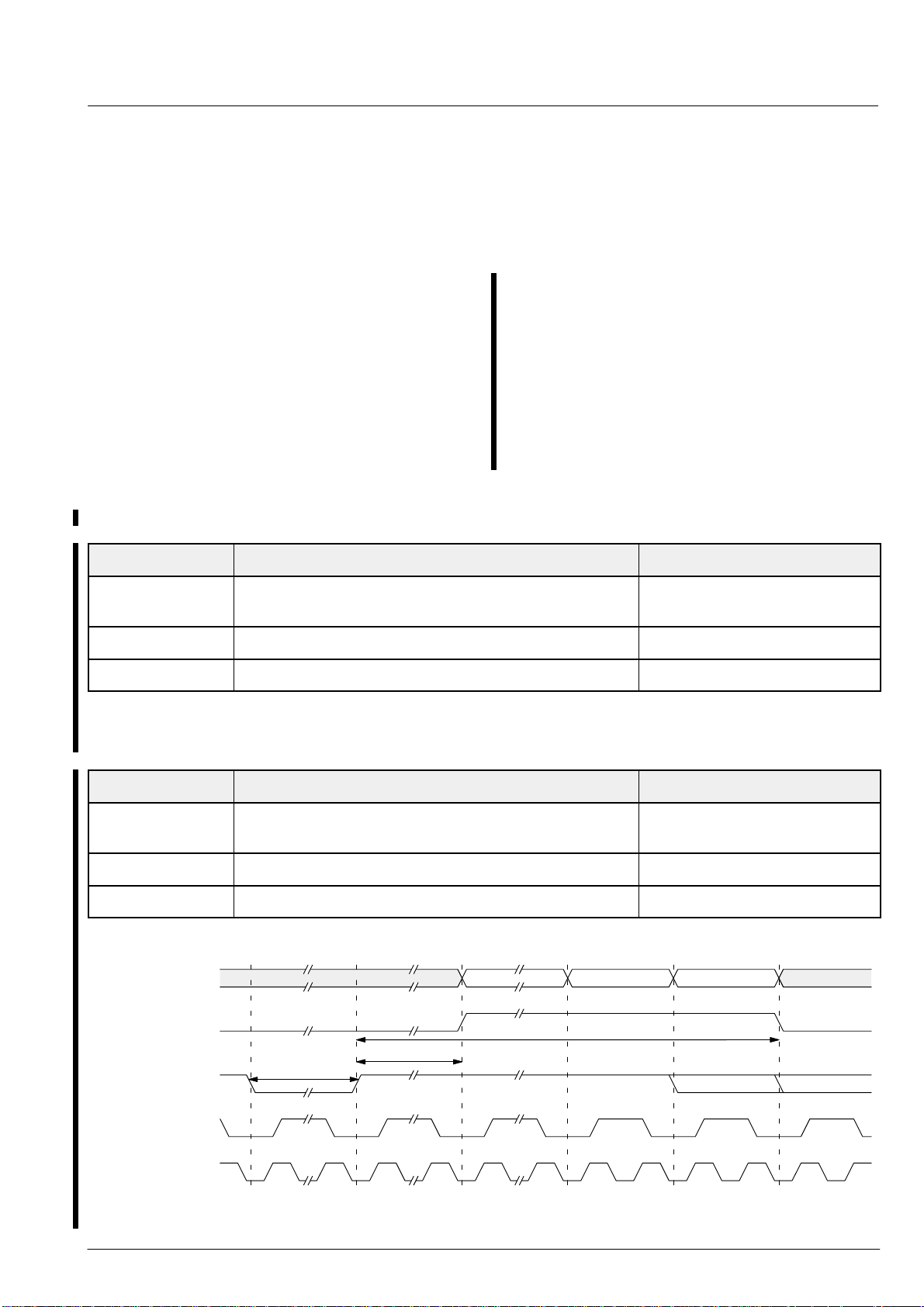

2.9. Operational Modes

The relationship between the video timing signals

(HREF and VREF) and the analog input video is determined by the selected operational mode. Three such

modes are available: the Open Mode, the Forced

Mode, and the Scan Mode. These modes are selected

2

via I

C commands [FP-RAM 0x140, settm, lattm].

2.9.1. Open Mode

In the Open Mode, both the HREF and the VREF signal

track the analog video input. In the case of a change in

the line standard (i.e. switching between the video input

ports), HREF and VREF automatically synchronize to

the new input. When no video is present, both HREF and

VREF float to the idling frequency of their respective

PLLs. During changes in the video input (drop-out,

switching between inputs), the performance of the

HREF and VREF signals is not guaranteed.

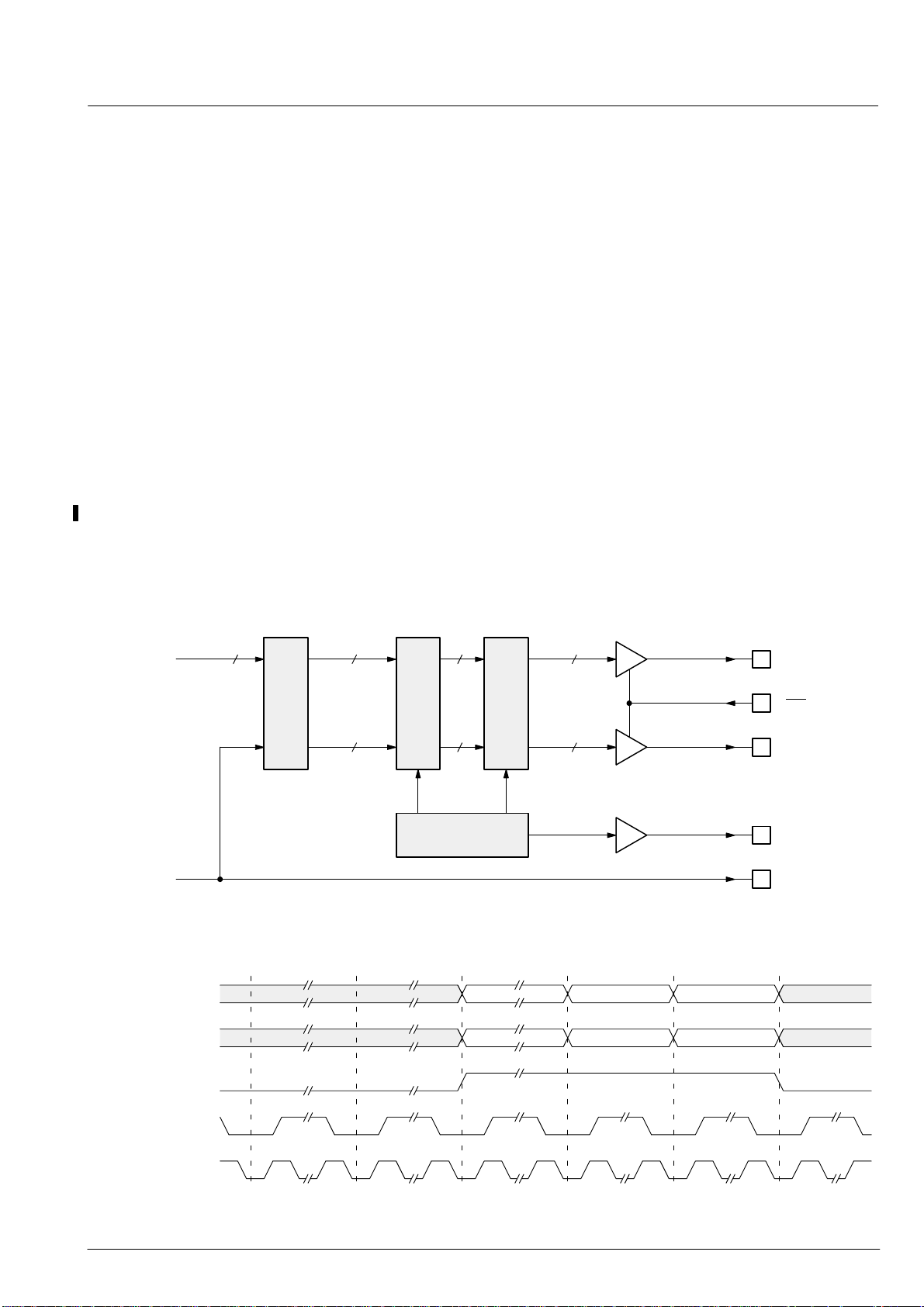

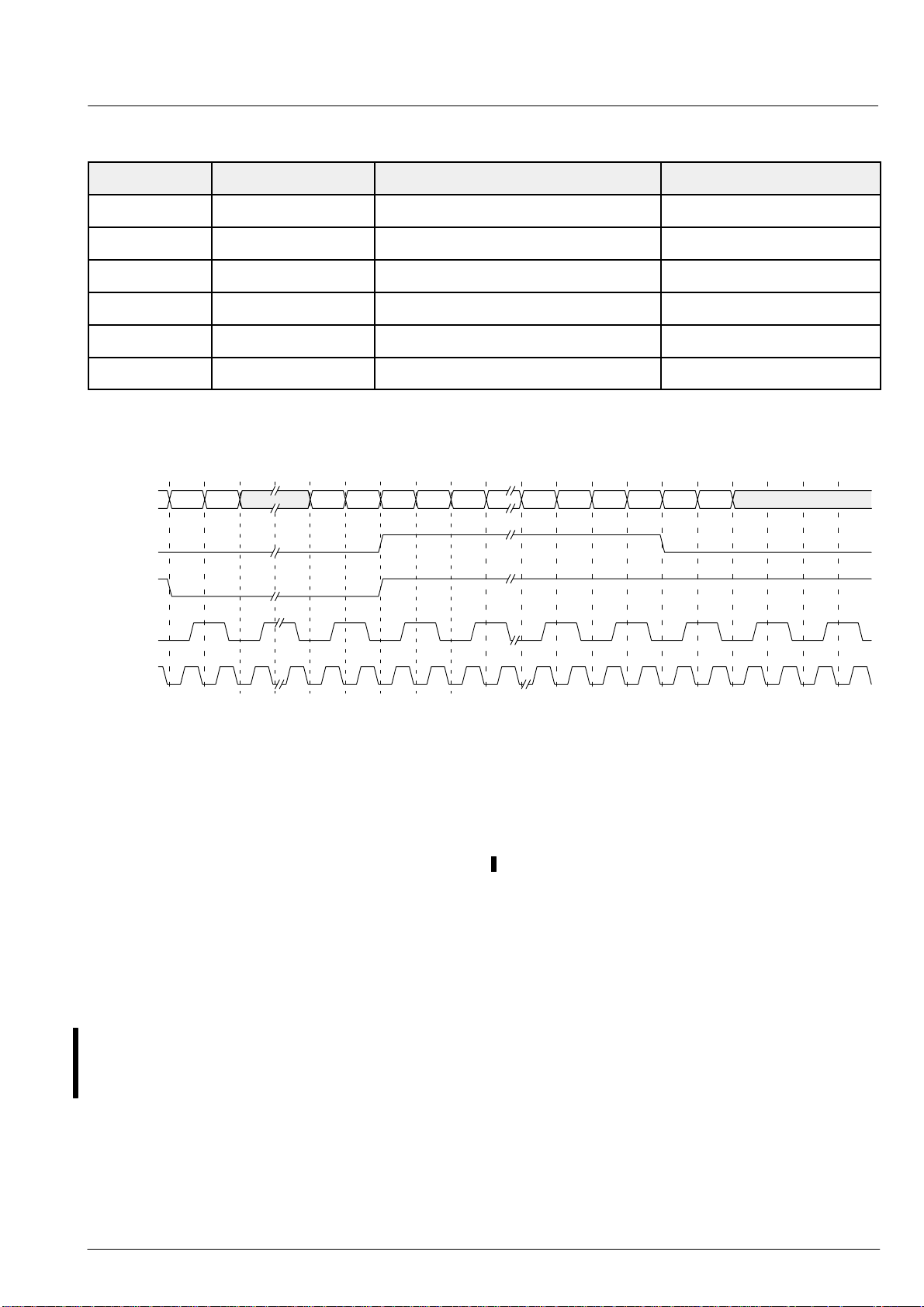

2.9.2. Scan Mode

In the Scan Mode, the HREF and VREF signals are always generated by free running hardware. They are

therefore completely decoupled from the analog input.

The output video data is always suppressed.

The purpose of the Scan Mode is to allow the external

controller to freely switch between the analog inputs

while searching for the presence of a video signal. Information regarding the video (standard, source, etc...)

can be queried via I

2

C read.

In the Scan Mode, the video line standard of the VREF

and HREF signals can be changed via I

2

C command.

The transition always occurs at the first frame boundary

after the I

2

C command is received. Fig. 2–30, below,

demonstrates the behavior of the VREF signal during

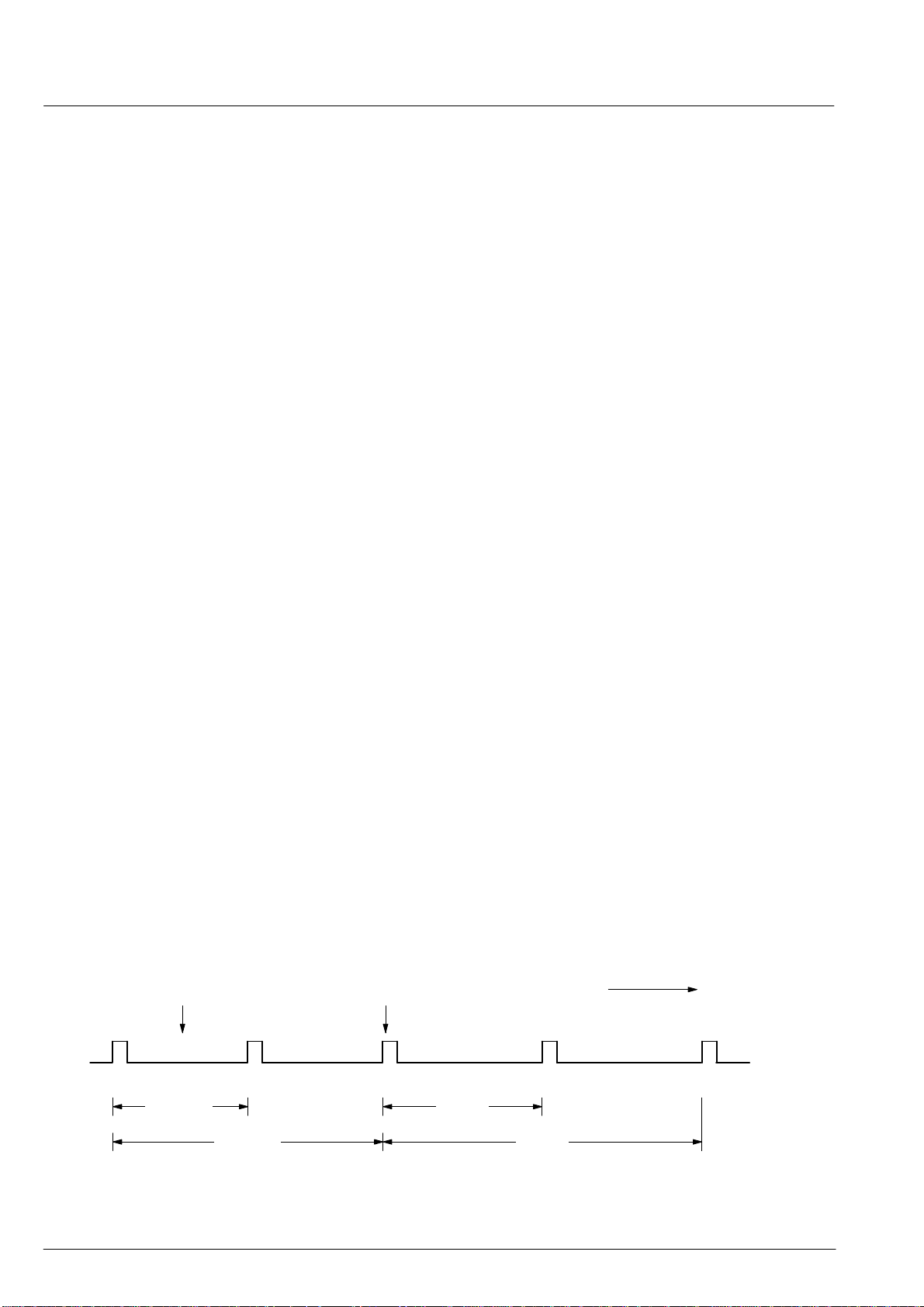

the transition from the 525/60 system to the 625/50 system (the width of the vertical reference pulse is exaggerated for illustration).

I2C Command to

switch video timing standard

Selected timing standard

becomes active

time

VREF

f

odd

16.683 ms

f

even

33.367 ms 40.0 ms

f

odd

20.0 ms

f

even

f

odd

(525/60) (625/50)

Fig. 2–30: Transition between timing standards

26 Micronas

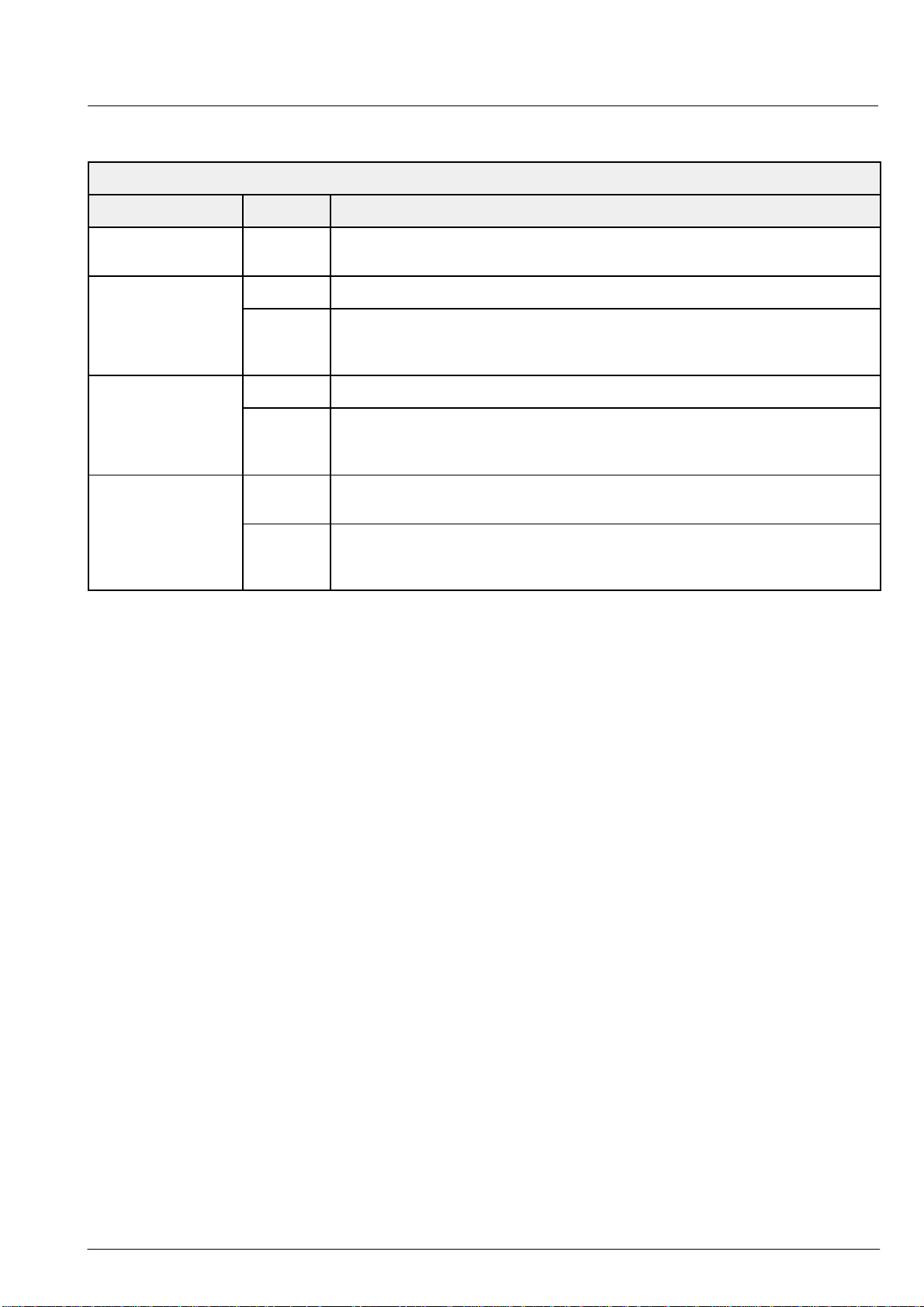

Table 2–10: Transition behavior as a function of operating mode

Transition Behavior as a Function of Operating Mode

Transition Mode Behavior

VPX 3225D, VPX 3224DPRELIMINARY DATA SHEET

Power up/Reset

(no video)

no video → video Open VREF, HREF: track the input signal

video → no video Open VREF, HREF: floats to steady state frequency of internal PLL

video → video Open VREF, HREF: track the input video immediately

Open VREF, HREF: floats to steady state frequency of internal PLL

Scan no visible effect on any data or control signals

– timing signals continue unchanged in free running mode

– VACT signal is suppressed

Scan no visible effect on any data or control signals

– timing signals continue unchanged in free running mode

– VACT signal is suppressed

Data: available immediately after color decoder locks to input.

Scan no outwardly visible effect on any data or control signals.

– timing signals continue unchanged in free running mode

– VACT signal is suppressed

27Micronas

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

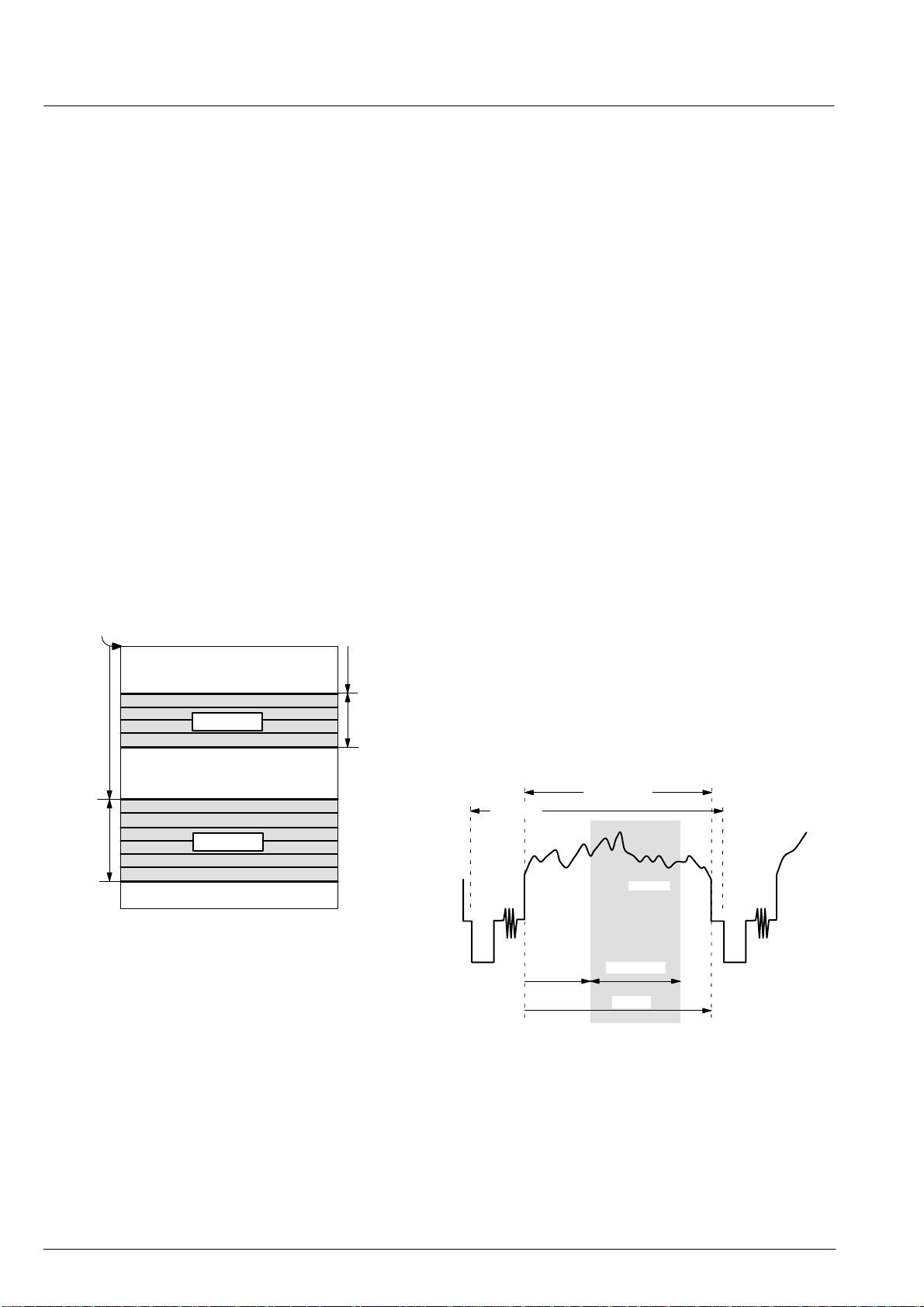

2.10. Windowing the Video Field

For each input video field, two non-overlapping video

windows can be defined. The dimensions of these windows are supplied via I

2

C commands. The presence of

two windows allows separate processing parameters

such as filter responses and the number of pixels per line

to be selected.

External control over the dimensions of the windows is

performed by I

2

C writes to a window-load-table (WinLoadT ab). For each window , a corresponding WinLoadT ab is defined in a table of registers in the FP-RAM [window1: 0x120–128; window2: 0x12a–132]. Data written

to these tables does not become active until the corresponding latch bit is set in the control register FP-

RAM 0x140. A 2-bit flag specifies the field polarity over

which the window is active [vlinei1,2].

Vertically, as can be seen in Fig. 2–31, each window is

defined by a beginning line given in FP-RAM 0x120/12A,

a number of lines to be read-in (FP-RAM 0x121/12B),

and a number of lines to be output (FP-RAM

0x122/12C). Each of these values is specified in units of

video lines.

Line 1

begin

begin

Window 1

# lines in,

# lines out

The option, to separately specify the number of input

lines and the number of output lines, enables vertical

compression. In the VPX, vertical compression is performed via simple line dropping. A nearest neighbor algorithm selects the subset of the lines for output. The

presence of a valid line is signalled by the ‘video active’

qualifier (or the corresponding SAV/EAV code in embedded sync modes).

The numbering of the lines in a field of interlace video is

dependent on the line standard. Figs. 2–33 and 2–34 illustrate the mapping of the window dimensions to the

actual video lines. The indices on the left are the line

numbers relative to the beginning of the frame. The indices on the right show the numbering used by the VPX.

As seen here, the vertical boundaries of windows are defined relative to the field boundary. Spatially, the lines

from field #1 are displayed above identically numbered

from field #2. For example: On an interlace monitor, line

#23 from field #1 is displayed directly above line #23

from field #2. There are a few restrictions to the vertical

definition of the windows. Windows must not overlap

vertically but can be adjacent. The first allowed line within a field is line #10 for 525/60 standards and line #7 for

625/50 standards. The number of output lines cannot be

greater than the number of input lines (no vertical zooming). The combined height of the two windows cannot

exceed the number of lines in the input field.

Horizontally , the windows are defined by a starting point

defined in FP-RAM 0x123/12D and the length in FPRAM 0x124/12E. They are both given relative to the

number of pixels (NPix) in the active portion of the line

(Fig. 2–32) selected in FP-RAM 0x125/12F . The scaling

factor is calculated internally from NPix.

# lines in,

# lines out

Window 2

Fig. 2–31: Vertical dimensions of windows

53.33 msec

64 msec

Window

H Begin H Length

N Pix

Fig. 2–32: Horizontal dimensions of sampling window

28 Micronas

Loading...

Loading...