Micronas VDP3116B, VDP3108B, VDP3104B Datasheet

VDP 31xxB

Video Processor Family

Edition Sept. 25, 1998

6251-437-2PD

PRELIMINARY DATA SHEET

MICRONAS

MICRONAS

Contents

Page Section Title

5 1. Introduction

6 1.1. VDP Applications

7 2. Functional Description

7 2.1. Analog Front-End

7 2.1.1. Input Selector

7 2.1.2. Clamping

7 2.1.3. Automatic Gain Control

7 2.1.4. Analog-to-Digital Converters

7 2.1.5. ADC Range

7 2.1.6. Digitally Controlled Clock Oscillator

7 2.1.7. Analog Video Output

9 2.2. Adaptive Comb Filter

10 2.3. Color Decoder

10 2.3.1. IF-Compensation

11 2.3.2. Demodulator

11 2.3.3. Chrominance Filter

11 2.3.4. Frequency Demodulator

1 1 2.3.5. Burst Detection

11 2.3.6. Color Killer Operation

11 2.3.7. PAL Compensation/1-H Comb Filter

12 2.3.8. Luminance Notch Filter

12 2.3.9. Skew Filtering

13 2.4. Horizontal Scaler

13 2.5. Black-Line Detector

13 2.6. Test Pattern Generator

14 2.7. Video Sync Processing

15 2.8. Display Part

15 2.8.1. Luma Contrast Adjustment

15 2.8.2. Black Level Expander

16 2.8.3. Dynamic Peaking

17 2.8.4. Digital Brightness Adjustment

17 2.8.5. Soft Limiter

17 2.8.6. Chroma Input

17 2.8.7. Chroma Interpolation

18 2.8.8. Chroma Transient Improvement

18 2.8.9. Inverse Matrix

18 2.8.10. RGB Processing

18 2.8.11. OSD Color Lookup Table

19 2.8.12. Picture Frame Generator

19 2.8.13. Priority Codec

19 2.8.14. Scan Velocity Modulation

19 2.8.15. Display Phase Shifter

PRELIMINARY DATA SHEETVDP 31xxB

2 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

Contents, continued

Page Section Title

21 2.9. Analog Back End

21 2.9.1. CRT Measurement and Control

22 2.9.2. SCART Output Signal

23 2.9.3. Average Beam Current Limiter

23 2.9.4. Analog RGB Insertion

24 2.9.5. Fast Blank Monitor

24 2.9.6. Half Contrast Control

24 2.10. IO Port Expander

26 2.1 1. Synchronization and Deflection

26 2.1 1.1. Deflection Processing

26 2.1 1.2. Horizontal Phase Adjustment

28 2.11.3. Vertical and East/West Deflection

28 2.1 1.4. Protection Circuitry

29 2.12. Reset Function

29 2.13. Standby and Power-On

30 3. Serial Interface

30 3.1. I

2

C-Bus Interface

30 3.2. Control and Status Registers

43 3.2.1. Scaler Adjustment

46 3.2.2. Calculation of Vertical and East-West Deflection Coefficients

47 4. Specifications

47 4.1. Outline Dimensions

47 4.2. Pin Connections and Short Descriptions

49 4.3. Pin Descriptions

51 4.4. Pin Configuration

52 4.5. Pin Circuits

54 4.6. Electrical Characteristics

54 4.6.1. Absolute Maximum Ratings

54 4.6.2. Recommended Operating Conditions

54 4.6.3. Recommended Crystal Characteristics

55 4.6.4. Characteristics

56 4.6.4.1. 5 MHz Clock Output

56 4.6.4.2. 20 MHz Clock Input/Output, External Clock Input (XTAL1)

56 4.6.4.3. Reset Input, Test Input

57 4.6.4.4. I

2

C-Bus Interface

57 4.6.4.5. IO Port Expander

57 4.6.4.6. Analog Video Inputs

58 4.6.4.7. Analog Front-End and ADCs

59 4.6.4.8. Picture Bus Input

60 4.6.4.9. INTLC, Front Sync Output

60 4.6.4.10. Main Sync Output

60 4.6.4.11. Combined Sync Output

3Micronas

VDP 31xxB PRELIMINARY DATA SHEET

Contents, continued

Page Section Title

61 4.6.4.12. Horizontal Flyback Input

61 4.6.4.13. Horizontal Drive Output

61 4.6.4.14. Vertical Protection Input

61 4.6.4.15. Vertical Safety Input

62 4.6.4.16. Vertical and East/West Drive Output

62 4.6.4.17. Sense A/D Converter Input

62 4.6.4.18. Analog RGB and FB Inputs

63 4.6.4.19. Half Contrast Switch Input

64 4.6.4.20. Analog RGB Outputs, D/A Converters

66 4.6.4.21. DAC Reference, Beam Current Safety

66 4.6.4.22. Scan Velocity Modulation Output

67 5. Application Circuit

72 6. Data Sheet History

4 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

Video, Display, and Deflection Processor

Release Notes: This data sheet describes functions

and characteristics of the VDP 31xxB–C2. Revision

bars indicate significant changes to the previous

edition.

1. Introduction

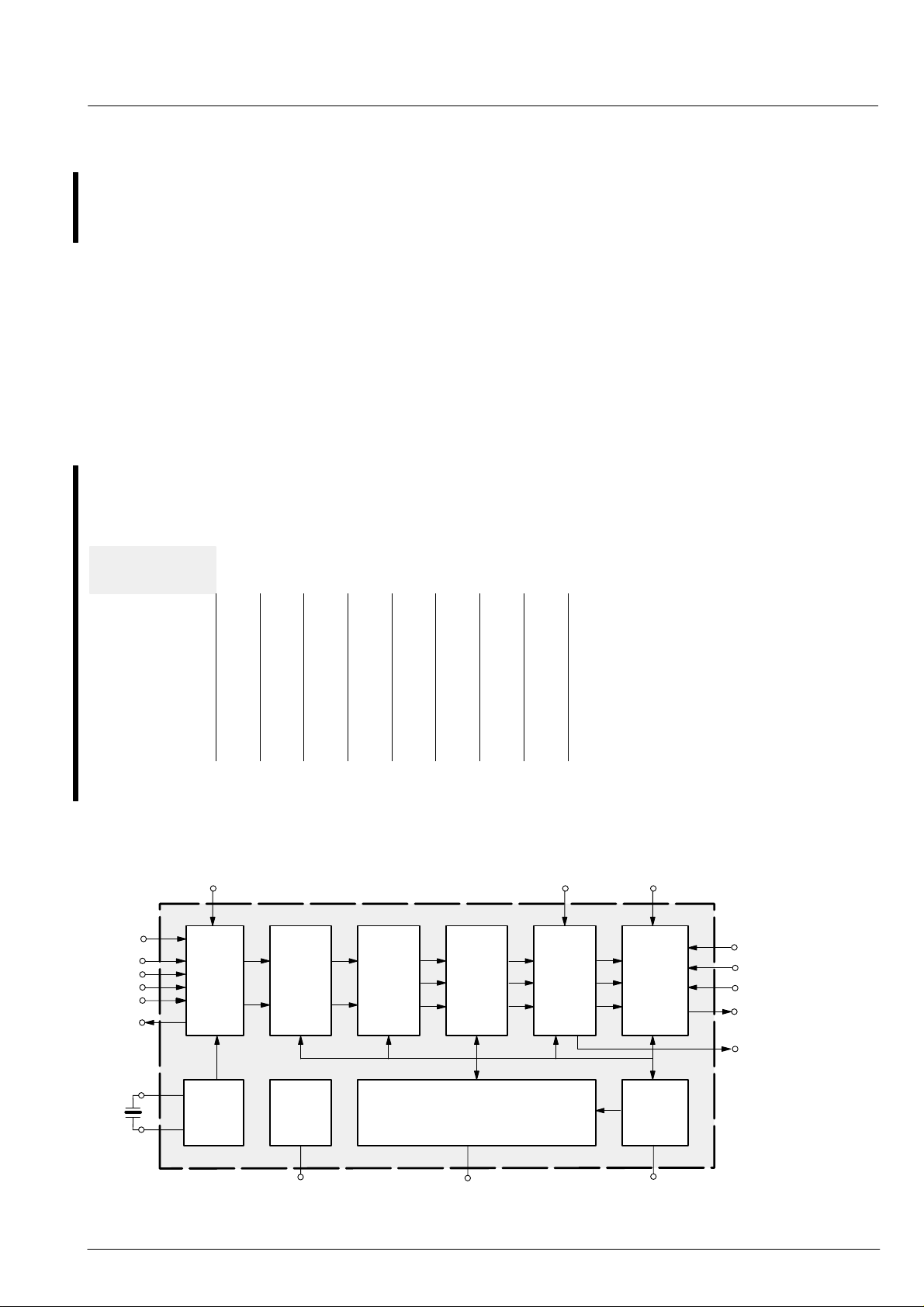

The VDP 31xxB is a Video IC family of high-quality

single-chip video processors. Modular design and a

submicron technology allow the economic integration of

features in all classes of TV sets. The VDP 31xxB family

is based on functional blocks contained in the two chips:

VDP 31xxB

Family

1H Combfilter

Horizontal Scaler

2H adapt. Comb

Color Trans. Impr.

Scan Vel. Mod.

VPC 3200A Video Processor and DDP 3300A Display

and Deflection Processor.

Each member of the family contains the entire video,

display, and deflection processing for 4:3 and 16:9

50/60 TV sets. Its performance and flexibility allow the

user to standardize his product development. Hardware

and software applications can profit from the modularity ,

as well as manufacturing, systems support, or maintenance. An overview of the VDP 31xxB video processor

family is shown in Fig. 1–1.

RGB Insertion

Prog. RGB Matrix

Tube Control

VDP 3104B

VDP 3108B

VDP 3112B

VDP 3116B

VDP 3120B

n

n

n

n

n

nn

n

n

Fig. 1–1: VDP 31xxB family overview

VRT

CIN

VIN1

VIN2

VIN3

VIN4

VOUT

Analog

Frontend

AGC,

2*8bit ADC

2H

Adaptive

Combfilter

n

n

n

n

nnn

n

Color

Decoder

NTSC,

PAL,

SECAM

n

n

n

n

n

Horizontal

Scaler

Panorama

Mode

n

n

n

n

n

n

n

n

n

n

Color Bus

Display

Processor

RGB Matrix,

CLUT,

Scan Veloc.

XREF

Analog

Backend

3*10bit DAC,

Tube Control,

RGB Switch

RGB/FB IN1

RGB/FB IN2

Half Contrast

RGB OUT

SVM

20.25

MHz

Clock Gen.

DCO

2

C

I

2

C

I

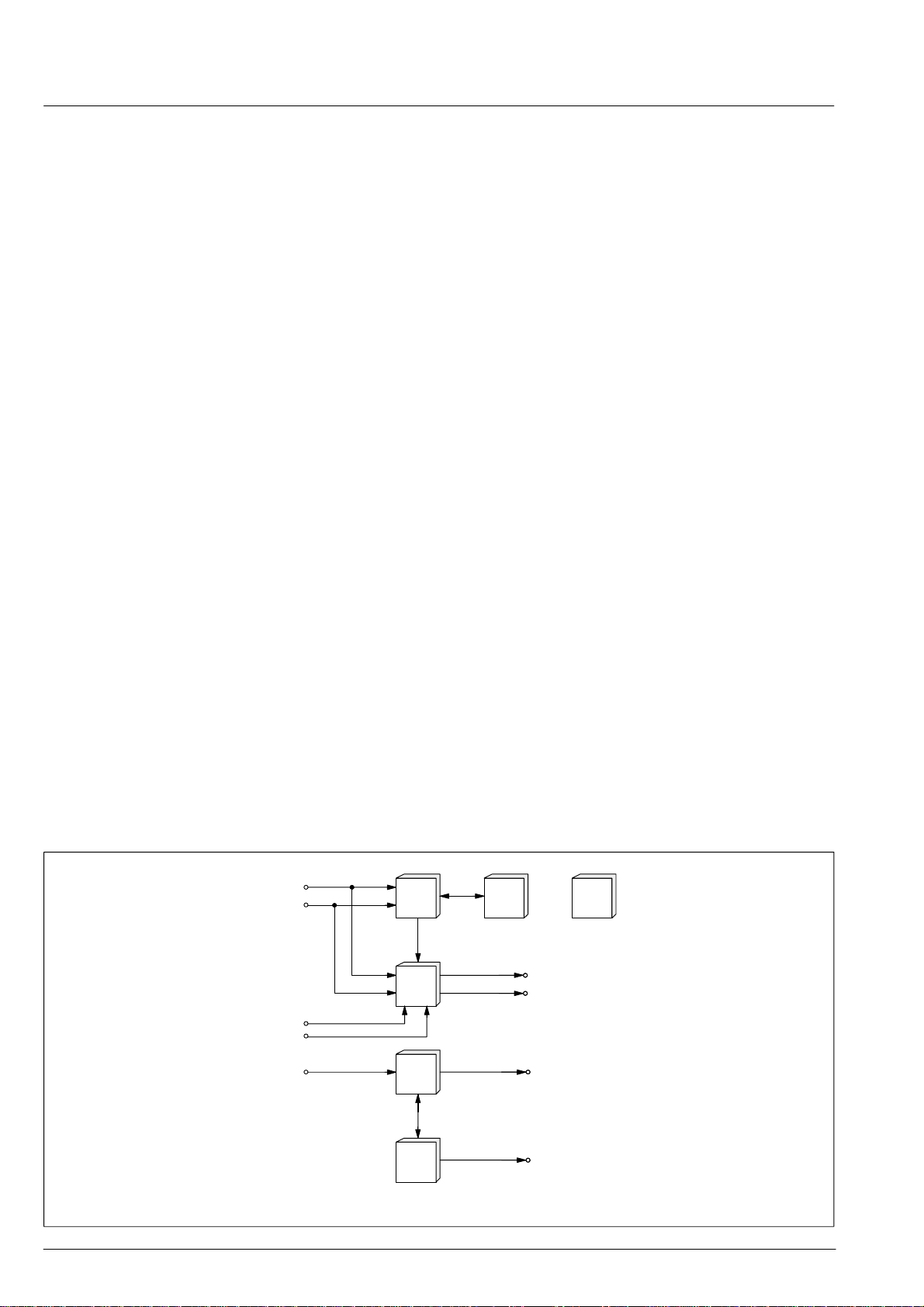

Fig. 1–2: Block diagram of the VDP 3120B

Sync & Deflection

H/V/EW

Measurement

ADC

Sense

5Micronas

VDP 31xxB PRELIMINARY DATA SHEET

1.1. VDP Applications

As a member of the VDP 31xxB family , the VDP 3120B

offers all video features necessary to design a state-ofthe-art TV set:

Video Decoding

– 4 composite inputs, 1 S-VHS input

– composite video & sync output

– integrated high-quality A/D converters

– adaptive 2H comb filter Y/C separator

– 1H NTSC comb filter

– multistandard color decoder (1 crystal)

– multistandard sync decoder

– black line detector

Video Processing

– horizontal scaling (0.25 to 4)

– panorama vision

– black level expander

– dynamic peaking

– soft limiter (gamma correction)

RGB Processing

– programmable RGB matrix

– digital color bus interface

– additional analog RGB / fast blank input

– half-contrast switch

– picture frame generator

Deflection

– scan velocity modulation output

– high-performance H/V deflection

– separate ADC for tube measurements

– EHT compensation

Miscellaneous

– one 20.25 MHz crystal, few external components

– embedded RISC controller (80 MIPS)

2

C-Bus Interface

– I

– single 5 V power supply

– submicron CMOS technology

– color transient improvement

Video 1

Video 2

RGB 1

RGB 2

Audio

TPU

3040

VDP

3120B

MSP

3410

– 64-pin PSDIP package

DRAM

CCU

300x

RGB

H/VDefl.

3 x Stereo

DPL

3420

Dolby Surround

Fig. 1–3: Full-feature TV set with VDP 3120B

6 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

2. Functional Description

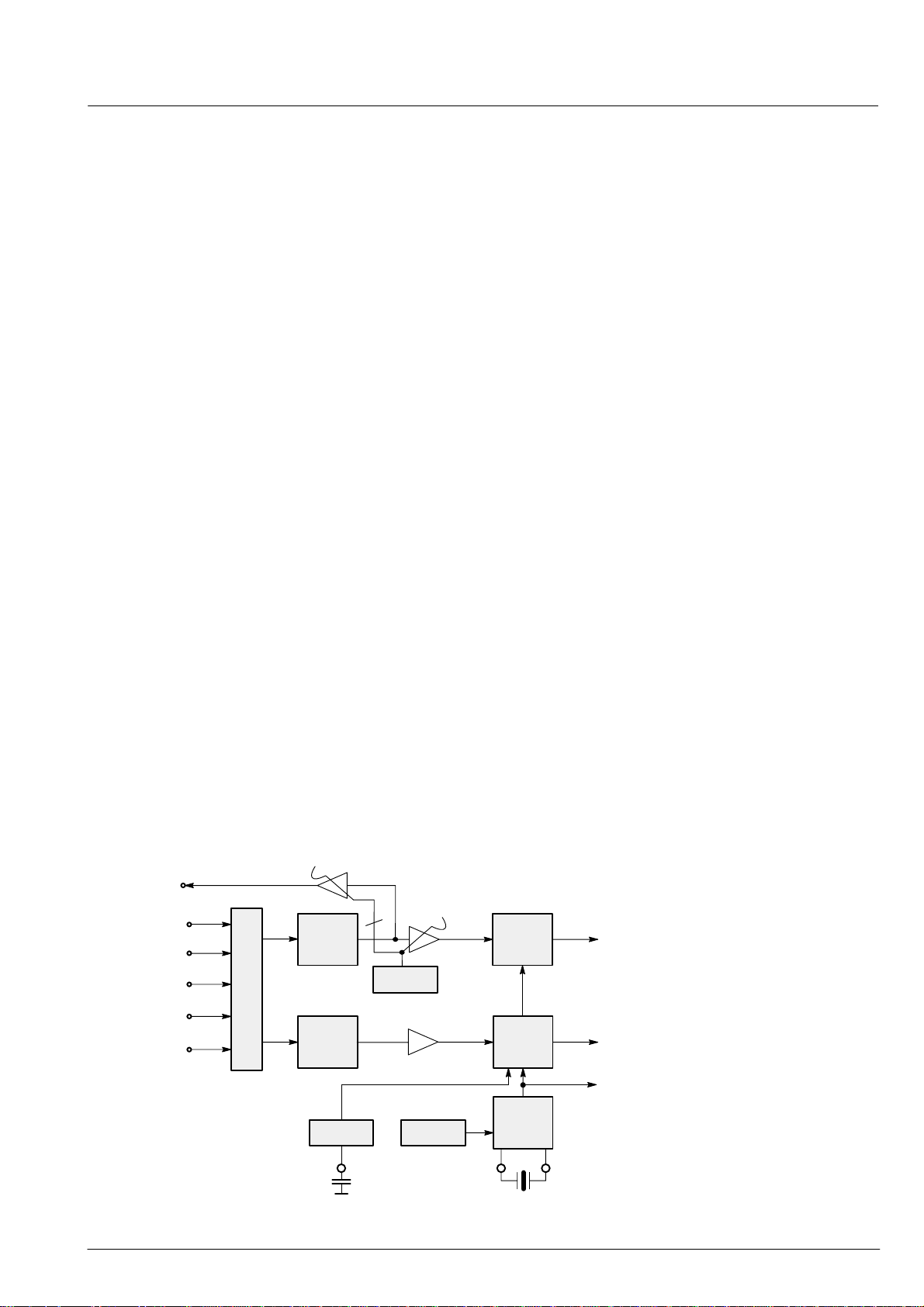

2.1. Analog Front-End

This block provides the analog interfaces to all video inputs and mainly carries out analog-to digital conversion

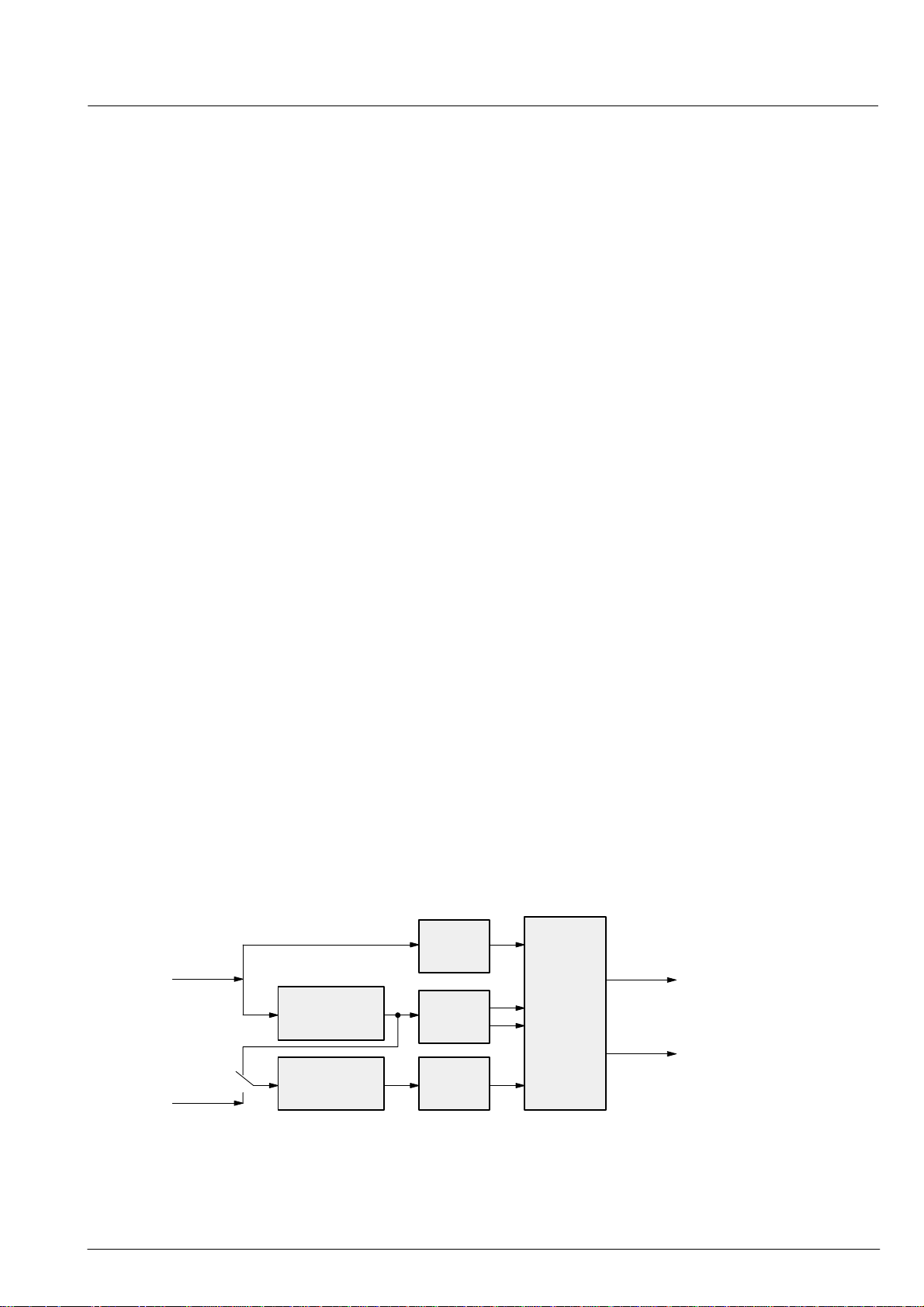

for the following digital video processing. A block diagram is given in Fig. 2–1.

Most of the functional blocks in the front-end are digitally

controlled (clamping, AGC, and clock-DCO). The control loops are closed by the Fast Processor (‘FP’) embedded in the decoder.

2.1.1. Input Selector

Up to five analog inputs can be connected. Four inputs

are for input of composite video or S-VHS luma signal.

These inputs are clamped to the sync back porch and

are amplified by a variable gain amplifier. One input is

for connection of S-VHS carrier-chrominance signal.

This input is internally biased and has a fixed gain amplifier.

2.1.3. Automatic Gain Control

A digitally working automatic gain control adjusts the

magnitude of the selected baseband by +6/–4.5 dB in 64

logarithmic steps to the optimal range of the ADC. The

gain of the video input stage including the ADC is 213

steps/V with the AGC set to 0 dB.

2.1.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals.

Each converter runs with 20.25 MHz and has 8 bit resolution. An integrated bandgap circuit generates the required reference voltages for the converters.

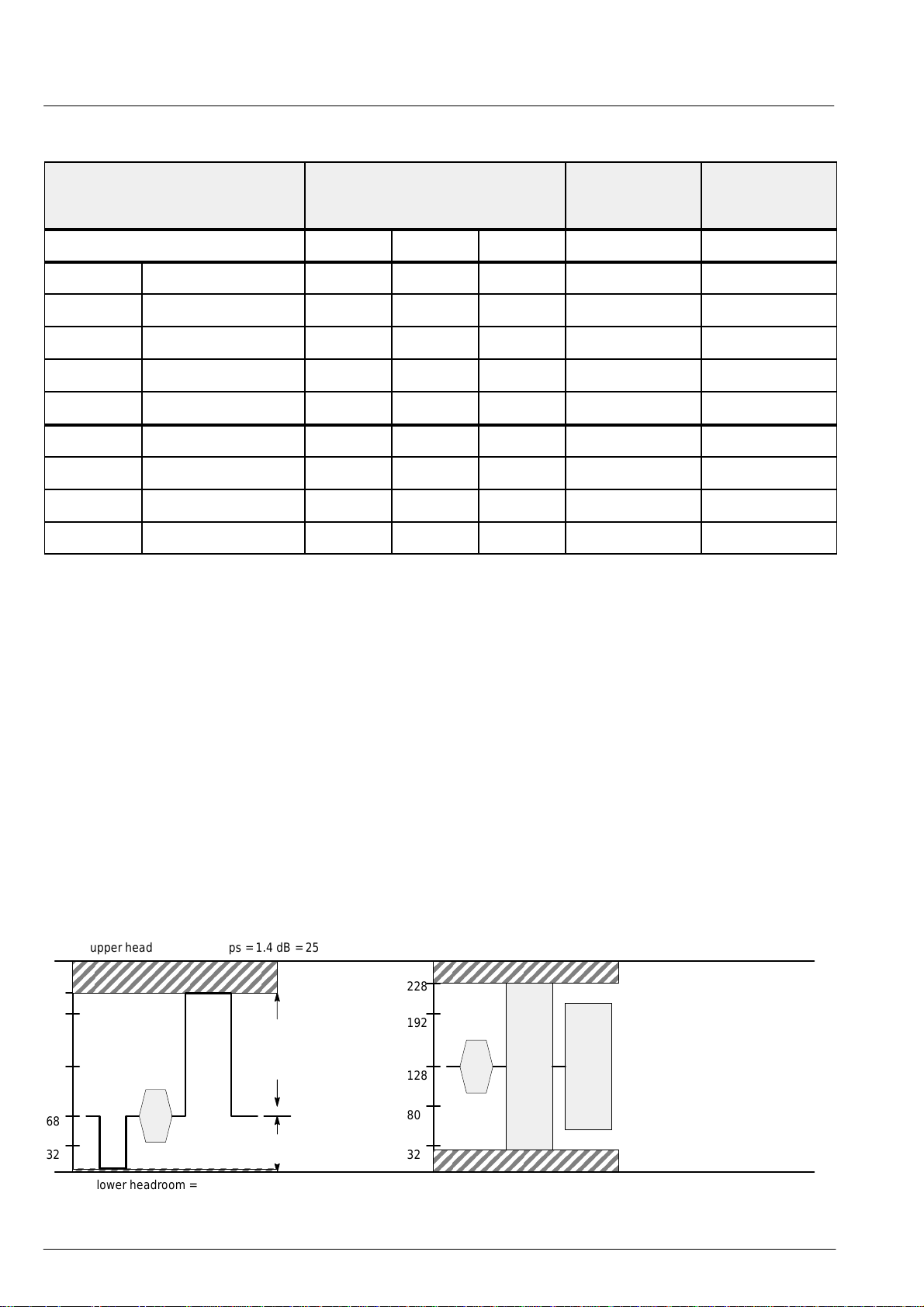

2.1.5. ADC Range

The ADC input range for the various input signals and

the digital representation is given in Table 2–1 and Fig.

2–2. The corresponding output signal levels of the

VDP 31xxB are also shown.

2.1.6. Digitally Controlled Clock Oscillator

2.1.2. Clamping

The composite video input signals are AC coupled to the

IC. The clamping voltage is stored on the coupling capacitors and is generated by digitally controlled current

sources. The clamping level is the back porch of the video signal. S-VHS chroma is also AC coupled. The input

pin is internally biased to the center of the ADC input

range.

Analog Video

Output

CVBS/Y

CVBS/Y

CVBS/Y

CVBS/Y/C

Chroma

VIN4

VIN3

VIN2

mux

VIN1

CIN digital Chroma

input

clamp

bias

3

gain

AGC

+6/–4.5 dB

The clock generation is also a part of the analog front

end. The crystal oscillator is controlled digitally by the

control processor; the clock frequency can be adjusted

within ±150 ppm.

2.1.7. Analog Video Output

The input signal of the Luma ADC is available at the analog video output pin. The signal at this pin must be buffered by a source follower. The output voltage is 2 V , thus

the signal can be used to drive a 75 W line. The magnitude is adjusted with an AGC in 8 steps together with the

main AGC.

ADC

ADC

digital CVBS or Luma

Fig. 2–1: Analog front-end

reference

generation

frequency

system clocks

DVCO

±150

ppm

20.25 MHz

7Micronas

VDP 31xxB PRELIMINARY DATA SHEET

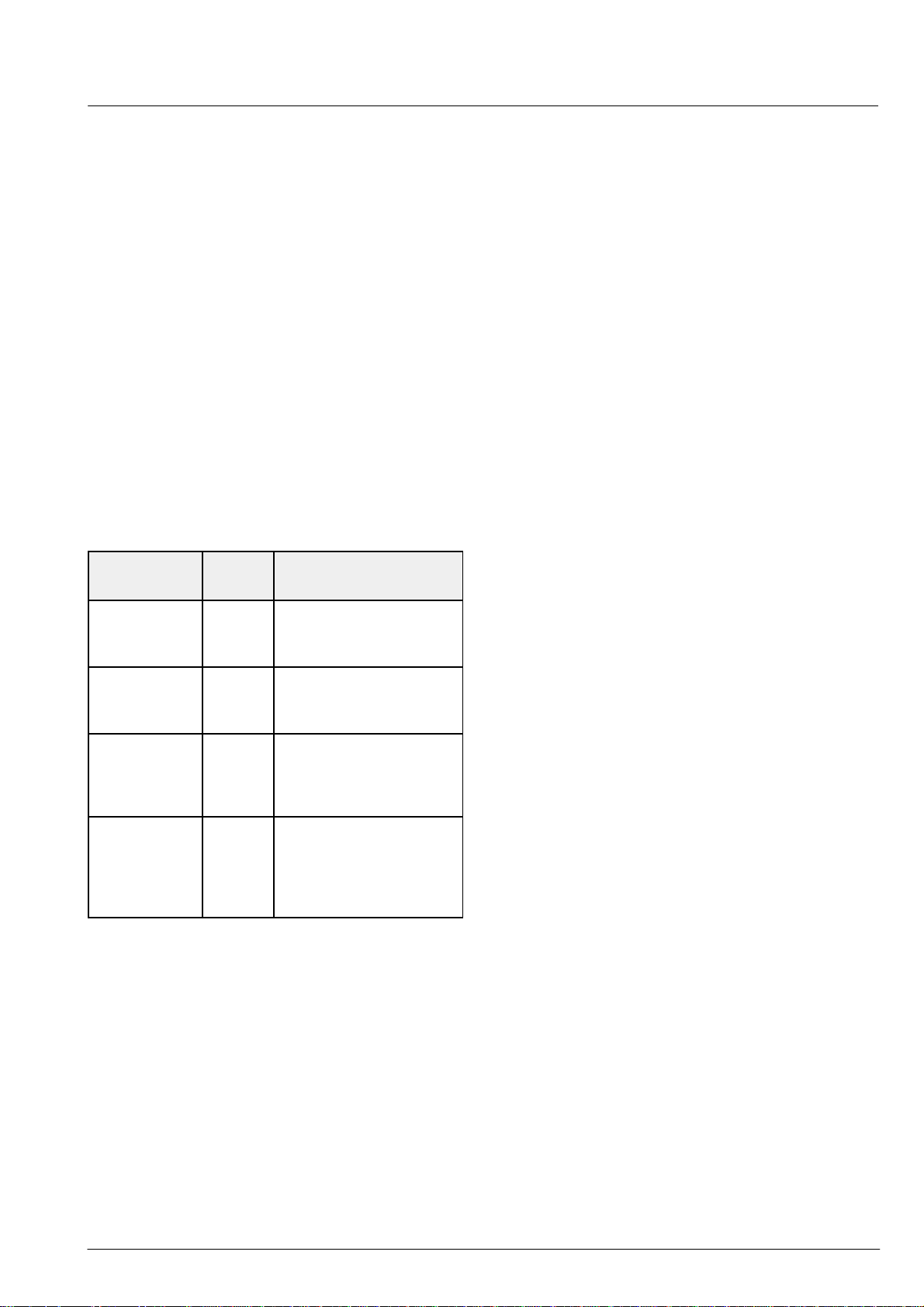

Table 2–1: ADC input range for PAL input signal and corresponding signal ranges

Signal Input Level [mVpp] ADC

Range

YCrC

b

Internal

Range

–6 dB 0 dB +4.5 dB [steps] [steps]

CVBS 100% CVBS 667 1333 2238 252 –

75% CVBS 500 1000 1679 213 –

video (luma) 350 700 1175 149 224

sync height 150 300 504 64 –

clamp level 68 16

Chroma burst 300 64 –

100% Chroma 890 190 128±112

75% Chroma 670 143 128±84

bias level 128 128

CVBS/Y Chroma

upper headroom = 38 steps = 1.4 dB = 25 IRE

255

217

192

128

68

32

0

lower headroom = 4 steps = 0.2 dB

white

black

= clamp

level

video = 100 IRE

sync = 41 IRE

headroom = 56 steps = 2.1 dB

228

100% Chroma

192

burst

128

80

32

75% Chroma

Fig. 2–2: ADC ranges for CVBS/Luma and Chroma, PAL input signal

8 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

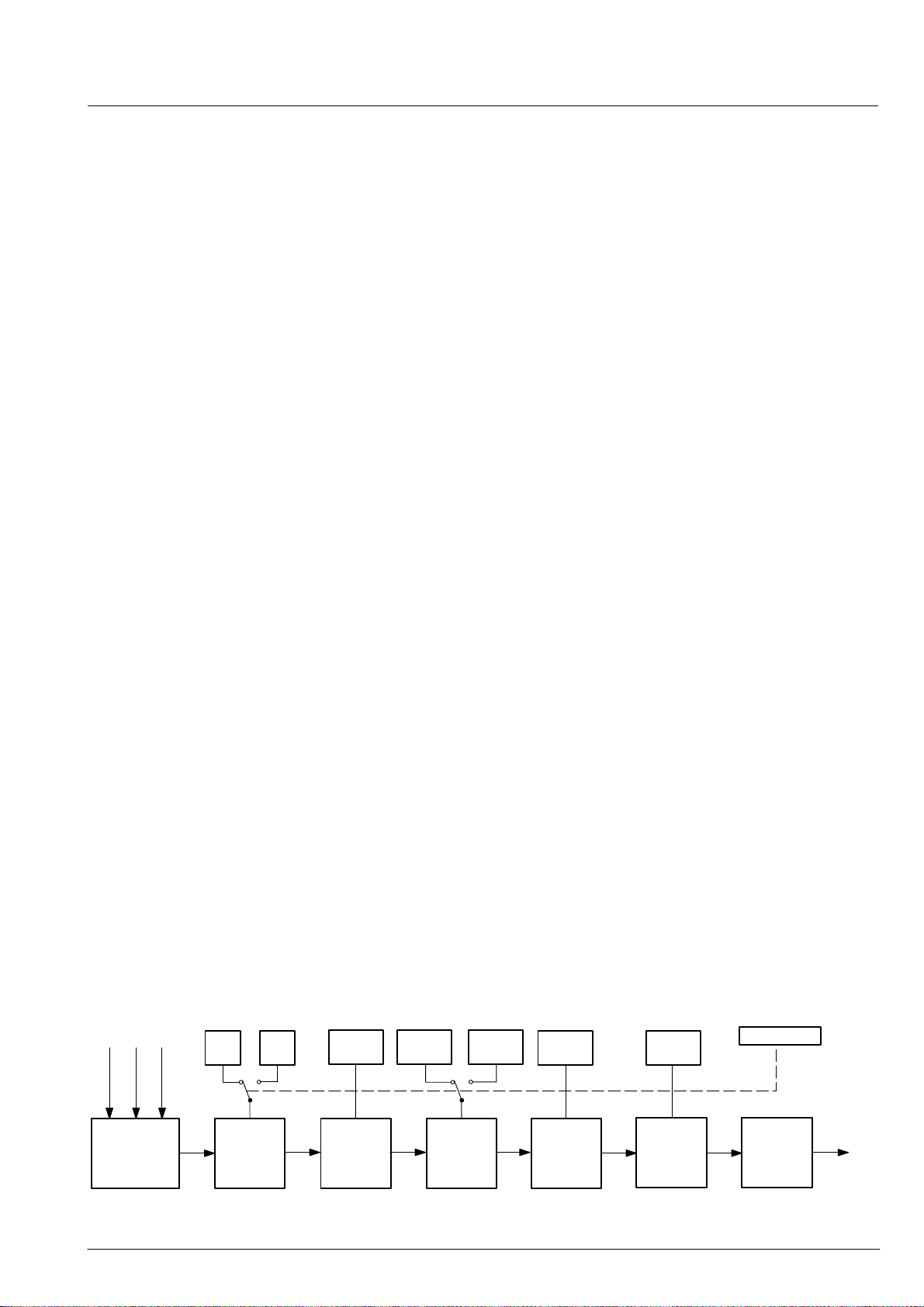

2.2. Adaptive Comb Filter

The adaptive comb filter is used for high-quality luminance/chrominance separation for PAL or NTSC signals. The comb filter improves the luminance resolution

(bandwidth) and reduces interferences like cross-luminance and cross-color artifacts. The adaptive algorithm

can eliminate most of the mentioned errors without

introducing new artifacts or noise.

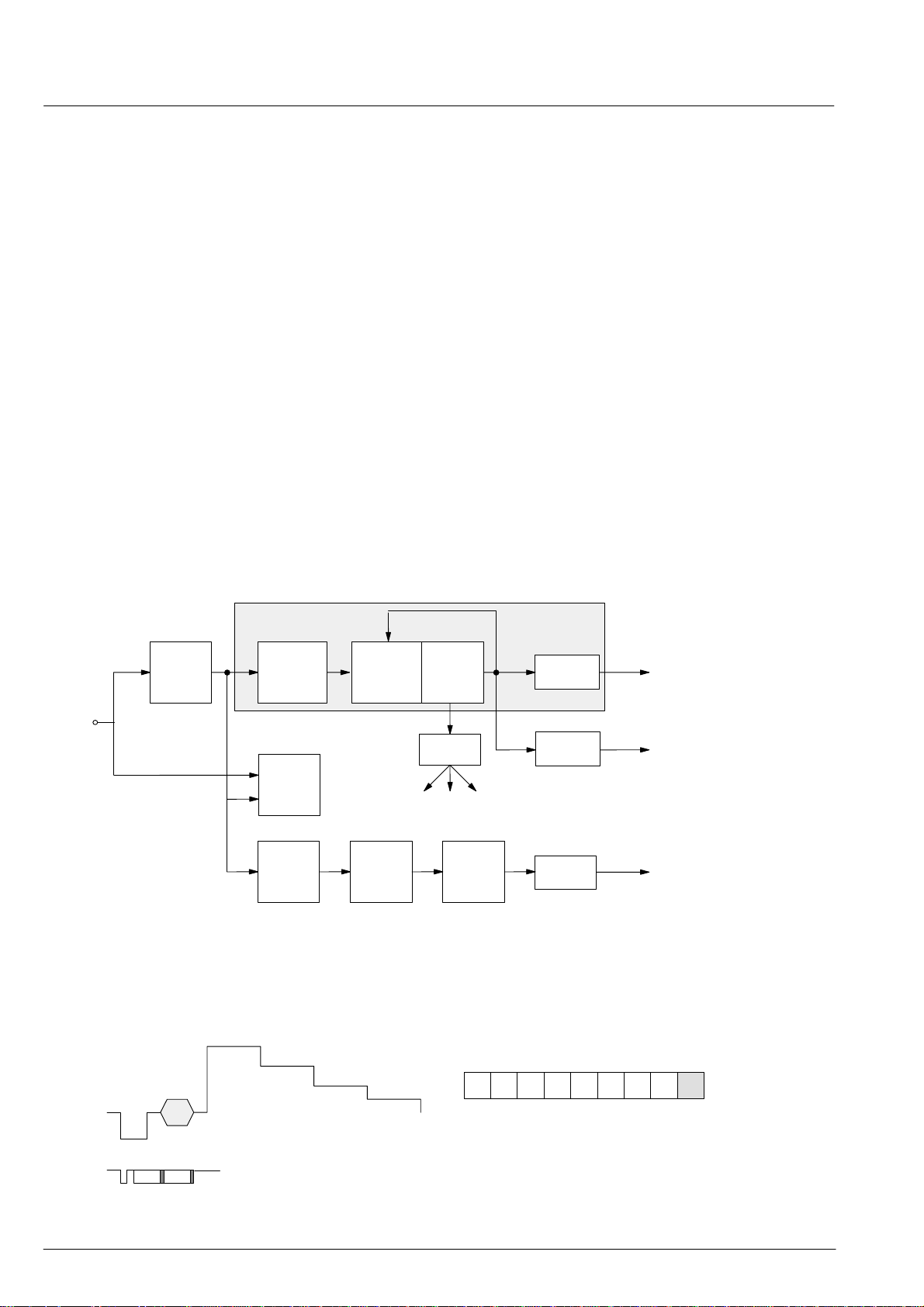

A block diagram of the comb filter is shown in Fig. 2–3.

The filter uses two line delays to process the information

of three adjacent video lines. T o have a fixed phase relationship of the color subcarrier in the three channels, the

system clock (20.25 MHz) is fractionally locked to the

color subcarrier. This allows the processing of all color

standards and substandards using a single crystal frequency.

The CVBS signal in the three channels is filtered at the

subcarrier frequency by a set of bandpass/notch filters.

The output of the three channels is used by the adaption

logic to select the weighting that is used to reconstruct

the luminance/chrominance signal from the 4 bandpass/

notch filter signals. By using soft mixing of the 4 signals

switching artifacts of the adaption algorithm are completely suppressed.

The comb filter uses the middle line as reference, therefore, the comb filter delay is one line. If the comb filter is

switched off, the delay lines are used to pass the luma/

chroma signals from the A/D converters to the luma/

chroma outputs. Thus, the comb filter delay is always

one line.

Various parameters of the comb filter are adjustable,

hence giving to the user the ability to adjust his own desired picture quality.

Two parameters (KY, KC) set the global gain of luma and

chroma comb separately; these values directly weigh

the adaption algorithm output. In this way, it is possible

to obtain a luma/chroma separation ranging from standard notch/bandpass to full comb decoding.

The parameter KB allows to choose between the two

proposed comb booster modes. This so-called feature

widely improves vertical high to low frequency transitions areas, the typical example being a multiburst to dc

change. For KB=0, this improvement is kept moderate,

whereas, in case of KB=1, it is maximum, but the risk to

increase the “hanging dots” amount for some given color

transitions is higher.

Using the default setting, the comb filter has separate

luma and chroma decision algorithms; it is however possible to switch the chroma comb factor to the current

luma adaption output by setting CC to 1.

Another interesting feature is the programmable limitation of the luma comb amount; proper limitation,

associated to adequate luma peaking, gives rise to an

enhanced 2-D resolution homogeneity . This limitation is

set by the parameter CLIM, ranging from 0 (no limitation)

to 31 (max. limitation).

The DAA parameter (1:off , 0:on) is used to disable/enable a very efficient built-in “rain effect” suppressor;

many comb filters show this side effect which gives

some vertical correlation to a 2-D uniform random area,

due to the vertical filtering. This unnatural-looking phenomenon is mostly visible on tuner images, since they

are always corrupted by some noise; and this looks like

rain.

CVBS Input

1 H Line Delay

1 H Line Delay

Chroma Input

Fig. 2–3: Block diagram of the adaptive comb filter

Bandpass

Filter

Bandpass/

Notch

Filter

Bandpass

Filter

Luma / Chroma Mixers

Adaption Logic

Luma Output

Chroma Output

9Micronas

VDP 31xxB PRELIMINARY DATA SHEET

2.3. Color Decoder

In this block, the standard luma/chroma separation and

multi-standard color demodulation is carried out. The

color demodulation uses an asynchronous clock, thus

allowing a unified architecture for all color standards.

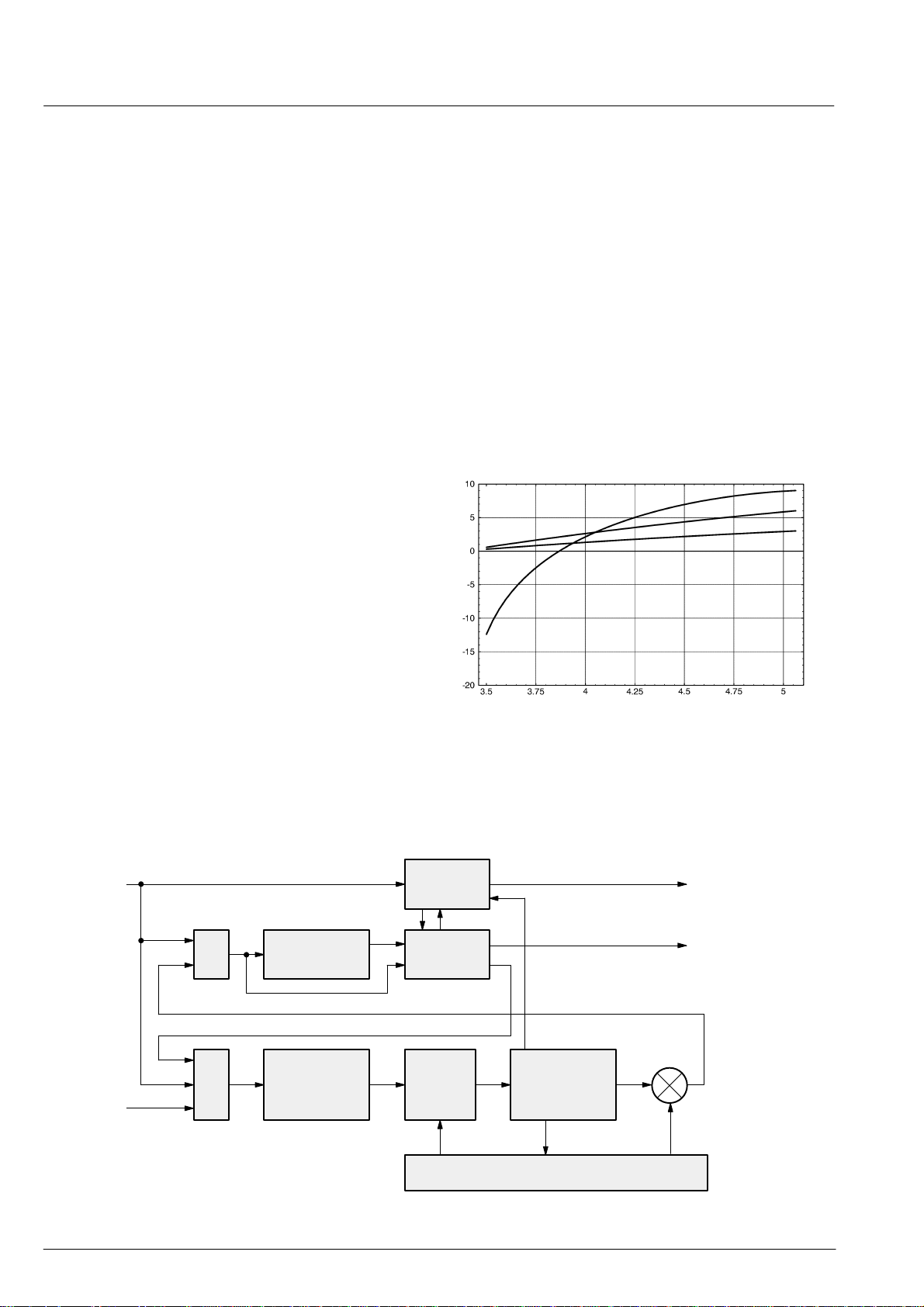

A block diagram of the color decoder is shown in Fig.

2–5. The luma as well as the chroma processing, is

shown here. The color decoder provides also some special modes, e.g. wide band chroma format which is intended for S-VHS wide bandwidth chroma.

If the adaptive comb filter is used for luma chroma separation, the color decoder uses the S-VHS mode processing. The output of the color decoder is YC

in a 4:2:2

rCb

format.

2.3.1. IF-Compensation

With off-air or mistuned reception, any attenuation at

higher frequencies or asymmetry around the color subcarrier is compensated. Four different settings of the IFcompensation are possible:

– flat (no compensation)

– 6 dB/octave

– 12 dB/octave

– 10 dB/MHz

The last setting gives a very large boost to high frequencies. It is provided for SECAM signals that are decoded

using a SAW filter specified originally for the PAL standard.

Luma / CVBS

Chroma

MUXMUX

1 H Delay

IF Compensation

DC-Reject

Fig. 2–4: Frequency response of chroma

IF-compensation

Notch

Filter

Cross-Switch

MIXER

Lowpass Filter

Phase/Freq

Demodulator

Color-PLL/Color-ACC

ACC

Luma

Chroma /CrC

b

Fig. 2–5: Color decoder

10 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

2.3.2. Demodulator

The entire signal (which might still contain luma) is now

quadrature-mixed to the baseband. The mixing frequency is equal to the subcarrier for PAL and NTSC, thus

achieving the chroma demodulation. For SECAM, the

mixing frequency is 4.286 MHz giving the quadrature

baseband components of the FM modulated chroma.

After the mixer, a lowpass filter selects the chroma components; a downsampling stage converts the color difference signals to a multiplexed half rate data stream.

The subcarrier frequency in the demodulator is generated by direct digital synthesis; therefore, substandards

such as PAL 3.58 or NTSC 4.43 can also be demodulated.

2.3.3. Chrominance Filter

The demodulation is followed by a lowpass filter for the

color difference signals for P AL/NTSC. SECAM requires

a modified lowpass function with bell-filter characteristic.

At the output of the lowpass filter, all luma information is

eliminated.

The lowpass filters are calculated in time multiplex for

the two color signals. Three bandwidth settings (narrow,

normal, broad) are available for each standard. For P AL/

NTSC, a wide band chroma filter can be selected. This

filter is intended for high bandwidth chroma signals, e.g.

a nonstandard wide bandwidth S-VHS signal.

2.3.4. Frequency Demodulator

The frequency demodulator for demodulating the SECAM signal is implemented as a CORDIC-structure. It

calculates the phase and magnitude of the quadrature

components by coordinate rotation.

The phase output of the CORDIC processor is differentiated to obtain the demodulated frequency. After the

deemphasis filter, the Dr and Db signals are scaled to

standard C

amplitudes and fed to the crossover-

rCb

switch.

2.3.5. Burst Detection

In the PAL/NTSC-system the burst is the reference for

the color signal. The phase and magnitude outputs of

the CORDIC are gated with the color key and used for

controlling the phase-lock-loop (APC) of the demodulator and the automatic color control (ACC) in P AL/NTSC.

The ACC has a control range of +30...–6 dB.

For SECAM decoding, the frequency of the burst is measured. Thus, the current chroma carrier frequency can

be identified and is used to control the SECAM processing. The burst measurements also control the color killer operation; they can be used for automatic standard

detection as well.

2.3.6. Color Killer Operation

The color killer uses the burst-phase / burst-frequency

measurement to identify a PAL/NTSC or SECAM color

signal. For PAL/NTSC, the color is switched off (killed)

as long as the color subcarrier PLL is not locked. For SECAM, the killer is controlled by the toggle of the burst frequency. The burst amplitude measurement is used to

switch-off the color if the burst amplitude is below a programmable threshold. Thus, color will be killed for very

noisy signals. The color amplitude killer has a programmable hysteresis.

PAL/NTSC

SECAM

Fig. 2–6: Frequency response of chroma filters

2.3.7. PAL Compensation/1-H Comb Filter

The color decoder uses one fully integrated delay line.

Only active video is stored.

The delay line application depends on the color standard:

– NTSC: 1-H comb filter or color compensation

– PAL: color compensation

– SECAM: crossover-switch

In the NTSC compensated mode, Fig. 2–7 c), the color

signal is averaged for two adjacent lines. Thus, crosscolor distortion and chroma noise is reduced. In the

NTSC combfilter mode, Fig. 2–7 d), the delay line is in

the composite signal path, thus allowing reduction of

11Micronas

VDP 31xxB PRELIMINARY DATA SHEET

cross-color components, as well as cross-luminance.

The loss of vertical resolution in the luminance channel

is compensated by adding the vertical detail signal with

removed color information.

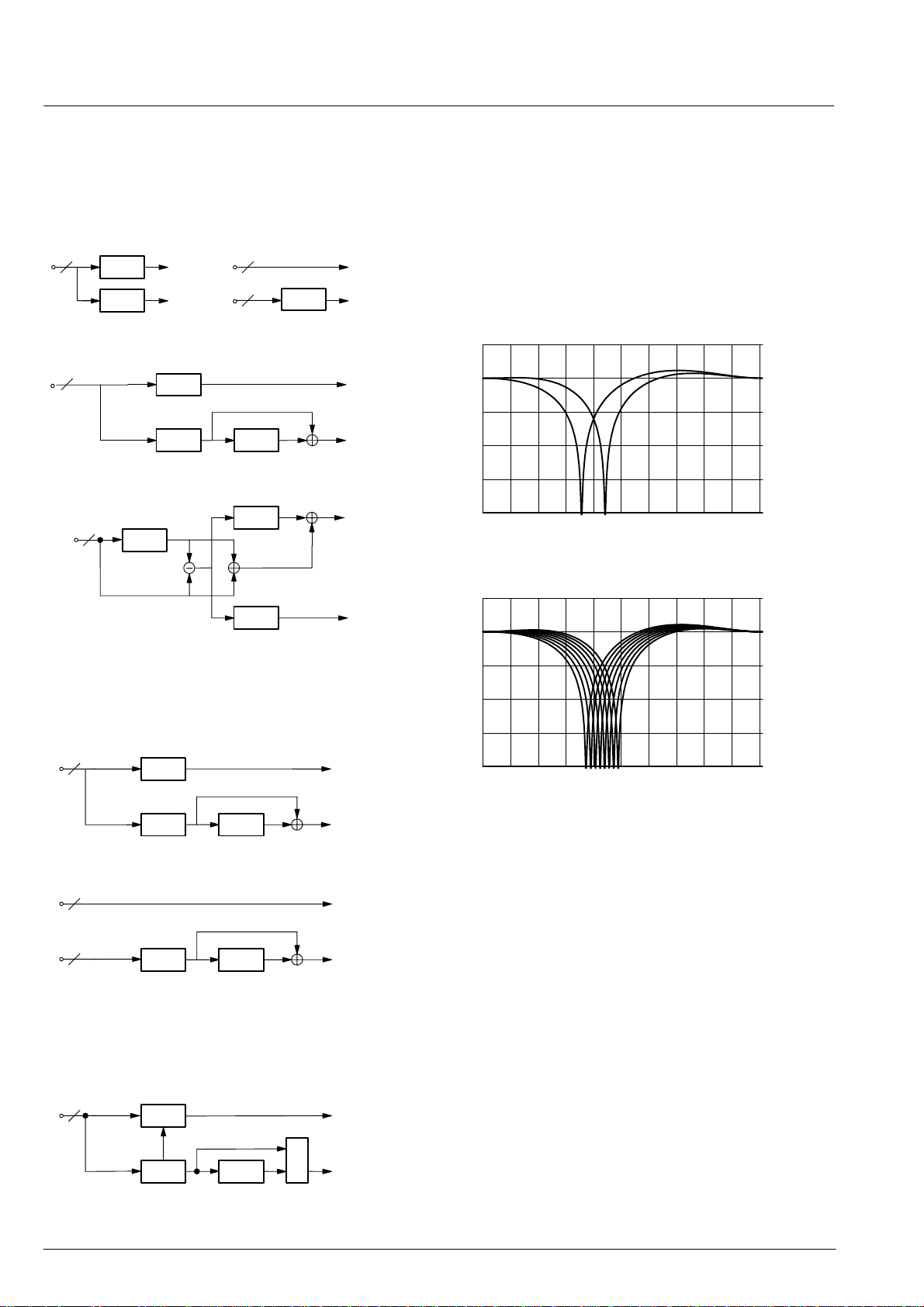

CVBS

8

Notch

filter

Chroma

Process.

Y

C C

r b

Luma

8

Chroma

8

Chroma

Process.

Y

C C

r b

a) conventional b) S-VHS

CVBS

8

Notch

filter

Chroma

Process.

1 H

Delay

Y

C C

r b

c) compensated

CVBS

Notch

1 H

8

Delay

filter

Y

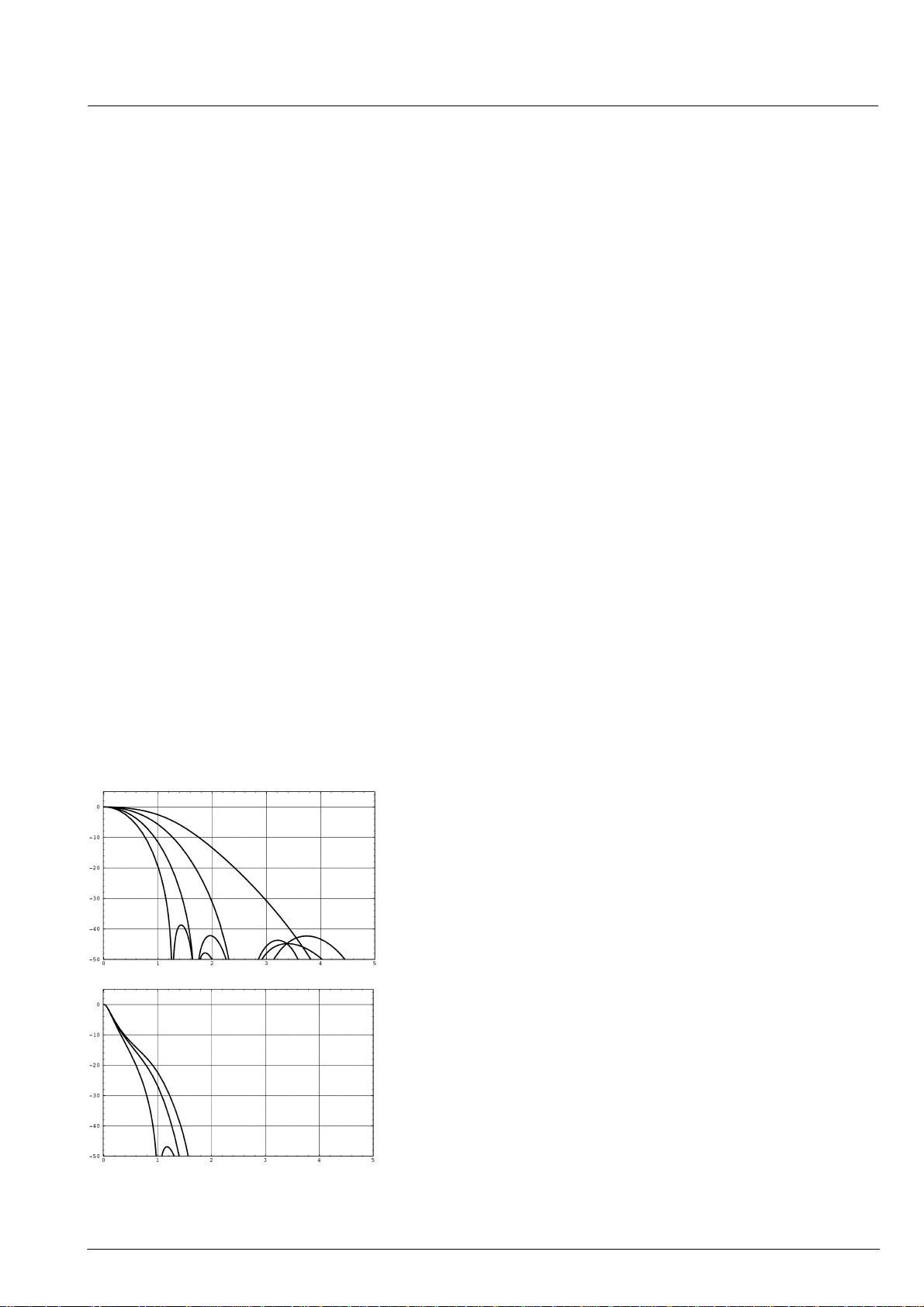

2.3.8. Luminance Notch Filter

If a composite video signal is applied, the color information is suppressed by a programmable notch filter. The

position of the filter center frequency depends on the

subcarrier frequency for PAL/NTSC. For SECAM, the

notch is directly controlled by the chroma carrier frequency. This considerably reduces the cross-luminance. The frequency responses for all three systems

are shown in Fig. 2–10.

dB

10

0

–10

–20

–30

–40

024 68 10

MHz

PAL/NTSC notch filter

Chroma

Process.

d) comb filter

Fig. 2–7: NTSC color decoding options

CVBS

8

Notch

filter

Chroma

Process.

1 H

Delay

a) conventional

Luma

8

Chroma

8

Chroma

Process.

1 H

Delay

b) S-VHS

Fig. 2–8: PAL color decoding options

CVBS

8

Notch

filter

Chroma

Process.

1 H

Delay

MUX

Fig. 2–9: SECAM color decoding

C C

Y

C C

r b

Y

C C

r b

Y

C C

r b

r b

dB

10

0

–10

–20

–30

–40

024 68 10

MHz

SECAM notch filter

Fig. 2–10: Frequency responses of the luma

notch filter for PAL, NTSC, and SECAM

2.3.9. Skew Filtering

The system clock is free-running and not locked to the

TV line frequency . Therefore, the ADC sampling pattern

is not orthogonal. The decoded YC

signals are con-

rCb

verted to an orthogonal sampling raster by the skew filters, which are part of the scaler block.

The skew filters allow the application of a group delay to

the input signals without introducing waveform or frequency response distortion.

The amount of phase shift of this filter is controlled by the

horizontal PLL1. The accuracy of the filters is 1/32

clocks for luminance and 1/4 clocks for chroma. Thus

the 4:2:2 YC

data is in an orthogonal pixel format

rCb

even in the case of nonstandard input signals such as

VCR.

12 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

2.4. Horizontal Scaler

The 4:2:2 YCrCb signal from the color decoder is processed by the horizontal scaler. The scaler block allows

a linear or nonlinear horizontal scaling of the input video

signal in the range of 0.25 to 4. Nonlinear scaling, also

called “panorama vision”, provides a geometrical distor-

tion of the input picture. It is used to fit a picture with 4:3

format on a 16:9 screen by stretching the picture geometry at the borders. Also, the inverse effect can be produced by the scaler. A summary of scaler modes is given

in Table 2–2.

The scaler contains a programmable decimation filter, a

1-line FIFO memory , and a programmable interpolation

filter. The scaler input filter is also used for pixel skew

correction, see 2.3.9. The decimator/interpolator structure allows optimal use of the FIFO memory. The controlling of the scaler is done by the internal Fast Processor.

Table 2–2: Scaler modes

Mode Scale

Description

Factor

Compression

4:3 → 16:9

0.75

linear

4:3 source displayed on a

16:9 tube,

with side panels

2.5. Black-Line Detector

In case of a letterbox format input video, e.g. Cinemascope, PAL+ etc., black areas at the upper and lower

part of the picture are visible. It is suitable to remove or

reduce these areas by a vertical zoom and/or shift operation.

The VDP 31xxB supports this feature by a letterbox detector. The circuitry detects black video lines by measuring the signal amplitude during active video. For every

field the number of black lines at the upper and lower

part of the picture are measured, compared to the previous measurement and the minima are stored in the

2

I

C-register BLKLIN. T o adjust the picture amplitude, the

external controller reads this register, calculates the vertical scaling coefficient and transfers the new settings,

e.g. vertical sawtooth parameters, horizontal scaling coefficient etc., to the VDP.

Letterbox signals containing logos on the left or right

side of the black areas are processed as black lines,

while subtitles, inserted in the black areas, are processed as non-black lines. Therefore the subtitles are

visible on the screen. T o suppress the subtitles, the vertical zoom coefficient is calculated by selecting the larger

number of black lines only . Dark video scenes with a low

contrast level compared to the letterbox area are indicated by the BLKPIC bit.

Panorama

4:3 → 16:9

Zoom

4:3 → 4:3

Panorama

4:3 → 4:3

nonlinear

compr

1.33

linear

nonlinear

zoom

4:3 source displayed on a

16:9 tube,

Borders distorted

Letterbox source (PAL+)

displayed on a 4:3 tube,

vertical overscan with

cropping of side panels

Letterbox source (PAL+)

displayed on a 4:3 tube,

vertical overscan, borders distorted, no cropping

2.6. Test Pattern Generator

The YCrCb outputs of the front-end can be switched to

a test mode where YCrCb data are generated digitally

in the VDP 31xxB. Test patterns include luma/chroma

ramps, flat fields and a pseudo color bar pattern.

13Micronas

VDP 31xxB PRELIMINARY DATA SHEET

2.7. Video Sync Processing

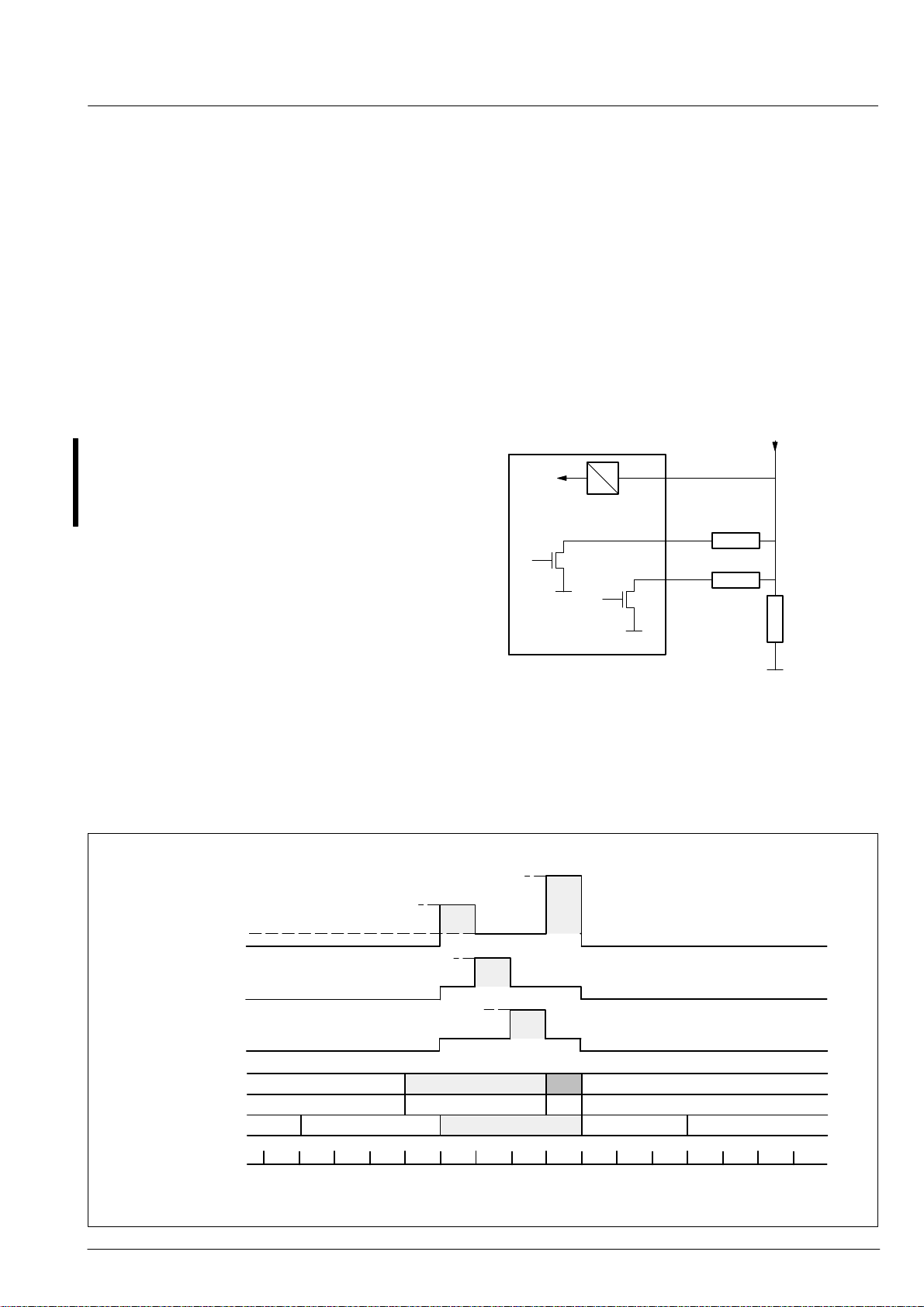

Fig. 2–11 shows a block diagram of the front-end sync

processing. To extract the sync information from the

video signal, a linear phase lowpass filter eliminates all

noise and video contents above 1 MHz. The sync is separated by a slicer; the sync phase is measured. A variable window can be selected to improve the noise immunity of the slicer. The phase comparator measures the

falling edge of sync, as well as the integrated sync pulse.

The sync phase error is filtered by a phase-locked loop

that is computed by the FP. All timing in the front-end is

derived from a counter that is part of this PLL, and it thus

counts synchronously to the video signal.

A separate hardware block measures the signal back

porch and also allows gathering the maximum/minimum

of the video signal. This information is processed by the

FP and used for gain control and clamping.

For vertical sync separation, the sliced video signal is integrated. The FP uses the integrator value to derive vertical sync and field information.

The information extracted by the video sync processing

is multiplexed onto the hardware front sync signal (FSY)

and is distributed to the rest of the video processing system. The format of the front sync signal is given in

Fig. 2–12.

The data for the vertical deflection, the sawtooth, and the

East-West correction signal is calculated by the

VDP 31xxB. The data is buffered in a FIFO and transferred to the back-end by a single wire interface.

Frequency and phase characteristics of the analog video signal are derived from PLL1. The results are fed to

the scaler unit for data interpolation and orthogonalization and to the clock synthesizer for line-locked clock

generation. Horizontal and vertical syncs are latched

with the line-locked clock.

video

input

lowpass

1 MHz

&

syncslicer

horizontal

sync

separation

clamp &

signal

meas.

vertical

sync

separation

Fig. 2–11: Sync separation block diagram

phase

comparator

&

lowpass

clamping, colorkey, FIFO_write

Sawtooth

Parabola

Calculation

counter

front-end

timing

FIFO

PLL1

generator

synthesizer

front

sync

clock

syncs

vertical

serial

data

front sync

skew

vblank

field

clock

H/V syncs

vertical

E/W

sawtooth

input

analog

video

FSY

skew skew

F1

LSB

F0 reserved

(not in scale)

F1

F0

MSB

not

used

FV

Parity

V: vertical sync

0 = off

1 = on

F: field #

0 = field 1

1 = field 2

Fig. 2–12: Front sync format

14 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

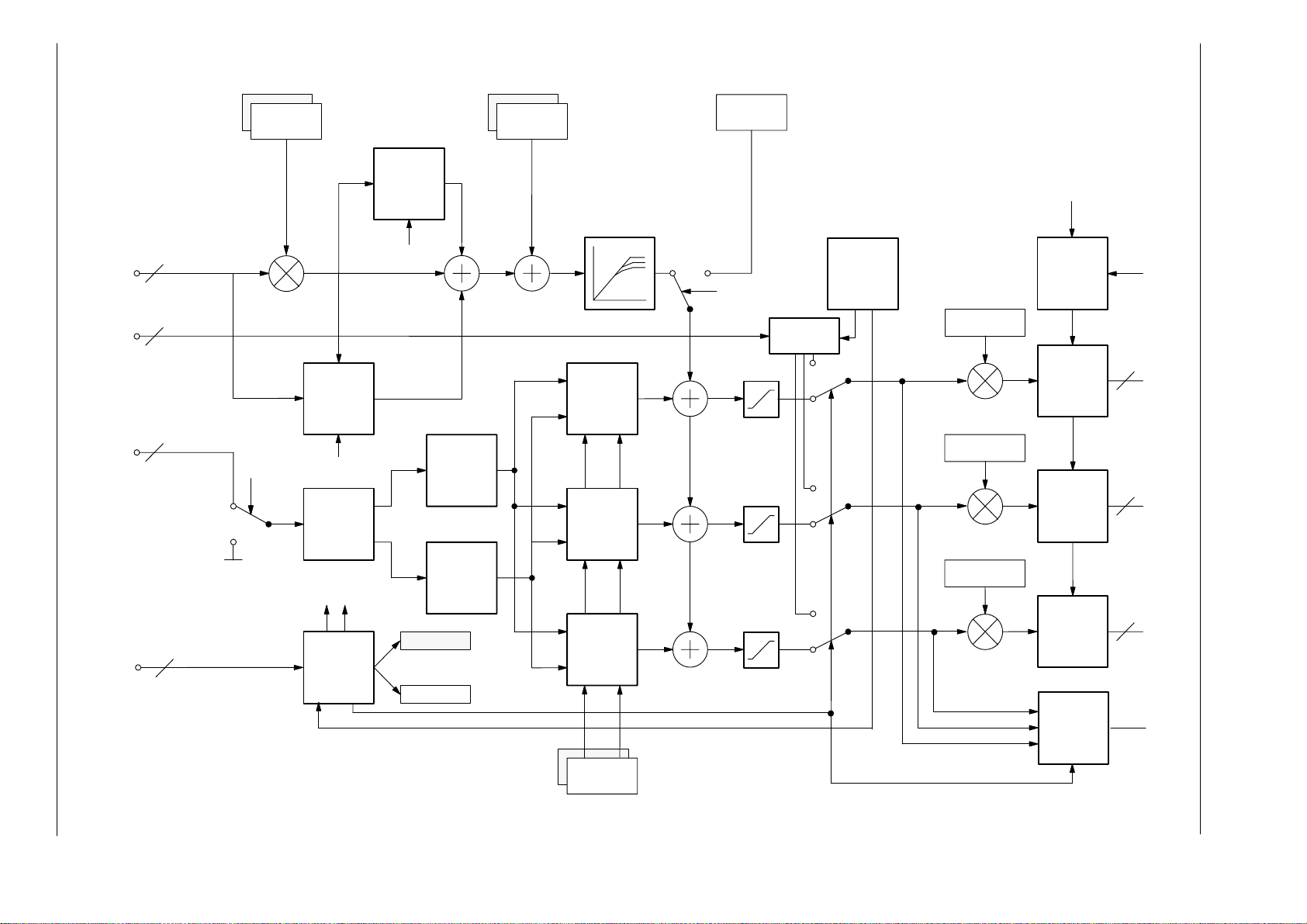

2.8. Display Part

In the display part the conversion from digital YCrCb to

analog RGB is carried out. A block diagram is shown in

Figure 2–20. In the luminance processing path, contrast

and brightness adjustments and a variety of features,

such as black level expansion, dynamic peaking and

soft limiting, are provided. In the chrominance path, the

C

signals are converted to 20.25 MHz sampling rate

rCb

and filtered by a color transient improvement circuit. The

YC

signals are converted by a programmable matrix

rCb

to RGB color space.

The display processor provides separate control settings for two pictures, i.e. different coefficients for a

‘main’ and a ‘side’ picture.

The digital OSD insertion circuit allows the insertion of

a 5-bit OSD signal. The color space for this signal is controlled by a partially programmable color look-up table

(CLUT) and contrast adjustment.

The OSD signals and the display clock are synchronized

to the horizontal flyback. For the display clock, a gate

delay phase shifter is used. In the analog backend, three

10-bit digital-to-analog converters provide the analog

output signals.

2.8.1. Luma Contrast Adjustment

The contrast of the luminance signal can be adjusted by

multiplication with a 6-bit contrast value. The contrast

value corresponds to a gain factor from 0 to 2, where the

value 32 is equivalent to a gain of 1. The contrast can be

adjusted separately for main picture and side picture.

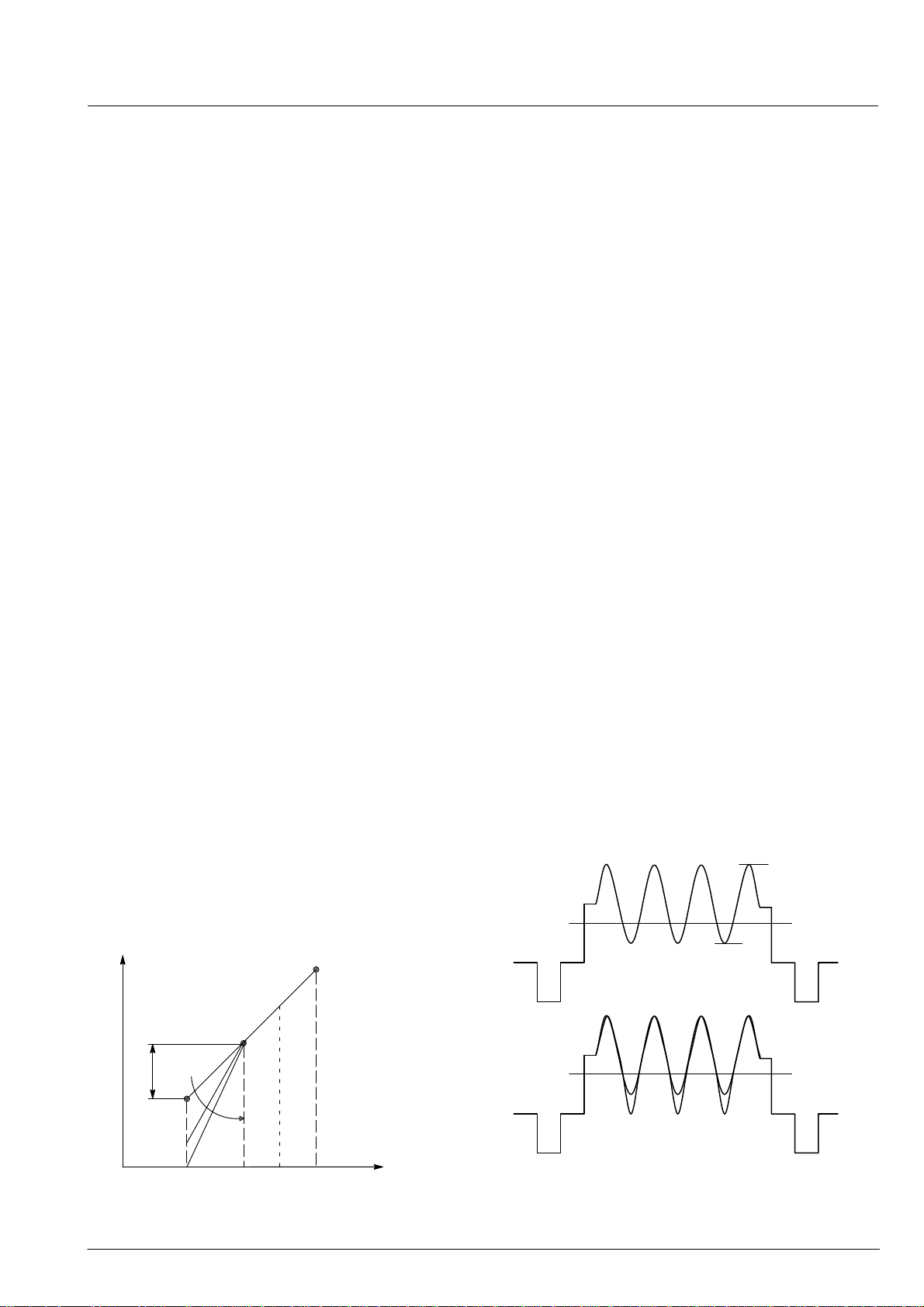

2.8.2. Black Level Expander

The black level expander enhances the contrast of the

picture. Therefore the luminance signal is modified with

an adjustable, non-linear function. Dark areas of the picture are changed to black, while bright areas remain unchanged. The advantage of this black level expander is

that the black expansion is performed only if it will be

most noticeable to the viewer.

The black level expander works adaptively. Depending

on the measured amplitudes ‘L

min

’ and ‘L

’ of the low-

max

pass-filtered luminance and an adjustable coefficient

BTLT, a tilt point ‘L

= L

L

t

’ is established by

t

+ BTLT (L

min

max

– L

min

).

Above this value there is no expansion, while all luminance values below this point are expanded according

to:

L

= Lin + BAM (Lin – Lt)

out

A second threshold, L

, can be programmed, above

tr

which there is no expansion. The characteristics of the

black level expander are shown in Fig. 2–13 and Fig.

2–14.

The tilt point L

is a function of the dynamic range of the

t

video signal. Thus, the black level expansion is only performed when the video signal has a large dynamic

range. Otherwise, the expansion to black is zero. This allows the correction of the characteristics of the picture

tube.

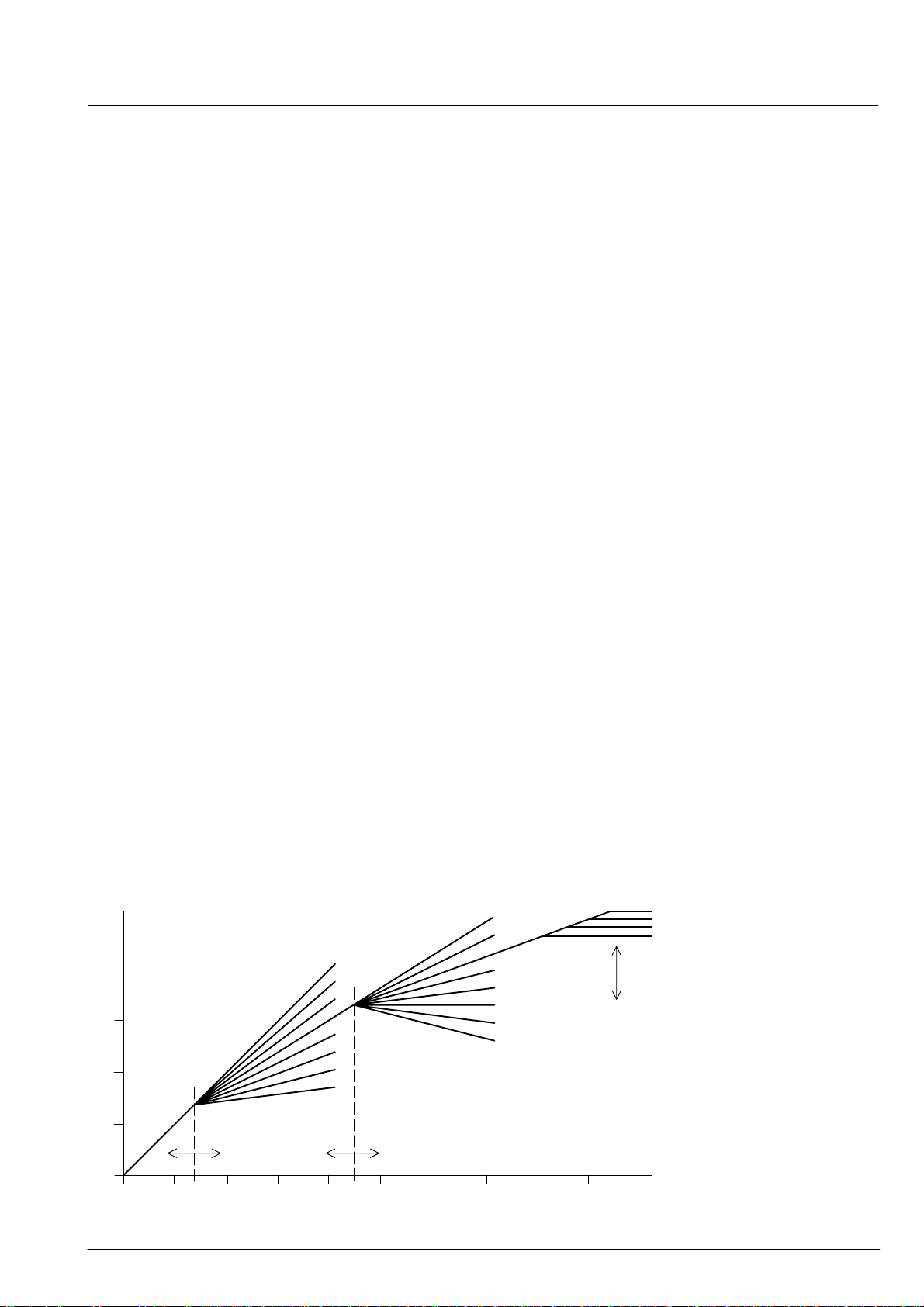

L

out

L

t

BAM

BTLT

L

min

L

tr

L

L

tr

BTHR

max

L

in

Fig. 2–13: Characteristics of the black level expander

a)

b)

Fig. 2–14: Black-level-expansion

a) luminance input

b) luminance input and output

L

max

L

t

L

min

L

t

15Micronas

PRELIMINARY DATA SHEETVDP 31xxB

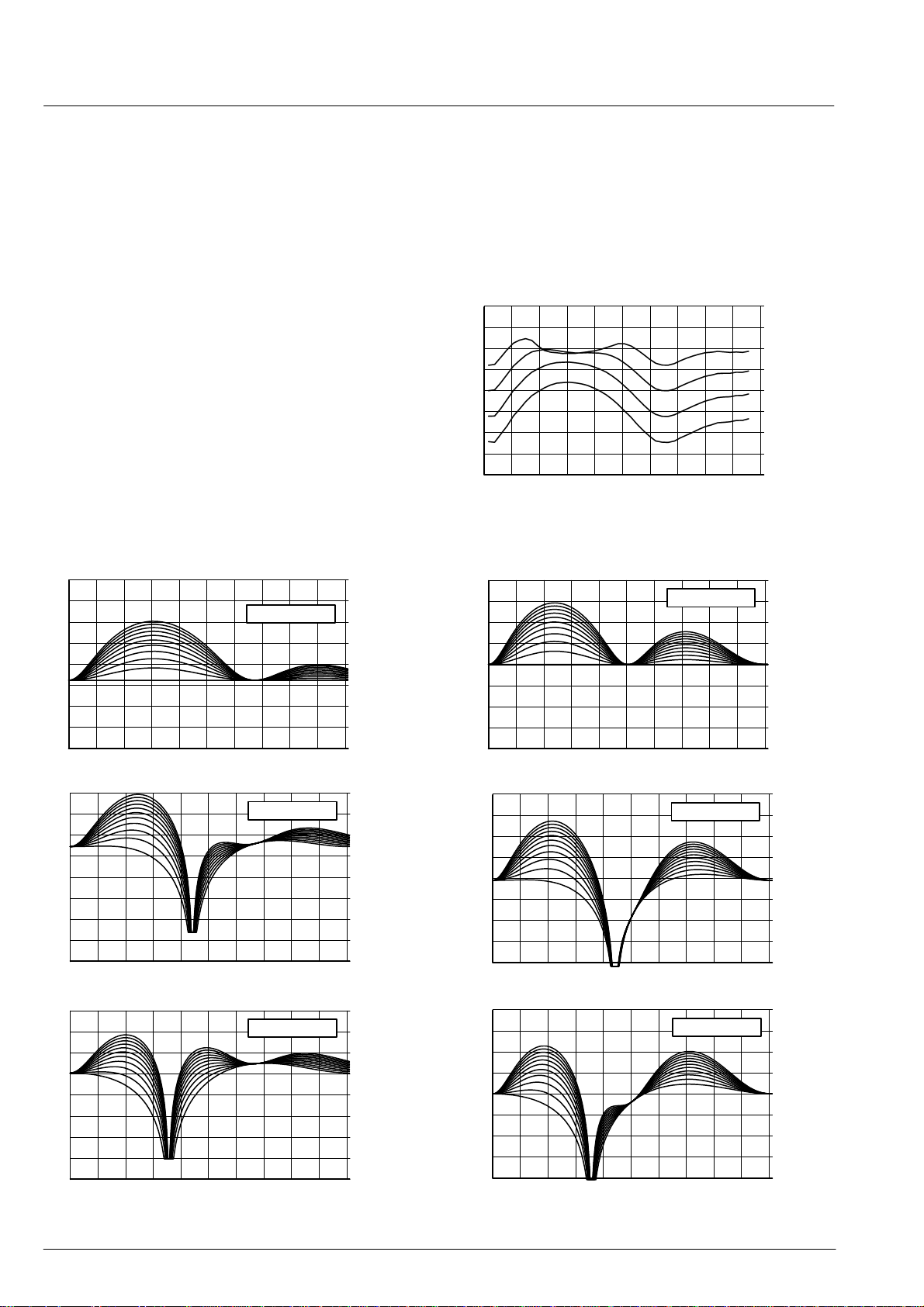

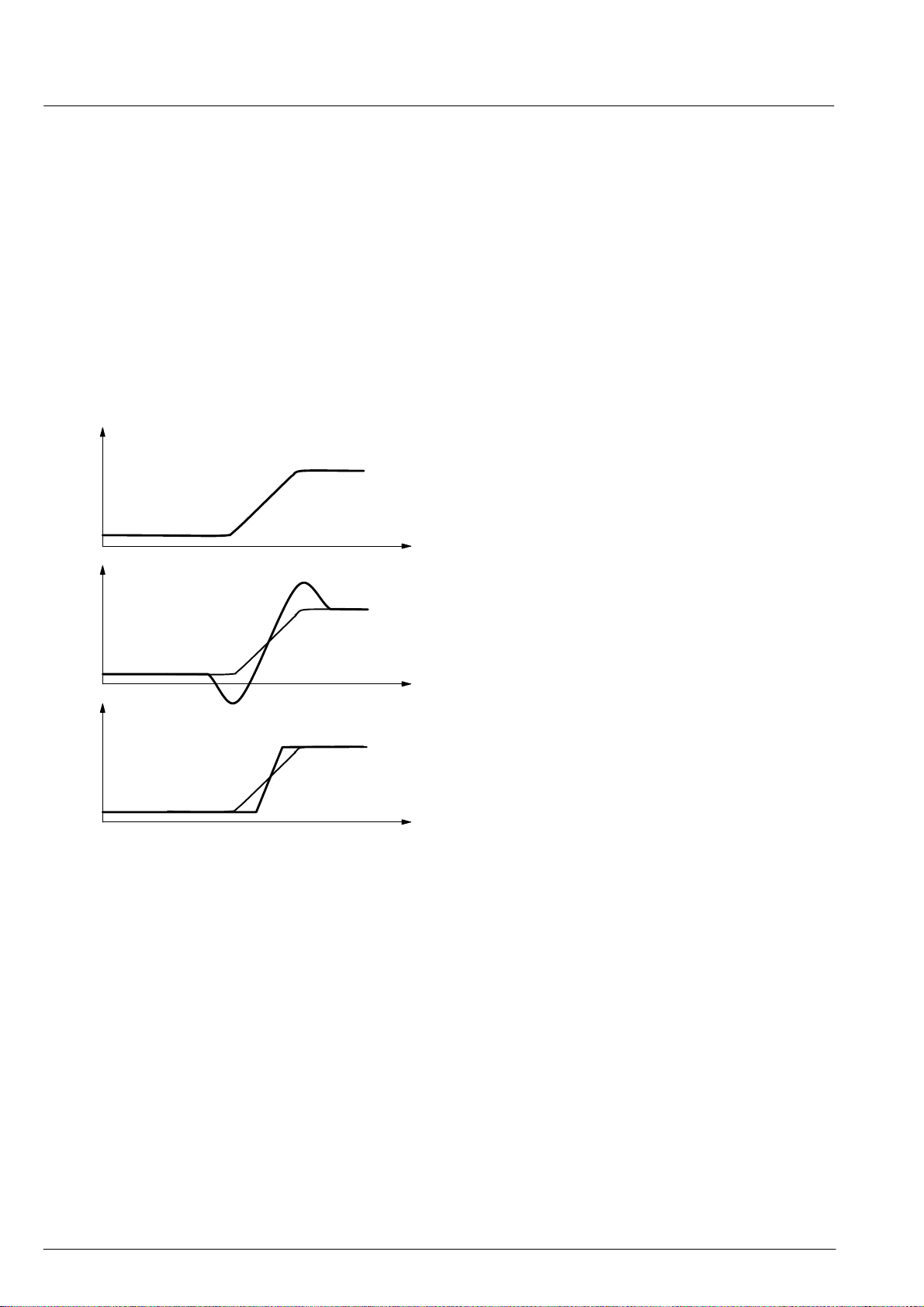

2.8.3. Dynamic Peaking

Especially with decoded composite signals and notch filter luminance separation, as input signals, it is necessary to improve the luminance frequency characteristics. With transparent, high-bandwidth signals, it is

sometimes desirable to soften the image.

In the VDP 31xxB, the luma response is improved by ‘dy-

namic’ peaking. The algorithm has been optimized regarding step and frequency response. It adapts to the

amplitude of the high frequency part. Small AC amplitudes are processed, while large AC amplitudes stay

nearly unmodified.

The dynamic range can be adjusted from *14 to

)14 dB for small high frequency signals. There is separate adjustment for signal overshoot and for signal undershoot. For large signals, the dynamic range is limited

by a non-linear function that does not create any visible

alias components. The peaking can be switched over to

“softening” by inverting the peaking term by software.

dB

20

15

10

5

0

–5

–10

–15

–20

024 68 10

CF= 3.2 MHz

S-VHS

MHz

The center frequency of the peaking filter is switchable

from 2.5 MHz to 3.2 MHz. For S-VHS and for notch filter

color decoding, the total system frequency responses

for both PAL and NTSC are shown in figure 2–16.

Transients, produced by the dynamic peaking when

switching video source signals, can be suppressed via

the priority bus.

dB

20

15

10

5

0

–5

–10

–15

–20

024 68 10

MHz

Fig. 2–15: Dynamic peaking frequency response

dB

20

15

10

5

0

–5

–10

–15

–20

024 68 10

CF= 2.5 MHz

MHz

dB

20

15

10

5

0

–5

–10

–15

–20

024 68 10

dB

20

15

10

5

0

–5

–10

–15

–20

024 68 10

CF= 3.2 MHz

CF= 3.2 MHz

PAL/SECAM

MHz

NTSC

MHz

dB

20

15

10

5

0

–5

–10

–15

–20

024 68 10

dB

20

15

10

5

0

–5

–10

–15

–20

024 68 10

Fig. 2–16: Total frequency response for peaking filter and S-VHS, PAL, NTSC

CF= 2.5 MHz

MHz

CF= 2.5 MHz

MHz

16 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

2.8.4. Digital Brightness Adjustment

The DC-level of the luminance signal can be adjusted by

adding an 8-bit number in the luminance signal path in

front of the softlimiter.

With a contrast adjustment of 32 (gain+1) the signal can

be shifted by "100%. After the brightness addition, the

negative going signals are limited to zero. It is desirable

to keep a small positive offset with the signal to prevent

undershoots produced by the peaking from being cut.

The digital brightness adjustment is separate for main

and side picture.

2.8.5. Soft Limiter

The dynamic range of the processed luma signal must

be limited to prevent the CRT from overload. An appropriate headroom for contrast, peaking and brightness

can be adjusted by the TV manufacturer according to the

CRT characteristics. All signals above this limit will be

‘soft’-clipped. A characteristic diagram of the soft limiter

is shown in Fig. 2–17. The total limiter consists of three

parts:

Part 1 includes adjustable tilt point and gain. The gain

before the tilt value is 1. Above the tilt value, a part

(0...15/16) of the input signal is subtracted from the input

signal itself. Therefore, the gain is adjustable from 16/16

to 1/16, when the slope value varies from 0 to 15. The

tilt value can be adjusted from 0 to 511.

Part 2 has the same characteristics as part 1. The subtracting part is also relative to the input signal, so the

total differential gain will become negative if the sum of

slope 1 and slope 2 is greater than 16 and the input signal is above the both tilt values (see characteristics).

Finally , the output signal of the soft limiter will be clipped

by a hard limiter adjustable from 256 to 511.

2.8.6. Chroma Input

The chroma input signal is a multiplexed C

and CB sig-

R

nal in 8-bit binary offset code. It can be switched between normal and inverted signal and between two’s

complement and binary offset code. The delay in respect to the luminance input can be adjusted in 5 steps

within a range of "2 clock periods.

2.8.7. Chroma Interpolation

A linear phase interpolator is used to convert the chroma

sampling rate from 10.125 MHz (4:2:2) to 20.25 MHz

(4:4:4). All further processing is carried out at the full

sampling rate.

511

400

300

200

100

0

Output

0

tilt 1 [ 0...511]

100 200 300

Part 1 Part 2 Hard limiter

0

slope 1 [0...15]

0

2

4

6

8

10

12

14

tilt 2 [0...511]

400 500

600 700 800

2

4

6

8

10

12

14

slope 2 [0...15]

Fig. 2–17: Characteristic of soft limiter a and b and hard limiter

range= 256...511

900

1023

Calculation Example for the

Softlimiter Input Amplitude.

(The real signal processing in

the limiter is 2 bit more than

described here)

Y Input 16...235 (ITUR)

Black Level 16 (constant)

Contrast 63

Dig. Brightness 20

BLE off

Peaking off

Limiter input signal:

(Yin-Black Level)·Contr ./32 + Brightn.

(235–16) · 63/32 + 20 = 451

Limiter Input

17Micronas

PRELIMINARY DATA SHEETVDP 31xxB

2.8.8. Chroma Transient Improvement

The intention of this block is to enhance the chroma

resolution. A correction signal is calculated by differentiation of the color difference signals. The differentiation

can be selected according to the signal bandwidth, e.g.

for PAL/NTSC/SECAM or digital component signals,

respectively. The amplitude of the correction signal is

adjustable. Small noise amplitudes in the correction signal are suppressed by an adjustable coring circuit. To

eliminate ‘wrong colors’, which are caused by over and

undershoots at the chroma transition, the sharpened

chroma signals are limited to a proper value automatically.

a)

Cr in

Cb in

t

b)

Ampl.

t

2.8.9. Inverse Matrix

A 6-multiplier matrix transcodes the Cr and Cb signals

to R–Y, B–Y, and G–Y. The multipliers are also used to

adjust color saturation in the range of 0 to 2. The coefficients are signed and have a resolution of 9 bits. There

are separate matrix coefficients for main and side pictures. The matrix computes:

R–Y+MR1*Cb)MR2*Cr

G–Y+MG1*Cb)MG2*Cr

B–Y+MB1*Cb)MB2*Cr

The initialization values for the matrix are computed

from the standard ITUR (CCIR) matrix:

Ǔ

Y

Cb

Cr

1

1

* 0.345

1

0

1.773

R

G

+

ǒ

B

For a contrast setting of CTM+32, the matrix values are

scaled by a factor of 64, see also table 3–1.

2.8.10. RGB Processing

After adding the post-processed luma, the digital RGB

signals are limited to 10 bits. Three multipliers are used

to digitally adjust the white drive. Using the same multipliers an average beam current limiter is implemented.

See also section 2.9.1. ‘CRT Measurement and Con-

trol’.

1.402

* 0.713

0

c)

Cr out

Cb out

a) Cr Cb input of DTI

b) Cr Cb input)Correction signal

c) sharpened and limited Cr Cb

Fig. 2–18: Digital Color Transient Improvement

2.8.11. OSD Color Lookup Table

The VDP 31xxB has five input lines for an OSD signal.

This signal forms a 5-bit address for a color look-up table

t

(CLUT). The CLUT is a memory with 32 words where

each word holds a RGB value.

Bits 0 to 3 (bit 4+0) form the addresses for the ROM part

of the OSD, which generates full RGB signals (bit 0 to 2)

and half-contrast RGB signals (bit 3).

Bit 4 addresses the RAM part of the OSD with 16 freely

programmable colors, addressable with bit 0 to 3. The

programming is done via the I

The amplitude of the CLUT output signals can be adjusted separately for R, G and B via the I2C-bus. The

switchover between video RGB and OSD RGB is done

via the Priority bus.

2

C-bus.

18 Micronas

PRELIMINARY DATA SHEET VDP 31xxB

2.8.12. Picture Frame Generator

When the picture does not fill the total screen (height or

width too small) it is surrounded with black areas. These

areas (and more) can be colored with the picture frame

generator. This is done by switching over the RGB signal

from the matrix to the signal from the OSD color look-up

table.

The width of each area (left, right, upper, lower) can be

adjusted separately. The generator starts on the right,

respectively lower side of the screen and stops on the

left, respectively upper side of the screen. This means,

it runs during horizontal, respectively vertical flyback.

The color of the complete border can be stored in the

programmable OSD color look-up table in a separate

address. The format is 3 4 bit RGB. The contrast can

be adjusted separately.

The picture frame generator includes a priority master

circuit. Its priority is programmable and the border is

generated only if the priority is higher than the priority at

the PRIO bus. Therefore the border can be underlay or

overlay depending on the picture source.

2.8.13. Priority Codec

2.8.14. Scan Velocity Modulation

The RGB input signal of the SVM is converted to Y in a

simple matrix. Then the Y signal is differentiated by a filter of the transfer function 1–Z

–N

, where N is programmable from 1 to 6. With a coring, some noise can be suppressed. This is followed by a gain adjustment and an

adjustable limiter. The analog output signal is generated

by an 8-bit D/A converter.

The signal delay can be adjusted by ±3.5 clocks in halfclock steps. For the gain and filter adjustment there are

two parameter sets. The switching between these two

sets is done with the same RGB switch signal that is

used for switching between video-RGB and OSD-RGB

for the RGB outputs. (See Fig. 2–19).

2.8.15. Display Phase Shifter

A phase shifter is used to partially compensate the

phase differences between the video source and the flyback signal. By using the described clock system, this

phase shifter works with an accuracy of approximately

1 ns. It has a range of 1 clock period which is equivalent

to ±24.7 ns at 20.25 MHz. The large amount of phase

shift (full clock periods) is realized in the front-end circuit.

The priority decoder has three input lines for up to eight

priorities. The highest priority is all three lines at low level. A 5-bit information is attached to each priority (see

table 3–1 ‘Priority Bus’). These bits are programmable

via the I

2

C-bus and have the following meanings:

– one of two contrast, brightness and matrix values for

main and side picture

– RGB from video signal or color look-up table

– disable/enable black level expander

– disable/enable peaking transient suppression when

signal is switched

– disable/enable analog fast blank input 1

– disable/enable analog fast blank input 2

GRB

N1 N2

Coring

Gain1 Gain2

Limit

Delay

RGB Switch

Matrix and

Shaping

Modulation

Notch

Differentiator

–Nx

1–Z

Fig. 2–19: SVM block diagram

Coring

adjustment

Gain

adjustment

Limiter

Delay

adjustment

D/A

Converter

Output

19Micronas

20 Micronas

Fig. 2–20: Digital back-end

dig.

Y in

8

5

dig. OSD in

8

dig.

CrCb in

contrast

expander

blanking

for CRTmeasurement

black

level

prio

Interpol

4:4:4

dynamic

peaking

prio

Cr

DTI

(Cr)

brightness

+ offset

softlimiter

Matrix

R’

Matrix

G’

whitedrive

measurement

luma insert

for CRTmeasurement

Y

R

G

CLUT,

Contrast

Picture

Frame

Generator

whitedrive R

x beamcurr. lim.

whitedrive G

x beamcurr. lim.

clock

display

& clock

control

Phase

Shift

0...1 clock

Phase

Shift

0...1 clock

horizontal

flyback

dig.

Rout

10

dig.

Gout

10

PRIO in

3

PRIO

decoder

DTI

(Cb)

Cb

side picture

select

coefficients

main picture

Matrix

B’

Matrix

saturation

whitedrive B

x beamcurr. lim.

dig.

Phase

Shift

0...1 clock

Bout

PRELIMINARY DATA SHEETVDP 31xxB

10

B

Scan

Velocity

Modulation

SVMout

PRELIMINARY DATA SHEET VDP 31xxB

2.9. Analog Back End

The digital RGB signals are converted to analog RGBs

using three video digital to analog converters (DAC) with

10-bit resolution. An analog brightness value is provided

by three additional DACs. The adjustment range is 40%

of the full RGB range.

Controlling the whitedrive/analog brightness and also

the external contrast and brightness adjustments is

done via the Fast Processor, located in the front-end.

Control of the cutoff DACs is via I

2

C-bus registers.

Finally cutoff and blanking values are added to the RGB

signals. Cutoff (dark current) is provided by three 9-bit

DACs. The adjustment range is 60% of full scale RGB

range.

The analog RGB-outputs are current outputs with current-sink characteristics. The maximum current drawn

by the output stage is obtained with peak white RGB. An

external half contrast signal can be used to reduce the

output current of the RGB outputs to 50%.

2.9.1. CRT Measurement and Control

The display processor is equipped with an 8-bit PDMADC for all measuring purposes. The ADC is connected

to the sense input pin, the input range is 0 to 1.5V. The

bandwidth of the PDM filter can be selected; it is

40/80 kHz for small/large bandwidth setting. The input

impedance is more than 1 MΩ.

Cutoff and white drive current measurement are carried

out during the vertical blanking interval. They always use

the small bandwidth setting. The current range for the

cutoff measurement is set by connecting a sense resistor to the MADC input. For the whitedrive measurement,

the range is set by using another sense resistor and the

range select switch 2 output pin (RSW2). During the active picture, the minimum and maximum beam current

is measured. The measurement range can be set by using the range select switch 1 pin (RSW1) as shown in

Fig. 2–21 and Fig. 2–22. The timing window of this measurement is programmable. The intention is to automatically detect letterbox transmission or to measure the actual beam current. All control loops are closed via the

external control microprocessor.

beam current

A

SENSE

D

MADC

RSW1

RSW2

R2

R3

R1

Fig. 2–21: MADC Range Switches

CR + IBRM

black

ultra black

active

measurement

resistor

PICTURE MEAS.

Lines

R1øR2øR3

RSW1=on, RSW2=on

PMSO

Fig. 2–22: MADC Measurement Timing

CR + IBRM + WDRV·WDR

cutoff

R

CG + IBRM

CB + IBRM

TUBE MEASUREMENT

TML

R1

cutoff

G

cutoff

B

white

drive

R

R1øR3

RSW2

=on

R

G

B

R1øR2øR3

RSW1=on, RSW2=on

PICTURE MEAS.

PMST

21Micronas

PRELIMINARY DATA SHEETVDP 31xxB

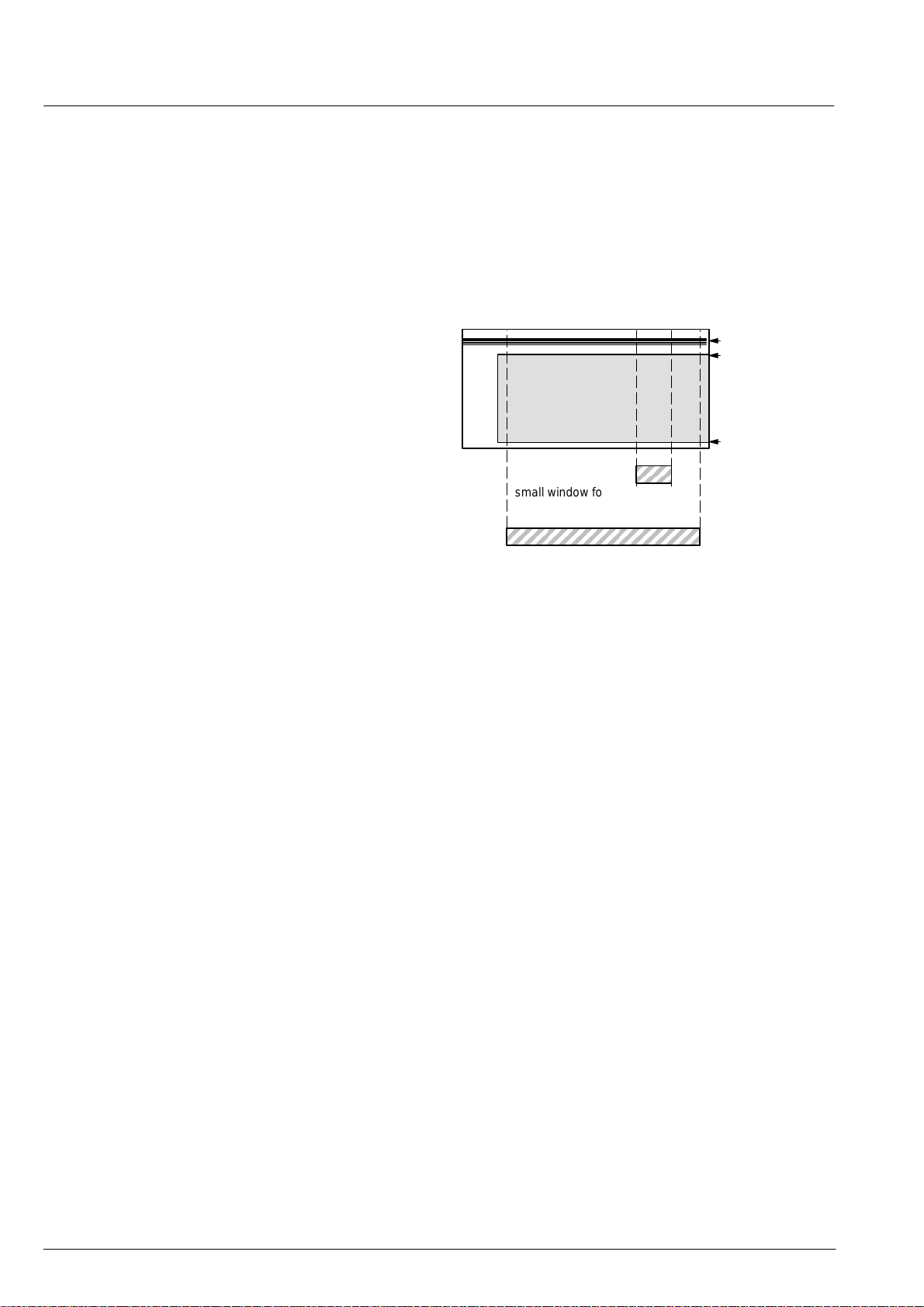

In each field two sets of measurements can be taken:

a) The picture tube measurement returns results for

– cutoff R

– cutoff G

– cutoff B

– white drive R or G or B (sequentially)

b) The picture measurement returns data on

– active picture maximum current

– active picture minimum current

The tube measurement is automatically started when

the cutoff blue result register is read. Cutoff control for

RGB requires one field only while a complete white-drive

control requires three fields. If the measurement mode

is set to ‘offset check’, a measurement cycle is run with

the cutoff/whitedrive signals set to zero. This allows to

compensate the MADC offset as well as input the

leakage currents. During cutoff and whitedrive measurements, the average beam current limiter function (ref.

2.9.3.) is switched off and a programmable value is used

for the brightness setting. The start line of the tube measurement can be programmed via I

2

C-bus, the first line

used for the measurement, i.e. measurement of cutoff

red, is 2 lines after the programmed start line.

The picture measurement must be enabled by the control microprocessor after reading the min./max. result

registers. If a ‘1’ is written into bit 2 in subaddress 25, the

measurement runs for one field. For the next measurement a ‘1’ has to be written again. The measurement is

always started at the beginning of active video.

The vertical timing for the picture measurement is programmable, and may even be a single line. Also the signal bandwidth is switchable for the picture measurement.

Two horizontal windows are available for the picture

measurement. The large window is active for the entire

active line. Tube measurement is always carried out with

the small window. Measurement windows for picture

and tube measurement are shown in Figure 2–23.

tube measurement

picture meas. start

active video

field 1/ 2

picture meas. end

small window for tube

measurement (cutoff, white drive)

large window for active picture

Fig. 2–23: Windows for tube and picture measure-

ments

2.9.2. SCART Output Signal

The RGB output of the VDP 31xxB can also be used to

drive a SCART output. In the case of the SCART signal,

the parameter CLMPR (clamping reference) has to be

set to 1. Then, during blanking, the RGB outputs are automatically set to 50% of the maximum brightness. The

DC offset values can be adjusted with the cutoff parameters CR, CG, and CB. The amplitudes can be adjusted

with the drive parameters WDR, WDG, and WDB.

22 Micronas

Loading...

Loading...