Page 1

P400m 2.5-Inch NAND Flash SSD

P400m 2.5-Inch SATA NAND Flash SSD

MTFDDAK100MAN-1S1AA, MTFDDAK200MAN-1S1AA,

MTFDDAK400MAN-1S1AA

Features

Features

• Micron® 25nm MLC NAND Flash

• RoHS-compliant package

• SATA 6 Gb/s interface

• ATA modes supported

– PIO mode 3, 4

– Multiword DMA mode 0, 1, 2

– Ultra DMA mode 0, 1, 2, 3, 4, 5

• Enterprise sector size support

– 512-byte

• Hot-plug capable

• Native command queuing support with 32-command slot support

• ATA-8 ACS2 command set compliant

• ATA security feature command set and password

login support

• Security erase command set: fast and secure erase

• Self-monitoring, analysis, and reporting technology

(SMART) command set

• 100GB performance (steady state)

– Sequential 64KB read: 380 MB/s

– Sequential 64KB write: 200 MB/s

– Random 4KB read: 52,000 IOPS

– Random 4KB write: 21,000 IOPS

– READ latency: 0.57ms

– WRITE latency: 2ms

• 200GB performance (steady state)

– Sequential 64KB read: 380 MB/s

– Sequential 64KB write: 310 MB/s

– Random 4KB read: 54,000 IOPS

– Random 4KB write: 26,000 IOPS

– READ latency: 0.51ms

– WRITE latency: 2ms

• 400GB performance (steady state)

– Sequential 64KB read: 380 MB/s

– Sequential 64KB write: 310 MB/s

– Random 4KB read: 60,000 IOPS

– Random 4KB write: 26,000 IOPS

– READ latency: 0.51ms

– WRITE latency: 2ms

1, 2

1, 2

1, 2

• Reliability

– Mean time to failure (MTTF): 2 million device

3

hours

– Static and dynamic wear leveling

– Uncorrectable bit error rate (UBER): <1 sector

per 1016 bits read

• Endurance: Total bytes written (TBW)

– 100GB: 1.75PB; 200GB: 3.50PB; 400GB: 7.00PB

• Capacity4 (unformatted): 100GB, 200GB, 400GB

• Mechanical: 7.0mm height

– SATA connector: 5V ±10%

– 2.5-inch drive: 100.5mm x 69.85mm x 7.0mm

• Field-upgradeable firmware

• Power consumption: <7.5W (TYP)

• Operating temperature

– Commercial (0°C to 70°C)

Notes:

1. Typical I/O performance numbers as measured using Iometer with a queue depth of

32 and write cache disabled.

2. 4KB transfers used for READ/WRITE latency

values.

3. The product achieves a MTTF based on population statistics not relevant to individual

units.

4. 1GB = 1 billion bytes; formatted capacity is

less.

5. Drive case temperature.

5

Warranty: Contact your Micron sales representative

for further information regarding the product,

including product warranties.

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

Products and specifications discussed herein are subject to change by Micron without notice.

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 2

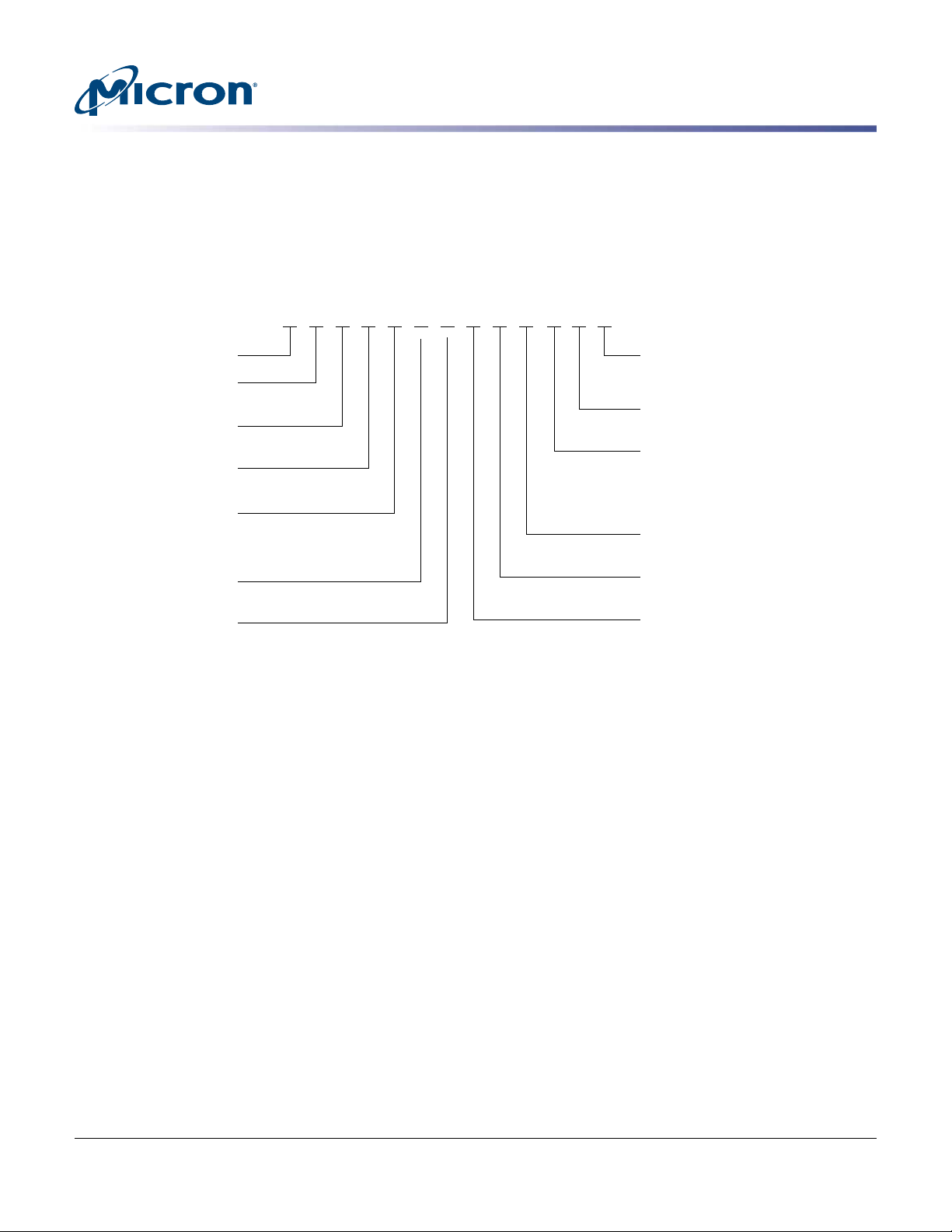

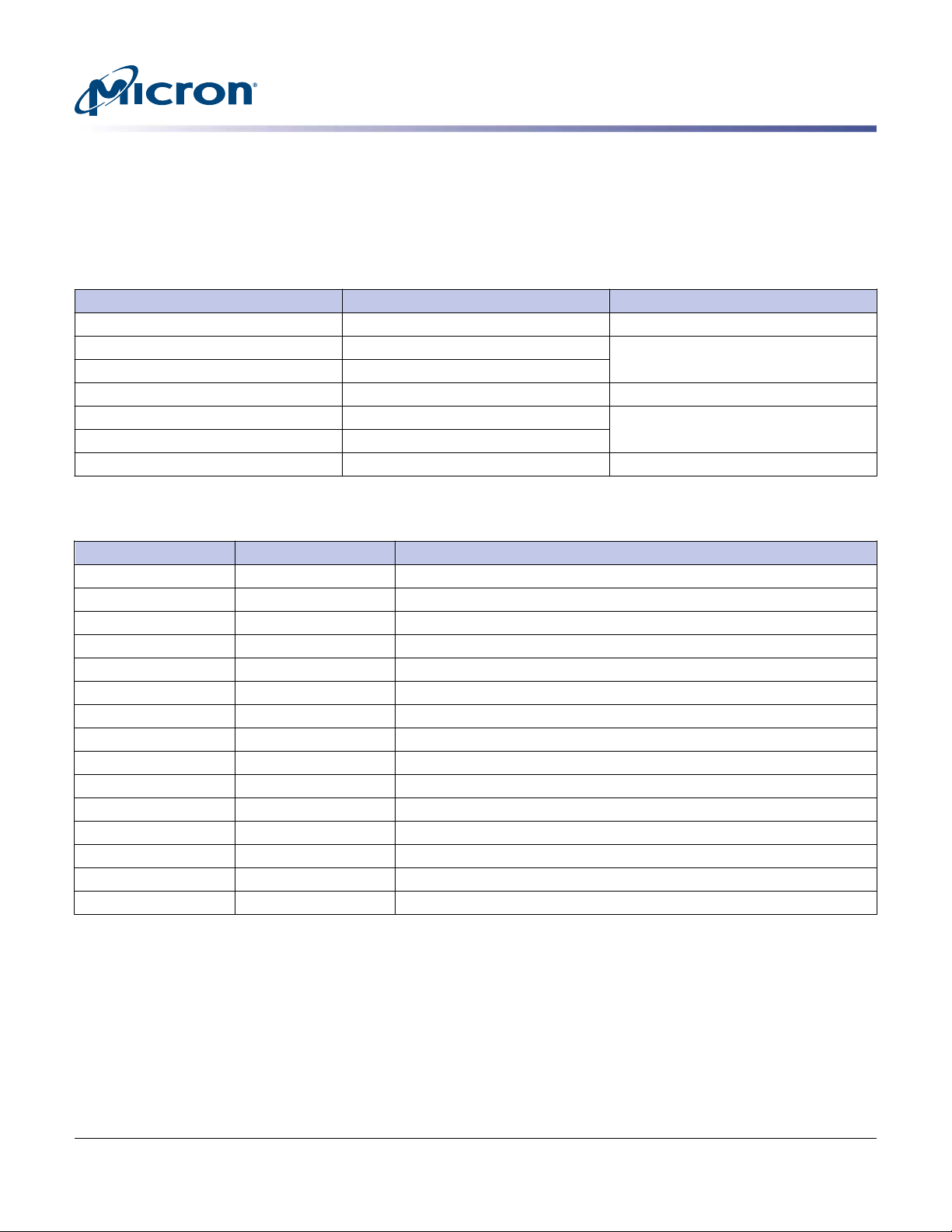

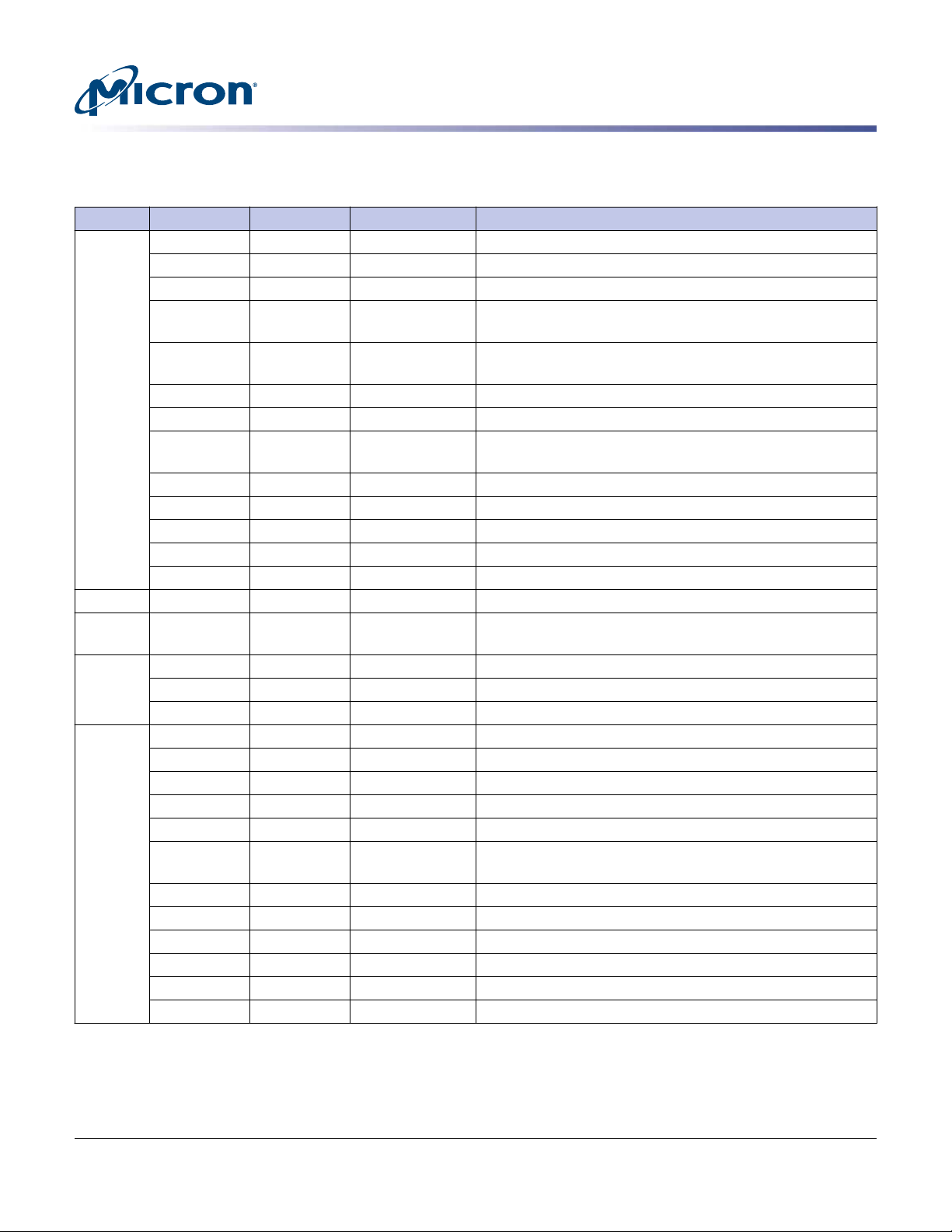

MT FD D AK 100 M AN - 1 S 1

Micron Technology

Product Family

FD = Flash drive

Drive Interface

D = SATA 6.0 Gb/s

Drive Form Factor

AK = 2.5-inch (7.0mm)

Drive Density

100 = 100GB

200 = 200GB

400 = 400GB

NAND Flash Type

M = MLC

Product Family

AN = P400m

Production Status

Blank = Production

ES = Engineering sample

Operating Temperature Range

Blank = Commercial (0°C to 70°C)

Hardware Feature Set

Blank = Null

AA = Contact factory

AB = Contact factory

AC = Contact factory

BOM Revision

1 = 1st generation

NAND Flash Component

S = 42Gb, MLC, x8 3.3V (25nm)

Sector Size

1 = 512-byte

ESAA

P400m 2.5-Inch NAND Flash SSD

Features

Part Numbering Information

Micron’s P400m SSD is available in different configurations and densities. Visit micron.com for a list of valid part

numbers.

Figure 1: Part Number Chart

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 3

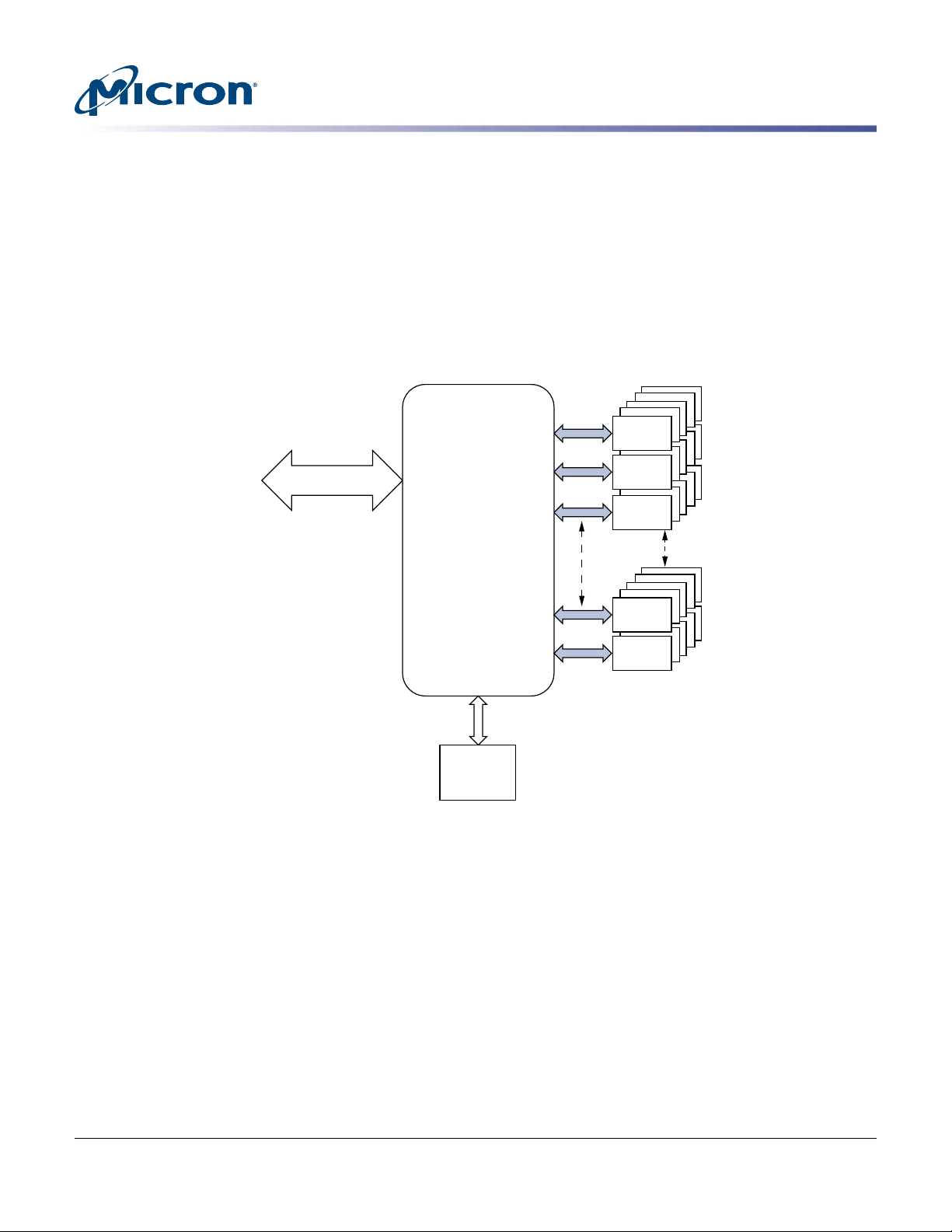

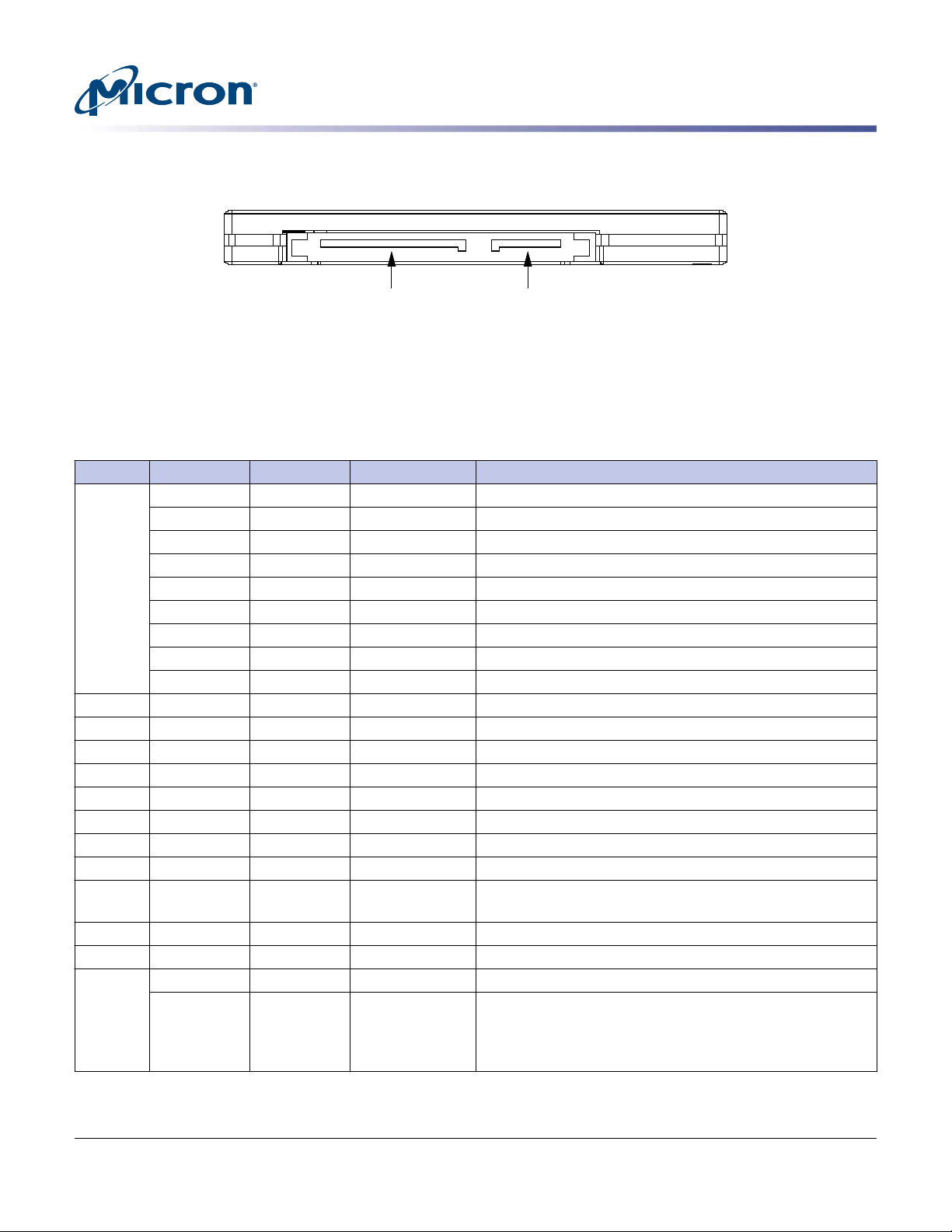

General Description

Micron’s P400m solid state drive (SSD) uses a single-chip controller with a SATA interface on the system side and n-channels of Micron NAND Flash internally. Packaged in

an HDD replacement enclosure, the SSD integrates easily in existing storage infrastructures.

The P400m SSD is designed to support and manage the needs of enterprise platforms

that utilize significant read/write mixed workloads. Optimized to support enterprise

needs previously supported solely by SLC solutions, the P400m will provide the endurance and data integrity required by these growing environments.

Figure 2: Functional Block Diagram

P400m 2.5-Inch NAND Flash SSD

General Description

NAND

SATA

SSD

controller

DRAM

buffer

NAND

NAND

NAND

NAND

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 4

P400m 2.5-Inch NAND Flash SSD

Logical Block Address Configuration

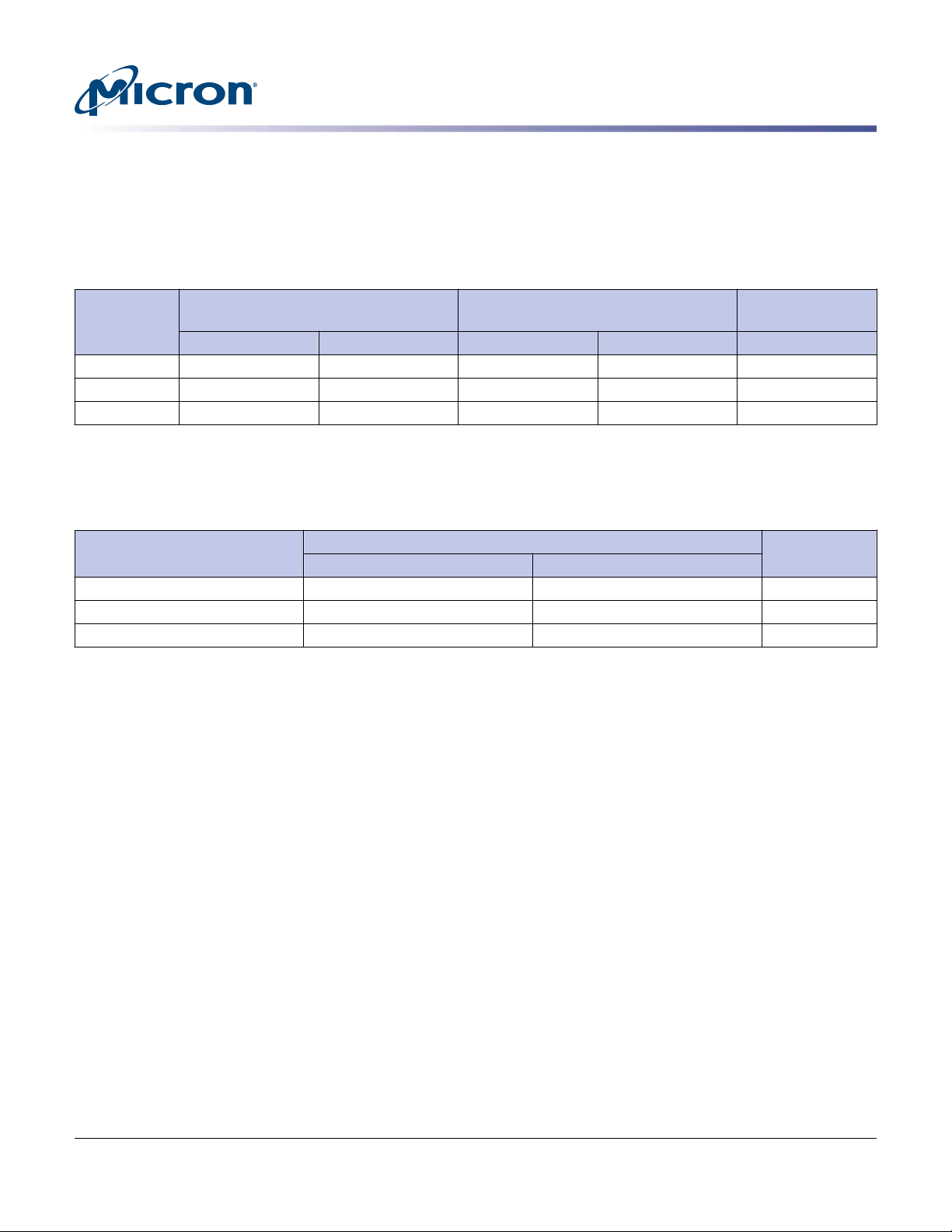

Logical Block Address Configuration

The drive is set to report the number of logical block addresses (LBA) that will ensure

sufficient storage space for the specified density. Standard LBA settings, based on the

IDEMA standard (LBA1-02), are shown below.

Table 1: Standard LBA Settings – 512-Byte Sector Size

User Available

Total LBA Max LBA

Drive Size

100GB 195,371,568 BA52230 195,371,567 BA5222F 100,030,242,816

200GB 390,721,968 1749F1B0 390,721,967 1749F1AF 200,049,647,616

400GB 781,422,768 2E9390B0 781,422,767 2E9390AF 400,088,457,216

Decimal Hexadecimal Decimal Hexadecimal (Unformatted)

Bytes

Physical Configuration

Table 2: 2.5-Inch Dimensions

Value

Specification

Height – 7.0 mm

Width 69.85 – mm

Length 100.50 – mm

UnitNom Max

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 5

Interface Connectors

The SATA signal segment interface cable has four conductors and three ground connections. As shown in Package Dimensions, the cable includes a 7-pin signal segment and a

15-pin power segment arranged in a single row with a 1.27mm (0.050in) pitch.

Table 3: SATA Signal Segment Pin Assignments

Signal Name Type Description

S1 GND Ground

S2 A

S3 A#

S4 GND Ground

S5 B#

S6 B

S7 GND Ground

Table 4: 2.5-Inch SATA Power Segment Pin Assignments

P400m 2.5-Inch NAND Flash SSD

Interface Connectors

Differential signal pair A and A#

Differential signal pair B and B#

Pin# Signal Name Description

P1 V33 No connect

P2 V33 No connect

P3 V33 No connect

P4 GND Ground

P5 GND Ground

P6 GND Ground

P7 V5 5V power, precharge

P8 V5 5V power

P9 V5 5V power

P10 GND Ground

P11 DAS Device activity signal

P12 GND Ground

P13 V12 No connect

P14 V12 No connect

P15 V12 No connect

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 6

Power

segment

P1 S1

Signal

segment

P400m 2.5-Inch NAND Flash SSD

Figure 3: SSD Interface Connections

Device ID

Table 5: Identify Device

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

0 – – – General configuration bit-significant information

15 F 0b 0 = ATA device

14–8 X 00000000 Retired

7 F 0b 1 = Removable media device

6 F 1b Obsolete

5–3 X 000b Retired

2 V 0b Response incomplete

1 X 0b Retired

0 F 0b Reserved

1 – – 3FFFh Obsolete

2 – F C837h Specific configuration

3 – F 0010h Obsolete

4 – F 0000h 0000h Retired

6 – F 003Fh Obsolete

7 – (O)V 0000h 0000h

9 – ( )X 0000h Retired

10 – (M)F Varies Serial number (20 ASCII characters)

20 – ( )X 0000h 0000h

0000h

23 – (M)F Varies Firmware revision (8 ASCII characters)

27 – (M)F Varies Model number (40 ASCII characters)

47 15–8 F 80h 80h

7–0 F 10h 00h = Reserved

Reserved for assignment by the CompactFlash™ Association

Retired/obsolete

01h-FFh = Maximum number of logical sectors that shall be

transferred per DRQ data block on READ/WRITE MULTIPLE

commands

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

6

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 7

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

48 – – – Trusted Computing feature set options

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13–1 F 0000000000000b Reserved for the Trusted Computing Group

0 F 0b 1 = Trusted Computing feature set is supported

49 – – – Capabilities

15–14 F 00b Reserved for the IDENTIFY PACKET DEVICE command

13 F 1b 1 = Standby timer values as specified in this standard are

supported

– – – 0 = Standby timer values shall be managed by the device

12 F 0b Reserved for the IDENTIFY PACKET DEVICE command

11 F 1b 1 = IORDY is supported

– – – 0 = IORDY may be supported

10 F 1b 1 = IORDY may be disabled

9 – 1b 1 = LBA is supported

8 F 1b 1 = DMA is supported

7–0 F 00000000b Retired

50 – – – Capabilities

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13–2 F 000000000000b Reserved

1 X 0b Obsolete

0 F 1b Shall be set to one to indicate a vendor-specific standby tim-

er value minimum

51 – ( )X 0000h 0000h Obsolete

53 15–3 F 0000000000000b Reserved

2 F 1b 1 = The fields reported in word 88 are valid

0 = The fields reported in word 88 are not valid

1 F 1b 1 = The fields reported in words (70:64) are valid

0 = the fields reported in words (70:64) are not valid

0 X 1b Obsolete

54 – ( )X 3FFFh 0010h

003Fh FC10h

00FBh

Obsolete

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

7

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 8

P400m 2.5-Inch NAND Flash SSD

Device ID

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

59 15 F 1b 1 = The BLOCK ERASE EXT command is supported

14 F 1b 1 = The OVERWRITE EXT command is supported

13 F 0b 1 = The CRYPTO SCRAMBLE EXT command is supported

12 F 1b 1 = The sanitize feature set is supported

11–9 F 000b Reserved

8 V 1b 1 = Multiple sector settings are valid

7–0 V 00010000b xxh = Current setting for number of logical sectors that shall

be transferred per DRQ data block on READ/WRITE MULTIPLE commands

60 – M(F) Varies by capacity Total number of user addressable logical sectors

62 – ( )X 0000h Obsolete

63 15–11 F 00000b Reserved

10 V 0b 1 = Multiword DMA mode 2 is selected

0 = Multiword DMA mode 2 is not selected

9 V 0b 1 = Multiword DMA mode 1 is selected

0 = Multiword DMA mode 1 is not selected

8 V 0b 1 = Multiword DMA mode 0 is selected

0 = Multiword DMA mode 0 is not selected

7–3 F 0000b Reserved

2 F 1b 1 = Multiword DMA mode 2 and below are supported

1 F 1b 1 = Multiword DMA mode 1 and below are supported

0 F 1b 1 = Multiword DMA mode 0 is supported

64 15–8 F 00h Reserved

7–0 F 03h PIO modes is supported

65 – F 0078h Minimum Multiword DMA transfer cycle time per word

Cycle time in nanoseconds

66 – F 0078h Manufacturer's recommended Multiword DMA transfer cy-

cle time

Cycle time in nanoseconds

67 – F 0078h Minimum PIO transfer cycle time without flow control

Cycle time in nanoseconds

68 – F 0078h Minimum PIO transfer cycle time with IORDY flow control

Cycle time in nanoseconds

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 9

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

69 – F – Additional supported

15 F 0b 1 = CFast specification is supported

14 F 1b 1 = Deterministic read after trim is supported

13 F 0b 1 = Long physical sector alignment error reporting control is

supported

12 F 0b 1 = DEVICE CONFIGURATION IDENTIFY DMA and DEVICE

CONFIGURATION SET DMA are supported

11 F 0b 1 = READ BUFFER DMA is supported

10 F 0b 1 = WRITE BUFFER DMA is supported

9 F 0b 1 = SET MAX PASSWORD DMA and SET MAX UNLOCK DMA

are supported

8 F 0b 1 = DOWNLOAD MICROCODE DMA is supported

7 F 0b Reserved for IEEE-1667

6 F 0b 1 = Optional ATA device 28-bit commands are supported

5 F 0b 1 = Read zero after trim is supported

4–0 F 00000b Reserved

70 – F 0000h Reserved

71 – F 0000h 0000h

0000h 0000h

75 – – – Queue depth

15–5 F 00000000000b Reserved

4–0 F 11111b Maximum queue depth - 1

76 – – – Serial ATA capabilities

15–13 F 000b Reserved

12 F 1b Native command queuing priority information is supported

11 F 0b Unload while NCQ commands are outstanding is supported

10 F 1b Physical event counters are supported

9 F 1b Receipt of host-initiated interface power management re-

8 F 1b Native command queuing is supported

7–4 F 0000b Reserved for future Serial ATA signaling speed grades

3 F 1b 1 = Serial ATA Gen-3 speed (6.0 Gb/s) is supported

2 F 1b 1 = Serial ATA Gen-2 speed (3.0 Gb/s) is supported

1 F 1b 1 = Serial ATA Gen-1 speed (1.5 Gb/s) is supported

0 F 0b Reserved (set to 0)

Reserved for the IDENTIFY PACKET DEVICE command

quests is supported

P400m 2.5-Inch NAND Flash SSD

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

9

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 10

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

77 – – – Serial ATA additional capabilities

15–6 F 0000000000b Reserved for future Serial ATA definition

5 F 0b NCQ QUEUE MANAGEMENT command is supported

4 F 0b NCQ streaming is supported

3–1 V 010b Coded value indicating current negotiated Serial ATA signal

speed

0 F 0b Shall be cleared to zero

78 – – – Serial ATA features are supported

15–7 F 000000000b Reserved

6 F 1b 1 = Supports software settings preservation

5 F 0b Reserved

4 F 0b 1 = In-order data delivery is supported

3 F 1b 1 = Dev initiate interface power management is supported

2 F 1b 1 = DMA setup auto-activate optimization is supported

1 F 0b 1 = Non-zero buffer offsets in DMA setup FIS are supported

0 F 0b Reserved (set to 0)

79 – – – Serial ATA features are enabled

15–7 V 000000000b Reserved

6 V 1b 1 = Software settings preservation is enabled

5 V 0b 1 = Asynchronous notification is enabled

4 V 0b 1 = In-order data delivery is enabled

3 V 0b 1 = Device initiating interface power management is ena-

bled

2 V 0b 1 = DMA setup auto-activate optimization is enabled

1 V 0b 1 = Non-zero buffer offsets in DMA setup FIS is enabled

0 V 0b Reserved (set to 0)

80 – – – Major revision number

15–10 F 000000b Reserved

9 F 1b 1 = ATA8-ACS2 is supported

8 F 1b 1 = ATA8-ACS is supported

7 F 1b 1 = ATA/ATAPI-7 is supported

6 F 1b 1 = ATA/ATAPI-6 is supported

5 F 1b 1 = ATA/ATAPI-5 is supported

4 F 0b 1 = ATA/ATAPI-4 is supported

3 F 0b Obsolete

2 S 0b Obsolete

1 S 0b Obsolete

0 F 0b Reserved

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

10

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 11

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

81 – F 0028h Minor revision number

82 – – – Command set is supported

15 X 0b Obsolete

14 F 1b 1 = NOP command is supported

13 F 1b 1 = READ BUFFER command is supported

12 F 1b 1 = WRITE BUFFER command is supported

11 X 0b Obsolete

10 F 1b 1 = Host-protected area feature set is supported

9 F 0b 1 = DEVICE RESET command is supported

8 F 0b 1 = Service interrupt is supported

7 F 0b 1 = Release interrupt is supported

6 F 1b 1 = Read look-ahead is supported

5 F 1b 1 = Write cache is supported

4 F 0b Shall be cleared to zero to indicate that the packet feature

set is not supported

3 F 1b 1 = Mandatory power management feature set is supported

2 F 0b Obsolete

1 F 1b 1 = Security feature set is supported

0 F 1b 1 = SMART feature set is supported

83 – – – Command set is supported

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13 F 1b 1 = FLUSH CACHE EXT command is supported

12 F 1b 1 = Mandatory FLUSH CACHE command is supported

11 F 1b 1 = Device configuration overlay feature set is supported

10 F 1b 1 = 48-bit address feature set is supported

9 F 0b 1 = Automatic acoustic management feature set is suppor-

ted

8 F 1b 1 = SET MAX security extension is supported

7 F 0b See Address Offset Reserved Area Boot INCITS TR27:2001

6 F 0b 1 = SET FEATURES subcommand required to spin-up after

power-up

5 F 0b 1 = Power-up in standby feature set is supported

4 F 0b Obsolete

3 F 1b 1 = Advanced power management feature set is supported

2 F 0b 1 = CFA feature set is supported

1 F 0b 1 = READ/WRITE DMA QUEUED is supported

0 F 1b 1 = DOWNLOAD MICROCODE command is supported

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

11

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 12

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

84 – – – Command set/feature-supported extension

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13 F 1b 1 = Idle immediate with unload feature is supported

12 F 0b Reserved for technical report INCITS TR-37-2004 (TLC)

11 F 0b Reserved for technical report INCITS TR-37-2004 (TLC)

10–9 F 00b Obsolete

8 F 1b 1 = 64-bit word wide name is supported

7 F 0b 1 = WRITE DMA QUEUED FUA EXT command is supported

6 F 1b 1 = WRITE DMA FUA EXT and WRITE MULTIPLE FUA EXT

commands are supported

5 F 1b 1 = General purpose logging feature set is supported

4 F 0b 1 = Streaming feature set is supported

3 F 0b 1 = Media card pass through command feature set is sup-

ported

2 F 0b 1 = Media serial number is supported

1 F 1b 1 = SMART self-test is supported

0 F 1b 1 = SMART error logging is supported

85 – – – Command set/feature is enabled

15 X 0b Obsolete

14 F 1b 1 = NOP command is supported

13 F 1b 1 = READ BUFFER command is supported

12 F 1b 1 = WRITE BUFFER command is supported

11 X 0b Obsolete

10 V 1b 1 = Host protected area feature set is enabled

9 F 0b 1 = DEVICE RESET command is supported

8 V 0b 1 = SERVICE interrupt is enabled

7 V 0b 1 = Release interrupt is enabled

6 V 1b 1 = Look-ahead is enabled

5 V 0b 1 = Write cache is enabled

4 F 0b Shall be cleared to zero to indicate that the packet feature

set is not supported

3 F 1b Power management feature set is enabled

2 F 0b Obsolete

1 V 0b 1 = Security mode feature set is enabled

0 V 1b 1 = SMART feature set is enabled

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

12

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 13

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

86 – – – Command set/feature is enabled

15 1b 1 = Words 120-119 are valid

14 F 0b 1 = Reserved

13 F 1b 1 = FLUSH CACHE EXT command is supported

12 F 1b 1 = FLUSH CACHE command is supported

11 F 1b 1 = Device configuration overlay is supported

10 F 1b 1 = 48-bit address feature set is supported

9 V 0b 1 = Automatic acoustic management feature set is enabled

8 F 0b 1 = SET MAX security enabled by SET MAX SET PASSWORD

7 F 0b Reserved for address offset reserved area boot, INCITS

TR27:2001

6 F 0b 1 = SET FEATURES subcommand required to spin-up after

power-up

5 V 0b 1 = Power-up in standby feature set is enabled

4 V 0b Obsolete

3 V 1b 1 = Advanced power management feature set is enabled

2 F 0b 1 = CFA feature set is supported

1 F 0b 1 = READ/WRITE DMA QUEUED command is supported

0 F 1b 1 = DOWNLOAD MICROCODE command is supported

87 – – – Command set/feature is enabled/supported

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13 F 1b 1 = IDLE IMMEDIATE with UNLOAD FEATURE is supported

12 V 0b Reserved for technical report- INCITS tr-37-2004 (TLC)

11 V 0b Reserved for technical report- INCITS TR-37-2004 (TLC)

10–9 F 00b Obsolete

8 F 1b 1 = 64-bit word wide name is supported

7 F 0b 1 = WRITE DMA QUEUED FUA EXT command is supported

6 F 1b 1 = WRITE DMA FUA EXT and WRITE MULTIPLE FUA EXT

commands are supported

5 F 1b 1 = General purpose logging feature set is supported

4 V 0b Obsolete

3 V 0b 1 = Media card pass through command feature set is sup-

ported

2 V 0b 1 = Media serial number is valid

1 F 1b 1 = SMART self-test is supported

0 F 1b 1 = SMART error logging is supported

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

13

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 14

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

88 – – 0b Ultra DMA modes

15 – 0b Reserved

14 – 0b 1 = Ultra DMA mode 6 is selected

0 = Ultra DMA mode 6 is not selected

13 – 0b 1 = Ultra DMA mode 5 is selected

0 = Ultra DMA mode 5 is not selected

12 – 0b 1 = Ultra DMA mode 4 is selected

0 = Ultra DMA mode 4 is not selected

11 – 0b 1 = Ultra DMA mode 3 is selected

0 = Ultra DMA mode 3 is not selected

10 – 0b 1 = Ultra DMA mode 2 is selected

0 = Ultra DMA mode 2 is not selected

9 – 0b 1 = Ultra DMA mode 1 is selected

0 = Ultra DMA mode 1 is not selected

8 – 0b 1 = Ultra DMA mode 0 is selected

0 = Ultra DMA mode 0 is not selected

7 – 0b Reserved

6 – 1b 1 = Ultra DMA mode 6 and below are supported

5 – 1b 1 = Ultra DMA mode 5 and below are supported

4 – 1b 1 = Ultra DMA mode 4 and below are supported

3 – 1b 1 = Ultra DMA mode 3 and below are supported

2 – 1b 1 = Ultra DMA mode 2 and below are supported

1 – 1b 1 = Ultra DMA mode 1 and below are supported

0 – 1b 1 = Ultra DMA mode 0 is supported

89 – (O)F 0001h Time required for security erase unit completion

90 – (O)F 0001h Time required for enhanced security erase completion

91 – (O)V 00FEh Current advanced power management value

92 – (O)V FFFEh Master password revision code

Device ID

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

14

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 15

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

93 – – – Shall be 0000h for SATA devices

15 – 0b Shall be cleared to zero

14 – 0b Shall be set to one

13 – 0b 1 = Device detected CBLID-above V

0 = device detected CBLID-below V

– – – Device 1 hardware reset result

Device 0 shall clear these bits to zero

Device 1 shall set these bits in accordance with the ATA8,

ACS2 specification. See specification for details.

12 – 0b Reserved

11 – 0b 0 = Device 1 did not assert PDIAG-

1 = Device 1 asserted PDIAG-

10–9 – 00b These bits indicate how device 1 determined the device

number:

00 = Reserved

01 = A jumper was used

10 = The CSEL signal was used

11 = Some other method was used or the method is unknown

8 – 0b Shall be set to one

– Device 0 hardware reset result. Device 1 shall clear these

bits to zero.

Device 0 shall set these bits in accordance with the ATA8,

ACS2 specification. See specification for details.

7 – 0b Reserved

6 – 0b 0 = Device 0 does not respond when device 1 is selected.

1 = Device 0 responds when device 1 is selected

5 – 0b 0 = Device 0 did not detect the assertion of DASP-

1 = Device 0 detected the assertion of DASP-

4 – 0b 0 = Device 0 did not detect the assertion of PDIAG-

1 = Device 0 detected the assertion of PDIAG-

3 – 0b 0 = Device 0 failed diagnostics.

1 = Device 0 passed diagnostics

2–1 – 00b These bits indicate how device 0 determined the device

number:

00 = Reserved

01 = A jumper was used

10 = The CSEL signal was used

11 = Some other method was used or the method is unknown

0 – 0b Shall be set to one

Device ID

IH

IL

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

15

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 16

P400m 2.5-Inch NAND Flash SSD

Device ID

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

94 15–8 F 00h Vendor's recommended acoustic management value

7–0 V 00h Current automatic acoustic management value

95 – (O)V 0000h Stream minimum request size

96 – (O)V 0000h Streaming transfer time - DMA

97 – (O)V 0000h Streaming access latency - DMA and PIO

98 – (O)F 0000h 0000h Streaming performance granularity (98-99)

100 – V Varies by capacity Maximum user LBA for 48-bit address feature set

104 – (O)V 0000h Streaming transfer time - PIO

105 – ( )F 0008h Maximum number of 512-byte blocks of LBA range entries

per DATA SET MANAGEMENT command

106 – – – Physical sector size/logical sector size

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13 F 0b 1 = Device has multiple logical sectors per physical sector

12 F 0b 1 = Device logical sector longer than 256 Words

11–4 F 00000000b Reserved

3–0 F 0000b 2^x logical sectors per physical sector

107 – (O)F 0000h Inter-seek delay for ISO-7779 acoustic testing in microsec-

onds

108 15–12 F 0101b NAA (3-0)

11–0 – 000000001010b IEEE OUI (23-12)

109 15–4 F 000001110101b IEEE OUI (11-0)

3–0 – Varies Unique ID (35-32)

110 – (M)F Varies 5-0 unique ID (31-16)

111 – (M)F Varies Unique ID (15-0)

112 – (O)F 0000h 0000h

0000h 0000h

116 – (O)V 0000h Reserved for INCITS TR-37-2004

117 – (O)F 0000h 0000h Words per logical sector

Reserved for 128-bit world wide name extension to 128 bits

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

16

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 17

P400m 2.5-Inch NAND Flash SSD

Device ID

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

119 – – – Commands and feature sets are supported (continued from

words 84-82)

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13–6 F 00000001b Reserved

5 F 0b 1 = Free-fall control feature set is supported

4 F 1b 1 = DOWNLOAD MICROCODE command with mode 3 sup-

ported

3 F 1b 1 = READ LOG DMA EXT and WRITE LOG DMA EXT com-

mands supported

2 F 1b 1 = The WRITE UNCORRECTABLE EXT command is supported

1 F 0b 1 = The write-read-verify feature set is supported

0 F 0b Reserved for DDT

120 – – – Commands and feature sets are supported or enabled (con-

tinued from words 87-85)

15 – 0b Shall be cleared to zero

14 – 1b Shall be set to one

13–6 – 00000000b Reserved

5 – 0b 1 = Free-fall control feature set is enabled

4 – 1b 1 = The DOWNLOAD MICROCODE command with mode 3 is

supported

3 – 1b 1 = The READ LOG DMA EXT and WRITE LOG DMA EXT

commands are supported

2 – 1b 1 = The WRITE UNCORRECTABLE EXT command is supported

1 – 0b 1 = The write-read-verify feature set is enabled

0 – 0b 1 = The disable data transfer after error detection feature

set is enabled

0 = The disable data transfer after error detection feature

set is disabled

121 – F 0000h 0000h

0000h 0000h

0000h 0000h

127 – (O) 0000h Obsolete

Reserved for expanded, supported, and enabled settings

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

17

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 18

P400m 2.5-Inch NAND Flash SSD

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

128 – – – Security status

15–9 F 0000000b Reserved

8 V 0b Security level 0 = High, 1 = Maximum

7–6 F 00b Reserved

5 F 1b 1 = Enhanced security erase is supported

4 V 0b 1 = Security count is expired

3 V 0b 1 = Security is frozen

2 V 0b 1 = Security is locked

1 V 0b 1 = Security is enabled

0 F 1b 1 = Security is supported

129 – ( )X Vendor-specific

data

160 – – – CFA power mode 1

15 F 0b Word 160 is supported

14 F 0b Reserved

13 F 0b CFA power mode 1 is required for one or more commands

12 V 0b CFA power mode 1 is disabled

11–0 F 000000000000b Maximum current in ma

161 – X 0000h 0000h

0000h 0000h

0000h 0000h

0000h

168 15–4 F 000h Reserved

3-0 F 3h Device nominal form factor

169 – – – DATA SET MANAGEMENT command is supported

15–1 F 000000000000000bReserved

Vendor specific

implemented by the device

Reserved for assignment by the CompactFlash Association

Device ID

0 F 1b 1 = The trim bit in the DATA SET MANAGEMENT command

is supported

170 – F 0000h 0000h

Additional product identifier

0000h 0000h

174 – F 0000h 0000h Reserved

176 – (O)V Varies Current media serial number (60 ASCII characters)

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

18

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 19

P400m 2.5-Inch NAND Flash SSD

Device ID

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

206 – – – SCT command transport

15–12 X 0000b Vendor-specific

11–6 F 000000b Reserved

5 F 1b SCT command transport data tables are supported

4 F 1b SCT command transport features control is supported

3 F 0b SCT command transport error recovery control is supported

2 F 1b SCT command transport write same is supported

1 F 0b SCT command transport long sector access is supported

0 F 1b SCT command transport is supported

207 – ( )F 0000h 0000h Reserved for CE-ATA

209 – (O) – Alignment of logical blocks within a larger physical block

15 F 0b Shall be cleared to zero

14 F 1b Shall be set to one

13–0 F 00000000000000b Logical sector offset within the first physical sector where

the first logical sector is placed

210 – (O)V 0000h 0000h Write-read-verify sector count mode 3 only

212 – (O)F 0000h 0000h Verify sector count mode 2 only

214 – (O) – NV cache capabilities

15–12 F 0000b NV cache feature set version

11–8 F 0000b NV cache power mode feature set version

7–5 F 000b Reserved

4 V 0b 1 = NV cache feature set is enabled

3–2 F 00b Reserved

1 V 0b 1 = NV cache power mode feature set is enabled

0 F 0b 1 = NV cache power mode feature set is supported

215 – (O)V 0000h NV cache size in logical blocks (LSW)

216 – (O)V 0000h NV cache size in logical blocks (MSW)

217 – (M)F 0001h Nominal media rotation rate (ATA8-ACS 1699-D revision 6)

– – – NV cache read transfer speed in MB/s (ATA8-ACS 1699-D re-

vision 3f)

218 – (O)V 0000h NV cache write transfer speed in MB/s

219 – – – NV cache options

15–8 F 00h Reserved

7–0 F 00h Device estimated time to spin-up in seconds

220 15–8 F 00h Reserved

7–0 V 00h Write-read-verify feature set current mode

221 – – 0000h Reserved

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

19

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 20

P400m 2.5-Inch NAND Flash SSD

Device ID

Table 5: Identify Device (Continued)

See Note 1 for setting definitions

Word Bit(s) Setting Default Value Description

222 – – – Transport major revision number. 0000h or FFFFh = Device

does not report version

15–12 – 0001b Transport type - 0 = Parallel, 1 = Serial, 2–15 = Reserved

Parallel (type = 0), serial (type = 1)

11–6 – 000000b Reserved

5 – 1b Reserved SATA rev 3.0

4 – 1b Reserved SATA rev 2.6

3 – 1b Reserved SATA rev 2.5

2 – 1b Reserved SATA II: Extensions

1 – 1b Reserved SATA 1.0a

0 – 1b ATA8-APT ATA8-AST

223 – (M)F 0000h Transport minor revision number

224 – ( )F 0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

234 – (O)F 0001h Minimum number of 512-byte units per DOWNLOAD MI-

235 – – 00FFh Maximum number of 512-byte units per DOWNLOAD MI-

236 – – 0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

0000h 0000h

0000h

255 – (M)F – Integrity word

15–8 – Varies Checksum

7–0 – A5h Signature

Reserved for CE-ATA

CROCODE command for mode 3

CROCODE command for mode 3

Reserved

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

Note:

1. F = The content of the word is fixed and does not change.

V = The content of the word is variable and may change depending on the state of the

device or the commands executed by the device.

X = The content of the word may be fixed or variable.

R = The content of the word is reserved and will be zero.

M = Support of the word is mandatory.

O = Support of the word is optional.

20

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 21

P400m 2.5-Inch NAND Flash SSD

Commands

Table 6: Supported ATA Command Set

See ATA-8 standard for command details

Command Name Command Code (hex)

CHECK POWER MODE 98h or E5h

DATA SET MANAGEMENT 06h

DEVICE CONFIGURATION RESTORE B1h/C0h

DEVICE CONFIGURATION FREEZE LOCK B1h/C1h

DEVICE CONFIGURATION IDENTIFY B1h/C2h

DEVICE CONFIGURATION SET B1h/C3h

DOWNLOAD MICROCODE 92h

EXECUTE DEVICE DIAGNOSTIC 90h

FLUSH CACHE E7h

FLUSH CACHE EXT EAh

IDENTIFY DEVICE ECh

IDLE E3h or 97h

IDLE IMMEDIATE E1h or 95h

INITIALIZE DEVICE PARAMETERS 91h

NOP 00h

READ BUFFER E4h

READ DMA (with retry) C8h

READ DMA (without retry) C9h

READ DMA EXT 25h

READ FPDMA QUEUED 60h

READ LOG EXT 2Fh

READ LOG DMA EXT 47h

READ MULTIPLE C4h

READ MULTIPLE EXT 29h

READ NATIVE MAX ADDRESS F8h

READ NATIVE MAX ADDRESS EXT 27h

READ SECTOR(S) EXT 24h

READ SECTOR(S) (with retry) 20h

READ SECTOR(S) (without retry) 21h

READ VERIFY SECTOR EXT 42h

READ VERIFY SECTOR(S) (with retry) 40h

REQUEST SENSE DATA EXT 0Bh

SANITIZE DEVICE B4h

SECURITY DISABLE PASSWORD F6h

SECURITY ERASE PREPARE F3h

SECURITY ERASE UNIT F4h

Commands

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

21

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 22

P400m 2.5-Inch NAND Flash SSD

Table 6: Supported ATA Command Set (Continued)

See ATA-8 standard for command details

Command Name Command Code (hex)

SECURITY FREEZE LOCK F5h

SECURITY SET PASSWORD F1h

SECURITY UNLOCK F2h

SEEK 70h

SET FEATURES EFh

SET MAX ADDRESS F9h

SET MAX ADDRESS EXT 37h

SET MULTIPLE MODE C6h

SLEEP E6h or 99h

SMART DISABLE OPERATIONS B0h/D9h

SMART ENABLE OPERATIONS B0h/D8h

SMART ENABLE/DISABLE AUTOSAVE B0h/D2h

SMART EXECUTE OFF-LINE IMMEDIATE B0h/D4h

SMART READ DATA B0h/D0h

SMART READ LOG B0h/D5h

SMART RETURN STATUS B0h/DAh

SMART WRITE LOG B0h/D6h

STANDBY E2h or 96h

STANDBY IMMEDIATE E0h or 94h

WRITE BUFFER E8h

WRITE DMA (with retry) CAh

WRITE DMA (without retry) CBh

WRITE DMA EXT 35h

WRITE DMA FUA EXT 3Dh

WRITE FPDMA QUEUED 61h

WRITE LOG EXT 3Fh

WRITE LOG DMA EXT 57h

WRITE MULTIPLE C5h

WRITE MULTIPLE EXT 39h

WRITE MULTIPLE FUA EXT CEh

WRITE SECTOR(S) (with retry) 30h

WRITE SECTOR(S) EXT 34h

WRITE UNCORRECTABLE EXT 45h

Commands

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

22

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 23

P400m 2.5-Inch NAND Flash SSD

Performance

Performance

Measured performance can vary for a number of reasons. The major factors affecting

drive performance are the density of the drive and the interface of the host. Additionally, overall system performance can affect the measured drive performance. When comparing drives, it is recommended that all system variables are the same, and only the

drive being tested varies.

Performance numbers will vary depending on the host system configuration.

Table 7: Drive Performance

Density 100GB 200GB 400GB Unit

Sequential read (64KB transfer) 380 380 380 MB/s

Sequential write (64KB transfer) 200 310 310 MB/s

Random read (4KB transfer) 52,000 54,000 60,000 IOPS

Random write (4KB transfer) 21,000 26,000 26,000 IOPS

READ latency (TYP) 0.57 0.51 0.51 ms

WRITE latency (TYP) 2 2 2 ms

Notes:

Reliability

Micron’s SSDs incorporate advanced technology for defect and error management.

They use various combinations of hardware-based error correction algorithms and

firmware-based static and dynamic wear-leveling algorithms.

Over the life of the SSD, uncorrectable errors may occur. An uncorrectable error is defined as data that is reported as successfully programmed to the SSD but when it is read

out of the SSD, the data differs from what was programmed.

Table 8: Uncorrectable Bit Error Rate

Uncorrectable Bit Error Rate Operation

<1 sector per 1016 bits READ

Mean Time to Failure

Mean time to failure (MTTF) for the SSD can be predicted based on the component reliability data using the methods referenced in the Telcordia SR-332 reliability prediction

procedures for electronic equipment.

1. Typical I/O performance numbers as measured using Iometer with a queue depth of 32

and write cache disabled.

2. Iometer measurements are performed in the steady state region.

3. 4KB transfers used for READ/WRITE latency values.

4. System variations may affect measured results.

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

Table 9: MTTF

Density MTTF (Operating Hours)

100GB 2 million

23

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

1

Page 24

Table 9: MTTF (Continued)

P400m 2.5-Inch NAND Flash SSD

Reliability

Endurance

Density MTTF (Operating Hours)

200GB 2 million

400GB 2 million

Note:

1. The product achieves a MTTF of 2 million hours based on population statistics not relevant to individual units.

Endurance for the SSD can be predicted based on the usage conditions applied to the

device, the internal NAND component cycles, the write amplification factor, and the

wear-leveling efficiency of the drive. Total bytes written measured with 55°C case temperature within the total bytes written values listed in this document. The table below

shows the drive lifetime for each SSD density based on predefined usage conditions.

Table 10: Drive Lifetime

Density Drive Lifetime (Total Bytes Written)

100GB 1.75PB

200GB 3.5PB

400GB 7PB

Notes:

1. Total bytes written calculated with the drive 90% full.

2. Access patterns are 50% sequential and 50% random and consist of the following: 5%

are 4KB; 5% are 8KB; 10% are 16KB; 10% are 32KB; 35% are 64KB; and 35% are 128KB.

1

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

24

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 25

P400m 2.5-Inch NAND Flash SSD

Electrical Characteristics

Electrical Characteristics

Stresses greater than those listed may cause permanent damage to the device. This is a

stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

reliability.

Table 11: SATA Power Consumption

Density Idle Average Sequential Write/Read Max (128KB transfer)

100GB 170mW 5.3W <5.3W

200GB 170mW 9W <9W

400GB 170mW 10W <10W

Notes:

1. Data taken at 25°C using a 6 Gb/s SATA interface.

2. Sequential power measured in IOMETER MAX with 128KB transfer size.

Table 12: Maximum Ratings

Parameter/Condition Symbol Min Max Unit

Voltage input V5 4.5 5.5 V

Operating temperature T

Non-operating temperature – –40 85 °C

Rate of temperature change – – 20 °C/hour

Relative humidity (non-condensing) – 5 95 %

C

0 70 °C

Table 13: Shock and Vibration

Parameter/Condition Specification

Operating shock 1,000G/0.5ms

Operating vibration 2–500Hz at 3.1G

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

25

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 26

Compliance

P400m 2.5-Inch NAND Flash SSD

Compliance

Micron SSDs comply with the following:

• RoHS

• CE (Europe): EN55022, 2006 + A1:2007 and EN55024, 1998 + A1:2001 + A2:2003

• FCC: CFR Title 47, Part 15 Class A

• UL/cUL: approval to UL-60950-1, 2nd Edition, IEC 60950-1:2005 (2nd Edition); Am

1:2009, EN 60950-1 (2006) + A11:2009+ A1:2010 + A12:2011

• BSMI (Taiwan): approval to CNS 13438

• C-TICK (Australia, New Zealand): approval to AS/NZS CISPR22

• KCC RRL (Korea): approval to KCC-REM-MU2-P400m25

• W.E.E.E.: Compliance with EU WEEE directive 2002/96/EC. Additional obligations

may apply to customers who place these products in the markets where WEEE is enforced

• TUV (Germany): approval to IEC60950/EN60950

• V

CCI

• IC (Canada):

– This Class B digital apparatus complies with Canadian ICES-003.

– Cet appareil numérique de la classe B est conforme à la norme NMB-003 du Cana-

da.

FCC Rules

This equipment has been tested and found to comply with the limits for a Class A digital

device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a

commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual,

may cause harmful interference to radio communications. Operation of this equipment

in a residential area is likely to cause harmful interference in which case the user will be

required to correct the interference at his own expense.

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

26

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 27

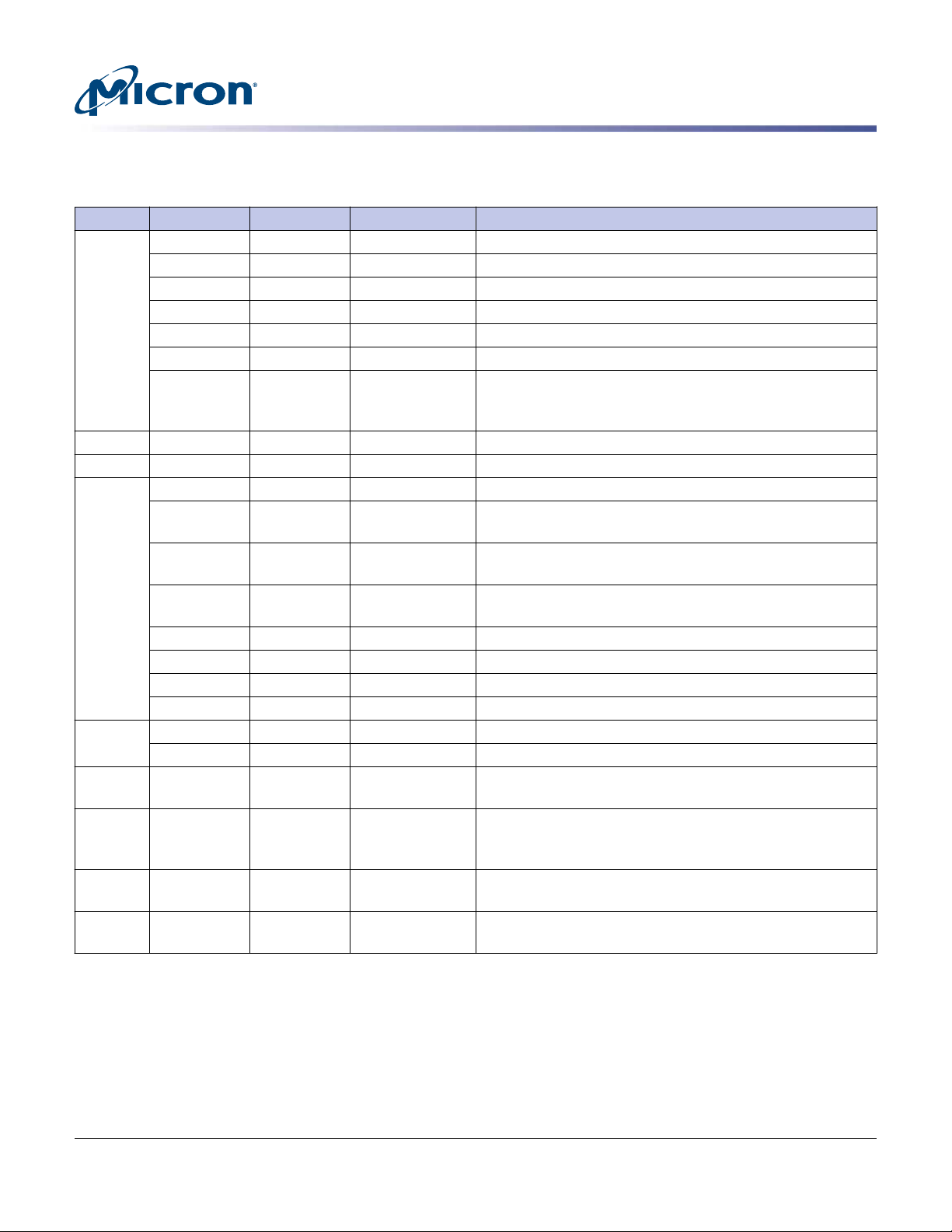

Package Dimensions

100.50mm/3.957in

for reference only

0.30mm/0.012in

for reference only

14.00mm

0.551in

90.60mm

3.567in

100.20mm ±0.25

3.957in ±0.010

4.07mm

0.160in

61.71mm

2.430in

3.0mm RAD

0.12in

(4 PLCS)

D&TM3 x 0.5mm

(4 PLCS)

14.00mm

0.551in

(both sides)

90.60mm

3.567in

(both sides)

3.00mm

0.118in

(2 PLCS)

(both sides)

D&TM3 x 0.5mm

(2 PLCS)(both sides)

3.50mm ±0.38

0.138in ±0.015

13.43mm/0.529in

for reference only

7.00mm

+0.00

-0.20

0.276in

+0.000

-0.008

9.40mm

0.370in

69.85mm ±0.25

2.750in ±0.010

3mm 3mm

Center thermocouple here

Power and data connectors

3mm

3mm

73.62mm

36.3mm

33.54mm

26.88mm

Non-label side of SSD

Figure 4: 2.5-Inch Package – 7mm

P400m 2.5-Inch NAND Flash SSD

Package Dimensions

Figure 5: Thermocouple Placement Guidelines for Temperature Measurement

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

27

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 28

References

P400m 2.5-Inch NAND Flash SSD

References

• Serial ATA: High-speed serialized AT attachment, Serial ATA working group, available

at www.sata-io.org

• SATA 3.0 GOLD

• ATA-8 Rev. 4

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

28

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Page 29

Revision History

Rev. H – 11/13

Rev. G – 5/13

Rev. F – 4/13

Rev. E – 2/13

Rev. D – 2/13

P400m 2.5-Inch NAND Flash SSD

Revision History

• Updated descriptions for bits 1 and 2 for Word 119

• Updated Compliance section

• Updated Compliance section

• Updated power consumption and operating shock numbers in Electrical Characteristics section

• Updated performance numbers in Features and Performance sections

Rev. C – 1/13

Rev. B – 2/12

Rev. A – 1/12

• Updated READ latency

• Updated default value of word 119, bit 1 in Identify Device table

• Updated default value of word 212 in Identify Device table

• Updated note 1 of Identity Device table

• Removed unavailable commands from the Commands section

• Updated 200GB in Drive Lifetime table

• Updated Compliance section

• Updated Features

• Added specifications throughout for 200GB and 400GB densities

• Updated Thermocouple Placement Guidelines figure

• Initial release

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

www.micron.com/productsupport Customer Comment Line: 800-932-4992

Micron and the Micron logo are trademarks of Micron Technology, Inc.

All other trademarks are the property of their respective owners.

This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein.

Although considered final, these specifications are subject to change, as further product development and data characterization some-

times occur.

PDF: 09005aef84952553

p400m_2_5.pdf - Rev. H 11/13 EN

29

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2011 Micron Technology, Inc. All rights reserved.

Loading...

Loading...