Page 1

Module height: 30mm (1.18in)

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DDR3 SDRAM SODIMM

MT8JSF12864HZ – 1GB

MT8JSF25664HZ – 2GB

DIMM

Features

Features

• DDR3 functionality and operations supported as

defined in the component data sheet

• 204-pin, small-outline dual in-line memory module

(SODIMM)

• Fast data transfer rates: PC3-12800, PC3-10600,

PC3-8500, or PC3-6400

• 1GB (128 Meg x 64)

• 2GB (256 Meg x 64)

• VDD = 1.5V ±0.075V

• V

• Nominal and dynamic on-die termination (ODT) for

data, strobe, and mask signals

• Single rank

• On-board I2C temperature sensor with integrated

serial presence-detect (SPD) EEPROM

• 8 internal device banks

• Fixed burst chop (BC) of 4 and burst length (BL) of 8

via the mode register set (MRS)

• Selectable BC4 or BL8 on-the-fly (OTF)

• Gold edge contacts

• Halogen-free

• Fly-by topology

• Terminated control, command, and address bus

= +3.0V to +3.6V

DDSPD

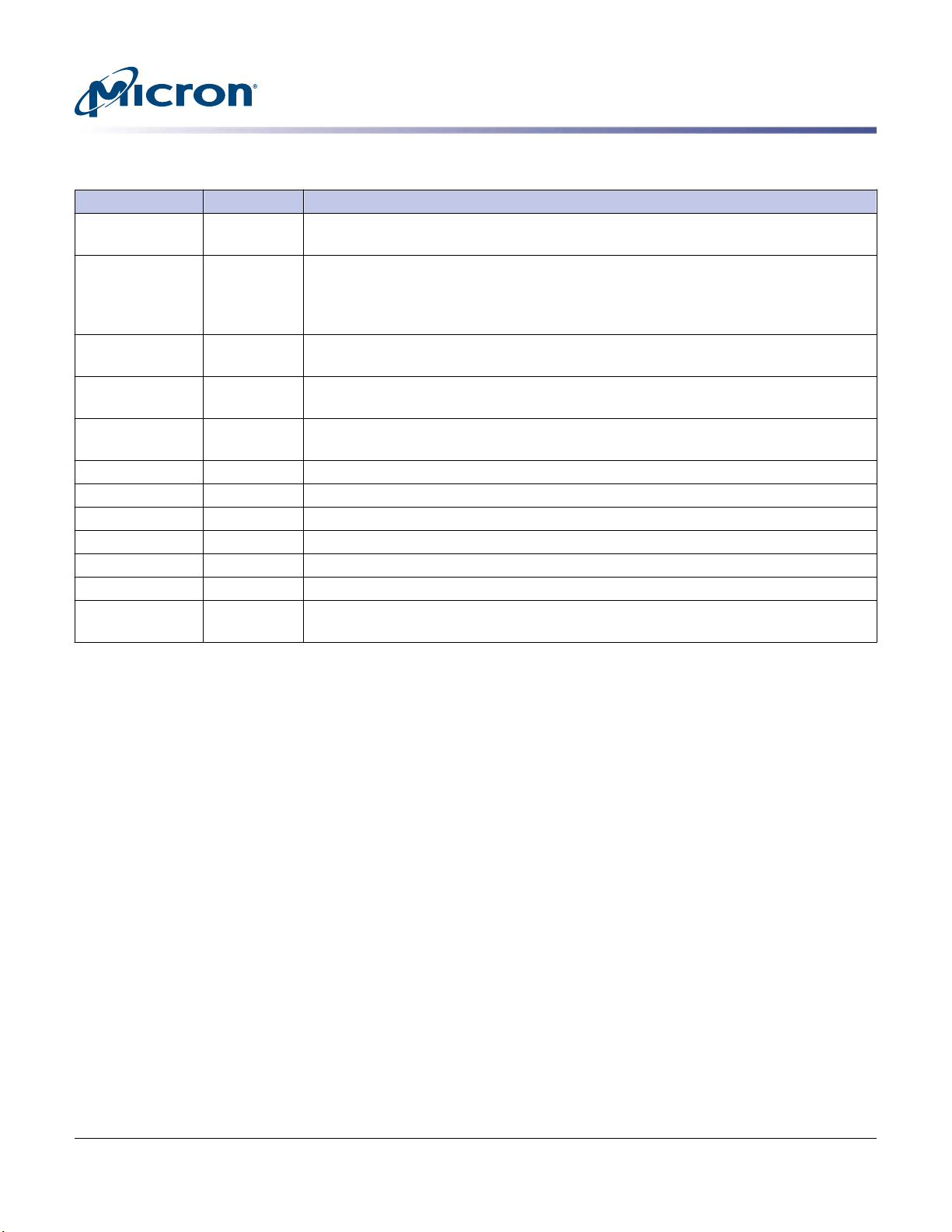

Figure 1: 204-Pin SODIMM (MO-268 R/C B)

Options Marking

• Operating temperature

– Commercial (0°C ≤ TA ≤ +70°C) None

– Industrial (–40°C ≤ TA ≤ +85°C) I

• Package

– 204-pin DIMM (halogen-free) Z

• Frequency/CAS latency

– 1.25ns @ CL = 11 (DDR3-1600) -1G6

– 1.5ns @ CL = 9 (DDR3-1333) -1G4

– 1.87ns @ CL = 7 (DDR3-1066) -1G1

Note:

1. Contact Micron for industrial temperature

module offerings.

1

Table 1: Key Timing Parameters

Speed

Grade

-1G6 PC3-12800 1600 1333 1333 1066 1066 800 667 13.125 13.125 48.125

-1G4 PC3-10600 – 1333 1333 1066 1066 800 667 13.125 13.125 49.125

-1G1 PC3-8500 – – – 1066 1066 800 667 13.125 13.125 50.625

-1G0 PC3-8500 – – – 1066 – 800 667 15 15 52.5

-80B PC3-6400 – – – – – 800 667 15 15 52.5

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

Nomenclature

Industry

Products and specifications discussed herein are subject to change by Micron without notice.

Data Rate (MT/s) t

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

RCD

(ns)

t

RP

(ns)

t

RC

(ns)CL = 11 CL = 10 CL = 9 CL = 8 CL = 7 CL = 6 CL = 5

Page 2

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

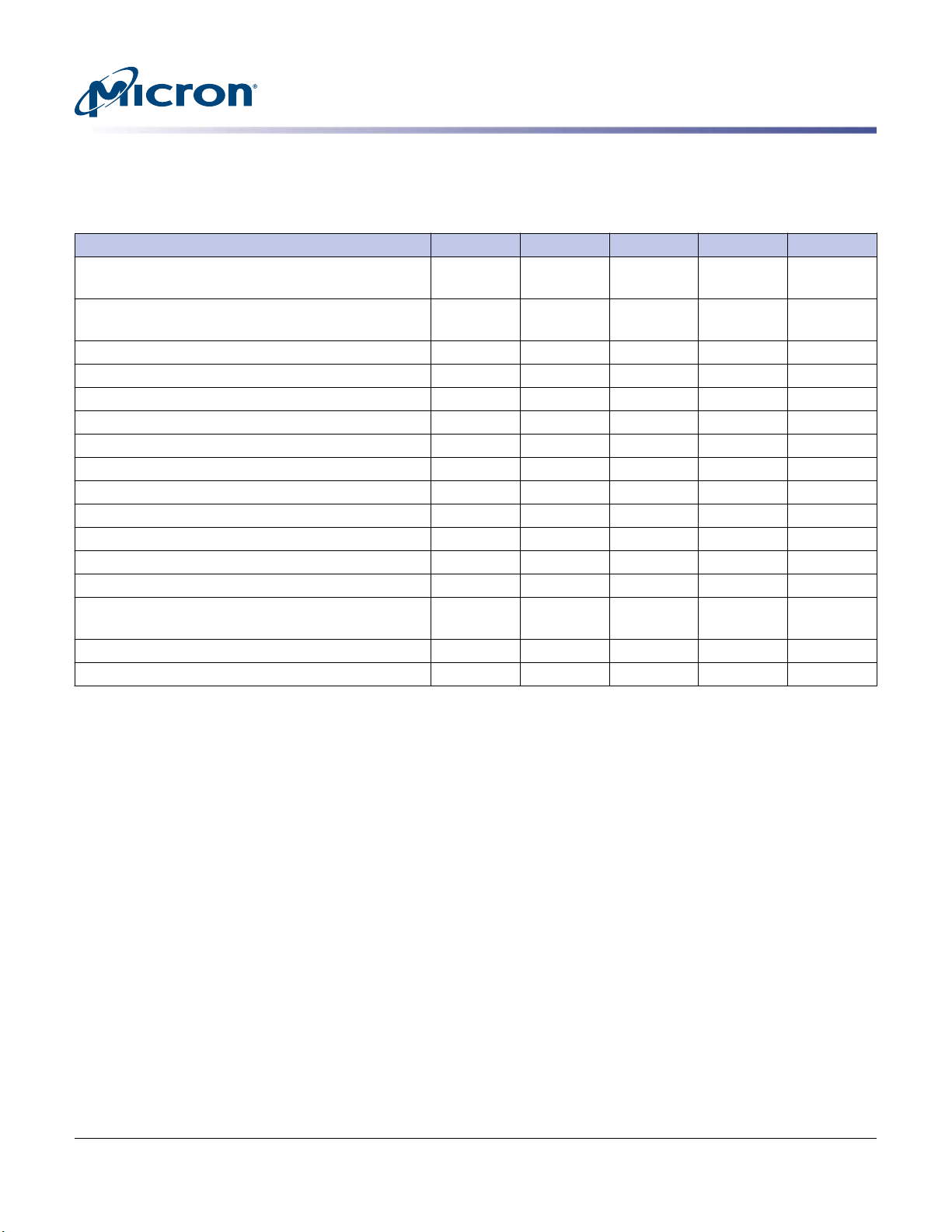

Table 2: Addressing

Parameter 1GB 2GB

Refresh count 8K 8K

Row address 16K A[13:0] 32K A[14:0]

Device bank address 8 BA[2:0] 8 BA[2:0]

Device configuration 1Gb (128 Meg x 8) 2Gb (256 Meg x 8)

Column address 1K A[9:0] 1K A[9:0]

Module rank address 1 S0# 1 S0#

Table 3: Part Numbers and Timing Parameters – 1GB Modules

Base device: MT41J128M8,1 1Gb DDR3 SDRAM

Part Number

2

Density Configuration

MT8JSF12864H(I)Z-1G6__ 1GB 128 Meg x 64 12.8 GB/s 1.25ns/1600 MT/s 11-11-11

MT8JSF12864H(I)Z-1G4__ 1GB 128 Meg x 64 10.6 GB/s 1.5ns/1333 MT/s 9-9-9

MT8JSF12864H(I)Z-1G1__ 1GB 128 Meg x 64 8.5 GB/s 1.87ns/1066 MT/s 7-7-7

Module

Module

Bandwidth

Memory Clock/

Data Rate

Clock Cycles

(CL-tRCD-tRP)

DIMM

Features

Table 4: Part Numbers and Timing Parameters – 2GB Modules

Base device: MT41J256M8,1 2Gb DDR3 SDRAM

Part Number

22

Density Configuration

MT8JSF25664H(I)Z-1G6__ 2GB 256 Meg x 64 12.8 GB/s 1.25ns/1600 MT/s 11-11-11

MT8JSF25664H(I)Z-1G4__ 2GB 256 Meg x 64 10.6 GB/s 1.5ns/1333 MT/s 9-9-9

MT8JSF25664H(I)Z-1G1__ 2GB 256 Meg x 64 8.5 GB/s 1.87ns/1066 MT/s 7-7-7

Module

Notes:

1. The data sheet for the base device can be found on Micron’s Web site.

2. All part numbers end with a two-place code (not shown) that designates component and PCB revisions.

Consult factory for current revision codes. Example: MT8JSF12864HZ-1G1D1.

Module

Bandwidth

Memory Clock/

Data Rate

Clock Cycles

(CL-tRCD-tRP)

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 3

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

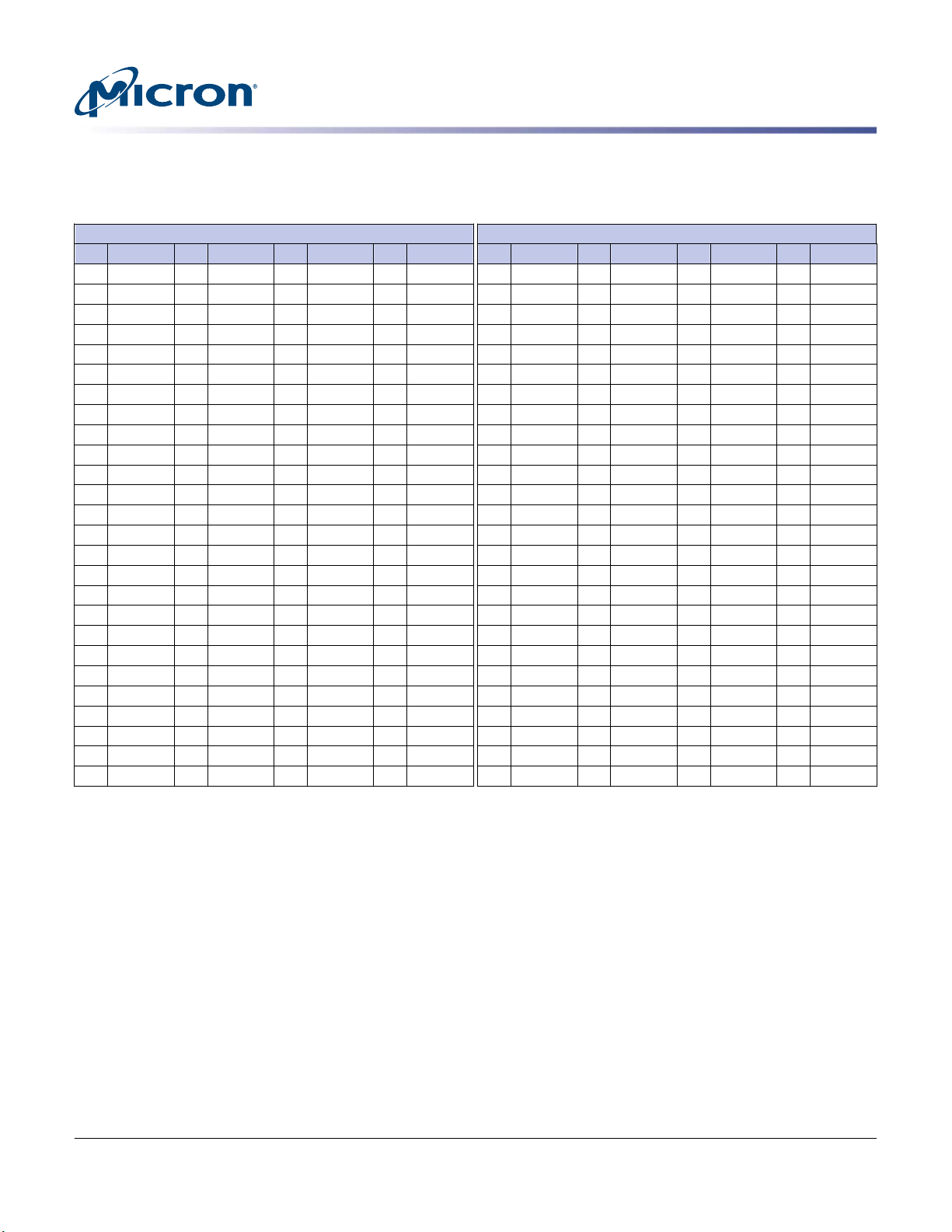

Pin Assignments

Pin Assignments

Table 5: Pin Assignments

204-Pin DDR3 SODIMM Front 204-Pin DDR3 SODIMM Back

Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol

1 V

REFDQ

3 V

5 DQ0 57 DQ24 109 BA0 161 V

7 DQ1 59 DQ25 111 V

9 V

11 DM0 63 DM3 115 CAS# 167 V

13 V

15 DQ2 67 DQ26 119 A13 171 DQS6 16 DQ6 68 DQ30 120 NC 172 V

17 DQ3 69 DQ27 121 NC 173 V

19 V

21 DQ8 73 CKE0 125 NC 177 DQ51 22 DQ12 74 NC 126 V

23 DQ9 75 V

25 V

27 DQS1# 79 BA2 131 DQ33 183 DQ57 28 DM1 80 NF/A14 132 DQ37 184 V

29 DQS1 81 V

31 V

33 DQ10 85 A9 137 DQS4 189 V

35 DQ11 87 V

37 V

39 DQ16 91 A5 143 DQ35 195 V

41 DQ17 93 V

43 V

45 DQS2# 97 A1 149 DQ41 201 SA1 46 DM2 98 A0 150 V

47 DQS2 99 V

49 V

51 DQ18 103 CK0# 155 V

53 DQ19 105 V

55 V

SS

61 V

SS

65 V

SS

71 V

SS

77 NC 129 DQ32 181 DQ56 26 V

SS

83 A12 135 DQS4# 187 DM7 32 V

SS

89 A8 141 DQ34 193 DQ59 38 V

SS

95 A3 147 DQ40 199 V

SS

101 CK0 153 DM5 – – 50 DQ22 102 CK1 154 DQS5 – –

SS

107 A10 159 DQ43 4 DQ4 56 DQ28 108 BA1 160 DQ47

SS

113 WE# 165 DQ49 10 DQS0# 62 DQ3# 114 S0# 166 DQ53

SS

117 V

SS

123 V

SS

127 V

DD

133 V

DD

139 V

DD

145 V

DD

151 V

DD

157 DQ42 2 V

DD

SS

163 DQ48 8 V

DD

SS

169 DQS6# 14 V

DD

SS

175 DQ50 20 V

DD

179 V

SS

185 V

SS

191 DQ58 36 DQ15 88 V

SS

197 SA0 42 DQ21 94 V

SS

203 V

SS

SS

– – 52 DQ23 104 CK1# 156 V

SS

SS

SS

SS

DDSPD

TT

6 DQ5 58 DQ29 110 RAS# 162 V

12 DQS0 64 DQ3 116 ODT0 168 V

18 DQ7 70 DQ31 122 NC 174 DQ54

24 DQ13 76 V

30 RESET# 82 V

34 DQ14 86 A7 138 V

40 DQ20 92 A4 144 V

44 V

48 V

SS

SS

SS

SS

SS

SS

SS

SS

SS

54 V

60 V

66 V

72 V

SS

SS

SS

SS

DD

106 V

112 V

118 V

124 V

128 V

DD

DD

DD

DD

REFCA

SS

78 NC 130 DQ36 182 DQ61

134 V

DD

SS

84 A11 136 DM4 188 DQS7

SS

140 DQ38 192 DQ62

DD

90 A6 142 DQ39 194 DQ63

SS

146 DQ44 198 EVENT#

DD

96 A2 148 DQ45 200 SDA

SS

100 V

152 DQS5# 204 V

DD

SS

158 DQ46

164 DQ52

170 DM6

176 DQ55

178 V

180 DQ60

186 DQS7#

190 V

196 V

202 SCL

– –

SS

SS

SS

SS

SS

SS

SS

TT

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 4

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

Pin Descriptions

Pin Descriptions

The pin description table below is a comprehensive list of all possible pins for all DDR3

modules. All pins listed may not be supported on this module. See Pin Assignments for

information specific to this module.

Table 6: Pin Descriptions

Symbol Type Description

Ax Input Address inputs: Provide the row address for ACTIVE commands, and the column ad-

dress and auto precharge bit (A10) for READ/WRITE commands, to select one location

out of the memory array in the respective bank. A10 sampled during a PRECHARGE

command determines whether the PRECHARGE applies to one bank (A10 LOW, bank

selected by BAx) or all banks (A10 HIGH). The address inputs also provide the op-code

during a LOAD MODE command. See the Pin Assignments Table for density-specific

addressing information.

BAx Input Bank address inputs: Define the device bank to which an ACTIVE, READ, WRITE, or

PRECHARGE command is being applied. BA define which mode register (MR0, MR1,

MR2, or MR3) is loaded during the LOAD MODE command.

CKx,

CKx#

CKEx Input Clock enable: Enables (registered HIGH) and disables (registered LOW) internal circui-

DMx Input Data mask (x8 devices only): DM is an input mask signal for write data. Input data

ODTx Input On-die termination: Enables (registered HIGH) and disables (registered LOW) termi-

Par_In Input Parity input: Parity bit for Ax, RAS#, CAS#, and WE#.

RAS#, CAS#, WE# Input Command inputs: RAS#, CAS#, and WE# (along with S#) define the command being

RESET# Input

Sx# Input Chip select: Enables (registered LOW) and disables (registered HIGH) the command

SAx Input Serial address inputs: Used to configure the temperature sensor/SPD EEPROM ad-

SCL Input Serial clock for temperature sensor/SPD EEPROM: Used to synchronize communi-

CBx I/O Check bits: Used for system error detection and correction.

DQx I/O Data input/output: Bidirectional data bus.

DQSx,

DQSx#

Input Clock: Differential clock inputs. All control, command, and address input signals are

sampled on the crossing of the positive edge of CK and the negative edge of CK#.

try and clocks on the DRAM.

is masked when DM is sampled HIGH, along with that input data, during a write access. Although DM pins are input-only, DM loading is designed to match that of the

DQ and DQS pins.

nation resistance internal to the DDR3 SDRAM. When enabled in normal operation,

ODT is only applied to the following pins: DQ, DQS, DQS#, DM, and CB. The ODT input

will be ignored if disabled via the LOAD MODE command.

entered.

Reset: RESET# is an active LOW asychronous input that is connected to each DRAM

(LVCMOS)

I/O Data strobe: Differential data strobes. Output with read data; edge-aligned with

and the registering clock driver. After RESET# goes HIGH, the DRAM must be reinitialized as though a normal power-up was executed.

decoder.

dress range on the I2C bus.

cation to and from the temperature sensor/SPD EEPROM on the I2C bus.

read data; input with write data; center-aligned with write data.

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 5

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

Table 6: Pin Descriptions (Continued)

Symbol Type Description

SDA I/O Serial data: Used to transfer addresses and data into and out of the temperature sen-

sor/SPD EEPROM on the I2C bus.

TDQSx,

TDQSx#

Err_Out# Output

EVENT# Output

V

DD

V

DDSPD

V

REFCA

V

REFDQ

V

SS

V

TT

NC – No connect: These pins are not connected on the module.

NF – No function: These pins are connected within the module, but provide no functional-

Output Redundant data strobe (x8 devices only): TDQS is enabled/disabled via the LOAD

MODE command to the extended mode register (EMR). When TDQS is enabled, DM is

disabled and TDQS and TDQS# provide termination resistance; otherwise, TDQS# are

no function.

Parity error output: Parity error found on the command and address bus.

(open drain)

Temperature event:The EVENT# pin is asserted by the temperature sensor when criti-

(open drain)

cal temperature thresholds have been exceeded.

Supply Power supply: 1.5V ±0.075V. The component VDD and V

module VDD.

Supply Temperature sensor/SPD EEPROM power supply: 3.0–3.6V.

Supply Reference voltage: Control, command, and address VDD/2.

Supply Reference voltage: DQ, DM VDD/2.

Supply Ground.

Supply Termination voltage: Used for control, command, and address VDD/2.

ity.

Pin Descriptions

are connected to the

DDQ

DIMM

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 6

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DQ Map

Table 7: Component-to-Module DQ Map

DIMM

DQ Map

Component

Reference

Number

U1 0 2 15 U2 0 22 50

U3 0 34 141 U4 0 50 175

U6 0 61 182 U7 0 45 148

U8 0 29 58 U9 0 9 23

Component

DQ Module DQ

1 1 7 1 17 41

2 6 16 2 18 51

3 5 6 3 21 42

4 7 18 4 23 52

5 0 5 5 16 39

6 3 17 6 19 53

7 4 4 7 20 40

1 36 130 1 53 166

2 38 140 2 54 174

3 33 131 3 49 165

4 35 143 4 55 176

5 32 129 5 48 163

6 39 142 6 51 177

7 37 132 7 52 164

1 62 192 1 42 157

2 57 183 2 44 146

3 58 191 3 46 158

4 60 180 4 40 147

5 59 193 5 47 160

6 56 181 6 41 149

7 63 194 7 43 159

1 26 67 1 10 33

2 25 59 2 13 24

3 31 70 3 11 35

4 24 57 4 12 22

5 30 68 5 15 36

6 28 56 6 8 21

7 27 69 7 14 34

Module Pin

Number

Component

Reference

Number

Component

DQ Module DQ

Module Pin

Number

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

6

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 7

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

U1

DM CS# DQS DQS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

U3

DM CS# DQS DQS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

U9

DM CS# DQS DQS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

U2

DM CS# DQS DQS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

U8

DM CS# DQS DQS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

U7

DM CS# DQS DQS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

U4

DM CS# DQS DQS#

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

ZQ

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

U6

DM CS# DQS DQS#

DQS0#

DQS0

DM0

S0#

DQS1#

DQS1

DM1

DQS2#

DQS2

DM2

DQS3#

DQS3

DM3

DQS4#

DQS4

DM4

DQS5#

DQS5

DM5

DQS6#

DQS6

DM6

DQS7#

DQS7

DM7

BA[2:0]

A[14/13:0]

RAS#

CAS#

WE#

CKE0

ODT0

RESET#

BA[2:0]: DDR3 SDRAM

A[14/13:0]: DDR3 SDRAM

RAS#: DDR3 SDRAM

CAS#: DDR3 SDRAM

WE#: DDR3 SDRAM

CKE0: DDR3 SDRAM

ODT0: DDR3 SDRAM

RESET#: DDR3 SDRAM

DDR3 SDRAM x 8

CK0

CK0#

CK1

CK1#

V

REFCA

V

SS

DDR3 SDRAM

DDR3 SDRAM

V

DD

DDR3 SDRAM

V

DDSPD

Temperature sensor/

SPD EEPROM

V

TT

DDR3 SDRAM

DDR3 SDRAM

V

REFDQ

Clock, control, command, and address line terminations:

V

SS

A0

Temperature

sensor/

SPD EEPROM

A1 A2

SA0 SA1

SDA

SCL

EVT

EVENT#

U10

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

CKE0, A[14/13:0],

RAS#, CAS#, WE#,

S0#, ODT0, BA[2:0]

DDR3

SDRAM

V

TT

CK

CK#

DDR3

SDRAM

V

DD

Vss

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

Functional Block Diagram

Figure 2: Functional Block Diagram

DIMM

Functional Block Diagram

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

Note:

1. The ZQ ball on each DDR3 component is connected to an external 240Ω ±1% resistor

that is tied to ground. It is used for the calibration of the component’s ODT and output

driver.

7

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 8

General Description

DDR3 SDRAM modules are high-speed, CMOS dynamic random access memory modules that use internally configured 8-bank DDR3 SDRAM devices. DDR3 SDRAM modules use DDR architecture to achieve high-speed operation. DDR3 architecture is essentially an 8n-prefetch architecture with an interface designed to transfer two data words

per clock cycle at the I/O pins. A single read or write access for the DDR3 SDRAM module effectively consists of a single 8n-bit-wide, one-clock-cycle data transfer at the internal DRAM core and eight corresponding n-bit-wide, one-half-clock-cycle data transfers

at the I/O pins.

DDR3 modules use two sets of differential signals: DQS, DQS# to capture data and CK

and CK# to capture commands, addresses, and control signals. Differential clocks and

data strobes ensure exceptional noise immunity for these signals and provide precise

crossing points to capture input signals.

Fly-By Topology

DDR3 modules use faster clock speeds than earlier DDR technologies, making signal

quality more important than ever. For improved signal quality, the clock, control, command, and address buses have been routed in a fly-by topology, where each clock, control, command, and address pin on each DRAM is connected to a single trace and terminated (rather than a tree structure, where the termination is off the module near the

connector). Inherent to fly-by topology, the timing skew between the clock and DQS signals can be easily accounted for by using the write-leveling feature of DDR3.

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

General Description

Temperature Sensor with Serial Presence-Detect EEPROM

Thermal Sensor Operations

The temperature from the integrated thermal sensor is monitored and converts into a

digital word via the I2C bus. System designers can use the user-programmable registers

to create a custom temperature-sensing solution based on system requirements. Programming and configuration details comply with JEDEC standard No. 21-C page 4.7-1,

"Definition of the TSE2002av, Serial Presence Detect with Temperature Sensor."

Serial Presence-Detect EEPROM Operation

DDR3 SDRAM modules incorporate serial presence-detect. The SPD data is stored in a

256-byte EEPROM. The first 128 bytes are programmed by Micron to comply with JEDEC standard JC-45, "Appendix X: Serial Presence Detect (SPD) for DDR3 SDRAM Modules." These bytes identify module-specific timing parameters, configuration information, and physical attributes. The remaining 128 bytes of storage are available for use by

the customer. System READ/WRITE operations between the master (system logic) and

the slave EEPROM device occur via a standard I2C bus using the DIMM’s SCL (clock)

SDA (data), and SA (address) pins. Write protect (WP) is connected to VSS, permanently

disabling hardware write protection. For further information refer to Micron technical

note TN-04-42, "Memory Module Serial Presence-Detect."

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 9

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

Electrical Specifications

Electrical Specifications

Stresses greater than those listed may cause permanent damage to the module. This is a

stress rating only, and functional operation of the module at these or any other conditions outside those indicated in each device's data sheet is not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability.

Table 8: Absolute Maximum Ratings

Symbol Parameter Min Max Units

V

DD

VIN, V

Table 9: Operating Conditions

Symbol Parameter Min Nom Max Units Notes

V

DD

I

VTT

V

TT

I

I

I

OZ

I

VREF

T

A

T

C

VDD supply voltage relative to V

Voltage on any pin relative to V

OUT

SS

SS

–0.4 1.975 V

–0.4 1.975 V

VDD supply voltage 1.425 1.5 1.575 V

Termination reference current from

V

TT

Termination reference voltage (DC) –

–600 – +600 mA

0.49 × VDD - 20mV 0.5 × V

0.51 × VDD + 20mV V 1

DD

command/address bus

Input leakage current;

Any input 0V ≤ VIN ≤

VDD;

V

input 0V ≤ VIN ≤

REF

0.95V (All other pins

not under test = 0V)

Output leakage current;

0V ≤ V

OUT

≤ VDD;

Address in-

–16 0 16 µA

puts, RAS#,

CAS#, WE#,

S#, CKE, ODT,

BA, CK, CK#

DM –2 0 2

DQ, DQS,

–5 0 5 µA

DQS#

DQ and ODT are

disabled; ODT is HIGH

V

supply leakage current;

REF

V

DQ = VDD/2 or V

REF

REFCA

= VDD/2

–8 0 8 µA

(All other pins not under test = 0V)

Module ambient

operating temperature

DDR3 SDRAM component case operating

Commercial 0 – 70 °C 2, 3

Industrial –40 – 85 °C

Commercial 0 – 95 °C 2, 3, 4

Industrial –40 – 95 °C

temperature

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

Notes:

1. VTT termination voltage in excess of the stated limit will adversely affect the command

and address signals’ voltage margin and will reduce timing margins.

2. TA and TC are simultaneous requirements.

3. For further information, refer to technical note TN-00-08: “Thermal Applications,”

available on Micron’s Web site.

4. The refresh rate is required to double when 85°C < TC ≤ 95°C.

9

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 10

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

DRAM Operating Conditions

DRAM Operating Conditions

Recommended AC operating conditions are given in the DDR3 component data sheets.

Component specifications are available on Micron’s web site. Module speed grades correlate with component speed grades, as shown below.

Table 10: Module and Component Speed Grades

DDR3 components may exceed the listed module speed grades; module may not be available in all listed speed grades

Module Speed Grade Component Speed Grade

-2G1 -093

-1G9 -107

-1G6 -125

-1G4 -15E

-1G1 -187E

-1G0 -187

-80C -25E

-80B -25

Design Considerations

Simulations

Micron memory modules are designed to optimize signal integrity through carefully designed terminations, controlled board impedances, routing topologies, trace length

matching, and decoupling. However, good signal integrity starts at the system level.

Micron encourages designers to simulate the signal characteristics of the system's

memory bus to ensure adequate signal integrity of the entire memory system.

Power

Operating voltages are specified at the DRAM, not at the edge connector of the module.

Designers must account for any system voltage drops at anticipated power levels to ensure the required supply voltage is maintained.

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

10

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 11

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

IDD Specifications

IDD Specifications

Table 11: DDR3 IDD Specifications and Conditions – 1GB

Values are for the MT41J128M8 DDR3 SDRAM only and are computed from values specified in the 1Gb (128 Meg x 8) component data sheet

Parameter Symbol 1600 1333 1066 Units

Operating current 0: One bank ACTIVATE-to-PRECHARGE

Operating current 1: One bank ACTIVATE-to-READto-PRECHARGE

Precharge power-down current: Slow exit I

Precharge power-down current: Fast exit I

Precharge quiet standby current I

Precharge standby current I

Precharge standby ODT current I

Active power-down current I

Active standby current I

Burst read operating current I

Burst write operating current I

Refresh current I

Self refresh temperature current: MAX TC = 85°C I

Self refresh temperature current (SRT-enabled): MAX

TC = 95°C

All banks interleaved read current I

Reset current I

I

DD0

I

DD1

DD2P

DD2P

DD2Q

DD2N

DD2NT

DD3P

DD3N

DD4R

DD4W

DD5

DD6

I

DD6ET

DD7

DD8

960 880 800 mA

1120 1040 960 mA

96 96 96 mA

360 320 280 mA

536 480 424 mA

560 520 440 mA

760 680 600 mA

360 320 280 mA

536 496 456 mA

2000 1600 1280 mA

2000 1760 1520 mA

2080 1920 1760 mA

48 48 48 mA

72 72 72 mA

4800 3920 3120 mA

112 112 112 mA

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

11

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 12

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

IDD Specifications

Table 12: DDR3 IDD Specifications and Conditions – 2GB (Die Revision D)

Values are for the MT41J256M8 DDR3 SDRAM only and are computed from values specified in the 2Gb (256 Meg x 8) component data sheet

Parameter Symbol 1600 1333 1066 Units

Operating current 0: One bank ACTIVATE-to-PRECHARGE

Operating current 1: One bank ACTIVATE-to-READto-PRECHARGE

Precharge power-down current: Slow exit I

Precharge power-down current: Fast exit I

Precharge quiet standby current I

Precharge standby current I

Precharge standby ODT current I

Active power-down current I

Active standby current I

Burst read operating current I

Burst write operating current I

Refresh current I

Self refresh temperature current: MAX TC = 85°C I

Self refresh temperature current (SRT-enabled): MAX

TC = 95°C

All banks interleaved read current I

Reset current I

I

DD0

I

DD1

DD2P

DD2P

DD2Q

DD2N

DD2NT

DD3P

DD3N

DD4R

DD4W

DD5

DD6

I

DD6ET

DD7

DD8

760 680 600 mA

840 800 760 mA

96 96 96 mA

280 240 200 mA

320 280 240 mA

336 296 256 mA

400 360 320 mA

320 280 240 mA

360 320 280 mA

1440 1280 1120 mA

1480 1320 1160 mA

1720 1600 1520 mA

96 96 96 mA

120 120 120 mA

3480 3080 2680 mA

112 112 112 mA

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

12

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 13

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

IDD Specifications

Table 13: DDR3 IDD Specifications and Conditions – 2GB (Die Revision M)

Values are for the MT41J256M8 DDR3 SDRAM only and are computed from values specified in the 2Gb (256 Meg x 8) component data sheet

Parameter Symbol 1600 1333 1066 Units

Operating current 0: One bank ACTIVATE-to-PRECHARGE

Operating current 1: One bank ACTIVATE-to-READto-PRECHARGE

Precharge power-down current: Slow exit I

Precharge power-down current: Fast exit I

Precharge quiet standby current I

Precharge standby current I

Precharge standby ODT current I

Active power-down current I

Active standby current I

Burst read operating current I

Burst write operating current I

Refresh current I

Self refresh temperature current: MAX TC = 85°C I

Self refresh temperature current (SRT-enabled): MAX

TC = 95°C

All banks interleaved read current I

Reset current I

I

DD0

I

DD1

DD2P

DD2P

DD2Q

DD2N

DD2NT

DD3P

DD3N

DD4R

DD4W

DD5

DD6

I

DD6ET

DD7

DD8

560 520 480 mA

640 600 560 mA

96 96 96 mA

296 256 216 mA

320 280 240 mA

344 304 264 mA

360 320 280 mA

400 360 320 mA

440 400 360 mA

1248 1128 1040 mA

1160 1040 920 mA

1560 1520 1480 mA

96 96 96 mA

120 120 120 mA

1920 1800 1680 mA

112 112 112 mA

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

13

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 14

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

Temperature Sensor with Serial Presence-Detect EEPROM

Temperature Sensor with Serial Presence-Detect EEPROM

The temperature sensor continuously monitors the module's temperature and can be

read back at any time over the I2C bus shared with the SPD EEPROM. Refer to JEDEC

standard No. 21-C page 4.7-1, "Definition of the TSE2002av, Serial Presence Detect with

Temperature Sensor."

Serial Presence-Detect

For the latest SPD data, refer to Micron's SPD page: www.micron.com/SPD.

Table 14: Temperature Sensor with SPD EEPROM Operating Conditions

Parameter/Condition Symbol Min Max Units

Supply voltage V

Supply current: VDD = 3.3V I

Input high voltage: Logic 1; SCL, SDA V

Input low voltage: Logic 0; SCL, SDA V

Output low voltage: I

= 2.1mA V

OUT

Input current I

DDSPD

DD

IH

IL

OL

IN

Temperature sensing range – –40 125 °C

Temperature sensor accuracy (class B) – –1.0 1.0 °C

3.0 3.6 V

– 2.0 mA

V

x 0.7 V

DDSPD

–0.5 V

+ 1 V

DDSPD

x 0.3 V

DDSPD

– 0.4 V

–5.0 5.0 µA

DIMM

Table 15: Temperature Sensor and SPD EEPROM Serial Interface Timing

Parameter/Condition Symbol Min Max Units

Time bus must be free before a new transition can

start

SDA fall time

SDA rise time

Data hold time

Start condition hold time

Clock HIGH period

Clock LOW period

SCL clock frequency

Data setup time

Start condition setup time

Stop condition setup time

t

BUF 4.7 – µs

t

F 20 300 ns

t

R – 1000 ns

t

HD:DAT 200 900 ns

t

H:STA 4.0 – µs

t

HIGH 4.0 50 µs

t

LOW 4.7 – µs

t

SCL 10 100 kHz

t

SU:DAT 250 – ns

t

SU:STA 4.7 – µs

t

SU:STO 4.0 – µs

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

14

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 15

EVENT# Pin

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

DIMM

Temperature Sensor with Serial Presence-Detect EEPROM

The temperature sensor also adds the EVENT# pin (open-drain). Not used by the SPD

EEPROM, EVENT# is a temperature sensor output used to flag critical events that can be

set up in the sensor’s configuration register.

EVENT# has three defined modes of operation: interrupt mode, compare mode, and

critical temperature mode. Event thresholds are programmed in the 0x01 register using

a hysteresis. The alarm window provides a comparison window, with upper and lower

limits set in the alarm upper boundary register and the alarm lower boundary register,

respectively. When the alarm window is enabled, EVENT# will trigger whenever the

temperature is outside the MIN or MAX values set by the user.

The interrupt mode enables software to reset EVENT# after a critical temperature

threshold has been detected. Threshold points are set in the configuration register by

the user. This mode triggers the critical temperature limit and both the MIN and MAX of

the temperature window.

The compare mode is similar to the interrupt mode, except EVENT# cannot be reset by

the user and returns to the logic HIGH state only when the temperature falls below the

programmed thresholds.

Critical temperature mode triggers EVENT# only when the temperature has exceeded

the programmed critical trip point. When the critical trip point has been reached, the

temperature sensor goes into comparator mode, and the critical EVENT# cannot be

cleared through software.

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

15

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Page 16

1GB, 2GB (x64, SR) 204-Pin Halogen-Free DDR3 SDRAM SO-

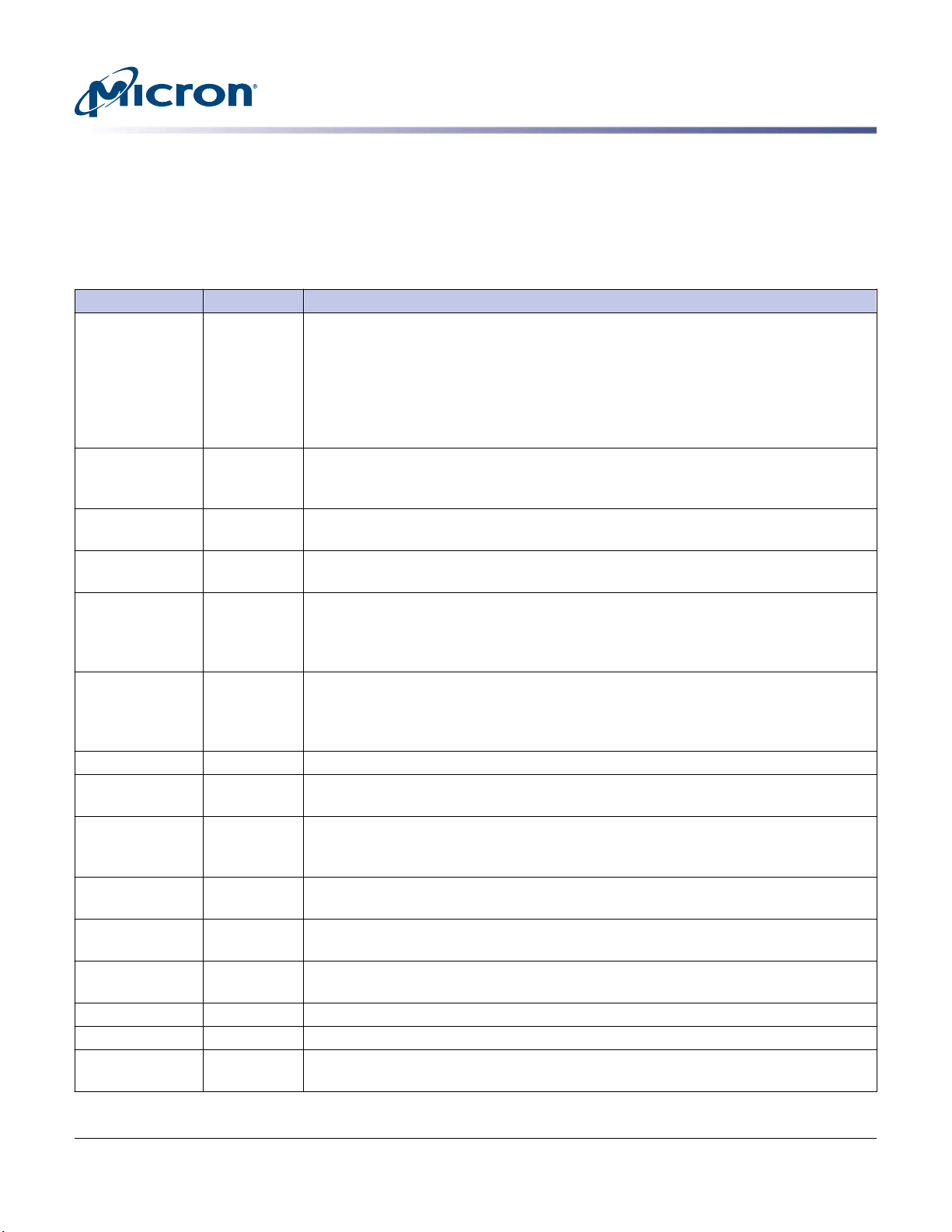

Module Dimensions

Figure 3: 204-Pin DDR3 SODIMM

DIMM

Module Dimensions

3.8 (0.15)

MAX

1.1 (0.043)

0.9 (0.035)

2.0 (0.079) R

(2X)

1.8 (0.071)

(2X)

2.55 (0.1)

6.0 (0.236)

TYP

2.0 (0.079)

TYP

TYP

Front view

67.75 (2.667)

67.45 (2.656)

U1

Pin 1

U2

1.0 (0.039)

TYP

63.6 (2.504)

TYP

U3 U4

0.45 (0.018)

TYP

0.6 (0.024)

Back view

U6 U7 U8 U9

U10

Pin 204

39.0 (1.535)

TYP

3.0 (0.12)

TYP

21.0 (0.827)

24.8 (0.976)

TYP

TYP

TYP

20.0 (0.787)

TYP

Pin 203

4.0 (0.157)

TYP

Pin 2

30.15 (1.187)

29.85 (1.175)

Notes:

1. All dimensions are in millimeters (inches); MAX/MIN or typical (TYP) where noted.

2. The dimensional diagram is for reference only.

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

www.micron.com/productsupport Customer Comment Line: 800-932-4992

Micron and the Micron logo are trademarks of Micron Technology, Inc.

All other trademarks are the property of their respective owners.

This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein.

Although considered final, these specifications are subject to change, as further product development and data characterization some-

times occur.

PDF: 09005aef83364a85

jsf8c128_256x64hz.pdf - Rev. E 04/13 EN

16

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Loading...

Loading...