MICRON MT4LC4M4E9TG-5, MT4LC4M4E9TG-6, MT4LC4M4E9TGS-5, MT4LC4M4E9DJS-5, MT4LC4M4E9DJ-6 Datasheet

...

4 Meg x 4 EDO DRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

D47.pm5 – Rev. 3/97 1997, Micron Technology, Inc.

1

4 MEG x 4

EDO DRAM

TECHNOLOGY, INC.

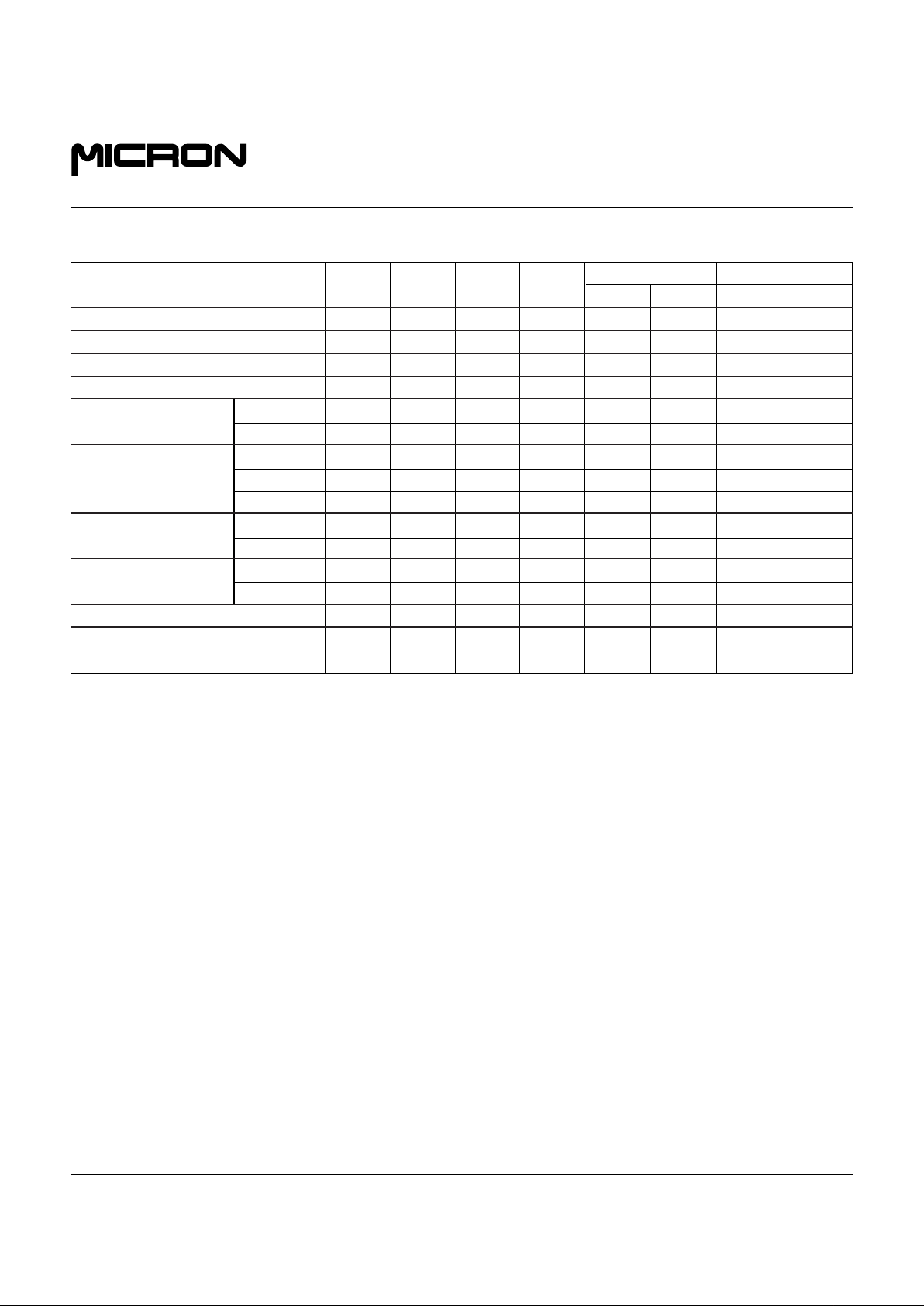

4 MEG x 4 EDO DRAM PART NUMBERS

PART NUMBER Vcc REFRESH PACKAGE REFRESH

MT4LC4M4E8DJ 3.3V 2K SOJ Standard

MT4LC4M4E8DJS 3.3V 2K SOJ Self

MT4LC4M4E8TG 3.3V 2K TSOP Standard

MT4LC4M4E8TGS 3.3V 2K TSOP Self

MT4LC4M4E9DJ 3.3V 4K SOJ Standard

MT4LC4M4E9DJS 3.3V 4K SOJ Self

MT4LC4M4E9TG 3.3V 4K TSOP Standard

MT4LC4M4E9TGS 3.3V 4K TSOP Self

MT4C4M4E8DJ 5V 2K SOJ Standard

MT4C4M4E8DJS 5V 2K SOJ Self

MT4C4M4E8TG 5V 2K TSOP Standard

MT4C4M4E8TGS 5V 2K TSOP Self

MT4C4M4E9DJ 5V 4K SOJ Standard

MT4C4M4E9DJS 5V 4K SOJ Self

MT4C4M4E9TG 5V 4K TSOP Standard

MT4C4M4E9TGS 5V 4K TSOP Self

MT4LC4M4E8, MT4C4M4E8

MT4LC4M4E9, MT4C4M4E9

DRAM

FEATURES

• Industry-standard x4 pinout, timing, functions and

packages

• State-of-the-art, high-performance, low-power CMOS

silicon-gate process

• Single power supply (+3.3V ±0.3V or +5V ±10%)

• All inputs, outputs and clocks are TTL-compatible

• Refresh modes: RAS#-ONLY, HIDDEN and CAS#BEFORE-RAS# (CBR)

• Optional Self Refresh (S) for low-power data retention

• 11 row, 11 column addresses (2K refresh) or

12 row, 10 column addresses (4K refresh)

• Extended Data-Out (EDO) PAGE MODE access cycle

• 5V-tolerant inputs and I/Os on 3.3V devices

OPTIONS MARKING

• Voltages

3.3V LC

5V C

• Refresh Addressing

2,048 (i.e. 2K) Rows E8

4,096 (i.e. 4K) Rows E9

• Packages

Plastic SOJ (300 mil) DJ

Plastic TSOP (300 mil) TG

• Timing

50ns access -5

60ns access -6

• Refresh Rates

Standard Refresh None

Self Refresh (128ms period) S

• Part Number Example: MT4LC4M4E8DJ-6

Note: The 4 Meg x 4 EDO DRAM base number differentiates the offerings in

two places - MT4LC4M4E8. The third field distinguishes the low voltage

offering: LC designates VCC = 3.3V and C designates VCC = 5V. The fifth field

distinguishes various options: E8 designates a 2K refresh and E9 designates a

4K refresh for EDO DRAMs.

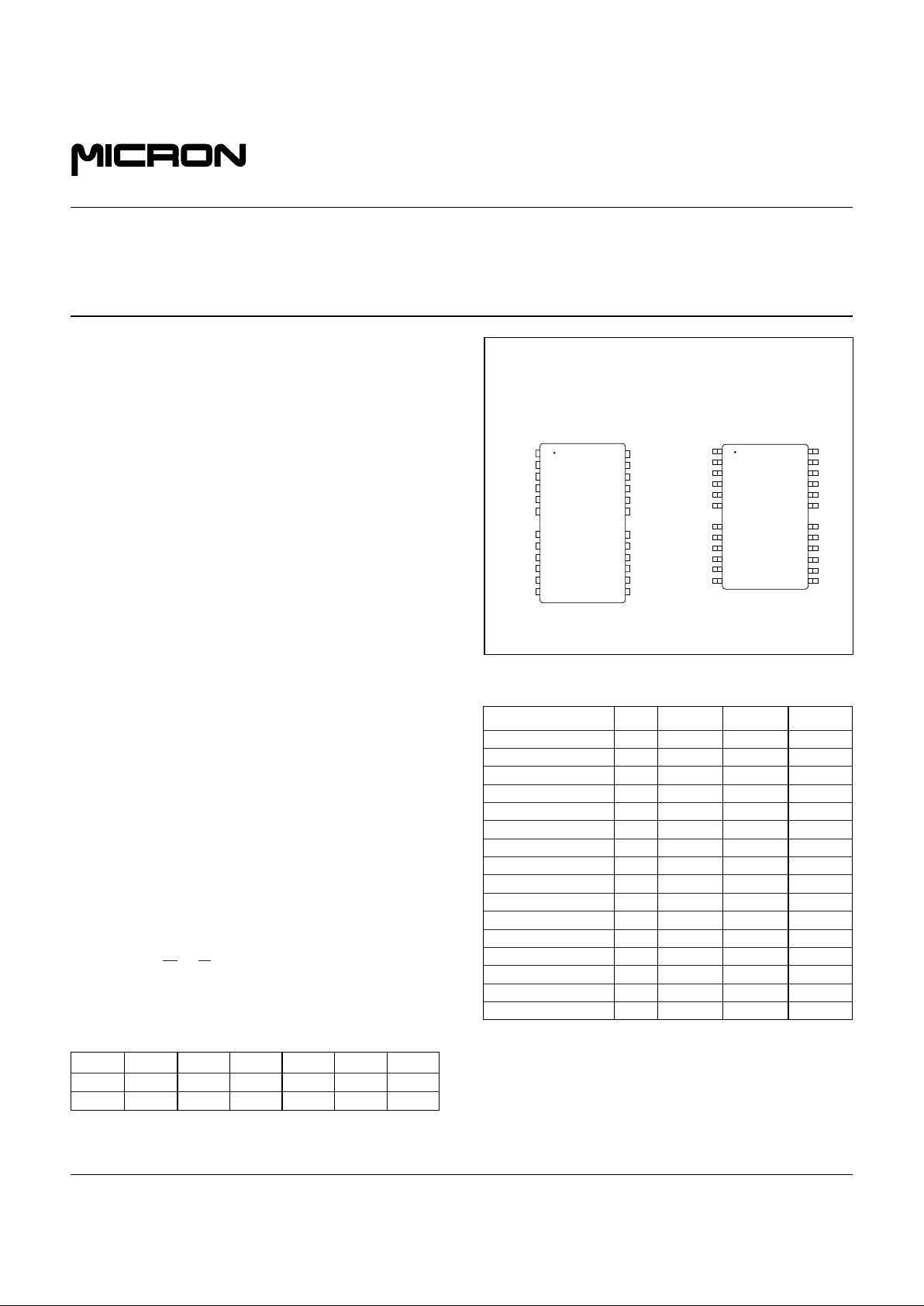

PIN ASSIGNMENT (Top View)

24/26-Pin SOJ

(DA-2)

VCC

DQ1

DQ2

WE#

RAS#

*NC/A11

A10

A0

A1

A2

A3

V

CC

1

2

3

4

5

6

8

9

10

11

12

13

26

25

24

23

22

21

19

18

17

16

15

14

VSS

DQ4

DQ3

CAS#

OE#

A9

A8

A7

A6

A5

A4

V

SS

V

CC

DQ1

DQ2

WE#

RAS#

*NC/A11

A10

A0

A1

A2

A3

V

CC

1

2

3

4

5

6

8

9

10

11

12

13

26

25

24

23

22

21

19

18

17

16

15

14

V

SS

DQ4

DQ3

CAS#

OE#

A9

A8

A7

A6

A5

A4

V

SS

24/26-Pin TSOP

(DB-2)

* NC on 2K refresh and A11 on 4K refresh options.

GENERAL DESCRIPTION

The 4 Meg x 4 DRAM is a randomly accessed, solid-state

memory containing 16,777,216 bits organized in a x4 configuration. RAS# is used to latch the row address (first 11

bits for 2K and first 12 bits for 4K). Once the page has been

opened by RAS#, CAS# is used to latch the column address

KEY TIMING PARAMETERS

SPEEDtRC

t

RAC

t

PC

t

AA

t

CACtCAS

-5 84ns 50ns 20ns 25ns 13ns 8ns

-6 104ns 60ns 25ns 30ns 15ns 10ns

Note: The “#” symbol indicates signal is active LOW.

4 Meg x 4 EDO DRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

D47.pm5 – Rev. 3/97 1997, Micron Technology, Inc.

2

4 MEG x 4

EDO DRAM

TECHNOLOGY, INC.

GENERAL DESCRIPTION (continued)

(the latter 11 bits for 2K and the latter 10 bits for 4K, address

pins A10 and A11 are “don’t care”). READ and WRITE

cycles are selected with the WE# input.

A logic HIGH on WE# dictates READ mode, while a logic

LOW on WE# dictates WRITE mode. During a WRITE

cycle, data-in (D) is latched by the falling edge of WE# or

CAS#, whichever occurs last. An EARLY WRITE occurs

when WE# is taken LOW prior to CAS# falling. A LATE

WRITE or READ-MODIFY-WRITE occurs when WE# falls

after CAS# is taken LOW. During EARLY WRITE cycles,

the data outputs (Q) will remain High-Z regardless of the

state of OE#. During LATE WRITE or READ-MODIFYWRITE cycles, OE# must be taken HIGH to disable the data

outputs prior to applying input data. If a LATE WRITE or

READ-MODIFY-WRITE is attempted while keeping OE#

LOW, no write will occur, and the data outputs will drive

read data from the accessed location.

The four data inputs and the four data outputs are routed

through four pins using common I/O, and pin direction is

controlled by WE# and OE#.

PAGE ACCESS

PAGE operations allow faster data operations (READ,

WRITE or READ-MODIFY-WRITE) within a row addressdefined page boundary. The PAGE cycle is always initiated

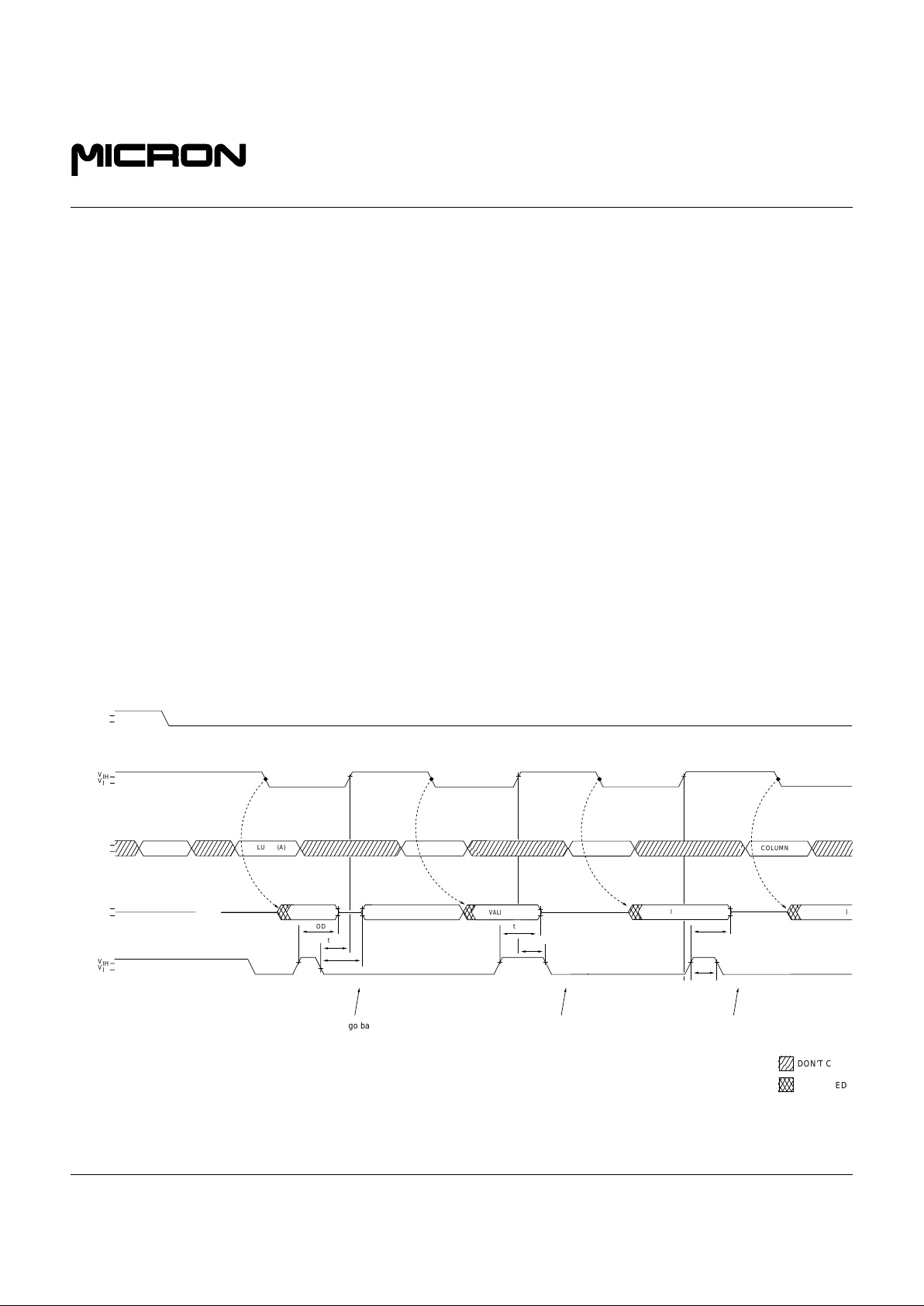

Figure 1

OE# CONTROL OF DQs

with a row address strobed-in by RAS#, followed by a

column address strobed-in by CAS#. CAS# may be

toggled-in by holding RAS# LOW and strobing-in different

column addresses, thus executing faster memory cycles.

Returning RAS# HIGH terminates the PAGE MODE of

operation, i.e., closes the page.

EDO PAGE MODE

The 4 Meg x 4 EDO DRAM provides EDO PAGE MODE,

which is an accelerated FAST PAGE MODE cycle. The

primary advantage of EDO is the availability of data-out

even after CAS# returns HIGH. EDO allows CAS# precharge

time (tCP) to occur without the output data going invalid.

This elimination of CAS# output control allows pipeline

READs.

FAST PAGE MODE DRAMs have traditionally turned

the output buffers off (High-Z) with the rising edge of

CAS#. EDO PAGE MODE DRAMs operate like FAST

PAGE MODE DRAMs, except data will remain valid or

become valid after CAS# goes HIGH during READs, provided RAS# and OE# are held LOW. If OE# is pulsed while

RAS# and CAS# are LOW, data will toggle from valid data

to High-Z and back to the same valid data. If OE# is toggled

or pulsed after CAS# goes HIGH while RAS# remains

LOW, data will transition to and remain High-Z (refer to

V

V

IH

IL

CAS#

V

V

IH

IL

RAS#

V

V

IH

IL

ADDR

ROW

,

COLUMN (A)

,,

COLUMN (B)

,,

DON’T CARE

UNDEFINED

V

V

IH

IL

OE#

V

V

IOH

IOL

OPEN

DQ

t

OD

VALID DATA (B)

VALID DATA (A)

COLUMN (C)

,,,

VALID DATA (A)

t

OE

VALID DATA (C)

COLUMN (D)

,,

VALID DATA (D)

t

OD

t

OEHC

t

OD

t

OEP

t

OES

The DQs go back to

Low-Z if

t

OES is met.

The DQs remain High-Z

until the next CAS# cycle

if

t

OEHC is met.

The DQs remain High-Z

until the next CAS# cycle

if

t

OEP is met.

4 Meg x 4 EDO DRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

D47.pm5 – Rev. 3/97 1997, Micron Technology, Inc.

3

4 MEG x 4

EDO DRAM

TECHNOLOGY, INC.

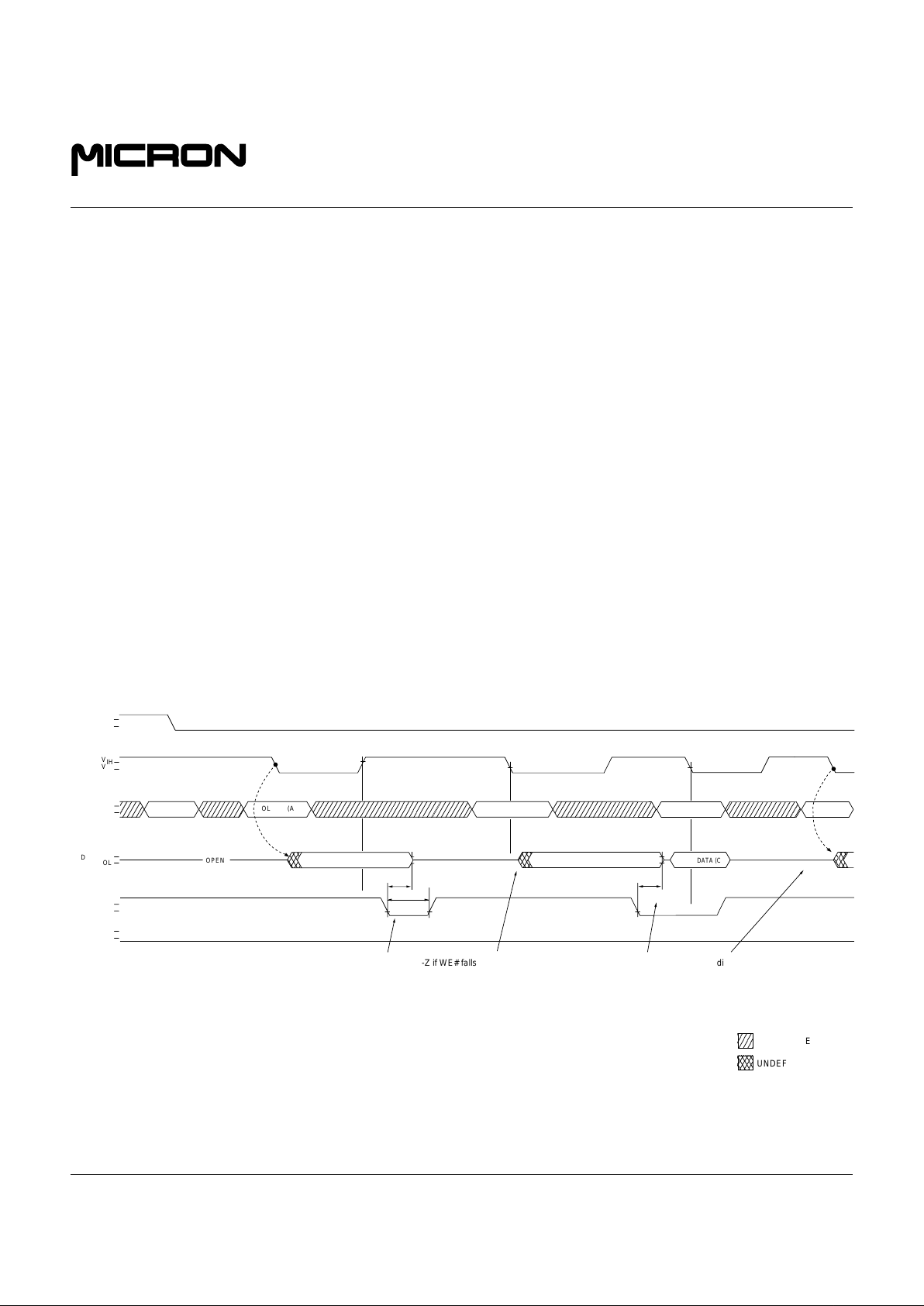

Figure 1). WE# can also perform the function of disabling

the output devices under certain conditions, as shown in

Figure 2.

During an application, if the DQ outputs are wire OR’d,

OE# must be used to disable idle banks of DRAMs. Alternatively, pulsing WE# to the idle banks during CAS# high

time will also High-Z the outputs. Independent of OE#

control, the outputs will disable after tOFF, which is referenced from the rising edge of RAS# or CAS#, whichever

occurs last.

REFRESH

Preserve correct memory cell data by maintaining power

and executing any RAS# cycle (READ, WRITE) or RAS#

refresh cycle (RAS#-ONLY, CBR or HIDDEN) so that all

combinations of RAS# addresses (2,048 for 2K and 4,096 for

4K) are executed within tREF (MAX), regardless of sequence. The CBR and Self Refresh cycles will invoke the

internal refresh counter for automatic RAS# addressing.

An optional Self Refresh mode is also available on the S

version. The “S” option allows the user the choice of a fully

static, low-power data retention mode or a dynamic refresh

mode at the extended refresh period of 128ms. The optional

Self Refresh feature is initiated by performing a CBR Re-

fresh cycle and holding RAS# LOW for the specified tRASS.

Additionally, the “S” option allows for an extended refresh

period of 128ms, or 31.25µs per row for a 4K refresh and

62.5µs per row for a 2K refresh if using distributed CBR

Refresh. This refresh rate can be applied during normal

operation, as well as during a standby or BATTERY BACKUP

mode.

The Self Refresh mode is terminated by driving

RAS#

HIGH for a minimum time of tRPS. This delay allows for the

completion of any internal refresh cycles that may be in

process at the time of the

RAS# LOW-to-HIGH transition.

If the DRAM controller uses a distributed refresh sequence, a burst refresh is not required upon exiting

Self Refresh

. However, if the DRAM controller utilizes

a

RAS#-ONLY or

burst refresh sequence, all rows must be

refreshed within the average internal refresh rate

, prior to

the resumption of normal operation.

STANDBY

Returning RAS# and CAS# HIGH terminates a memory

cycle and decreases chip current to a reduced standby level.

The chip is preconditioned for the next cycle during the

RAS# HIGH time.

Figure 2

WE# CONTROL OF DQs

V

V

IH

IL

CAS#

V

V

IH

IL

RAS#

V

V

IH

IL

ADDR

ROW

,

COLUMN (A)

,

DON’T CARE

UNDEFINED

V

V

IH

IL

WE#

V

V

IOH

IOL

OPEN

DQ

,

t

WPZ

The DQs go to High-Z if WE# falls and, if tWPZ is met,

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

V

V

IH

IL

OE#

VALID DATA (B)

t

WHZ

WE# may be used to disable the DQs to prepare

for input data in an EARLY WRITE cycle. The DQs

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

t

WHZ

COLUMN (D)

,,,

VALID DATA (A)

COLUMN (B)

COLUMN (C)

INPUT DATA (C)

4 Meg x 4 EDO DRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

D47.pm5 – Rev. 3/97 1997, Micron Technology, Inc.

4

4 MEG x 4

EDO DRAM

TECHNOLOGY, INC.

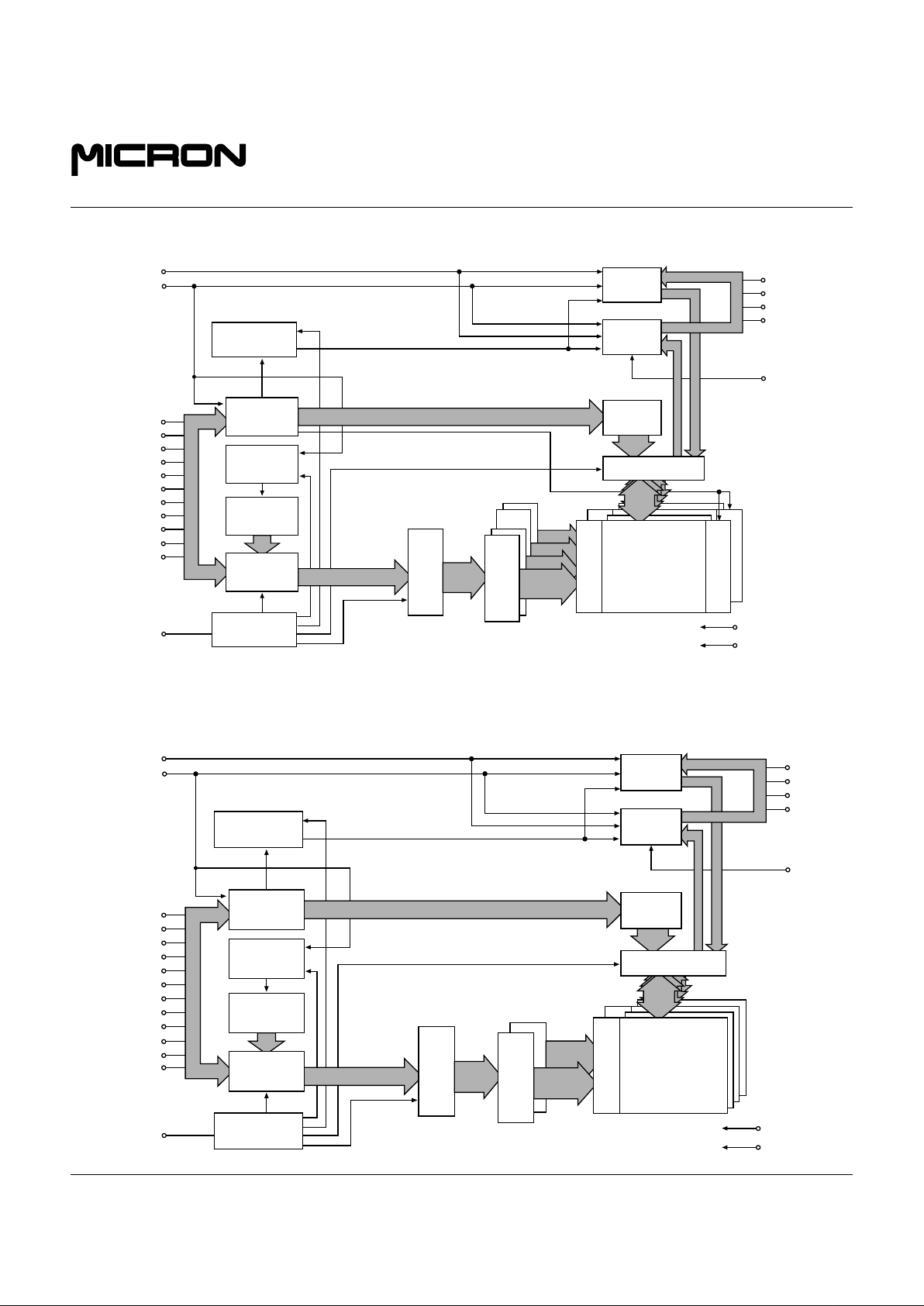

FUNCTIONAL BLOCK DIAGRAM - 2K REFRESH

2048

2048

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

RAS#

11

11

11

NO. 2 CLOCK

GENERATOR

REFRESH

CONTROLLER

NO. 1 CLOCK

GENERATOR

V

DD

VSS

11

WE#

CAS#

10

COLUMN

ADDRESS

BUFFER(11)

ROW

ADDRESS

BUFFERS (11)

2048

ROW

DECODER

2048

1024

COLUMN

DECODER

OE#

DQ1

DQ2

DQ3

DQ4

4

4

4

4

REFRESH

COUNTER

1

ROW TRANSFER

(1 OF 2)

ROW TRANSFER

(1 OF 2)

1024

4096 x 1024 x 4

MEMORY

ARRAY

SENSE AMPLIFIERS

I/O GATING

DATA-OUT

BUFFER

DATA-IN

BUFFER

COMPLEMENT

SELECT

2048

ROW SELECT

(2 of 4096)

FUNCTIONAL BLOCK DIAGRAM - 4K REFRESH

4096

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

RAS#

12

12

10

NO. 2 CLOCK

GENERATOR

REFRESH

CONTROLLER

NO. 1 CLOCK

GENERATOR

V

DD

V

SS

12

WE#

CAS#

10

COLUMN

ADDRESS

BUFFER(10)

ROW

ADDRESS

BUFFERS (12)

ROW

DECODER

4096

1024

COLUMN

DECODER

OE#

DQ1

DQ2

DQ3

DQ4

4

4

4

4

REFRESH

COUNTER

1024

4096 x 1024 x 4

MEMORY

ARRAY

SENSE AMPLIFIERS

I/O GATING

DATA-OUT

BUFFER

DATA-IN

BUFFER

COMPLEMENT

SELECT

4096

ROW SELECT

(1 of 4096)

4 Meg x 4 EDO DRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

D47.pm5 – Rev. 3/97 1997, Micron Technology, Inc.

5

4 MEG x 4

EDO DRAM

TECHNOLOGY, INC.

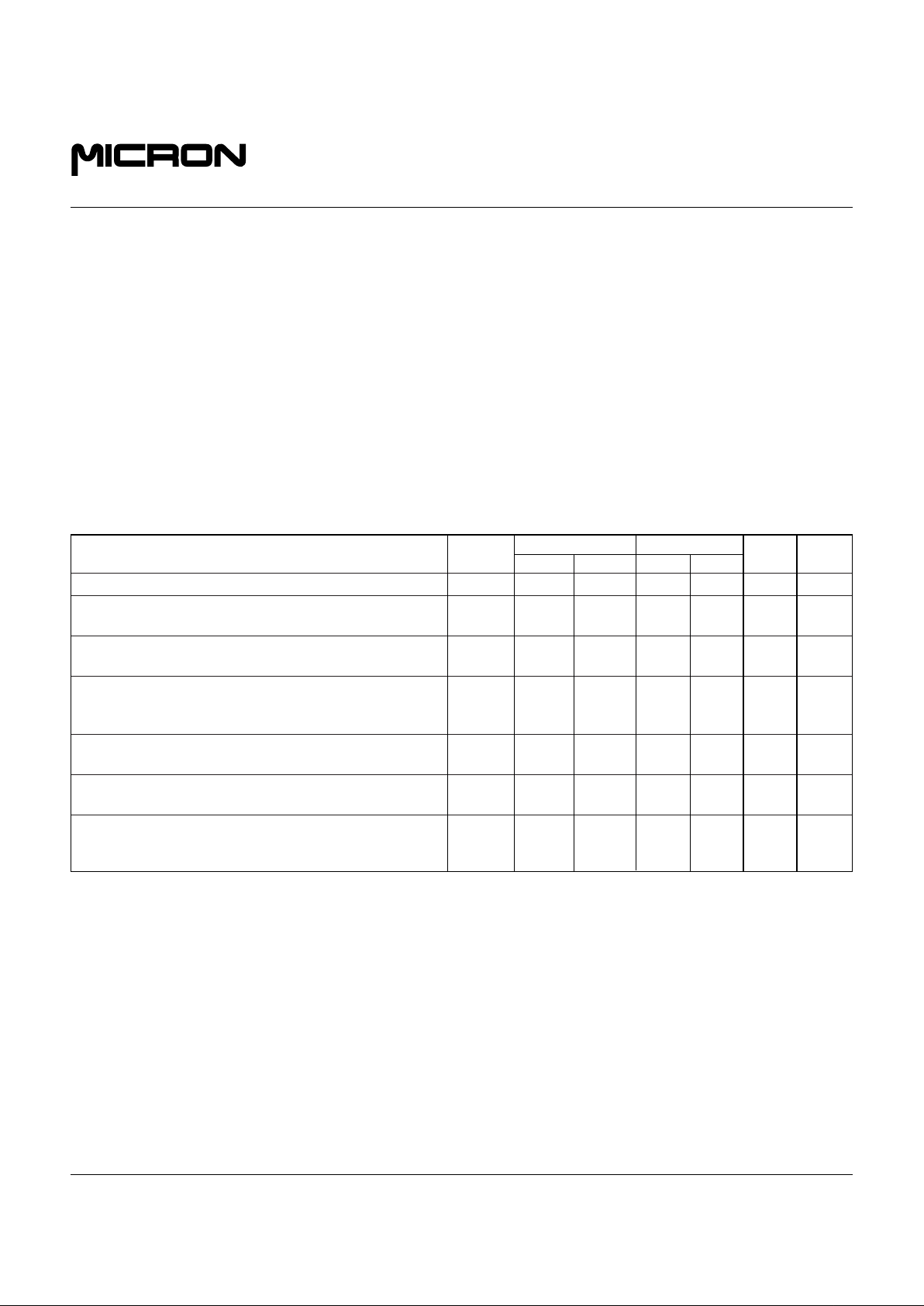

TRUTH TABLE

ADDRESSES DATA-IN/OUT

FUNCTION RAS# CAS# WE# OE#

t

R

t

C DQ1-DQ4

Standby H H→XXXXX High-Z

READ L L H L ROW COL Data-Out

EARLY WRITE L L L X ROW COL Data-In

READ WRITE L L H→LL→H ROW COL Data-Out, Data-In

EDO-PAGE-MODE 1st Cycle L H→L H L ROW COL Data-Out

READ 2nd Cycle L H→L H L n/a COL Data-Out

EDO-PAGE-MODE 1st Cycle L H→L L X ROW COL Data-In

EARLY WRITE 2nd Cycle L H→L L X n/a COL Data-In

Any Cycle L L→H H L n/a n/a Data-Out

EDO-PAGE-MODE 1st Cycle L H→LH→LL→H ROW COL Data-Out, Data-In

READ-WRITE 2nd Cycle L H→LH→LL→H n/a COL Data-Out, Data-In

HIDDEN READ L→H→L L H L ROW COL Data-Out

REFRESH WRITE L→H→L L L X ROW COL Data-In

RAS#-ONLY REFRESH L H X X ROW n/a High-Z

CBR REFRESH H→L L H X X X High-Z

SELF REFRESH H→L L H X X X High-Z

4 Meg x 4 EDO DRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

D47.pm5 – Rev. 3/97 1997, Micron Technology, Inc.

6

4 MEG x 4

EDO DRAM

TECHNOLOGY, INC.

ABSOLUTE MAXIMUM RATINGS*

Voltage on VCC Pin Relative to VSS:

3.3V ................................................................ -1V to +4.6V

5V ...................................................................... -1V to +7V

Voltage on NC, Inputs or I/O Pins Relative to VSS:

3.3V ................................................................ -1V to +5.5V

5V ...................................................................... -1V to +7V

Operating Temperature, TA (ambient) .......... 0°C to +70°C

Storage Temperature (plastic).................... -55°C to +150°C

Power Dissipation ............................................................. 1W

Short Circuit Output Current ..................................... 50mA

*Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.

This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not

implied. Exposure to absolute maximum rating conditions

for extended periods may affect reliability.

DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

(Notes: 1)

3.3V 5V

PARAMETER/CONDITION SYMBOL MIN MAX MIN MAX UNITS NOTES

Supply Voltage VCC 3.0 3.6 4.5 5.5 V

Input High Voltage:

Valid Logic 1; all inputs, I/Os and any NC VIH 2.0 5.5 2.4 VCC +1 V

Input Low Voltage:

Valid Logic 0; all inputs, I/Os and any NCVIL-1.00.8-0.5 0.8V

Input Leakage Current:

Any input at VIN (0V ≤ VIN ≤ VIH [MAX]); II -2 2 -2 2 µA 4

all other pins not under test = 0V

Output High Voltage:

IOUT = -2mA (3.3V), -5mA (5V) VOH 2.4 - 2.4 - V

Output Low Voltage:

IOUT = 2mA (3.3V), 4.2mA (5V) VOL - 0.4 - 0.4 V

Output Leakage Current:

Any output at VOUT (0V ≤ VOUT ≤ 5.5V); IOZ -5 5 -5 5 µA

DQ is disabled and in High-Z state

4 Meg x 4 EDO DRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

D47.pm5 – Rev. 3/97 1997, Micron Technology, Inc.

7

4 MEG x 4

EDO DRAM

TECHNOLOGY, INC.

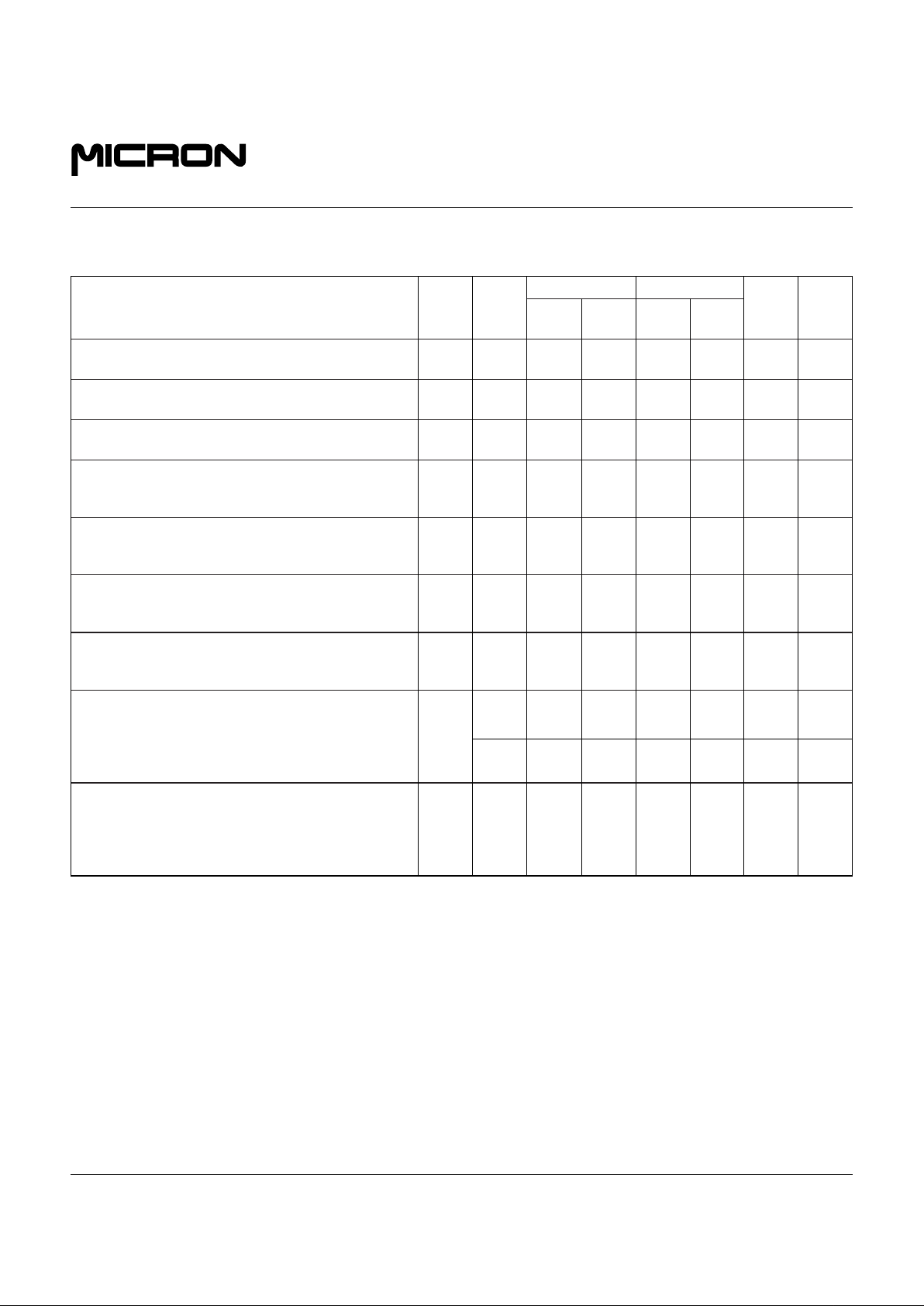

Icc OPERATING CONDITIONS AND MAXIMUM LIMITS

(Notes: 1, 2, 3)

3.3V 5V

2K 4K 2K 4K

PARAMETER/CONDITION SYM SPEED Refresh Refresh Refresh Refresh UNITS NOTES

STANDBY CURRENT: TTL ICC1 ALL1111mA

(RAS# = CAS# = VIH)

STANDBY CURRENT: CMOS (non-S version only) ICC2 ALL 500 500 500 500 µA

(RAS# = CAS# = other inputs = VCC -0.2V)

STANDBY CURRENT: CMOS (S version only) ICC2 ALL 150 150 150 150 µA

(RAS# = CAS# = other inputs = VCC -0.2V)

OPERATING CURRENT: Random READ/WRITE -5 110 90 140 120 mA 5, 6

Average power supply current ICC3 -6 100 80 130 110

(RAS#, CAS#, address cycling: tRC = tRC [MIN])

OPERATING CURRENT: EDO PAGE MODE -5 110 100 110 100 mA 5, 6

Average power supply current (RAS# = VIL,ICC4 -6 100 90 100 90

CAS#, address cycling: tPC = tPC [MIN])

REFRESH CURRENT: RAS#-ONLY -5 110 90 140 120 mA 5, 6

Average power supply current ICC5 -6 100 80 130 110

(RAS# cycling, CAS# = VIH: tRC = tRC [MIN])

REFRESH CURRENT: CBR -5 110 90 140 120 mA 5, 7

Average power supply current ICC6 -6 100 80 130 110

(RAS#, CAS#, address cycling: tRC = tRC [MIN])

REFRESH CURRENT: Extended (S version only)

Average power supply current: CAS# = 0.2V or ALL 300 300 300 300 µA 5, 7

CBR cycling; RAS# = tRAS (MIN); WE# = ICC7

VCC -0.2V; A0-A11,OE# and DIN = VCC -0.2V or

t

RC 62.5 31.25 62.5 31.25 µs25

0.2V (DIN may be left open)

REFRESH CURRENT: Self (S version only)

Average power supply current: CBR with

RAS# ≥ tRASS (MIN) and CAS# held LOW; WE# = ICC8 ALL 300 300 300 300 µA 5, 7

VCC -0.2V; A0-A11, OE# and DIN = VCC -0.2V

or 0.2V (DIN may be left open)

Loading...

Loading...