MICRON MT49H8M32FM-5, MT49H16M16FM-4, MT49H16M16FM-5, MT49H8M32FM-33, MT49H8M32FM-4 Datasheet

...

ADVANCE

‡

1

256: x16, x32 RLDRAM ©2002, Micron Technology, Inc.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

‡

PRODUCTS AND SPECIFICATIONS DISCUSSED HEREIN ARE FOR EVALUATION AND REFERENCE PURPOSES ONLY AND ARE SUBJECT TO CHANGE BY

MICRON WITHOUT NOTICE. PRODUCTS ARE ONLY WARRANTED BY MICRON TO MEET MICRON’S PRODUCTION DATA SHEET SPECIFICATIONS.

REDUCED LATENCY

DRAM (RLDRAM)

FEATURES

• 2.5V VEXT, 1.8V VDD, 1.8V VDDQ I/O

• Cyclic bank addressing for maximum data out

bandwidth

• Non-multiplexed addresses

• Non-interruptible sequential burst of two (2-bit

prefetch) and four (4-bit prefetch) DDR

• Target 600 Mb/s/p data rate

• Programmable Read Latency (RL) of 5-8

• Data valid signal (DVLD) activated as read data is

available

• Data Mask signals (DM0/DM1) to mask first and

second part of write data burst

• IEEE 1149.1 compliant JTAG boundary scan

• Pseudo-HSTL 1.8V I/O Supply

• Internal Auto Precharge

• Refresh requirements: 32ms at 100°C junction

temperature (8K refresh for each bank, 64K refresh

command must be issued in total each 32ms)

OPTIONS MARKING

• Clock Cycle Timing

3.3ns (300 MHz) -3.3

4ns (250 MHz) -4

5ns (200 MHz) -5

• Configuration

8 Meg x 32 MT49H8M32FM

(1 Meg x 32 x 8 banks)

16 Meg x 16 MT49H16M16FM

(2 Meg x 16 x 8 banks)

• Package

144-ball, 11mm x 18.5mm T-FBGA FM

144-Ball T-FBGA

MT49H8M32 – 1 Meg x 32 x 8 banks

MT49H16M16 – 2 Meg x 16 x 8 banks

For the latest data sheet, please refer to the Micron

Web site: www.micron.com/dramds

GENERAL DESCRIPTION

The Micron® 256Mb Reduced Latency DRAM

(RLDRAM) contains 8 banks x32Mb of memory accessible with 32-bit or 16-bit I/Os in a double data rate (DDR)

format where the data is provided and synchronized with

a differential echo clock signal. RLDRAM does not require

VALID PART NUMBERS

PART NUMBER DESCRIPTION

MT49H8M32FM-xx 8 Meg x 32

MT49H16M16FM-xx 16 Meg x 16

row/column address multiplexing and is optimized for

fast random access and high-speed bandwidth.

RLDRAM is designed for communication data

storages like transmit or receive buffers in telecommunication systems as well as data or instruction cache

applications requiring large amounts of memory.

POWER-UP INITIALIZATION

Since the RLDRAM does not have a designated reset

function, the following procedure must be executed in

order to initalize the internal state machine, regulators,

and force the DRAM to be in ready state.

• Apply power, then start clock

• After power on, an initial pause of 200µs is required

• MRS command for 2 clocks and set standard mode

register for 1 clock (2 dummies plus 1 valid MRS set)

• 8 refresh cycles (minimum), one on each bank and

separated by 2,048 cycles (tMRSC must be satisfied

between MRS and first REF command)

• Ready for normal operation (tRC cycles after the last

refresh command)

2

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

NOTE: 1. When the BL4 setting is used, A18 is a “Don’t Care.”

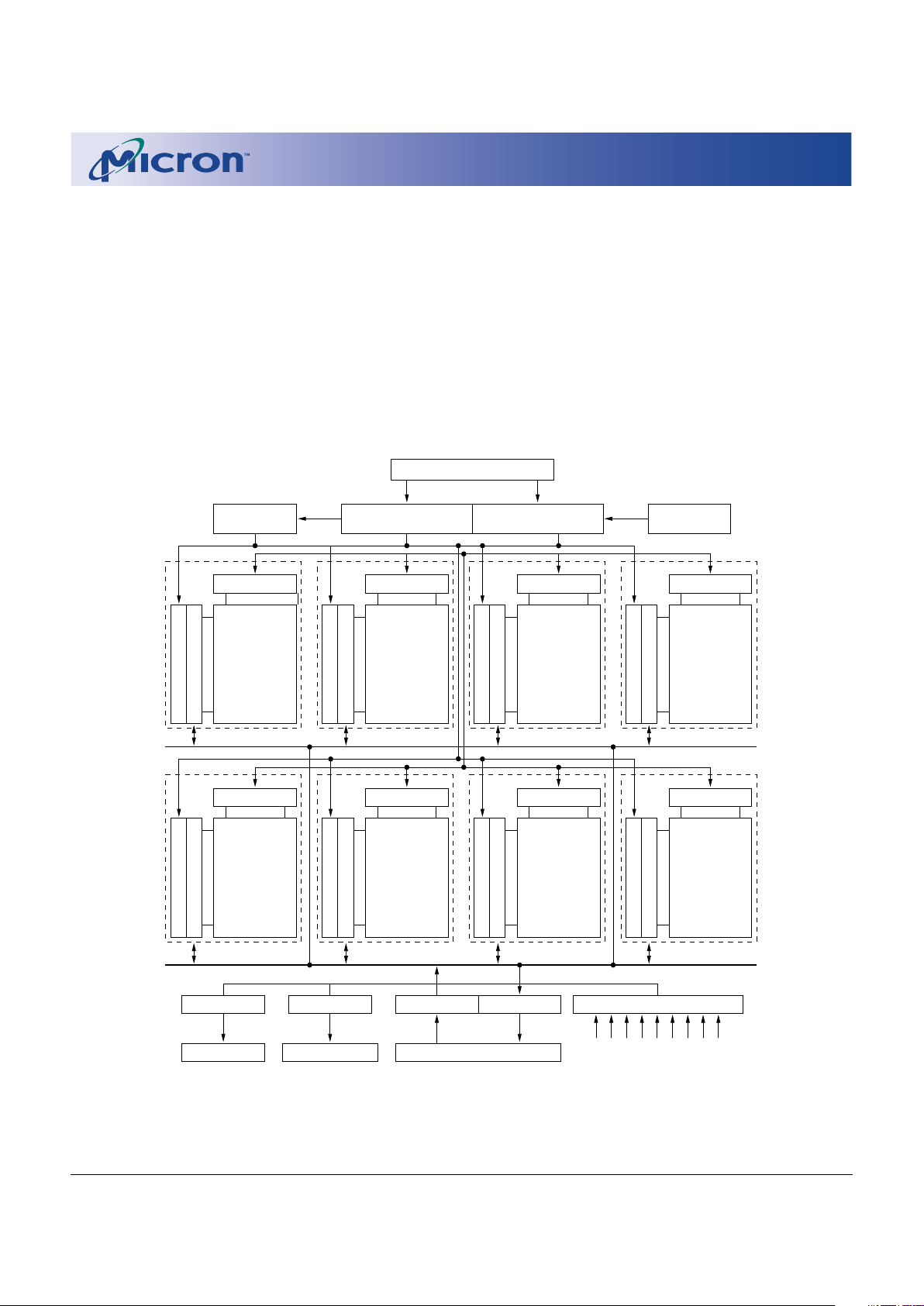

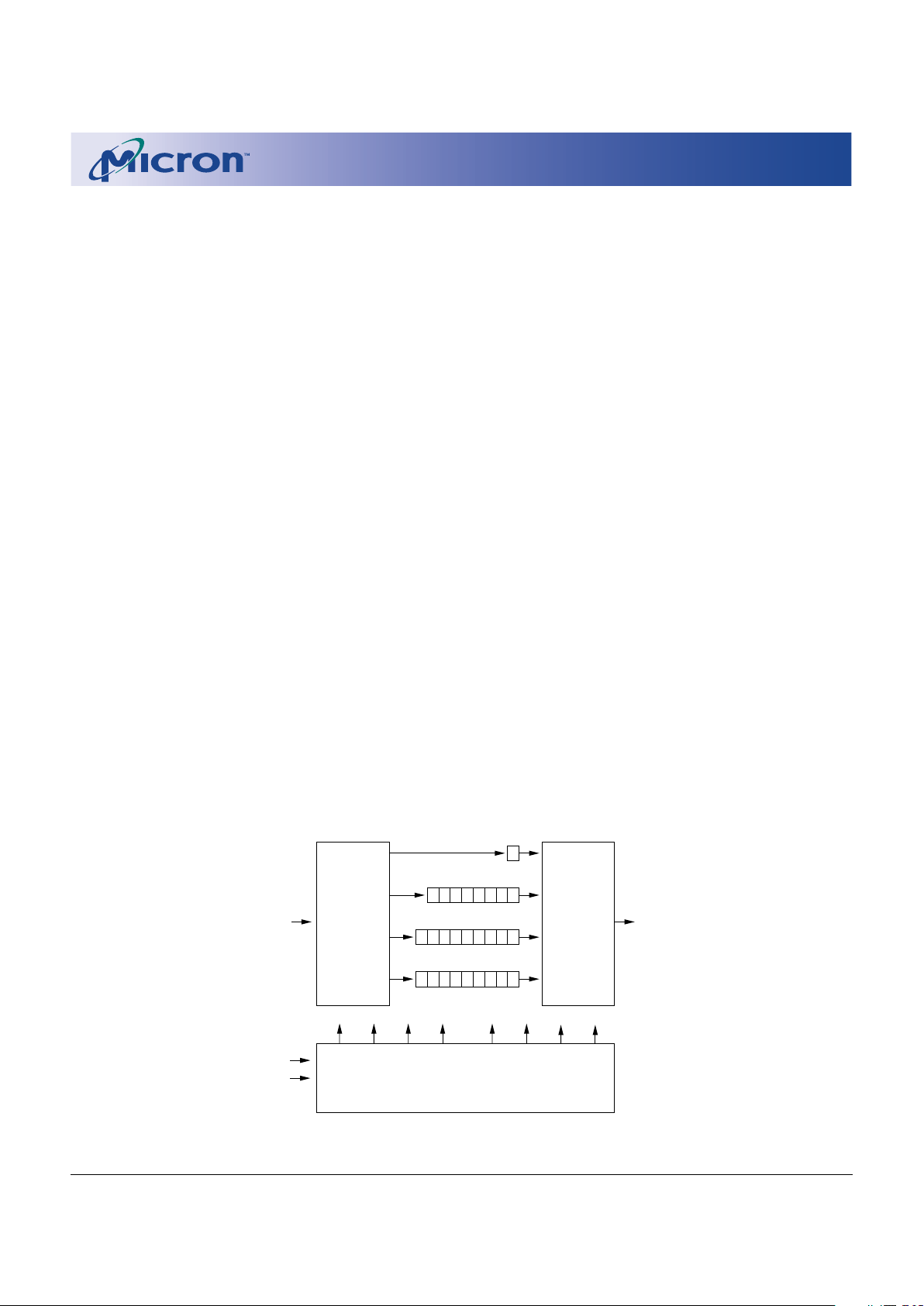

FUNCTIONAL BLOCK DIAGRAM

8 Meg x 32

A0–A18, B0, B1, B2

Column Address

Buffer

Column Address

Counter

Refresh

Counter

Row Decoder

Memory Array

Bank 1

Column Decoder

Sense Amp and Data Bus

Row Address

Buffer

Row Decoder

Memory Array

Bank 0

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 2

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 3

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 5

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 4

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 6

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 7

Column Decoder

CK

CK#

AS#

WE#

CS#

REF#

DM0

DM1

V

REF

Sense Amp and Data Bus

Data Valid

DVLD

Data Read Strobe

DQS[3:0], DQS#[3:0]

Input Buffers Output Buffers Control Logic and Timing Generator

DQ0–DQ31

POWER-DOWN

Because the RLDRAM uses multiple power supply

voltage, the following sequence is required for powerdown.

• Take all input signals to be VSS or High-Z

It is recommended to place Schottky diodes on the

board between the 2.5V and 1.8V power supplies.

3

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

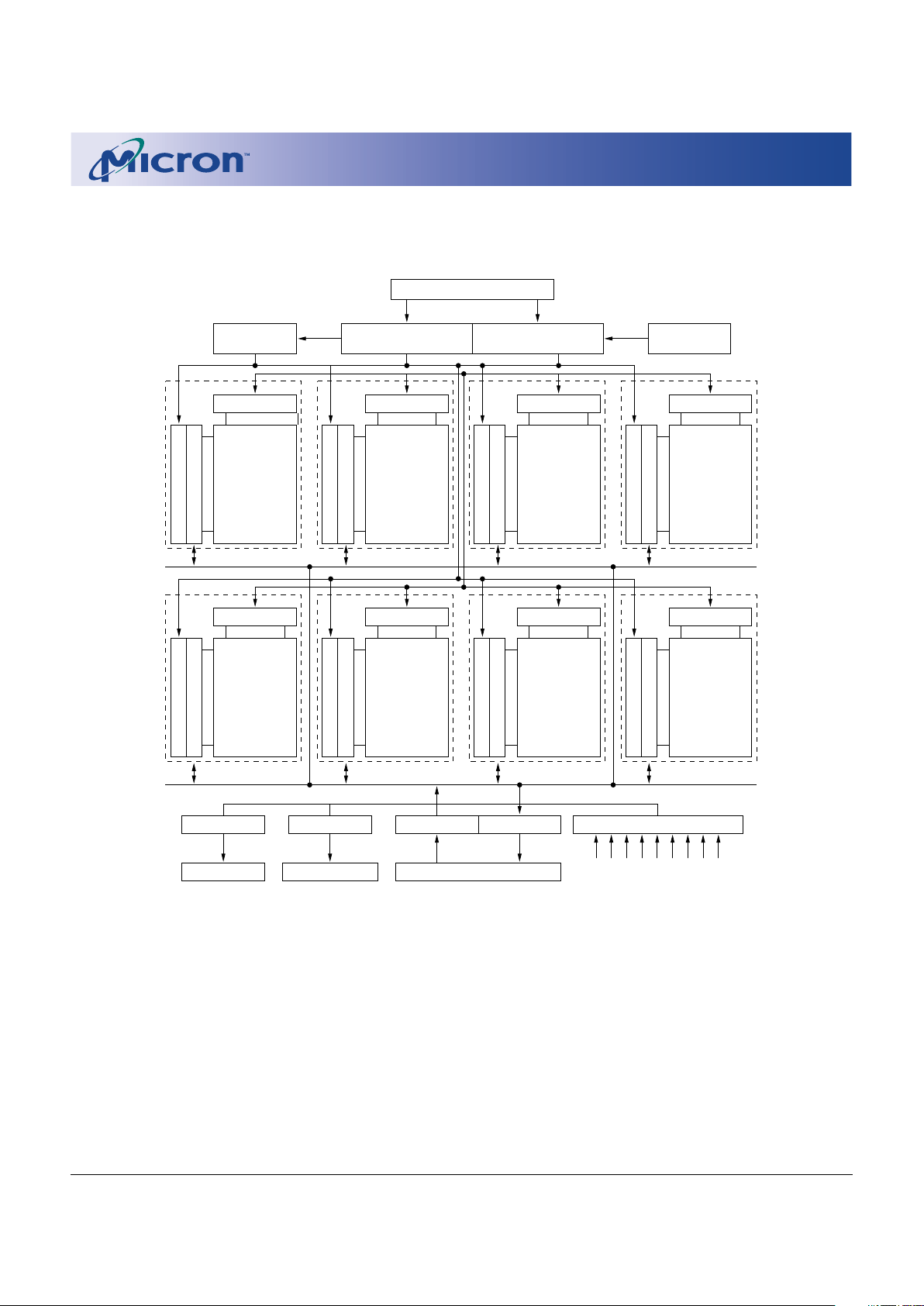

NOTE: 1. When the BL4 setting is used, A19 is a “Don’t Care.”

2. In the 16 Meg x 16 configuration, only DQS[1:0] and DQS#[1:0] are used.

FUNCTIONAL BLOCK DIAGRAM

16 Meg x 16

A0–A19, B0, B1, B2

Column Address

Buffer

Column Address

Counter

Refresh

Counter

Row Decoder

Memory Array

Bank 1

Column Decoder

Sense Amp and Data Bus

Row Address

Buffer

Row Decoder

Memory Array

Bank 0

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 2

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 3

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 5

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 4

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 6

Column Decoder

Sense Amp and Data Bus

Row Decoder

Memory Array

Bank 7

Column Decoder

CK

CK#

AS#

WE#

CS#

REF#

DM0

DM1

V

REF

Sense Amp and Data Bus

Data Valid

DVLD

Data Read Strobe

DQS[1:0], DQS#[1:0]

Input Buffers Output Buffers Control Logic and Timing Generator

DQ0–DQ15

4

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

TABLE OF CONTENTS

General Description ....................................................... 1

Power-Up Initialization ................................................... 1

Functional Block Diagram, 8 Meg x 32 ................ 2

Power-Down ................................................................... 2

Functional Block Diagram, 16 Meg x 16 ............. 3

8 Meg x 32 Ball Assignment (Top View)

144-Ball T-FBGA ............................................... 5

16 Meg x 16 PIN Assignment (Top View)

144-Ball T-FBGA ............................................... 5

Ball Descriptions .................................................... 6

Ball Descriptions (continued) ................................ 7

Truth Table 1 .......................................................... 8

Programming Description .............................................. 9

RLDRAM Programming Table .............................. 9

Mode Register Description ............................................ 10

Mode Register Command Table........................... 10

IEEE 1149.1 Serial Boundary Scan (JTAG) ................ 11

Disabling the JTAG Feature .......................................... 11

Figure 1, TAP Controller State Diagram .............. 11

Test Access Port (TAP).................................................. 11

Test Clock (TCK) ........................................................ 11

Test MODE SELECT (TMS) ...................................... 11

Test Data-In (TDI) ...................................................... 11

Test Data-Out (TDO) ................................................. 1 2

Performing a TAP Reset ........................................... 12

TAP Registers ............................................................ 12

Instruction Register .................................................... 1 2

Figure 2, TAP Controller Block Diagram ............. 12

Bypass Register ......................................................... 12

Boundary Scan Register ........................................... 12

Identification (ID) Register ........................................ 1 3

TAP Instruction Set ........................................................ 13

Overview ..................................................................... 13

Extest .......................................................................... 13

Idcode ......................................................................... 13

Sample Z .................................................................... 13

Sample/Preload ......................................................... 13

Bypass ........................................................................ 14

TAP Timing ............................................................. 1 4

TAP AC Electrical Characteristics ........................ 14

Reserved .................................................................... 14

TAP DC Electrical Characteristics and

Operating Conditions ........................................ 15

Identification Register Definitions ........................ 16

Scan Register Sizes .............................................. 16

Instruction codes ................................................... 1 6

Boundary Scan (Exit) Order ................................. 17

Absolute Maximum Ratings .......................................... 1 8

Recommended DC Operation Ranges ........................ 18

DC Electrical Characteristics and

Operating Conditions ........................................ 18

DC Electrical Characteristics and

Operating Conditions ........................................ 19

IDD Electrical Characteristics and

Operating Conditions ........................................ 20

Capacitance ........................................................... 21

AC Electrical Characteristics and

Operating Conditions ........................................ 21

AC Electrical Characteristics ................................ 22

Timing Waveforms

General Overview and Timing Definition

(BL2/WL2) .......................................................... 23

READ Timing (BL = 2)........................................... 24

READ Timing (BL = 4)........................................... 25

WRITE Timing (BL = 2, RL = 6) ........................... 26

WRITE Timing (BL = 4, RL = 6) ........................... 27

READ to WRITE Timing (BL = 2, WL = 2) .......... 28

WRITE to READ Timing (BL = 2, WL = 2) .......... 29

Refresh Timing ....................................................... 3 0

Example of Refresh Implementation

(Cyclic Bank Burst Refresh) ............................. 31

WRITE Data Mask Timing (BL = 2, WL = 2) ....... 32

WRITE Data Mask Timing (BL = 4, WL = 1) ....... 33

WRITE/READ and READ/WRITE Timing, Cyclic

Bank Access (RL = 6, BL = 2, WL = 3) ........... 34

WRITE/READ and READ/WRITE Timing, Cyclic

Bank Access (RL = 5, BL = 2, WL = 2) ........... 35

WRITE/READ and READ/WRITE Timing, Cyclic

Bank Access (RL = 6, BL = 4, WL = 2) ........... 36

WRITE/READ and READ/WRITE Timing, Cyclic

Bank Access (RL = 5, BL = 4, WL = 1) ........... 37

Random Access, Single Bank

(RL = 6, BL = 2, WL = 3) ................................... 38

Random Access, Single Bank

(RL = 5, BL = 2, WL = 2, tRC = 6).................... 39

Random Access, Single Bank

(RL = 6, BL = 4, WL = 2) ................................... 40

Random Access, Single Bank

(RL = 5, BL = 4, WL = 1, tRC = 6).................... 41

Package Drawing

144-Ball T-FBGA .................................................... 42

5

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

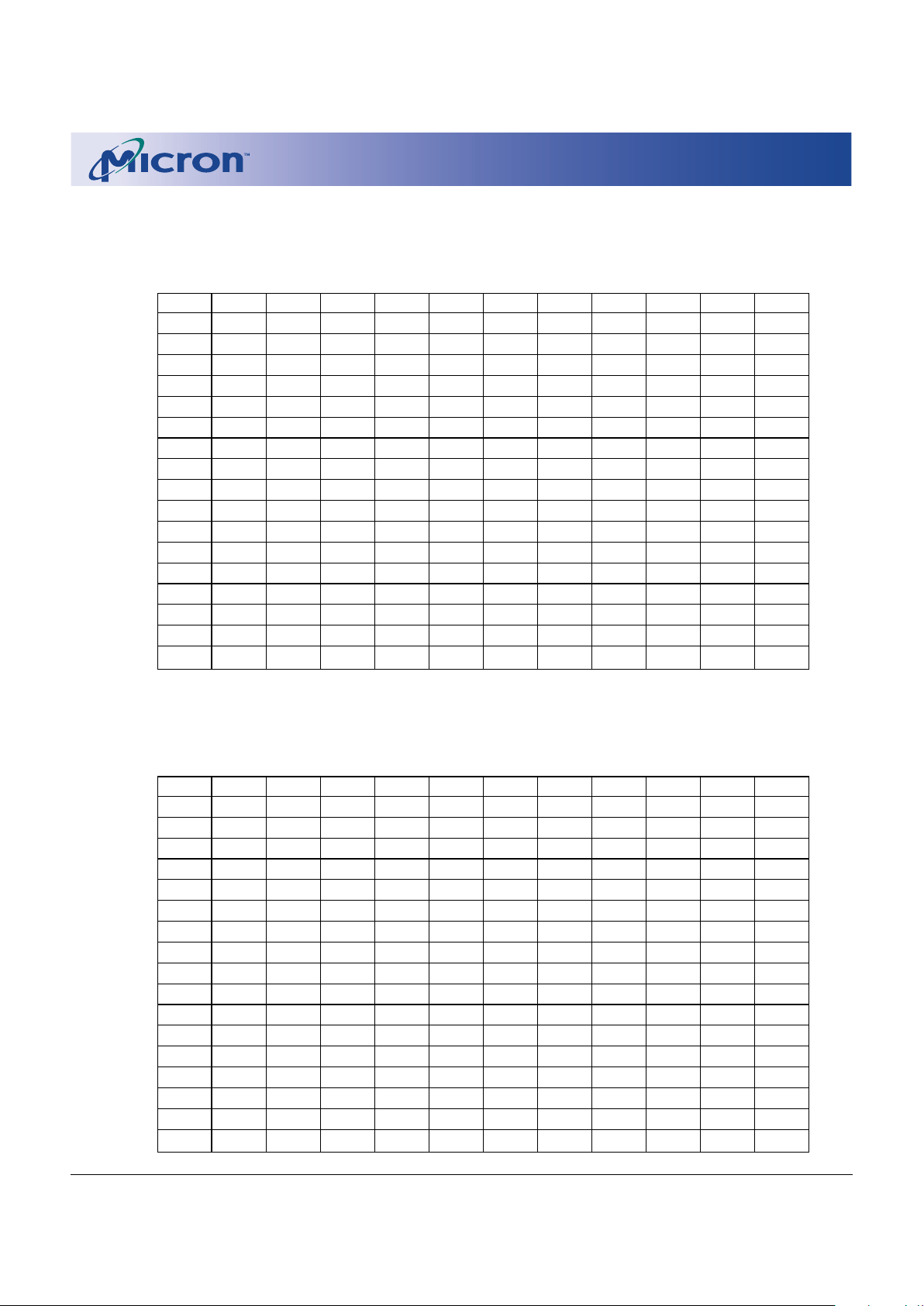

8 MEG x 32 BALL ASSIGNMENT (Top View)

144-Ball T-FBGA

123456789101112

A VSS VEXT VREF VSS VSS VEXT TMS TCK

B VSS DQ8 DQ9 VSSQVSSQ DQ1 DQ0 VSS

C VSS DQ10 DQ11 VDDQVDDQ DQ3 DQ2 VSS

D VSS DQS1 DQS1# VSSQVSSQ DQS0# DQS0 VSS

E VSS DQ12 DQ13 VDDQVDDQ DQ5 DQ4 VSS

F DM0 DQ14 DQ15 VSSQVSSQ DQ7 DQ6 DVLD

G A5 A6 A7 VDD VDD A2 A1 A0

H A8 A9 VSS VSS VSS VSS A4 A3

J AS# B2 VDD VDD VDD VDD B0 CK

K WE# REF# VDD VDD VDD VDD B1 CK#

L A18 CS# VSS VSS VSS VSS A14 A13

M A15 A16 A17 VDD VDD A12 A11 A10

N DM1 DQ22 DQ23 VSSQVSSQ DQ31 DQ30 NC

P VSS DQ20 DQ21 VDDQVDDQ DQ29 DQ28 VSS

R VSS DQS2 DQS2# VSSQVSSQ DQS3# DQS3 VSS

T VSS DQ18 DQ19 VDDQVDDQ DQ27 DQ26 VSS

U VSS DQ16 DQ17 VSSQVSSQ DQ25 DQ24 VSS

V VSS VEXT VREF VSS VSS VEXT TDO TDI

16 MEG x 16 BALL ASSIGNMENT (Top View)

144-Ball T-FBGA

123456789101112

A VSS VEXT VREF VSS VSS VEXT TMS TCK

B VSS NC NC VSSQVSSQ DQ1 DQ0 VSS

C VSS NC NC VDDQVDDQ DQ3 DQ2 VSS

D VSS NC NC VSSQVSSQ DQS0# DQS0 VSS

E VSS NC NC VDDQVDDQ DQ5 DQ4 VSS

F DM0 NC NC VSSQVSSQ DQ7 DQ6 DVLD

G A5 A6 A7 VDD VDD A2 A1 A0

H A8 A9 VSS VSS VSS VSS A4 A3

J AS# B2 VDD VDD VDD VDD B0 CK

K WE# REF# VDD VDD VDD VDD B1 CK#

L A19 CS# VSS VSS VSS VSS A14 A13

M A15 A16 A17 VDD VDD A12 A11 A10

N DM1 NC NC VSSQVSSQ DQ15 DQ14 A18

P VSS NC NC VDDQVDDQ DQ13 DQ12 VSS

R VSS NC NC VSSQVSSQ DQS1# DQS1 VSS

T VSS NC NC VDDQVDDQ DQ11 DQ10 VSS

U VSS NC NC VSSQVSSQ DQ9 DQ8 VSS

V VSS VEXT VREF VSS VSS VEXT TDO TDI

6

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

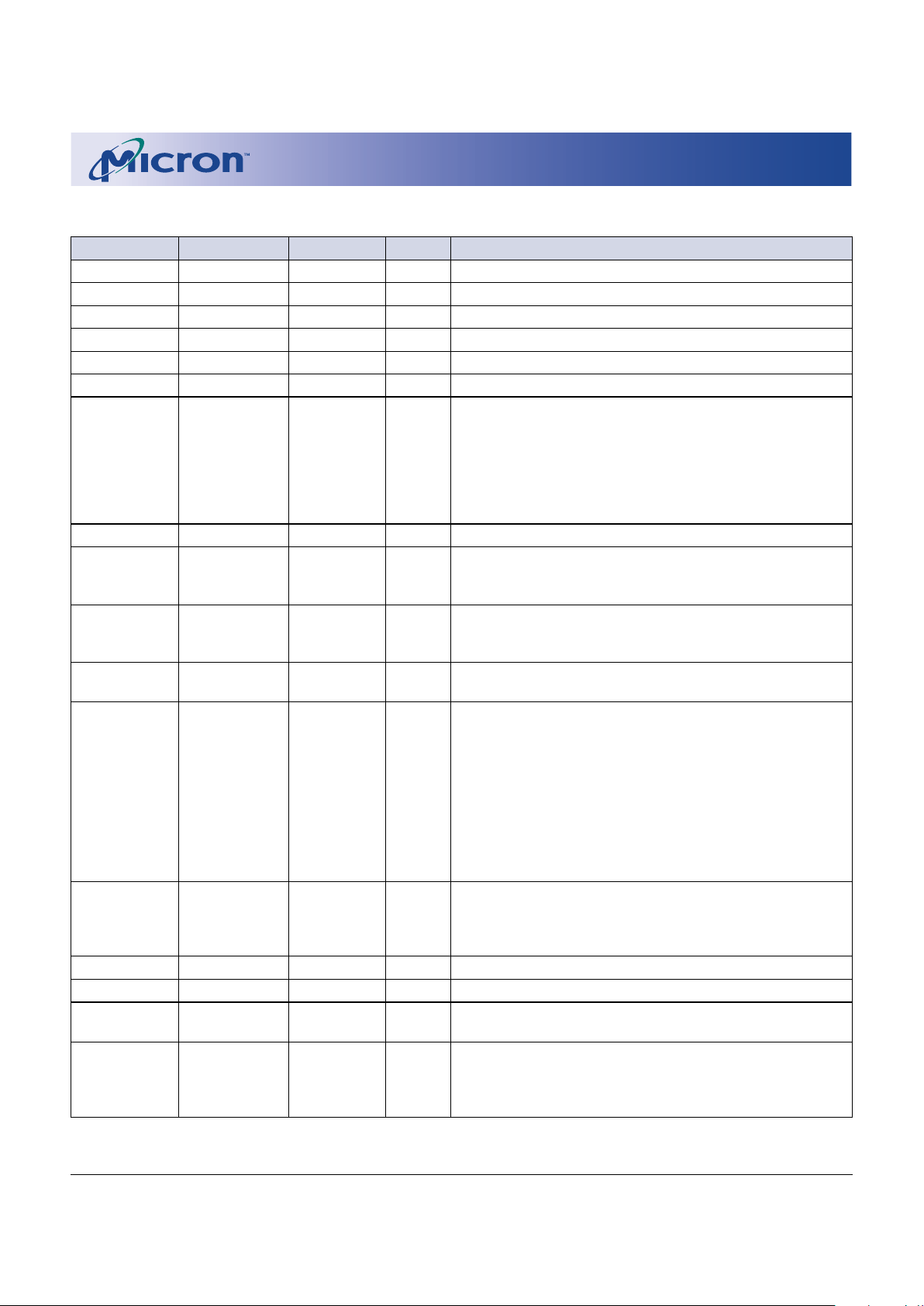

BALL DESCRIPTIONS

T-FBGA (x32) T-FBGA (x16) SYMBOL TYPE DESCRIPTION

12J, 12K 12J, 12K CK, CK# Input Differential input clock pair

2L 2L CS# Input Chip select

1J 1J AS# Input Address strobe

1K 1K WE# Input Write enable

2K 2K REF# Input Auto refresh

11J, 11K, 2J 11J, 11K, 2J B[0:2] Input Bank select

12G, 11G, 10G, 12G, 11G, 10G, A[0:18] Input Address input

12H, 11H, 1G, 12H, 11H, 1G, A[0:19]

2G, 3G, 1H, 2G, 3G, 1H,

2H, 12M, 11M, 2H, 12M, 11M,

10M, 12L, 11L, 10M, 12L, 11L,

1M, 2M, 3M, 1L 1M, 2M, 3M,

12N, 1L

1F, 1N 1F, 1N DM0, DM1 Input Data Mask

11A 11A TMS Input IEEE 1149.1 Test Inputs: JEDEC-standard 1.8V I/O levels.

12V 12V TDI These pins may be left Not Connected if the JTAG

function is not used in the circuit.

12A 12A TCK Input IEEE 1149.1 Clock Input: JEDEC-standard 1.8V I/O levels.

This pin must be tied to VSS if the JTAG function is not

used in the circuit.

3A, 3V 3A, 3V VREF Input Input Reference Voltage: Nominally VDDQ/2. Provides a

reference voltage for the input buffers.

11B, 10B, 11C, 11B, 10B, 11C, DQ0–DQ31 Input/ Synchronous Data I/Os: Input data must meet setup and

10C, 11E, 10E, 10C, 11E, 10E, Output hold times around the rising edges of CK and CK#.

11F, 10F, 2B, 11F, 10F, 11U, Output data is synchronized to DQS and DQS#.

3B, 2C, 3C, 2E, 10U, 11T, 10T,

3E, 2F, 3F, 2U, 11P, 10P, 11N,

3U, 2T, 3T, 2P, 10N

3P, 2N, 3N,

11U, 10U, 11T,

10T, 11P, 10P,

11N, 10N

11D, 2D, 2R, 11D, 11R, DQS0–3 (x32) Output Differential data read strobe

11R, 10D, 3D, 10D, 10R DQS#0–3 (x32)

3R, 10R DQS0–1 (x16)

DQS#0–1 (x16)

12F 12F DVLD Output Data Valid

11V 11V TDO Output IEEE 1149.1 Test Output: JEDEC-standard 1.8V I/O level.

2A, 2V, 2A, 2V, VEXT Supply Power Supply: 2.5V nominal. See DC Electrical

10A, 10V 10A, 10V Characteristics and Operating Condidtions for range.

3J, 3K, 4G, 3J, 3K, 4G, VDD Supply Power Supply: 1.8V nominal. See DC Electrical

4J, 4K, 4M, 4J, 4K, 4M, Characteristics and Operating Conditions for range.

9G, 9J, 9K, 9G, 9J, 9K,

9M, 10J, 10K 9M, 10J, 10K

(continued on next page)

7

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

BALL DESCRIPTIONS (continued)

T-FBGA (x32) T-FBGA (x16) SYMBOL TYPE DESCRIPTION

4C, 4E, 4P, 4C, 4E, 4P, VDDQ Supply Power Supply: Isolated Output Buffer Supply. Nominally

4T, 9C, 9E, 4T, 9C, 9E, 1.8V. See DC Electrical Characteristics and Operating

9P, 9T 9P, 9T Conditions for range.

1A–E, 1P–V, 1A–E, 1P–V, VSS Supply Power Supply: GND.

3H, 3L, 4A, 3H, 3L, 4A,

4H, 4L, 4V, 4H, 4L, 4V,

9A, 9H, 9L, 9A, 9H, 9L,

9V, 10H, 10L, 9V, 10H, 10L,

12B–E, 12P–U 12B–E, 12P–U

4B, 4D, 4F, 4B, 4D, 4F, VSSQ Supply Power Supply: Isolated Output Buffer Supply. GND.

4N, 4R, 4U, 4N, 4R, 4U,

9B, 9D, 9F, 9B, 9D, 9F,

9N, 9R, 9U 9N, 9R, 9U

12N 2B–2F, 2N–2U, NC – No Connect: These signals are not internally connected

3B–3F, 3N–3U and may be connected to ground to improve package

heat dissipation.

8

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

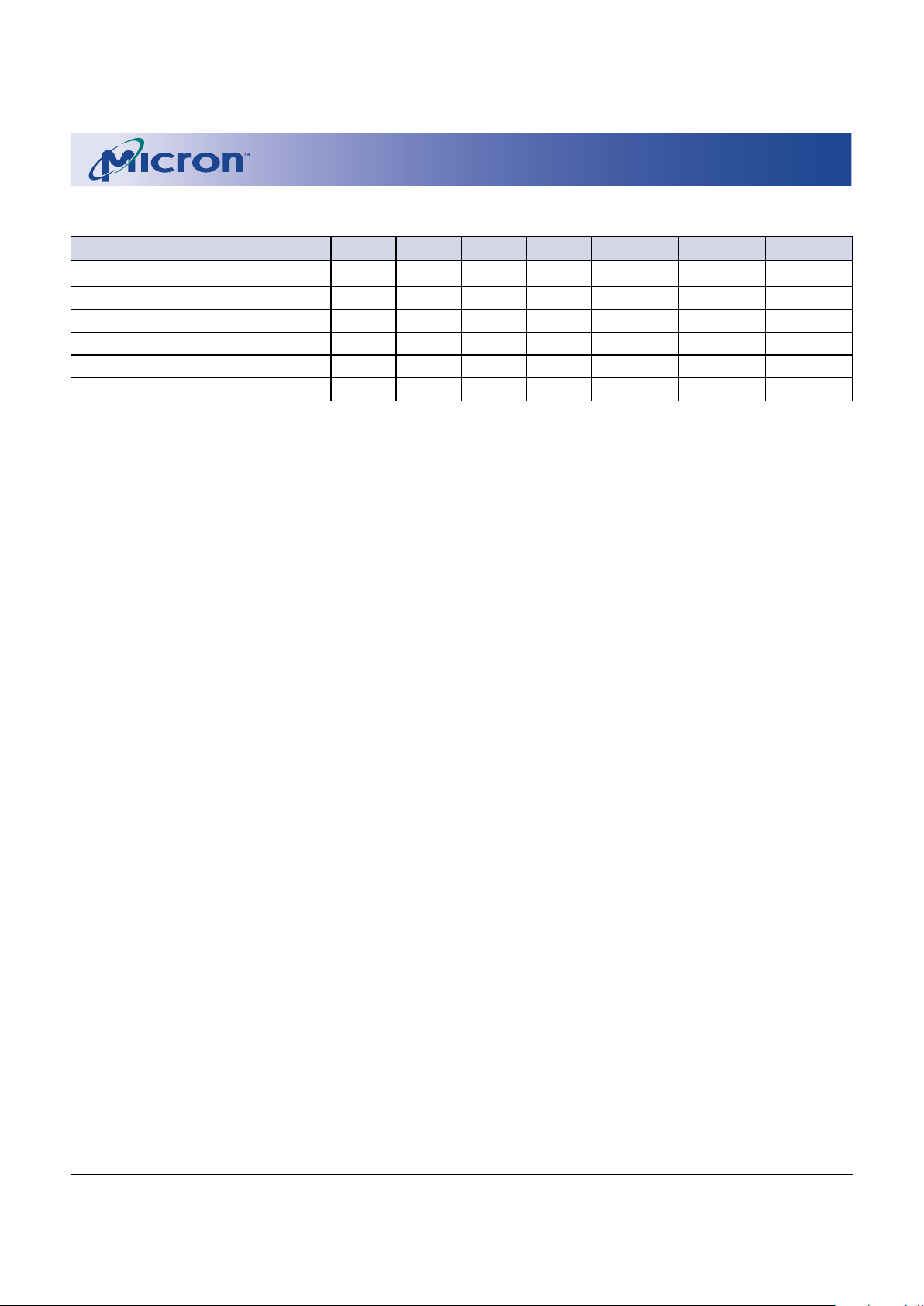

TRUTH TABLE

1

OPERATION CS# AS# WE# REF# A[19:0]

2

B[2:0] DM[1:0]

READ Cycle L L H H VALID VALID X

WRITE Cycle L L L H VALID VALID VALID

NOP: No operation L H H H X X X

Deselect H X X X X X X

Auto Refresh L H H L X VALID X

MRS: Mode Register Set

3

LLLLVALID X X

NOTE: 1. X = “Don’t Care.”

H = logic HIGH.

L = logic LOW.

2. In the x32 configuration A19 is not used.

3. Only A17–A0 are used for the Mode Register Set Command.

9

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

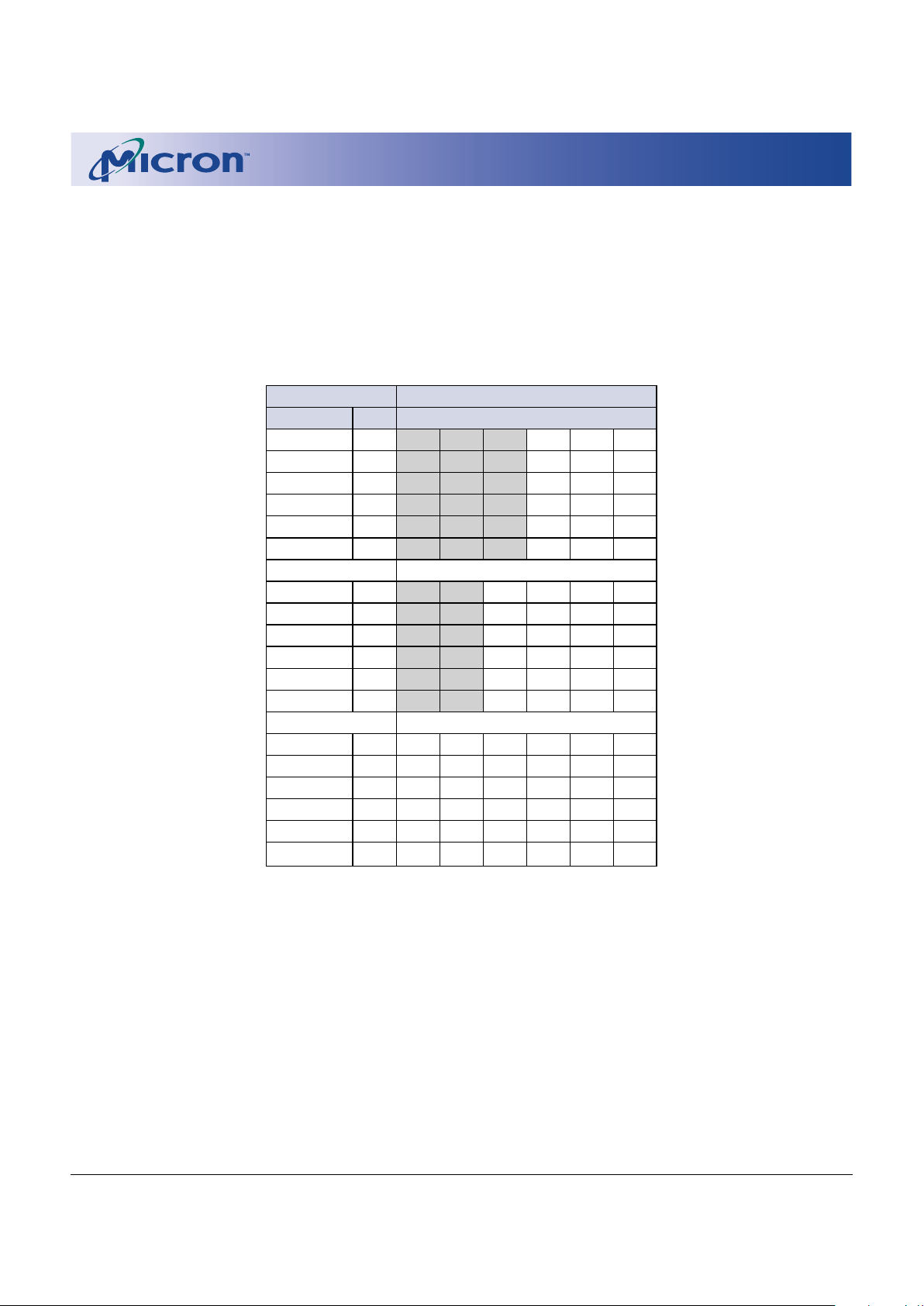

PROGRAMMING DESCRIPTION

The following table shows, for three operating frequencies, the different RLDRAM configurations that can be

programmed into the Mode Register. The Read Latency

(RL) values and the Write Latencies (WL) used by the

RLDRAM Programming Table

NOTE: 1. The speed sort -3.3 provides part functional up to 300 MHz in the configurations 4, 5,

and 6 only.

The functionality of the configurations 1, 2, and 3 is not guaranteed for speed sort -

3.3.

2. The speed sort -4 provides part functional up to 250 MHz in the configurations 3, 4, 5,

and 6 only.

The functionality of the configurations 1 and 2 is not guaranteed for speed sort -4.

3. The speed sort -5 provides part functional up to 200 MHz in all configurations.

RLDRAM for the two Burst Lengths (BL) are also indicated. Finally, the minimum allowed tRC in clock cycles

and in ns are shown as well. The shaded areas correspond

to configurations that are not allowed.

FREQUENCY

Unit -3.3 (300 MHz)

Config. Nb. 1 2 3 4 5 6

RL TCK555678

WL (BL2) TCK 2 2 2 3 4 5

WL (BL4) TCK 1 1 1 2 3 4

t

RC (MIN) TCK 5 6 7 8 9 10

t

RC (MIN) ns 16.7 20.0 23.3 26.7 30.0 33.3

-4 (250 MHz)

Config. Nb. 1 2 3 4 5 6

RL TCK555678

WL (BL2) TCK 2 2 2 3 4 5

WL (BL4) TCK 1 1 1 2 3 4

t

RC (MIN) TCK 5 6 7 8 9 10

t

RC (MIN) ns 20 24 28 32 36 40

-5 (200 MHz)

Config. Nb. 1 2 3 4 5 6

RL TCK555678

WL (BL2) TCK 2 2 2 3 4 5

WL (BL4) TCK 1 1 1 2 3 4

t

RC (MIN) TCK 5 6 7 8 9 10

t

RC (MIN) ns 25 30 35 40 45 50

10

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

MODE REGISTER DESCRIPTION

The address signals A[17:0] are used to set the mode

register.

Mode Register Command Table

NOTE: 1. HSTL-complient current specification

2. Bits A17–A6 MUST be set LOW (Logic 0)

3. Default configuration

4. When Matched Mode is asserted, the automatic I/O impedance calibration is activated

5. Test Mode entry for vendor test mode only

6. The Mode Register Set default configuration corresponds to all address bits equal to zero

RLDRAM

Configuration

Test Mode I/O Driver

Strength

Matched

Mode

Burst

Length

A17–A7

A6 A5 A4

A3 A2

A1

A0

Address

Mode Register

Commands

Reserved

2

0

1

Burst Length

2

3

4

A3

0

0

0

0

1

1

1

1

RLDRAM

Configuration

3

3

1

2

3

4

5

6

3

A2

0

0

1

1

0

0

1

1

A1

0

1

0

1

0

1

0

1

A0

0

1

Matched Mode

Inactive

3

Active

4

A4

0

1

Driver Strength

1

8mA

3

4mA

A5

0

1

Test Mode

Default Mode

3

Test Mode Entry

A6

11

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

IEEE 1149.1 SERIAL BOUNDARY SCAN

(JTAG)

The RLDRAM incorporates a serial boundary scan

Test Access Port (TAP). This port operates in accordance

with IEEE Standard 1149.1-1990 but does not have the

set of functions required for full 1149.1 compliance. These

functions from the IEEE specification are excluded because their inclusion places an added delay in the critical

speed path of the RLDRAM. Note that the TAP controller

functions in a manner that does not conflict with the

operation of other devices using 1149.1 fully compliant

TAPs. The TAP operates using JEDEC-standard 1.8V I/O

logic levels.

The RLDRAM contains a TAP controller, instruction

register, boundary scan register, bypass register, and ID

register.

DISABLING THE JTAG FEATURE

It is possible to operate the RLDRAM without using the

JTAG feature. To disable the TAP controller, TCK must be

tied LOW (VSS) to prevent clocking of the device. TDI and

TMS are internally pulled up and may be unconnected.

They may alternately be connected to VDD through a pullup resistor. TDO should be left unconnected. Upon powerup, the device will come up in a reset state which will not

interfere with the operation of the device.

TEST ACCESS PORT (TAP)

TEST CLOCK (TCK)

The test clock is used only with the TAP controller. All

inputs are captured on the rising edge of TCK. All outputs

are driven from the falling edge of TCK.

TEST MODE SELECT (TMS)

The TMS input is used to give commands to the TAP

controller and is sampled on the rising edge of TCK. It is

allowable to leave this pin unconnected if the TAP is not

used. The pin is pulled up internally, resulting in a logic

HIGH level.

TEST DATA-IN (TDI)

The TDI pin is used to serially input information into the

registers and can be connected to the input of any of the

registers. The register between TDI and TDO is chosen by

the instruction that is loaded into the TAP instruction

register. For information on loading the instruction register, see Figure 1. TDI is internally pulled up and can be

unconnected if the TAP is unused in an application. TDI

is connected to the most significant bit (MSB) of any

register. (See Figure 2.)

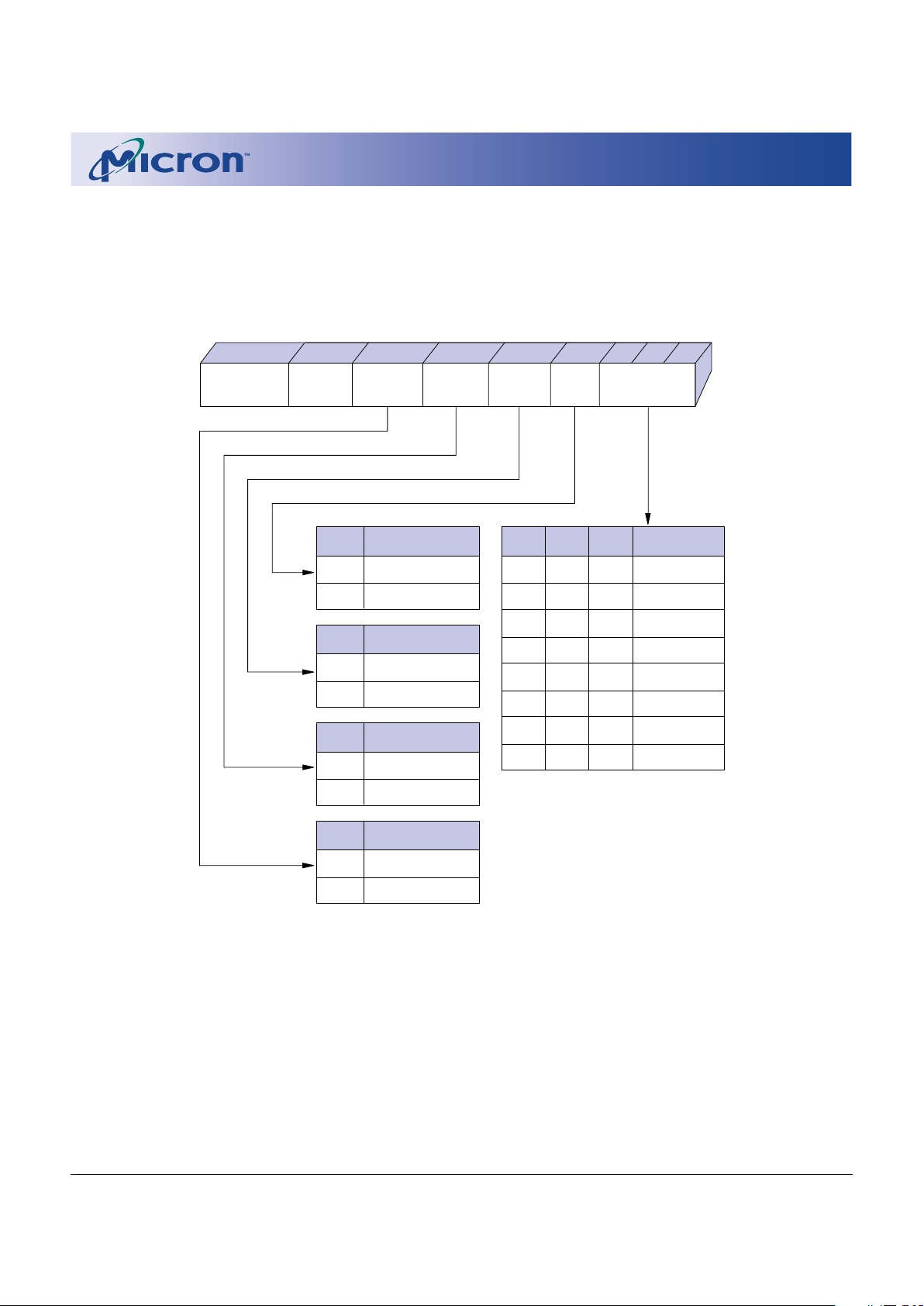

Figure 1

TAP Controller State Diagram

NOTE: The 0/1 next to each state represents the value of TMS at the rising edge of TCK.

TEST-LOGIC

RESET

RUN-TEST/

IDLE

SELECT

DR-SCAN

SELECT

IR-SCAN

CAPTURE-DR

SHIFT-DR

CAPTURE-IR

SHIFT-IR

EXIT1-DR

PAUSE-DR

EXIT1-IR

PAUSE-IR

EXIT2-DR

UPDATE-DR

EXIT2-IR

UPDATE-IR

1

1

1

0

1 1

0 0

1 1

1

0

0

0

0 0

0

0

0 0

1

0

1

1

0

1

0

1

1

1

1 0

12

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

TEST DATA-OUT (TDO)

The TDO output pin is used to serially clock data-out

from the registers. The output is active depending upon

the current state of the TAP state machine. (See Figure 1.)

The output changes on the falling edge of TCK. TDO is

connected to the least significant bit (LSB) of any register.

(See Figure 2.)

PERFORMING A TAP RESET

A RESET is performed by forcing TMS HIGH (VDD) for

five rising edges of TCK. This RESET does not affect the

operation of the RLDRAM and may be performed while the

RLDRAM is operating.

At power-up, the TAP is reset internally to ensure that

TDO comes up in a High-Z state.

TAP REGISTERS

Registers are connected between the TDI and TDO

pins and allow data to be scanned into and out of the

RLDRAM test circuitry. Only one register can be selected

at a time through the instruction register. Data is serially

loaded into the TDI pin on the rising edge of TCK. Data is

output on the TDO pin on the falling edge of TCK.

INSTRUCTION REGISTER

Three-bit instructions can be serially loaded into the

instruction register. This register is loaded when it is

placed between the TDI and TDO pins as shown in Figure

2. Upon power-up, the instruction register is loaded with

the IDCODE instruction. It is also loaded with the IDCODE

instruction if the controller is placed in a reset state as

described in the previous section.

Bypass Register

0

Instruction Register

01234567

Identification Register

012293031 ...

Boundary Scan Register

012..x ...

Selection

Circuitry

Selection

Circuitry

TCK

TMS

TAP Controller

TDI TDO

x = 103 for all configurations.

Figure 2

TAP Controller Block Diagram

When the TAP controller is in the Capture-IR state,

the two least significant bits are loaded with a binary “01”

pattern to allow for fault isolation of the board-level serial

test data path.

BYPASS REGISTER

To save time when serially shifting data through registers, it is sometimes advantageous to skip certain chips.

The bypass register is a single-bit register that can be

placed between the TDI and TDO pins. This allows data to

be shifted through the RLDRAM with minimal delay. The

bypass register is set LOW (VSS) when the BYPASS

instruction is executed.

BOUNDARY SCAN REGISTER

The boundary scan register is connected to all the

input and bidirectional pins on the RLDRAM. Several no

connect (NC) pins are also included in the scan register to

reserve pins. The RLDRAM has a 104-bit register.

The boundary scan register is loaded with the contents

of the RAM I/O ring when the TAP controller is in the

Capture-DR state and is then placed between the TDI and

TDO pins when the controller is moved to the

Shift-DR state. The EXTEST, SAMPLE/PRELOAD, and

SAMPLE Z instructions can be used to capture the contents of the I/O ring.

The Boundary Scan Order tables show the order in

which the bits are connected. Each bit corresponds to one

of the pins on the RLDRAM package. The MSB of the

register is connected to TDI, and the LSB is connected to

TDO.

13

256: x16, x32 RLDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT49H8M32_3.p65 – Rev. 3, Pub. 6/02 ©2002, Micron Technology, Inc.

ADVANCE

256Mb: x16, x32

2.5V VEXT, 1.8V VDD, 1.8V VDDQ, RLDRAM

ter upon power-up or whenever the TAP controller is

given a test logic reset state.

SAMPLE/PRELOAD

SAMPLE/PRELOAD is a 1149.1 mandatory instruction. The PRELOAD portion of this instruction is not

implemented, so the device TAP controller is not fully

1149.1-compliant.

When the SAMPLE/PRELOAD instruction is loaded

into the instruction register and the TAP controller is in the

Capture-DR state, a snapshot of data on the inputs and bidirectional pins is captured in the boundary scan register.

The user must be aware that the TAP controller clock

can only operate at a frequency up to 10 MHz, while the

RLDRAM clock operates more than an order of magnitude

faster. Because there is a large difference in the clock

frequencies, it is possible that during the Capture-DR

state, an input or output will undergo a transition. The TAP

may then try to capture a signal while in transition (metastable state). This will not harm the device, but there is no

guarantee as to the value that will be captured. Repeatable results may not be possible.

To guarantee that the boundary scan register will

capture the correct value of a signal, the RLDRAM signal

must be stabilized long enough to meet the TAP controller’s

capture setup plus hold time (tCS plus tCH). The RLDRAM

clock input might not be captured correctly if there is no

way in a design to stop (or slow) the clock during a

SAMPLE/PRELOAD instruction. If this is an issue, it is still

possible to capture all other signals and simply ignore the

value of the CK and CK# captured in the boundary scan

register.

Once the data is captured, it is possible to shift out the

data by putting the TAP into the Shift-DR state. This places

the boundary scan register between the TDI and TDO pins.

Note that since the PRELOAD part of the command is

not implemented, putting the TAP to the Update-DR state

while performing a SAMPLE/PRELOAD instruction will

have the same effect as the Pause-DR command.

BYPASS

When the BYPASS instruction is loaded in the instruction register and the TAP is placed in a Shift-DR state, the

bypass register is placed between TDI and TDO. The

advantage of the BYPASS instruction is that it shortens

the boundary scan path when multiple devices are connected together on a board.

RESERVED

These instructions are not implemented but are reserved for future use. Do not use these instructions.

IDENTIFICATION (ID) REGISTER

The ID register is loaded with a vendor-specific, 32-bit

code during the Capture-DR state when the IDCODE

command is loaded in the instruction register. The IDCODE

is hardwired into the RLDRAM and can be shifted out when

the TAP controller is in the Shift-DR state. The ID register

has a vendor code and other information described in the

Identification Register Definitions table.

TAP INSTRUCTION SET

OVERVIEW

Eight different instructions are possible with the threebit instruction register. All combinations are listed in the

Instruction Codes table (see page 16). Three of these

instructions are listed as RESERVED and should not be

used. The other five instructions are described in detail

below.

The TAP controller used in this RLDRAM is not fully

compliant to the 1149.1 convention because some of the

mandatory 1149.1 instructions are not fully implemented.

The TAP controller cannot be used to load address, data

or control signals into the RLDRAM and cannot preload

the I/O buffers. The RLDRAM does not implement the

1149.1 commands EXTEST or INTEST or the PRELOAD

portion of SAMPLE/PRELOAD; rather it performs a capture of the I/O ring when these instructions are executed.

Instructions are loaded into the TAP controller during

the Shift-IR state when the instruction register is placed

between TDI and TDO. During this state, instructions are

shifted through the instruction register through the TDI

and TDO pins. To execute the instruction once it is shifted

in, the TAP controller needs to be moved into the UpdateIR state.

EXTEST

EXTEST is a mandatory 1149.1 instruction which is to

be executed whenever the instruction register is loaded

with all 0s. EXTEST is not implemented in the TAP

controller, hence this device is not IEEE 1149.1 compliant.

The TAP controller does recognize an all-0 instruction.

When an EXTEST instruction is loaded into the instruction

register, the RLDRAM responds as if a SAMPLE/PRELOAD

instruction has been loaded. EXTEST does not place the

RLDRAM outputs in a High-Z state, CQ, CQ#.

IDCODE

The IDCODE instruction causes a vendor-specific, 32bit code to be loaded into the instruction register. It also

places the instruction register between the TDI and TDO

pins and allows the IDCODE to be shifted out of the device

when the TAP controller enters the Shift-DR state. The

IDCODE instruction is loaded into the instruction regis-

Loading...

Loading...