MICRON MT46V32M8FJ-75Z, MT46V32M8FJ-6, MT46V64M4TG-6, MT46V64M4TG-6T, MT46V64M4TG-75Z Datasheet

...

PRELIMINARY

256Mb: x4, x8, x16

DDR333 SDRAM Addendum

‡

DOUBLE DATA RATE

(DDR) SDRAM

FEATURES

• 167 MHz Clock, 333 Mb/s/p data rate

•VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V

• Bidirectional data strobe (DQS) transmitted/

received with data, i.e., source-synchronous data

capture (x16 has two - one per byte)

• Internal, pipelined double-data-rate (DDR)

architecture; two data accesses per clock cycle

• Differential clock inputs (CK and CK#)

• Commands entered on each positive CK edge

• DQS edge-aligned with data for READs; centeraligned with data for WRITEs

• DLL to align DQ and DQS transitions with CK

• Four internal banks for concurrent operation

• Data mask (DM) for masking write data (x16 has

two - one per byte)

• Programmable burst lengths: 2, 4, or 8

• Concurrent Auto Precharge option supported

• Auto Refresh and Self Refresh Modes

• FBGA package available

• 2.5V I/O (SSTL_2 compatible)

•tRAS lockout (tRAP = tRCD)

• Backwards compatible with DDR200 and DDR266

MT46V64M4 – 16 Meg x 4 x 4 banks

MT46V32M8 – 8 Meg x 8 x 4 banks

MT46V16M16 – 4 Meg x 16 x 4 banks

For the latest data sheet revisions, please refer to the Micron

Web site: www.micron.com/dramds

DDR333 COMPATIBILITY

DDR333 meets or surpasses all DDR266 timing requirements thus assuring full backwards compatibility

with current DDR designs. In addition, these devices

support concurrent auto-precharge and tRAS lockout

for improved timing performance. The 256Mb,

DDR333 device will support an (tREFI) average periodic refresh interval of 7.8us.

The standard 66-pin TSOP package is offered for

point-to-point applications where the FBGA package

is intended for the multi-drop systems.

The Micron 256Mb data sheet provides full specifications and functionality unless specified herein.

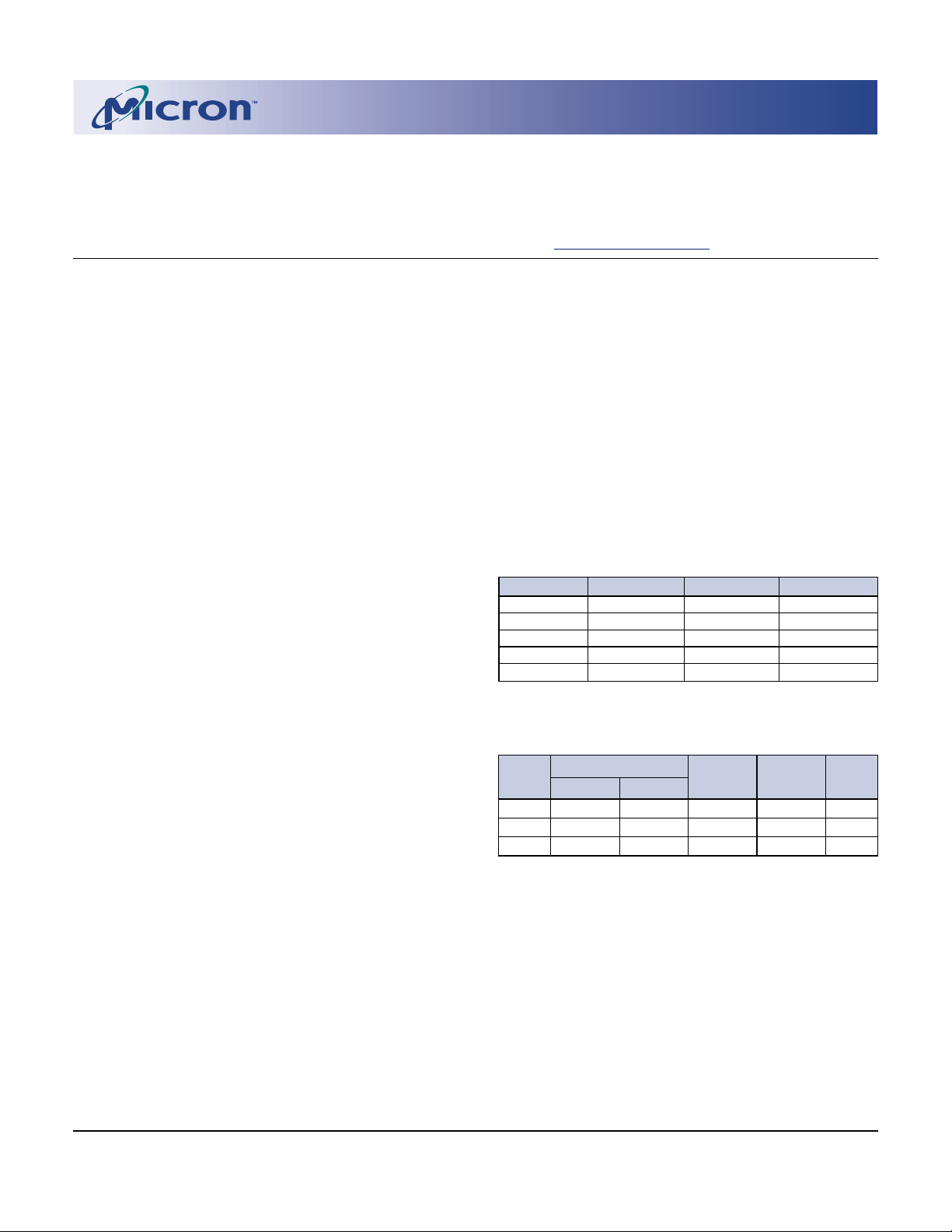

CONFIGURATION

Architecture 64 Meg x 4 32 Meg x 8 16 Meg x 16

Configuration 16 Meg x 4 x 4 banks 8 Meg x 8 x 4 banks 4 Meg x 16 x 4 banks

Refresh Count 8K 8K 8K

Row Addressing 8K (A0–A12) 8K (A0–A12) 8K (A0–A12)

Bank Addressing 4 (BA0, BA1) 4 (BA0, BA1) 4 (BA0, BA1)

Column Addressing 2K (A0–A9, A11) 1K (A0–A9) 512 (A0– A8)

OPTIONS PART NUMBER

• Configuration

64 Meg x 4 (16 Meg x 4 x 4 banks) 64M4

32 Meg x 8 (8 Meg x 8 x 4 banks) 32M8

16 Meg x 16 (4 Meg x 16 x 4 banks) 16M16

• Plastic Package

66-Pin TSOP (OCPL) TG

60-Ball FBGA (16x9mm) FJ

• Timing - Cycle Time

6ns @ CL = 2.5 (DDR333B–FBGA)

6ns @ CL = 2.5 (DDR333B–TSOP)

7.5ns @ CL = 2 (DDR266A)

• Self Refresh

Standard none

NOTE: 1. Supports PC2700 modules with 2.5-3-3 timing

2. Supports PC2100 modules with 2-3-3 timing

256Mb: x4, x8, x16 DDR333 SDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

256Mx4x8x16DDR333_B.p65 – Rev. B; Pub. 10/01 ©2001, Micron Technology, Inc.

‡ PRODUCTS AND SPECIFICATIONS DISCUSSED HEREIN ARE FOR EVALUATION AND REFERENCE PURPOSES ONLY AND ARE SUBJECT TO CHANGE BY

MICRON WITHOUT NOTICE. PRODUCTS ARE ONLY WARRANTED BY MICRON TO MEET MICRON’S PRODUCTION AND DATA SHEET SPECIFICATIONS.

2

1

-6

1

-6T

-75Z

KEY TIMING PARAMETERS

SPEED CLOCK RATE DATA-OUT ACCESS DQS-DQ

GRADE CL = 2

-6 133 MHz 167 MHz 2.15ns ±0.70ns +0.35ns

-6T 133 MHz 167 MHz 2.0ns ±0.75ns +0.45ns

-75Z 133 MHz 133 MHz 2.5ns ±0.75ns +0.50ns

NOTE: 1. CL = CAS (Read) Latency

2. With a 50/50 clock duty cycle and a minimum clock

3. -75, -8 are also available; see base data sheet.

1

CL = 2.51WINDOW2WINDOW SKEW

rate @ CL = 2 ( -75Z) and CL = 2.5 (-6, -6T).

1

3

PRELIMINARY

256Mb: x4, x8, x16

DDR333 SDRAM Addendum

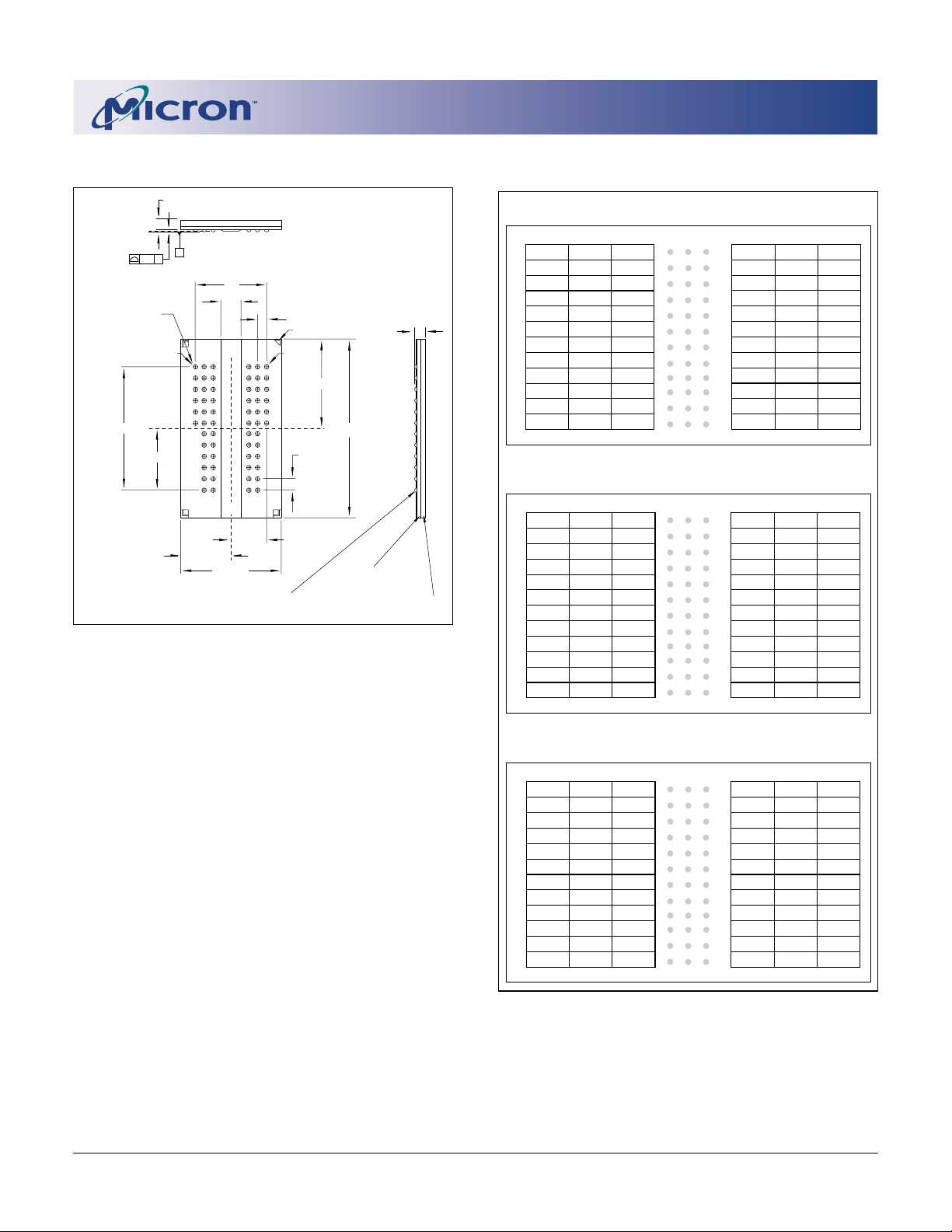

FBGA 60-BALL PACKAGE DIMENSION

0.850 ±0.075

SEATING PLANE

C

0.10 C

6.40

1.80

61X ∅0.45

SOLDER BALL DIAMETER

REFERS TO POST REFLOW

CONDITION. THE PREREFLOW DIAMETER IS Ø 0.40

BALL A9

11.00

5.50 ±0.05

CTR

Bottom View

C

L

3.20 ±0.05

4.50 ±0.05

9 .00 ±0.10

SOLDER BALL MATERIAL: EUTECTIC 63% Sn, 37% Pb or

62% Sn, 36% Pb, 2%Ag

SOLDER BALL PAD: Ø .33mm

0.80 TYP

BALL A1

C

L

PIN A1 ID

8.00 ±0.05

1.00

TYP

1.20 MAX

16.00 ±0.10

SUBSTRATE: PLASTIC LAMINATE

MOLD COMPOUND: EPOXY NOVOLAC

FBGA PACKAGE MARKING

Due to the physical size of the FBGA package, the full

ordering part number is not printed on the package.

Instead the following package code is utilized.

FBGA PACKAGE PINOUT

x4 (Top View)

123456 789

A

V

B

C

D

E

V

F

G

H

J

K

L

M

A

V

B

C

D

E

F

G

H

J

K

L

M

NC

SS

NC

NC

NC

NC

REF

Q

V

V

V

V

DD

SS

DD

SS

SS

V

CK

A12

A11

A8

A6

A4

VSS

Q

DQ3

Q

NC

Q

DQ2

Q

DQS

DM

CK#

CKE

A9

A7

A5

SS

V

x8 (Top View)

123456 789

DQ7

SS

V

NC

NC

NC

NC

Q

V

V

V

V

REF

DD

SS

DD

SS

SS

V

CK

A12

A11

A8

A6

A4

VSS

Q

DQ6

Q

DQ5

Q

DQ4

Q

DQS

DM

CK#

CKE

A9

A7

A5

SS

V

A

B

C

D

E

F

G

H

J

K

L

M

A

B

C

D

E

F

G

H

J

K

L

M

V

DD

DQ0

NC

DQ1

NC

NC

WE#

RAS#

BA1

A0

A2

DD

V

V

DD

DQ1

DQ2

DQ3

NC

NC

WE#

RAS#

BA1

A0

A2

DD

V

NC

SS

V

DD

V

V

SS

DD

V

DD

V

CAS#

CS#

BA0

A10

A1

A3

DQ0

SS

V

DD

V

SS

V

DD

V

DD

V

CAS#

CS#

BA0

A10

A1

A3

V

DD

Q

Q

NC

Q

NC

Q

NC

Q

NC

A13

V

DD

Q

Q

NC

Q

NC

Q

NC

Q

NC

A13

Top mark contains five fields 12345

• Field 1 (Product Family)

DRAM D

DRAM - ES Z

• Field 2 (Product Type)

2.5 Volt, DDR SDRAM, 60-ball L

• Field 3 (Width)

x4 devices B

x8 devices C

x16 devices D

123456 789

A

B

C

D

E

F

G

H

J

K

L

M

V

SS

Q

DQ14

DQ12

DQ10

DQ8

REF

V

DQ15

DD

V

V

SS

Q

DD

V

SS

Q

V

SS

V

CK

A12

A11

A8

A6

A4

Q

Q

VSS

DQ13

DQ11

DQ9

UDQS

UDM

CK#

CKE

A9

A7

A5

V

x16 (Top View)

SS

A

B

C

D

E

F

G

H

J

K

L

M

V

DD

DQ2

DQ4

DQ6

LDQS

LDM

WE#

RAS#

BA1

A0

A2

DD

V

DQ0

SS

V

DD

V

SS

V

DD

V

V

DD

CAS#

CS#

BA0

A10

A1

A3

V

DD

Q

Q

DQ1

Q

DQ3

Q

DQ5

Q

DQ7

A13

• Field 4 (Density / Size)

256Mb H

• Filed 5 (Speed Grade)

-6 J

-75Z P

-75 F

-8 C

Example top mark for a MT46V32M4FJ-6: DLBFJ

256Mb: x4, x8, x16 DDR333 SDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

256Mx4x8x16DDR333_B.p65 – Rev. B; Pub. 10/01 ©2001, Micron Technology, Inc.

2

PRELIMINARY

256Mb: x4, x8, x16

DDR333 SDRAM Addendum

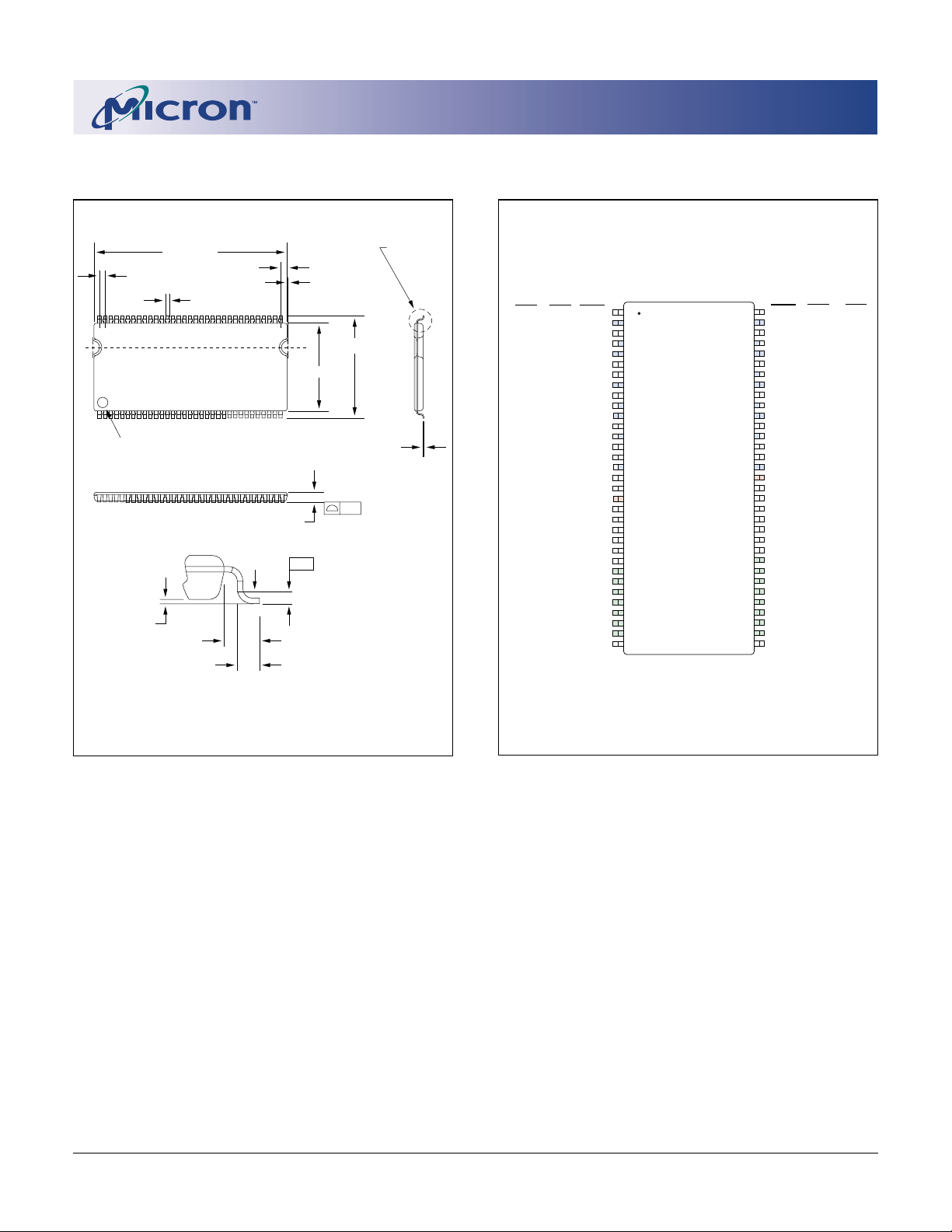

66-PIN TSOP PACKAGE DIMENSION

PIN #1 ID

0.10

0.65 TYP

+0.10

-0.05

22.22 ± 0.08

0.32 ± .075 TYP

DETAIL A

1.20 MAX

GAGE PLANE

0.71

0.10 (2X)

11.76 ±0.10

10.16 ±0.08

0.10

0.25

0.80 TYP

0.50 ±0.10

0.15

SEE DETAIL A

+0.03

-0.02

66-PIN TSOP PACKAGE PIN ASSIGMENT

(TOP VIEW)

V

NC

V

DD

NC

DQ0

V

SS

NC

NC

V

DD

NC

DQ1

V

SS

NC

NC

V

DD

NC

NC

V

DNU

NC

WE#

CAS#

RAS#

CS#

NC

BA0

BA1

A10/AP

A0

A1

A2

A3

V

DD

Q

Q

Q

Q

Q

DD

DD

x8x4

V

DQ0

V

DD

DQ1

V

SS

DQ2

V

DD

DQ3

V

SS

V

DD

V

DNU

WE#

CAS#

RAS#

CS#

BA0

BA1

A10/AP

V

DD

NC

NC

NC

NC

NC

NC

NC

DD

NC

NC

A0

A1

A2

A3

DD

Q

Q

Q

Q

Q

x16

VDD

DQ0

VDDQ

DQ1

DQ2

VssQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VssQ

DQ7

V

DD

LDQS

VDD

DNU

LDM

WE#

CAS#

RAS#

CS#

BA0

BA1

A10/AP

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

NC

15

Q

16

17

NC

18

19

20

21

22

23

24

25

NC

26

27

28

29

A0

30

A1

31

A2

32

A3

33

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

x16

V

SS

DQ15

V

SS

Q

DQ14

DQ13

V

DD

DQ12

DQ11

V

SS

Q

DQ10

DQ9

V

DD

DQ8

NC

V

SS

Q

UDQS

DNU

V

REF

V

SS

UDM

CK#

CK

CKE

NC

A12

A11

A9

A8

A7

A6

A5

A4

V

SS

Q

Q

x8 x4

V

SS

DQ7

V

SS

Q

NC

DQ6

V

DD

Q

NC

DQ5

V

SS

Q

NC

DQ4

V

DD

Q

NC

NC

V

SS

Q

DQS

DNU

V

REF

V

SS

DM

CK#

CK

CKE

NC

A12

A11

A9

A8

A7

A6

A5

A4

V

SS

V

SS

NC

V

SS

NC

DQ3

V

DD

NC

NC

V

SS

NC

DQ2

V

DD

NC

NC

V

SS

DQS

DNU

V

REF

V

SS

DM

CK#

CK

CKE

NC

A12

A11

A9

A8

A7

A6

A5

A4

V

SS

Q

Q

Q

Q

Q

NOTE: 1. All dimensions in millimeters.

2. Package width and length do not include mold protrusion; allowable mold protrusion is 0.25mm

per side.

256Mb: x4, x8, x16 DDR333 SDRAM Micron Technology, Inc., reserves the right to change products or specifications without notice.

256Mx4x8x16DDR333_B.p65 – Rev. B; Pub. 10/01 ©2001, Micron Technology, Inc.

3

Loading...

Loading...