MICRON MT28F800B3WG-9BET, MT28F800B3WG-9T, MT28F800B3WG-9TET, MT28F800B3SG-9TET, MT28F800B3SG-9T Datasheet

...

8Mb

SMART 3 BOOT BLOCK FLASH MEMORY

FLASH MEMORY

FEATURES

• Eleven erase blocks:

16KB/8K-word boot block (protected)

Two 8KB/4K-word parameter blocks

Eight main memory blocks

• Smart 3 technology (B3):

3.3V ±0.3V VCC

3.3V ±0.3V VPP application programming

5V ±10% VPP application/production programming

• Compatible with 0.3µm Smart 3 device

• Advanced 0.18µm CMOS floating-gate process

• Address access time: 90ns

• 100,000 ERASE cycles

• Industry-standard pinouts

• Inputs and outputs are fully TTL-compatible

• Automated write and erase algorithm

• Two-cycle WRITE/ERASE sequence

• TSOP, SOP and FBGA packaging options

• Byte- or word-wide READ and WRITE

(MT28F800B3):

1 Meg x 8/512K x 16

MT28F008B3

MT28F800B3

3V Only, Dual Supply (Smart 3)

40-Pin TSOP Type I 48-Pin TSOP Type I

1

44-Pin SOP

OPTIONS MARKING

• Timing

90ns access -9

• Configurations

1 Meg x 8 MT28F008B3

512K x 16/1 Meg x 8 MT28F800B3

• Boot Block Starting Word Address

Top (7FFFFh) T

Bottom (00000h) B

• Operating Temperature Range

Commercial (0ºC to +70ºC) None

Extended (-40ºC to +85ºC) ET

• Packages

40-pin TSOP Type I

48-pin TSOP Type I (

44-pin SOP (

NOTE: 1. This generation of devices does not support 12V VPP

MT28F800B3)

production programming; however, 5V VPP application

production programming can be used with no loss of

performance.

MT28F800B3WG-9 BET

(MT28F008B3)

MT28F800B3)

Part Number Example:

VG

WG

SG

GENERAL DESCRIPTION

The MT28F008B3 (x8) and MT28F800B3 (x16/x8) are

low-voltage, nonvolatile, electrically block-erasable (flash),

programmable memory devices containing 8,388,608 bits

organized as 524,288 words (16 bits) or 1,048,576 bytes (8

bits). Writing and erasing the device is done with a VPP

voltage of either 3.3V or 5V, while all operations are

performed with a 3.3V VCC. Due to process technology

advances, 5V VPP is optimal for application and production

programming. These devices are fabricated with Micron’s

advanced 0.18µm CMOS floating-gate process.

The MT28F008B3 and MT28F800B3 are organized

into eleven separately erasable blocks. To ensure that

critical firmware is protected from accidental erasure or

overwrite, the devices feature a hardware-protected

boot block. This block may be used to store code implemented in low-level system recovery. The remaining

blocks vary in density and are written and erased with

no additional security measures.

Refer to Micron’s Web site (www.micron.com/flash)

for the latest data sheet.

8Mb Smart 3 Boot Block Flash Memory

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

PRODUCTS AND SPECIFICATIONS DISCUSSED HEREIN ARE SUBJECT TO CHANGE BY MICRON WITHOUT NOTICE.

1

V

PP

A18

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE#

V

SS

OE#

DQ0

DQ8

DQ1

DQ9

DQ2

DQ10

DQ3

DQ11

RP#

WE#

A8

A9

A10

A11

A12

A13

A14

A15

A16

BYTE#

V

SS

DQ15/(A - 1)

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

48-Pin TSOP Type I 44-Pin SOP

A15

A14

A13

A12

A11

A10

WE#

RP#

V

WP#

A18

A17

A9

A8

NC

NC

NC

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

PP

13

14

15

16

17

18

19

20

21

22

23

24

ORDER NUMBER AND PART MARKING

MT28F800B3WG-9 B

MT28F800B3WG-9 T

MT28F800B3WG-9 BET

MT28F800B3WG-9 TET

SMART 3 BOOT BLOCK FLASH MEMORY

PIN ASSIGNMENT (Top View)

A16

48

BYTE#

47

V

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

SS

DQ15/(A - 1)

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

CC

V

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

SS

V

CE#

A0

8Mb

ORDER NUMBER AND PART MARKING

MT28F800B3SG-9 B

MT28F800B3SG-9 T

MT28F800B3SG-9 BET

MT28F800B3SG-9 TET

40-Pin TSOP Type I

A16

A15

A14

A13

A12

A11

A9

A8

WE#

RP#

V

PP

WP#

A18

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

ORDER NUMBER AND PART MARKING

MT28F008B3VG-9 B

MT28F008B3VG-9 T

MT28F008B3VG-9 BET

MT28F008B3VG-9 TET

2

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

A17

V

SS

NC

A19

A10

DQ7

DQ6

DQ5

DQ4

CC

V

V

CC

NC

DQ3

DQ2

DQ1

DQ0

OE#

SS

V

CE#

A0

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

2

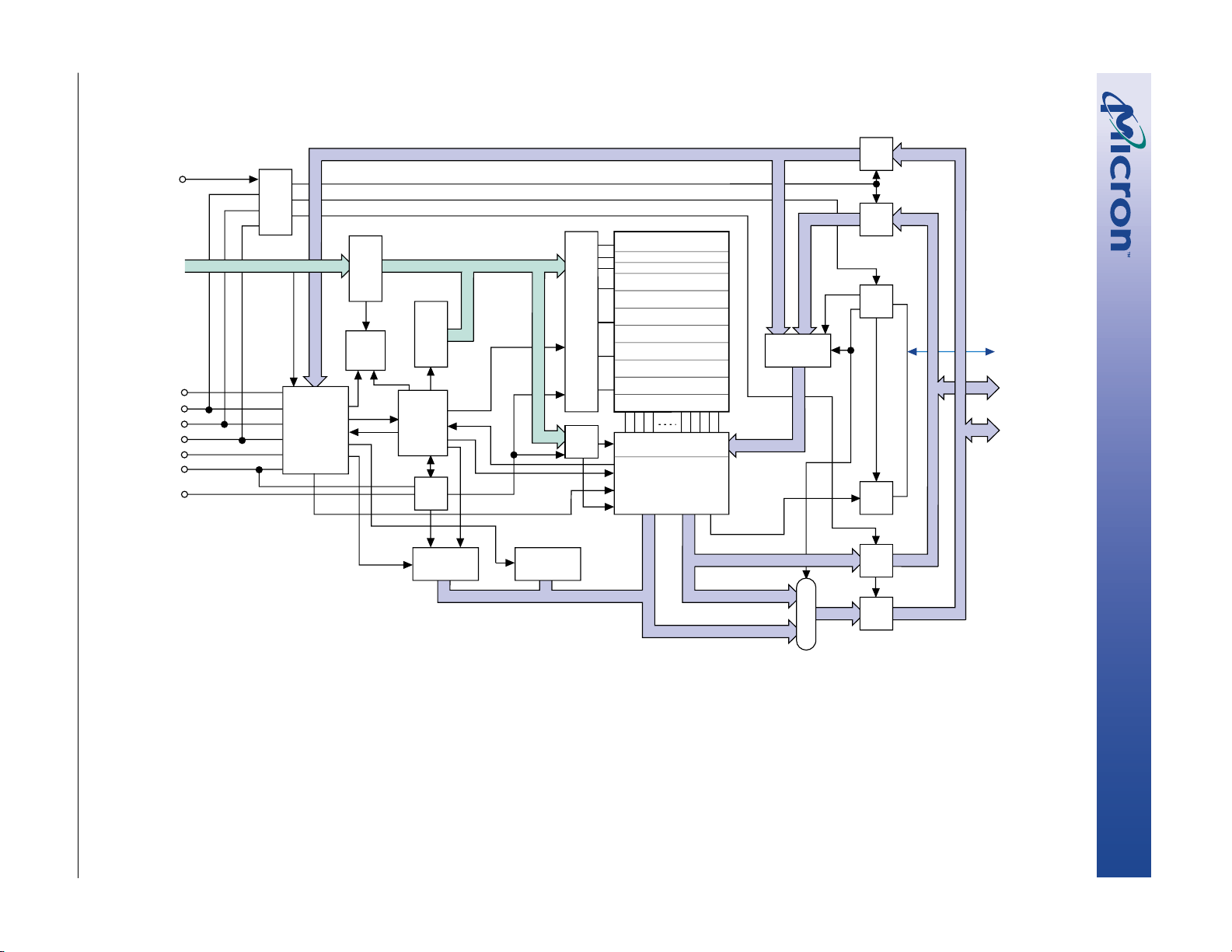

BYTE#

I/O

Control

Logic

A0–A18/(A19)

A9

1

WP#

CE#

OE#

WE#

3

RP#

V

V

CC

PP

Command

Execution

Logic

Addr.

Buffer/

Latch

Power

(Current)

Control

FUNCTIONAL BLOCK DIAGRAM

16KB Boot Block

19 (20)

Addr.

Counter

State

Machine

V

Switch/

Pump

PP

Status

Register

10

9

(10)

Identification

Register

X - Decoder/Block Erase Control

Y -

Decoder

8KB Parameter Block

8KB Parameter Block

96KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

Y - Select Gates

Sense Amplifiers

Write/Erase-Bit

Compare and Verify

DQ15

7

Input Data

Latch/Mux

16

Input

8

Buffer

Input

7

Buffer

Input

Buffer

A-1

2

2

SMART 3 BOOT BLOCK FLASH MEMORY

Output

Buffer

Output

Buffer

DQ15/(A - 1)

DQ8–DQ14

7

DQ0–DQ7

8

NOTE: 1. Does not apply to MT28F800B3SG.

2. Does not apply to MT28F008B3.

8

8

MUX

Output

Buffer

8Mb

8Mb

SMART 3 BOOT BLOCK FLASH MEMORY

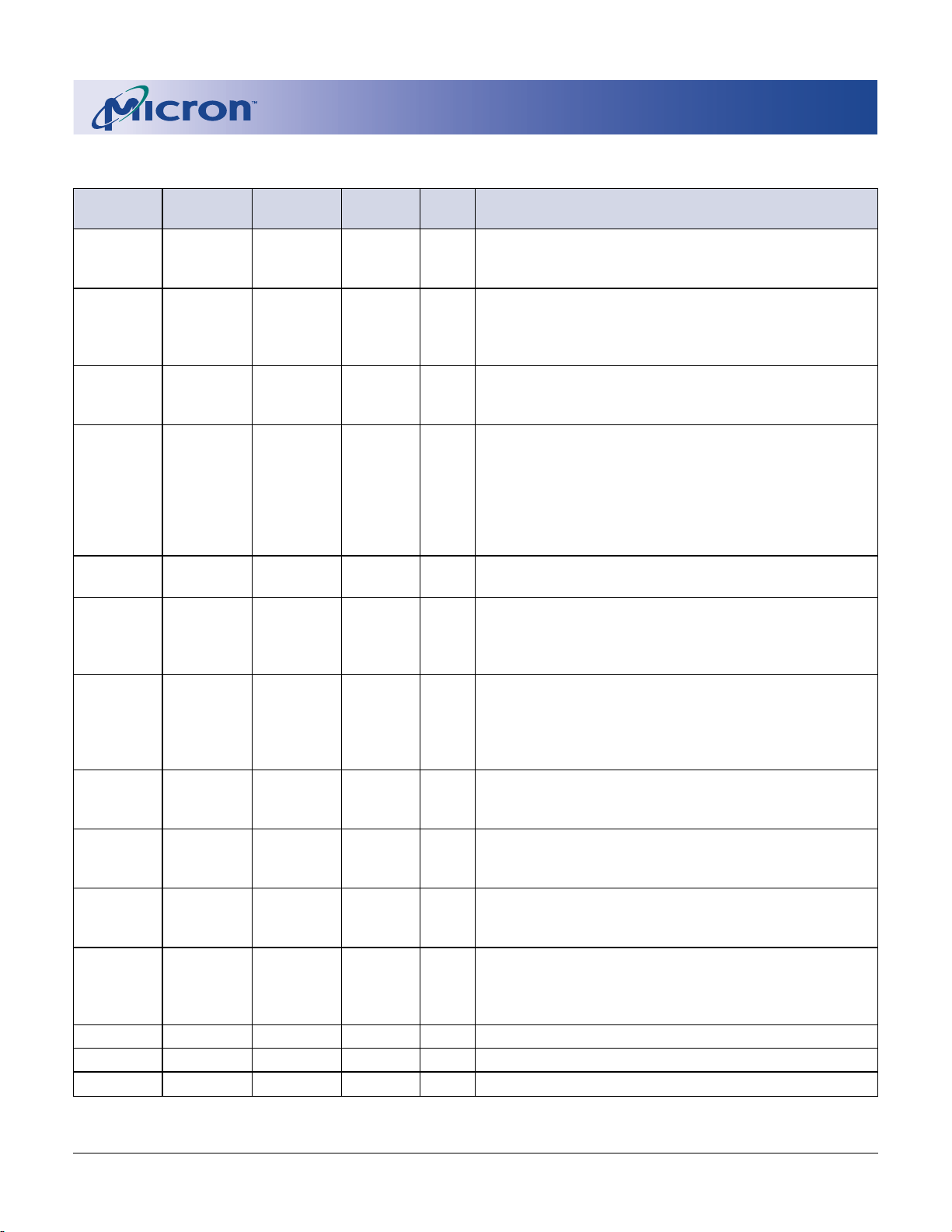

PIN DESCRIPTIONS

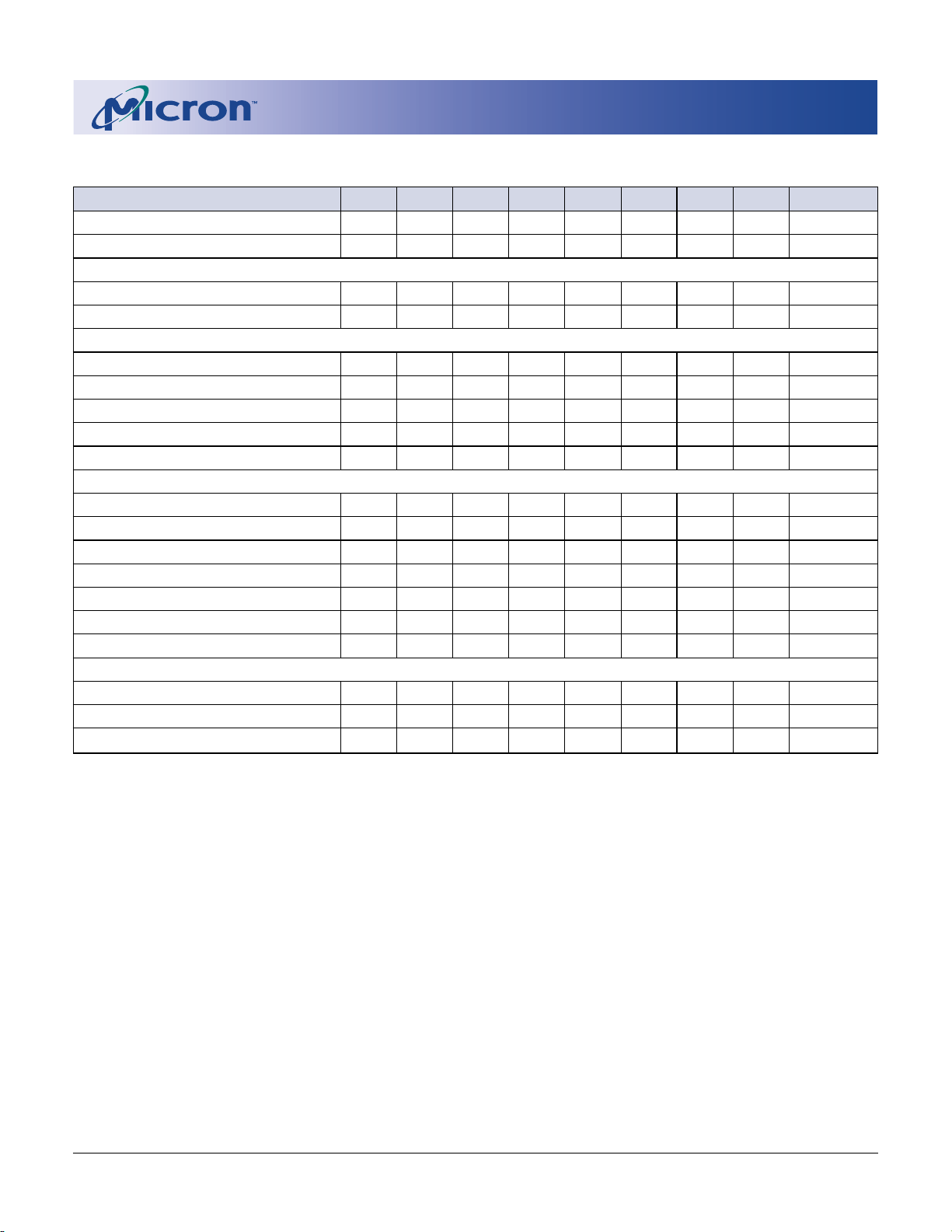

44-PIN SOP 40-PIN TSOP 48-PIN TSOP

NUMBERS NUMBERS NUMBERS SYMBOL TYPE DESCRIPTION

43 9 11 WE# Input Write Enable: Determines if a given cycle is a WRITE cycle. If

WE# is LOW, the cycle is either a WRITE to the command

execution logic (CEL) or to the memory array.

– 12 14 WP# Input Write Protect: Unlocks the boot block when HIGH if VPP =

V

PPH

1 (3.3V) or V

ERASE. Does not affect WRITE or ERASE operation on other

blocks.

12 22 26 CE# Input Chip Enable: Activates the device when LOW. When CE# is

HIGH, the device is disabled and goes into standby power

mode.

44 10 12 RP# Input Reset/Power-Down: When LOW, RP# clears the status register,

sets the internal state machine (ISM) to the array read mode

and places the device in deep power-down mode. All inputs,

including CE#, are “Don’t Care,” and all outputs are High-Z.

RP# unlocks the boot block and overrides the condition of

WP# when at VHH (12V), and must be held at VIH during all

other modes of operation.

14 24 28 OE# Input Output Enable: Enables data output buffers when LOW.

When OE# is HIGH, the output buffers are disabled.

33 – 47 BYTE# Input Byte Enable: If BYTE# = HIGH, the upper byte is active through

DQ8–DQ15. If BYTE# = LOW, DQ8–DQ14 are High-Z, and all

data is accessed through DQ0–DQ7. DQ15/(A - 1) becomes the

least significant address input.

11, 10, 9, 8,

7, 6, 5, 4, 42,

41, 40, 39,

38, 37, 36,

35, 34, 3, 2

21, 20, 19, 18, 25, 24, 23, A0–A18/ Input Address Inputs: Select a unique 16-bit word or 8-bit byte. The

17, 16, 15, 14, 22, 21, 20, (A19) DQ15/(A - 1) input becomes the lowest order address when

8, 7, 36, 6, 5, 19, 18, 8, 7, BYTE# = LOW (MT28F800B3) to allow for a selection of an 8-

4, 3, 2, 1, 40, 6, 5, 4, 3, 2, bit byte from the 1,048,576 available.

13, 37 1, 48, 17, 16

31 – 45 DQ15/ Input/ Data I/O: MSB of data when BYTE# = HIGH. Address Input: LSB

(A - 1) Output of address input when BYTE# = LOW during READ or WRITE

operation.

15, 17, 19,

21, 24, 26,

28, 30

16, 18, 20,

22, 25, 27,

25, 26, 27, 29, 31, 33, DQ0– Input/ Data I/Os: Data output pins during any READ operation or

28, 32, 33, 35, 38, 40, DQ7 Output data input pins during a WRITE. These pins are used to input

34, 35 42, 44 commands to the CEL.

– 30, 32, 34, DQ8– Input/ Data I/Os: Data output pins during any READ operation or

36, 39, 41, DQ14 Output data input pins during a WRITE when BYTE# = HIGH. These

29 43 pins are High-Z when BYTE# is LOW.

11113V

PP

Supply Write/Erase Supply Voltage: From a WRITE or ERASE CONFIRM

until completion of the WRITE or ERASE, VPP must be at V

(3.3V) or V

operations.

23 30, 31 37 V

13, 32 23, 39 27, 46 V

CC

SS

Supply Power Supply: +3.3V ±0.3V.

Supply Ground.

– 29, 38 9, 10, 15 NC – No Connect: These pins may be driven or left unconnected.

PPH

2 (5V). V

PPH

2 (5V) and RP# = V

PP

= “Don’t Care” during all other

IH

during a WRITE or

PPH

1

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

4

8Mb

SMART 3 BOOT BLOCK FLASH MEMORY

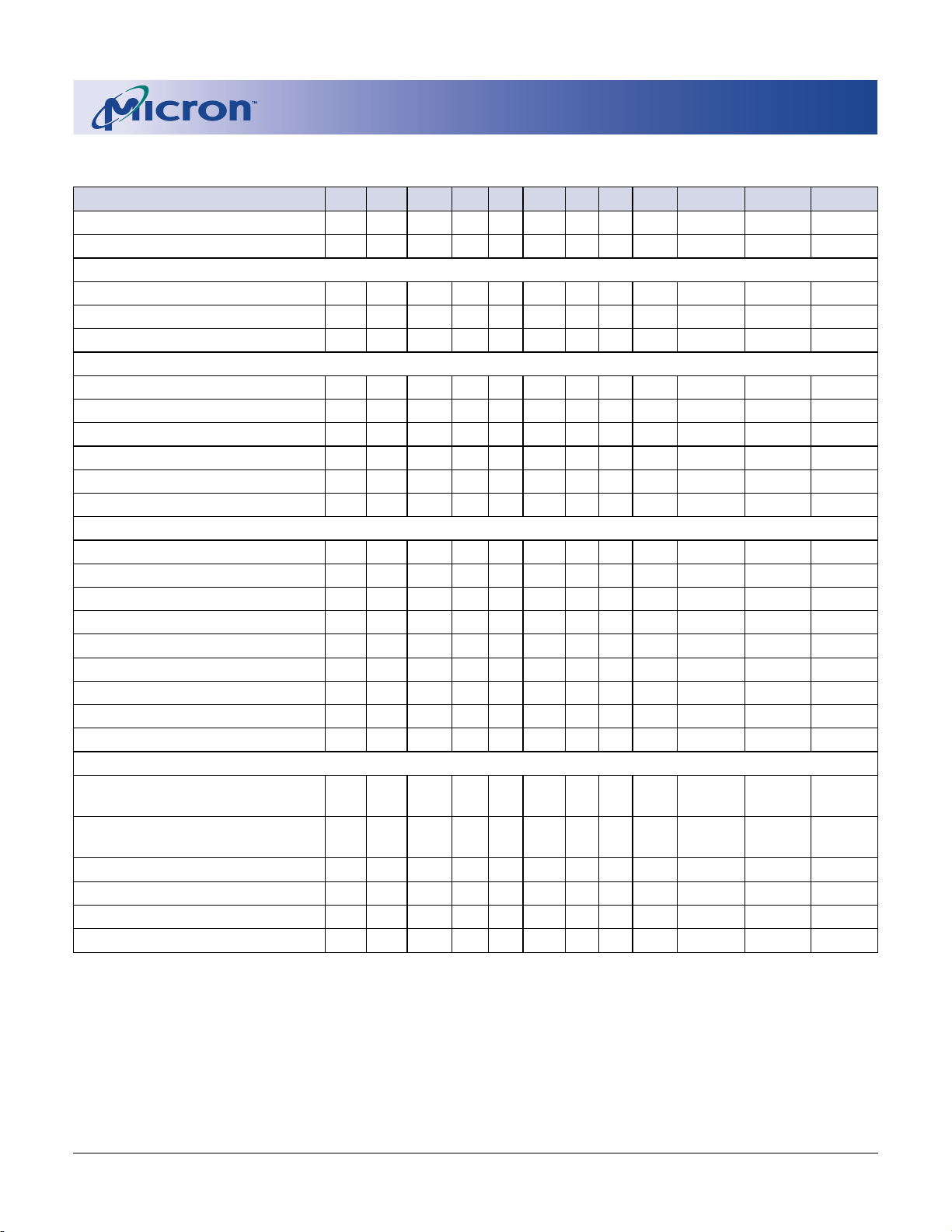

TRUTH TABLE (MT28F800B3)

1

FUNCTION RP# CE# OE# WE# WP# BYTE# A0 A9 VPP DQ0–DQ7 DQ8–DQ14 DQ15/A - 1

Standby H H X X X X X X X High-Z High-Z High-Z

RESET L X X X X X X X X High-Z High-Z High-Z

READ

READ (word mode) H L L H X H X X X Data-Out Data-Out Data-Out

READ (byte mode) H L L H X L X X X Data-Out High-Z A-1

Output Disable H L H H X X X X X High-Z High-Z High-Z

WRITE/ERASE (EXCEPT BOOT BLOCK)

2

ERASE SETUP H L H L X X X X X 20h X X

ERASE CONFIRM

3

HLHLXXXXV

PPH

D0h X X

WRITE SETUP H L H L X X X X X 10h/40h X X

WRITE (word mode)

WRITE (byte mode)

READ ARRAY

WRITE/ERASE (BOOT BLOCK)

4

4

5

HLHLXHXXV

HLHLXLXXV

PPH

Data-In Data-In Data-In

PPH

Data-In X A-1

HLHLXXXXX FFh X X

2, 7

ERASE SETUP H L H L X X X X X 20h X X

ERASE CONFIRM

ERASE CONFIRM

3

3, 6

V

HH

LHLXXXXV

HLHLHXXXV

PPH

PPH

D0h X X

D0h X X

WRITE SETUP H L H L X X X X X 10h/40h X X

WRITE (word mode)

WRITE (word mode)

WRITE (byte mode)

WRITE (byte mode)

READ ARRAY

DEVICE IDENTIFICATION

Manufacturer Compatibility H L L H X H L V

(word mode)

10

Manufacturer Compatibility H L L H X L L V

4

4, 6

4

4, 6

5

8, 9

V

HH

LHLXHXXV

HLHLHHXXV

V

HH

LHLXLXXV

HLHLHLXXV

PPH

Data-In Data-In Data-In

PPH

Data-In Data-In Data-In

PPH

Data-In X A-1

PPH

Data-In X A-1

HLHLXXXXX FFh X X

ID

X 89h 00h –

ID

X 89h High-Z X

(byte mode)

Device (word mode, top boot)

Device (byte mode, top boot) H L L H X L H V

Device (word mode, bottom boot)

Device (byte mode, bottom boot) H L L H X L H V

10

HL LHXHHVIDX 9Ch 88h –

ID

X 9Ch High-Z X

10

HL LHXHHVIDX 9Dh 88h –

ID

X 9Dh High-Z X

NOTE: 1. L = VIL (LOW), H = VIH (HIGH), X = VIL or VIH (“Don’t Care”).

2. VPPH = VPPH1 = 3.3V or VPPH2 = 5V.

3. Operation must be preceded by ERASE SETUP command.

4. Operation must be preceded by WRITE SETUP command.

5. The READ ARRAY command must be issued before reading the array after writing or erasing.

6. When WP# = VIH, RP# may be at VIH or VHH.

7. VHH = 12V.

8. VID = 12V; may also be read by issuing the IDENTIFY DEVICE command.

9. A1–A8, A10–A18 = VIL.

10. Value reflects DQ8–DQ15.

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

5

8Mb

SMART 3 BOOT BLOCK FLASH MEMORY

TRUTH TABLE (MT28F008B3)

1

FUNCTION RP# CE# OE# WE# WP# A0 A9 VPP DQ0–DQ7

Standby H H XXXXXXHigh-Z

RESET L X XXXXXXHigh-Z

READ

READ H L L H X X X X Data-Out

Output Disable H L H H X X X X High-Z

WRITE/ERASE (EXCEPT BOOT BLOCK)

2

ERASE SETUP H L H L X X X X 20h

ERASE CONFIRM

3

HLHLXXXVPPH D0h

WRITE SETUP H L H L X X X X 10h/40h

4

WRITE

READ ARRAY

5

WRITE/ERASE (BOOT BLOCK)

HLHLXXXVPPH Data-In

HLHLXXXX FFh

2, 7

ERASE SETUP H L H L X X X X 20h

ERASE CONFIRM

ERASE CONFIRM

3

3, 6

VHH LHLXXXVPPH D0h

HLHLHXXVPPH D0h

WRITE SETUP H L H L X X X X 10h/40h

4

WRITE

4, 6

WRITE

READ ARRAY

5

DEVICE IDENTIFICATION

8, 9

VHH LHLXXXVPPH Data-In

HLHLHXXVPPH Data-In

HLHLXXXX FFh

Manufacturer Compatibility H L L H X L VID X 89h

Device (top boot) H L L H X H VID X 98h

Device (bottom boot) H L L H X H VID X 99h

NOTE: 1. L = VIL, H = VIH, X = VIL or VIH.

2. VPPH = VPPH1 = 3.3V or VPPH2 = 5V.

3. Operation must be preceded by ERASE SETUP command.

4. Operation must be preceded by WRITE SETUP command.

5. The READ ARRAY command must be issued before reading the array after writing or erasing.

6. When WP# = VIH, RP# may be at VIH or VHH.

7. VHH = 12V.

8. VID = 12V; may also be read by issuing the IDENTIFY DEVICE command.

9. A1–A8, A10–A19 = VIL.

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

6

SMART 3 BOOT BLOCK FLASH MEMORY

FUNCTIONAL DESCRIPTION

The MT28F800B3 and MT28F008B3 Flash devices incorporate a number of features ideally suited for system

firmware. The memory array is segmented into individual erase blocks. Each block may be erased without

affecting data stored in other blocks. These memory

blocks are read, written and erased with commands to

the command execution logic (CEL). The CEL controls

the operation of the internal state machine (ISM), which

completely controls all WRITE, BLOCK ERASE and VERIFY

operations. The ISM protects each memory location from

over-erasure and optimizes each memory location for

maximum data retention. In addition, the ISM greatly

simplifies the control necessary for writing the device insystem or in an external programmer.

The Functional Description provides detailed information on the operation of the MT28F800B3 and

MT28F008B3 and is organized into these sections:

• Overview

• Memory Architecture

• Output (READ) Operations

• Input Operations

• Command Set

• ISM Status Register

• Command Execution

• Error Handling

• WRITE/ERASE Cycle Endurance

• Power Usage

• Power-Up

OVERVIEW

SMART 3 TECHNOLOGY (B3)

Smart 3 operation allows maximum flexibility for insystem READ, WRITE and ERASE operations. WRITE and

ERASE operations may be executed with a VPP voltage of

3.3V or 5V. Due to process technology advances, 5V VPP is

optimal for application and production programming.

8Mb

HARDWARE-PROTECTED BOOT BLOCK

This block of the memory array can be erased or

written only when the RP# pin is taken to VHH or when the

WP# pin is brought HIGH. (The WP# pin does not apply to

the SOP package.) This provides additional security for

the core firmware during in-system firmware updates

should an unintentional power fluctuation or system

reset occur. The MT28F800B3 and MT28F008B3 are available with the boot block starting at the bottom of the

address space (“B” suffix) and the top of the address

space (“T” suffix).

SELECTABLE BUS SIZE (MT28F800B3)

The MT28F800B3 allows selection of an 8-bit

(1 Meg x 8) or 16-bit (512K x 16) data bus for reading and

writing the memory. The BYTE# pin is used to select the

bus width. In the x16 configuration, control data is read

or written only on the lower eight bits (DQ0–DQ7).

Data written to the memory array utilizes all active

data pins for the selected configuration. When the x8

configuration is selected, data is written in byte form;

when the x16 configuration is selected, data is written in

word form.

INTERNAL STATE MACHINE (ISM)

BLOCK ERASE and BYTE/WORD WRITE timing are

simplified with an ISM that controls all erase and write

algorithms in the memory array. The ISM ensures protection against overerasure and optimizes write margin to

each cell.

During WRITE operations, the ISM automatically increments and monitors WRITE attempts, verifies write

margin on each memory cell and updates the ISM status

register. When BLOCK ERASE is performed, the ISM automatically overwrites the entire addressed block (eliminates overerasure), increments and monitors ERASE attempts, and sets bits in the ISM status register.

ELEVEN INDEPENDENTLY ERASABLE MEMORY BLOCKS

The MT28F800B3 and MT28F008B3 are organized into

eleven independently erasable memory blocks that allow portions of the memory to be erased without affecting the rest of the memory data. A special boot block is

hardware-protected against inadvertent erasure or writing by requiring either a super-voltage on the RP# pin or

driving the WP# pin HIGH. (The WP# pin does not apply

to the SOP package.) One of these two conditions must

exist along with the VPP voltage (3.3V or 5V) on the VPP pin

before a WRITE or ERASE is performed on the boot

block. The remaining blocks require that only the VPP

voltage be present on the VPP pin before writing or

erasing.

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

ISM STATUS REGISTER

The ISM status register enables an external processor

to monitor the status of the ISM during WRITE and ERASE

operations. Two bits of the 8-bit status register are set and

cleared entirely by the ISM. These bits indicate whether

the ISM is busy with an ERASE or WRITE task and when an

ERASE has been suspended. Additional error information is set in three other bits: VPP status, write status and

erase status.

COMMAND EXECUTION LOGIC (CEL)

The CEL receives and interprets commands to the

device. These commands control the operation of the

ISM and the read path (i.e., memory array, ID register or

status register). Commands may be issued to the CEL

7

8Mb

SMART 3 BOOT BLOCK FLASH MEMORY

while the ISM is active. However, there are restrictions

on what commands are allowed in this condition. See

the Command Execution section for more detail.

DEEP POWER-DOWN MODE

To allow for maximum power conservation, the

MT28F800B3 and MT28F008B3 feature a very low current, deep power-down mode. To enter this mode, the

RP# pin is taken to VSS ±0.2V. In this mode, the current

draw is a maximum of 8µA at 3.3V VCC. Entering deep

power-down also clears the status register and sets the

ISM to the read array mode.

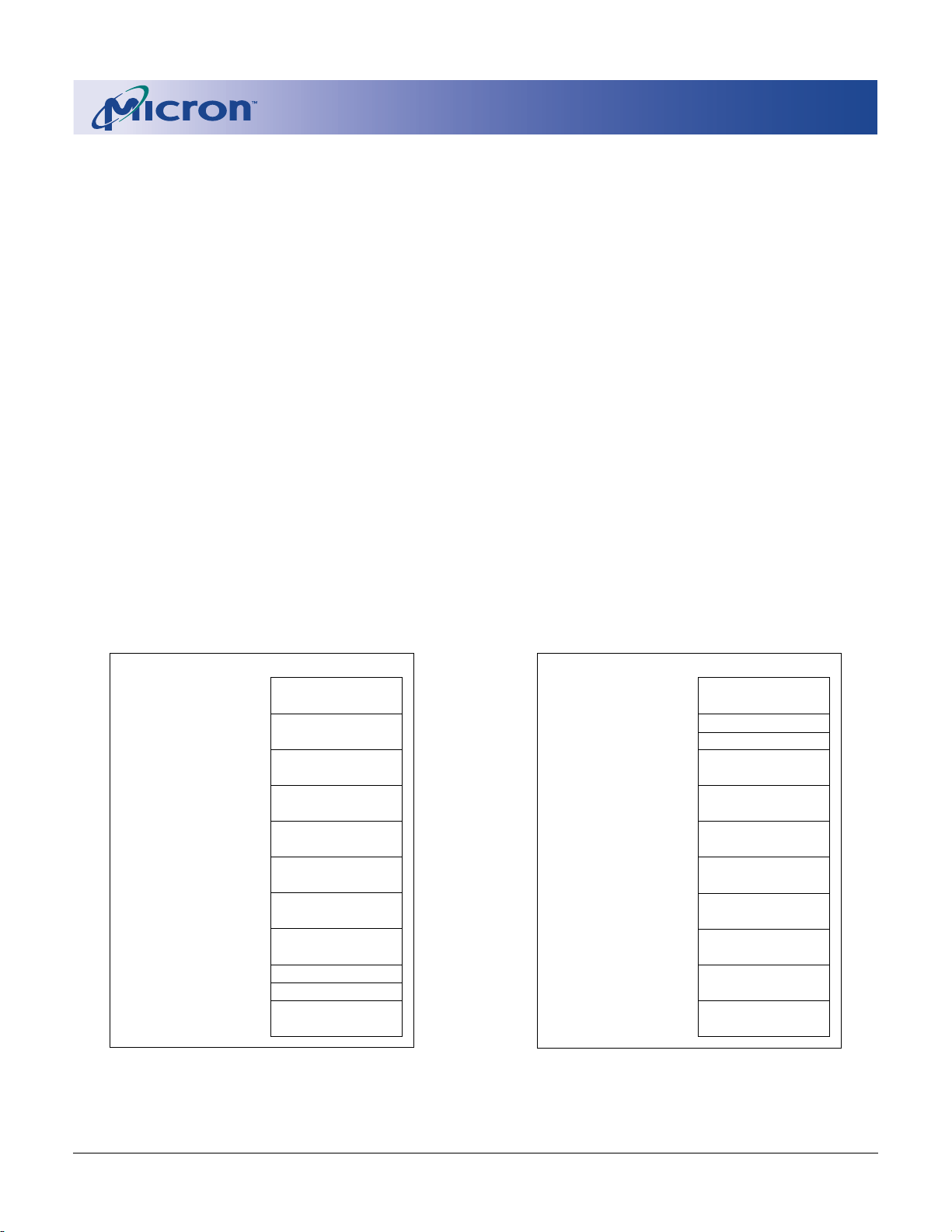

MEMORY ARCHITECTURE

The MT28F800B3 and MT28F008B3 memory array

architecture is designed to allow sections to be erased

without disturbing the rest of the array. The array is

divided into eleven addressable blocks that vary in size

and are independently erasable. When blocks rather than

the entire array are erased, total device endurance is

enhanced, as is system flexibility. Only the ERASE func-

Figure 1

Memory Address Maps

tion is block-oriented. All READ and WRITE operations

are done on a random-access basis.

The boot block is protected from unintentional ERASE

or WRITE with a hardware protection circuit which requires that a super-voltage be applied to RP# or that the

WP# pin be driven HIGH before erasure is commenced.

The boot block is intended for the core firmware required

for basic system functionality. The remaining ten blocks

do not require that either of these two conditions be met

before WRITE or ERASE operations.

BOOT BLOCK

The hardware-protected boot block provides extra

security for the most sensitive portions of the firmware.

This 16KB block may only be erased or written when the

RP# pin is at the specified boot block unlock voltage (VHH)

of 12V or when the WP# pin is HIGH. During a WRITE or

ERASE of the boot block, the RP# pin must be held at VHH

or the WP# pin held HIGH until the WRITE or ERASE is

completed. (The WP# pin does not apply to the SOP

package.) The VPP pin must be at VPPH (3.3V or 5V) when

the boot block is written to or erased.

WORD ADDRESS

7FFFFh

70000h

6FFFFh

60000h

5FFFFh

50000h

4FFFFh

40000h

3FFFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

04000h

03FFFh

03000h

02FFFh

02000h

01FFFh

00000h

BYTE ADDRESS

FFFFFh

E0000h

DFFFFh

C0000h

BFFFFh

A0000h

9FFFFh

80000h

7FFFFh

60000h

5FFFFh

40000h

3FFFFh

20000h

1FFFFh

08000h

07FFFh

06000h

05FFFh

04000h

03FFFh

00000h

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

96KB Main Block

8KB Parameter Block

8KB Parameter Block

16KB Boot Block

Bottom Boot

MT28F008B3/800B3xx-xxB

WORD ADDRESS

7FFFFh

7E000h

7DFFFh

7D000h

7CFFFh

7C000h

7BFFFh

70000h

6FFFFh

60000h

5FFFFh

50000h

4FFFFh

40000h

3FFFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

00000h

BYTE ADDRESS

FFFFFh

FC000h

FBFFFh

FA000h

F9FFFh

F8000h

F7FFFh

E0000h

DFFFFh

C0000h

BFFFFh

A0000h

9FFFFh

80000h

7FFFFh

60000h

5FFFFh

40000h

3FFFFh

20000h

1FFFFh

00000h

16KB Boot Block

8KB Parameter Block

8KB Parameter Block

96KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

128KB Main Block

Top Boot

MT28F008B3/800B3xx-xxT

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

8

8Mb

SMART 3 BOOT BLOCK FLASH MEMORY

The MT28F800B3 and MT28F008B3 are available in

two configurations and top or bottom boot block. The top

boot block version supports processors of the x86 variety.

The bottom boot block version is intended for 680X0 and

RISC applications. Figure 1 illustrates the memory address maps associated with these two versions.

PARAMETER BLOCKS

The two 8KB parameter blocks store less sensitive and

more frequently changing system parameters and also

may store configuration or diagnostic coding. These

blocks are enabled for erasure when the VPP pin is at VPPH.

No super-voltage unlock or WP# control is required.

MAIN MEMORY BLOCKS

The eight remaining blocks are general-purpose

memory blocks and do not require a super-voltage on

RP# or WP# control to be erased or written. These blocks

are intended for code storage, ROM-resident applications or operating systems that require in-system update

capability.

OUTPUT (READ) OPERATIONS

The MT28F800B3 and MT28F008B3 feature three different types of READs. Depending on the current mode of

the device, a READ operation produces data from the

memory array, status register or device identification

register. In each of these three cases, the WE#, CE# and

OE# inputs are controlled in a similar manner. Moving

between modes to perform a specific READ is described

in the Command Execution section.

MEMORY ARRAY

To read the memory array, WE# must be HIGH, and

OE# and CE# must be LOW. Valid data is output on the

DQ pins when these conditions have been met, and a

valid address is given. Valid data remains on the DQ pins

until the address changes, or until OE# or CE# goes HIGH,

whichever occurs first. The DQ pins continue to output

new data after each address transition as long as OE# and

CE# remain LOW.

The MT28F800B3 features selectable bus widths.

When the memory array is accessed as a 512K x 16, BYTE#

is HIGH, and data is output on DQ0–DQ15. To access the

memory array as a 1 Meg x 8, BYTE# must be LOW, DQ8–

DQ14 must be High-Z, and all data must be output on

DQ0–DQ7. The DQ15/(A - 1) pin becomes the lowest

order address input so that 1,048,576 locations can be

read.

After power-up or RESET, the device is automatically

in the array read mode. All commands and their operations are covered in the Command Set and Command

Execution sections.

STATUS REGISTER

Performing a READ of the status register requires

the same input sequencing as a READ of the array

except that the address inputs are “Don’t Care.” The

status register contents are always output on DQ0–

DQ7, regardless of the condition of BYTE# on the

MT28F800B3. DQ8–DQ15 are LOW when BYTE# is

HIGH, and DQ8–DQ14 are High-Z when BYTE# is LOW.

Data from the status register is latched on the falling

edge of OE# or CE#, whichever occurs last. If the contents of the status register change during a READ of the

status register, either OE# or CE# may be toggled while

the other is held LOW to update the output.

Following a WRITE or ERASE, the device automatically enters the status register read mode. In addition, a

READ during a WRITE or ERASE produces the status

register contents on DQ0–DQ7. When the device is in the

erase suspend mode, a READ operation produces the

status register contents until another command is issued. In certain other modes, READ STATUS REGISTER

may be given to return to the status register read mode.

All commands and their operations are described in the

Command Set and Command Execution sections.

IDENTIFICATION REGISTER

A READ of the two 8-bit device identification registers

requires the same input sequencing as a READ of the

array. WE# must be HIGH, and OE# and CE# must be

LOW. However, ID register data is output only on DQ0–

DQ7, regardless of the condition of BYTE# on the

MT28F800B3. A0 is used to decode between the two bytes

of the device ID register; all other address inputs are

“Don’t Care.” When A0 is LOW, the manufacturer compatibility ID is output, and when A0 is HIGH, the device

ID is output. DQ8–DQ15 are High-Z when BYTE# is LOW.

When BYTE# is HIGH, DQ8–DQ15 are 00h when the

manufacturer compatibility ID is read and 88h when the

device ID is read.

To get to the identification register read mode, READ

IDENTIFICATION may be issued while the device is in

certain other modes. In addition, the identification register read mode can be reached by applying a super-voltage (VID) to the A9 pin. Using this method, the ID register

can be read while the device is in any mode. When A9 is

returned to VIL or VIH, the device returns to the previous

mode.

INPUT OPERATIONS

The DQ pins are used either to input data to the array

or to input a command to the CEL. A command input

issues an 8-bit command to the CEL to control the mode

of operation of the device. A WRITE is used to input

data to the memory array. The following section de-

8Mb Smart 3 Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

Q10_3.p65 – Rev. 3, Pub. 10/01 ©2001, Micron Technology, Inc.

9

Loading...

Loading...