MICRON MT28F160A3FD-11T, MT28F160A3FD-11TET, MT28F160A3FD-9T, MT28F160A3FD-9TET Datasheet

1

1 Meg x 16 Enhanced Boot Block Flash Memory ©2001, Micron Technology, Inc.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

‡

‡

PRODUCTS AND SPECIFICATIONS DISCUSSED HEREIN ARE FOR EVALUATION AND REFERENCE PURPOSES ONLY AND

ARE SUBJECT TO CHANGE BY MICRON WITHOUT NOTICE. PRODUCTS ARE ONLY WARRANTED BY MICRON TO MEET

MICRON’S PRODUCTION DATA SHEET SPECIFICATIONS.

FLASH MEMORY MT28F160A3

Low Voltage, Extended Temperature

GENERAL DESCRIPTION

The MT28F160A3 is a nonvolatile, electrically blockerasable (flash), programmable, read-only memory containing 16,777,216 bits organized as 1,048,576 words

(16 bits).

The MT28F160A3 is manufactured on 0.22µm process

technology in a 48-ball FBGA package. The device has an

I/O supply of 2.7V (MIN). Programming in production is

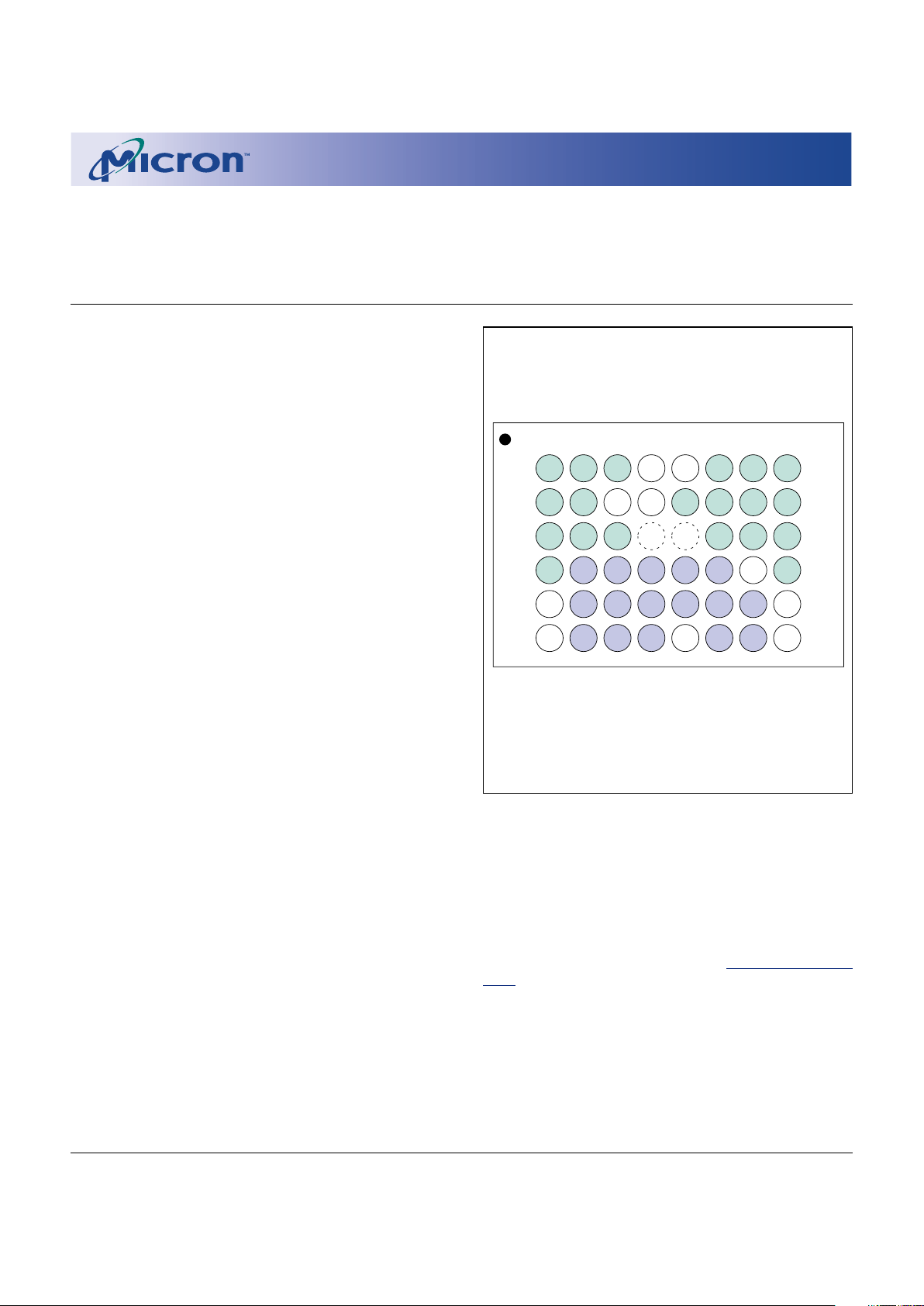

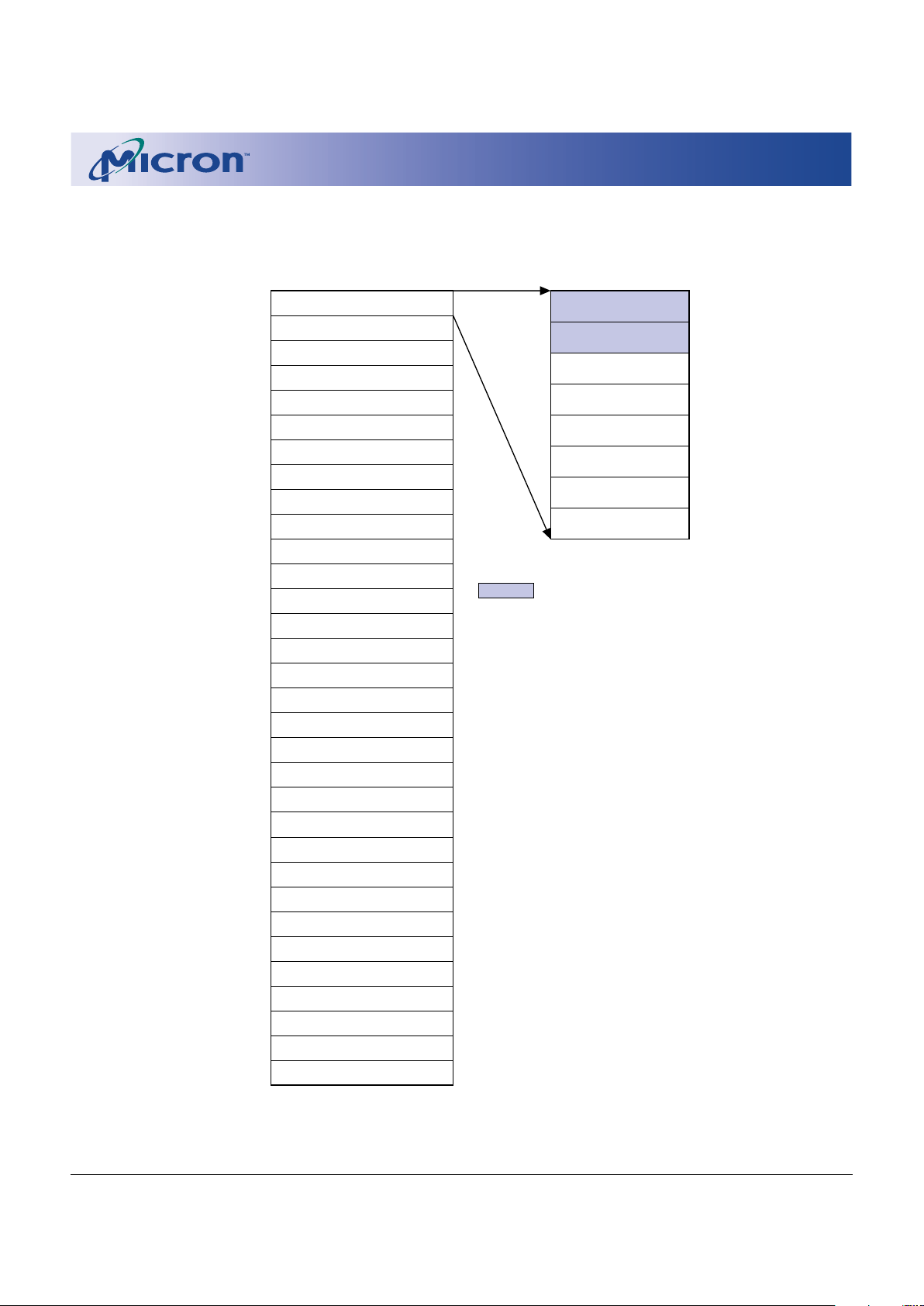

BALL ASSIGNMENT (Top View)

46-Ball FBGA

FEATURES

• Thirty-nine erase blocks:

Two 4K-word boot blocks (protected)

Six 4K-word parameter blocks

Thirty-one 32K-word main memory blocks

•VCC, VCCQ and VPP voltages:

2.7V–3.3V VCC and VPP

2.7V–3.3V VCCQ*

5V VPP fast programming voltage

• Address access times:

90ns, 110ns at 2.7V–3.3V

• Low power consumption:

Standby and deep power-down mode < 1µA

(typical ICC)

Automatic power saving feature (APS mode)

• Enhanced WRITE/ERASE SUSPEND (1µs typical)

• Industry-standard command set compatibility

• Hardware block protection

OPTIONS NUMBER

• Timing

90ns access -9

110ns access -11

• Boot Block Starting Address

Top (FFFFFH) T

Bottom (00000H) B

• Package

46-ball FBGA (6 x 8 ball grid) FD

• Temperature Range

Commercial (0°C to +70°C) None

Extended (-40°C to +85°C) ET

*Lower VCCQ ranges are available upon request.

Part Number Example:

MT28F160A3FD-11 TET

A

B

C

D

E

F

A13

A14

A15

A16

V

CC

Q

V

SS

A19

A17

A6

DQ8

DQ9

DQ10

WP#

A18

DQ2

DQ3

V

CC

V

PP

RP#

DQ11

DQ12

DQ4

A8

WE#

A9

DQ5

DQ6

DQ13

A4

A2

A1

A0

V

SS

OE#

A7

A5

A3

CE#

DQ0

DQ1

A11

A10

A12

DQ14

DQ15

DQ7

1 2 3 4 5 6 7 8

(Ball Down)

NOTE: See page 3 for Ball Description Table.

See last page for mechanical drawing.

accomplished by using high voltage which can be supplied on a separate line.

The embedded WORD WRITE and BLOCK ERASE

functions are fully automated by an on-chip write state

machine (WSM), which simplifies these operations and

relieves the system processor of secondary tasks. The

WSM status can be monitored by an on-chip status

register to determine the progress of program/erase tasks.

Please refer to Micron’s Web site (www.micron.com/

flash) for the latest data sheet.

DEVICE MARKING

Due to the size of the package, Micron’s standard part

number is not printed on the top of each device. Instead,

an abbreviated device mark comprised of a five-digit

alphanumeric code is used. The abbreviated device marks

are cross referenced to Micron part numbers in

Table 1.

2

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

Table 1

Cross Reference for Abbreviated

Device Marks

1

PRODUCT SAMPLE

PART NUMBER MARKING MARKING

MT28F160A3FD-9 BET FW310 FX310

MT28F160A3FD-9 TET FW311 FX311

MT28F160A3FD-11 BET FW312 FX312

MT28F160A3FD-11 TET FW313 FX313

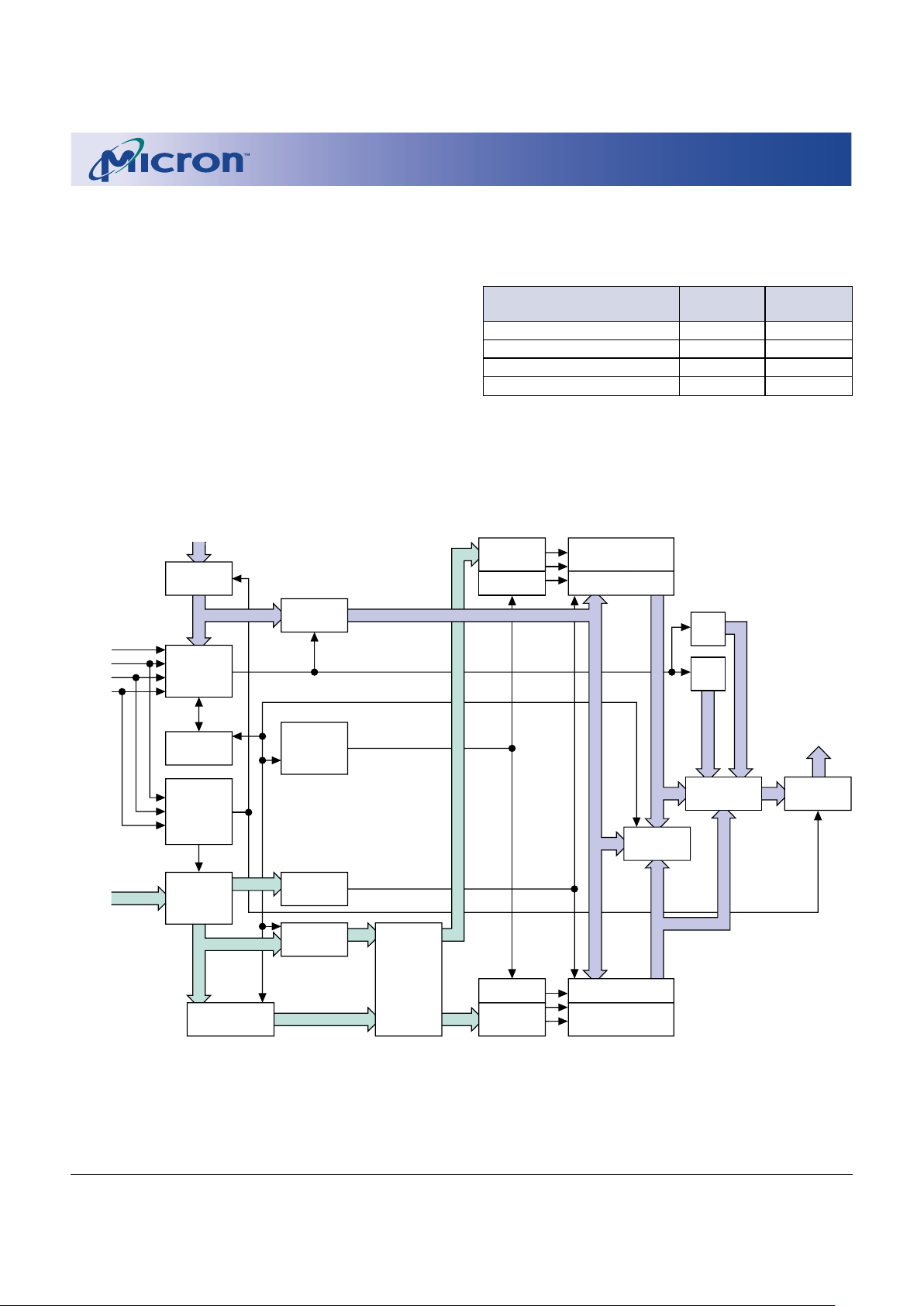

FUNCTIONAL BLOCK DIAGRAM

Address

Input

Buffer

X DEC

Y/Z DEC

Data Input

Buffer

APS

Control

Data

Comparator

Output

Multiplexer

Address

CNT WSM

Output

Buffer

Status

Reg.

ID

Reg.

WSM

Program/

Erase Change

Pump Voltage

Switch

Address Latch

DQ0–DQ15

DQ0–DQ15

CSM

RP#

CE#

X DEC

Y/Z DEC

WE#

OE#

I/O Logic

A0–A19

Address

Multiplexer

Bank b Blocks

Y/Z Gating/Sensing

Data

Register

Bank a Blocks

Y/Z Gating/Sensing

ARCHITECTURE

The MT28F160A3 flash contains eight 4K-word parameter blocks and thirty-one 32K-word blocks. The first

two 4K-word blocks are called boot blocks and are locked

with WP# control. Memory is organized by using a blocked

architecture to allow independent erasure of selected

memory blocks. Any address within a block address range

selects that block for the required READ, WRITE, or ERASE

operation (see Figures 1 and 2).

NOTE: 1. The mechanical sample marking is FY310.

3

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

BALL DESCRIPTIONS

46-BALL FBGA

NUMBERS SYMBOL TYPE DESCRIPTION

3B WE# Input Write Enable: Determines if a given cycle is a WRITE cycle. If WE# is

LOW, the cycle is either a WRITE to the command state machine (CSM)

or to the memory array.

5A WP# Input Write Protect: Unlocks the boot blocks when HIGH if VPP = 2.7V–3.3V

or 5V (WRITE only) and RP# = VIH for WRITE or ERASE. Does not affect

WRITE or ERASE operation on other blocks.

7D CE# Input Chip Enable: Activates the device when LOW. When CE# is HIGH, the

device is disabled and goes into standby power mode.

4B RP# Input Reset/Power-Down: When LOW, RP# clears the status register, sets the

write state machine (WSM) to the array read mode and places the

device in deep power-down mode. All inputs, including CE#, are

“Don’t Care,” and all outputs are High-Z. RP# must be held at VIH

during all other modes of operation.

8F OE# Input Output Enable: Enables data output buffers when LOW. When OE# is

HIGH, the output buffers are disabled.

1A, 1B, 1C, 1D, A0-A19 Input Address Inputs: These address inputs select a unique, 16-bit word out

2A, 2B, 2C, 3A, of the 1,048,576 available.

3C, 5B, 6A, 6B,

6C, 7A, 7B, 7C,

8A, 8B, 8C, 8D

2D, 2E, 2F, 3D, DQ0-DQ15 Input/ Data I/O: These data I/O are data output lines during any READ

3E, 3F, 4D, 4E, Output operation or data input lines during a WRITE. Data I/O are used to

4F, 5D, 5E, 6D, input commands to the CSM.

6E, 6F, 7E, 7F

4A VPP Supply Write/Erase Supply Voltage: From a WRITE or ERASE CONFIRM until

completion of the operation, VPP must be 2.7V–3.3V or 5V (WRITE

only). VPP = “Don’t Care” during all other operations.

5F VCC Supply Power Supply: 2.7V–3.3V.

1E VCCQ Supply I/O Supply Voltage: 2.7V–3.3V.

1F, 8E VSS Supply Ground.

4

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

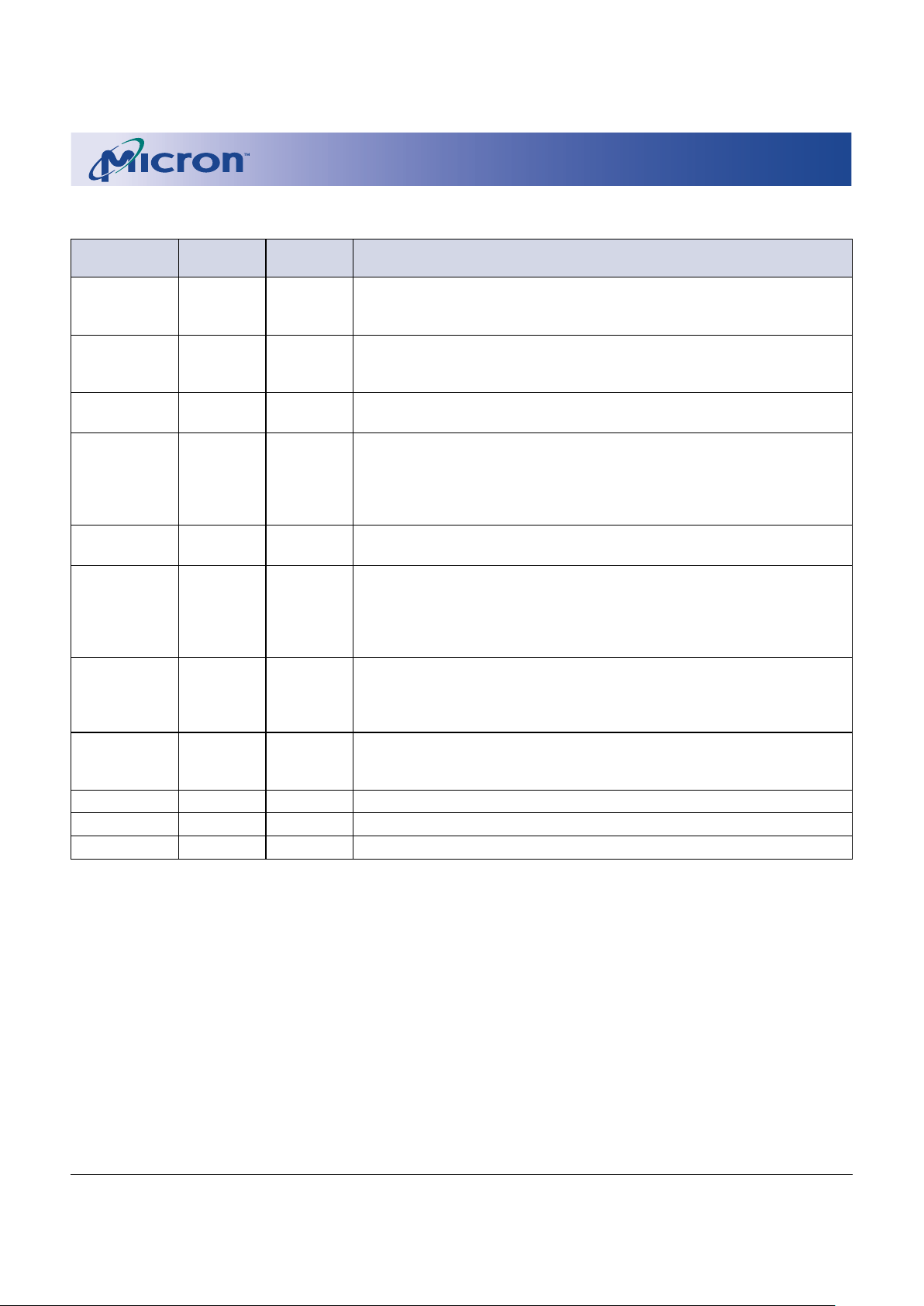

NOTE: 1. L = VIL (LOW), H = VIH (HIGH), X = VIL or VIH (“Don’t Care”).

2. VPPH = 2.7V–3.3V for ERASE, and VPPH = 2.7V–3.3V or 5V for WRITE.

3. Operation must be preceded by ERASE SETUP command.

4. Operation must be preceded by WRITE SETUP command.

5. The READ ARRAY command must be issued before reading the array after writing or erasing.

6. See Table 3 for the IDENTIFY DEVICE command.

TRUTH TABLE

1

FUNCTION RP# CE# OE# WE# WP# V

PP

A0 DQ0-DQ7 DQ8-DQ15

Standby H H XXXXXHigh-Z High-Z

RESET L XXXXXXHigh-Z High-Z

READING

READ H L L H X X X Data-Out Data-Out

Output Disable H L H H X X X High-Z High-Z

WRITE/ERASE (EXCEPT BOOT BLOCKS)

2

ERASE SETUP H L H L X X X 20H X

ERASE CONFIRM

3

HLHLXVPPH X D0H X

WRITE SETUP H L H L X X X 10H/40H X

WRITE

4

HLHLXVPPH X Data-In Data-In

READ ARRAY

5

HLHLXXX FFH X

WRITE/ERASE (BOOT BLOCKS)

2

ERASE SETUP H L H L X X X 20H X

ERASE CONFIRM

3

HLHLHVPPH X D0H X

WRITE SETUP H L H L X X X 10H/40H X

WRITE

4

HLHLHVPPH X Data-In Data-In

READ ARRAY

5

HLHLXXX FFH X

DEVICE IDENTIFICATION

6

Manufacturer H L L H X X L 2CH 00H

Device (top boot) H L L H X X H 90H 44H

Device (bottom boot) H L L H X X H 91H 44H

5

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

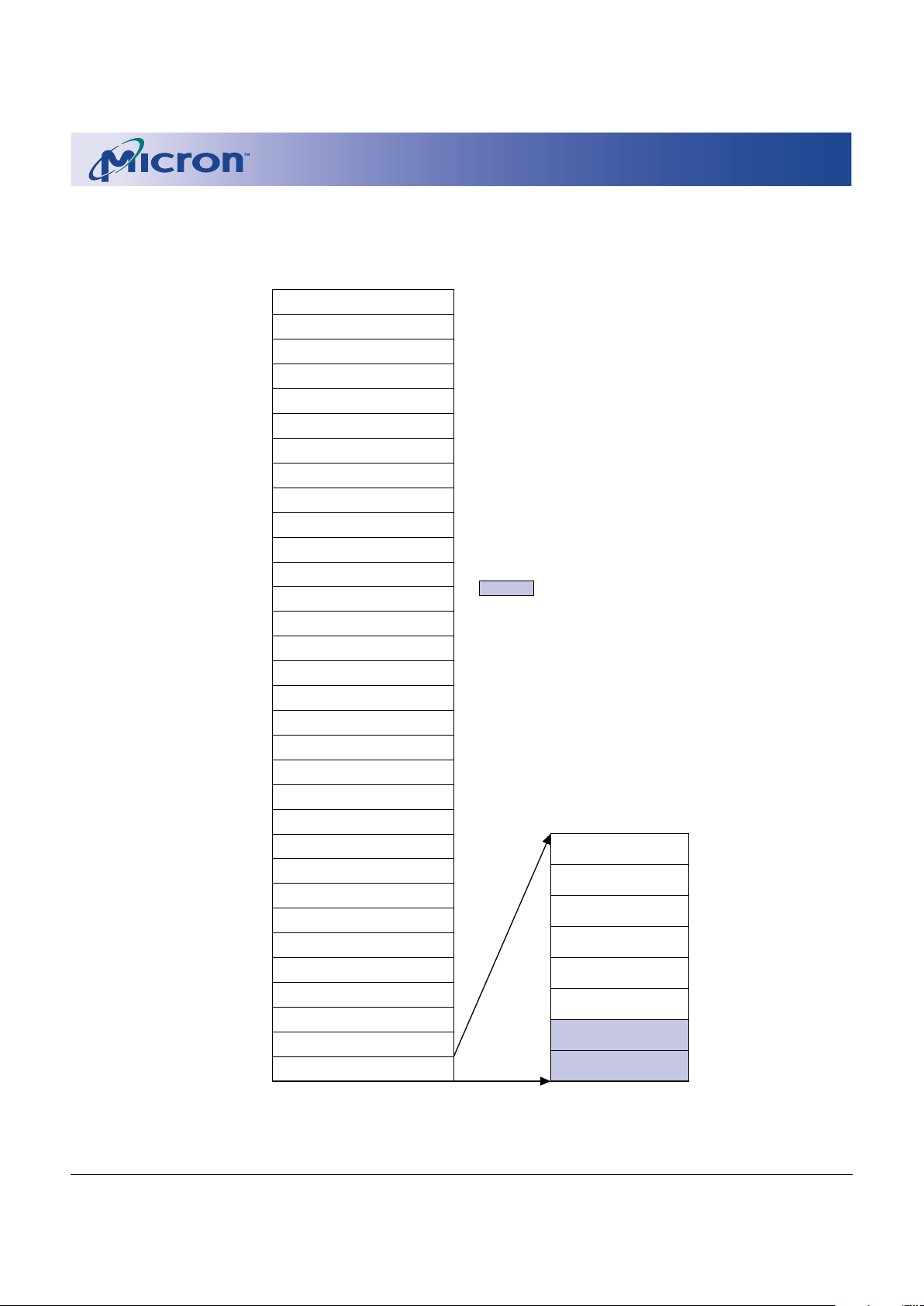

8 x 4K-Word Blocks

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

Boot Blocks

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

Parameter

Blocks

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

FFFFFh

F8000h

F7FFFh

F0000h

EFFFFh

E8000h

E7FFFh

E0000h

DFFFFh

D8000h

D7FFFh

D0000h

CFFFFh

C8000h

C7FFFh

C0000h

BFFFFh

B8000h

B7FFFh

B0000h

AFFFFh

A8000h

A7FFFh

A0000h

9FFFFh

98000h

97FFFh

90000h

8FFFFh

88000h

87FFFh

80000h

7FFFFh

78000h

77FFFh

70000h

6FFFFh

68000h

67FFFh

60000h

5FFFFh

58000h

57FFFh

50000h

4FFFFh

48000h

47FFFh

40000h

3FFFFh

38000h

37FFFh

30000h

2FFFFh

28000h

27FFFh

20000h

1FFFFh

18000h

17FFFh

10000h

0FFFFh

08000h

07FFFh

00000h

FFFFFh

FF000h

FEFFFh

FE000h

FDFFFh

FD000h

FCFFFh

FC000h

FBFFFh

FB000h

FAFFFh

FA000h

F9FFFh

F9000h

F8FFFh

F8000h

ADDRESS RANGE

Figure 1

Top Boot Block Memory Address Map

NOTE: 1. The two 4K-word blocks (boot blocks) can only be locked/unlocked by WP#.

6

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

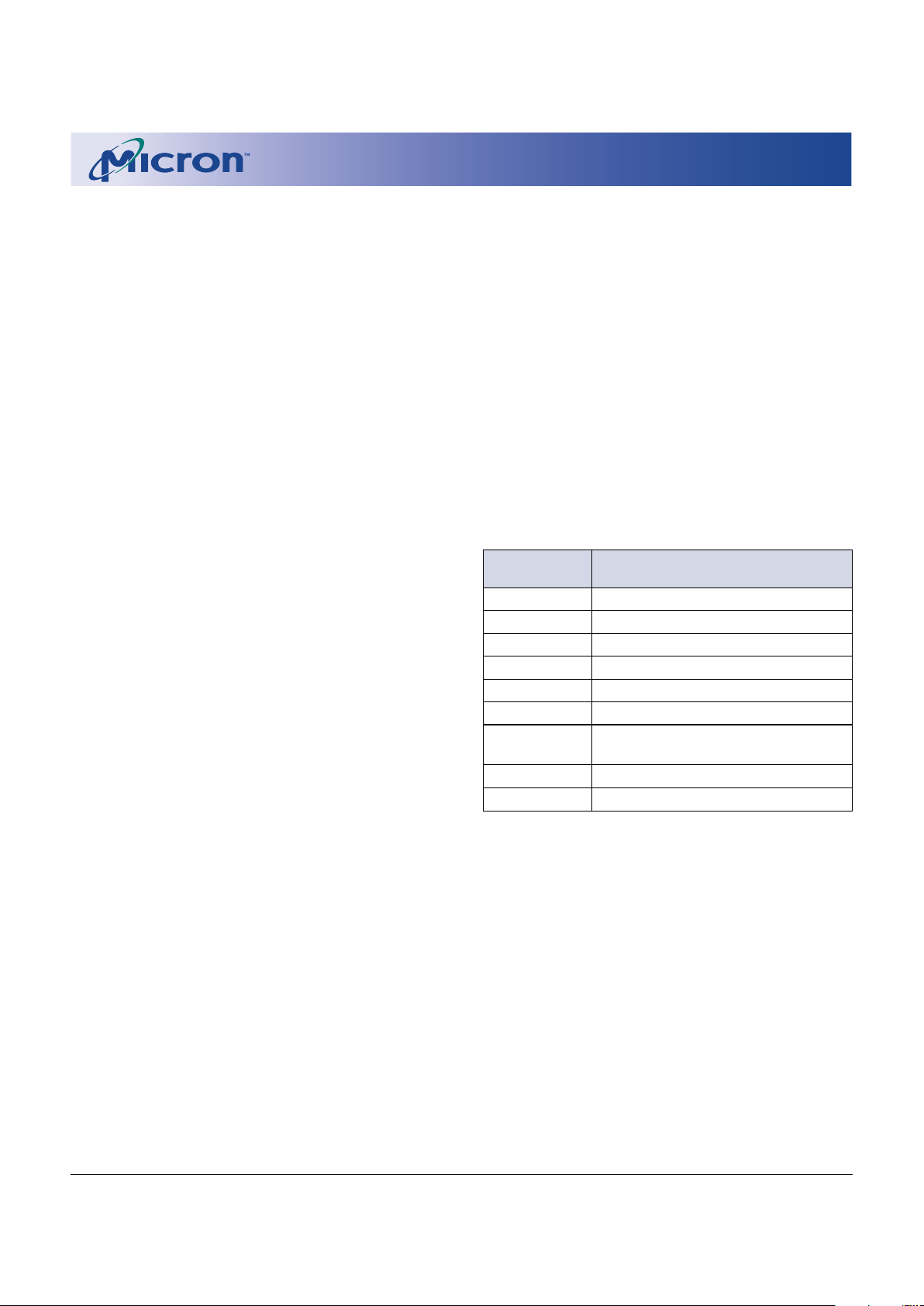

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

32K-Word Block

8 x 4K-Word Blocks

Boot Blocks

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

4K-Word Block

Parameter

Blocks

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

FFFFFh

F8000h

F7FFFh

F0000h

EFFFFh

E8000h

E7FFFh

E0000h

DFFFFh

D8000h

D7FFFh

D0000h

CFFFFh

C8000h

C7FFFh

C0000h

BFFFFh

B8000h

B7FFFh

B0000h

AFFFFh

A8000h

A7FFFh

A0000h

9FFFFh

98000h

97FFFh

90000h

8FFFFh

88000h

87FFFh

80000h

7FFFFh

78000h

77FFFh

70000h

6FFFFh

68000h

67FFFh

60000h

5FFFFh

58000h

57FFFh

50000h

4FFFFh

48000h

47FFFh

40000h

3FFFFh

38000h

37FFFh

30000h

2FFFFh

28000h

27FFFh

20000h

1FFFFh

18000h

17FFFh

10000h

0FFFFh

08000h

07FFFh

00000h

07FFFh

07000h

06FFFh

06000h

05FFFh

05000h

04FFFh

04000h

03FFFh

03000h

02FFFh

02000h

01FFFh

01000h

00FFFh

00000h

ADDRESS RANGE

Figure 2

Bottom Boot Block Memory Address Map

NOTE: 1. The two 4K-word blocks (boot blocks) can only be locked/unlocked by WP#.

7

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

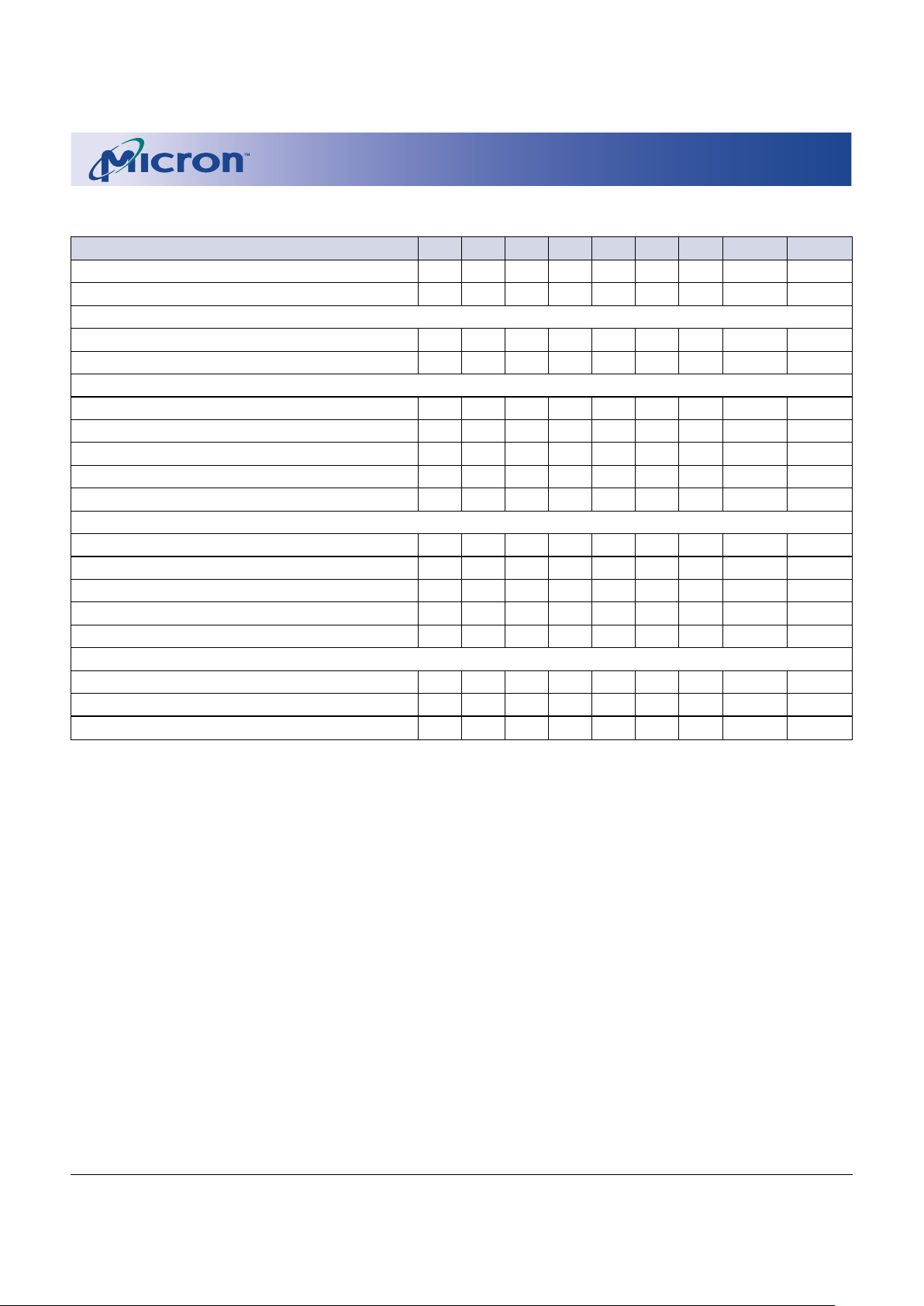

MEMORY ORGANIZATION

The MT28F160A3 memory array is segmented into 31

blocks of 32K words, along with eight 4K-word parameter

blocks. The device is available with block architecture

mapped in either of the two configurations: the boot

blocks located at the top or at the bottom of the memory

array, as required by different microprocessors. The

MT28F160A3 top boot configuration with the blocks and

address ranges is shown in Figure 1 and the bottom boot

configuration in Figure 2.

The boot blocks are used to store key system data and

are seldom changed during normal operation. When the

WP# is at VIL , the contents of the boot block cannot be

erased or reprogrammed. The boot block contents can be

changed only through proper command sequences when

WP# is HIGH (see Table 5).

COMMAND STATE MACHINE

Commands are issued to the command state machine (CSM) using standard microprocessor write timings. The CSM acts as an interface between the external

microprocessor and the internal write state machine

(WSM). The available commands are listed in Table 2,

and the descriptions of these commands are shown in

Table 3. Program and erase algorithms are automated by

an on-chip WSM. Once a valid program/erase command

sequence is entered, the WSM executes the appropriate

algorithm, which generates the necessary timing signals

to control the device internally to accomplish the requested operation. A command is valid only if the exact

sequence of WRITEs is completed. After the WSM completes its task, the WSM status bit (SR7) is set to a logic

HIGH level (1), allowing the CSM to respond to the full

command set again.

OPERATION

Device operations are selected by entering standard

JEDEC 8-bit command codes with conventional microprocessor timings into an on-chip CSM through I/Os

DQ0-DQ7. When the device is powered up, internal reset

circuitry initializes the chip to a read array mode of operation. Changing the mode of operation requires that a

command code be entered into the CSM. The on-chip

status register allows the progress of various operations

to be monitored. The status register is interrogated by

entering a READ STATUS REGISTER command onto the

CSM (cycle 1) and reading the register data on I/Os DQ0DQ7 (cycle 2). Status register bits SR0-SR7 correspond to

DQ0-DQ7 (see Table 3).

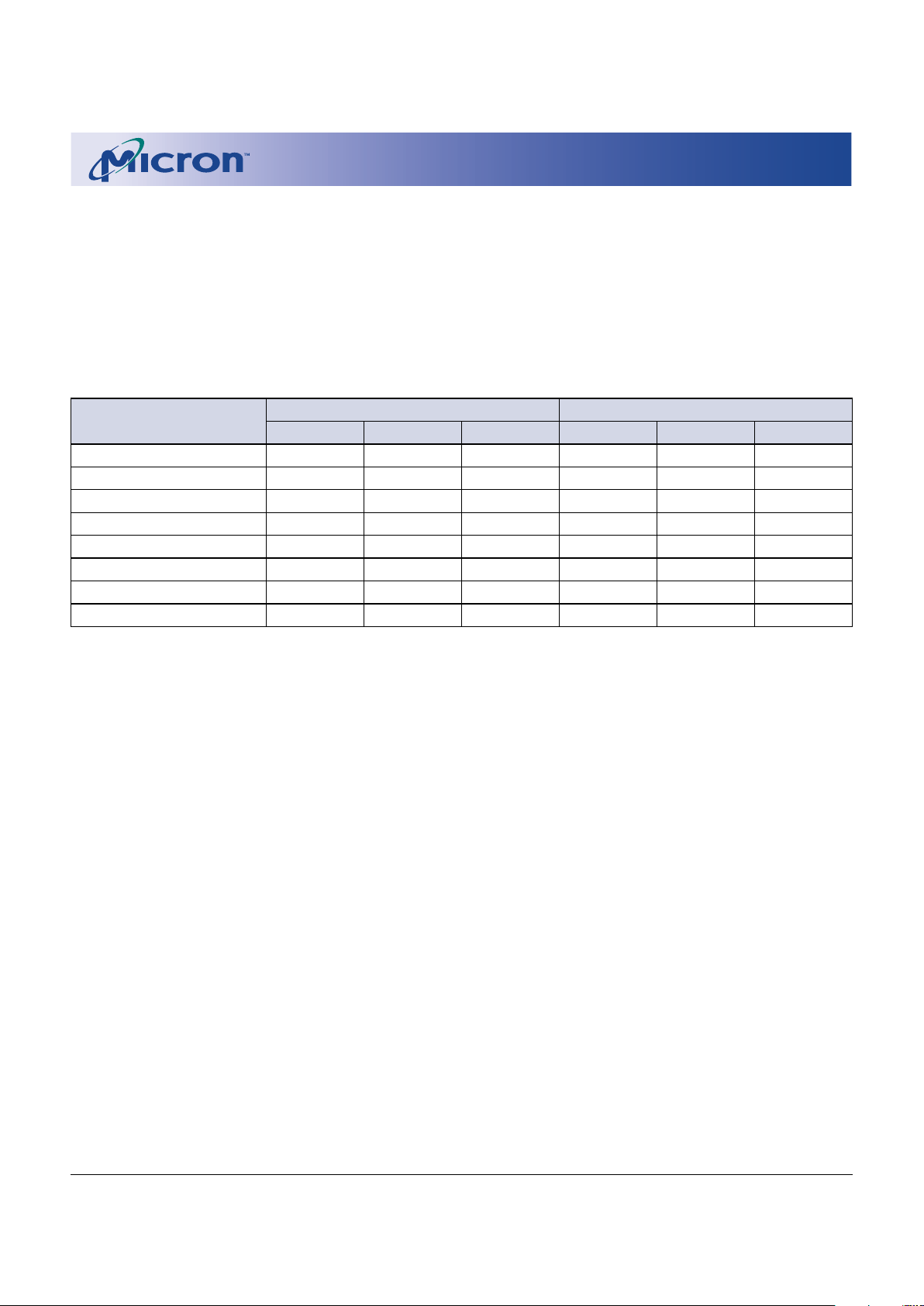

Table 2

Command State Machine Codes for

Device Mode Selection

COMMAND CODE ON

DQ0-DQ7 DEVICE MODE

10h/40h Write setup/alternate write setup

20h Block erase setup

50h Clear status register

70h Read status register

90h Identify device

B0h Program/erase suspend

D0h Program/erase resume

Erase confirm

FFh Read array

60h, 0Fh, AFh Reserved

8

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

Table 3

Command Definitions

FIRST CYCLE SECOND CYCLE

COMMAND OPERATION ADDRESS CSM/INPUT OPERATION ADDRESS DATA

READ ARRAY WRITE X FFh READ WA AD

IDENTIFY DEVICE WRITE X 90h READ IA ID

READ STATUS REGISTER WRITE X 70h READ BA SRD

WORD PROGRAM WRITE X 10h/40h WRITE WA PD

BLOCK ERASE WRITE X 20h WRITE BA D0h

PROGRAM/ERASE SUSPEND WRITE X B0h

PROGRAM/ERASE RESUME WRITE X D0h

CLEAR STATUS REGISTER WRITE X 50h

COMMAND DEFINITIONS

Once a specific command code has been entered, the

WSM executes an internal algorithm generating the necessary timing signals to program, erase, and verify data.

See Table 3 for the CSM command definitions and data

for each of the bus cycles.

NOTE: 1. The command data is written through DQ0-DQ7

2. ID = Manufacturer ID: 002Ch; Device ID (Top Boot): 4490h; Device ID (Bottom Boot): 4491h

3. IA = Identify address: 00000h for manufacturer code and 00001h for device code

4. BA = Any address within the block to be selected

5. WA = Word address

6. AD = Array data

7. SRD = Data read from status register

8. PD = Data to be written at location WA

9. X = Don’t Care

9

1 Meg x 16 Enhanced Boot Block Flash Memory Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT28F160A3_3.p65 – Rev. 3, Pub. 8/01 ©2001, Micron Technology, Inc.

1 MEG x 16

ENHANCED BOOT BLOCK FLASH MEMORY

ADVANCE

STATUS REGISTER

The status register allows the user to determine

whether the state of a PROGRAM/ERASE operation is

pending or complete. The status register is monitored by

toggling OE# and CE# and by reading the resulting status

code on I/Os DQ0-DQ7. The high-order I/Os (DQ8-DQ15)

are set to 00h internally, so only the low-order I/Os (DQ0DQ7) need interpreting.

Register data is updated on the falling edge of OE# or

CE#. The latest falling edge of either of these two signals

updates the latch within a given READ cycle. Latching the

data prevents errors from occurring if the register input

changes during a status register monitoring. To ensure

that the status register output contains updated status

data, CE# or OE# must be toggled for each subsequent

STATUS READ.

The status register provides the internal state of the

WSM to the external microprocessor. During periods

when the WSM is active, the status register can be polled

to determine the WSM status. Table 4 defines the status

register bits.

After monitoring the status register during a PROGRAM/ERASE, the data appearing on DQ0-DQ7 remains

as status register data until a new command is issued to

the CSM. To return the device to other modes of operation, a new command must be issued to the CSM.

COMMAND STATE MACHINE

OPERATIONS

The CSM decodes instructions for read, read device

identification code, read status register, clear status register, program, erase, erase suspend, erase resume, program suspend, and program resume. The 8-bit command code is input to the device on DQ0-DQ7 (see Table

2 for CSM codes). During a PROGRAM or ERASE cycle,

the CSM informs the WSM that a PROGRAM or ERASE

cycle has been requested.

During a PROGRAM cycle, the WSM controls the program sequences and the CSM responds to a PROGRAM

SUSPEND command only. During an ERASE cycle, the

CSM responds to an ERASE SUSPEND command only.

When the WSM has completed its task, the WSM status

bit (SR7) is set to a logic HIGH level and the CSM responds

to the full command set. The CSM stays in the current

command state until the microprocessor issues another

command.

The WSM successfully initiates an ERASE or PROGRAM operation only when VPP is within its correct voltage range. For data protection, it is required that RP# be

held at a logic LOW level during a CPU reset.

CLEAR STATUS REGISTER

The WSM can set to “1” the block lock status bit (SR1),

the VPP status bit (SR3), the program status bit (SR4), and

the erase status bit (SR5) of the status register. The CLEAR

STATUS REGISTER command (50h) allows the external

microprocessor to clear these status bits and synchronize to internal operations. After issuing this command,

the status bits are cleared and the device returns to the

read array mode.

READ OPERATIONS

Three READ operations are available: read array, read

device identification code, and read status register.

READ ARRAY

The array is read by entering the command code FFh

on DQ0-DQ7. Control signals CE# and OE# must be at a

logic LOW level (VIL) and WE# and RP# must be at a logic

HIGH level (VIH) to read data from the array. Data is

available on DQ0-DQ15. Any valid address within any of

the blocks selects that address and allows data to be read

from that address. Upon initial power-up, the device

defaults to the read array mode.

READ DEVICE IDENTIFICATION CODE

Device identification codes are read by entering command code 90h on DQ0-DQ7. Two bus cycles are required for this operation, the first to enter the command

code and the second to read the selected code. Control

signals CE# and OE# must be at a logic LOW level (VIL)

and WE# and RP# must be at a logic HIGH level (VIH). The

manufacturer code is obtained on DQ0-DQ15 in the second cycle, after the identify address 00000h is latched.

The device code is obtained on DQ0-DQ15 in the second

cycle, after the identify address 00001h is latched (see

Table 3).

READ STATUS REGISTER

The status register is read by entering the command

code 70h on DQ0-DQ7. Control signals CE# and OE#

must be at a logic LOW level (VIL), and WE# and RP# must

be at a logic HIGH level (VIH). Two bus cycles are required

for this operation: one to enter the command code, and

one to read the status register. The status register contents are updated on the falling edge of CE# or OE#,

whichever occurs last within the cycle.

Loading...

Loading...