Micro Linear Corporation ML65F16244CT, ML65F16244CR Datasheet

June 1998

PRELIMINARY

ML65F16244*

16-Bit Buffer/Line Driver with 3-State Outputs

GENERAL DESCRIPTION

The ML65F16244 is a BiCMOS, 16-bit buffer/line driver

with 3-state outputs. This device was specifically designed

for high speed bus applications. Its 16 channels support

propagation delay of 2ns maximum, and fast output

enable and disable times of 5ns or less to minimize

datapath delay.

This device is designed to minimize undershoot,

overshoot, and ground bounce to decrease noise delays.

These transceivers implement a unique digital and analog

implementation to eliminate the delays and noise

inherent in traditional digital designs. The device offers a

new method for quickly charging up a bus load capacitor

to minimize bus settling times, or FastBus™ Charge.

FastBus Charge is a transition current, (specified as

I

DYNAMIC

on output load) of current during the rise time and fall

time. This current is used to reduce the amount of time it

takes to charge up a heavily-capacitive loaded bus,

effectively reducing the bus settling times, and

improving data/clock margins in tight timing budgets.

Micro Linear’s solution is intended for applications for

critical bus timing designs that include minimizing

device propagation delay, bus settling time, and time

delays due to noise. Applications include; high speed

memory arrays, bus or backplane isolation, bus to bus

bridging, and sub-2ns propagation delay schemes.

) that injects between 60 to 200mA (depending

FEATURES

■ Low propagation delays — 2ns maximum for 3.3V,

2.5ns maximum for 2.7V

■ Fast output enable/disable times of 5ns maximum

■ FastBus Charge current to minimize the bus settling

time during active capacitive loading

■ 2.7 to 3.6V V

LV-TTL compatible input and output levels with 3-state

capability

■ Industry standard pinout compatible to FCT, ALV, LCX,

LVT, and other low voltage logic families

■ ESD protection exceeds 2000V

■ Full output swing for increased noise margin

■ Undershoot and overshoot protection to 400mV

typically

■ Low ground bounce design

supply operation;

CC

The ML65F16244 follows the pinout and functionality of

the industry standard 2.7V to 3.6V-logic families.

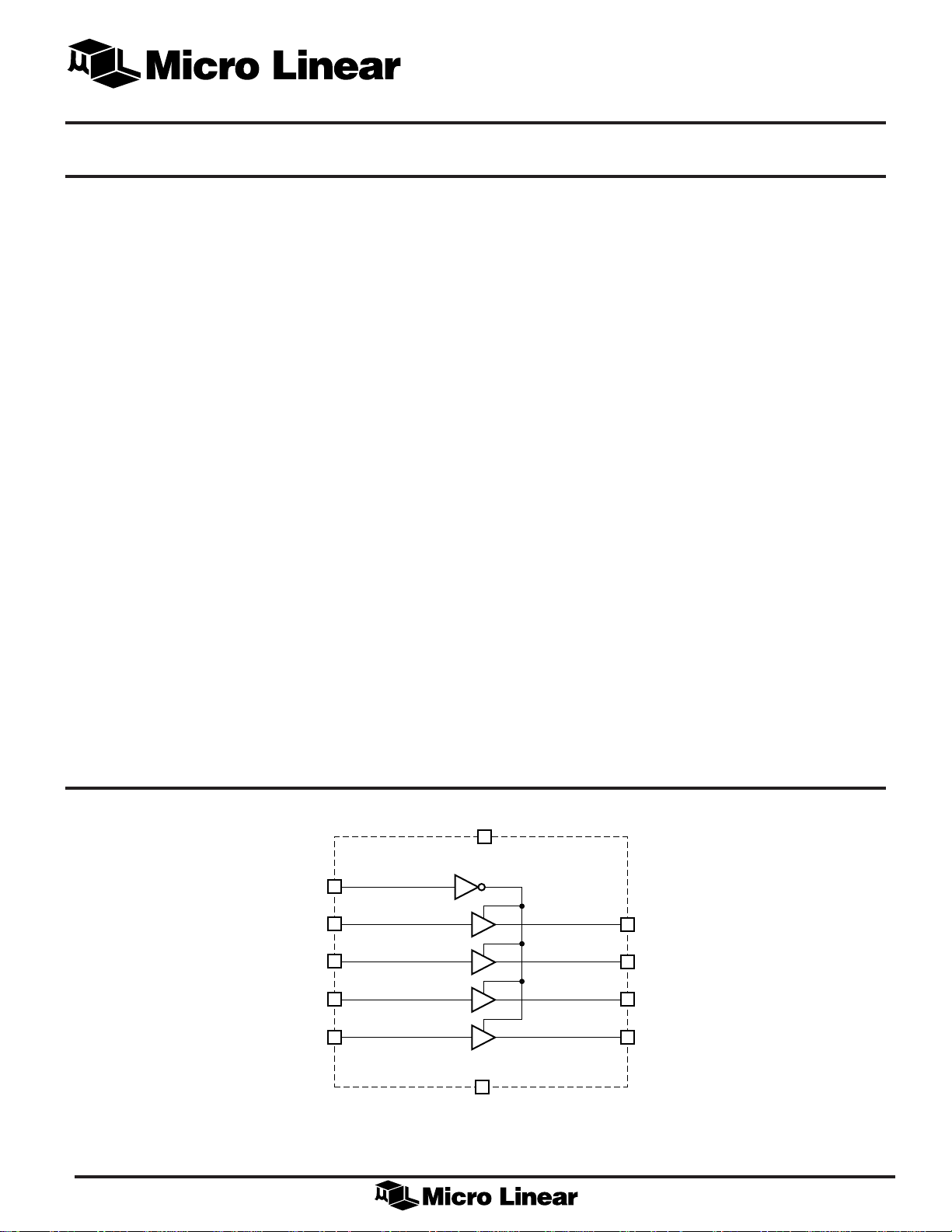

BLOCK DIAGRAM

OE

A0

A1

A2

A3

* This Part Is End Of Life As Of August 1, 2000

V

CC

B0

B1

B2

B3

GND

1 of 4

1

ML65F16244

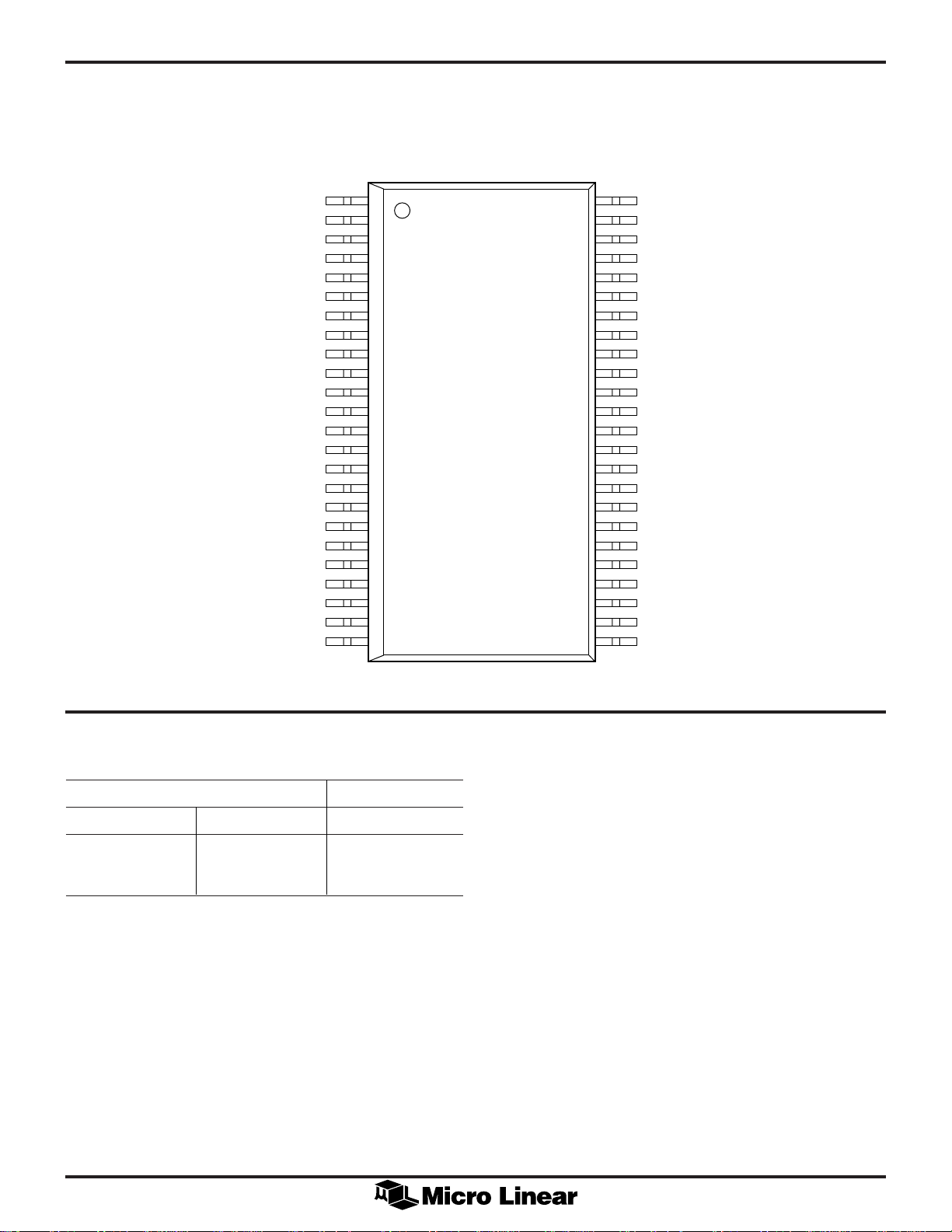

PIN CONFIGURATION

1OE

1B0

1B1

GND

1B2

1B3

V

CC

2B0

2B1

GND

2B2

2B3

3B0

3B1

GND

3B2

3B3

V

CC

4B0

4B1

GND

4B2

4B3

4OE

ML65F16244

48-Pin SSOP (R48)

48-Pin TSSOP (T48)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

2OE

1A0

1A1

GND

1A2

1A3

V

CC

2A0

2A1

GND

2A2

2A3

3A0

3A1

GND

3A2

3A3

V

CC

4A0

4A1

GND

4A2

4A3

3OE

FUNCTION TABLE

(Each 4-bit section)

INPUTS OUTPUTS

OE 1Ai, 2Ai, 3Ai, 4Ai 1Bi, 2Bi, 3Bi, 4Bi

LHH

LLL

HXZ

L = Logic Low, H = Logic High, X = Don’t Care, Z = High Impedance

TOP VIEW

2

PIN DESCRIPTION

ML65F16244

PIN NAME FUNCTION

11OE Output Enable

2 1B0 Data Output

3 1B1 Data Output

4 GND Signal Ground

5 1B2 Data Output

6 1B3 Data Output

7V

8 2B0 Data Output

9 2B1 Data Output

10 GND Signal Ground

11 2B2 Data Output

12 2B3 Data Output

13 3B0 Data Output

CC

2.7V to 3.6V Supply

PIN NAME FUNCTION

25 3OE Output Enable

26 4A3 Data Input

27 4A2 Data Input

28 GND Signal Ground

29 4A1 Data Input

30 4A0 Data Input

31 V

32 3A3 Data Input

33 3A2 Data Input

34 GND Signal Ground

35 3A1 Data Input

36 3A0 Data Input

37 2A3 Data Input

CC

2.7V to 3.6V Supply

14 3B1 Data Output

15 GND Signal Ground

16 3B2 Data Output

17 3B3 Data Output

18 V

19 4B0 Data Output

20 4B1 Data Output

21 GND Signal Ground

22 4B2 Data Output

23 4B3 Data Output

24 4OE Output Enable

CC

2.7V to 3.6V Supply

38 2A2 Data Input

39 GND Signal Ground

40 2A1 Data Input

41 2A0 Data Input

42 V

43 1A3 Data Input

44 1A2 Data Input

45 GND Signal Ground

46 1A1 Data Input

47 1A0 Data Input

48 2OE Output Enable

CC

2.7V to 3.6V Supply

3

Loading...

Loading...